# FPGA BASED DESIGN OF ON-CHIP PERIPHERAL (OPB) BUS BRIDGES FOR MULTIMEDIA APPLICATIONS

# **A DISSERTATION**

Submitted in partial fulfilment of the requirements for the award of the degree

0Î

MASTER OF TECHNOLOGY

in

# **ELECTRICAL ENGINEERING**

(With Specialization in System Engineering and Operations Research)

By

# PARVEEN KUNDU

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE-247 667 (INDIA)

JUNE, 2005

# **CANDIDATE'S DECLARATION**

I hereby declare that the work presented in this dissertation entitled "FPGA BASED DESIGN OF ON-CHIP PERIPHERAL (OPB) BUS BRIDGES FOR MULTIMEDIA APPLICATIONS" submitted in partial fulfillment of the requirements for the award of degree of Master of Technology in Electrical Engineering with specialization in System Engineering and Operations Research, in the Department of Electrical Engineering, Indian Institute of Technology Roorkee, Roorkee, is an authentic record of my own work carried out from July 2004 to June 2005 under the guidance of Prof.M.K.Vasantha, Professor and Dr.Indra Gupta, Asstt Professor, Department of Electrical Engineering, Indian Institute of Technology Roorkee,

The matter embodied in this report has not been submitted by me for the award of any other degree or diploma.

Date: 29 JUNE 2005 Place: Roorkee

Valveen Knohn

(PARVEEN KUNDU)

### CERTIFICATE

This is to certify that the above statement made by the candidate is true to the best of my knowledge and belief.

I

**Prof. M.K.Vasantha** Brofessor Department Of Electrical Engineering Indian Institute of Technology Roorkee. Roorkee.

Dr.\Indra Gupta Asst Professor Department of Electrical Engineering Indian Institute of Technology Roorkee Roorkee. I take this opportunity to express my sincere gratitude to **Prof.M.K.Vasantha**, Professor, and **Dr.Indra Gupta**, Asstt Professor, Department of Electrical Engineering, Indian Institute of Technology Roorkee, Roorkee for encouraging me to undertake this dissertation as well as providing me their valuable guidance and inspirational support without which this work would not have been in present shape.

I consider myself extremely fortunate for having got the opportunity to learn and work under their able supervision. They provided me the latest technology to work on and state of the art facilities and equipments at the lab. Their able guidance ensured me that I should not have any lack of resources while carrying out my thesis work. I have deep sense of admiration for their innate goodness and inexhaustible enthusiasm. The valuable hours of discussions and suggestions that I had with them have undoubtedly helped in supplementing my thoughts in the right direction for attaining the desired objective. Working under their guidance will always remain a cherished experience in my memory and I will adore it throughout my life.

I am also thankful to **Dr. H.O Gupta**, Professor and Head of Department of Electrical Engineering, IIT Roorkee for helping me in my dissertation work. I am especially thankful to him for providing us the technical training in M/S Mechtaronics, Pune which was pivotal in completion of my work.

My heartfelt gratitude and indebtedness goes to all the teachers of SEOR group who, with their encouraging and caring words, constructive criticism and suggestions, have contributed directly or indirectly in a significant way towards completion of this report.

I am highly grateful to Mr.Rahul Dubey, Research scholar, Department of Electrical Engineering, Indian Institute of Technology Roorkee, and Roorkee for his keen interest and generous encouragement during this venture.

I am especially thankful to Major Seby Thomas for his feedback in the class. His ideas and discussions not only helped in technical areas but also in personality development.

I am also thankful to Mr.Vishal Saxena and Mr.Vijender Singh Research Scholar for their valuable guidance in the hour of need.

Π

I am thankful to Mr. Kalyan Singh and Mr. C.M Joshi, Laboratory staff of Micro Processor & Computer Lab for providing the required facilities and co-operation during this work.

Special, sincere and heartfelt gratitude goes to my parents and my friends whose sincere prayers, best wishes, support and encouragement have been a constant source of assurance, guidance, strength and inspiration to me.

Paeveen Kindu

PARVEEN KUNDU

## ABSTRACT

With the recent advancements in silicon densities it is now possible to integrate numerous functions onto a single silicon chip. With this increased density, the peripherals that were formerly attached to the processor at the card level are now integrated onto the same chip as the processor. Even it is possible now that the chip may contain several processors. Now a days this technology is popularly known as System-on-Chip (SoC).

As large numbers of peripherals are present on the single chip, on-chip buses are required to connect peripherals and the processor. With this aim in mind on-chip peripheral bus (OPB) and Processor Local Bus (PLB) were designed to integrate the different components as a complete system.

On-chip Peripheral Bus (OPB) and Processor Local Bus (PLB) have different functions to perform.OPB is used for connecting slower peripherals and PLB for connecting faster peripherals that operate almost at the same speed as that of the processor .For carrying out the transaction between slower and faster components attached to the different buses bridges are designed called PLB to OPB bridge and OPB to PLB bridge.

Xilinx has designed a tool called Embedded Development Kit (EDK) 6.3 that eases the designing of the complete embedded system .This dissertation uses this tool to design application. OPB, PLB and bus bridges have been used to carry out the connectivity of the peripherals and the processor. Virtex-II Pro FPGA, one of the most sophisticated FPGA available till date is used to realize the design in real time.

Virtex-II Pro-PCI Video Card has been used in this dissertation for implementing the Multimedia Application. Power PC that is embedded into the Virtex-II Pro FPGA has been used as processing unit of the embedded design.PLB to OPB Bridge has been used to connect the multimedia application to the Power PC.These bridges acts as a link between devices connected to different buses.

Xilinx design tool ISE 6.3 has been used to actually Place and Route the design on the Virtex-II Pro FPGA.

# CONTENTS

|                                                        | Page No.   |

|--------------------------------------------------------|------------|

| CANDIDATES'S DECLARATION                               | I          |

| ACKNOWLEDGEMENTS                                       | Π          |

| ABSTRACT                                               | IV         |

| LIST OF FIGURES                                        | VII        |

| ABBREVIATION AND ACRONYMS                              | VIII       |

| INTRODUCTION                                           | 1          |

| CHAPTER 1: TECHNOLOGY AND BACKGROUND                   | 3          |

| 1.1. System on Chip (SoC)                              | 3          |

| 1.2. Application Specific Integrated Circuits (ASIC's) | 3          |

| 1.3. Programmable Logic Devices (PLD's)                | 4          |

| 1.4. Field Programmable Gate Arrays (FPGA's)           | 4          |

| 1.5. Hardware Description Languages (HDL's)            | 4          |

| 1.6. Active HDL.                                       | 4          |

| 1.7. Processors Cores                                  | 4          |

| 1.7.1. Soft Processor.                                 |            |

| 1.7.2. Hard Processor                                  | 5<br>5     |

| 1.8. IBM Core connect Bus Architecture                 | 5          |

| 1.9. Embedded Development Kit                          | 6          |

| 1.10. ISE.                                             | 7          |

| 1.11. Bus Bridges                                      | 7          |

| CHAPTER 2: EMBEDDED SYSTEM TOOLS                       | 8          |

| 2.1. Embedded development Kit (EDK)                    | 8          |

| 2.1.1. Xilinx Platform Studio                          | <b>9</b> · |

| 2.1.2. Base System Builder                             | 9          |

| 2.1.3. Create/Import IP Wizard                         | 10         |

| 2.1.4. Platform Generator                              | 10         |

| 2.1.5. Simulation Model Generator                      | 10         |

| 2.1.6. Library Generator                               | 10         |

| 2.1.7. Bitstream Initializer                           | 10         |

| 2.1.8. GNU Compiler Tools                              | 11         |

| 2.2. Tools Flow In the creation of Embedded System     | 11         |

| 2.2.1. Hardware Platform Creation                      | 11         |

| 2.2.2. Verification Platform Creation                  | 12         |

| 2.2.3. Software Platform Creation                      | 12         |

| 2.2.4. Software Application Creation and Verification  | 13         |

V

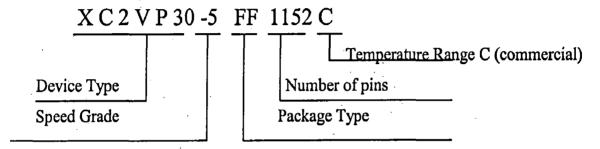

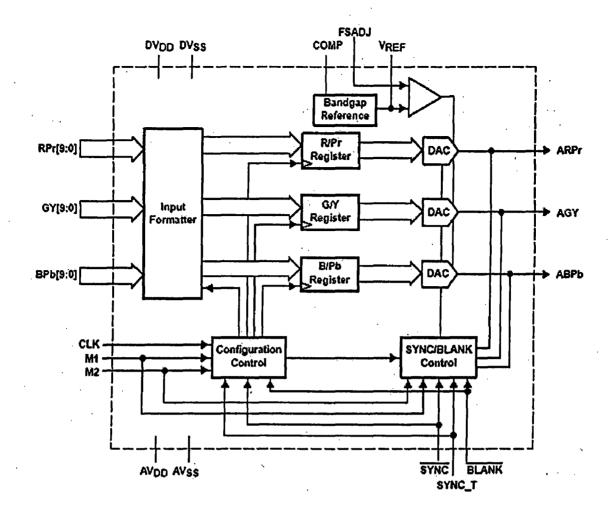

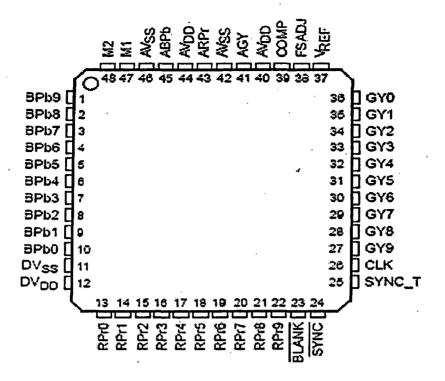

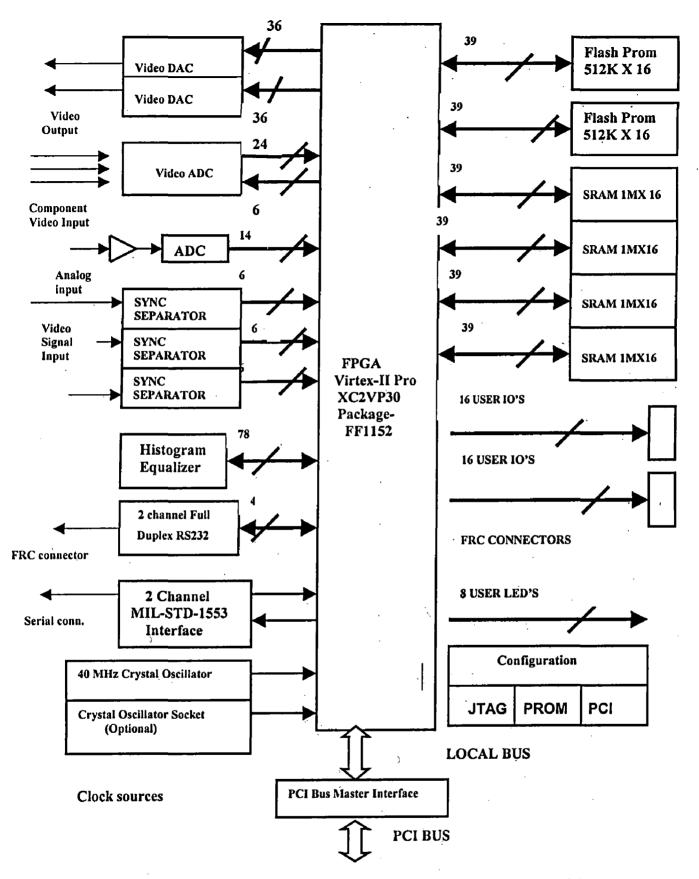

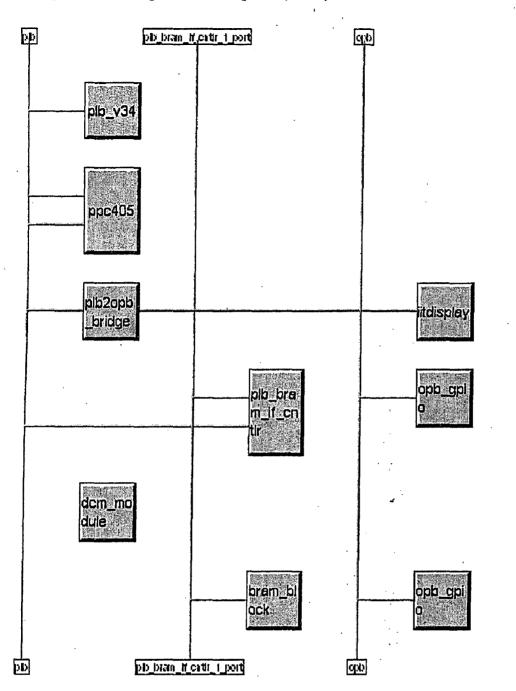

| CHAPTER 3: BUS BRIDGES IN EMBEDDED SYSTEMS       15         3.1. Introduction       15         3.2. Bridges in Embedded system design.       15         3.3. PLB to OPB Bridge       17         3.3.1. Interfaces in PLB to OPB Bridge.       19         3.4.OPB to PLB Bridge.       20         3.4.I. Interfaces in OPB to PLB Bridge.       22         CHAPTER 4: DESIGN OF EMBEDDED SYSTEM USING BUS BRIDGES       23         4.1. Introduction       23         4.2. Microblaze       23         4.3. Power PC       24         4.4. Design of embedded system using MicroBlaze       27         4.5. Design of embedded system using Power PC       28         4.6. On-chip Peripheral (OPB) Bus.       29         4.7. General Purpose Input Output       29         4.8. Virtex-II Pro FPGA.       30         4.9. Digital to Analog Converter (DAC) THS8133.       32         4.10. Multimedia Application using Virtex-II Pro and bridges       37         CONCLUSIONS       40         FUTURE SCOPE       41         REFERENCES       42         APPENDIX       A. Virtex-II Pro -PCI Video Board         B. Program Code (VHDL)       C. Program Code (C)         D. RESULTS       D. RESULTS |                                                             |             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------|

| 3.2. Bridges in Embedded system design.153.3. PLB to OPB Bridge173.3.1. Interfaces in PLB to OPB Bridge.193.4.0PB to PLB Bridge.203.4.1. Interfaces in OPB to PLB Bridge.22CHAPTER 4: DESIGN OF EMBEDDED SYSTEM USING BUS BRIDGES234.1. Introduction4.2. Microblaze234.3. Power PC244.4. Design of embedded system using MicroBlaze274.5. Design of embedded system using Power PC284.6. On-chip Peripheral (OPB) Bus.294.7. General Purpose Input Output294.8. Virtex-II Pro FPGA.304.9. Digital to Analog Converter (DAC) THS8133.324.10. Multimedia Application using Virtex-II Pro and bridges37CONCLUSIONS4041REFERENCES42A.PPENDIXA. Virtex-II Pro -PCI Video BoardB. Program Code (VHDL)C. Program Code (C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CHAPTER 3: BUS BRIDGES IN EMBEDDED SYSTEMS                  | 15          |

| 3.3. PLB to OPB Bridge173.3.1. Interfaces in PLB to OPB Bridge.193.4.OPB to PLB Bridge.203.4.1. Interfaces in OPB to PLB Bridge.22CHAPTER 4: DESIGN OF EMBEDDED SYSTEM USING BUS BRIDGES234.1. Introduction234.2. Microblaze234.3. Power PC244.4. Design of embedded system using MicroBlaze274.5. Design of embedded system using Power PC284.6. On-chip Peripheral (OPB) Bus.294.7. General Purpose Input Output294.8. Virtex-II Pro FPGA.304.9. Digital to Analog Converter (DAC) THS8133.324.10. Multimedia Application using Virtex-II Pro and bridges37CONCLUSIONS40FUTURE SCOPE41REFERENCES42APPENDIXA. Virtex-II Pro -PCI Video BoardB. Program Code (VHDL)C. Program Code (C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3.1. Introduction                                           | 15          |

| 3.3.1. Interfaces in PLB to OPB Bridge.193.4.OPB to PLB Bridge.203.4.1. Interfaces in OPB to PLB Bridge.22CHAPTER 4: DESIGN OF EMBEDDED SYSTEM USING BUS BRIDGES234.1. Introduction234.2. Microblaze234.3. Power PC4.4. Design of embedded system using MicroBlaze274.5. Design of embedded system using Power PC284.6. On-chip Peripheral (OPB) Bus.294.7. General Purpose Input Output294.8. Virtex-II Pro FPGA.304.9. Digital to Analog Converter (DAC) THS8133.324.10. Multimedia Application using Virtex-II Pro and bridges37CONCLUSIONS4040FUTURE SCOPE41REFERENCES42APPENDIXA. Virtex-II Pro –PCI Video BoardB. Program Code (VHDL)C. Program Code (C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | • • •                                                       | 15          |

| 3.4.OPB to PLB Bridge.203.4.I. Interfaces in OPB to PLB Bridge.22CHAPTER 4: DESIGN OF EMBEDDED SYSTEM USING BUS BRIDGES234.1. Introduction234.2. Microblaze234.3. Power PC244.4. Design of embedded system using MicroBlaze274.5. Design of embedded system using Power PC284.6. On-chip Peripheral (OPB) Bus.294.7. General Purpose Input Output294.8. Virtex-II Pro FPGA.304.9. Digital to Analog Converter (DAC) THS8133.324.10. Multimedia Application using Virtex-II Pro and bridges37CONCLUSIONS40FUTURE SCOPEFUTURE SCOPE41REFERENCES42APPENDIXA. Virtex-II Pro –PCI Video BoardB. Program Code (VHDL)C. Program Code (C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | · ·                                                         |             |

| 3.4.1. Interfaces in OPB to PLB Bridge.22CHAPTER 4: DESIGN OF EMBEDDED SYSTEM USING BUS BRIDGES234.1. Introduction234.2. Microblaze234.3. Power PC244.4. Design of embedded system using MicroBlaze274.5. Design of embedded system using Power PC284.6. On-chip Peripheral (OPB) Bus.294.7. General Purpose Input Output294.8. Virtex-II Pro FPGA.304.9. Digital to Analog Converter (DAC) THS8133.324.10. Multimedia Application using Virtex-II Pro and bridges37CONCLUSIONS4040FUTURE SCOPE41REFERENCES42APPENDIXA. Virtex-II Pro –PCI Video Board8. Program Code (VHDL)C. Program Code (C)1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                             |             |

| CHAPTER 4: DESIGN OF EMBEDDED SYSTEM USING BUS BRIDGES234.1. Introduction234.2. Microblaze234.3. Power PC244.4. Design of embedded system using MicroBlaze274.5. Design of embedded system using Power PC284.6. On-chip Peripheral (OPB) Bus.294.7. General Purpose Input Output294.8. Virtex-II Pro FPGA.304.9. Digital to Analog Converter (DAC) THS8133.324.10. Multimedia Application using Virtex-II Pro and bridges37CONCLUSIONS40FUTURE SCOPE41REFERENCES42APPENDIXA. Virtex-II Pro -PCI Video BoardB. Program Code (VHDL).C. Program Code (C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                             |             |

| 4.1. Introduction234.2. Microblaze234.3. Power PC244.4. Design of embedded system using MicroBlaze274.5. Design of embedded system using Power PC284.6. On-chip Peripheral (OPB) Bus.294.7. General Purpose Input Output294.8. Virtex-II Pro FPGA.304.9. Digital to Analog Converter (DAC) THS8133.324.10. Multimedia Application using Virtex-II Pro and bridges37CONCLUSIONS4040FUTURE SCOPE41REFERENCES42APPENDIXA. Virtex-II Pro –PCI Video Board8. Program Code (VHDL)C. Program Code (C)1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3.4.1. Interfaces in OPB to PLB Bridge.                     | 22          |

| 4.1. Introduction234.2. Microblaze234.3. Power PC244.4. Design of embedded system using MicroBlaze274.5. Design of embedded system using Power PC284.6. On-chip Peripheral (OPB) Bus.294.7. General Purpose Input Output294.8. Virtex-II Pro FPGA.304.9. Digital to Analog Converter (DAC) THS8133.324.10. Multimedia Application using Virtex-II Pro and bridges37CONCLUSIONS4040FUTURE SCOPE41REFERENCES42APPENDIXA. Virtex-II Pro –PCI Video Board8. Program Code (VHDL)C. Program Code (C)1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CHAPTER 4. DESIGN OF EMBEDDED SYSTEM USING BUS BRIDGES      | 23          |

| <ul> <li>4.2. Microblaze</li> <li>4.3. Power PC</li> <li>4.4. Design of embedded system using MicroBlaze</li> <li>4.4. Design of embedded system using Power PC</li> <li>4.5. Design of embedded system using Power PC</li> <li>4.6. On-chip Peripheral (OPB) Bus.</li> <li>4.6. On-chip Peripheral (OPB) Bus.</li> <li>4.7. General Purpose Input Output</li> <li>4.8. Virtex-II Pro FPGA.</li> <li>4.9. Digital to Analog Converter (DAC) THS8133.</li> <li>4.9. Digital to Analog Converter (DAC) THS8133.</li> <li>4.10. Multimedia Application using Virtex-II Pro and bridges</li> <li>40</li> <li>FUTURE SCOPE</li> <li>FUTURE SCOPE</li> <li>41</li> <li>REFERENCES</li> <li>42</li> <li>APPENDIX</li> <li>A. Virtex-II Pro -PCI Video Board</li> <li>B. Program Code (VHDL)</li> <li>C. Program Code (C)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                              |                                                             |             |

| 4.3. Power PC24.4.4. Design of embedded system using MicroBlaze274.5. Design of embedded system using Power PC284.6. On-chip Peripheral (OPB) Bus.294.7. General Purpose Input Output294.8. Virtex-II Pro FPGA.304.9. Digital to Analog Converter (DAC) THS8133.324.10. Multimedia Application using Virtex-II Pro and bridges37CONCLUSIONS4040FUTURE SCOPE41REFERENCES42APPENDIX4.A. Virtex-II Pro –PCI Video Board8.B. Program Code (VHDL)C. Program Code (C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                             |             |

| 4.5. Design of embedded system using Power PC 28<br>4.6. On-chip Peripheral (OPB) Bus. 29<br>4.7. General Purpose Input Output 29<br>4.8. Virtex-II Pro FPGA. 30<br>4.9. Digital to Analog Converter (DAC) THS8133. 32<br>4.10. Multimedia Application using Virtex-II Pro and bridges 37<br>CONCLUSIONS 40<br>FUTURE SCOPE 41<br>REFERENCES 42<br>APPENDIX<br>A. Virtex-II Pro –PCI Video Board<br>B. Program Code (VHDL)<br>C. Program Code (C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.3. Power PC                                               | <b>2</b> 4. |

| <ul> <li>4.6. On-chip Peripheral (OPB) Bus.</li> <li>4.7. General Purpose Input Output</li> <li>4.8. Virtex-II Pro FPGA.</li> <li>4.9. Digital to Analog Converter (DAC) THS8133.</li> <li>4.10. Multimedia Application using Virtex-II Pro and bridges</li> <li>37</li> </ul> CONCLUSIONS <ul> <li>40</li> <li>FUTURE SCOPE</li> <li>41</li> <li>REFERENCES</li> <li>42</li> </ul> APPENDIX <ul> <li>A. Virtex-II Pro –PCI Video Board</li> <li>B. Program Code (VHDL)</li> <li>C. Program Code (C)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.4. Design of embedded system using MicroBlaze             | 27          |

| <ul> <li>4.7. General Purpose Input Output</li> <li>4.8. Virtex-II Pro FPGA.</li> <li>4.9. Digital to Analog Converter (DAC) THS8133.</li> <li>4.10. Multimedia Application using Virtex-II Pro and bridges</li> <li>37</li> </ul> CONCLUSIONS <ul> <li>40</li> <li>FUTURE SCOPE</li> <li>41</li> <li>REFERENCES</li> <li>42</li> </ul> APPENDIX <ul> <li>A. Virtex-II Pro –PCI Video Board</li> <li>B. Program Code (VHDL)</li> <li>C. Program Code (C)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                             |             |

| 4.8. Virtex-II Pro FPGA. 30<br>4.9. Digital to Analog Converter (DAC) THS8133. 32<br>4.10. Multimedia Application using Virtex-II Pro and bridges 37<br>CONCLUSIONS 40<br>FUTURE SCOPE 41<br>REFERENCES 42<br>APPENDIX<br>A. Virtex-II Pro –PCI Video Board<br>B. Program Code (VHDL)<br>C. Program Code (C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                             |             |

| 4.9. Digital to Analog Converter (DAC) THS8133.324.10. Multimedia Application using Virtex-II Pro and bridges37CONCLUSIONS40FUTURE SCOPE41REFERENCES42APPENDIXA. Virtex-II Pro –PCI Video BoardB. Program Code (VHDL)C. Program Code (C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                             |             |

| 4.10. Multimedia Application using Virtex-II Pro and bridges 37<br>CONCLUSIONS 40<br>FUTURE SCOPE 41<br>REFERENCES 42<br>APPENDIX<br>A. Virtex-II Pro –PCI Video Board<br>B. Program Code (VHDL)<br>C. Program Code (C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                             |             |

| CONCLUSIONS40FUTURE SCOPE41REFERENCES42APPENDIX<br>A. Virtex-II Pro –PCI Video Board<br>B. Program Code (VHDL)<br>C. Program Code (C)40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                             |             |

| FUTURE SCOPE41REFERENCES42APPENDIX<br>A. Virtex-II Pro –PCI Video Board42B. Program Code (VHDL)<br>C. Program Code (C)42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4.10. Multimedia Application using vintex-11 FT0 and ondges | 51          |

| REFERENCES42APPENDIX<br>A. Virtex-II Pro –PCI Video BoardB. Program Code (VHDL)<br>C. Program Code (C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CONCLUSIONS                                                 | 40          |

| APPENDIX<br>A. Virtex-II Pro –PCI Video Board<br>B. Program Code (VHDL)<br>C. Program Code (C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | FUTURE SCOPE                                                | 41          |

| A. Virtex-II Pro –PCI Video Board<br>B. Program Code (VHDL)<br>C. Program Code (C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | REFERENCES                                                  | 42          |

| A. Virtex-II Pro –PCI Video Board<br>B. Program Code (VHDL)<br>C. Program Code (C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | APPENDIX                                                    |             |

| C. Program Code (C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                             |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | B. Program Code (VHDL)                                      |             |

| D. RESULTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | C. Program Code (C)                                         | •           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | D. RESULTS                                                  |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                             |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                             |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                             |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                             |             |

· ·

VI

| Figure No. | Title                                          | Page no. |

|------------|------------------------------------------------|----------|

| 1.1        | IBM Core Connect Structure                     | 6        |

| 2.1        | Embedded Software Tool Architecture            | 9        |

| 2.2        | Hardware Platform Creation                     | 11       |

| 2.3        | Verification Platform                          | 12       |

| 2.4        | Software Platform                              | 13       |

| 2.5        | Software Application Creation and Verification | 14       |

| 3.1        | On-chip bus structure                          | 16       |

| 3.2        | Block Diagram of PLB to OPB Bridge             | 18       |

| 3.3        | Block Diagram of OPB to PLB Bridge             | 21       |

| 4.1        | MicroBlaze Core Block Diagram                  | 23       |

| 4.2        | Power PC organization                          | 26       |

| 4.3        | Embedded System Design using MicroBlaze        | 27       |

| 4.4        | Embedded System Design using Power PC          | 28       |

| 4.5        | Block Diagram of DAC THS 8133                  | 34       |

| 4.6        | THS8133 DAC Pin Diagram                        | 36       |

| 4.7        | Multimedia Application using bus bridge        | 37       |

| 4.8        | IPIF Module connecting IP core                 | 39 .     |

|            |                                                |          |

# LIST OF FIGURES

# **ABBREVIATIONS**

| ADC  | Analog to Digital                        |

|------|------------------------------------------|

| ASIC | Application Specific Integrated Circuits |

| BRAM | Block Random Access Memory               |

| BSB  | Base System Builder                      |

| CLB  | Configurable Logic Blocks                |

| DAC  | Digital to Analog                        |

| DCM  | Digital Clock Manager                    |

| DCR  | Device Control Register Bus              |

| DLMB | Data Local Memory Bus                    |

| DMA  | Direct Memory Access                     |

| DOPB | Data On-Chip Peripheral Bus              |

| EDIF | Electronic Design Interchange Format     |

| EDK  | Embedded Development Kit                 |

| EMAC | Ethernet Media Access Control            |

| FIFO | First In First Out                       |

| FPGA | Field Programmable Gate Arrays           |

| FSL  | Fast Simplex Link                        |

| GPIO | General Purpose Input Output             |

| GUI  | General User Interface                   |

| HDL  | Hardware Description Language .          |

| HW   | Hardware                                 |

| IBM  | International Business Machines          |

| IOB  | Input Output Blocks                      |

| IP   | Intellectual Property                    |

| IPIF | Intellectual Property Interface          |

| JTAG | Joint Test Action Group                  |

| LUT  | Look Up Tables                           |

| MB   | MicroBlaze                               |

|      |                                          |

VIII

### INTRODUCTION

In near future, the microelectronics industry will face the reality of a billion transistors on a chip. Now it is not economical to use the chip for a single function, as large resources will remain unutilized. Therefore these days there is a growing trend towards designing the complete system on a single chip. This is popularly known as System-on-Chip (SoC) Technology. This technology allows the designer to implement a complete system on a single chip dedicated to particular application.

In an effort to implement the system from scratch the costs incurred are enormous and only a few companies can build the needed competency in all the design areas. In most cases, designers have to use intellectual property (IP) blocks, possibly originating from external vendors. IP blocks are predefined, large grained blocks, such as filters, peripherals, memories, and processors, whose function has been precisely specified. Designing a system based on reusable IP blocks challenges industry to develop new design methodologies and tools.

Xilinx has developed a tool called Embedded Development Kit (EDK) [6] to provide a solution to the problem of placing a complete system on the single chip using IP blocks from different sources. It provides the platform to integrate the IP's from different vendors with the resources available within the tool to design the system according to particular application. This approach is known as a plug and play environment.

Such an integration environment as provided by the Xilinx is typically a design platform for a specific application domain. The IP blocks are standard building blocks that can be easily integrated within the application domain. The integration platform consists of components such as a target hardware and software architecture, a portfolio of virtual components (IP blocks), and a design validation methodology.

A simple general-purpose processor core is the basic component in the integration platform. Xilinx have included two processor cores into the design, Microblaze [8] which is a soft processor and Power PC [11] core which is hard processor. These processor cores are integrated into the fabric of the chip. All the IP blocks are glued together through buses that communicate with the processor.

Two kinds of buses are introduced for the purpose of connecting different peripherals on the chip: the processor local bus (PLB) and the on-chip peripheral bus (OPB) [10]. The OPB is connected to the PLB through a module interface called Bus Bridge. There are two bus bridges available PLB to OPB Bridge[2] and OPB to PLB Bridge[4]. The PLB arbiter controls the PLB communications among the processor, memory and OPB bridge. The OPB arbiter controls the OPB communications among the IP blocks.

The IP blocks can be user-defined logic blocks or third party IP blocks. Other company which is also working in this area is ARM and they have designed there own on-chip bus known as AMBA.

FPGA's are the programmable logic devices that are used for real time testing for the system designed for the chips.Virtex-II Pro FPGA's [14] are the latest in the family of Xilinx devices which has almost all the features for designing the complex embedded system .

**CHAPTER-1**

# 1.1. System-on chip (SoC)

System-on chip is referred to devices where whole of the computing system is integrated on the one chip. Main features of SoC are:

- 1. Reduced chip interconnect.

- 2. Reduced power dissipation.

- 3. Reduced device size.

A typical SoC may contain one or many processor, on-chip memory, different types of bus structures, bridges to connect the different buses, an arbitrary number of peripherals connected to each other to form a complete circuit. The system on chip aims at providing only one circuit for any particular application. A SoC contains a large number of I/O interfaces to connect to the other circuits.

A SoC are designed with limited applications in mind and need less processing power then general purpose computer .An SoC processor works on only few MHz range while modern PC run on 500 MHz –GHz range. Frequency required to operate the SoC is just sufficient to run the design. Due to low frequency the power consumption and chip temperature is reduced and the system operates with less cooling devices and better battery utilization.

# **1.2.** Application Specific Integrated Circuits (ASIC's)

Application Specific Integrated Circuits (ASIC) is one of the common types of chip types ASIC can implement designs ranging from very simple to complex which are dedicated to specific application.ASIC are therefore customized for reduced power dissipation, less area and greater clock frequencies.ASIC have low mass production costs.

Main disadvantages of ASIC's are long design phases, low configurability and high start up costs. ASIC's are mainly used for large scale manufacturing of verified designs but not for prototypes.

# 1.3. Programmable Logic Device (PLD's)

This are also used to design systems whose complexity varies from simple combinatorial design to complex SoC's.

### 1.4. Field Programmable Gate Arrays (FPGA's)

Field Programmable Gate Arrays (FPGA) are a type of Programmable Logic Devices.FPGA is a general architecture consisting of configurable logic blocks and programmable interconnections. Several FPGA has enough logic to implement complex SoC's. FPGA's are not optimized for a particular design and therefore consume more power or implement a design less efficient then the ASIC's. Price per chip is high.

Advantages of FPGA's is that they are easy to reprogram, which shortens design cycles and allow early real world tests. This makes FPGA's well suited for prototypes and small production volumes.

# 1.5. Hardware Description Languages (HDL's)

Hardware Description Language (HDL) provides ways to design hardware .VHDL and Verilog are two popular hardware description Languages

### 1.6. Active HDL

This is the simulation software used to simulate VHDL design. Version 6.1 of this software has been used.

### **1.7.** Processor Cores.

Processor cores refer to a processor excluding any peripherals that are connected to it .In SoC one or more processors are connected to peripherals in a single chip.

There are three different types of processor cores:

- 1. Soft Processor core: Cores delivered as technology dependent gate-level netlist or HDL source code.

- 2. Firm processor cores: Cores delivered as library elements.

3. Hard processor cores: Cores which has a fixed physical layout and which are incorporated into the design as standard cell.

# 1.7.1. Soft Processor:

Soft Processor Core: These are the cores delivered as technology dependent gate-level netlist or HDL source code for synthesis. Soft processors have recently gained wide popularity .This popularity appears to more amongst the FPGA developers.

This popularity is mainly due to several factors as:

1. Increase in performance,

- 2. Increased in performance/price ratio on FPGA's.

- 3. Increased availability of both commercial and academic cores.

- 4. Free soft processors have been released by teams consisting of professionals, academics and enthusiasts (FPGACPU, OPENCORES).

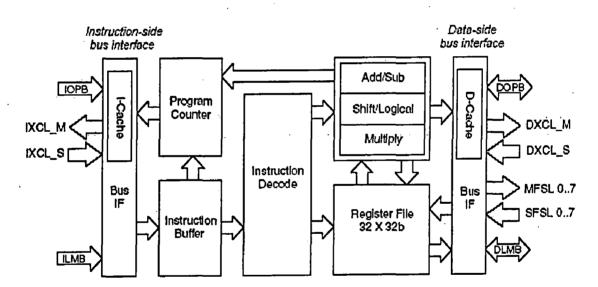

Microblaze [8] is such a soft processor core provided by the Xilinx.

### 1.7.2 Hard Processor:

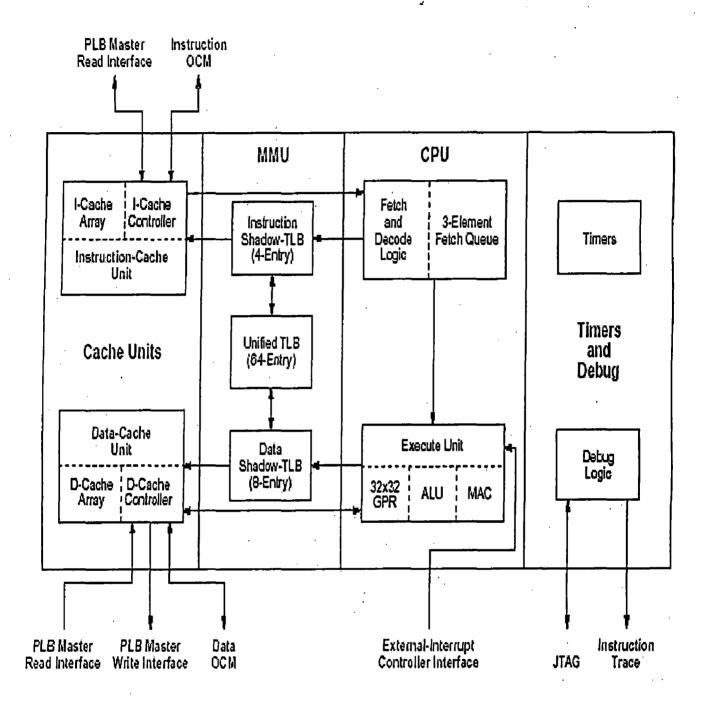

Power PC[11] is the hard processor .Xilinx have embedded the these hard processor into the FPGA Fabric from Virtex-II Pro FPGA families onwards.

### **1.8. IBM Coreconnect Bus Architecture:**

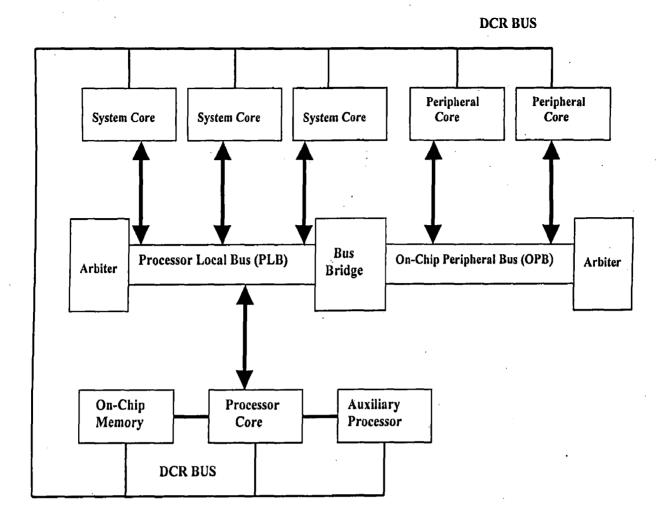

IBM Coreconnect Bus[1] Architecture is a small set of buses intended for SoC designs. The block diagram IBM Coreconnect structure is shown above in the Figure 1-1:

IBM Coreconnect features three buses:

- 1. Processor Local Bus (PLB): High performance bus for connecting fast processor cores and high performance peripherals (PCI interface, memory controllers) etc.

- 2. On-Chip Peripheral Bus (OPB): This is a simple bus for connecting slow peripherals like UART are connected to this bus.

- 3. Device Control Register bus (DCR): Control Bus that links to all of the devices, controllers and bridges.

By using these buses the overall SoC can be optimized for performance while simple peripherals may be optimized for simplicity.

Xilinx has developed the IBM Core connect OPB with most configurable OPB parameters set to specific values. Xilinx OPB is based on OR-Gates and does not use enable inputs which are used in IBM OPB which are used to assert when the bus is not used.

Xilinx OPB devices share the same parameters because of which they are compatible. Xilinx devices include Xilinx Microblaze Soft processor core, Xilinx Picoblaze Soft processor core and a large set of OPB peripherals.

## 1.9. Embedded Development Kit:

EDK[6] is a series of software tools for designing embedded programmable systems, and supports designs of processor sub-systems using the IBM PowerPC hard processor core and the Xilinx Microblaze soft processor core. It has graphical user interface Platform Studio that integrates all the processes from design entry to design debug and verification. This is used to design both simple and complex designs .EDK 6.3 has been used in this dissertation work though EDK7.1 has been launched in the market.

# 1.10. ISE:

This software is used to place and route the design into the FPGA.

# 1.11. Bus Bridges:

There are two bridges core recently introduced:

- 1. PLB to OPB Bridge.

- 2. OPB to PLB Bridge.

These two bridges PLB to OPB Bridge[2] and OPB to PLB[4] Bridge allow the PPC 405 to be connected to OPB devices. These bridges are used in the recently built Virtex -2 Pro boards.

### 2.1. Embedded Development Kit (EDK)

Embedded Development Kit (EDK)[6] 6.3 contains the rich set design tools and a wide selection of standard peripherals required to build embedded processor systems using MicroBlaze, the industry's fastest soft processor solution, and the new and unique feature in Virtex-II Pro, the IBM PowerPC CPU.

These tools, contains processor platform for particular application, software application development tool, a full featured debug tool chain and device drivers and libraries, which allows the developer to develop a System-On-Chip(SoC) design with the help of MicroBlaze[8] and Virtex-II Pro[14] based Power PC[11].

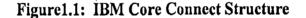

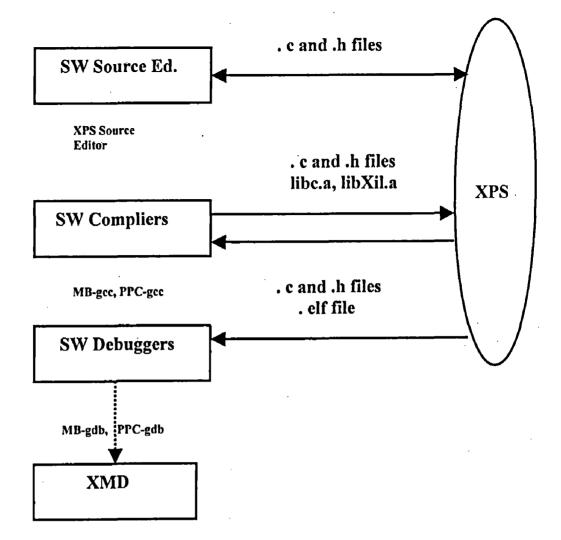

Figure 2.1 below shows embedded software tool architecture. Multiple tools based on a common framework allow the user to design the complete embedded system. System design consists of the creation of the hardware and software components of the embedded processor system, and optionally, a verification or simulation component as well. The hardware component consists of an automatically generated hardware platform that can be optionally extended to include other hardware functionality specified by the user.

The software component of the design consists of the software platform generated by the tools, along with the user designed application software. The verification component consists of automatically generated simulation models targeted to a specific simulator, based on the hardware and software components.

A typical embedded system design project involves the following phases:

- 1. Hardware platform creation,

- 2. Hardware platform verification (simulation),

- 3. Software platform creation,

- 4. Software application creation, and

- 5. Software verification (debugging).

Figure 2.1 Embedded Software Tool Architecture

### Embedded Development Kit contains the following tools in the design:

### 2.1.1. Xilinx Platform Studio

The Xilinx Platform Studio (XPS)[9] tool provides a GUI (General User Interface) for creating the MHS and MSS files for the hardware and software flow. XPS also provides source file editor capability and project and process management capability. XPS is used for managing the complete tool flow, that is, both hardware and software implementation flows.

### 2.1.2. Base System Builder

The Base System Builder (BSB) wizard is a software tool that helps users quickly build a working system targeted at a specific development board. BSB is invoked by XPS when the user wants to create a new system.

### 2.1.3. Create/Import IP Wizard

The Create/Import Peripheral[13] Wizard helps to create own peripherals and import them into EDK compliant repositories or Xilinx Platform Studio (XPS) projects. This wizard uses the Psf Utility tool to create the necessary Platform Specification files.

### 2.1.4. Platform Generator

The embedded processor system in the form of hardware net lists (HDL and EDIF files) is customized and generated by the Platform Generator (PlatGen).

### 2.1.5 Simulation Model Generator

The Simulation Platform Generation tool (simgen) generates and configures various simulation models for the hardware. It takes a Microprocessor Hardware Specification (MHS) file as input.

#### 2.1.6. Library Generator

XPS calls the Library Generator tool for configuring the software flow. The Library Generator (LibGen) tool configures libraries, device drivers, file systems and interrupt handlers for the embedded processor system. The input to LibGen is an MSS file.

#### 2.1.7. Bitstream Initializer

The Bitstream Initializer tool initializes the instruction memory of processors on the FPGA. The instruction memories of processors are stored in BlockRAMs in the FPGA. This utility reads an MHS file, and invokes the Data2MEM utility provided in ISE to initialize the FPGA BlockRAMs.

### 2.1.8. Platform Generator

The embedded processor system in the form of hardware net lists (HDL and EDIF files) is customized and generated by the Platform Generator (PlatGen).

### 2.1.9. Simulation Model Generator

The Simulation Platform Generation tool (simgen) generates and configures various simulation models for the hardware. It takes a Microprocessor Hardware Specification (MHS) file as input.

### 2.1.10. Library Generator

XPS calls the Library Generator tool for configuring the software flow. The Library Generator (LibGen) tool configures libraries, device drivers, file systems and interrupt handlers for the embedded processor system. The input to LibGen is an MSS file.

### 2.1.11. GNU Compiler Tools

XPS calls GNU compiler tools for compiling and linking application executables for each processor in the system.

# 2.2. Tools Flow In the creation of Embedded System:

### 2.2.1. Hardware Platform Creation

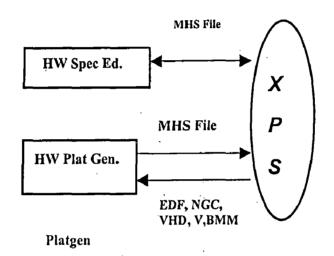

Xilinx Platform Studio[9] provides the Base System Builder Wizard for creating the Hardware Platform.Details of hardware platform creation are depicted in Figure 2.2

**Figure 2.2 Hardware Platform Creation**

### Microprocessor Hardware Specification (MHS):

The hardware platform is defined by the MHS (Microprocessor Hardware Specification) file. The hardware platform consists of one or more processors and peripherals connected to the processor buses. Several peripherals are provided with the software. Peripherals can be designed according to any particular applications and can be included into the MHS. The MHS file is a simple text file and any text editor can be used to create this file. The XPS tool provides graphical means to create the MHS file.

The MHS file defines the system architecture, peripherals and embedded processors. The MHS file also defines the connectivity of the system, the address map of each peripheral in the system and configurable options for each peripheral. Multiple processor instances connected to one or more peripherals through one or more buses and bridges can also be specified in the MHS.

### Platform Generator tool (PlatGen):

The Platform Generator tool (PlatGen) creates the hardware platform using the MHS file as input. PlatGen creates netlist files in various formats (NGC, EDIF), as well as support files for downstream tools, and top-level HDL wrappers to allow designers to add other components to the automatically generated hardware platform.

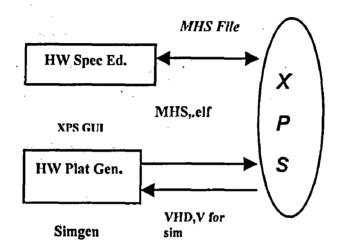

### 2.2.2. Verification Platform Creation

**Figure 2.3 Verification Platform**

The verification platform is based on the hardware platform. The MHS file is processed by the Simgen tool to create simulation files (VHDL, Verilog or various compiled models) along with some command files for specific simulators supported by the tool. As in the case of the hardware platform, edit these simulation files can be edited to add other components to the automatically generated verification platform. If the software application that runs on the hardware platform is available in executable format, it can be used to initialize memories in the verification platform. The processor of verification is shown in Figure 2.3.

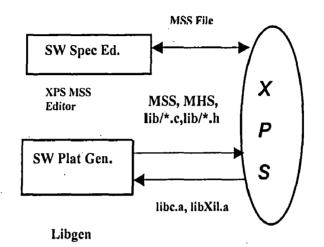

### 2.2.3. Software Platform Creation:

Microprocessor Software Specification (MSS) File:

The software platform is defined by the MSS (Microprocessor Software Specification) file. The MSS file defines driver and library customization parameters for peripherals, processor customization parameters, standard input/output devices, interrupt handler routines, and other

related software features. The MSS file is a simple text file and any text editor can be used to create this file. The XPS tool provides a graphical user interface for creating the MSS file.

The MSS file is an input to the Library Generator tool (LibGen) for customization of drivers, libraries and interrupt handlers. The entire process of creating the software platform is shown in Figure 2-4.

#### 2.2.4. Software Application Creation and Verification:

#### Software Application:

The software application is the code that runs on the hardware and software platforms. The source code for the application is written in a high level language such as C or C++, or in assembly language. XPS [9] provides a source editor for creating these files, but any other text editor may be used here. Once the source files are created, they are compiled and linked to generate executable files in the ELF (Executable and Link Format) format. GNU compiler tools for PowerPC and MicroBlaze are used by default.

### Verification:

XMD (Xilinx Microprocessor Debugger) and the GNU debugger (GDB) are used together to debug the software application. XMD provides an instruction set simulator, and optionally connects to a working hardware platform to allow GDB to run the user application. This process of Software Application Creation and Verification is depicted in Figure 2-5.

Figure 2-5 Software Application Creation and Verification

These processes help in the hardware and software co-design.

# 3.1. Introduction:

There are large numbers of buses following different standards for communicating with the peripherals attached to them. If a peripheral attached to a particular bus wants to carry out any transaction with any other peripheral attached to different bus then it will cause a problem in carrying out the desired operations. To solve this issue bridges are designed so that they take care o all the factors to make the communication work. The bridge takes care of all the issues of different buses operating at different frequencies, and having different data width. There are large number o bridges like PCI bridge that is used for providing the compatibility between the Processor and the outer peripherals. Similarly when a system is designed on the chip then processor will have its owr bus system and it will work at higher speed then the other peripherals. So a bridge becomes a necessity to connect on chip peripherals and also off chip peripherals.

# 2. Bridges in Embedded system design.

In embedded system there are two different types buses .The PLB and the OPB.So there are two bridges that are designed for carrying out the transactions between the devices connected to the either bus.

The two bridges available are:

- 1. PLB to OPB Bridge.

- 2. OPB to PLB Bridge.

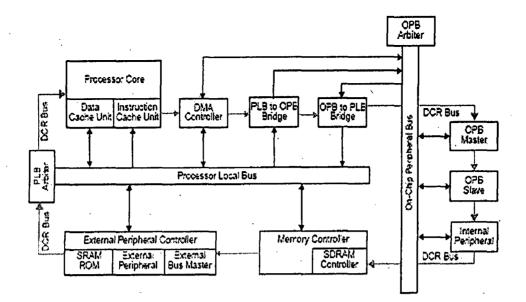

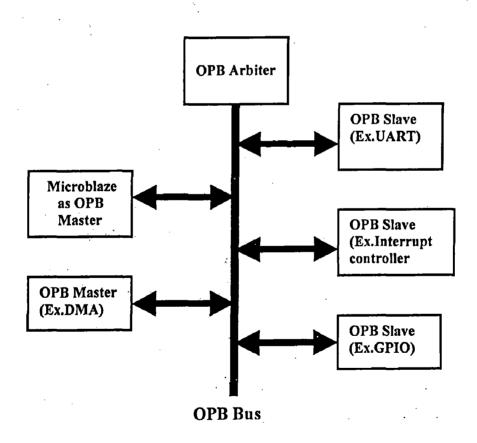

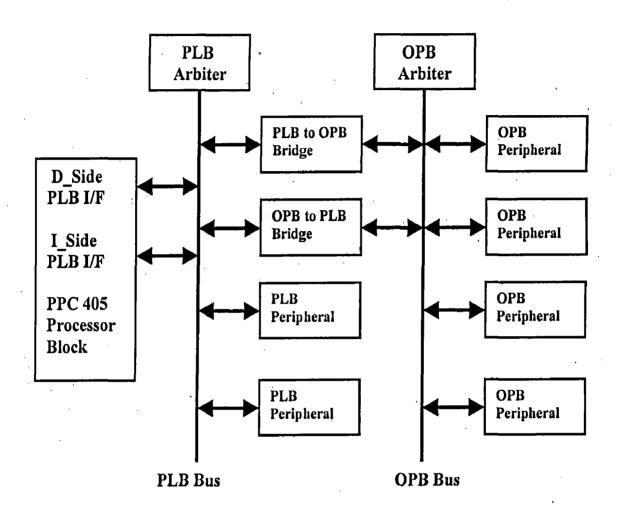

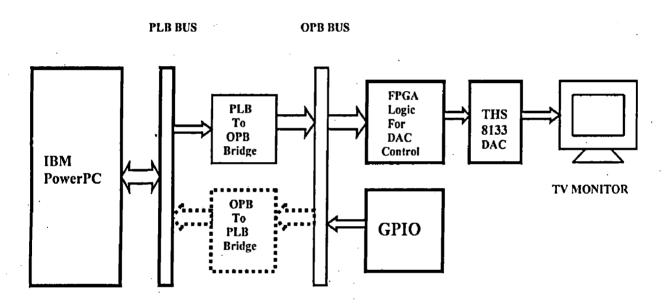

These bridges and the Processor Local Bus (PLB) are supported only with PowerPC, which are available with the Xilinx Virtex-2 Pro Devices onwards. Xilinx Microblaze soft processor core is used for designing simple systems with OPB.Microblaze does not support bridges architecture and Processor Local Bus (PLB). Microblaze is attached directly with OPB bus. Figure 3-1 demonstrates how the PLB to OPB Bridge and OPB to PLB Bridge are connected for the purpose of development of system-on-a-chip design.

Figure 3-1 On-Chip Bus Structure

As shown in Figure 3-1, the on-chip bus structure provides a link between the processor core and other peripherals which consist of PLB and OPB master and slave devices.

The processor local bus (PLB) is the high performance bus used to access memory through the bus interface units. The two bus interface units shown above: external peripheral controller and memory controller are the PLB slaves. The processor core has two PLB master connections, one for instruction cache and one for data cache. Attached to the PLB is also the direct memory access (DMA) controller, which is a PLB master device, used in data intensive applications to improve data transfer performance.

Lower performance peripherals (such as OPB master, slave, and other internal peripherals) are attached to the on-chip peripheral bus (OPB). A bridge is provided between the PLB and OPB to enable data transfer by PLB masters to and from OPB slaves. In the Figure 1 we have two bridges, a PLB to OPB Bridge which is a slave on the PLB and a master on the OPB and an OPB to PLB Bridge which is a slave on the OPB and a master on the PLB. OPB peripherals may also comprise DMA peripherals.

The device control register (DCR) bus is used primarily for accessing status and control registers within the various PLB and OPB masters and slaves. It is meant to off-load the PLB from the lower performance status and control read and writes transfers. The DCR bus architecture allows data transfers among OPB peripherals to occur independently from and concurrent with, data transfers between the processor and memory, or among other PLB devices.

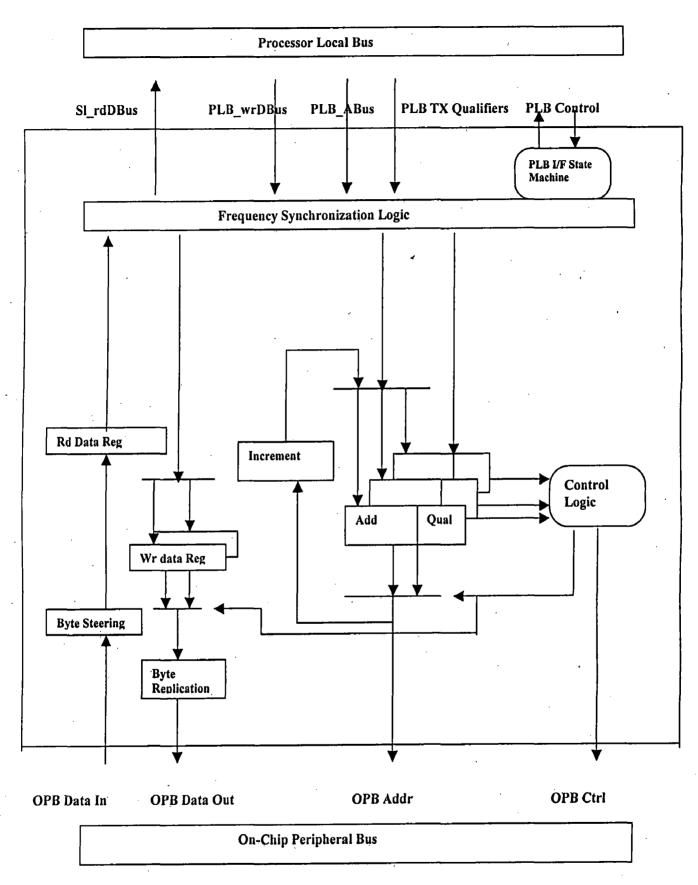

# 3.3. PLB to OPB Bridge:

The Processor Local Bus (PLB) to On-chip Peripheral Bus (OPB) Bridge translates PLB transactions into OPB transactions. It functions as a slave on the PLB side and a master on the OPB side. The bridge is required in those system designs which have OPB slave devices, which must be accessed by the processor.

#### Features of PLB to OPB Bridge[2]:

- 1. PLB slave device and OPB master device

- 2. External programmable address space via address decode pin (this allows the PLB to OPB bridge to be located anywhere in the address map.

- 3. Supports 8 PLB masters.

- 4. 64-bit PLB slave interface supports.

- Double Word (64-bit) writes or (32-bit writes) and Word (32-bit) reads

- All partial transfers

- 5. Supports word, halfword, and byte burst reads and writes, including fixed-length bursts.

- 6. Supports pipelining for read transfers.

- 7. Compliant with quad-, and octal-word bursts for upward compatibility.

- 8. Supports 4-, 8-, and 16-word line transfers.

- 9. OPB master performs dynamic bus sizing for varying width slave devices

- 10. Bus error log accessible through device control registers

Figure 3-2 Block Diagram of PLB to OPB Bridge

11. 66+ MHz OPB clock frequency.

12. Support for PLB bus-speeds at 1x, 2x, 3x, or 4x the frequency of the OPB.

13. Watchdog timer for implementations omitting OPB arbiter.

# 3.3.1. Interfaces in PLB to OPB Bridge

### PLB Interface:

The PLB to OPB Bridge [2] interfaces to the PLB as a 64-bit slave device for write operations, and as a 32-bit slave for reads. It has a single input for address decode so that the OPB slaves may be relocated in the system address map. The PLB to OPB bridge has the logic which steps down the PLB frequency by an integer amount (2:1, 3:1, etc.), allowing the OPB side of the bridge to run at the same (slower) frequency as the OPB. The PLB side always runs at the PLB bus frequency. All PLB to OPB bridge operations on the OPB are performed in the order accepted by the PLB. This insures that coherency is preserved.

### **OPB Interface:**

The PLB to OPB Bridge interfaces to the OPB as a 32-bit master device. It fully implement the OPB architecture on the OPB side, performing dynamic bus sizing transfers as necessary. In case when the PLB to OPB Bridge is the only master device on the OPB, and the arbiter need not be attached.

### PLB to OPB Bridge Buffering:

The PLB to OPB bridge buffering has three sections called data buffering, address and transfer qualifiers buffering and error registers.

### **Data Buffering**:

The PLB to OPB Bridge contains an 8 byte write data buffer, dynamically configurable as a single 64-bit, or two independent 32-bit data registers, and a separate 4 byte read data register. The write buffer resources are dynamically configured to the width of the requested write data transfer.

### Address and Transfer Qualifiers Buffering:

The PLB to OPB Bridge contains three sets of address and PLB transfer qualifier registers. These FIFO address and qualifier registers are dynamically allocated between reads and writes. The PLB to OPB Bridge may accept a secondary read request or a second primary

write request, depending on the current allocation of data buffer resources and the state of the current transfer.

### **Error Registers**:

The PLB to OPB Bridge also contains a set of error reporting registers accessed through the device control register (DCR) bus. There are two 32-bit registers, one for the address that the error occurred at - Bridge Error Address Register (BEAR), and one that contains what type of error occurred and for which master - Bridge Error Status Register (BESR).

### Address Registers:

Separate 32-bit PLB addresses are registered by the PLB to OPB Bridge for each operation. Byte addresses are incremented as necessary to implement dynamic bus sizing on the OPB. Word addresses are incremented only for PLB burst and line transfers.

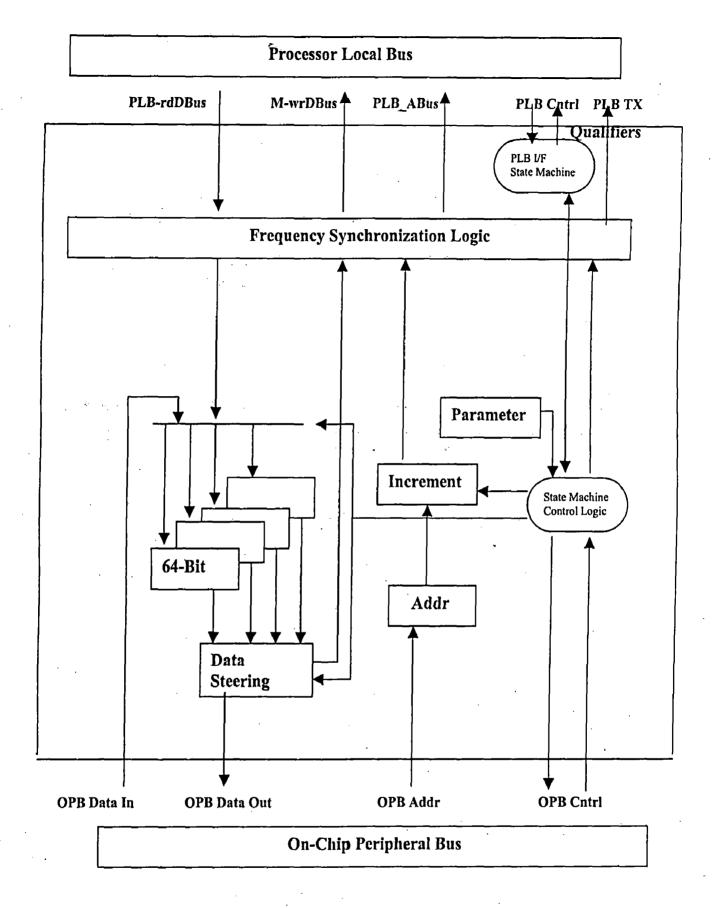

# 3.4. OPB to PLB Bridge:

The On-Chip Peripheral Bus (OPB) to Processor Local Bus (PLB) Bridge module translates OPB transactions into PLB transactions. It functions as a slave on the OPB side and a master on the PLB side. The OPB to PLB Bridge [4] is necessary in systems where an OPB master device, such as an OPB based coprocessor, requires access to PLB devices (i.e. high speed memory devices, etc.).

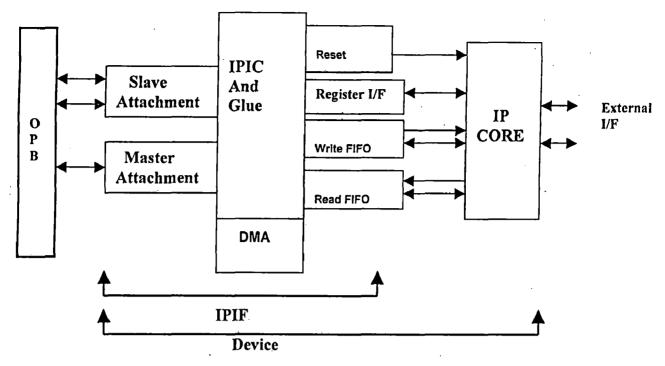

Features of the OPB to PLB Bridge Include: