# IMPLEMENTATION OF THE FFT PROCESSOR USING FPGA

# **A DISSERTATION**

Submitted in partial fulfilment of the requirements for the award of the degree

of

MASTER OF TECHNOLOGY

in

#### ELECTRICAL ENGINEERING

(With Specialization in System Engineering and Operations Research)

By

# **M.NAVEEN KUMAR REDDY**

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE-247 667 (INDIA)

**JUNE, 2005**

I hereby declare that the work presented in this dissertation entitled "IMPLEMENTATION OF THE FFT PROCESSOR USING FPGA" submitted in partial fulfillment of the requirements for the award of degree of Master of Technology in Electrical Engineering with specialization in System Engineering and Operations Research, in the Department of Electrical Engineering, Indian Institute of Technology Roorkee, Roorkee, is an authentic record of my own work carried out from July 2004 to June 2005 under the guidance of Prof.M.K.Vasantha, Professor and Dr. Indra Gupta, Asstt Professor, Department of Electrical Engineering, Indian Institute of Technology Roorkee, Roorkee, Roorkee.

I have not submitted the matter embodied in this report for the award of any other degree or diploma.

Date: 29 June 2005 Place: Roorkee M. Novem Con (M.Naveen Kumar Reddy)

#### CERTIFICATE

This is to certify that the above statement made by the candidate is true to the best of my knowledge and belief.

i

van11. Prof. M.K.Vasantha

Professor Department of Electrical Engineering Indian Institute of Technology Roorkee Roorkee.

Dr. Indra Gupta

Asstt Professor Department of Electrical Engineering Indian Institute of Technology Roorkee Roorkee.

I express my heartfelt gratitude to Prof.M.K.Vasantha, Professor and Dr.Indra Gupta, Asstt Professor, Department of Electrical Engineering, Indian Institute of Technology Roorkee, Roorkee for their valuable guidance, support encouragement and immense help.

I consider myself extremely fortunate for having got the opportunity to learn and work under their able supervision. I have deep sense of admiration for their innate goodness and inexhaustible enthusiasm. The valuable hours of discussions and suggestions that I had with them have undoubtedly helped in supplementing my thoughts in the right direction for attaining the desired objective. Working under their guidance will always remain a cherished experience in my memory and I will adore it throughout my life.

My heartfelt gratitude and indebtedness goes to all the teachers of SEOR group who, with their encouraging and caring words, constructive criticism and suggestions, have contributed directly or indirectly in a significant way towards completion of this report.

I am highly grateful to Mr.Rahul Dubey, Research scholar, Department of Electrical Engineering, Indian Institute of Technology Roorkee, and Roorkee for his keen interest and generous encouragement during this venture.

I am especially thankful to Major Seby Thomas for his feedback in the class. His ideas and discussions not only helped in technical areas but also in personality development.

A word of thanks also goes to Mr.Vijender singh and Mr.Vishal Saxena, research scholar, Electrical Engineering department for always being there to help at the hour of need.

I would also like to extend our sincere appreciation to Mr. Kalyan Singh and Mr.Joshi, Laboratory staff of Micro Processor & Computer Lab for providing the required facilities and co-operation during this work.

Special, sincere and heartfelt gratitude goes to my parents and my friends whose sincere prayers, best wishes, support and encouragement have been a constant source of assurance, guidance, strength and inspiration to me.  $M \cdot Naugen$

(M.Naveen Kumar Reddy)

ii

The Fast Fourier Transform (FFT) is a computationally intensive digital signal processing function widely used in applications such as imaging, software defined radio, wireless communication, instrumentation and machine inspection. Historically, this has been a relatively difficult function to implement optimally in hardware, leading many software designers to use digital signal processors (DSPs) in soft implementations. Unfortunately, because of the function's computationally intensive nature, such an approach typically requires multiple DSPs within the system to support the processing requirements. This is costly from a device and board realestate perspective.

Field-programmable gate array (FPGA) have become an extremely costeffective means of off-loading computationally intensive algorithms to improve overall system performance. The FFT processor implementation on FPGA that utilizes dedicated hardware multiplier resources can cost effectively achieve application-specific integrated circuit (ASIC)-like performance while reducing development time, cost and risks.

In this thesis 16-point FFT processor has been designed and implemented. The design is based on a decimation-in-frequency radix-4 algorithm and employs in-place computation to optimize memory usage. In order to operate the processor, data must first be loaded into the internal RAM. The processor is then instructed to compute the FFT, overwriting the input data in the RAM with the results. Upon completion of the FFT, the results may be read out from the RAM via the output data port. The design specifications for the FFT processor are laid down using radix-4 algorithm. It is capable of computing one butterfly computation every 40ns thus it can compute 16-complex point FFT in 1300ns including data input and output processes. The chip is operating with a clock frequency of 100MHz. The FFT processor is designed and tested according to the design specifications with the help of ISE (Integrated Software Environment) provided by Xilinx. The designed FFT processor has been implemented in Xilinx Spartan-II FPGA.

iii

# CONTENTS

| CH<br>No. | Торіс                                            | Page No.   |

|-----------|--------------------------------------------------|------------|

| 2         | CANDIDATES'S DECLARATION                         | i          |

|           | ACKNOWLEDGEMENTS                                 | ii         |

|           | ABSTRACT                                         | iii        |

|           | CONTENTS                                         | iv         |

|           | LIST OF FIGURES                                  | vii        |

|           | LIST OF TABLES                                   | viii       |

|           | ABBREVIATIONS AND ACRONYMS                       | ix         |

| 1.        | INTRODUCTION TO FFT PROCESSOR                    | · 1        |

|           | 1.1 overview                                     |            |

|           | 1.2 Scope of The Report                          | 3          |

|           | 1.3 Thesis of Organization                       | 3          |

| 2.        | FFT PROCESSOR ALGORITHMS                         | E          |

|           | 2.1 Introduction                                 | 5          |

|           | 2.2 Discrete Fourier Transform                   | 8          |

|           | 2.3 Fast Fourier Transform                       | 8          |

|           | 2.4 FFT Algorithms                               | . 9        |

|           | 2.4.1 Radix-2 FFT Algorithm: DIT FFT             | 9          |

|           | 2.4.2 Radix-2 FFT Algorithm: DIF FFT             | 11         |

|           | 2.4.3 Radix-4 FFT Algorithm: DIF FFT             | 14         |

|           | 2.5 Inverse Fast Fourier Transform               | 20         |

| -         |                                                  |            |

| 3.        | ARCHITECTURE OF SPARTAN-II FPGA AND VHDL         | 21         |

|           | 3.1 Field Programmable Gate Arrays               | 22         |

|           | 3.2 Brief Description of Xilinx FPGAs            | 23         |

|           | 3.2.1 Features                                   | 24         |

|           | 3.2.2 General Overview                           | 25         |

|           | 3.2.3 Architectural Description Spartan-II Array | <b>2</b> 6 |

|           | 3.2.4 Input/Output Block                         | 29         |

|           | 3.2.5 I/O Banking                                | 30         |

|           | 3.2.6 Configurable Logic Block                   | 30         |

|           | 3.2.7 Block RAM                                  | 22         |

|    | 3.3 Hardware Description Languages.                                                                                                                                                                                                                                                                                                    | 33                                                 |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

|    | 3.3.1 Verilog HDL                                                                                                                                                                                                                                                                                                                      | 34                                                 |

|    | 3.3.2 VHDL                                                                                                                                                                                                                                                                                                                             | 35                                                 |

| 4. | DESIGN AND IMPLEMENTATION OF FFT<br>PROCESSOR                                                                                                                                                                                                                                                                                          |                                                    |

|    | 4.1 Introduction                                                                                                                                                                                                                                                                                                                       | 38                                                 |

|    | 4.2 Algorithm Choice                                                                                                                                                                                                                                                                                                                   | 38                                                 |

|    | 4.3 FFT Processor                                                                                                                                                                                                                                                                                                                      | 39                                                 |

|    | 4.3.1 Data Input                                                                                                                                                                                                                                                                                                                       | 39                                                 |

|    | 4.3.2 FFT Computation                                                                                                                                                                                                                                                                                                                  | 39                                                 |

|    | 4.3.3 Data Output Process                                                                                                                                                                                                                                                                                                              | 40                                                 |

|    | 4.4 Architecture                                                                                                                                                                                                                                                                                                                       | 40                                                 |

|    | 4.4.1 Coefficient ROM                                                                                                                                                                                                                                                                                                                  | 40                                                 |

|    | 4.4.2 Block RAM                                                                                                                                                                                                                                                                                                                        | 40                                                 |

|    | 4.4.3 Radix-4 Butterfly Implementation Details                                                                                                                                                                                                                                                                                         | 40                                                 |

|    | 4.4.4 Address generation unit                                                                                                                                                                                                                                                                                                          | 44                                                 |

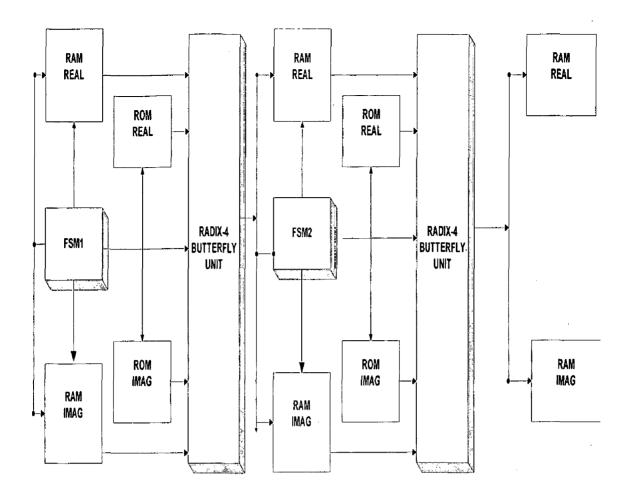

|    | 4.5 FFT Processor architecture                                                                                                                                                                                                                                                                                                         | 46                                                 |

|    |                                                                                                                                                                                                                                                                                                                                        | •                                                  |

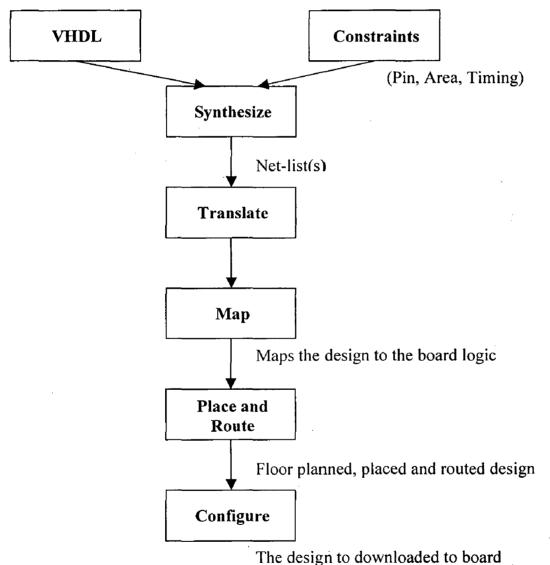

| 5. | DESIGN FLOW AND FINAL IMPLEMENTATION ON FPGA                                                                                                                                                                                                                                                                                           |                                                    |

| 5. |                                                                                                                                                                                                                                                                                                                                        | 49                                                 |

| 5. | FPGA                                                                                                                                                                                                                                                                                                                                   | 49<br>50                                           |

| 5. | FPGA<br>5.1 Introduction                                                                                                                                                                                                                                                                                                               |                                                    |

| 5. | FPGA<br>5.1 Introduction<br>5.2 Specification                                                                                                                                                                                                                                                                                          | 50                                                 |

| 5. | <ul><li>FPGA</li><li>5.1 Introduction</li><li>5.2 Specification</li><li>5.3 Design Entry</li></ul>                                                                                                                                                                                                                                     | 50<br>50                                           |

| 5. | <ul> <li>FPGA</li> <li>5.1 Introduction</li> <li>5.2 Specification</li> <li>5.3 Design Entry</li> <li>5.4 Simulation</li> </ul>                                                                                                                                                                                                        | 50<br>50<br>50                                     |

| 5. | <ul> <li>FPGA</li> <li>5.1 Introduction</li> <li>5.2 Specification</li> <li>5.3 Design Entry</li> <li>5.4 Simulation</li> <li>5.5 User Constrain File</li> </ul>                                                                                                                                                                       | 50<br>50<br>50<br>50                               |

| 5. | <ul> <li>FPGA</li> <li>5.1 Introduction</li> <li>5.2 Specification</li> <li>5.3 Design Entry</li> <li>5.4 Simulation</li> <li>5.5 User Constrain File</li> <li>5.6 Synthesis</li> </ul>                                                                                                                                                | 50<br>50<br>50<br>50<br>50                         |

| 5. | <ul> <li>FPGA</li> <li>5.1 Introduction</li> <li>5.2 Specification</li> <li>5.3 Design Entry</li> <li>5.4 Simulation</li> <li>5.5 User Constrain File</li> <li>5.6 Synthesis</li> <li>5.7 Implementation</li> </ul>                                                                                                                    | 50<br>50<br>50<br>50<br>50<br>51                   |

| 5. | <ul> <li>FPGA</li> <li>5.1 Introduction</li> <li>5.2 Specification</li> <li>5.3 Design Entry</li> <li>5.4 Simulation</li> <li>5.5 User Constrain File</li> <li>5.6 Synthesis</li> <li>5.7 Implementation</li> <li>5.8 Place and Route</li> </ul>                                                                                       | 50<br>50<br>50<br>50<br>50<br>51<br>51             |

|    | <ul> <li>FPGA</li> <li>5.1 Introduction</li> <li>5.2 Specification</li> <li>5.3 Design Entry</li> <li>5.4 Simulation</li> <li>5.5 User Constrain File</li> <li>5.6 Synthesis</li> <li>5.7 Implementation</li> <li>5.8 Place and Route</li> <li>5.9 FPGA Configuration</li> </ul>                                                       | 50<br>50<br>50<br>50<br>50<br>51<br>51             |

|    | <ul> <li>FPGA</li> <li>5.1 Introduction</li> <li>5.2 Specification</li> <li>5.3 Design Entry</li> <li>5.4 Simulation</li> <li>5.5 User Constrain File</li> <li>5.6 Synthesis</li> <li>5.7 Implementation</li> <li>5.8 Place and Route</li> <li>5.9 FPGA Configuration</li> </ul> RESULTS AND DISCUSSIONS                               | 50<br>50<br>50<br>50<br>50<br>51<br>51<br>53       |

|    | <ul> <li>FPGA</li> <li>5.1 Introduction</li> <li>5.2 Specification</li> <li>5.3 Design Entry</li> <li>5.4 Simulation</li> <li>5.5 User Constrain File</li> <li>5.6 Synthesis</li> <li>5.7 Implementation</li> <li>5.8 Place and Route</li> <li>5.9 FPGA Configuration</li> </ul> <b>RESULTS AND DISCUSSIONS</b> 6.1 Simulation Results | 50<br>50<br>50<br>50<br>50<br>51<br>51<br>53<br>53 |

•

**CONCLUSIONS AND FUTURE SCOPE OF WORK** 7. 62 7.1 Conclusions

| 7.2 Future Scope of Work | 62 |

|--------------------------|----|

| DEEEDENICES              | 63 |

# REFERENCES

# APPENDIX

Software Code ( CD Attached)

# LIST OF FIGURES

| Fig No | Title                                                               | Page No |

|--------|---------------------------------------------------------------------|---------|

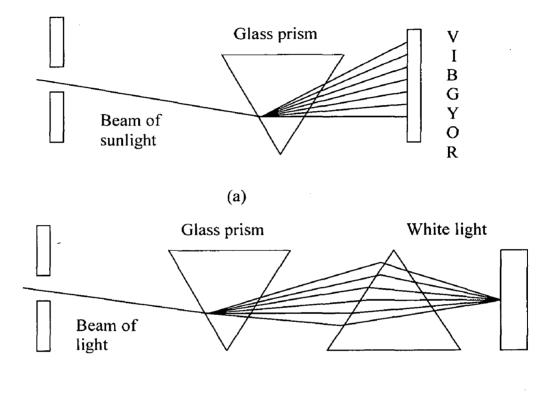

| 2.1    | (a) Analysis (b) Synthesis of the White Light Using Glass Pris      | ms 5    |

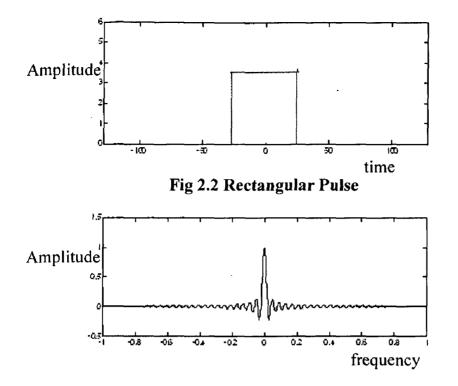

| 2.2    | Rectangular Pulse                                                   | 7       |

| 2.3    | Sin Function                                                        | 7       |

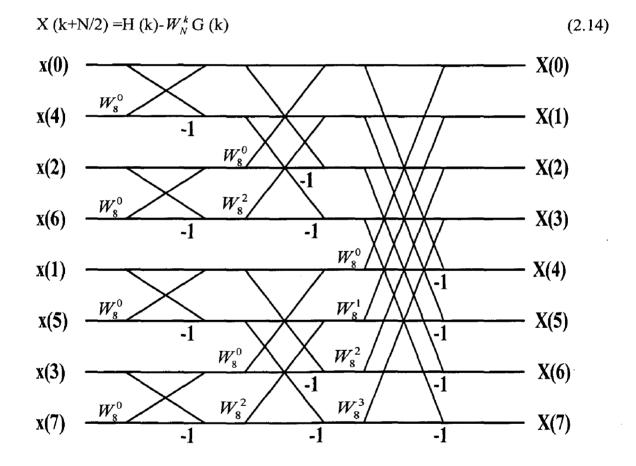

| 2.4    | 8-Point FFT with 3-Stage DIT Radix-2 Structure                      | 10      |

| 2.5    | Basic Butterfly Computation in the DIT FFT Algorithm                | 11      |

| 2.6    | N=8-Point Decimation-in-Frequency FFT Algorithm.                    | 12      |

| 2.7    | Basic Butterfly Computation in the DIF-FFT Algorithm                | 13      |

| 2.8    | Basic Butterfly Computation in a Radix-4 FFT Algorithm.             | 16      |

| 2.9    | 16-point,Radix-4 DIT FFT Algorithm                                  | 17      |

| 3.1    | Basic Spartan-II Family FPGA Block Diagram                          | 27      |

| 3.2    | Spartan-II Input/Output Block (IOB)                                 | 28      |

| 3.3    | Spartan-II I/O Banks                                                | 29      |

| 3.4    | Spartan-II CLB Slice (two identical slices in each CLB)             | 32      |

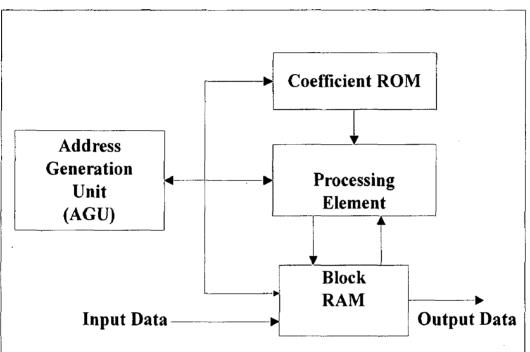

| 4.1    | Three sub-processes of the FFT Algorithm                            | 39      |

| 4.2    | Block Diagram Representation of the FFT processor                   | 41      |

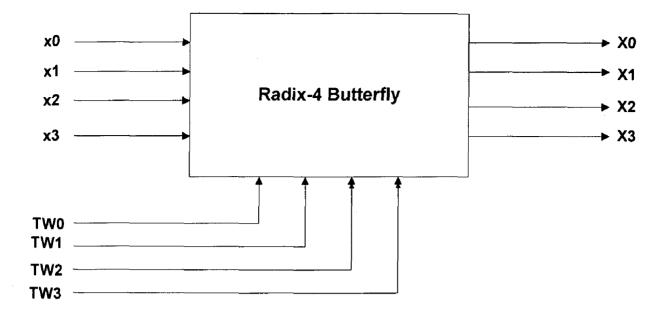

| 4.3    | Block Diagram of Radix-4 Component                                  | 42      |

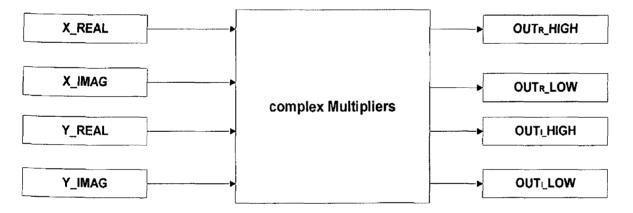

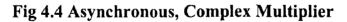

| 4.4    | Asynchronous, Complex Multiplier                                    | 42      |

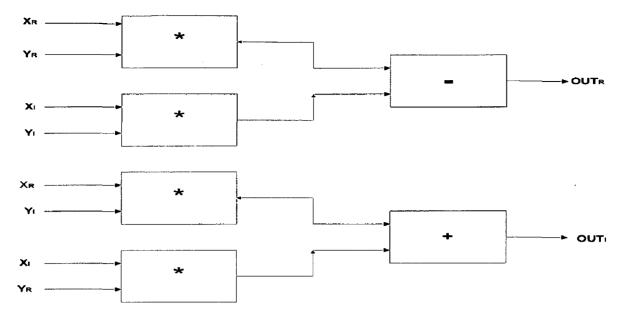

| 4.5    | Complex Multiplier block diagram                                    | 43      |

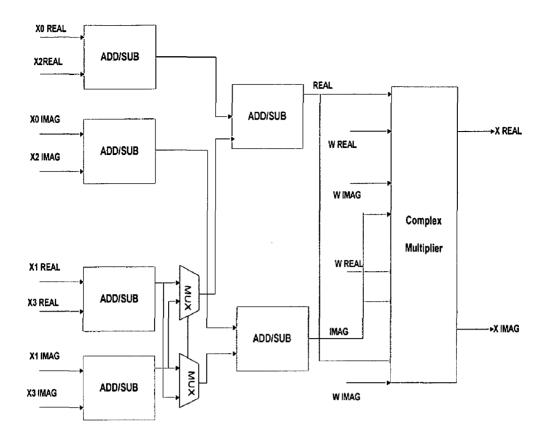

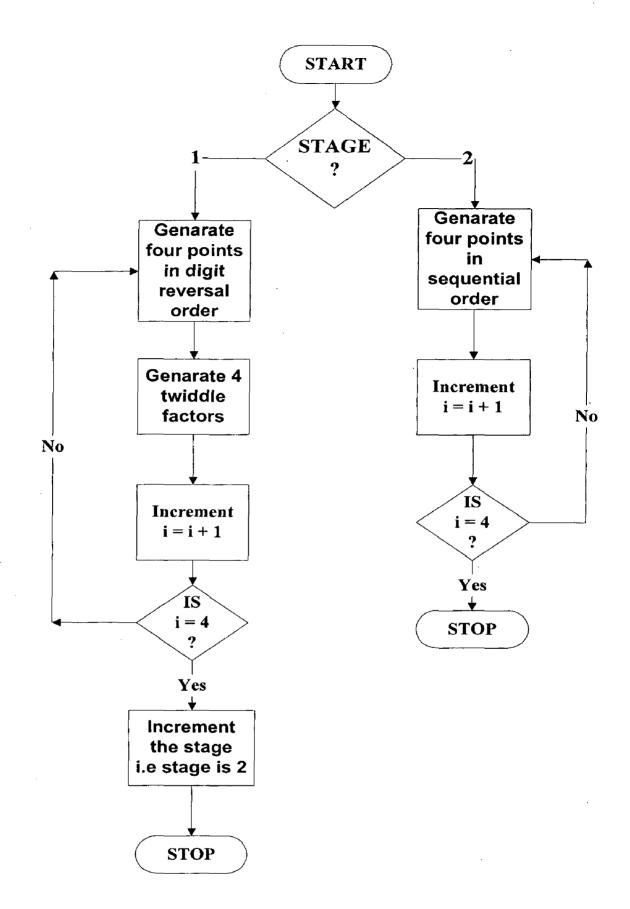

| 4.6    | Butterfly Processing Element Architecture for 1st stage             | 45      |

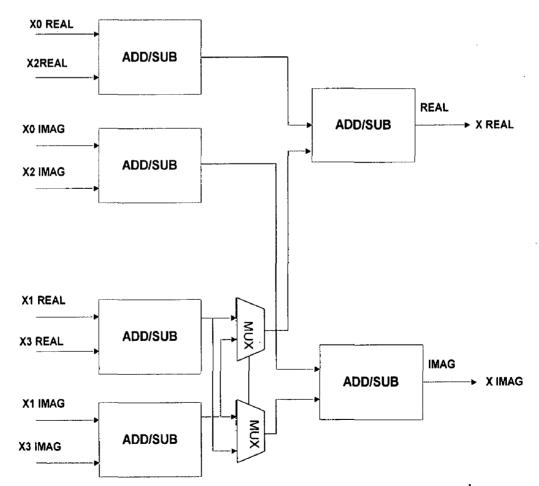

| 4.7    | Butterfly Processing Element Architecture for 2 <sup>nd</sup> stage | 45      |

| 4.8    | Flow chart for address generation unit                              | 47      |

| 4.9    | 16-point FFT architecture                                           | 48      |

| 5.1    | The High-Level Design Flow                                          | 49      |

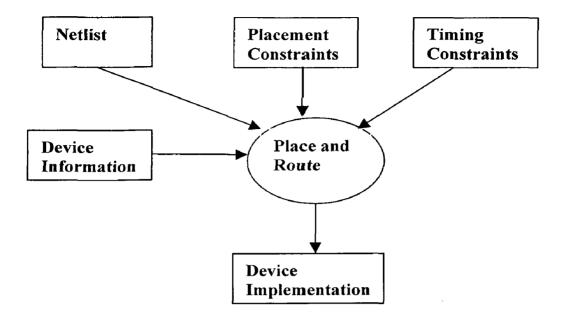

| 5.2    | Place and Route Data Flow                                           | 52      |

| 6.1    | The input is stored in RAM                                          | 55      |

| 6.2    | The inputs which are applied to 16-point FFT processor              | . 56    |

| 6.3    | Final output of the 16-point FFT processor                          | 57      |

| 6.4    | The matlab results of 16-point FFT                                  | 58      |

| 6.5    | RTL View of 16-Point FFT Processor                                  | 61      |

|        |                                                                     |         |

.

# LIST OF TABLES

•

| Table | Title                                                                    | Page No |

|-------|--------------------------------------------------------------------------|---------|

| No    |                                                                          |         |

| 2.1   | Relation between Linear and Bit -Reverse Order                           | 13      |

| 2.2   | The comparison of radix-4 with radix-2 algorithms for N-point FF         | Г 17    |

| 2.3   | The quarternary system for decimal numbers 0 through 15.                 | 18      |

| 2.4   | The digit-reversed positions for a 16-point sequence                     | - 19    |

| 3.1   | Spartan-II FPGA Family Members                                           | 24      |

| 3.2   | Spartan-II Block RAM Amounts                                             | 33      |

| 6.1   | Hardware utilization for 1 <sup>st</sup> stage of radix-4 FFT algorithm. | 59      |

| 6.2   | Hardware utilization for 2 <sup>nd</sup> stage of radix-4 FFT algorithm. | 59      |

| 6.3   | Hardware utilization for 16-point FFT processor                          | 60      |

### **ABBREVIATION AND ACRONYMS**

.

.

.

| AGU            | Address Generation Unit                   |

|----------------|-------------------------------------------|

| ASIC           | Application Specific Integrated Circuits  |

| CLB            | Configurable Logic Block                  |

| DFT            | Discrete Fourier Transform                |

| DIF            | Decimation-In-Frequency                   |

| DIT            | Decimation-In-Time                        |

| DLL            | Delay-Locked Loop                         |

| DSP            | Digital Signal Processing                 |

| EDIF           | Electronic Design Interchange Format      |

| FFT            | Fast Fourier Transform                    |

| FPGA           | Field Programmable Gate Arrays            |

| HDL            | Hardware Description Language             |

| IDFT           | Inverse Discrete Fourier Transform        |

| IFFT           | Inverse Fast Fourier Transform            |

| IOB            | Input/Output Block                        |

| ISE            | Integrated Software Environment           |

| LC             | Logic Cell                                |

| LUT            | Look-Up Tables                            |

| RAM            | Random Access Memory                      |

| ROM            | Read Only Memory                          |

| RTL            | Register Transfer Level                   |

| SDF            | Standard Delay Format                     |

| UCF            | User Constrain File                       |

| VLSI           | Very Large Scale Integrated Circuit       |

| VHDL           | Very High Speed Integrated Circuits HDL   |

| Floor Planning | Process of choosing the best grouping and |

|                | Connectivity of logic in a design         |

| Net list       | Text description of circuit connectivity  |

|                |                                           |

#### 1.1 Overview

The Discrete Fourier Transform (DFT) is one of the most fundamental operations in digital signal processing [1]. The Discrete Fourier transforms play an important role in many digital signal processing applications including acoustics, optics, telecommunications, speech, signal, image processing[17], linear filtering, quantum mechanics, noise reduction and image reconstruction. The Discrete Fourier Transform is a very popular technique used for converting signals in time domain to the frequency domain[9]. The DFT operation can be represented by the following expression.

$$X(k) = \sum_{n=0}^{N-1} x(n) W_N^{kn} \qquad \text{for } k=0, 1 \dots N-1$$

(1.1)

Where X(k) = frequency transform of signal

x(n) = data points in time domain

N = number of data points

$W_N$  = twiddle factor

If the DFT operation is computed using the above expression then the complexity of the algorithm is  $O(N^2)$  for N data points and it will take a long time to compute the DFT. The Fast Fourier Transform (FFT) algorithm reduces the complexity of computing the Discrete Fourier Transform[2].

In 1965, Cooley and Tukey introduced the fast fourier transform, which efficiently and significantly reduces the computational cost of calculating N-point DFT from  $0(N^2)$  to  $0(Nlog_2N)$ . A large number of FFT algorithms have been developed by Cooley and Tukey [4]. Among these, the radix-2, radix-4, split-radix and FHT algorithms are the ones that have been mostly used for practical applications due to their simple structure, with a constant butterfly geometry, and the possibility of performing them "in place". Most of the research to date for the implementation and benchmarking of FFT algorithms have been performed using general purpose processors [3,4], Digital Signal Processors(DSPs) and dedicated FFT processor ICs [5,6]. However, as Field Programmable Gate Arrays (FPGAs) have grown in

1

capacity, improved in performance, and decreased in cost, they have become a viable solution for performing computationally intensive tasks (i.e. computation of FFT), with the ability to tackle applications for custom chips and programmable DSP devices [7,8]. In this thesis, since we mainly focus on the fast structures of the DFT, the terms DFT and FFT will be used interchangeably. The order of the multiplicative complexity is commonly used to measure and compare the efficiency of the algorithms since multiplications are intrinsically more complicated among all operations [5]. It is well-known in the field of VLSI that among the digital arithmetic operations (addition, multiplication, shifting and addressing, etc.), multiplication is the operation that consumes most of the time and power required for the entire computation and, therefore, causes the resulting devices to be large and expensive. Therefore, reducing the number of multiplications in digital chip design is usually a desirable task [14].

FPGAs have become an attractive option for implementing signal processing applications because of their high processing power and customizability. The inclusion of new features in the FPGA fabric, such as a large number of embedded multipliers, adds to this attractiveness. FPGAs can now be considered for computationally demanding applications such as those in signal processing. Traditionally, the performance metrics for signal processing and indeed, most processing in general, have been latency and throughput.

Over last years, the interest in high speed multimedia communication systems has grown enormously [18]. These systems, including digital television, high speed wired data connections, and wireless local area networks, adopt multicarrier modulation scheme such as orthogonal frequency division multiplexing and discrete multi-tone to enhance data transmission rate [13]. In this scheme, sub carriers are generated by using fast Fourier transform (FFT). Therefore, it is very important to design the high speed FFT processor [11,15,19]. For the pipeline architecture, it is desirable to use the radix-4 algorithm because of the double processing rate compared to the radix-2 algorithm. However, the radix-4 algorithm requires more nontrivial multipliers than the radix-2 algorithm. Therefore, the radix-4 based algorithm, which can minimize the number of nontrivial multipliers required to implement the FFT Processor was presented previously. The same computational complexity as the split radix algorithm can be obtained but with a much spatially regular signal flow graph

(SFG) [10]. Only one full complex multiplication is required for every three columns, and the other two columns contain either pure trivial factor -j or a combination of -j and the special twiddle factor  $W_8$ , enabling an implementation with two additive operations and two constant scaling. However, based on the radix-2 butterfly unit, it has a lower processing rate than the radix-4 based algorithm. In this thesis, we propose an efficient FFT algorithm and present the results on its pipeline implementation. Pipelining the FFT process allows parallel processing and divides the complexity of computing the DFT into a number of stages. The result obtained from one stage is immediately available to the next stage without any delay. The proposed algorithm results in a reduced number of nontrivial multipliers like the radix-2 algorithm, but the processing rate is twice as fast as the radix-2 algorithm because it is based on the radix-4 butterfly unit [6].

### 1.2 Scope of The Report

The report is concentrated on 16-point FFT processors, and what architectures and algorithms are most suitable for dedicated FFT processors. The first part of the report gives a review on the theory behind the DFT and FFT algorithm. Some terminologies like radix butterflies, algorithms, architectures, etc., are introduced in this part. The second part of the report describes the main goal of this master's thesis project, i.e. to design and implement a FFT processor for transform length of 16-point. These transform lengths reduces the amount of algorithms, architectures, and so on, that could be taken into account when designing a processor according to these criteria. Some parts of the theory are therefore very briefly described compared to others, because of its limited usefulness in the considered area. What trade-offs have to be made? What architecture and algorithm should be used? What types of simulations should be done? How is testing performed? These are some of the questions that will be discussed in this report.

# 1.3 Organization of Thesis

Chapter-2: This chapter reviews the brief discussion on frequency analysis and the detail notes on DFT, FFT and FFT algorithms.

Chapter-3: This chapter focuses on Xilinx FPGA family on which FFT processor is implemented and also explains HDL languages.

Chapter-4: This chapter presents the complete architecture and implementation of fft processor.

Chapter-5: This chapter describes the process of implementation of FFT processor on FPGA.

Chapter-6: This chapter discusses the simulation results and these results are compared with matlab results and it also provides the synthesis report.

Chapter-7: This chapter concludes the total work and proposes the future scope of work.

~ .....

#### FFT PROCESSOR ALGORITHMS

# 2.1 Introduction

It is well known that a prism can be used to break up white light into the colors of the rainbow.

(b)

Fig 2.1(a) Analysis (b) Synthesis of the White Light Using Glass Prisms.

When a white light is passed through a prism, it will separates white light into different colors. Next place another prism upside-down with respect to the first and observe that the colors blended back into white light [1].

Frequency analysis of a signal involves the resolution of the signal into its frequency (sinusoidal) components. Instead of light, our signal wave forms are basically functions of time. The role of the prism is played by the Fourier analysis i.e Fourier series and Fourier transform [1].

If we decompose a waveform into sinusoidal components, in much the same way that a prism separates white light into different colors, the sum of those sinusoidal components results in the original waveform. on the other hand, If any of these components is missing, the result is a different signal[1].

#### Fourier Series

The basic mathematical representation of periodic signals is the Fourier series, which is a linear weighted sum of harmonically related sinusoids or complex exponentials [1].

Linear combination of harmonically related complex exponentials of the form

$$x(t) = \sum_{k=-\infty}^{\infty} c_k e^{j2\Pi kF0t}$$

(2.1)

$$c_{k} = \frac{1}{Tp} \int_{Tp} x(t) e^{-j2\Pi kF0t} dt$$

(2.2)

Is a periodic signal with fundamental period  $Tp=1/F_0$ . Hence we can think of the exponential signals

$$e^{j2\Pi kF0t}$$

k=0,±1,±2,....

As the basic "building blocks", from which we can construct periodic signals of various type by proper choice of the fundamental frequency and the coefficients  $\{c_k\}$ .Fo determines the fundamental period of x(t) and the coefficients  $\{c_k\}$  specify the shape of the waveform[1].

#### Fourier Transform

The Fourier transform is one of several mathematical tools that is useful in the analysis and design of LTI systems. These signal representations basically involve the decomposition of the signals in terms of sinusoidal (or complex exponential) components [7]. With such decomposition, a signal is said to be represented in the frequency domain. Most signals of practical interest can be decomposed into a sum of sinusoidal signal components for the class of finite energy signals, the decomposition is called the Fourier Transform [1].

Fourier transform of continuous a periodic signal is defined as.

Fig 2.3 Sin Function

$$X(f) = \int_{-\infty}^{\infty} x(t) e^{-j2\pi f t} dt$$

(2.3)

$$x(t) = \int_{-\infty}^{\infty} X(f) e^{j2\Pi/t} df$$

(2.4)

Frequency analysis of discrete-time signals is usually and most conveniently performed on a digital signal processor, which may be a general-purpose digital computer or specially designed hardware. To perform a frequency analysis on a discrete-time signal  $\{x(n)\}$ , we convert the time-domain sequence to an equivalent frequency-domain representation. We know that such a representation is given by the Fourier Transform X(w) of the sequence  $\{x(n)\}$ . However, X(w) is a continuous function of frequency and therefore, it is not a computationally convenient representation of the sequence  $\{x(n)\}$ .

In this section we consider the representation of a sequence  $\{x(n)\}\$  by samples of its spectrum X(w). Such a frequency-domain representation leads to the Discrete Fourier Transform, which is a powerful computational tool for performing frequency analysis of discrete –time signals [6].

#### 2.2 Discrete Fourier Transform

The discrete Fourier transform is the counterpart of the Fourier transform in the discrete time domain. The definition of the DFT is given by the expression:

$$X(k) = \sum_{n=0}^{N-1} x(n) W_N^{kn} \qquad \text{for } k=0, 1, \dots, N-1$$

(2.5)

and the inverse DFT( IDFT) is expressed as:

$$x(n) = \frac{1}{N} \sum_{n=0}^{N-1} X(k) W_N^{-kn} \qquad \text{for n=0,1,....N-1}$$

(2.6)

where  $W_N^k = e^{-j2\Pi k/N}$  is a sequence of twiddle factors of the DFT and is equally spaced around the unit cycle. In these equations x(n) is the sample value in the time domain and X(k) is the sample value in the frequency domain. If the sampling rate of a signal is F, the sequence of time-domain sampling locations becomes

0, 1/F, 2/F, 3/F,....,(N-1)/F

Thus, corresponding to these time-domain samples, the sequence of frequency-domain sampling locations will be

0, F/N, 2F/N, 3F/N,....,(N-1)F/N.

These equations show that the complexity of a direct computation of DFTs and IDFTs is  $O(N^2)$ , hence the long transforms considered to be very costly in a straight forward computation. The FFT algorithm deals with these complexity problems by exploiting regularities in the DFT algorithm [2].

#### 2.3 Fast Fourier Transform

At the outset it should be pointed out that the FFT is not a different transform from the DFT, but rather it represents a means for computing the DFT with a considerable reduction in the number of computations.

Fast Fourier Transform, as the name suggests, is a fast and efficient way of computing the DFT. This algorithm was independently presented by Cooley-Tukey in 1965.A direct computation of the DFT or IDFT requires  $N^2$  complex multiplications and N(N-1) complex additions. FFT removes the redundant multiplication and addition/subtraction operations seen in the naive approach of direct computation of DFT. The DFT can be computed in O(Nlog<sub>2</sub> N) multiplications by using the FFT[3].

## 2.4 FFT Algorithms:

The following algorithms are used for computing the DFT efficiently.

- Divide –and-Conquer Approach.

- ➤ Radix -2

- ▶ Radix -4

- Split-Radix

And also exists radix-16,  $32,2^{N}$ ...etc. In the following section, we presents

- (1) Radix-2 decimation-in-time algorithm (DIT).

- (2) Radix-2 decimation-in-frequency algorithm (DIF).

- (3) Radix-4 decimation-in-frequency algorithm (DIF).

## 2.4.1 Radix-2 FFT Algorithm: DIT FFT

The fast Fourier transform algorithm achieves its computational efficiency through a divide and conquer strategy. The essential idea is a grouping of the time and frequency samples such that the DFT summation over N values can be expressed as a combination of DFT summations over N/2 samples. When N is a power of two, this process of grouping can be repeatedly applied until the DFT summation has been reduced to a combination of DFT summation over only two samples [1]. For example, when N is a power of two, equation 2.5 can be decomposed as follows [1]:

$$X(k) = \sum_{n=0}^{N/2-1} x(2n) W_N^{2kn} + \sum_{n=0}^{N/2-1} x(2n+1) W_N^{(2n+1)k}$$

$$= \sum_{n=0}^{N/2-1} x(2n) W_N^{2kn} + W_N^k \sum_{n=0}^{N/2-1} x(2n+1) W_N^{(2n)k}$$

(2.7)

Define two (N/2)-point sequences (h (n)) and (g (n)) as the even and odd elements of (x(n)), respectively. Then,

$$h(n) = x(2n)$$

(2.8)

$$g(n)=x(2n+1)$$

(2.9)

The discrete Fourier transform of the two (N/2)-point sequences can be defined as follows

$$H(k) = \sum_{n=0}^{N/2-1} h(n) W_{N/2}^{kn}$$

(2.10)

$$G(k) = \sum_{n=0}^{N/2-1} g(n) W_{N/2}^{kn}$$

(2.11)

Thus, the discrete Fourier transform of x (n) can be expressed in terms of even and odd elements as[1]:

$$X(k) = \sum_{n=0}^{N/2-1} h(n) W_{N/2}^{kn} + W_N^k \sum_{n=0}^{N/2-1} g(n) W_{N/2}^{kn}$$

(2.12)

In terms of H (k) and G (k), we have:

$$X(k) = H(k) + W_N^k G(k)$$

(2.13)

For the coefficient at (K + N/2), we obtain:

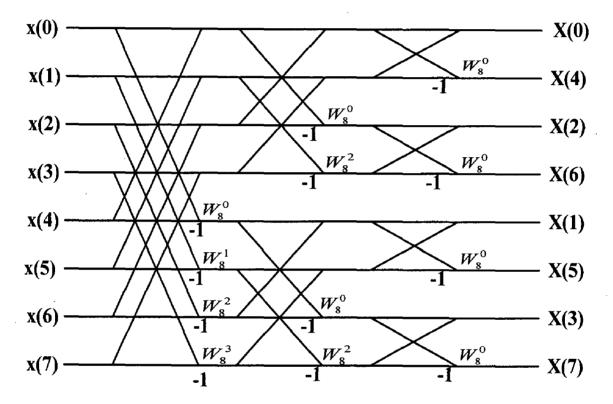

Therefore, N-Point discrete Fourier transform can be represented by two (N/2)point discrete Fourier transform. Since N is a power of two, the above partitioning scheme can be iteratively applied to the sequences (h(n)) and (g(n)) by N/2 elements. These partitions can be carried out until the two-point DFT is reached. The process is known as decimation-in-time, depicted in fig 2.4 for N = 8. Figure 2.5 shows the basic butterfly computation in the decimation-in-time FFT algorithm [1].

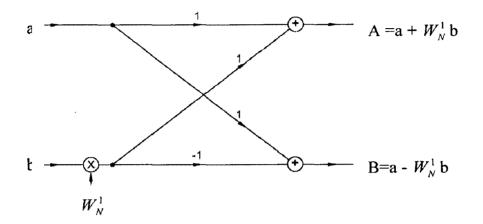

The structure shown in fig. 2.4 is called decimation-in-time (DIT). Its basic module is a radix-2 butterfly shown in fig.2.5 in which two points 'a' and 'b' are computed to give two output points 'A' and 'B' via the operations represented by equations, 2.13 and 2.14. In addition, the input is in bit-reverse order and output is in linear order [2].

Fig 2.5 Basic Butterfly Computation in the Decimation-In-Time FFT Algorithm

# 2.4.2 Radix-2 FFT Algorithm: DIF FFT

We begin by splitting the DFT into two summations, one of which involves the sum over the first N/2 data points and the second sum involves the last N/2 data points, thus we obtain

$$X(k) = \sum_{n=0}^{(N/2)-1} x(n) W_N^{kn} + \sum_{n=N/2}^{N-1} x(n) W_N^{kn} = \sum_{n=0}^{(n/2)-1} x(n) W_N^{kn} + W_N^{Nk/2} \sum_{n=0}^{(n/2)-1} x\left(n + \frac{N}{2}\right) W_N^{kn} \quad (2.15)$$

Since  $W_N^{kN/2} = (-1)^k$ , the above expression can be rewritten as

$$X(k) = \sum_{n=0}^{(n/2)-1} \left[ x(n) + (-1)^k x \left( n + \frac{N}{2} \right) \right] W_N^{kn}$$

(2.16)

Now, let us split (decimate) X (k) into the even- and odd-numbered samples. Thus we obtain final expression as

$$X(2k) = \sum_{n=0}^{(N/2)-1} h(n) W_{N/2}^{kn} \qquad \text{for k=0, 1, 2, ..., } \frac{N}{2} - 1 \qquad (2.17)$$

$$X(2k+1) = \sum_{n=0}^{(N/2)-1} g(n) W_{N/2}^{kn} \qquad \text{for k=0, 1, 2, ..., } \frac{N}{2} - 1 \qquad (2.18)$$

Where,

$$h(n) = x(n) + x\left(n + \frac{N}{2}\right)$$

$$g(n) = \left[x(n) - x\left(n + \frac{N}{2}\right)\right] W_N^n$$

for n=0, 1, 2, ...,  $\frac{N}{2} - 1$

(2.19)

Fig 2.6 N=8-Point Decimation-in-Frequency FFT Algorithm.

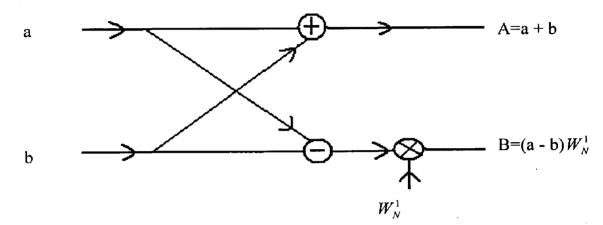

This computation procedure can be repeated through decimation of the N/2-point DFTs, X(2k), X(2k+1). This process is known as decimation-in-frequency(DIF). The computation of the N-point DFT via DIF FFT algorithm requires same number of complex multiplications and complex additions as in the decimation-in-time algorithm.8-point (N=8) DIF algorithm is given in fig.2.6.we observe that the basic computation in this figure involves the butterfly operation illustrated in fig.2.7 and the input data x(n) occurs in natural order, but the output DFT occurs in bit-reversed order[3].

We observed from the above discussion is each radix-2 butterfly requires one complex multiplication and two complex additions. Observing fig.2.6 and fig.2.7, it can be seen that there are Log<sub>2</sub> N radix-2 butterfly stages for N-point FFT and each stage has N/2 radix-2 butterflies. Therefore, there are totally (N/2) log2 N radix-2 butterflies in an N-point FFT. Both structures employ the in-place algorithm. In-place means that the computed outputs can be placed on the same storage as the inputs. Moreover, the addressing for the input and output data can be shared [1].

Fig 2.7 Basic Butterfly Computation in the DIF-FFT Algorithm

| LINE    | LINEAR |       | BIT-REVERSE |  |  |

|---------|--------|-------|-------------|--|--|

| DECIMAL | DIGIT  | DIGIT | DECIMAL     |  |  |

| 0       | 000    | 000   | 0           |  |  |

| 1       | 001    | 100   | 4           |  |  |

| 2       | 010    | 010   | 2           |  |  |

| 3       | 011    | 110   | 6           |  |  |

| 4       | 100    | 001   | 1           |  |  |

| 5       | 101    | 101   | 5           |  |  |

| 6       | 110    | 011   | 3           |  |  |

| 7       | 111    | 111   | 7           |  |  |

Table 2.1 Relation between Linear and Bit -Reverse Order

#### 2.4.3 Radix-4 FFT Algorithm: DIF FFT

Whereas a radix-2 FFT divides an N-point sequence successively in half until only two-point DFTs remain, a radix-4 FFT divides an N-point sequence successively in quarters until only four-point DFTs remain. An N-point sequence is divided into four N/4-point sequences; each N/4-point sequence is broken into four N/16-point sequences, and so on, until only four-point DFTs are left. The four-point DFT is the core calculation (butterfly) of the radix-4 FFT, just as the two-point DFT is the butterfly for a radix-2 FFT [1].

A radix-4 FFT essentially combines two stages of a radix-2 FFT into one, so that half as many stages are required. Although addressing of data and twiddle factors is more complex, a radix-4 FFT requires fewer calculations than a radix-2 FFT. Like the radix-2 FFT, the radix-4 FFT requires data scrambling and/or unscrambling. However, radix-4 FFT sequences are scrambled and unscrambled through digit reversal, rather than bit reversal as in the radix-2 FFT. Digit reversal is described later in this section [1].

The radix-4 DIF FFT expresses the DFT equation as four summations, and then divides it into four equations, each of which computes every fourth output sample. The following equations illustrate radix-4 decimation in frequency.

$$X(k) = \sum_{n=0}^{N-1} x(n) W_N^{nk}$$

=  $\sum_{n=0}^{(N/4)^{-1}} x(n) W_N^{nk} + \sum_{n=N/4}^{(N/2)^{-1}} x(n) W_N^{nk} + \sum_{n=N/2}^{(3N/4)^{-1}} x(n) W_N^{nk} + \sum_{n=3N/4}^{(N/4)^{-1}} x(n) W_N^{nk}$

=  $\sum_{n=0}^{(N/4)^{-1}} x(n) W_N^{nk} + \sum_{n=0}^{(N/4)^{-1}} x(n+N/4) W_N^{(n+N/4)k}$

+  $\sum_{n=0}^{(N/4)^{-1}} x(n+N/2) W_N^{(n+N/2)k} + \sum_{n=0}^{(N/4)^{-1}} x(n+3N/4) W_N^{(n+3N/4)k}$

$$= \sum_{n=0}^{\infty} [x(n) + W_N^{k(N/4)} x(n+N/4) + W_N^{k(N/2)} x(n+N/2) + W_N^{K(3N/4)} x(n+3N/4)] W_N^{nk}$$

(2.20)

The three twiddle factor coefficients can be expressed as follows:

$$W_N^{k(N/4)} = (e^{-j2\pi/N})^{k(N/4)} = (e^{-j\pi/2})^k = (\cos(\pi/2) - j\sin(\pi/2))^k = (-j)^k$$

(2.21)

Similarly

$$W_N^{k(N/2)} = (-1)^k$$

(2.22)

$W_N^{k(3N/4)} = j^k$  (2.23)

Equation 2.20 can thus be expressed as

$$X(k) = \sum_{n=0}^{(N/4)-1} [x(n) + (-j)^{k} x(n+N/4) + (-1)^{k} x(n+N/2) + (j)^{k} x(n+3N/4)] W_{N}^{nk}$$

(2.24)

Four sub-sequences of the output (frequency) sequence are created by setting k=4r, k=4r+1, k=4r+2 and k=4r+3:

$$X(4r) = \sum_{n=0}^{(N/4)-1} [(x(n) + x(n + N/4) + x(n + N/2) + x(n + 3N/4))W_N^0]W_{N/4}^{nr}$$

(2.25)

$$X(4r+1) = \sum_{n=0}^{(N/4)-1} [(x(n) - jx(n+N/4) - x(n+N/2) + jx(n+3N/4))W_N^n]W_{N/4}^{nr} \quad (2.26)$$

$$X(4r+2) = \sum_{n=0}^{(N/4)-1} [(x(n) - x(n+N/4) + x(n+N/2) - x(n+3N/4))W_N^{2n}]W_{N/4}^{nr}$$

(2.27)

$$X(4r+3) = \sum_{n=0}^{(N/4)-1} [(x(n) + jx(n + N/4) - x(n + N/2) - jx(n + 3N/4))W_N^{3n}]W_{N/4}^{nr} \quad (2.28)$$

For r = 0 to (N/4)-1.

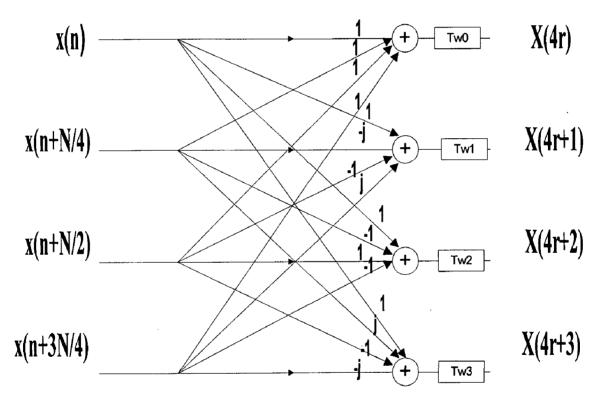

X (4r), X(4r+1), X(4r+2), and X(4r+3) are N/4-point DFTs. Each of their N/4 points is a sum of four input samples (x(n), x(n+N/4), x(n+N/2) and (n+3N/4)), each multiplied by either +1, -1, j, or -j. The sum is multiplied by a twiddle factor  $(W_N^0, W_N^n, W_N^{2n}, \text{ or } W_N^{3n})[1].$

The four one-point DFT equations make up the butterfly calculation of the radix-4 FFT. A radix-4 butterfly is shown graphically in fig 2.8.

The output of each leg represents one of the four equations which are combined to make a four-point DFT. These four equations correspond to equations, (2.25) through (2,28), for one point rather than N/4 points. The radix-4 butterfly expressed in matrix form as

$$\begin{bmatrix} X(0) \\ X(1) \\ X(2) \\ X(3) \end{bmatrix} = \begin{bmatrix} 1 & 1 & 1 & 1 \\ 1 & -j & -1 & j \\ 1 & -1 & 1 & -1 \\ 1 & j & -1 & -j \end{bmatrix} \begin{bmatrix} W_N^0 x(0) \\ W_N^q x(1) \\ W_N^{2q} x(2) \\ W_N^{3q} x(3) \end{bmatrix}$$

Where q = 0, 1, 2, 3.

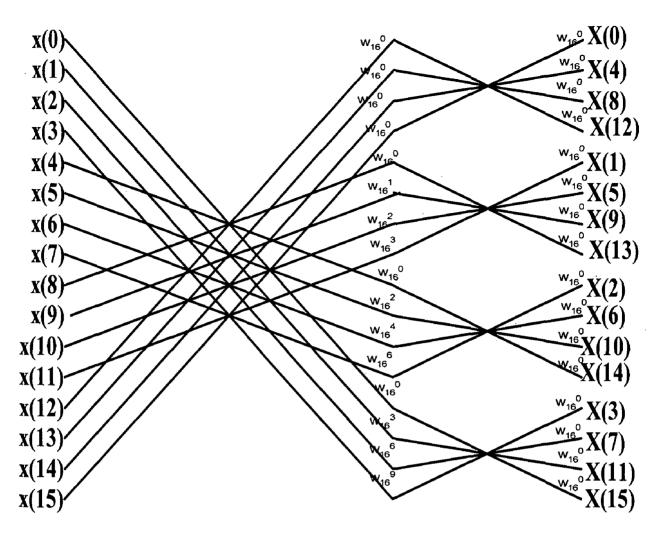

The 16-point radix-4 decimation-in-frequency FFT algorithm is shown in fig 2.9 .Its input in normal order and its output is in digit-reversed order. The computational complexity of radix-2 and radix-4 algorithm for N-point FFT is depicted in Table.2.2.

Fig 2.8 Basic Butterfly Computation in a Radix-4 FFT Algorithm.

Fig 2.9 16-point, Radix-4 DIT FFT Algorithm

The radix-4 butterfly is consequently larger and more complicated than a radix-2 butterfly; however, fewer butterflies are needed. Specifically, N/4 butterflies are used in each of  $(\log_4 N)$  stages, which is one quarter the number of butterflies in a radix-2 FFT[16].

|  | Complex | Complex | Number of | No. of Butterflies |

|--|---------|---------|-----------|--------------------|

|  |         |         |           |                    |

Table 2.2 The comparison of radix-4 with radix-2 algorithms for N-point FFT

| Complex<br>Multiplications | Complex<br>Additions    | Number of<br>Stages                                                                  | No. of Butterflies<br>(for each Stage)                                             |

|----------------------------|-------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| (N/2)log <sub>2</sub> N    | N log <sub>2</sub> N    | log <sub>2</sub> N                                                                   | N/2                                                                                |

| (3N/4) log <sub>4</sub> N  | 3N log <sub>4</sub> N   | Log <sub>4</sub> N                                                                   | N/4                                                                                |

|                            | (N/2)log <sub>2</sub> N | Multiplications     Additions       (N/2)log <sub>2</sub> N     N log <sub>2</sub> N | Multiplications     Additions     Stages       (N/2)log2 N     N log2 N     log2 N |

# **Digit Reversal**

Whereas bit reversal reverses the order of bits in binary (base 2) numbers, digit reversal reverses the order of digits in quarternary (base 4) numbers. Every two bits in the binary number system correspond to one digit in the quarternary number system. (For example, binary 1110 = quarternary 32.) The quarternary system is illustrated in below table for decimal numbers 0 through 15[16].

| Decimal | Binary | Quarternary |

|---------|--------|-------------|

|         |        |             |

| 0       | 0000   | 00          |

| 1       | 0001   | 01          |

| 2       | 0010   | 02          |

| 3       | 0011   | 03          |

| 4       | 0100   | 10          |

| 5       | 0101   | 11          |

| 6       | 0110   | 12          |

| 7       | 0111   | 13          |

| 8       | 1000   | 20          |

| 9       | 1001   | 21          |

| 10      | 1010   | 22          |

| 11      | 1011   | 23          |

| 12      | 1100   | 30          |

| 13      | 1101   | 31          |

| 14      | 1110   | 32          |

| 15      | . 1111 | 33          |

| ļ       |        |             |

Table 2.3 The quarternary system for decimal numbers 0 through 15.

The radix-4 DIF FFT successively divides a sequence into four subsequences, resulting in an output sequence in digit-reversed order. A digit-reversed sequence is unscrambled by digit-reversing the data positions. For example, position 12 in quarternary (six in decimal) becomes position 21 in quarternary (nine in decimal) after digit reversal. Therefore, data in position six is moved to position nine when the

digit reversed sequence is unscrambled. The digit-reversed positions for a 16-point sequence (samples X(0) through X(15)) are shown in Table 2.4.

In an N-point radix-4 FFT, only the number of digits needed to represent N locations is reversed. Two digits are needed for a 16-point FFT, three digits for a 64-point FFT, and five digits for a 1024-point FFT[16].

| Sample,    | Sequential Location        |    | Sequential Location Digit-Reversed Location |    | Sample,<br>Digit-Reversed |  |

|------------|----------------------------|----|---------------------------------------------|----|---------------------------|--|

| Sequential | ential Decimal Quarternary |    | Decimal Quarternary                         |    |                           |  |

| Order      |                            |    |                                             |    | Order                     |  |

| X(0)       | 0                          | 00 | 0                                           | 00 | X(0)                      |  |

| X(1)       | 1                          | 01 | 4                                           | 10 | X(4)                      |  |

| X(2)       | 2                          | 02 | 8                                           | 20 | X(8)                      |  |

| X(3)       | 3                          | 03 | 12                                          | 30 | X(12)                     |  |

| X(4)       | 4                          | 10 | 1                                           | 01 | X(1)                      |  |

| X(5)       | 5                          | 11 | 5                                           | 11 | X(5)                      |  |

| X(6)       | 6                          | 12 | 9                                           | 21 | X(9)                      |  |

| X(7)       | 7                          | 13 | 13                                          | 31 | X(13)                     |  |

| X(8)       | 8                          | 20 | 2                                           | 02 | X(2)                      |  |

| X(9)       | 9                          | 21 | 6                                           | 12 | X(6)                      |  |

| X(10)      | 10                         | 22 | 10                                          | 22 | X(10)                     |  |

| X(11)      | 11                         | 23 | 14                                          | 32 | X(14)                     |  |

| X(12)      | 12                         | 30 | 3                                           | 03 | X(3)                      |  |

| X(13)      | 13                         | 31 | 7                                           | 13 | X(7)                      |  |

| X(14)      | 14                         | 32 | 11                                          | 23 | X(11)                     |  |

| X(15)      | 15                         | 33 | 15                                          | 33 | X(15)                     |  |

|            | 1                          |    |                                             |    |                           |  |

Table 2.4 The digit-reversed positions for a 16-point sequence

#### 2.5. Inverse Fast Fourier Transform

The inverse FFT (IFFT) defined by eqs., (2.29) can be changed to the following form:

$$x(n) = \frac{1}{N} \left[ \sum_{k=0}^{N-1} X^{*}(k) W_{N}^{kn} \right]$$

for n=0, 1, ..... N-1 (2.29)

where the notation of the superscript \* denotes the conjugated data. If the input frequency samples are conjugated, the bracketed term in eqs., (2.29) is exactly an FFT operation. Thus, the computation of the IFFT is the same as the FFT except the input data sequence of the first stage and output data sequence of the last stage are conjugated. The results computed by the FFT instructions are reference values and not exact values shown by eqs., (2.29). If users like to get exact values, the results have to be multiplied by a factor. This factor can be derived from the length of data N and the total number of scaling for the block data [1].

#### 3.1 Field Programmable Gate Arrays

A field programmable gate array (FPGA) is an inexpensive hardware component, which allows the user to program its functionality quickly and inexpensively. This allows for cheaper prototyping and shorter time to-market of hardware designs. FPGAs have a lower gate density than full custom (customized VLSI chips) and semi custom (mask programmed gate arrays) design methodologies FPGAs were first introduced in the mid-1980s to replace multi-chip glue logic circuits with a single reconfigurable solution [12]. FPGAs have far outgrown their sole use as a replacement for simple glue logic circuits [13]. Presently, FPGA applications include signal and image processing, graphic accelerators, military target correlation/recognition, cryptography, reconfigurable computing, and on-chip coprocessors. FPGAs are utilized in four major design areas: rapid prototyping, emulation, pre-production, and full-production [14]. FPGAs are the direct result of the convergence of two distinct technologies: Programmable Logic Devices (PLDs) and Application Specific Integrated Circuits (ASICs) [15]. A simple PLD consists of arrays of AND and OR gates that can be used to create basic circuit designs. ASICs are custom-made chips generally used in high volume applications because nonrecurring engineering costs (NREs) are much higher than in an FPGA design cycle.FPGAs are sized from thousands of gates to tens-of-million gates and are available in a variety of sizes with different packaging, internal logic blocks, and process technologies [25].

Internal FPGA architectures are commonly constructed using a symmetric tile structure containing a network of switchboxes, logic blocks, wire channels, and inputoutput blocks .A switchbox (SB) is a location in the FPGA fabric that provides a method to connect internal wires together. The switchbox allows horizontal wire segments to switch to vertical wire segments and vice versa. The switchbox also allows horizontal wire segments to connect to other horizontal wire segments as well as connecting vertical wires to other vertical wires. The size and contents within a logic block vary greatly depending on the manufacture and target market. For

example, FPGAs targeted towards cost-effective solutions typically contain simpler logic blocks than an FPGA targeted for high-performance applications. Although the contents within logic blocks can vary for different architectures, there are two basic building blocks found in a logic block: memory elements and function generators. Memory elements provide designers with the ability to temporarily store information until desired conditions are met. Function generators can be configured to produce any function up to the number of inputs into the function generator. Depending on the architecture, some function generators can operate in different modes such as random access memory (RAM), read only memory (ROM), or more complex modes like shift registers. FPGAs are configured through a bitstream that is loaded into the device. A bitstream is a file created by the FPGA manufacturer that configures the switchboxes, logic blocks, and other internal FPGA logic[25].

FPGAs have redefined the boundaries of digital electronics allowing designers to build systems piecewise. Multiple designers can rapidly test and verify the functionality of each individual piece of a system to ensure proper functionality prior to merging the entire system together. With increasing interest in reconfigurable computing, FPGAs are recognized as the most viable, cost effective solution. Whether a design is statically or dynamically reconfigurable, FPGAs provide rapid programmability, and a short time to market design cycle. Many companies have marketed FPGAs, the major companies being Xilinx, Actel and Altera. Reprogrammable FPGAs use EPROM, EEPROM or static RAM technology. Xilinx FPGAs, which use static RAM technology, are the FPGAs used in this thesis[25].

### 3.2 Brief Description of Xilinx FPGAs

The Spartan-II 2.5V Field-Programmable Gate Array family gives users high performance, abundant logic resources, and a rich feature set, all at an exceptionally low price. The six-member family offers densities ranging from 15,000 to 200,000 system gates, as shown in Table 1. System performance is supported up to 200 MHz. Spartan-II devices deliver more gates, I/Os, and features per dollar than other FPGAs by combining advanced process technology with a streamlined Virtex-based architecture. Features include block RAM (to 56K bits), distributed RAM (to 75,264 bits), 16 selectable I/O standards, and four Delay-Locked Loops (DLLs). Fast,

predictable interconnect means that successive design iterations continue to meet timing requirements. The Spartan-II family is a superior alternative to maskprogrammed ASICs. The FPGA avoids the initial cost, lengthy development cycles, and inherent risk of conventional ASICs. Also, FPGA programmability permits design upgrades in the field with no hardware replacement necessary (impossible with ASICs)[25].

#### 3.2.1 Features:

- (1) Second generation ASIC replacement technology

- Densities as high as 5,292 logic cells with up to 200,000 system gates

- Streamlined features based on Virtex architecture

- Unlimited reprogrammability

- Very low cost

- Advanced 0.18 micron process

- (2) System level features

- Select RAM hierarchical memory:

- ✤ 16 bits/LUT distributed RAM

- Configurable 4K bit block RAM

- Fast interfaces to external RAM

- Fully PCI compliant

- Low-power segmented routing architecture

- Full read back ability for verification/observability

- Dedicated carry logic for high-speed arithmetic

- Efficient multiplier support

- Cascade chain for wide-input functions

- Abundant registers/latches with enable, set, reset

- Four dedicated DLLs for advanced clock control

- Four primary low-skew global clock distribution nets

- ✤ IEEE 1149.1 compatible boundary scan logic

- (3) Versatile I/O and packaging

- Pb-free package options

- Low-cost packages available in all densities

- Family footprint compatibility in common packages

- ✤ 16 high-performance interface standards

- Hot swap Compact PCI friendly

- Zero hold time simplifies system timing

- (4) Fully supported by powerful Xilinx development system

- ✤ Foundation ISE Series: Fully integrated software

- ✤ Alliance Series: For use with third-party tools

- Fully automatic mapping, placement, and routing

#### 3.2.2 General Overview

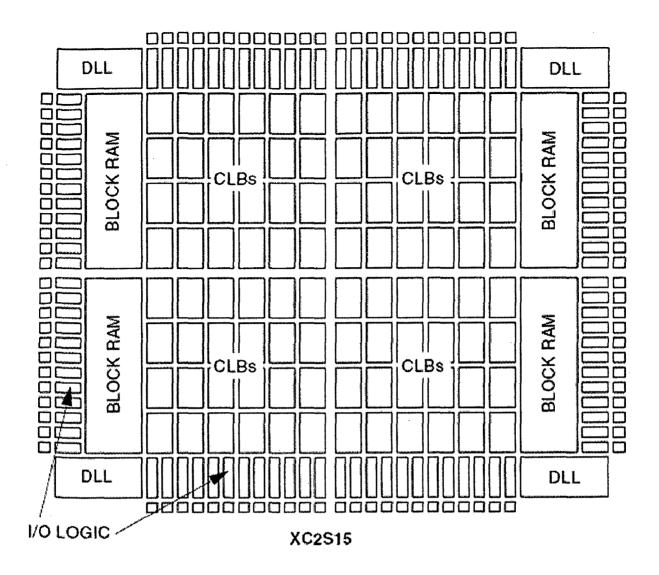

The Spartan-II family of FPGAs have a regular, flexible, programmable architecture of Configurable Logic Blocks (CLBs), surrounded by a perimeter of programmable Input/Output Blocks (IOBs). There are four Delay-Locked Loops (DLLs), one at each corner of the die. Two columns of block RAM lie on opposite sides of the die, between the CLBs and the IOB columns. These functional elements are interconnected by a powerful hierarchy of versatile routing channels .This is shown in Fig.3.1[25]

| Spartan-II<br>Device | Logic<br>Cells | System Gates<br>(Logic and<br>RAM) | CLB<br>Array<br>(R x C) | Total<br>CLBs | Maximum<br>Available<br>User I/O | Total<br>Distributed<br>RAM<br>Bits | Total<br>Block<br>RAM<br>Bits |

|----------------------|----------------|------------------------------------|-------------------------|---------------|----------------------------------|-------------------------------------|-------------------------------|

| XC2S15               | 432            | 15,000                             | 8 x 12                  | 96            | 86                               | 6,144                               | 16K                           |

| XC2S30               | 972            | 30,000                             | 12 x 18                 | 216           | 92                               | 13,824                              | 24K                           |

| XC2S50               | 1,728          | 50,000                             | <u>16 x 24</u>          | 384           | 176                              | 24,576                              | <u>32K</u>                    |

| XC2S100              | 2,700          | 100,000                            | 20 x 30                 | 600           | 176                              | 38,400                              | <u>40K</u>                    |

| XC2S150              | 3,880          | 150,000                            | 24 x 36                 | 864           | 260                              | 55,296                              | 48K                           |

| XC2S200              | 5,292          | 200,000                            | 28 x 42                 | 1,176         | 284                              | 75,264                              | 56K                           |

Table 3.1 Spartan-II FPGA Family Members

Spartan-II FPGAs are customized by loading configuration data into internal static memory cells. Unlimited reprogramming cycles are possible with this approach. Stored values in these cells determine logic functions and interconnections implemented in the FPGA. Configuration data can be read from an external serial PROM (master serial mode), or written into the FPGA in slave serial, slave parallel, or Boundary Scan modes [25].

Spartan-II FPGAs are typically used in high-volume applications where the versatility of a fast programmable solution adds benefits. Spartan-II FPGAs are ideal for shortening product development cycles while offering a cost-effective solution for high volume production [25].

Spartan-II FPGAs achieve high-performance, low-cost operation through advanced architecture and semiconductor technology. Spartan-II devices provide system clock rates up to 200 MHz. Spartan-II FPGAs offer the most cost-effective solution while maintaining leading edge performance. In addition to the conventional benefits of high-volume programmable logic solutions, Spartan-II FPGAs also offer on-chip synchronous single-port and dual-port RAM (block and distributed form), DLL clock drivers, programmable set and reset on all flip-flops, fast carry logic, and many other features [25].

#### 3.2.3 Architectural Description Spartan-II Array

The Spartan-II user-programmable gate array, shown in Figure 1, is composed of five major configurable elements.

- ◆ IOBs provide the interface between the package pins and the internal logic

- CLBs provide the functional elements for constructing most logic

- Dedicated block RAM memories of 4096 bits each

- Clock DLLs for clock-distribution delay compensation and clock domain control

- Versatile multi-level interconnect structure

As can be seen in fig.3.1, the CLBs form the central logic structure with easy access to all support and routing structures. The IOBs are located around all the logic and memory elements for easy and quick routing of signals on and off the chip. Values stored in static memory cells control all the configurable logic elements and

interconnect resources. These values load into the memory cells on power-up, and can reload if necessary to change the function of the device. Each of these elements will be discussed in detail in the following sections [25].

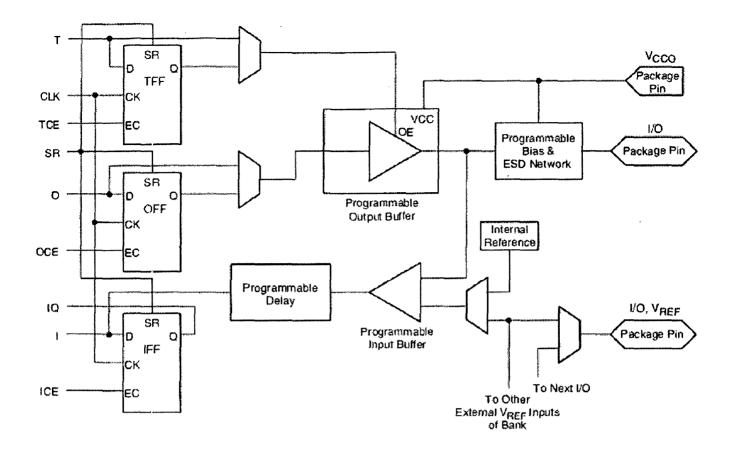

#### 3.2.4 Input/Output Block

The Spartan-II IOB, as seen in fig.4.2, features inputs and outputs that support a wide variety of I/O signaling standards. These high-speed inputs and outputs are capable of supporting various state of the art memory and bus interfaces. The three IOB registers function either as edge-triggered D-type flip-flops or as level-sensitive latches. Each IOB has a clock signal (CLK) shared by the three registers and independent Clock Enable (CE) signals for each register [25].

In addition to the CLK and CE control signals, the three registers share a Set/Reset (SR). For each register, this signal can be independently configured as a synchronous Set, a synchronous Reset, an asynchronous Preset, or an asynchronous Clear A feature not shown in the block diagram, but controlled by the software, is polarity control. The input and output buffers and all of the IOB control signals have independent polarity controls [25].

Optional pull-up and pull-down resistors and an optional weak-keeper circuit are attached to each pad. Prior to configuration all outputs not involved in configuration are forced into their high-impedance state. The pull-down resistors and the weak-keeper circuits are inactive, but inputs may optionally be pulled up. The activation of pull-up resistors prior to configuration is controlled on a global basis by the configuration mode pins. If the pull-up resistors are not activated, all the pins will float. Consequently, external pull-up or pull-down resistors must be provided on pins required to be at a well-defined logic level prior to configuration [25].

All pads are protected against damage from electrostatic discharge (ESD) and from over-voltage transients. Two forms of over-voltage protection are provided, one that permits 5V compliance, and one that does not. For 5V compliance, a zener-like structure connected to ground turns on when the output rises to approximately 6.5V. When 5V compliance is not required, a conventional clamp diode may be connected to the output supply voltage, VCCO. The type of over-voltage protection can be selected independently for each pad [25].

Fig 3.1 Basic Spartan-II Family FPGA Block Diagram

Input Path

A buffer In the Spartan-II IOB input path routes the input signal either directly to internal logic or through an optional input flip-flop. An optional delay element at the D-input of this flip-flop eliminates pad-to-pad hold time. The delay is matched to the internal clock-distribution delay of the FPGA, and when used, assures that the pad-to-pad hold time is zero. Each input buffer can be configured to conform to any of the low-voltage signaling standards supported. In some of these standards the input buffer utilizes a user-supplied threshold voltage, VREF. The need to supply VREF imposes constraints on which standards can used in close proximity to each other. There are optional pull-up and pull-down resistors at each input for use after configuration.

Fig 3.2 Spartan-II Input/Output Block (IOB)

## **Output Path**

The output path includes a 3-state output buffer that drives the output signal onto the pad. The output signal can be routed to the buffer directly from the internal logic or through an optional IOB output flip-flop. The 3-state control of the output can also be routed directly from the internal logic or through a flip-flip that provides synchronous enable and disable. Each output driver can be individually programmed for a wide range of low-voltage signaling standards. Each output buffer can source up to 24 mA and sink up to 48 mA. Drive strength and slew rate controls minimize bus transients [25].

In most signaling standards, the output high voltage depends on an externally supplied VCCO voltage. The need to supply VCCO imposes constraints on which standards can be used in close proximity to each other. An optional weak-keeper circuit is connected to each output. When selected, the circuit monitors the voltage on the pad and weakly drives the pin High or Low to match the input signal. If the pin is connected to a multiple-source signal, the weak keeper holds the signal in its last state if all drivers are disabled. Maintaining a valid logic level in this way helps eliminate bus chatter. Because the weak-keeper circuit uses the IOB input buffer to monitor the input level, an appropriate VREF voltage must be provided if the signaling standard requires one. The provision of this voltage must comply with the I/O banking rules [25].

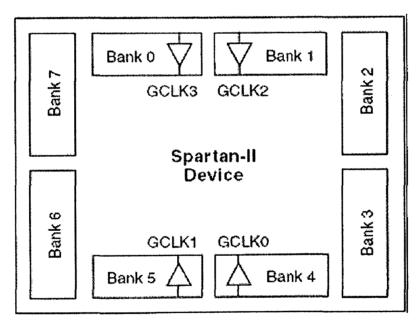

## 3.2.5 I/O Banking

Some of the I/O standards described above require VCCO and/or VREF voltages. These voltages are externally connected to device pins that serve groups of IOBs, called banks. Consequently, restrictions exist about which I/O standards can be combined within a given bank. Eight I/O banks result from separating each edge of the FPGA into two banks as shown in Figure 3). Each bank has multiple VCCO pins which must be connected to the same voltage. Voltage is determined by the output standards in use [25].

Fig 3.3 Spartan-II I/O Banks

Some input standards require a user-supplied threshold voltage,  $V_{REF}$ . In this case, certain user-I/O pins are automatically configured as inputs for the  $V_{REF}$  voltage. About one in six of the I/O pins in the bank assume this role. $V_{REF}$  pins within a bank are interconnected internally and consequently only one  $V_{REF}$  voltage can be used within each bank. All  $V_{REF}$  pins in the bank, however, must be

connected to the external voltage source for correct operation. In a bank, inputs requiring  $V_{REF}$  can be mixed with those that do not but only one  $V_{REF}$  voltage may be used within a bank. Input buffers that use  $V_{REF}$  are not 5V tolerant. The  $V_{CCO}$  and  $V_{REF}$  pins for each bank appear in the device pinout tables. Within a given package, the number of  $V_{REF}$  and  $V_{CCO}$  pins can vary depending on the size of device. In larger devices, more I/O pins convert to  $V_{REF}$  pins. Since these are always a superset of the  $V_{REF}$  pins used for smaller devices, it is possible to design a PCB that permits migration to a larger device. All  $V_{REF}$  pins for the largest device anticipated must be connected to the  $V_{REF}$  voltage, and not used for I/O [25].

#### 3.2.6 Configurable Logic Block

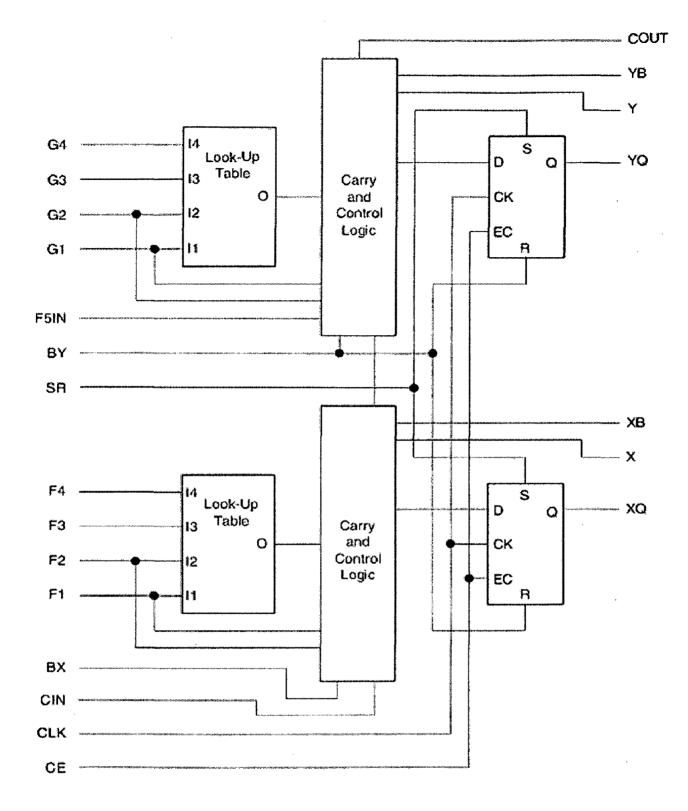

The basic building block of the Spartan-II CLB is the logic cell (LC). An LC includes a 4-input function generator, carry logic, and storage element. Output from the function generator in each LC drives the CLB output and the D input of the flip-flop. Each Spartan-II CLB contains four LCs, organized in two similar slices ; a single slice is shown in Figure 4. In addition to the four basic LCs, the Spartan-II CLB contains logic that combines function generators to provide functions of five or six inputs[25].

#### Look-Up Tables

Spartan-II function generators are implemented as 4-input look-up tables (LUTs). In addition to operating as a function generator, each LUT can provide a 16x1-bit synchronous RAM. Furthermore, the two LUTs within a slice can be combined to create a 16x2-bit or 32x1-bit synchronous RAM, or a 16x1-bit dual-port synchronous RAM.

The Spartan-II LUT can also provide a 16-bit shift register that is ideal for capturing high-speed or burst-mode data. This mode can also be used to store data in applications such as Digital Signal Processing [25].

#### Storage Elements

Storage elements in the Spartan-II slice can be configured either as edgetriggered D-type flip-flops or as level-sensitive latches. The D inputs can be driven either by function generators within the slice or directly from slice inputs, bypassing the function generators. In addition to Clock and Clock Enable signals, each slice has synchronous set and reset signals (SR and BY). SR forces a storage element into the initialization state specified for it in the configuration. BY forces it into the opposite state. Alternatively, these signals may be configured to operate asynchronously. All control signals are independently invertible, and are shared by the two flip-flops within the slice [25].

## Additional Logic