### A DISSERTATION

# Submitted in partial fulfillment of the requirements for the award of the degree

of

## MASTER OF TECHNOLOGY

in

#### **ELECTRICAL ENGINEERING**

(with Specialization in System Engineering and Operations Research)

# By SOUMYOJYOTI MAITRA

## DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE -247 667 (INDIA) JUNE, 2007

# INDIAN INSTITUTE OF TECHNOLOGY, ROORKEE ROORKEE

398/2007-31/JG

# **CANDIDATE'S DECLARATION**

I hereby declare that the work, which is being presented in this dissertation entitled INDUSTRIAL SEQUENCERS FOR PROCESS CONTROL APPLICATIONS USING PETRI NETS AND LADDER LOGIC DIAGRAM in the partial fulfillment of the requirements for the award of the degree of Master of Technology in Electrical Engineering with specialization in System Engineering and Operations Research, submitted in the Department of Electrical Engineering, Indian Institute of Technology Roorkee, Roorkee is an authentic record of my own work carried out during a period from May 2006 to June 2007 under the supervision of Dr. Indra Gupta, Assoc. Professor, Electrical Engineering Department, Indian Institute of Technology Roorkee, Roorkee.

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other Institute.

(Soumyojyoti Maitra)

This is to certify that the above statement made by the candidate is correct to the best of my knowledge and belief.

Date: 28.6.07

Dr. Indra Gupta Assoc. Professor Department of Electrical engineering Indian Institute of Technology Roorkee.

# ABSTRACT

Earlier hardwired electromechanical relays were used to realize and control discrete event systems, then a steep rise of the PLC was observed and today sequencing is normally implemented in software instead of relays. PLC's are industrially hardened microcomputer that performs discrete and continuous control functions in a variety of processing plants and control environments.

Originally PLC's were introduced as a relay replacement tool but in present days they find usage in all sorts of industrial control applications. From their onset in market one of the languages that gained prominence for programming PLC's is ladder logic diagrams of IEC 1131-3, recently flexible industrial automation are challenging the use of LLD's and other high level programming language methods. LLD's grow too large and difficult to understand and troubleshoot once complexity in sequence control increases.

Petri Nets originated from the field of computer science and is used as a tool for modeling asynchronous and concurrent activity, lately it is gaining popularity as an effective technique for sequence control of industrial automation systems. The popularity of Petri Nets is due to the fact that unlike LLD's not only they successfully control the system but they also help in system analysis, evaluation and simulation thereby making control strategies more easier to understand, troubleshoot, modify and evaluate.

In this dissertation complexity of sequence controllers designed using both LLD and PN for process control applications are compared based on number of basic elements used to model strategies and number of rules and logic transformations required to implement them. It is shown that with increasing complexity in applications Petri Nets (PN) supercedes its LLD counterpart in both measures thereby establishing PN as a better solution for designing controllers for discrete event systems.

Real Time Petri Net Controllers for different process control applications are synthesized on FPGA using VHDL, the syntactic and semantic compatibility of Petri Net descriptions with VHDL is observed for considered applications. Further it is observed that Field Programmable Logic for controller design results in creation of near-optimal controller implementations in terms of performance.

1

# Acknowledgements

It is my proud privilege to express my deep sense of gratitude and indebtedness towards my thesis supervisor Dr. Indra Gupta, Assoc.Professor, Department of Electrical Engineering, for her invaluable guidance & criticism, and kind and continuous encouragement, which were the vital factors in successful completion of the present work. I am heartily thanking her for deep concern towards my academics and personal welfare.

Her painstaking support and involvement in preparation of manuscript, theoretical analysis and simulation studies are gratefully acknowledged. I humbly acknowledge a lifetime's gratitude to her and hope for a continued interaction even in the future.

I express my deep sense of gratitude to the Prof. S. P. Gupta, Head, Electrical Engineering Department, Indian Institute of Technology, Roorkee, for providing excellent facilities and nice working atmosphere in the department for the research work.

I am thankful to Prof. M. K. Vasantha in so many ways. His constant encouragement and willingness to listen to and help with my academic queries or personal problems are some of the things I benefited with. I found him a complete teacher, who taught me that it is equally important to be a good human being as much as to be a good technocrat. The education given by him will help me all my life.

My sincere thanks are also due to Dr. Surendra Kumar, Dr. Rajendra Prasad, Dr. H.O. Gupta, and Dr. G. N. Pillai for extending moral support and technical discussions as and when required during the work.

I thankfully appreciate and acknowledge my indebtedness to research scholars Dr. Vishal Kumar, Dr. Vijayender Singh, Mr. Rohit Bhakar, Mrs. Nidhi Singh, Mrs. Nidhi Kulkarni and Mr. S. K. Tomar for their help, cooperation, and moral support from time to time. My special thanks goes to the fellow classmates Mr. Shashank Saran Rai, Mr. Rohith Kumar H.C, Ms. Sowmya Kollipara, Mr. Patel Vinod Kumar, Mr. Siluveru Karunakar, Mr. Srikanth Reddy, Mr. Anil Kumar, Mr. Kalyan Ayyagiri, Mr. M. Chandrashekar, Mr. Praveen Rangisetti for their cooperation and moral support during my stay.

Besides the enjoyment of doing research work, this time has also given me an opportunity to make great friends. I shall never be able to forget the time, which I spent with Mr. Dept of Electrical Engineering, IIT Roorkee

V.S.Sriram and Mr. Sheri Sundeep and Mr.Abhishek Banick and Mr. Suman Chatterjee and this writing space is not enough to write about the memories I have in my mind.

I am thankful to the technical staff of the SEOR Lab Shri Kalyan Singh, Shri C.M. Joshi, and other staff members for their timely cooperation and needful help.

Thanks are also due to all those who helped me directly and indirectly for the completion of the work.

My heartiest gratitude goes to my parents and other members of family, for constantly supporting me, which allowed me to concentrate on my work.

I would like to dedicate this research work to my family and my well wishers.

If what you are working for really matters, you will give it all you have got. Efforts may fail but don't fail to make efforts.

(Soumyojyoti Maitra)

# Contents

#### Page Number

| ABSTRACT                                                        | i   |

|-----------------------------------------------------------------|-----|

| ACKNOWLEDGEMENTS                                                | ii  |

| CONTENTS                                                        | iv  |

| LIST OF FIGURES                                                 | vii |

| LIST OF TABLES                                                  | X   |

| LIST OF ABBREVIATIONS                                           | xi  |

| 1) INTRODUCTION                                                 | 1   |

| 1.1 General                                                     | 1   |

| 1.2 Formal Methods in Controller Design                         | 3   |

| 1.2.1 Informal Specification                                    | - 3 |

| 1.2.1.1 Problem specific Functional Properties                  | 3   |

| 1.2.1.2 Standard Functional Properties                          | 5   |

| 1.2.1.3 Non-functional Properties                               | 5   |

| 1.2.2 Formalization                                             | 5   |

| 1.2.2.1 Formalization of Problem specific functional Properties | 5   |

| 1.2.2.2 Formalization of standard functional properties         | 5   |

| 1.2.2.3 Formalization of non-functional properties              | 5   |

| 1.2.3 Verification and Validation                               | 6   |

| 1.2.3.1 Verification                                            | 6   |

| 1.2.3.2 Validation                                              | 6   |

| 1.2.4 Evaluation                                                | 6   |

| 1.2.5 Implementation                                            | 6   |

| 1.3 Objective of Thesis                                         | 6   |

| 1.4 Outline of Thesis                                           | 7   |

|                                                                 |     |

# 2) PETRI NETS

| 2.1 Introduction                              | 9  |

|-----------------------------------------------|----|

| 2.2 Brief History of Petri Nets               | 9  |

| 2.3 Overview of Petri Nets                    | 10 |

| 2.4 Structure of Petri Nets                   | 15 |

| 2.4.1 Marking and Execution rule of Petri Net | 16 |

|                                               |    |

#### Page Number

27

| 2.5 Delessie wel Deservetien of Detail Net                     | 18 |  |

|----------------------------------------------------------------|----|--|

| 2.5 Behavioral Properties of Petri Net.                        | 10 |  |

| 2.5.1 Reachability                                             | 18 |  |

| 2.5.2 Boundedness                                              | 18 |  |

| 2.5.3 Liveness                                                 | 18 |  |

| 2.5.4 Reversibility and Home State                             | 20 |  |

| 2.5.5 Persistence                                              | 20 |  |

| 2.6 Analysis of Petri Net Model based on Reachability Criteria |    |  |

| 2.7 Petri Nets and Industrial Automation                       |    |  |

| 2.8 The Real Time Petri Net Algorithm                          |    |  |

| 2.9 Conclusion                                                 |    |  |

# 3) THE PROGRAMMABLE LOGIC CONTROLLERS

| 3.1 Introduction                       | 27   |

|----------------------------------------|------|

| 3.2 Evolution of PLC                   | 27   |

| 3.3 PLC Architecture                   | 28   |

| 3.4 Benefits of PLC                    | 31   |

| 3.5 Programming Languages              | 31   |

| 3.5.1 Graphical                        | 32   |

| 3.5.1.1 Ladder diagram (LD)            | 32   |

| 3.5.1.2 Functional Block Diagram (FBD) | 33   |

| 3.5.2 Textual                          | 33   |

| 3.5.2.1 Instruction List               | 33   |

| 3.5.2.2 Structured Text                | 35   |

| 3.6 Conclusion                         | - 35 |

|                                        | ,    |

| 4) EVALUATION CRITERIA                            | 35 |

|---------------------------------------------------|----|

| 4.1 Introduction                                  | 37 |

| 4.2 Criteria for Evaluation                       | 39 |

| 4.2.1 Design Complexity                           | 39 |

| 4.2.1.1 Graphical Complexity                      | 39 |

| 4.2.1.2 Adaptability for change of Specifications | 40 |

| 4.2.2 Response Time                               | 41 |

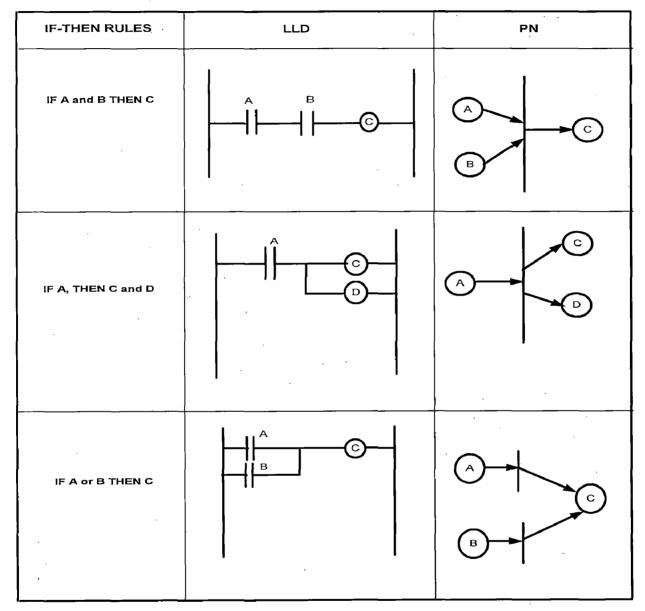

| 4.3 Rule based Comparison                         | 42 |

•

| Page Nu                                                  | ımber |

|----------------------------------------------------------|-------|

| 4.4 Example                                              | 44    |

| 4.5 Conclusion                                           | 52    |

| 5) CASE STUDIES                                          | 53    |

| 5.1 Introduction                                         | 53    |

| 5.2 Case Study 1:Two Level Elevator Controller System    | 54    |

| 5.3 Case Study 2: Three Level Elevator Controller System | 62    |

| 5.4 Case Study 3: Four Level Elevator Controller System  | 71    |

| 5.5 Conclusion                                           | 80    |

| 6) RESULTS AND DISCUSSIONS                               | 81    |

| 6.1 Results and Discussion                               | 81    |

| 7) CONCLUSION AND SCOPE FOR FUTURE WORK                  | 85    |

| 7.1 Conclusion                                           | 85    |

| 7.2 Scope for Future Work                                | 85    |

| BIBLIOGRAPHY                                             | 87    |

| APPENDIX A                                               | 91    |

| APPENDIX B                                               | 109   |

| APPENDIX C                                               | 115   |

.

# **LIST OF FIGURES**

| Number | Figure<br>Number | Figure Description                                        | Page<br>Number |

|--------|------------------|-----------------------------------------------------------|----------------|

| 1      | Fig 1.1          | Development of Standards for PLC Programming              | · 1            |

| 2      | Fig 1.2          | Design Process for a Logic Control System                 | 2              |

| 3      | Fig 1.3          | Formal Methods in Design Process                          | 4              |

| 4      | Fig 2.1          | A Simple Graph Representation of a PN Structure           |                |

| •      |                  |                                                           | 11 ·           |

| 5      | Fig 2.2          | Marked Graph Representation of PN structure in Fig        |                |

| •      |                  | 2.1                                                       | 12             |

| 6      | Fig 2.3          | A Petri Net graph after firing t2                         | 13             |

| 7      | Fig 2.4          | A Petri Net graph after firing t1                         | 14             |

| 8      | Fig 2.5          | A Petri Net graph after firing t3                         | 14             |

| . 9    | Fig 2.6          | A Petri Net graph after firing t5                         | 15             |

| 10     | Fig 2.7          | The Simple PN Graph                                       | 16             |

| 11     | Fig 2.8          | Marked PN graph of fig 2.7 with initial marking           | 17             |

|        | C                | $\mu$ (p1) = (1, 0, 1, 0, 2)                              |                |

| 12     | Fig 2.9          | Basic Firing Rules                                        | 19             |

| 13     | Fig 2.10         | A Petri Net with initial marking $(1,0,1,0)$ and infinite |                |

|        |                  | reachable state space                                     | 22             |

| 14     | Fig 2.11         | Reachability Tree for PN of Fig 2.10                      | 22             |

| 15     | Fig 3.1          | Architecture of a Programmable Logic Controller           | 29 ·           |

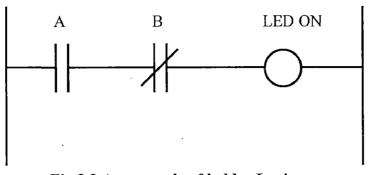

| 16     | Fig 3.2          | An example of Ladder Logic                                | 34             |

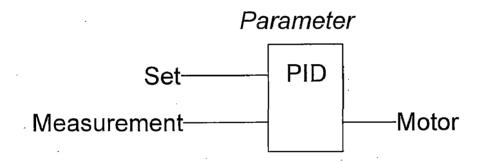

| 17     | Fig 3.3          | An example of FBD                                         | 34             |

| 18     | Fig 3.4          | An example of IL program                                  | 34             |

| 19     | Fig 3.5          | An example of ST program                                  | 34             |

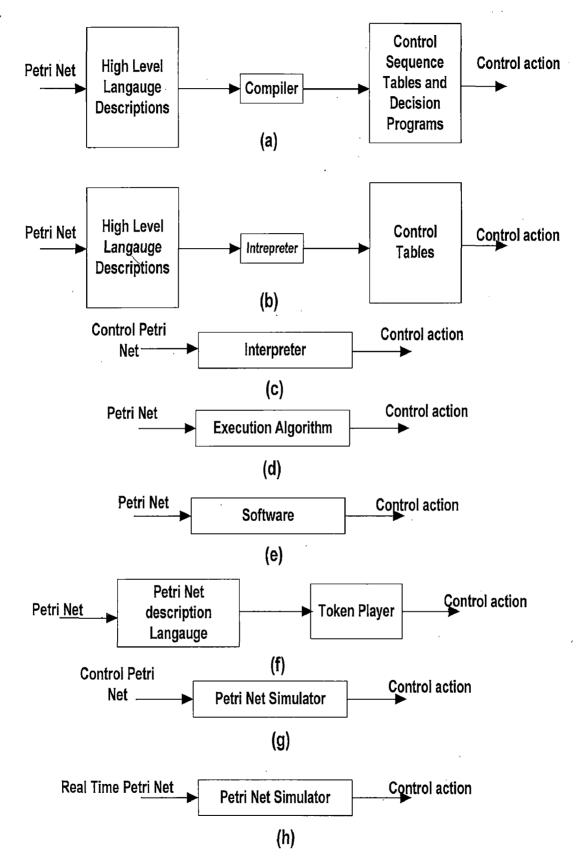

| 20     | Fig 4.1          | Various methods of Petri Net based sequence Control       | 38             |

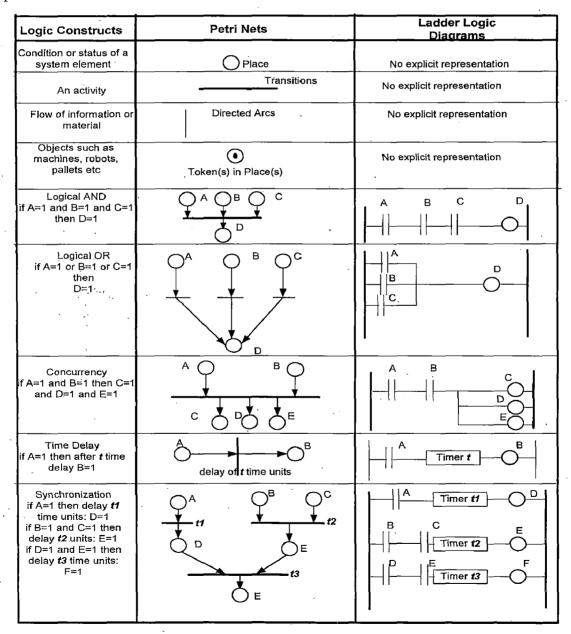

| 21     | Fig 4.2          | Control logic representation in PN and LLD                | 40             |

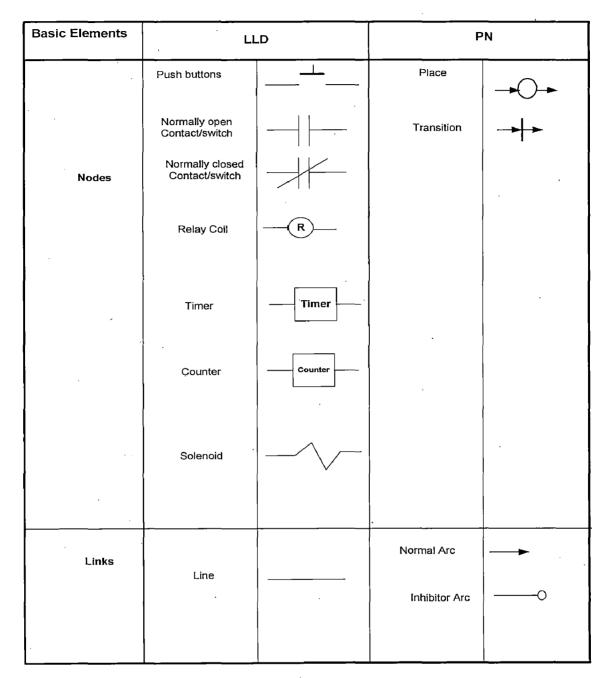

| 22     | Fig 4.3          | Basic Elements representation in LLD and PN               | 41             |

| - 23   | Fig 4.4          | IF-THEN Rules for LLD and PN                              | 43             |

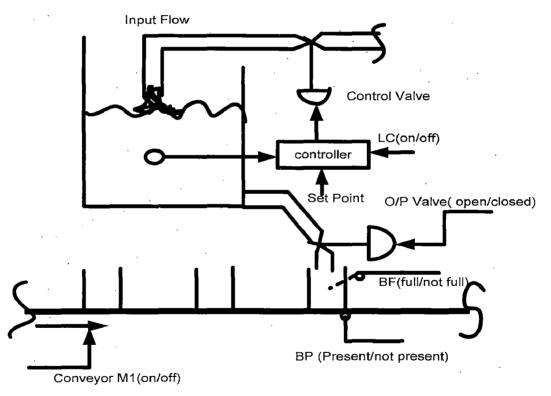

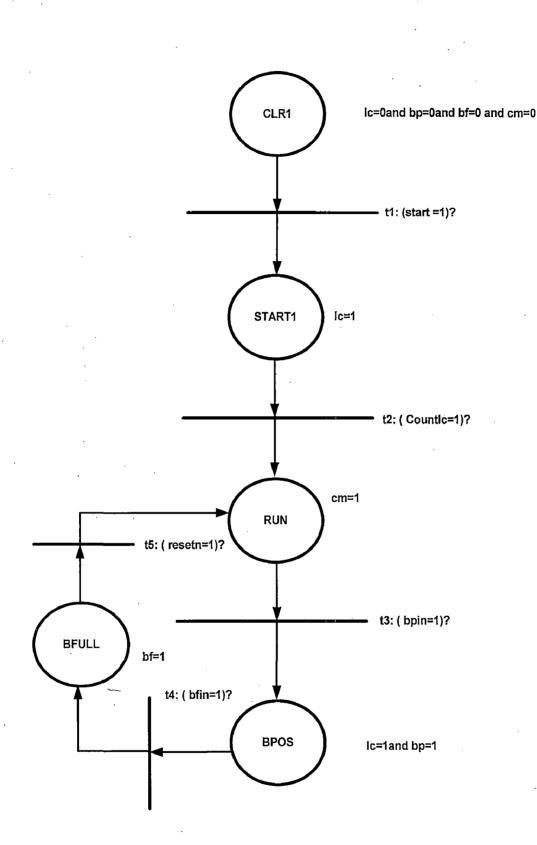

| 24     | Fig 4.5          | Bottle Filling System                                     | 44             |

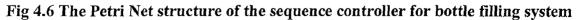

| 25     | Fig 4.6          | The Petri Net structure of sequence controller for        |                |

|        |                  | bottle filling system                                     | 48             |

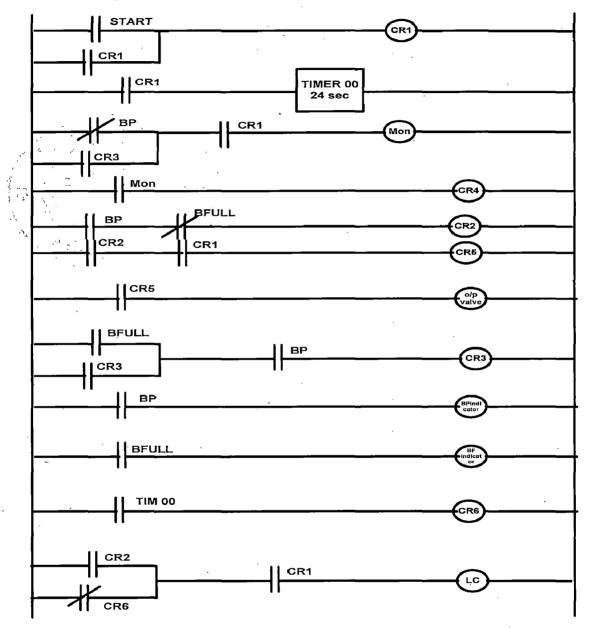

| 26     | Fig 4.7          | The Logic Diagram of the LLD algorithm for the            |                |

|        | Ŭ.               | bottle filling system                                     | 49             |

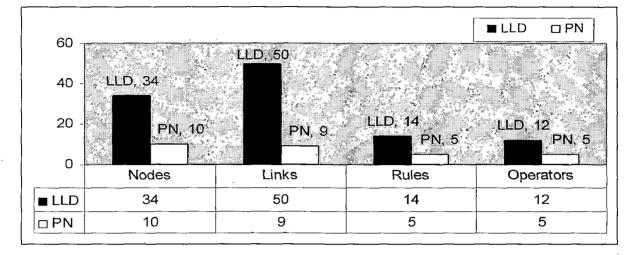

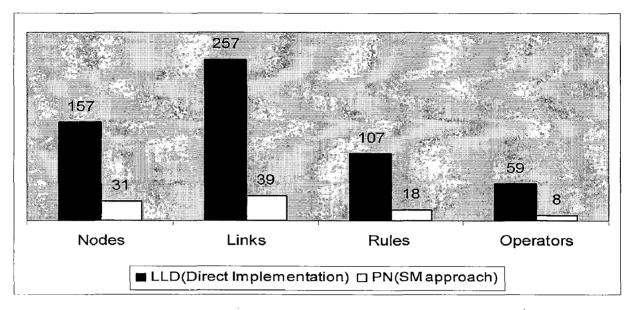

| 27     | Fig 4.8          | The comparison of LLD and PN algorithms for the           |                |

|        | U                | sequence controller of bottle filling system              | 52             |

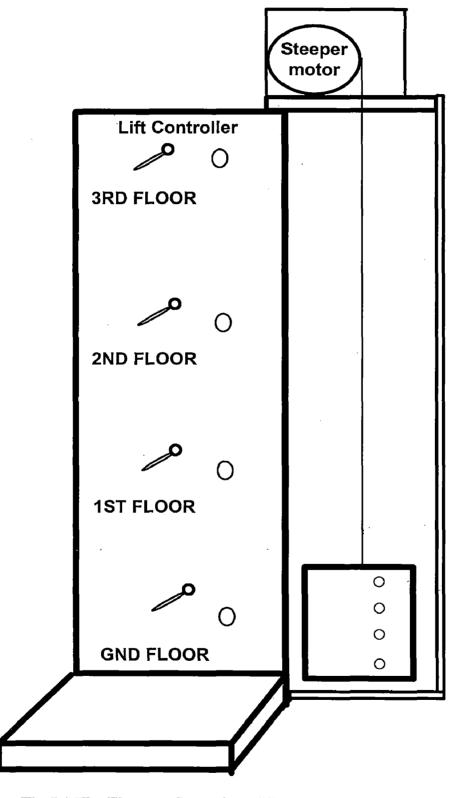

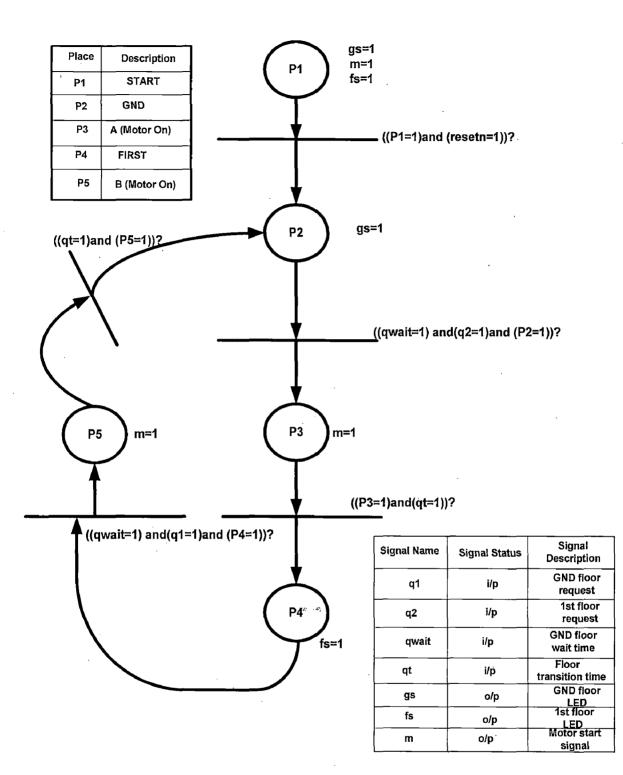

| 28     | Fig 5.1          | The Elevator Setup from Vinytics Peripherals Ltd          | 55             |

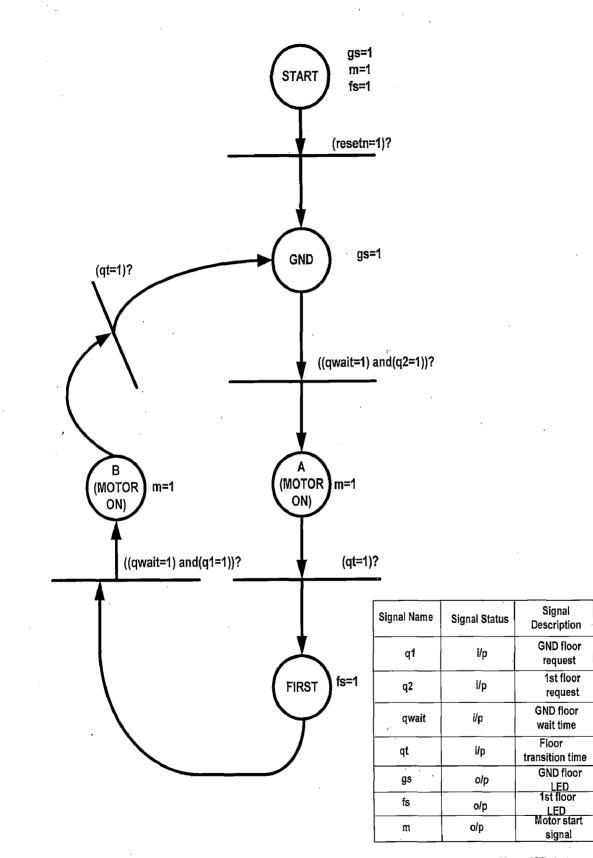

| 29     | Fig 5.2          | The RTPN structure of two level elevator sequence         |                |

| -      | 0                | controller (SM Approach)                                  | 56             |

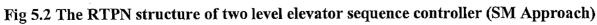

| 30     | Fig 5.3          | The RTPN structure of two level elevator sequence         |                |

|        | C                | controller (Place Oriented Conditionals Approach)         | 57             |

|        |                  |                                                           | •              |

Dept of Electrical Engineering, IIT Roorkee

vii

|          | Number           | Figure<br>Number    | Figure Description                                                                         | Page<br>Number |

|----------|------------------|---------------------|--------------------------------------------------------------------------------------------|----------------|

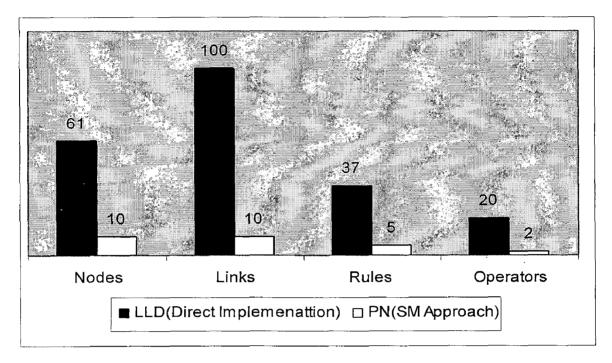

| •        | 31               | Fig 5.4.1           | The comparison of PN (SM) and LLD based sequence controllers for two level elevator system | 59             |

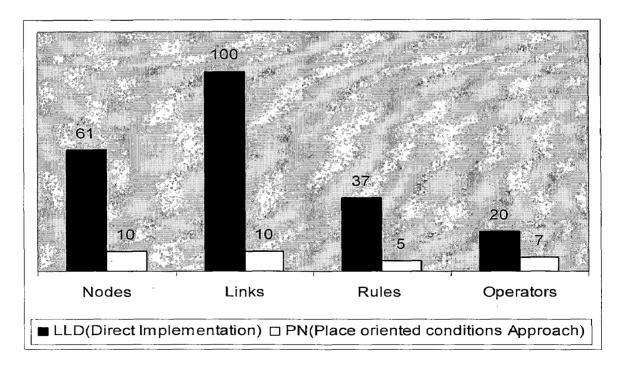

|          | 32               | Fig 5.4.2           | The comparison of PN (Place Oriented conditionals                                          |                |

|          | 52               | 1 lg J. <b>4.</b> 2 | Approach) and LLD based sequence controllers two                                           | 59             |

|          |                  |                     | level elevator system                                                                      | 57             |

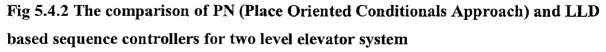

|          | 33               | Fig 5.4.3           | The comparison of PN(SM Approach) and PN(Place                                             |                |

|          |                  | 11g 5.4.5           | Oriented Conditionals Approach) based sequence                                             |                |

|          |                  |                     | controllers for two level elevator system                                                  | 60             |

|          | 34               | Fig 5.4.4           | The Comparison of LLD (Directly Obtained) and                                              | 60             |

|          | 57               | 11g J1              | LLD (Obtained from Formalization) based sequence                                           | 00             |

|          |                  |                     | controllers for two level elevator system.                                                 | · .            |

|          | 35               | Fig 5.4.5           | The Reachability Graph for RTPN structure of two                                           | 61             |

|          | 55               | 1 ig 5.4.5          | level elevator sequence controller                                                         | 01             |

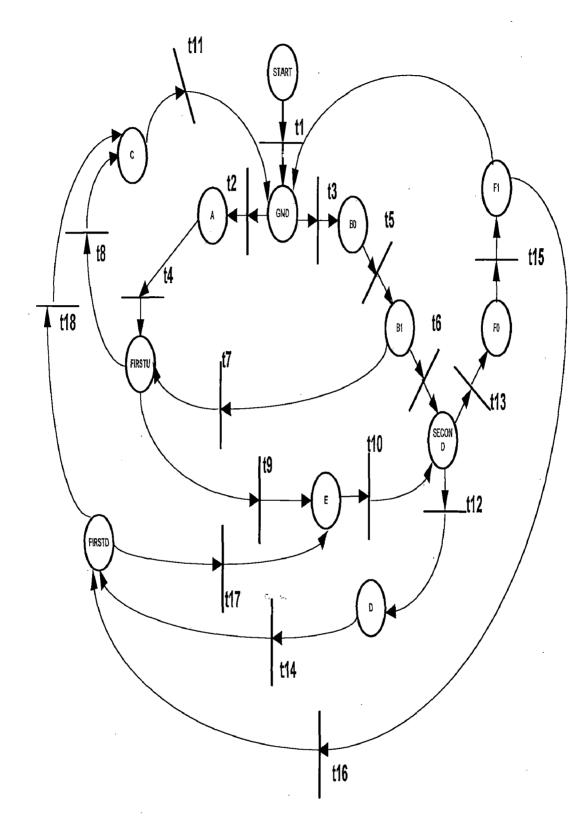

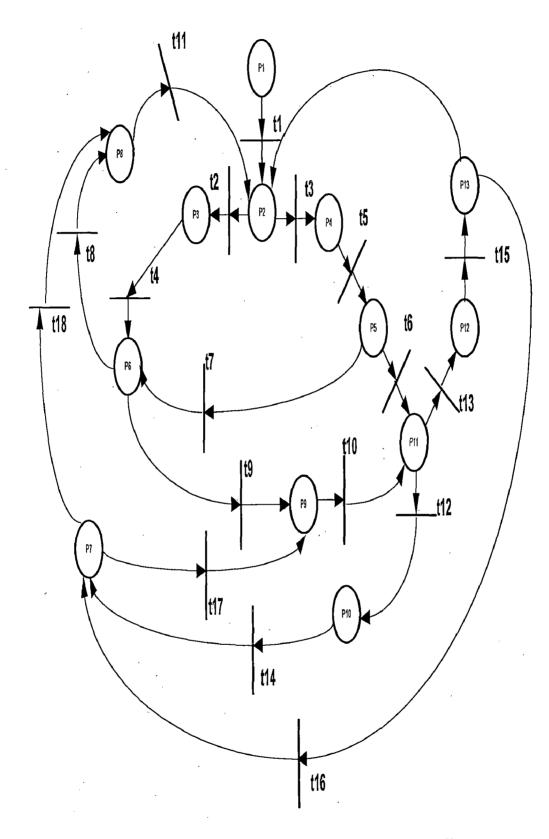

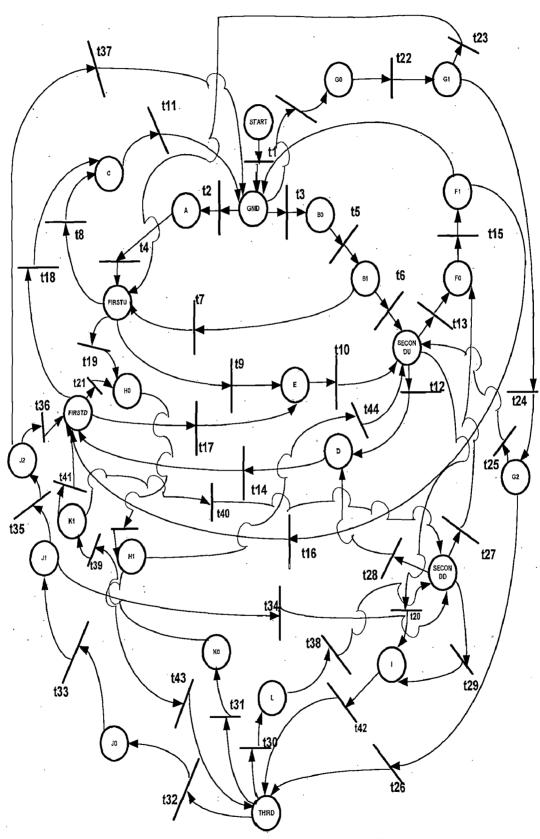

|          | 36               | Fig 5.5             | The RTPN structure of a three level elevator                                               | 63             |

|          | 50               | Fig 5.5             | sequence controller (SM Approach)                                                          |                |

|          | 37               | Fig 5.6             | The RTPN structure of a three level elevator                                               | 64             |

|          | 57               | 1 ig 5.0            | sequence controller (Place Oriented Conditionals                                           | 07             |

|          |                  | • •                 | Approach)                                                                                  | -              |

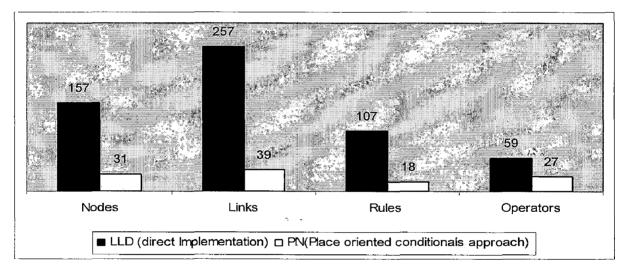

|          | 38               | Fig 5.7.1           | The comparison of PN (SM Approach) and LLD                                                 | 69             |

|          | 30 .             | 1 lg 5.7.1          | based sequence controllers for three level elevator                                        | 07             |

|          |                  |                     | system                                                                                     | •              |

|          | 39               | Fig 5.7.2           | The comparison of PN (SM Approach) and LLD                                                 | 69             |

|          | 29               | rig 5.7.2           | based sequence controllers for three level elevator                                        | 09             |

|          |                  |                     | system                                                                                     |                |

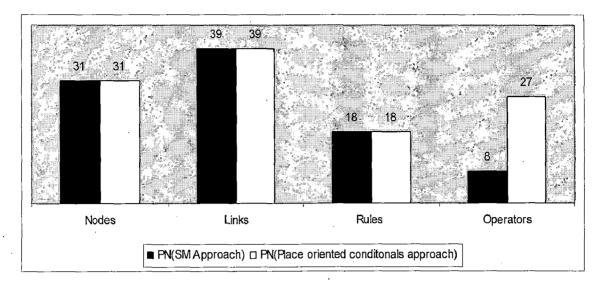

|          | 40               | Fig 5.7.3           | The comparison of PN (SM Approach) and PN (Place                                           | 70             |

|          | 40               | 1 ig 5.7.5          | Oriented Conditionals Approach) based sequence                                             | 70             |

|          |                  |                     | controllers for three level elevator system                                                |                |

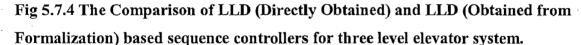

|          | 41               | Fig 5.7.4           | The Comparison of LLD (Directly Obtained) and                                              | 70             |

|          | 41               | 11g J.7.4           | LLD (Obtained from Formalization) based sequence                                           | 10             |

|          |                  |                     | controllers for three level elevator system.                                               |                |

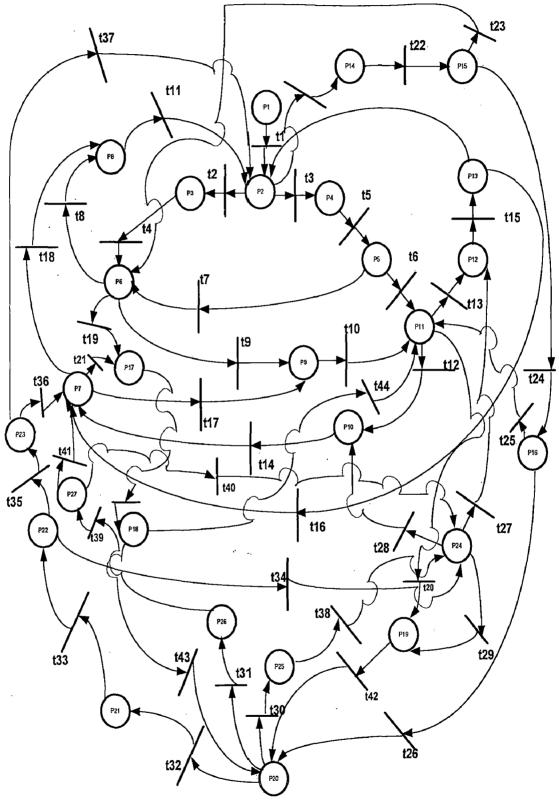

|          | 42               | Fig 5.8             | •                                                                                          | 72             |

|          | 42               | 11g 5.0             | Controller (SM Approach)                                                                   | 12             |

|          | 43               | Fig 5.9             | The RTPN Algorithm of Four Level Elevator                                                  |                |

| <b>`</b> | чJ               | 11g J.J             | Sequence Controller (Place Oriented Conditionals                                           |                |

|          |                  |                     | Approach)                                                                                  | 73             |

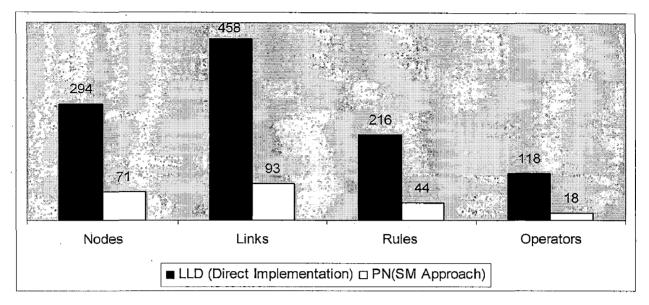

|          | 44               | Fig 5.10.1          | The comparison of PN (SM Approach) and LLD                                                 | 15             |

|          |                  | 11g 5.10,1          | based sequence controller for four level elevator                                          |                |

|          |                  |                     | system                                                                                     | 78             |

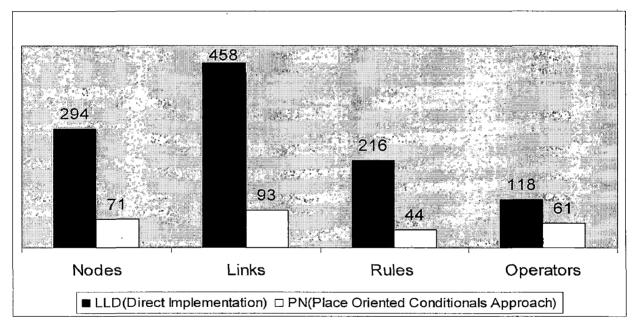

|          | 45               | Fig 5.10.2          | The comparison of PN (Place Oriented Conditionals                                          | 10             |

|          | 45               | 1 ig 5.10.2         | Approach) and LLD based sequence controllers for                                           |                |

|          |                  |                     | four level elevator system                                                                 | 78             |

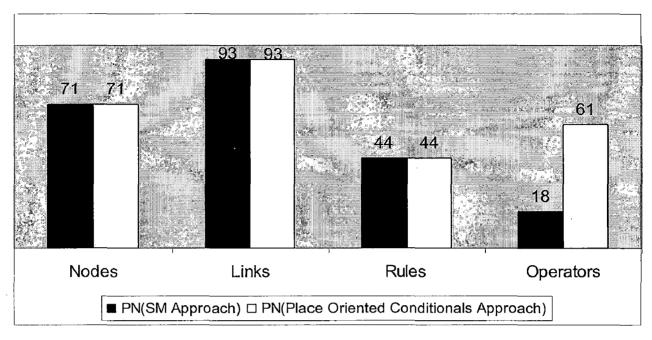

|          | 46               | Fig 5.10.3          | The comparison of PN (SM Approach) and PN (Place                                           | 10             |

|          | - <del>1</del> 0 | 1.18 2.10.2         | Oriented Conditionals Approach) based sequence                                             | -              |

|          |                  |                     | controllers for four level elevator system                                                 | 79             |

|          |                  |                     | controllers for tour lever elevator system                                                 | 17             |

Dept of Electrical Engineering, IIT Roorkee

viii

| Number               | Figure<br>Number                         | Figure Description                                                                                                                                                                                                                                                     | Page<br>Number               |

|----------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 47                   | Fig 5.10.4                               | The Comparison of LLD (Directly Obtained) and<br>LLD (Obtained from Formalization) based sequence<br>controllers for four level elevator system.                                                                                                                       | 79                           |

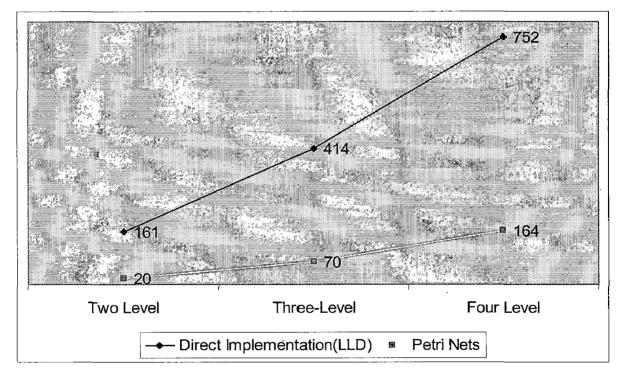

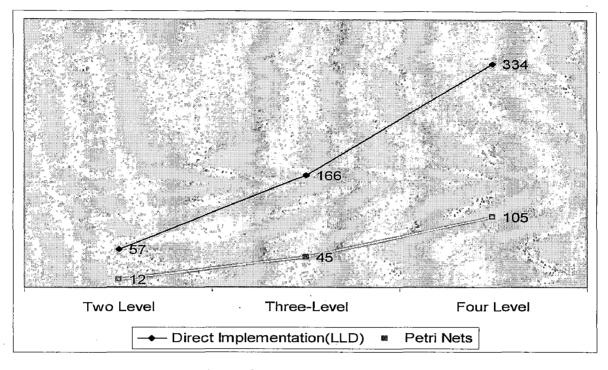

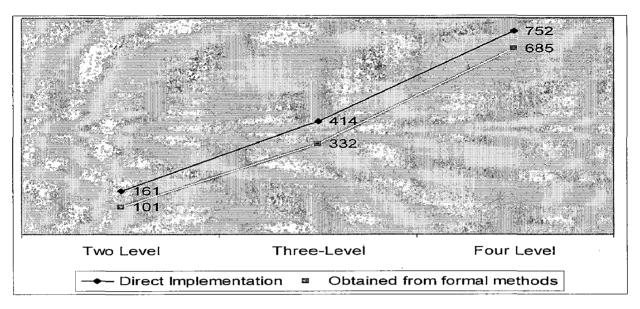

| 48                   | Fig 6.1                                  | Complexity comparison of two, three and four level elevator sequence controller designed using LLD and                                                                                                                                                                 |                              |

| 49                   | Fig 6.2                                  | PN Approach in terms of number of basic elements<br>Complexity comparison of two, three and four level<br>elevator sequence controller designed using LLD and<br>PN Approach in terms of sum of number of rules and                                                    | 79                           |

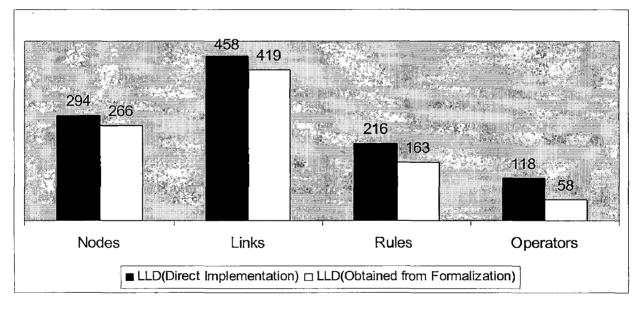

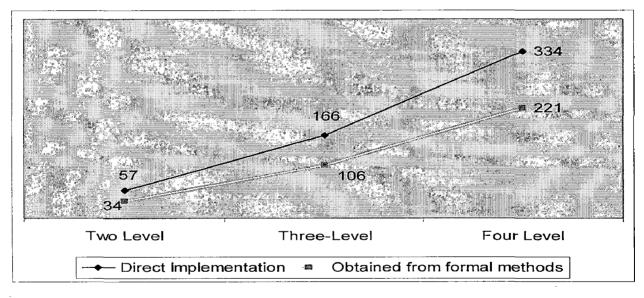

| 50                   | Fig 6.3                                  | logical operators<br>Complexity comparison of two, three and four level<br>elevator sequence controller designed using LLD<br>(directly implemented) and LLD (derived from                                                                                             | 82                           |

| 51                   | Fig 6.4                                  | formal methods) in terms of number of basic<br>elements<br>Complexity comparison of two, three and four level<br>elevator sequence controller designed using LLD<br>(directly implemented) and LLD (derived from<br>formal methods) in terms of sum of number of rules | 83                           |

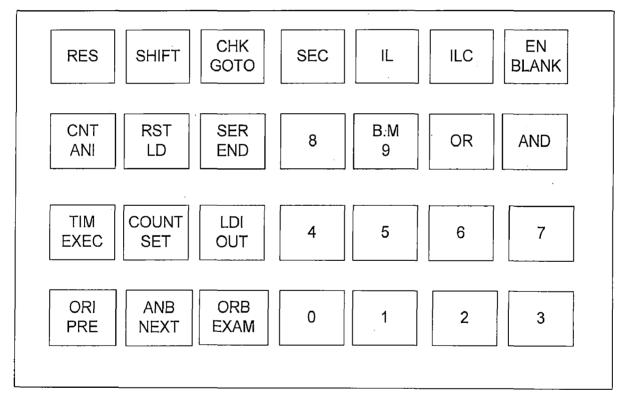

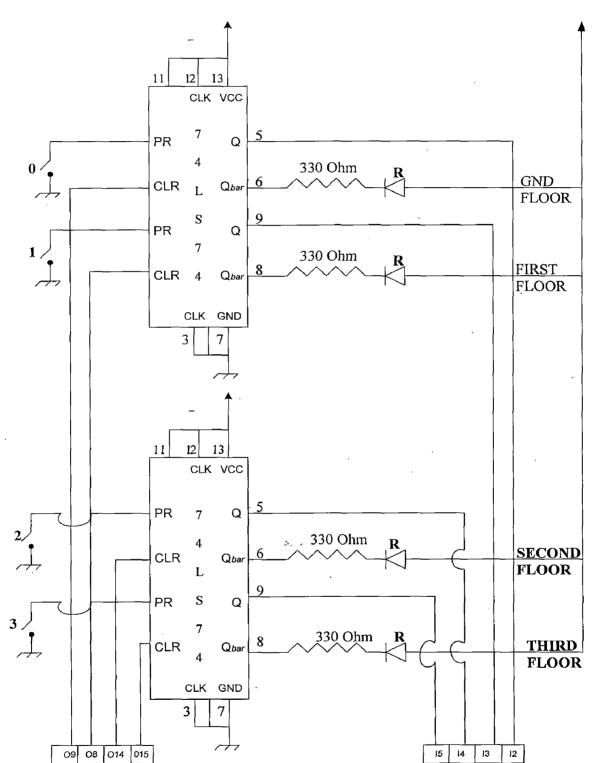

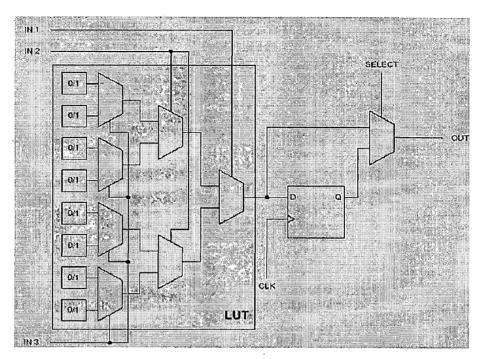

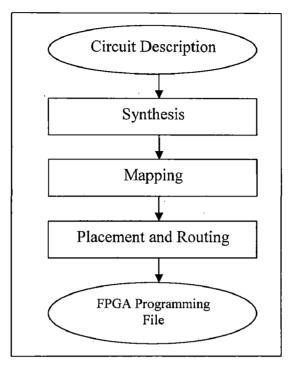

| 52<br>53<br>54<br>55 | Fig A.1<br>Fig A.2<br>Fig B.1<br>Fig 7.6 | and logical operators<br>Front View of Hand Held Programmer<br>The Elevator Controller Card<br>Simple Logic Block Structure<br>FPGA design flow                                                                                                                        | 83<br>92<br>95<br>111<br>112 |

#### Dept of Electrical Engineering, IIT Roorkee

5

ix

# **LIST OF TABLES**

| Number | Table<br>Number | Table Description                                                                                             | Page<br>Number |

|--------|-----------------|---------------------------------------------------------------------------------------------------------------|----------------|

| 1      | Table 3.1       | Advantages of PLC Programming                                                                                 | 31             |

| 2      | Table 4.1       | Hardware platforms used                                                                                       | 37             |

| 3      | Table 4.2       | The I/O specification for the RTPN based sequence                                                             | . *            |

|        |                 | controller of bottle filling system.                                                                          | 47             |

| 4      | Table 4.3       | Comparison of LLD and PN based Sequence controller for bottle filling system                                  | 51             |

| 5      | Table 5.1       | I/O Specifications for two level elevator system                                                              | 54             |

| 6      | Table 5.2       | Comparison of Sequence Controllers designed for two                                                           |                |

|        |                 | level elevator system                                                                                         | 58             |

| 7      | Table 5.3       | I/O Specifications for three level elevator sequence controller                                               | 62             |

| 8      | Table 5.4       | Details description of transitions and places of RTPN structure for three level elevator sequence controller. | 65             |

| 9      | Table 5.5       | I/O's used in RTPN structure of three level elevator sequence controller.                                     | 67             |

| 10     | Table 5.6       | Comparison of Sequence Controllers designed for three level elevator system                                   | . 68           |

| 11     | Table 5.7       | I/O specifications of Four level elevator controller                                                          | 08             |

| 11     | 1 abic 5.7      | module                                                                                                        | 71.            |

| 12     | Table 5.8       | The Place and transition descriptions of RTPN structures of sequence controllers for four level               |                |

|        |                 | elevator system                                                                                               | 74             |

| 13     | Table 5.9       | The I/O description for RTPN structures of four level sequence controller                                     | 76             |

| 14     | Table 5.10      | Comparison of sequence controllers designed for four<br>level elevator system                                 | 77             |

| 15     | Table A.1       | The I/O Description of the Elevator Controller Card                                                           | 97             |

#### Dept of Electrical Engineering, IIT Roorkee

х

# LIST OF ABBREVIATIONS

1 IEC International Electrotechnical Commission

2 PLC Programmable Logic Controller

3 LLD Ladder Logic Diagrams

4 PN Petri Nets

5 VHDL Very High Speed Integrated Circuit Hardware Description Language

6 FPGA Field Programmable Gate Array

7 VPL Vinytics Peripherals Ltd

8 FSM Finite State Machine

9 RTPN Real Time Petri Net

10 NEMA National Electrical Manufacturers Association

11 CPU Central Processing Unit

12 LD Ladder Diagram

13 FBD Functional Block Diagram

14 IL Instruction List

15 ST Structured Text

16 PLCT PLC Trainer

17 PC Personal Computer

18 LED Light Emitting Diode

19 EPROM Electronically Programmable Read Only Memory

20 HDL Hardware Description Language

21 IP Intellectual Property

22 DSP Digital Signal Processing

23 VLSI Very Large Scale Integration

24 JTAG Joint Technology Action Group

25 IEEE Institute of Electrical and Electronics Engineers

26 IDE Integrated Drive Electronics

27 VGA Video Graphic Adapter

28 PROM Programmable Read Only Memory

29 SRAM Static Random Access Memory

30 SDRRAM Single Data Rate Random Access Memory

31 USB Universal Serial Bus

32 LCD Liquid Crystal Display

- 33 BST Boundary Scan Test

- 34 PCB Printed Circuit Board

35 CMOS Complementary Metal Oxide Semiconductor

36 TTL Transistor Transistor Logic

37 SM State Machine

# CHAPTER 1

# **INTRODUCTION**

# 1.1: General

Since 1970's PLC have been the primary workhorse of industrial automation. [1] For the few last decades it has been providing a distinct field of research, development and application in the field of control engineering. [24]

The area of control engineering in particular has contributed greatly in terms of design methods and programming languages used for design of PLC's. Due to the importance of PLC's for industrial applications many of these methods have been standardized internationally.

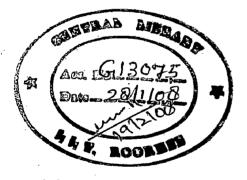

Figure 1.1 shows an overview of the standardization, with IEC 1131 being one of the most influential one. [6]

NEMA programmable controllers committe formed (USA)

#### Fig 1.1 Development of Standards for PLC Programming

Dept of Electrical Engineering, IIT Roorkee

Although it has been a perceptive discipline for a long time, industrial PLC programming methods have been more and more influenced by formal methods. [2] [36]

There are several reasons for the application of formal methods with PLC programming:

1) The growing complexity of the control problem with the demand for reduced development time and the possible reuse of existing software modules requires the need for a formal approach in PLC programming.[1]

2) The demand for high quality solutions and especially the application of PLC's in safety critical processes need verification and validation procedures, hence there is a requirement of formal methods in the process of design to prove specific static and dynamic properties of the programs. For example properties such as liveness, boundedness and reachability. [1]

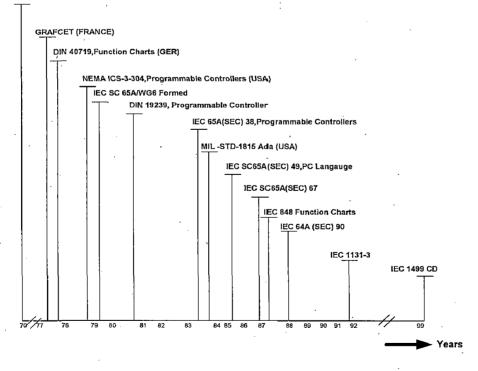

In figure 1.2 a general model of the logic control design process is shown, without the use of formal methods the controller design process only consists of the external ring. The controller is realized from the informal specification by direct implementation and afterwards it is informally validated against the informal specifications. [1]-[2]

#### Fig 1.2 Design Process for a Logic Control System

Dept of Electrical Engineering, IIT Roorkee'

In almost all design procedures, the designer of a logic control system starts with a given informal specification of the problem in hand. [36]

"The term informal refers to everything that is not based on strictly composed, syntactically and semantically well-defined form". [1] In general the informal specification consists of details of the uncontrolled process and the requirements for control system.

The industrial standard approach to obtain the realization from the informal specification is direct implementation of controller using any one of the standard PLC programming languages and with standard hardware and well defined PLC functionality, the realization consists of the programmed control algorithm [1]. The non model based validation or in short the informal method of validation involves test of the implemented controller against the informal specification. The problems that are encountered with informal validation procedure is that it lacks completeness and is quite time consuming involving a lot of manhour in work.

Recent years have seen a need amongst the PLC fraternity to use formal methods in programming and validation because of the advantages we have already discussed. Formalization refers to conversion of an informal specification to a formal specification and deriving the realization from formal specification is called Implementation. [34]

# **1.2:** Formal methods in Controller Design

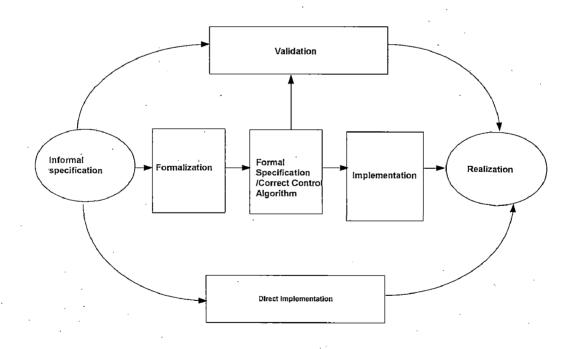

Figure 1.3 demonstrates the different parts of informal specification, how they are formalized and how the control algorithm obtained be checked against the formal specification.

# **1.2.1: Informal Specification**

An informal specification contains different types of properties, the functional properties include standard and problem specific properties along with the non-functional ones the prominent one being quality requirements to be met by the controller.

#### **1.2.1.1**Problem specific Functional Properties

The problem specific functional properties include those aspects of informal specification that describes the expected behavior of the controller under design.

Ex: turn on/off a motor when a certain switch is pressed.

Fig 1.3 Formal Methods in Design Process

Dept of Electrical Engineering, IIT Roorkee

#### **1.2.1.2 Standard Functional Properties**

Standard functional properties are not dependent on the control objective but formalization of these properties does depend on the formalism used to describe the controller. Ex: A controller should never get struck in an infinite loop.

#### **1.2.1.3 Non-Functional Properties**

These are the properties that do not affect the behavior of controller, mainly they include details about software quality.

#### **1.2.2:** Formalization

In order to be used in a formal design approach all the informal properties need to be formalized.

#### **1.2.2.1** Formalization of Problem Specific Functional Properties

It consists of two parts: first, the formalization of the control algorithm and then the formal description of problem specific properties to be fulfilled by the algorithm. The formalization of problem specific properties is done manually and is the main effort taking assignment during controller development cycle.

#### **1.2.2.2** Formalization of Standard Functional Properties

"Standard properties include first and foremost that the algorithm respects the percepts of his formalism". [2]

#### **1.2.2.3 Formalization of Non-Functional Properties**

All non-functional properties cannot be formalized, however it is possible to connect a nonfunctional property to some measurable properties of algorithm and hence, obtain a corresponding measure.

Ex: Readability of an algorithm can be connected to number of comments.

### **1.2.3: Verification and Validation**

As, both the terms are not disjoint so often one seems to confuse one term with another. The two terms as given in both reference [1] and [2] is

"<< Verification: Am I building the product right? >>

<< Validation: Am I building the right product? >>"

#### **1.2.3.1 Verification**

Refers to the correct functioning of control algorithm while adhering to the standard functional properties. It is the first step after all formalizations and if result of verification is negative, the control algorithm has to be redesigned again and again until a satisfactory result is obtained.

#### 1.2.3.2 Validation

Refers to the correct functioning of designed control algorithm while adhering to the problem specific functional properties. If the result of validation is negative, then first, the control algorithm is checked for failure and if there is no failure in control algorithm, next it is checked if informal property is formalized properly. If error is found in the process of formalization then the informal properties are rechecked and formalized again if required with additional assumptions to meet the correct validation requirements. Care must be taken that if during validation process the control algorithm is modified then verification of the modified control algorithm is must before proceeding to the next step.

#### 1.2.4: Evaluation

In this process the non-functional properties of the controller are verified and measured.

#### 1.2.5: **Implementation**

It is the last and final step in design process where a correct realization of the controller under design is obtained from the correct formal description so formulated.

### **1.3: Objective of the Thesis**

In this thesis complexity of sequence controllers designed using both ladder logic diagrams and Petri Nets for the following process control applications:

a) A bottle filling system.

b) A two level elevator system. Dept of Electrical Engineering, IIT Roorkee

c) A three level elevator system.

d) A four level elevator system.

are compared based on number of basic elements used to model strategies and number of rules and logic transformations used to implement them. It has been shown that with increasing complexity in applications Petri Nets supercedes its LLD counterpart in both the measures thereby establishing PN as a better tool for designing controllers for process control applications.

Further, real time Petri Net controllers for all the above applications are synthesized on FPGA using VHDL and ladder logic codes are also derived from PN structures and it is observed that the LLD codes obtained by using the formal methods like PN instead of direct realization from informal specification gives more compact and readable codes than the ones obtained from direct implementation.

# 1.4: Outline of the Thesis

Chapter two discusses the Petri Nets concepts along with the extension of RTPN.

Chapter three gives a brief idea about the PLC and the languages that are used for the programming of PLC based applications.

Chapter four gives a short description of the criteria of comparison which are explained in detail by considering a controller designed for a bottle filling system by the method of direct implementation along with the use of formal methods.

Chapter five discusses all the case studies used in this thesis and also compares and tabulates both PN and LLD structure of controllers developed for these applications.

Chapter six discusses the results derived from the experiments carried out during the thesis and finally chapter seven concludes the thesis and lays down the future work that could be done using formal methods in field of sequencer designs.

Dept of Electrical Engineering, IIT Roorkee

# CHAPTER 2 PETRI NETS

# **2.1:Introduction**

Petri Net is an abstract, formal model of information flow. The properties, concepts and techniques of Petri nets have been developed with an aim to obtain a natural, simple and powerful tool for analysis and study of flow of information and control in systems with asynchronous and concurrent activities. [3] [18]

Petri Nets are widely used as a graphical and mathematical modeling tool for studying and describing information systems. As a graphical tool it is very similar in form to flowcharts and block diagrams. Unlike flowcharts and block diagrams PN possess the concept of tokens which are used to simulate the dynamic and concurrent behavior of a system. As a mathematical tool it is used to derive state equations, algebraic equations and other mathematical properties governing the behavior of systems.

The main advantage of PN as modeling tool is that it is popular with both theoreticians and practitioners. The practitioners can learn from theoreticians how to make a model more methodical in turn teaching the latter to make their model more realistic.

# **2.2:Brief History of Petri Nets**

The theory of Petri Nets has developed from the work of Carl Adam Petri, A. W. Holt, Jack Dennis, and many others. Petri Nets originated in the early work of Petri, in Germany, who in his thesis, developed a new model of information flow in systems. This model was based on the concepts of asynchronous and concurrent operation by the parts of a system and the realization that relationships between the parts could be represented by a graph, or Net. [3] The ideas communicated by Petri in his thesis drew attention from a group of researchers at Applied Data Research, Inc. working on the Information Systems Theory Project. This group led by Anatol Holt, developed the theory of systemic which was concerned with the representation and analysis of systems and their behavior. It was their work that led to the

Dept of Electrical Engineering, IIT Roorkee

development of early theory, notation, and representation of Petri Nets, and showed how Petri Nets could be applied to the modeling and analysis of systems of concurrent processes. Applied Data Research's associations with Project MAC at MIT, and particularly the Computation Structures Group under the direction of Jack Dennis, introduced the concepts of Petri Nets to this latter group. The Computation Structures Group has been a most productive source of research and literature in this field, publishing several PhD theses and numerous reports and memos on Petri Nets. Two pertinent conferences have been held by the Computation Structures Group: the Project MAC Conference on Concurrent Systems and Parallel Computation at Woods Hole in 1970, and the Conference on Petri Nets and Related Methods at MIT in 1975.[21]

Unlike the work of Petri, Holt, and many European researchers, who emphasized more on the fundamental concepts of systems, the work at MIT and many other American research centers concentrates on those mathematical aspects of Petri Nets that are more closely related to automata theory. This approach is motivated by a desire to analyze systems by modeling them as Petri Nets, and then manipulating the Petri Nets to derive Properties of the modelled systems. [22]

A large amount of research has been done on both the nature and the application of Petri Nets, and their use seems to be expanding. The simplicity and power of Petri nets make them excellent tools for working with asynchronous concurrent systems. [3]

# **2.3:Overview of Petri Nets**

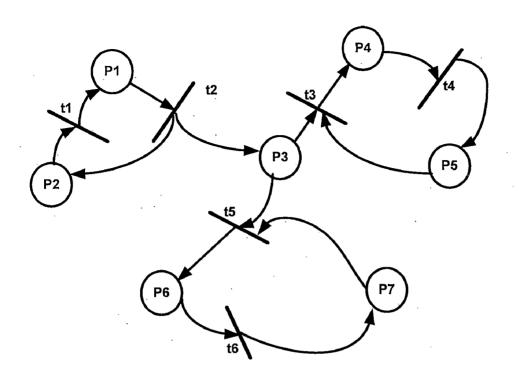

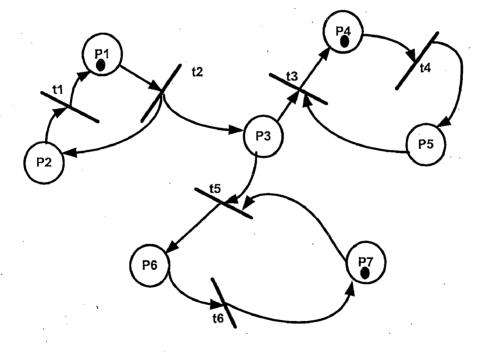

In this section, our primary aim is to study and understand the static and dynamic properties of systems modeled by means of Petri Nets by means of a simple example as shown in Fig 2.1. The Petri Net models the static properties of a system just like a flowchart represents the static properties of a computer program. The graph contains two types of nodes: circles (called *places*) and bars (called *transitions*). These nodes, places and transitions are connected by directed arcs from places to transitions and from transitions to places. If an arc is directed from node i to node j (either from a place to a transition or a transition to a place), then i is an *input to j* and j is an *output* of i. For example in the fig 2.1, place Pl is an input to transition t2 while places P2 and P3 are outputs of transition t2.

#### Fig 2.1 A Simple Graph Representation of a PN Structure

In addition to the static properties, a Petri Net also has dynamic properties that result from its execution. The execution of a Petri Net is controlled by the position and movement of **tokens** represented by a black dot that reside in circles representing places of the net. A Petri Net with marking is called a *marked Petri Net*.

One of the various marked Petri Net structures possible for the fig 2.1 example is as shown in fig 2.2. The position of tokens at various places in Petri Net graph is governed by a set of rules. They are

1) A transition t is said to be enabled if each input place t is marked with atleast w (p, t) tokens, where w (p, t) is the weight of the arc from p to t.

2) An enabled transition may or may not fire (depending on whether or not the event actually takes place).

3) A firing of an enabled transition t removes w(p, t) tokens from each input place p of t, and adds w(t, p) tokens to each output place p of t, where w(t, p) is the weight of the arc from t to p. [4]

#### Fig 2.2 Marked Graph Representation of PN structure in fig 2.1

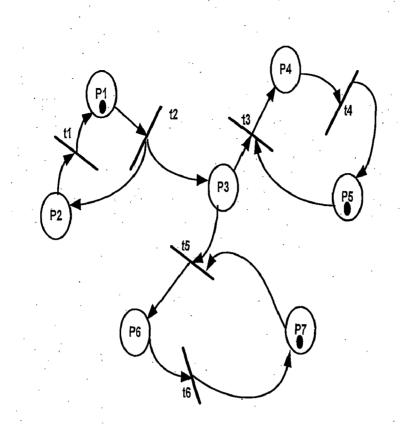

In short tokens are moved by firing of transitions of net, which are enabled when all the input places to transition have token in them. The transition fires by removing enabling tokens from their input places and by generating new tokens which are deposited in output places. In the marked graph example in fig 2.2 transition t2 is enabled since it has got a token in its input place t1, while t5 is not enabled since one of its input places p3 doesn't possess any tokens.

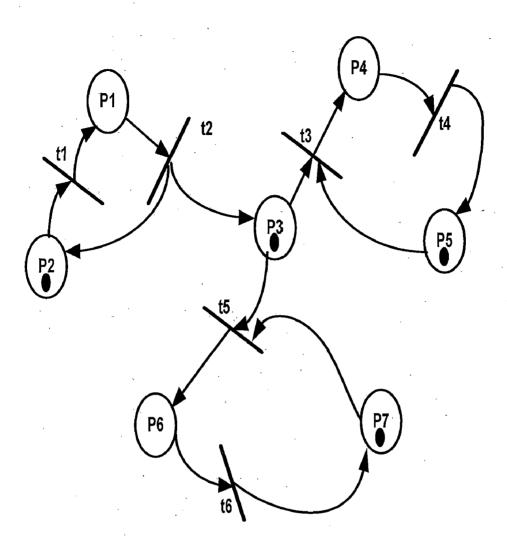

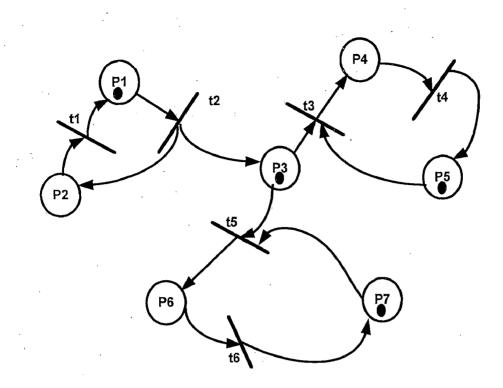

The Petri Net structure that results from firing of enabled transition t2 in fig 2.2 is as shown in fig 2.3. In fig 2.3 t2 fires thereby removing token from its input place P1 and depositing tokens one each at its output place P2 and P3. The distribution of tokens in a marked Petri Net signifies the state of net and is called its marking. In fig 2.3 three transitions t1, t3 and t5 are enabled due to firing of t2, the marked net structure that results due to firing of them single handedly is as shown in fig 2.4, fig 2.5 and fig 2.6 respectively.

Fig 2.3 A Petri Net Graph after firing t2

Now this process of obtaining new marked net structure will continue as long as any enabled transition will be present.

The whole discussion about static and dynamic properties of systems modeled by using Petri Nets was to give an introduction to concepts and working of Petri Nets. With this knowledge gained from our discussion, we are now in a position to study the structure of Petri Net.

Fig 2.4 A Petri Net Graph after firing t1

Fig 2.5 A Petri Net Graph after firing t3

Fig 2.6 A Petri Net Graph after firing t5

### **2.4:Strucutre of Petri Nets**

The use of Petri Nets for the modeling of concurrent systems requires a good amount of knowledge and understanding about its properties. They are composed of two basic elements: a set of places P and a set of transitions T. To make the relationship more appropriate it is required to define a relationship between places and transitions. This can be done by using two functions connecting transitions to places, the input function I defines for each transition tj, the set of input places for the transition I (tj). The output function O defines for each transition tj, the set of output places O (tj).

Thus, these four structures model the primitive form a Petri Net. Formally a Petri Net C is defined as the four – tuple C = (P, T, I, O).

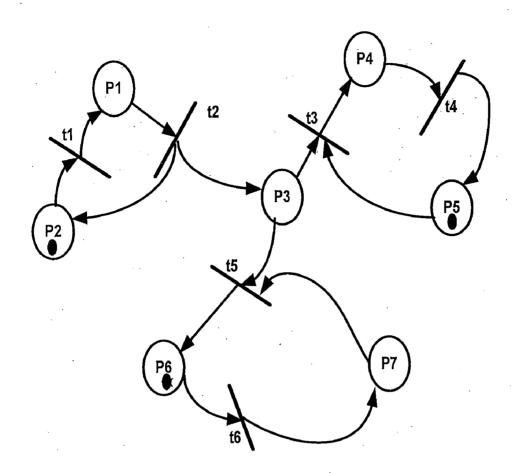

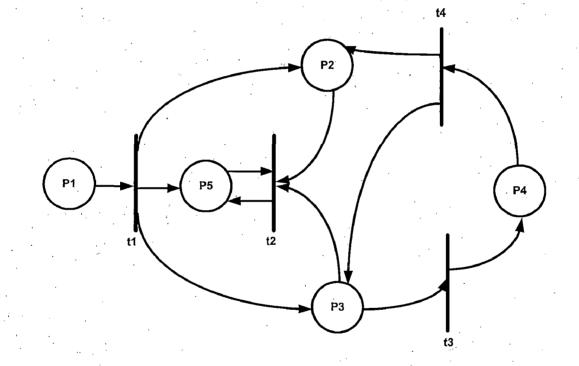

Consider the following example as shown in fig 2.7 Petri Net structure, defined as a four-tuple structure.

Each component of the structure is given:

$$\mathbf{C} = (\mathbf{P}, \mathbf{T}, \mathbf{I}, \mathbf{O})$$

$P = \{P1, P2, P3, P4, P5\}$

$T = \{t1, t2, t3, t4\}$

$I (t1) = \{P1\} O (t1) = \{P2, P3, Ps\}$   $I (t2) = \{P2, P3, P5\} O (t2) = \{P5\}$   $I (t3) = \{P3\} O (t3) = \{P4\}$  $I (t4) = \{P4\} O (t4) = \{P2, P3\}$

#### Fig 2.7 The Simple PN Graph

The similarity between Petri Net Graphs and Petri Net structures makes one to consider them as not different representations but as the same concept.[3] Hence, the term Petri Net is used to describe both PN Graphs and PN Structures.

#### 2.4.1: Markings and Execution Rule of Petri Net

A marking  $\mu$  of a Petri net is an assignment of tokens to places of that net. Tokens reside in the places of the net and the number and position of tokens in a net may change during its

execution. The vector  $\mu = (\mu 1, \mu 2, \mu 3, \mu 4, \dots, \mu n)$  depicts for each place in the Petri Net, the number of tokens in that place. The number of tokens in place Pi is  $\mu i = 1 \dots n$  also a marking function  $\mu$ : P  $\rightarrow$  N from the set of places to the natural numbers, N = {0, 1, 2 ...} can be defined. This makes it appropriate to use the notation  $\mu$  (Pi) to specify the number of tokens in place Pi. For a marking  $\mu$ ,  $\mu$  (Pi) =  $\mu i$ . The marked Petri Net structure of figure 2.7 is shown in figure 2.8 with initial marking  $\mu$  (p1) = (1, 0, 1, 0, 2).

Fig 2.8 Marked PN Graph of fig 2.7 with initial marking  $\mu$  (p1) = (1, 0, 1, 0, 2)

A Petri net C = (P, T, I, O) with a marking  $\mu$  becomes the Marked Petri Net  $M = (P, T, I, O, \mu)$ . Since the number of tokens in a place is unbounded over the set of all markings, there are an infinite number of markings possible for a Petri Net. [3]

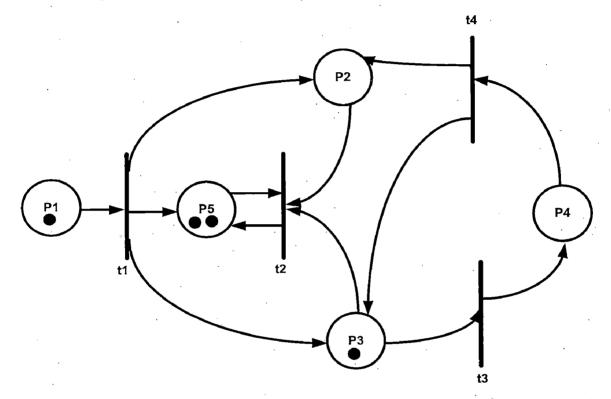

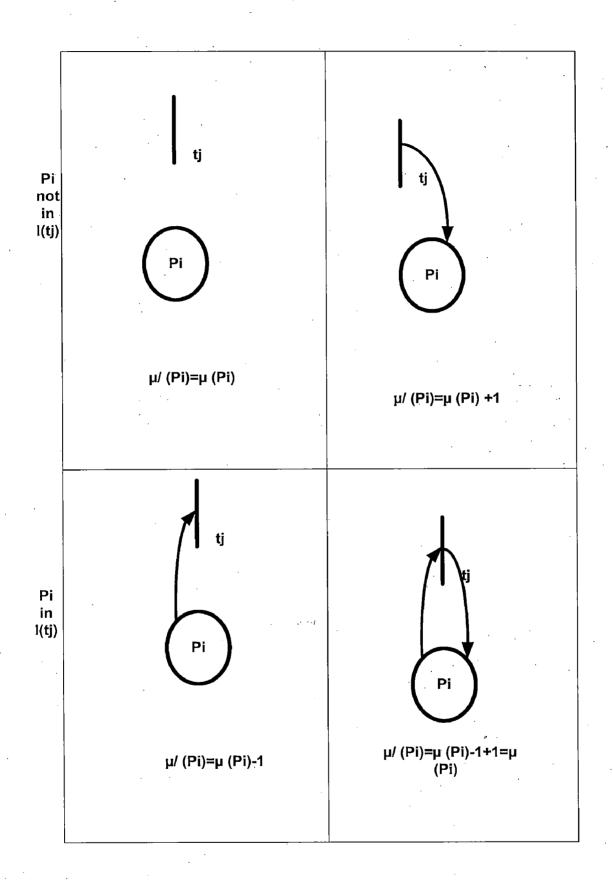

Firing of any transition will change the initial marking of Petri Net  $\mu$  to  $\mu'$ . It is observed that since only enabled transitions fire so the number of transitions at a place will always be non-negative even after a token is removed from it due to firing. Firing a transition can never take token from a place where there is no token in short if input places to a transition don't have any tokens the transition will never fire. The four basic rules involved in execution of transition are shown in fig 2.9.

### 2.4.2: The Reachability Set of a Petri Net

From a marking  $\mu$ , it is possible to fir a set of transition. The result of firing a transition in a marking  $\mu$  is a new marking  $\mu$ '. So, it could be said that  $\mu$ ' is immediately reachable from  $\mu$  if it is possible to fire some enabled transition in the marking  $\mu$  resulting in the marking  $\mu$ '. A marking  $\mu$ ' is reachable from  $\mu$  if it is immediately reachable from  $\mu$  or is reachable from any marking which is immediately reachable from  $\mu$ . Thus the Reachability set R (M) for a marked Petri net M = (P, T, I, O,  $\mu$ ) is defined as the set of all markings which can be reached from  $\mu$ , so Reachability set of a marked Petri Net is the set of all states into which the Petri Net can enter by any possible execution.

### **2.5:Behavioral Properites of Petri Nets**

A major strength of Petri Nets is their support for analysis of many properties and problems associated with concurrent systems. Those properties of concurrent systems modeled by Petri Nets which are marking dependent are called behavioral properties. Some of them are discussed in the following sections:

**2.5.1:** Reachability: Reachability is a fundamental property of a system that models its dynamic behaviour. With reference to our present discussion reachability in Petri Net is stated as follows a marking  $\mu'$  is reachable from a marking  $\mu_0$  if there is a series of fireable transitions from  $\mu_0$  to  $\mu'$ . The set of all possible markings reachable from a set  $\mu_0$  in net (N,  $\mu_0$ ) is denoted by R (N,  $\mu_0$ ).

**2.5.2: Boundedness :** A Petri Net is considered to be bounded or to be precise Kbounded if the number of tokens in each place does not exceed a finite number K for every marking reachable from  $\mu_0$ , i.e.  $\mu(\mathbf{P}) \leq \mathbf{K}$  for every place P and every marking  $\mu \sum \mathbf{R}(\mu_0)$ . A Petri Net is said to be safe if it is 1-bounded.

**2.5.3:** Liveness: The concept of liveness could be related to absence of deadlock in operating system. A Petri Net is said to be live if it is possible to fire any transition of net from any new marking obtained from  $\mu_0$  by progressing through some further firing sequence.

#### Fig 2.9 Basic Firing Rules

Dept of Electrical Engineering, IIT Roorkee

2.5.4: Reversibility and Home State: A Petri Net is reversible if one could reach initial marking  $\mu_0$  from a new marking  $\mu'$ . In many physical applications once a system changes state hardly the system gets back to its initial state. In such systems a new state called a Home state is defined which is nothing but a marking  $\mu'$  which is reachable from every making  $\mu$  of **R** ( $\mu_0$ ). [20]

**2.5.5: Persistence:** A Petri Net is said to be persistent if for any two enabled transitions the firing of one will not disable the other. A transition in a persistent net once enabled will stay enabled until it fires.

## 2.6: Analysis of a PN model based on Reachability Criteria

The Reachability criteria states that given a marked Petri Net with a marking  $\mu$  and  $\mu'$ , is  $\mu'$  reachable from  $\mu$ . It is a very important problem to the analysis of Petri nets, where it is to be determined whether a set of all markings  $S = {\mu 1, \mu 2, \mu 3..... \mu k}$  is a subset of Reachability set R ( $\mu$ ) of a marked Petri Net.

One of the approaches to analyze a Petri Net is to find the finite representation for the Reachability set of Petri Net as many properties of Petri Net could be studied from the properties of its Reachability set. The representation commonly known as the Reachability tree consists of a tree whose nodes represent markings of the net and the arcs represent the possible changes in the state resulting from firing of transitions.

The Reachability set of a marked Petri Net is often infinite, to make it finite many markings are mapped into the same node of the tree. This many to one mapping is accomplished by collapsing a set of nodes by ignoring the number of tokens in a place of net. This is represented by a special symbol  $\omega$  for the number of tokens in this place.  $\omega$  is said to represent an arbitrary large value.[3] As a result the operation of addition, subtraction and comparison is shown below:

$$\omega + \mathbf{n} = \omega$$

$\omega - n = \omega$

n < 00

For any natural number n

Each node in Reachability tree is marked with a marking and arcs are labeled with transitions. The initial node is labeled with an initial marking. For any given node x additional nodes are added to the tree for all markings that are reachable from marking of node x. For each transition tj which is enabled in the marking of node x, a new node with marking  $\delta(x, tj)$  is created and an arc labeled tj is directed from node x to this new node.[3] This process repeats itself until the whole state-space has been created. A marking from the root node to a node corresponds to a execution sequence. Two steps are taken to make it certain the state space if infinite models into finite Reachability tree.

First, if a new marking is obtained which is equal to an existing marking on the path from the root node to the new marking, the new (duplicate) marking becomes a terminal node. Since the new marking is equal to the previous marking, all markings reachable from it have already been added to the Reachability tree by the earlier identical marking. [3]

Second, if any new marking x is obtained which is greater than a marking y on the path from the root node to the marking x, then the components of marking x which are strictly greater than the corresponding components of marking y are replaced by the symbol  $\omega$ . Since marking x is greater than marking y, any sequence of transition firings which is possible from marking y is also possible from marking x. In particular, the sequence that transformed marking y into marking x can be repeated as many number of times its possible thereby increasing the number of tokens in those places which have a  $\omega$ . Thus the number of tokens in these places could have large values. [3]

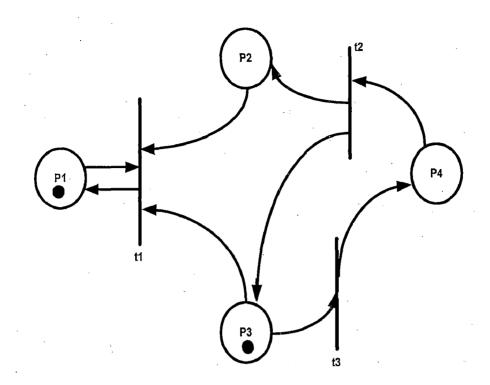

The Reachability tree of Petri Net structure of fig 2.10 is as shown in fig 2.11. After discussing the basics of Reachability tree, one needs to answer the important question how will it be used to understand properties of nets? As per to safeness and boundedness it has already been stated that if a Petri Net is K (note K=1 for safeness) bounded then no more than K tokens can reside in any place. Now if the Reachability tree of a Petri Net contains  $\omega$  then it violates both the condition of both boundedness and safeness. [3]

Fig 2.10 A Petri Net with initial marking (1, 0, 1, 0) and infinite reachable state space

### Fig 2.11 The Reachability Tree of Petri Net of Fig 2.10

# 2.7:Petri Nets and Industrial Automation

The ladder logic diagrams (LLD) have been widely used in manufacturing systems to design sequence controllers and is generally implemented on a PLC.

The I/O procedures of the PLC are specified by ladder logic diagrams (LLD) which makes industrial machines run repetitive operations easily. For most simple systems it is easy to program the PLC by heuristic methods, but modern manufacturing systems are more complex as a result the design of corresponding sequencers by LLD alone is increasingly difficult. Further, the usage of LLD is limited to control of the system rather than in analysis and evaluation of qualitative and performance characteristics.

Both finite state machines (FSM) and Petri nets (PN) effectively model sequential system but when it comes to complexity FSMs fail to model systems with increasing complexity since, they require the knowledge of all the states (global states) of the system. PN uses the local states while modeling a system and hence knowledge of all system states is not a prerequisite. The need for only the knowledge of local states while designing a PN based strategy makes them easily expandable i.e. addition of new components to the system only affects a PN's model locally, unlike in FSM's where it might affect every state in the model. Infact, it is possible to model a FSM using PN.

Petri Nets are capable of modeling sequential, asynchronous and concurrent events that drive an industrial process. Using PN's strategies are developed that are able to capture the discrete event dynamics of the process. The control strategies so developed are easier to understand, troubleshoot and modify and gives better evaluation of system performance.

The use of Petri Nets for modeling and analysis has received great importance because of several reasons

1) Graphical form of PN is easy to understand and has direct correspondence to discrete event control characteristics of industrial control systems especially in the field of manufacturing.

2) Petri Nets have a sound mathematical foundation and hence are amenable to the analysis for logical consistency, such as boundedness, liveness and Reachability.

3) The definition of PN makes quantitative performance evaluation possible.

NDUSTTRIAL SEQUENCERS FOR PROCESS CONTROL APPLICATIONS USING PETRI NETS AND LADDER LOGIC DIAGRAMS

4) PN can be employed to do modular designs because it exhibits natural decomposition properties.

5) PN makes it possible to translate itself into control code ready to be implemented on plant floor for desired execution.

One of the strategies for design of Industrial Sequencers could be to model the system using PN and then to analyze the model for its validity in terms of liveness, boundedness and reversibility and finally to implement the net structure by transforming it into equivalent LLD code for the sequencer.

## 2.8: The Real Time Petri Net Algorithm(RTPN)

A Real-Time Petri Net (RTPN) based controllers can be obtained by assigning physical (I/O) input/output functions to places and physical (I/O) and timing variables to transitions of the PN model.

A RTPN is eight tuple and is defined as

RTPN: (P, T, I, O, m, D, Y, Z) where

(P, T, I, O, m) are the properties of the untimed Petri Net model.

**D** is a firing time delay function, consisting of non-negative real numbers.

¥ Y is defined as the set of physical input signal functions mapped to transitions.

Z is defined as the set of physical output signal functions mapped to places. [14]

1) Timing vector D assigns time delays to transitions. Timing vector D models the delays and synchronization of activities in the system.

2) Vector Y is used as an enable signal and determines when a transition is fired. Vector Y can be mapped to a single input address or can be Boolean expression of input addresses. When the function associated with Y (i) is true and all input places are marked, then the firing rule is executed i.e. tokens are removed form input places and deposited to output places. Vector Y is the firing attribute of all transitions in RTPN.

3) Vector Z write commands to the digital output interfaces. When a place  $P_i$  is marked by a token, then some output function occurs.

RTPN Algorithm has been used for obtaining Petri Net based sequence Controllers for all the process control applications discussed in this dissertation. The places of such sequence

controllers are assigned with actuator outputs; they remain valid as long as the places are active. The inputs are mapped to the transitions and they act as second condition for firing of transitions, i.e. if an input place to a transition is marked along with it being activated by its I/P sensors it fires.

The delay function is used along with transition as a third condition to delay firing of a transition if it is required in application.

## 2.9: Conclusion

In this chapter the basics of Petri Nets have been discussed along with the importance of Petri Nets in the field of Industrial Automation. Finally, a RTPN algorithm is given which have been extensively used for design of PN based sequence controllers for all the applications considered in this dissertation study. The popularity of Petri Nets for modeling system could be attributed to following factors

1) The same system model designed using PN could be used for analysis and performance evaluation of the system

2) Petri Nets are super class of state machines and unlike state machine could model system with concurrency, conflict and synchronization thereby making them as an obvious tool for modeling manufacturing systems.

3) Petri Nets as a graphical tool acts as a powerful medium between engineer and customer and its strong mathematical background enables it to do formal checking on behavior of modeled system.

Next chapter introduces the basics of Programmable Logic Controllers along with the discussion of standardized languages used for PLC programming.

#### NDUSTTRIAL SEQUENCERS FOR PROCESS CONTROL APPLICATIONS USING PETRI NETS AND LADDER LOGIC DIAGRAMS

.....

Dept of Electrical Engineering, IIT Roorkee

26

### CHAPTER 3

# **PROGRAMMABLELOGIC CONTROLLERS**

## 3.1:Introduction

The PLC's can be classified as a solid state member of computer family. A PLC is an industrial computer in which control devices such as limit switches, push buttons, proximity or photoelectronic sensors, float switches or pressure switches, to name a few, provide incoming control signals into the unit. [9] [24]

Incoming control signals termed as inputs interacts with instructions specified in user ladder program, which tells the PLC how to react to incoming signals. The user program also directs the PLC on how to control field devices like motor starters, pilot lights and solenoids. A signal going out of PLC to control a field device is called an output. [8]

A formal definition of PLC comes from the National Electrical Manufacturers Association (NEMA):

"A Programmable controller is a digitally operated electronic system, designed for use in an a industrial environment and uses a programmable memory for the internal storage of user oriented instructions for implementing specific functions such as logic, sequencing, timing, counting and arithmetic to control through digital or analog inputs and outputs, various types of machines or processes. Both the PLC and its associated peripherals are designed so that they can be easily integrated into an industrial control system and easily used in all their intended applications." [5]

## **3.2:Evolution of PLC**

The PLC was originally designed and developed by group of engineers of General Motors Corporation in 1968 to eliminate costly scrapping of assembly line relays during model changeover of cars. These PLC's had to be easily designed, programmed and reprogrammed, preferably in a plant, easily maintained and repaired, smaller than its relay equivalent and cost competitive with the solid state and relay panels then in use. This provoked great

interest from engineers of all disciplines using PLC for the industrial control. A microprocessor based PLC was introduced in 1977 by Allen-Bradley Corporation in USA, using INTEL 8080 microprocessor with circuitry to handle bit logic instructions at higher speeds. The early PLC's were designed using only for logic based sequencing operations (on/off signals).

Present day sees quite a lot of different brands in market differing in memory size and I/O capacity. The smaller ones serve as relay replacers with added timer and counter capability. The modern medium sized PLCs perform all the relay replacement functions expected of it but also add many other functions such as counting, timing and complex mathematical applications. In addition, new age medium and large size PLCs have been provided with data highway capabilities which enable them to function in liaison with Distributed Control System. [8]

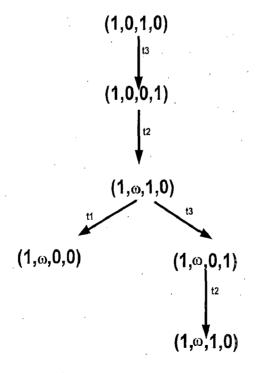

### **3.3:PLC** Architecture

A Programmable Logic Controller (PLC) manufactured by any company has several common functional units. The basic PLC architecture is as shown in fig 3.1.

The PLC architecture of fig 3.1 consists of

a) Power supply

**b**) Input/output (I/O) system

c) Real-time central processing unit

d) Memory unit

e) Programmer unit

#### a) **Power Supply**

The power supply unit provides the isolation unit necessary to protect solid-state components from most high voltage line spikes. The power supply unit converts power line voltages to those required by the solid state components. In addition, the power supply is rated for heat dissipation requirements for plant floor operation. This dissipation capability allows PLC's to have high ambient temperature specifications and represent an important difference between programmable logic controllers and personnel computer for industrial applications.

The power supply unit drives the I/O logic signals, the central processing unit, the memory unit and some peripheral devices.

Fig 3.1 Architecture of a Programmable Logic Controller

### b) Input/Output (I/O) System

Inputs are defined as real-world signals giving the controller real time status of process variables. These signals can be analog or digital, low or high frequency, maintained or momentary. Typically they are presented to PLC system as a varying voltage, current or resistance value. Signals from Thermocouples and RTD's are common examples of analog signals. Some flow meters and strain gauges provide variable frequency signals, while pushbutton, limit switches or even electromechanical relay contacts are examples of digital, contact closure type signals. Register input is another type of input signal that reflects the computer nature of PLC. The register input is only useful when the process condition is

NDUSTTRIAL SEQUENCERS FOR PROCESS CONTROL APPLICATIONS USING PETRI NETS AND LADDER LOGIC DIAGRAMS

represented by a collection of digital signals delivered to the PLC at the same time. There are three common categories of outputs: discrete, register and analog. The discrete outputs can be pilot lights, solenoid valves or annunciator windows. Register outputs can drive panel meters or displays. Analog outputs can drive signals to variable speed drives or to I/P (current to air) and thus to control valves.

### c) Real-time Central Processing Unit

The Central processing unit (CPU) also called central control unit (CCU) performs the task necessary to fulfill the PLC function such scanning I/O bus traffic control program execution, peripheral and external device communications, special functions or data handling execution(enhancements), and self diagnostics.

### d) Memory Unit

The memory unit of PLC serves several functions. It is the library, where the application program is stored. It is also where the PLC's executive program is stored. An executive table functions as the operating system of PLC. It is the program that interprets, manages and executes the user's application program. Finally, the memory module is the part of the programmable controller, where the process data from the input modules and control data from output modules are temporarily stored as data tables. Typically, an image of these data tables is used by the CPU and when appropriate is sent to output modules.

### e) **Programmer units**

The programmer unit provides an interface between the PLC and the user during program development, start-up and troubleshooting. The instructions to be performed during each scan are coded and inserted into memory with the programmer unit. The programmer unit may vary from small hand held units to desktop stand-alone intelligent CRT screens. Programming units are the liaison between what the PLC understands and what the engineer desires to occur during the control sequence.

INDUSTITIAL SEQUENCERS FOR PROCESS CONTROL APPLICATIONS USING PETRI NETS AND LADDER LOGIC DIAGRAMS

# **3.4:Benefits of PLC**

#### Table 3.1: Advantages of PLC Programming

| Features                 | Benefits                       |

|--------------------------|--------------------------------|

| Solid state components   | High reliability               |

| Programmable memory      | 1) Flexible control            |

|                          | 2) Simplifies changes          |

| Microprocessor based     | 1) Communication capability    |

|                          | 2) Multi-functional capability |

|                          | 3) High quality products       |

|                          | 4) High level performance      |

| Small size               | Minimum space required         |

| Software timers/counters | 1) Eliminate hardware          |

|                          | 2) Easily changed presets      |

| Software control relays  | 1) Reduced cost                |

|                          | 2) Reduced space requirements  |

| Modular I/O interface    | 1) Easily maintained           |

|                          | 2) Easily connected            |

|                          |                                |

|                          |                                |

## **3.5: PROGRAMMING LANGUAGES**

As programmable controller manufacturers increased, so did the number of programming languages. The most disturbing fact was each manufacturer had its own language and protocol for using its PLC hardware; some were easier than other which left industry users with no choice of selecting a common platform.

IEC 1131-3 programming languages was introduced to take care of this menace and it addressed the problem successfully by establishing four interlinking languages to work together under the supervision of the fifth one. In addition it made the languages portable so that they could be used by any programmer, technician or PLC operator. The language for PLC Programming consists of two textual and two graphical versions. [6]

IDUSTIFIAL SEQUENCERS FOR PROCESS CONTROL APPLICATIONS USING PETRI NETS AND LADDER LOGIC DIAGRAMS

They are

### GRAPHICAL

Ladder Diagram (LD)

Functional Block Diagram (FBD)

### **TEXTUAL**

Instruction List (IL)

Structured Text (ST)

The choice of programming language is dependent on:

• ... The programmers' background.

• ... The problem at hand.

• ... The level of describing the problem.

• The interface to other people/departments. [10]

### **3.5.1 : GRAPHICLA LANGUAGES**

They are employed as one of the most recognizable language type when one is programming PLC's. As engineers make the first hand drawn sketch of their plans, they actually provide the rough draft of what will finally be a detailed control scheme.

**3.5.1.1 : LADDER DIAGRAM (LD):** Ladder Diagram has its roots in the USA. It is based on the graphical presentation of Relay Ladder Logic. They are the probably the first thing to come to mind in a discussion of a PLC. Much credit goes to the electrical and electronics engineers for building a standardized set of symbols to represent the electrical sequence of an applications operation. The working of a ladder diagram is explained in fig 3.2.All equipments and devices used in the process or machine have an on/off state. Therefore, a ladder diagram can activate any of these devices based upon the state, or condition of another. All this is done in some predetermined sequence, from top-down, left-to-right running of the ladder diagram. This process continues till the end and then repeats itself, constantly checking the status of each contact as it scans the diagram. In fig 3.2 if A is on and B is off then LED is on, where A and B are Relays and LED ON represents the output coil.

**3.5.1.2 : FUNCTIONAL BLOCK DIAGRAM (FBD):** Function Block Diagram is very common to the process industry. It expresses the behavior of functions, function blocks and programs as a set of interconnected graphical blocks, like in electronic circuit diagrams. It looks at a system in terms of the flow of signals between processing elements. Program elements appear as blocks on the screen and are then wired together. The shell of the block receives inputs and sends output information all the while processing the I/O as necessary. In this way, the program elements can execute their respective algorithms and operations in the manner the wires dictate. The fig 3.3 shows the Functional Block Diagram of a PID Controller for Motor Control.

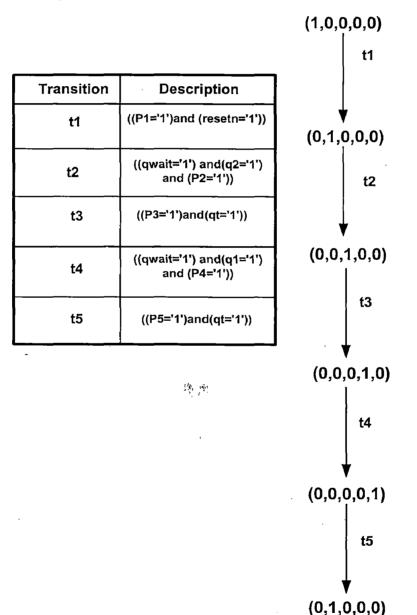

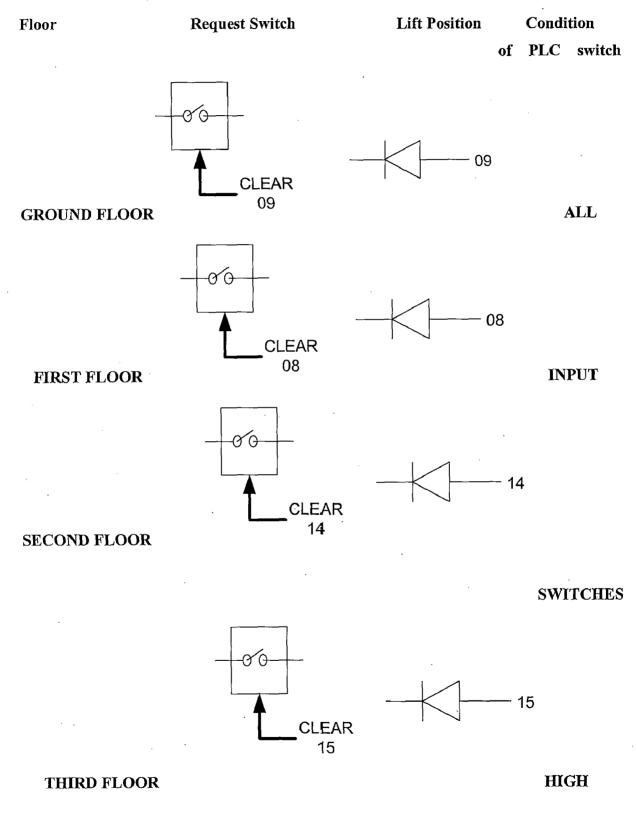

#### **3.5.2: TEXTUAL LANGUAGES**