# IMPLEMENTATION OF FILTERED BACKPROJECTION ALGORITHM ON FPGA

## A DISSERTATION

# Submitted in partial fulfillment of the requirements for the award of the degree of

# MASTER OF TECHNOLOGY

## ELECTRICAL ENGINEERING

(with Specialization in System Engineering and Operations Research)

By

## SHASHANK SHARAN RAI

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE -247 667 (INDIA) JUNE, 2007

# INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE

## **CANDIDATE'S DECLARATION**

I hereby declare that the work, which is being presented in this dissertation entitled IMPLEMENTATION OF FILTERED BACKPROJECTION ALGORITHM ON FPGA in the partial fulfilment of the requirements for the award of the degree of Master of Technology in Electrical Engineering with specialization in System Engineering and Operations Research, submitted in the Department of Electrical Engineering, Indian Institute of Technology Roorkee, Roorkee is an authentic record of my own work carried out during a period from May 2006 to June 2007 under the supervision of Dr. Indra Gupta, Associate Professor, Electrical Engineering Department, Indian Institute of Technology Roorkee, Roorkee.

The matter presented in this thesis has not been submitted by me for the award of any other degree of this or any other Institute.

(SHASHANK SHARAN RAI)

This is to certify that the above statement made by the candidate is correct to the best of my knowledge and belief.  $\rho$

Date: 28/6/07

Dr.<sup>A</sup>ndra Gupta Associate Professor Department of Electrical engineering Indian Institute of Technology Roorkee.

## ABSTRACT

Recently, Field Programmable Gate Array (FPGA) technology has become a promising and viable platform for the implementation of image and video processing algorithms. The special features available with today's FPGAs have allowed the digital technology to be used in many such applications. Image reconstruction is a problem that involves complex trigonometric calculations and is inherently serial in nature. A high-speed hardware implementation of Filtered backprojection algorithm can address the problem of real-time image reconstruction for various practical applications.

Today most of the applications where image reconstruction is required are demanding for a real-time image processing facility. However, an inherent serial nature of the process makes it infeasible with a software implementation. Though the software implementation of an image-processing algorithm may be comparatively easy from the development point of view, an upper limit on the speed of the execution is imposed by the slow speed is imposed by the slow speed interfaces. In that case, even a very fast CPU is not able to deliver the desired performance. For such cases, a dedicated hardware implementation generally gives a better result.

As images grow larger in size and depth, the software implementation of image processing algorithms becomes less useful. For a real-time system, a hardware implementation may provide a more useful solution. In the current work, a Xilinx Virtex II-Pro video board is being used to implement the algorithm. A novel approach is proposed for the implementation of Filtered backprojection algorithm, which combines filtering and backprojection processes on a single chip. Few advanced features of Xilinx Virtex device are used to design architecture for Filtered backprojection algorithm that is able to perform filtering and backprojection operations in parallel. A one dimensional FIR filter has been implemented for filtering the individual projections. Then a custom digital circuitry is implementing the backprojection part of the algorithm. The final goal of the work is to demonstrate the reconstructed images from their respective Radon transforms.

## ACKNOWLEDGEMENTS

It is my proud privilege to express my deep sense of gratitude and indebtedness towards my thesis supervisor Dr. Indra Gupta, Associate Professor, Department of Electrical Engineering, for her invaluable guidance & criticism, and kind and continuous encouragement, which were the vital factors in successful completion of the present work. I am heartily thanking her for her deep concern towards my academics and personal welfare.

Her painstaking support and involvement in preparation of manuscript, theoretical analysis, simulation, and hardware result studies are gratefully acknowledged. I humbly acknowledge a lifetime's gratitude to her and hope for a continued interaction even in the future.

I express my deep sense of gratitude to the Prof. S. P. Gupta, Head, Electrical Engineering Department, Indian Institute of Technology, Roorkee, for providing excellent facilities and nice working atmosphere in the department for the research work.

I am thankful to Prof. M. K. Vasantha in so many ways. His constant encouragement and willingness to listen to and help with my academic queries or personal problems are some of the things I benefited with. I found him a complete teacher, who taught me that it is equally important to be a good human being as much as to be a good technocrat. The education given by him will help me all my life.

My sincere thanks are also due to Dr. H. O. Gupta, Dr. Surendra Kumar, Dr. Rajendra Prasad, and Dr. G. N. Pillai for extending moral support and technical discussions as and when required during the work.

I thankfully appreciate and acknowledge my indebtedness to research scholars Dr. Vishal Kumar, Dr. Vijayender Singh, Mr. Rohit Bhakar, Mrs. Nidhi Singh, Mrs. Nidhi Kulkarni and Mr. S. K. Tomar for their help, cooperation, and moral support from time to time. My special thanks goes to the fellow classmates Mr. Rohith Kumar H. C., Mr. Soumyojoti Maitra, Ms. Sowmya Kollipara, Mr. Patel Vinod Kumar, Mr. Siluveru Karunakar, Mr. Srikanth Reddy, Mr. Anil Kumar, Mr. Kalyan Ayyagiri, Mr. M. Chandrashekar, Mr. Praveen Rangisetti for their cooperation and moral support during my stay.

ii

Besides the enjoyment of doing research work, this time has also given me an opportunity to make great friends. I shall never be able to forget the time, which I spent with Mr. V.S.Sriram and Mr. Sheri Sundeep and this writing space is not enough to write about the memories I have in my mind.

I am thankful to the technical staff of the SEOR Lab Shri Kalyan Singh, Shri C.M. Joshi, and other staff members for their timely cooperation and needful help.

Thanks are also due to all those who helped me directly and indirectly for the completion of the work.

My heartiest gratitude goes to my parents, brothers and other members of family, for constantly supporting, which allowed me to concentrate on my work.

I would like to dedicate this research work to my family.

(Shashank Sharan Rai)

## CONTENTS

|         |                                                       | P                                                  | age No. |  |

|---------|-------------------------------------------------------|----------------------------------------------------|---------|--|

| ABSTRA  | АСТ                                                   |                                                    | i       |  |

| ACKNO   | WLEDGE                                                | MENTS                                              | ii      |  |

| CONTEN  | NTS                                                   |                                                    | iv      |  |

| LIST OF | FIGURE                                                | S                                                  | vi      |  |

| LIST OF | SYMBO                                                 | LS                                                 | viii -  |  |

| LIST OF |                                                       | /IATIONS                                           | ix      |  |

| Chapter | -1 INTRO                                              | DUCTION                                            | 1       |  |

| 1.1     | Genera                                                | l                                                  | 1       |  |

| 1.2     | Objectiv                                              | e of the Dissertation                              | 5       |  |

| 1.3     | Organiz                                               | ration of the Thesis                               | 6       |  |

| Chapter | -2 INTRO                                              | DUCTION TO COMPUTED TOMOGRAPHY                     | 7       |  |

| 2.1     | Introduc                                              | ction                                              | 7       |  |

| 2.2     | Calculation of Tomographic Images                     |                                                    |         |  |

| 2.3     | Projections                                           |                                                    |         |  |

| 2.4     | The Radon Transform                                   |                                                    |         |  |

| 2.5     | Discrete                                              | e Radon Transform                                  | 13      |  |

| 2.6     | Conclus                                               | sion                                               | 14      |  |

| Chapter | -3 IMAGE                                              | RECONSTRUCTION USING BACKPROJECTION                | 15      |  |

| 3.1     | Introduc                                              | stion                                              | 15      |  |

| 3.2     | The Fou                                               | urier Slice Theorem                                | 15      |  |

| 3.3     | Image F                                               | Reconstruction Techniques                          | 17      |  |

|         | 3.3.1                                                 | Brute Force Inversion Technique                    | 18      |  |

|         | 3.3.2                                                 | Iterative Reconstruction Technique                 | 18      |  |

|         | 3.3.3                                                 | Fourier Based Techniques                           | 19      |  |

|         | 3.3.4                                                 | Filtered Backprojection Technique                  | 20      |  |

| 3.4     | Conclus                                               | sion                                               | 22      |  |

| Chapter | -4 PROP                                               | OSED ALGORITHM FOR DIGITAL IMPLEMENTATION OF IMAGE | 23      |  |

|         | RECO                                                  | NSTRUCTION                                         | 20      |  |

| 4.1     | Introduc                                              | ction                                              | 23      |  |

| 4.2     | Propose                                               | ed algorithm for Radon transform implementation    | 24      |  |

| 4.3     | Proposed strategy for Radon transforms implementation |                                                    |         |  |

1 -

| 4.4    | Proposed algorithm for Filtered backprojection                         | 29   |

|--------|------------------------------------------------------------------------|------|

| 4.5    | Implementation strategy for proposed Filtered backprojection algorithm | 30   |

| 4.6    | Conclusion                                                             | 34   |

| hapter | -5 DESIGN AND IMPLEMENTATION USING FPGA                                | 35   |

| 5.1    | Introduction                                                           | 35   |

| 5.2    | VHDL                                                                   | 36   |

| 5.3    | VHDL Programming techniques                                            | 36   |

|        | 5.3.1 Behavioral Programming                                           | 35   |

|        | 5.3.2 Structural Programming                                           | 37   |

|        | 5.3.3 Dataflow Programming                                             | 37   |

|        | 5.3.4 Mixed Mode Programming                                           | 38   |

| 5.4    | Terminologies in VHDL                                                  | 38   |

|        | 5.4.1 Entity                                                           | 38   |

|        | 5.4.2 Packages                                                         | 39   |

|        | 5.4.3 Design Libraries                                                 | 39   |

|        | 5.4.4 Components                                                       | 39   |

|        | 5.4.5 Configurations                                                   | 39   |

| 5.5    | FPGA                                                                   | 40   |

| 5.6    | Xilinx Virtex-II Pro Platform FPGA                                     | 41   |

| 5.7    | Xilinx CORE Generator System                                           | 43   |

| 5.8    | Conclusion                                                             | 44   |

| hapter | -6 RESULTS AND CONCLUSION                                              | 45   |

| 6.1    | Results                                                                | 45   |

| 6.2    | Conclusion                                                             | 50   |

| hapter | -7 FUTURE SCOPE                                                        | 53   |

| EFERI  | ENCES                                                                  | 55   |

| PPENI  | DIX A                                                                  | . 57 |

| PPEN   | DIX B                                                                  | . 63 |

# LIST OF FIGURES

| Figure No.               | Figure Description                                                                                      | Page                  |

|--------------------------|---------------------------------------------------------------------------------------------------------|-----------------------|

| Figure 2.1               | A single X-ray beam passing through a segment of tissue                                                 | <b>no.</b><br>8       |

| Figure 2.2               | A 2-D matrix of attenuation coefficients representing a block tissues                                   | k of 8                |

| Figure 2.3               | Parallel Beam and Angular Scanning                                                                      |                       |

| Figure 2.4               | Parallel beam geometry and coordinate system                                                            | <b>9</b> <sup>1</sup> |

| Figure 2.5               | A Single beam from a parallel beam projection and                                                       | 10                    |

| Figure 3.1               | definition<br>A simple illustration of Fourier slice theorem                                            | its 11                |

| Figure 3.2               | A conceptual block diagram of a                                                                         | 16                    |

| Figure 3.3               | A conceptual block diagram of Fourier-based Reconstruction.<br>Backprojection of a point mass on origin | 19                    |

| Figure 4.1<br>Figure 4.2 | Address calculation for Radon space                                                                     | 20.                   |

|                          | Algorithm for implementation of Part                                                                    | 25                    |

| Figure                   | grain of Radon Transform                                                                                | 25                    |

| Figure 4 -               | a shieliation of book                                                                                   | 27                    |

| Figure                   | and grain of backprojection                                                                             | 30                    |

| Figur                    | an on meclure of Backprojection E                                                                       | 31                    |

| Bloc<br>Algo             | rithm<br>rithm                                                                                          | 32                    |

| Figure                   | Sound for a seven-to-                                                                                   | 33                    |

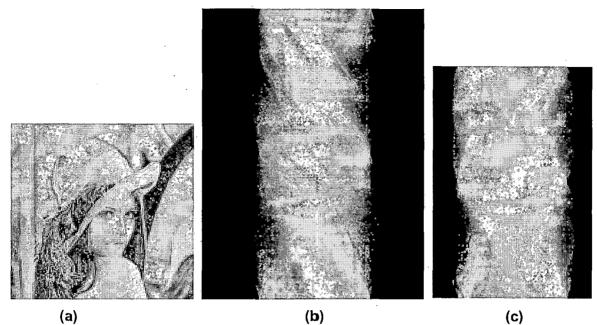

| (a) A<br>Rador           | standard test image of Lena (128x128 Bitmap), (b) The 4                                                 | 47                    |

| obtain                   | a transform of (a), (c) The Radon transform of (a)                                                      | 8                     |

ء. در

# LIST OF SYMBOLS

| p(x)                         | Projection function                                                                                    |  |  |  |  |

|------------------------------|--------------------------------------------------------------------------------------------------------|--|--|--|--|

| $\mu_i$                      | Attenuation coefficient of i <sup>th</sup> tissue along the X-ray beam                                 |  |  |  |  |

| Io                           | Intensity of projected radiation                                                                       |  |  |  |  |

| I                            | Intensity of received radiation                                                                        |  |  |  |  |

| S                            | One coordinate in radon space, represents the distance of the line of projection from origin           |  |  |  |  |

| θ                            | Second coordinate in radon space, represents the angle of projection                                   |  |  |  |  |

| x                            | Horizontal coordinate in image space                                                                   |  |  |  |  |

| У                            | Vertical coordinate in image space                                                                     |  |  |  |  |

| f(x,y)                       | Two-dimensional object function, f is the intensity of function at (x, y)                              |  |  |  |  |

| L                            | Set of parallel lines of projection                                                                    |  |  |  |  |

| . <b>r</b>                   | Distance along a line of projection                                                                    |  |  |  |  |

| p <sub>θ</sub> (s)           | Projection, one-dimensional array of projection functions along the set of lines L at an angle $	heta$ |  |  |  |  |

| p(s, θ)                      | The Radon transform                                                                                    |  |  |  |  |

| $\overline{p}$ (s, $	heta$ ) | Discrete Radon Transform                                                                               |  |  |  |  |

| ω                            | Natural frequency component in frequency domain                                                        |  |  |  |  |

| $S_{\theta}(\omega)$         | One-dimensional Fourier transform of $p_{\theta}(s)$                                                   |  |  |  |  |

| F(u,v)                       | Two-dimensional Fourier transform of f(x, y)                                                           |  |  |  |  |

| (u,v)                        | Fourier domain coordinates                                                                             |  |  |  |  |

| F(ω, θ)                      | A slice in Fourier domain corresponding to $S_{	heta}(\omega)$                                         |  |  |  |  |

| d                            | Dimension of the image                                                                                 |  |  |  |  |

| Ν                            | Number of projections                                                                                  |  |  |  |  |

| P                            | Pixel array                                                                                            |  |  |  |  |

| g                            | Multiplication coefficients in Iterative reconstruction                                                |  |  |  |  |

| bin                          | Rounded integer address in the Radon space                                                             |  |  |  |  |

| fract                        | Interpolation factor used to compensate the rounding during projection and backprojection              |  |  |  |  |

# LIST OF ABBREVATIONS

| Algebraic Reconstruction Technique       |

|------------------------------------------|

| Active Interconnect Technology           |

| Application Specific Integrated Circuits |

| Computer Added Design                    |

| Complementary Metal Oxide Semiconductor  |

| Configurable Logic Block                 |

| Computed Tomography                      |

| Computed Axial tomography                |

| Digital Clock Manager                    |

| Discrete Radon Transform                 |

| Digital Signal Processing/Processor      |

| Discrete Time Fourier Transform          |

| Filtered backprojection                  |

| Finite Impulse Response                  |

| Fast Fourier Transform                   |

| Field Programmable Gate Array            |

| Finite State Machine                     |

| General Routing Matrix                   |

| Hardware Description Language            |

| Intellectual Property                    |

| Non Destructive Evaluation               |

| Non Recurring Engineering                |

| Printed Circuit Board                    |

| Random Access Memory                     |

| Reduced Instruction Set Computer         |

| Read Only Memory                         |

| Radon Transform                          |

| Switch Bank                              |

|                                          |

ix

.

| SRAM | Static Random Access Memory                                              |

|------|--------------------------------------------------------------------------|

| VLSI | Very Large Scale Integration                                             |

| VHDL | VHSIC (Very High Speed Integrated circuit) Hardware Description Language |

|      |                                                                          |

|      |                                                                          |

. . . **X**

.

### CHAPTER - 1

## INTRODUCTION

#### 1.1 GENERAL

Image reconstruction is a vital part of image processing, which appears in the cases where visual details of a section of opaque object are intended to be imaged. Normally, this object is a living body that can not be harmed for gathering the required information. Therefore, the required information is collected near the body of object rather than from inside. This data is collected by illuminating the object by penetrating radiations and measuring them after penetration, and is called projection or sinogram. From the projections taken at various angles, image of a desired section of the object can be obtained using an image reconstruction technique. The way, in which the projection data has been collected, decides the image reconstruction technique to be used. This type of imaging is called tomography [1]-[3]. Literal meaning of Tomography is imaging by sections or "slices".

The problem of reconstruction of the image, from measurements of its projections belongs to a class of inverse problems. An inverse problem is characterized by the fact that the information required to user is not directly available. In case of medical imaging, these projections are obtained by measurement of some type of electromagnetic radiation near the body of the patient, and the imaging device (camera or detector array) provides a transformation of the desired data. Therefore, for reconstructing the original image from available data, it is necessary to have knowledge of the mathematical operations performed by the imaging system.

J. Radon gave the mathematical principles of computed tomography (CT) [1]-[3] in 1917. At that time, his theory remained of mathematical interest only due to the lack of further research in that field and support of computation devices. His work was again used and extended over the complex fields by Kirillov during late 1950s. Although today, computed tomography is one of the most famous tools in medical diagnosis; its first application was found in field of radio astronomy during late 1950s. Presently, computed tomography is being used over diverse fields such as: medical imaging, seismology, radio astronomy, electron microscopy, and under water acoustic imaging. CT is used for non-invasive diagnostics, surgical planning etc., as a diagnostic tool. The idea behind

tomography is to reconstruct an object from the integration of data on a slice-by-slice basis. Hence, a 3-dimensional object can be viewed in two different ways, as a stack of 2-dimensional slices or a natural 3-dimensional object. Original theory of CT defines the mathematical relationships between the object attributes and projections obtained using parallel beam geometry. Now, CT systems have gone through a series of generations, and the mathematical relations have been modified. A brief discussion about these generation has been given in following chapter of this thesis.

Prior to the introduction of digital computers, the problem of image reconstruction was limited to mathematical practices only. Before introduction of computers as an integral part of imaging systems, sectional images were created by longitudinal or transverse scanning. Conventional tomographic devices were able to image the whole anatomy as a slice. However, in this imaging system, the resulting image was poor in visual qualities because of the blurring effects caused by neighboring structures. Another contributing factor for poor image quality was shadowing caused by other structures of different density distributions falling in the same slice of the anatomy. However, even at this time, when the mathematical problem of image reconstruction has been explored very deeply, and being applied to many more fields other than medical imaging, there is still much debate about the most suitable numerical technique for image reconstruction.

Earlier CT scanners used iterative reconstruction techniques to reconstruct the images. Later on Fourier transform based techniques gained their importance after the introduction of "center-slice theorem" [1]-[4] and nowadays it forms the basis for most of the image reconstruction techniques. After Fourier based methods, backprojection based techniques appeared and received a wide acceptance because of their better accuracy and faster implementation. Hence, today the backprojection-based algorithms are the most favorable choice for real-time image processing.

The natural transform caused by a CT scanner is known as Radon transform (RT) [1]-[3]. The straightforward way to get the image from this data is to take inverse Radon transform. However, direct inversion of RT is not possible, as it have no non-trivial analog in the one-dimensional space. Then, a discrete version of RT (DRT) was suggested by Beylkin to simplify the inversion problem [12]. After the formulation of DRT, many ideas to implement RT using digital signal processor (DSP) chips and Very Large Scale Integration (VLSI) came into picture [10], [11]. Few more efforts to solve this projection based image-processing problem were also made during 1990s [6]-[9]. Later Matus and Flusser suggested two more discrete approximations to the classical RT [13].

Kingston and Svalbe [14], proposed a method to map the digital and continuous projections in Fourier space. Recently many works has been cited to be discussing about the fast implementation of Radon transform and its inverse on digital hardware [5], [15], [16]. Most of these works had assumed that the input data has been collected in advance and then it can be provided in parallel at the inputs and hence give a fast implementation [16]. For implementation of filtered backprojection, in most of the cited works filtering and backprojection are performed separately and performance analysis for only backprojection operation is compared. In the current work, an effort has been made to use the most recent features available with FPGAs to perform filtering and backprojection operations together. However, the performance of current design can not be directly compared with any cited work because the hardware constrains are restricting the implementation to be serial in nature. Although emphasis has been placed to achieve an improved performance in terms of speed and resource utilization.

In most of the computer assisted imaging systems, the reconstruction work is carried out by software implementation of a suitable image reconstruction algorithm. Today medical diagnostic and surgery demand for a real-time visualization of the object, which is not possible with a software implementation. An obvious reason is that the amount of data to be processed is large and the classical algorithms are inherently complex and serial in nature [5]. Moreover, this data needs to be processed repeatedly, which makes the software implementation a further bad choice. The projection data is stored in physical memory in a serial manner, but the addressing of the data from the algorithm is complex [25]. Hence, most of the times it may happen that the required data is not available in cache memory of the computer, and it has to be read from secondary storage memory like hard disk drive. Therefore, the slow speed memory devices further limit the speed of processing. These reasons make the image reconstruction using a software implementation a very time consuming and expensive proposition.

On the other hand, the real-time image processing needs filtering and reconstruction of the image within a short duration. The capability of real-time image processing helps in reducing the motion artifact in image and capturing the transient movements inside the object. Real-time imaging is also very much helpful in radiation therapy and other new techniques of surgery. Here it enables a doctor to monitor the region of interest during therapy or surgical procedure. Therefore, it is necessary to design a powerful image processing system, which can perform the required task at the desired speed. Until date, many efforts have been made for designing such a powerful

3

Anto in

computation system. The first idea was to design a multiprocessor system using several general-purpose processors. However, even the most powerful processors are designed to be general purpose, and hence somewhere or other their capacity to perform such complex data processing operations is sacrificed against their flexibility. Even if such a system is able to meet the processing requirements, the slow communication overheads limit their speed, and this condition would worsen as the system scale increases.

Another choice is to design a dedicated hardware for the particular operation. There are two options available for a designer, one is to design an application specific integrated circuit (ASIC) and second is to use a reprogrammable hardware. ASICs are the most efficient way to meet such speed requirements but they lack in flexibility. In the face of any change in algorithm or reuse of existing design, they cannot be adopted. Another factor is the design and development cost of an ASIC is very high, and it is still growing rapidly even with the shrinking size of semiconductor devices. However, reprogrammable devices offer a good relative trade-off between performance and flexibility. They are also affordable and promising than ASICs for a real-time image processing application design.

FPGAs are a class of re-programmable devices. FPGA contains a number of configurable logic cells or logic elements, which can be programmed to perform any basic operation of a digital design. Moreover, it also contains programmable interconnects which can either automatically used to connect the different logic cells or can be defined by designer to work as a data bus. Both of these features can be used together to design more complex digital units like state machines, signal processors or even a microprocessor. Many advanced FPGAs also provide additional facilities like on-chip Static Random Access Memory (SRAM), dedicated circuits like multipliers etc to simplify the design of a higher end digital device. SRAM-based FPGAs are said to be of a very long life as they can be re-programmed as many times as designer want [24].

Some advanced FPGAs also provide on-chip microprocessors like PowerPC-405 by Xilinx. Those FPGAs are called platform FPGAs and they provide another possibility to use the advantages of software-hardware co-design. While working with a platform FPGA, designer has an option to split the design in software and hardware and implement it to get the best possible results. Hence, nowadays FPGA are self-contained for a large SOC (system-on-chip) design [24]. Moreover, in medical imaging the power of FPGA lies in its flexibility, customizability and re-configurability. Here, customizability means FPGA can be programmed to perform a particular operation, as the algorithm

requires it. Re-configurability means that an FPGA design can be altered or completely changed in case of any modification in the algorithm or if a new algorithm comes out.

#### 1.2 OBJECTIVE OF THE DISSERTATION

The key objective of the present work includes studying of the image reconstruction problem from the medical imaging point of view, exploring the mathematical principles involved in computing projections and backprojection and development of a customized digital circuit to perform these operations on chip. Following points are given to point out the attempts made in the current work:

- 1. A comprehensive literature survey was conducted on computed tomography. Initially, different ways to perform the computed tomography were studied for understanding the system and its uses. Then, special attention was given to parallel beam tomography because this method forms the basis for all other geometries of tomography. Related principles and underlying mathematics in parallel beam tomography were looked deeply. Extensive studies were carried out to look for the best possibilities, which can be depicted for design and verification of parallel beam backprojection.

- 2. Since most of the standard mathematical tools available use, their own representation of data the first necessity was to generate the Radon transform [1]-[3] for the test images. Hence, another literature survey was made for the understanding Radon transform and its discretization issue in-depth. The Radon transform was implemented on FPGA for a better density. An additional issue of address generation in radon space was also addressed on-chip. For this purpose an Intellectual Property (IP) core provided by Xilinx Core-Generator was used.

- 3. Backprojection circuit has been designed with the same addressing strategy and every projection is backprojected on a grid of initially blank image. The results of backprojection hardware are in confirmation with the input image. An effort was made to keep the resource utilization low by using a fixed-point arithmetic.

- 4. Filtered Backprojection (FBP) algorithm has been implemented on FPGA chip. In this design on-chip memory resource (Block SRAM) has been used to store intermediate data. The design is also having a special feature that allows it to

perform filtering and Backprojection operation simultaneously with a small time delay.

VHDL (Very high speed integrated circuit Hardware Description Language) is used here to implement the design. Among all the available HDL language, VHDL was used because of it is easy to design large digital structures using smaller modules in VHDL. Also VHDL is most widely used HDL; hence, the code can be understood and reused easily if required later.

#### 1.3 ORGANIZATION OF THESIS

The organization and flow of rest of work is explained under many chapters as following: Chapter 2 presents a detailed overview of the computed tomography process, defines the various terminologies, which must be known before going through next chapters. In addition, it presents some basic mathematics involved in CT.

Chapter 3 includes the discussion of basic principles for image reconstruction from projections. Several techniques utilized for image reconstruction from projections are discussed in this chapter. Finally, FBP (Filtered Backprojection) is discussed both in continuous and discrete space. Need of filtering and type of filtering required are discussed here.

Chapter 4 this chapter presents the formulation of algorithms for all problems, which has been implemented on the FPGA. The assumptions made, truncation and discretization used in formulation of those algorithms are discussed.

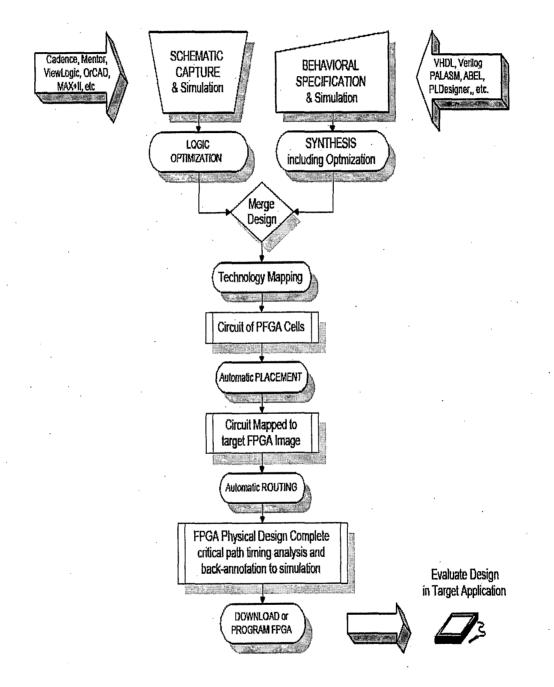

Chapter 5 explains the design flow on an FPGA device and explains various terminologies involved in it.

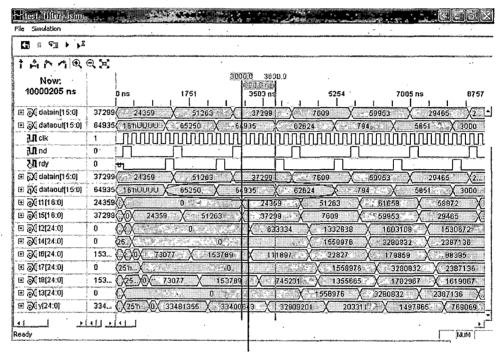

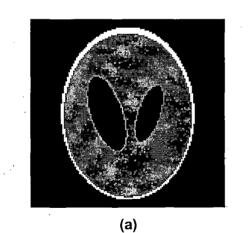

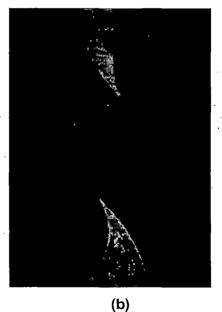

Chapter 6 this chapter shows the practical results obtained after placing the design on FPGA chip. Simulation results for some modules are included to give a better understanding of underlying complex digital functions.

Chapter 7 presents the discussion regarding the improvements and advancements that can be made in the current work.

### CHAPTER - 2

## INTRODUCTION TO COMPUTED TOMOGRAPHY

#### INTRODUCTION

Computed tomography (CT) originally known as computed axial tomography (CAT), is a medical imaging technique, which uses tomography for getting the internal details of an object from a large series of two-dimensional X-ray images taken around a single axis of rotation. However, nowadays, CT is not limited to the medical imaging only instead of it has spread over a wide application area. Now, CT is a powerful non-destructive evaluation (NDE) technique for producing two-dimensional or three-dimensional cross sectional images of an object from the flat X-ray images. Using CT, one can fetch the internal characteristics of an object such as dimension, shape, internal defects etc [25][26].

Even though, a CT image provides information not available in a traditional X-ray, this does not come without paying any cost. The radiation dose required for imaging a single CT slice is more than twice what it is required in general medical procedures. The effect of the radiation dose depends on various parameters. If a dose of large quantity is supplied within a very short period, biological effects may appear within hours and in the worst case it may cause death. Therefore, always some efforts are made to reduce the exposure time of X-rays to the patient. For reducing the exposure time a fast data capturing mechanism along with a fast processing system is required.

#### 2.2 CALCULATION OF TOMOGRAPHIC IMAGES

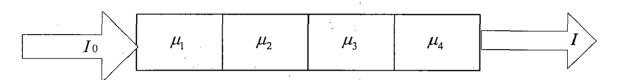

Consider the case of an X-ray passing through a slice of tissue with four attenuation coefficients as shown in Figure 2.1. The output intensity I is given by

$$I = I_0 exp \left[ -(\mu_1 + \mu_2 + \mu_3 + \mu_4) x \right]$$

(2.1)

Where, x is the distance traveled by the X-ray beam [26]. Rearranging Equation (2.1) and taking logarithm, we obtain the projection function as in Equation (2.2.d)

$$\frac{I}{I_0} = exp\left[-\left(\mu_1 + \mu_2 + \mu_3 + \mu_4\right)x\right]$$

(2.2.a)

$$ln\left(\frac{I_{0}}{I}\right) = \left(\mu_{1} + \mu_{2} + \mu_{3} + \mu_{4}\right)x$$

(2.2.b)

$$p(x) = ln\left(\frac{I_0}{I}\right) * x^{-1} = \left(\mu_1 + \mu_2 + \mu_3 + \mu_4\right)$$

(2.2.c)

$$p(x) = \sum_{i=1}^{4} \mu_i$$

(2.2.d)

It is clear from Equation (2.2.d) that a projection function is a simple summation of all different attenuation coefficients along a given path of X-ray beam.

Figure 2.1: A single X-ray beam passing through a segment of tissue

In X-ray, CT contrast between different types of body tissues and bones is associated with the different attenuation coefficients of the material involved. The projection data collected over a range of angles forms the basis for tomographic image reconstruction. If the tissues in a cross section of object are assumed to have attenuation coefficients in a matrix form as in Figure 2.2, then for a particular row *i* the projection is defined as:

$\mu_{33}$

$\mu_{n3}$

$\mu_{3m}$

$\mu_{m}$

Figure 2.2: A 2-D matrix of attenuation coefficients representing a block of tissues

$\mu_{n2}$

$\mu_{31}$

$\mu_{m}$

п

$\mu_{32}$

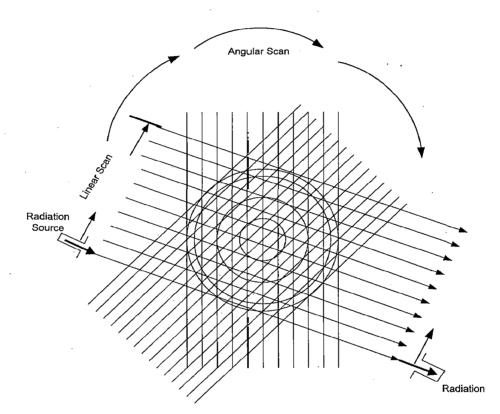

A scan shown in the Figure 2.2 is taken at zero degree with respect to horizontal. In a standard X-ray CT scanner, two types of motions are involved. Initially, the radiation source scans the object along a line for a given value of  $\theta$ , and after the completion of the scan, the radiation source and detector array are rotated for a small angle  $\Delta \theta$  and the linear scan is performed again for that view angle. This process is performed until all the projections over180° rotation are collected. This is shown in Figure 2.3.

Figure 2.3: Parallel Beam and Angular Scanning

The goal of CT is determining the attenuation coefficient value of each type of tissues only based on these sets of projection functions. For final image reconstruction, each of these projection functions is backprojected on a blank image after some filtering.

The CT equipments used in Parallel beam tomography were first generation equipments of tomographic imaging. Now, these equipments have undergone various generations of development. The first generation was Hounsfield's configuration, and consisted of pencil beam source and detectors. Later, the CT equipment took the measurements by linear motion of source and detector for each projection. The next generation of CT introduced a small fan beam source and linear detector array. Projections were measured by translating and rotating the system around the object.

Third generation CT equipments were a slight improvement over the previous generation, as they used a wide fan bean source. The concept behind using a wide beam was to scan the whole object without any translation. The fourth generation CT equipments introduced a stationary circular detector array and a rotating wide fan beam source. Therefore, this generation CT equipments had only one rotating part that helped in reducing motion artifact largely. The fifth generation CT equipments are used for three-dimensional or volume imaging. These equipments use a cone beam source and a two-dimensional array of detectors. The mathematics involved in all these new generation CT equipments is derived from first generation parallel beam scanners. Therefore, the next section discusses the mathematics of first generation CT scanners.

#### 2.3 **PROJECTIONS**

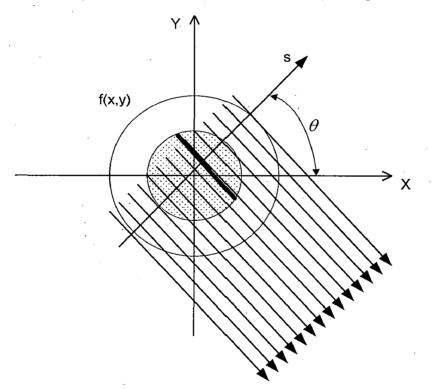

In the previous section, a term projection function was introduced. This projection function was nothing but a linear summation of all the different attenuation coefficients along a single beam of X-ray. In medical imaging also the word, projection has the similar meaning. Here, a projection is the collection of all detected radiations for a single linear scan at a given angle  $\theta$ . This is illustrated with the help of Figure 2.4.

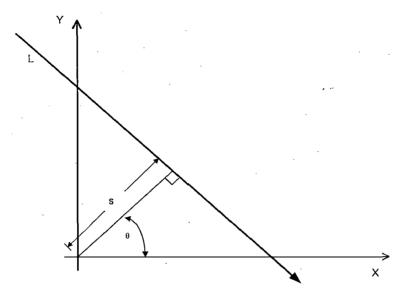

Figure 2.4: Parallel beam geometry and coordinate system

Here, f(x, y) represents the density distribution or attenuation coefficient distribution in a particular section of the object where, x and y are spatial coordinates. The figure shows a number of parallel lines passing through f(x, y) to represent a projection of the object taken at an angle  $\theta$ . The symbol s is the perpendicular distance of particular line from the origin. Single line of projection is given in Figure 2.5.

From the Figure 2.5 the parametric equation of the given line L may be given as:

$$s = x\cos\theta + y\sin\theta \tag{2.4}$$

Let r be the distance of an element at (x, y) along the line L, then value of r can be calculated by using following relationship:

$$r = -x\sin\theta + y\cos\theta \tag{2.5}$$

Therefore, a new coordinate system is defined by rotating (x, y) by an angle  $\theta$  in counterclockwise direction. The transformation from one coordinate system to other is found by Equations (2.6) and (2.7) given as:

$$\begin{bmatrix} x \\ y \end{bmatrix} = \begin{bmatrix} \cos\theta & -\sin\theta \\ \sin\theta & \cos\theta \end{bmatrix} \begin{bmatrix} s \\ r \end{bmatrix}$$

(2.6)

And

$$\begin{bmatrix} s \\ r \end{bmatrix} = \begin{bmatrix} \cos\theta & \sin\theta \\ -\sin\theta & \cos\theta \end{bmatrix} \begin{bmatrix} x \\ y \end{bmatrix}$$

(2.7)

11

s a star

For line L given in Figure 2.5, the attenuation line sum can be calculated using following equation:

$$I_{\theta_L}(s) = I_0 exp\left[-\sum_r f(x, y) \Delta r\right]$$

(2.8)

$$= I_0 exp\left[-\sum_r f(scos\theta - rsin\theta, ssin\theta + rcos\theta) \Delta r\right]$$

(2.9)

Similarly, calculation of attenuation line sum for every line given in Figure 2.4 is carried out. These line sums for a given angle can be represented collectively by a single attenuation profile as:

$$p_{\theta}(s) = -ln \left[ \frac{I_{\theta}(s)}{I_{\theta}} \right] = \sum_{r} (f(s\cos\theta - r\sin\theta, s\sin\theta + r\cos\theta)) \Delta r$$

(2.10)

If the attenuation coefficient is considered to be defined by a continuous function, then this formulation would become as:

$$p_{\theta}(s) = \int_{-\infty}^{\infty} f(s\cos\theta - r\sin\theta, s\sin\theta + r\cos\theta) dr$$

(2.11)

The function  $p_{\theta}(s)$  is called the projection of the function f(x, y) along the angle  $\theta$ . Every projection contains some information about the object. However, for a faithful reconstruction of the original object many of these projections are required. Usually these projections are taken for various values of  $\theta$  over the range 0 to 180°. A projection is a one-dimensional vector of received intensities in (s,  $\theta$ ) space. All projections are stacked together to form a two-dimensional data set  $p(s,\theta)$ , which is called a sinogram. This transformation of function f(x, y) in to the sinogram  $p(s, \theta)$  is called the Radon transform (RT).

#### 2.4 THE RADON TRANSFORM

The two-dimensional RT is an operator that maps a real function f(x, y) into a set of its line integrals. Mathematically, RT is given by the following equation [1]-[4]:

$$\Re\left\{f(x,y)\right\} = \int_{-\infty}^{\infty} \int_{-\infty}^{\infty} f(x,y)\delta(x\cos\theta + y\sin\theta - s)dxdy$$

(2.12)

where,  $\Re$  is the Radon operator and  $\delta$  is the Dirac delta function. The term  $(x\cos\theta + y\sin\theta - s)$  is the parametric equation of the line as shown in Figure 2.5. The RT maps a two-dimensional function in rectangular space (x, y) to radon space

characterized by (s,  $\theta$ ). Physical significance of radon space coordinates (s,  $\theta$ ) can be understood by taking an illustration given in Figure 2.4. The values of s are obtained by linear translation of source and detector array and the values of  $\theta$  are obtained by rotating the source-detector pair around the body of the object.

Theoretically, Radon transform is defined over an infinite space. However, in a practical situation the object represents a limited space. In addition to this, the coordinates of image space (x, y) assume a set of discrete values only. Therefore, the resultant radon space would be a discrete space and can be described with the help of summations instead of integrations. A detailed discussion of Discrete Radon transform (DRT) [12] [13] is given in following section.

#### 2.5 DISCRETE RADON TRANSFROM

The Radon transform of the object consists of continuous projections for an infinite number of angles in a given range. However, practically there are only a number of discrete projections taken at finite discrete intervals over a given range of angles. Projections are discrete because of another practical limitation that is the detectors are discrete recording elements. Each detector records the intensities independent of neighboring detectors. Therefore, the practical Radon transform is not a continuous transformation. A discrete formulation of the practical RT is given in Equation (2.13) as:

$$p(s,\theta) = \sum_{L(s,\theta)} f(x,y) \Delta r$$

(2.13)

where, L(s,  $\theta$ ) represents set of lines passing through the object f(x, y). Here,  $\theta$  assumes a value from finite discrete values. Literature reveals several approaches to compute DRT. These methods differ mainly in the way of calculating the weight factor  $\Delta r$ , for a given sampled input image. The summation and sampling terms requires some interpolation. There are various interpolation methods in use such as nearest neighbor interpolation, linear interpolation, line length and pixel area [10]. For a hardware implementation, different interpolation schemes offer a different computational loading. From the literature and initial MATLAB simulations, it linear interpolation was found to give the best compromise between the qualities of reconstructed image and the computational loading [10].

13

· + 16 .

#### 2.6 CONCLUSION

Parallel beam tomography forms the mathematical basis of all other generations of CT. All mathematical relations for later generations can be derived from parallel beam tomography. Therefore, a digital implementation of Radon transform for the former can be altered appropriately to get an implementation for any later generation CT. Since, RT is not directly invertible to image space; DRT becomes a better choice for implementation. Sampling and summation need some interpolation. Linear interpolation technique is a better choice as it offers a good trade off between quality of result and complexity of calculation.

#### CHAPTER - 3

## **IMAGE RECONSTRUCTION USING BACKPROJECTION**

#### 3.1 INTRODUCTION

Reconstruction of original two-dimensional function f(x, y) is an important problem in the field of non-invasive imaging. Image reconstruction is the process of estimating an image f(x, y) from a set of one-dimensional projection. We cannot reconstruct a two-dimensional function with the help of a single projection due to loss of information during the projection operation. However, if a number of projections taken at different angles are available, one can estimate the information contained in the original object. The required number of projections for a given image is still a topic of debate. However, an estimate about the required number of projections was given by Ronald Bracewell [6].

The problem of image reconstruction is constrained by many parameters. First important constraint is the number of projections available for image reconstruction. Another constraint is the view of projection, as it may be a full view projection or a truncated projection. In case of truncated projections, extrapolation techniques are used to complete the projection before reconstructing the image [17].

In practice, there are many ways to reconstruct a two-dimensional function from projection data. In this chapter, before discussing the image reconstruction techniques, a very basic theorem relating the Radon space with Fourier space is described. A brief description of most of the important reconstruction methods is given in a later section. Finally, the method implemented during the present thesis work is discussed in detail along with comparisons with other methods.

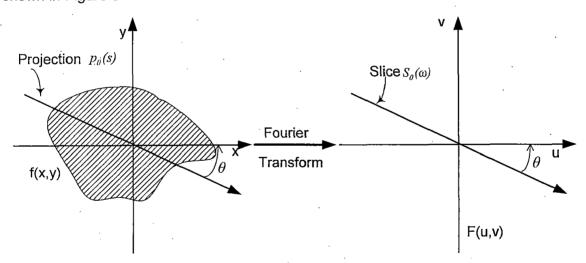

#### 3.2 THE FOURIER SLICE THEOREM

The Fourier slice theorem builds the fundamental basis for a number of image reconstruction techniques. It relates the one-dimensional Fourier transform of a projection of a two-dimensional function f(x, y) with the two-dimensional Fourier transform of f(x, y). Let F(u, v) be the Fourier transform of the image f(x, y). Mathematically, it is given by Equation (3.1).

$$F(u,v) = \int_{-\infty}^{\infty} \int_{-\infty}^{\infty} f(x,y) e^{-j2\pi(ux+vy)} dxdy$$

(3.1)

Also, let  $S_{\theta}(\omega)$  be the Fourier transform of the projection  $p_{\theta}(s)$ , i.e.

$$S_{\theta}(\omega) = \int_{-\infty}^{\infty} p_{\theta}(s) e^{-j2\pi\omega s} ds$$

(3.2)

The Fourier slice theorem is stated as, "The one-dimensional Fourier transform of a projection  $p_{\theta}(s)$ , taken with respect to s, is equal to the central slice, at angle  $\theta$ , of two-dimensional Fourier transform of the object f(x, y)" [1] [3]

i.e. if

$$f(x,y) = \int_{-\infty}^{\infty} \int_{-\infty}^{\infty} F(u,v) e^{j2\pi(ux+vy)} du dv$$

(3.3.a)

Then,

$$S_{\theta}(\omega) \equiv F(\omega, \theta) \tag{3.3.b}$$

Where,  $F(\omega, \theta)$  denotes the value of F(u, v) along a line at an angle  $\theta$  with the *u*-axis as shown in Figure 3.1.

Figure 3.1: A simple example of Fourier slice theorem

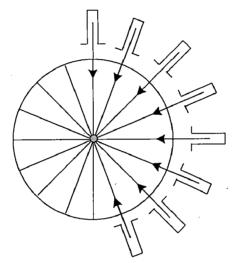

Therefore, Fourier slice theorem indicates that by taking the projections of the object at angles  $\theta_1, \theta_2, \theta_3, ..., \theta_k$ , and taking Fourier transform of them, one can determine the values of F(u,v) on the radial lines. If an infinite number of projections were taken, then F(u,v) would be known at all points in uv-plane. Knowing F(u,v), the image f(x, y) can be recovered by taking the two-dimensional inverse Fourier transform, as given by Equation (3.4).

$$f(x,y) = \int_{-\infty}^{\infty} \int_{-\infty}^{\infty} F(u,v) e^{j2\pi(ux+vy)} du dv$$

(3.4)

In most of the practical cases, such as, image two-dimensional function is a bounded function in space. Suppose, if the function f(x, y) is bounded by  $-\frac{d}{2} < x < \frac{d}{2}$  and  $-\frac{d}{2} < y < \frac{d}{2}$ , then for the purpose of computation, Equation (3.4) must be modified into a two-dimensional discrete-time Fourier transform (2-D DTFT).

Practically, it is impossible to take infinite number of projections over a finite space due to computational limitations. Therefore, if there are N numbers of projections available, frequency domain coordinates will vary from -N/2 to N/2 only. It is obvious from Figure 3.1 that if the number of projections is finite, then the density of values at higher frequencies will be sparse and it will be very dense at the low frequencies. If an inverse of this function is taken, there will be excessive blurring of the resultant image. Therefore, some kind of preprocessing is desired before taking the inverse transform as to get a faithful reconstruction of the original object. The knowledge of Fourier slice theorem enables us to correlate the Radon space with the Fourier space. Some important reconstruction techniques are discussed in the following section.

#### 3.3 IMAGE RECONSTRUCTION TECHNIQUES

There are several algorithms existing to reconstruct an image from projections. Following are the few important methods used for this purpose:

- Brute force inversion technique

- Iterative reconstruction technique

- Fourier-based technique

- Filtered backprojection technique

Brute force and iterative techniques are the oldest techniques used for this purpose. However, introduction of "Fourier slice theorem" revolutionized the field of image reconstruction. Fourier based methods were accepted widely because of better understanding and prior knowledge about Fourier transforms. Another idea was to take the direct inverse of Radon transform, which gave rise to Backprojection technique. Filtered backprojection technique is a complete direct inversion technique. This method has received a good acceptance and it is being used in most of the modern medical image processing machines.

#### **3.3.1 Brute force inversion technique**

This inversion technique takes help of linear algebra in estimating the pixel values in the image to be reconstructed. It formulates a set of simultaneous linear equation from the given projection data. Any algorithm used for solving simultaneous linear equations can solve this set of simultaneous linear equations. Consider, the following example having six projections over a 2x2 matrix.

$\begin{bmatrix} a & b \\ c & d \end{bmatrix} 10$ (3.5.a) 6 10 8 12

These can be organized in a matrix form, which represents a set of six simultaneous equations as follows:

|   |   |   | _ |                                   |   |    |  |

|---|---|---|---|-----------------------------------|---|----|--|

| 1 | 1 | 0 | 0 |                                   |   | 10 |  |

| 0 | 0 | 1 | 1 | $\begin{bmatrix} a \end{bmatrix}$ |   | 8  |  |

| 1 | 0 | 1 | 0 | b                                 |   | 10 |  |

| 0 | 1 | 0 | 1 | c                                 | = | 8  |  |

| 1 | 0 | 0 | 1 | $\lfloor d \rfloor$               |   | 12 |  |

| 0 | 1 | 1 | 0 |                                   |   | 6  |  |

(3.5.b)

The set of simultaneous equations shown in Equation (3.5.b) represents a simple problem in linear algebra. This is again an over-determined problem because there are six equation and only four unknowns. However, this technique may require to solve hundreds of linear equation for a single slice. Therefore, it is not suitable for real-time implementation.

#### 3.3.2 Iterative reconstruction technique

Iterative reconstruction technique was first technique to be used in practical tomographic image reconstruction. Basic mathematics involved in this technique was algebra. Therefore, it was also known by algebraic reconstruction technique (ART). This technique follows a stepwise procedure to compute the estimates for the image pixels. The steps involved are given as follows:

- 1. Make an initial guess of the solution

- 2. Compute the projections based on this guess

- 3. Improve the initial guess by comparing the results obtained from previous step with the actual projection values. The improvement is made using the following relationship

$$P^{i+1} = P^i + g(actual - computed)$$

(3.6)

Here,  $P^i$  denotes one-dimensional array of all pixels at  $i^{th}$  iteration and g is a multiplication coefficient, which is a real number in the range [0.0, 1.0]. The multiplication coefficient is used to control the rate of improvement. Selection of a suitable value is done in an inverse relation with the number of projections available. For a large number of projections its value is taken to be sufficiently small and vice versa.

The ART was used practically in initial CT scanner to reconstruct the image. This technique has certain drawbacks such as, slow convergence and high sensitivity to noise. With more noise, convergence slows down further and may lead to an incompatible result.

#### 3.3.3 Fourier-based technique

The principle of Fourier based image reconstruction is to take one-dimensional Fourier transform of the projection data and fill the two-dimensional Fourier space using Fourier slice theorem. Suppose, the image f(x, y) is bounded by -d/2 < x < d/2 and -d/2 < y < d/2, then we can reconstruct the image by using Equation (3.7) given as:

$$f(x, y) = \frac{1}{d^2} \sum_{m=n} F(\frac{m}{d}, \frac{n}{d}) e^{j2\pi(\frac{m}{d}x + \frac{n}{d}y)}$$

(3.7)

Here, variables m and n will vary from -N/2 to N/2 for N number of projections. This equation can be implemented rapidly using the Fast Fourier transform (FFT) algorithm provided the N<sup>2</sup> Fourier coefficients are known. The concept of Fourier-based reconstruction is shown with the help of a block diagram in Figure 3.2.

Figure 3.2: A conceptual block diagram of Fourier-based Reconstruction

Since, we have a limited number of projections, the function F(u,v) is known only along a finite number of radial lines. In order to be able to use Equation (3.7) one must have to interpolate from these radial lines to the points on a square grid. Theoretically, one can calculate all N<sup>2</sup> coefficients required in Equation (3.7) provided as many values on these radial lines are given. However, this interpolation is computationally intensive and often leads to unstable results. Moreover, interpolation error at higher frequencies is much higher in comparison to that at lower frequencies, this result in degradation of the image quality.

#### 3.3.4 Filtered backprojection technique

In backprojection, the measurement obtained at each projection is projected back along the same lines and at the same angles. Thus, each projection is smeared back on a blank square grid and then the contribution of each projection is accumulated for each pixel. The estimated gray level for each pixel is then calculated by dividing the corresponding accumulated value by total number of projections. The process of backprojection is shown with a simple example in Figure 3.3.

Figure 3.3: Backprojection of a point mass on origin

Backprojection algorithm is based on use of a backprojection operator. A backprojection operator  $\mathfrak{B}$  is defined as:

$$b_{\theta}(x, y) = \Re \left\{ p_{\theta}(s) \right\} = \int p_{\theta}(s) \delta(x \cos \theta + y \sin \theta - s) ds$$

(3.8)

The quantity  $b_{\theta}(x, y)$  is the backprojection density due to projection  $p_{\theta}(s)$ . Backprojection operator assigns the value of projection to the entire pixels that are falling on the line  $x \cos \theta + y \sin \theta - s$ . Adding up the projections at all angles, we obtain

$$f_b(x,y) = \int_0^{\pi} b_{\theta}(x,y) d\theta$$

(3.9.a)

$$= \int_{0}^{\pi} \int_{-\infty}^{\infty} p_{\theta}(s) \delta(x \cos \theta + y \sin \theta - s) ds d\theta$$

(3.9.b)

The result obtained from Equation (3.9.b) will give a distorted estimate of the original function f(x, y). For practical purposes, this distorted reconstruction is not acceptable. It is desirable to reduce this blur without using any two-dimensional transform. The Fourier

slice theorem provides such possibilities. With the help of Fourier slice theorem Equation (3.9.b) can be re-written as given in Equation (3.10)

$$f_b(x,y) = \int_{0}^{\pi} \int_{-\infty}^{\infty} \left[ \int_{-\infty}^{\infty} S_{\theta}(\omega) e^{j2\pi\omega s} d\omega \right] \delta(x\cos\theta + y\sin\theta - s) ds d\theta$$

(3.10)

Integrating with respect to s and replacing  $S_{\theta}(\omega)$  with  $F(\omega, \theta)$ , above equation becomes

$$f_b(x,y) = \int_{0-\infty}^{\pi} \int_{-\infty}^{\infty} F(\omega,\theta) e^{j2\pi\omega(x\cos\theta + y\sin\theta)} d\omega d\theta$$

(3.11)

The two-dimensional inverse Fourier transform in polar form is defined as:

$$f(x,y) = \int_{0}^{2\pi} \int_{0}^{\infty} F(\omega,\theta) e^{j2\pi (x\cos\theta + y\sin\theta)} \omega d\omega d\theta$$

(3.12)

This can also be written as

$$f(x,y) = \int_{0}^{\pi} \int_{-\infty}^{\infty} F(\omega,\theta) e^{j2\pi(x\cos\theta + y\sin\theta)} |\omega| d\omega d\theta$$

(3.13)

It is necessary to use  $|\omega|$  since, the integration includes the negative values. Comparing Equations (3.11) and (3.13) gives that the original function and the reconstructed function differs only by a weighting term  $|\omega|$ . This term accounts for the blurred reconstruction of f(x, y). Therefore, for fixing this problem the projections are pre-weighted with this weighing term  $|\omega|$  using filtering before backprojection.

This reconstruction technique is called filtered backprojection (FBP) technique. Most of the modern day's tomographic imaging systems use this technique for image reconstruction purpose. The key advantage of this technique is that it involves only onedimensional Fourier transform for filtering purpose.

Digital computer implementation of FBP would require a discrete representation of Equation (3.13). Continuous to discrete space transformation is a straightforward process. The integration becomes summation and the derivative term happens to be the finite differences. The only problem in this conversion is the weighing term  $|\omega|$ . This term clearly represents a ramp filter. A ramp filter is not a stable system. Instability of this filter makes it useless in practice. However, an approximation can be made because the input data can be assumed to be band limited. This is true in practice, because of the sampling involved in measurement process. Ramachandran and Lakshminarayanan [18]

[19] gave a suitable approximation of the above-mentioned frequency domain filter, which is popularly known as Ram-Lak filter. Impulse response of the Ram-Lak filter is given as:

$$h(nT) = \begin{cases} \frac{1}{4T^2} & n = 0\\ 0 & n \, even\\ -\frac{1}{n^2 p^2 T^2} & n \, odd \end{cases}$$

(3.14)

There are many other approximations of ideal ramp filter [2]. These approximations provide different trade-offs between spatial frequency resolution and the noise immunity.

#### 3.4 CONCLUSION

Iterative reconstruction technique is a practically working technique. The drawback of this technique is that it is slow in convergence and very much sensitive to noise. In presence of excessive noise, it may not converge at all. Fourier-based reconstruction takes the advantage of Fourier slice theorem to find a rigorous mathematical solution of image reconstruction problem. However, due to the complexities involved with interpolation in frequency domain and two-dimensional transforms, it is also not suitable for high-speed implementation. Filtered backprojection technique shows the best promising features for digital implementation, as it needs only one-dimensional transforms. Also, filtering can be performed in spatial domain itself by designing a FIR filter from the given impulse response. It is also clear that the image reconstruction algorithms are inherently serial in nature. For a parallel implementation, a large amount of on-chip or off-chip memory to handle intermediate results will be required.

#### CHAPTER - 4

# PROPOSED ALGORITHM FOR DIGITAL IMPLEMENTATION OF IMAGE RECONSTRUCTION

#### INTRODUCTION

The architecture used in the implementation of Filtered backprojection algorithm is presented here. Image reconstruction operation needs to take inverse of Radon transformed data, which Is available in the form of projections. Therefore it is useful to go through a brief discussion about implementation of Radon transform, before Backprojection algorithm. It has been found that both operations are very much similar in terms of operators required and mathematically backprojection is a direct inverse of Radon transform.

Proposed algorithms for implementations are formulated considering various constraints. These constraints are decided by the inherent serial nature of these transforms as well as the resources available for their implementation. In current work, the design is purely serial in nature. However, parallel implementation of the algorithm is possible, but is not feasible to implement it with the available resources with current work. The main constraint is imposed by the memory required to store the intermediate results. An image processing application need a bulk amount of data to be processed and hence requires a bulk amount of on-chip as well as off-chip memory. In support of the current work, asynchronous memory resources are available off-chip. However, it is required to design dedicated memory interfaces to use these memories, which limits the performance of the circuit largely. Memory resources available on-chip is used to fulfill the need of a fast intermediate storage.

Input digital image is a two-dimensional array of pixel, where each pixel is represented by 8-bit data value. In other words, input image has 256-color resolution. The calculation of forward and inverse transform involves complex trigonometric functions. Therefore, integer arithmetic introduces large rounding errors. A floating-point representation can be used to address this problem. A floating-point representation gives best performance in terms of accuracy. However, it needs a large amount of logic and routing resources on the chip and larger memory for storing the intermediate results.

23

12.14

A fixed-point representation provides very good trade-off between the accuracy and requirement of hardware [25]. Since in the current work the ultimate goal is to restore the visual qualities of the image, a very good extent of accuracy is not necessary. Therefore, in the current work a fixed-point representation is used to optimize the speed and resource utilization. In this chapter, first and second sections describe the development of algorithm for Radon transform and its implementation on FPGA. Then in the next section algorithm for implementation of Backprojection is formulated. Finally, this chapter is concluded with discussion of implementation of FIGA.

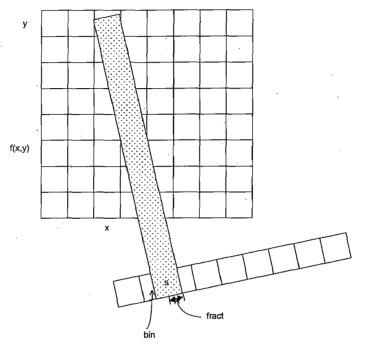

#### 4.2 PROPOSED ALGORITHM FOR RADON TRANSFORM IMPLEMENTATION

The calculation of Radon transform is generally not required. The data obtained from CT scanner is already in the Radon transform form. Calculation of Radon transform is required in some special cases where a three-dimensional image has to be constructed from two-dimensional slices. The implementation starts with the initialization of the Radon space  $p(s, \theta)$  with a zero value. The input image i(x, y) contains the data to be transformed. RT is calculated one projection at a time. For the calculation of each projection, all pixels in the input image are passed once through the processor element. Each pixel from the input image is passed in a raster scan way and the corresponding address in radon space is calculates as:

$$s = x\cos\theta + y\sin\theta \tag{4.1}$$

However, one can see that the value *s* calculated in above equation is not an integer number in most of the cases: Therefore, truncation is used to get a valid address in Radon space. For truncation, the lower bound of the real number represented by *s* is taken as:

$$bin = floor(s)$$

This truncation introduces an error. This error can be compensated by using the remaining fractional value for interpolation. Therefore, the remaining fraction value is stored in a different variable.

$$fract = s - bin \tag{4.3}$$

(4.2)

The origin for an MxM image is taken at (M/2, M/2). Although this convention is easily realizable in software (as used by MATHWORKS), in a digital hardware implementation it is not so straightforward. Since origin has been chosen in the center of the image, at least one of the image coordinates (x, y) assumes negative values in three quadrants.

#### Proposed algorithm for digital implementation of Image Reconstruction

The first problem arising from this situation is to generate the values of x and y in the range -M/2 to M/2. Moreover, the result of Equation (4.1) gives some negative values of s. Since an address in the Radon space can have a negative value, s is shifted properly to give a valid address. Therefore, the first challenge for a complete on-chip implementation is to ensure a correct address generation. Figure 4.1 shows a simple example of address calculation scheme for Radon transform.

Figure 4.1: Address calculation for Radon space

If the address generation process has been implemented successfully, the only work left is data processing. Data processing is a relatively straightforward task, as it requires interpolation and addition only. The flow of whole algorithm is demonstrated in Figure 4.2. Here  $\hat{p}(bin,\theta)$  denotes the modified value of the Radon space element  $p(bin,\theta)$  after each pass of input image. Once the execution is complete,  $p(bin,\theta)$  contains the radon transform of the input image.

#### 4.3 PROPOSED STRATEGY FOR RADON TRANSFORM IMPLEMENTATION

The key goal is to get a high-speed implementation of RT for an image. The fast RT calculation is not required in general, but in few cases such as iterative reconstruction algorithms, where a fast RT capability is desirable.

This section is dedicated to discuss the strategy used for the digital implementation of the algorithm presented in pervious section. In a digital hardware

every variable in the given algorithm has to be modeled as a signal or register. A signal carries the information from one point to another point in the architecture where as, a register stores the information for later use. A registers assigns the stored value to a signal for further use at a predefined moment of time. Here every signal is represented by an array of bits. An optimal number of bits are taken for each signal to minimize the hardware utilization, which in turn minimizes the cost of the hardware.

| Input : Image <i>i</i>  | (x, y);                                                     |

|-------------------------|-------------------------------------------------------------|

| Initialization : p      | $p(s, \theta)$ with zero;                                   |

| set $\theta$ = 0;       |                                                             |

| while ( $\theta$ < 256) | )                                                           |

| Repeat :                | for each pixel in input image, do                           |

|                         | $s = x\cos\theta + y\sin\theta;$                            |

|                         | <i>bin</i> = floor(s);                                      |

|                         | fract = s - bin;                                            |

|                         | $\hat{p}(bin,\theta) = p(bin,\theta) + i(x,y)^* (1-fract);$ |

| 1                       | $\hat{p}(bin+1,\theta) = p(bin+1,\theta) + i(x,y)^*$ fract; |

|                         | $\theta$ + +;                                               |

| end while;              | · · · · · · · · · · · ·                                     |

#### Figure 4.2: Algorithm for implementation of Radon transform

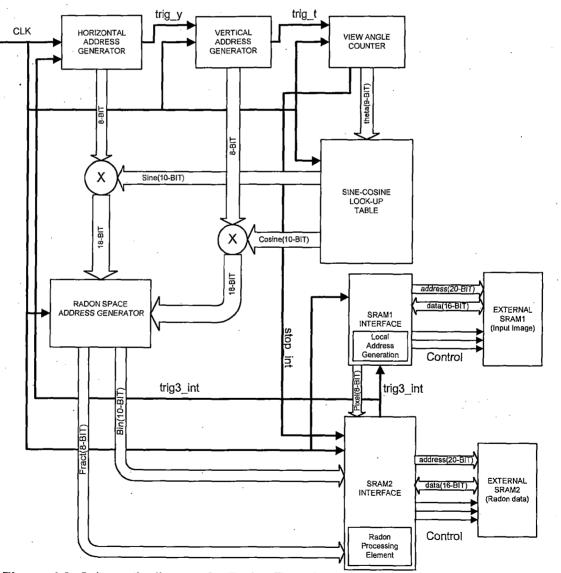

A block diagram of the circuit designed to compute the Radon transform is given in Figure 4.3. Here input image and output radon data are stored in different external memories. SRAM1 Interface block is designed to interface the input SRAM with the custom circuit. This circuit is responsible for address generation for SRAM1 and for generating the required control signals to communicate with the external memory. This interface uses a seven state finite-state-machine (FSM) to generate the control signals in a proper sequence. However, as this circuit is generating the address locally, a control of address generation is also necessary. Rest of the circuit can accept a new data value only when the current data value has been processed completely. Therefore, a handshaking signal between the output interface and input interface circuits has been used to address this difficulty. A sophisticated variable wait states insertion technique is used with the help of this handshaking signal. In Figure 4.3, signal trig3\_int generated by SRAM2 Interface circuit shows represents that signal. Initially, the FSM of SRAM1 Interface goes through all the previous states and then waits for a variable number of cycles in a wait state until signal trig3\_int becomes high. Number of variable wait cycles

## Proposed algorithm for digital implementation of Image Reconstruction

depends on the number of the sates in the FSM running in SRAM2 Interface circuit. In terminologies of digital design, this is a case of interacting state machine design. Therefore, after going through a complete cycle, FSM of SRAM1 Interface sends a signal to the local address generation block to increment the address. SRAM1 Interface circuit read a single pixel from the input image in every cycle and sends it directly to the SRAM2 Interface circuit. In SRAM2 Interface circuit, a process is designed to works as a Radon processing element. This process takes pixel data coming from SRAM1 Interface and *fract* coming from Radon address generator block, shown in Figure 4.3. This process runs in concurrency with the FSM of SRAM2 Interface circuit. Depending on the states of FSM, this process performs different arithmetic operations on the data given in the Figure 4.2.

Figure 4.3: Schematic diagram for Radon Transform computation circuit

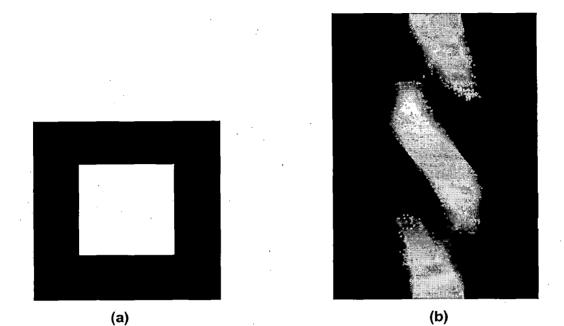

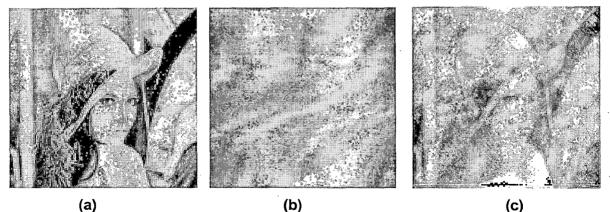

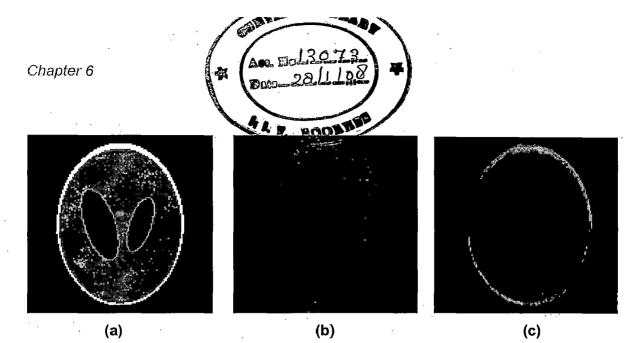

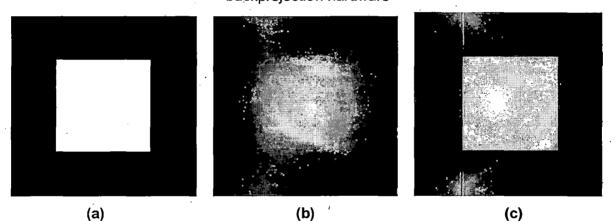

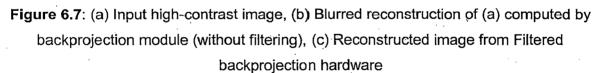

In this design, another important module is SRAM2 Interface. This circuit connects the custom circuit with another external SRAM, which is being used to store the radon data. As it can be seen that for every input pixel, two consecutive values of Radon data is being modified. For this, data is to be read from external SRAM, modified and ultimately written back to the SRAM, twice for every input pixel. This becomes a complicated memory access process, known as *Read before Write* memory access. This type of memory access should be addressed properly to ensure that the data written back after processing is a valid one. In the current work, SRAM2 Interface circuit uses a twenty-five state FSM to solve this problem. At the end of every a single input pixel has been processed completely and related results are saved on external SRAM. In addition to this, SRAM2 Interface circuit also sends a handshaking signal trig3\_int to SRAM1 Interface circuit as well as to the horizontal address generator circuit.