66-68 KAU

# Design and Performance of Phase Comparison Carrier Current Relaying

A Dissertation submitted in partial fulfilment of the requirements for the Degree of MASTER OF ENGINEERING

in POWER SYSTEM ENGINEERING

> By B.L. KAUL

DEPARTMENT OF ELECTRICAL ENGINEERING UNIVERSITY OF ROORKEE ROORKEE September, 1968

#### CERTIFICATE

Certified that the dissertation entitled "Design and Performance of Phase Comparison Carrier Current Relaying" which is being submitted by Sri B.L. Kaul in partial fulfilment for the award of the Degree of Master of Engineering in "Power System Engineering", of the University of Roorkee, Roorkee, is a record of candidate's own work carried out by him under my supervision and guidance. The matter embodied in this dissertation has not been submitted for the award of any other degree or diploma.

This is further to certify that he has worked for nine months from January 1968 to September, 1968 for preparing dissertation for the Master of Engineering Degree at this University.

(T.S.M. RAO) Professor and Head, Department of Elect.Engg., University of Roorkee, <u>ROORKEE</u>

ROORKEE, Dated: 19/5 Sept. 1968

#### ACKNOWLEDGEMENT

The author wishes to acknowledge his deep sense of gratitude to his teacher and guide, Dr. T.S.M. Rao, Professor and Head of the Electrical Engineering Department, University of Roorkee, Roorkee, for his expert guidance and continuous encouragement during the course of this dissertation work. He has been very kind to devote much df his valuable time in helping at every stage of the work and providing the various facilities afforded by the department in connection with this work.

The author wishes to thank Sri S.C. Gupta and Sri T. Subba Rao Lecturers in Electrical Engineering Department, University of Roorkee, for their valuable suggestions while carrying on the experimentalowork.

Thanks are also due to the laboratory and workshop staff for their cooperation during the course of fabrication work.

B.L.kaul (B.L. KAUL)

Roorkee, Beptember 19, 1968.

#### SYNOPSIS

For the past few years, Junction transistors have been widely used for power system protection. Because of their reliability, long life and high speed of operation, they have replaced thermionic valves to a great extent. Only recently, Junction transistors have been used for phase comparison carrier protection. It is seen, that high frequency, high power transistors, which are not available, make it possible to obtain the required level of carrier output power.

One of the most important aspects of phase comparison system lies in the choice of relaying quantities. Selection of such a suitable network has been made, which produces all the relaying quantities simultaneously, while using only three main current transformers. Within this network means have been provided for an easy variation of the proportions of positive and negative sequence components in the combined sequence output. A filter network has been used to eliminate the d.c. transient and harmonic components. Two successive equipments have been build and thoroughly tested.

|     |         | C   | CERTIFI         | CATE             |                      | • • •    |           |         | • • •      | <u>Page</u> |

|-----|---------|-----|-----------------|------------------|----------------------|----------|-----------|---------|------------|-------------|

|     |         | 1   | ACKNOWL         | EDGEM            | ENT                  |          |           |         |            |             |

|     |         | 5   | SYNOPSI         | S                |                      |          |           |         |            |             |

|     | CHAPTER | 1.  | . INTR          | ODUCT            | ION                  |          |           | ·       |            | 1           |

|     |         | 1.  | L. INTR         | ODUCT            | ION TO C             | ARRIER   | CURRENT   | RELAYIN | ₩G••       | 1           |

|     |         | 1.2 | 2. GENE<br>SYST |                  | EQUIREME             | NTS OF   | A CARRIE  | R RELAY | ING.       | 2           |

|     |         |     | 1.2.            | 1. Li            | ne Coupl             | ing      |           |         |            |             |

|     |         |     | 1.2.            | 2. Co            | upling C             | apacito  | r         |         |            |             |

|     |         |     | 1.2.            | 3. Li            | ne Trap.             |          |           |         |            |             |

|     |         |     | 1.2.            | 4. Li:           | ne Tuner             | •        |           |         |            |             |

|     |         |     | 1.2.            | 5. Tr            | ansmitte             | er-Recei | ver unit  | •       |            |             |

|     |         |     | 1.2.            | 6. Ca            | rrier Fr             | equency  | •         |         |            |             |

|     |         |     | 1.2.            | 7. At            | tenuatio             | on.      |           |         |            |             |

|     |         | 1.: | 3. TYPE         | STOR             | CARRIER              | CURRENT  | RELAYIN   | G SCHEM | <b>IES</b> | 12          |

|     |         |     | 1.3.            | 1. Di:           | rectiona             | l Compa  | rison Scl | heme    |            |             |

|     |         |     | 1.3.            | 2. Ph            | ase Comp             | arison   | Scheme    | ·       |            |             |

|     |         | 1.4 |                 |                  | PROPERTI<br>N SCHEME |          | IRECTION  | AL AND  | PHASE      | <b>1</b> 5  |

| · ( | CHAPTER | 2   | • PHAS          | E COM            | PARISON              | SCHEMES  |           |         | • • •      | 18          |

|     |         | 2.  | L. PHAS<br>VALV |                  | PARISON              | SYSTEM   | EMPLOYIN  | G THERM | IONIC      | 18          |

|     |         |     | 2.1.            | 1. De:           | scriptic             | on of th | e relayi  | ng Equi | pment      |             |

|     |         |     | 2.1.            | 2. Am            | plifier              |          |           |         |            |             |

|     |         |     | 2.1.            | 3. Fa            | ult Dete             | ector    |           |         |            |             |

|     |         |     | 2.1.            | 4. Co            | mparer a             | and Trip | Relay     |         |            |             |

|     |         |     | 2.1.            | 5. Si            | gnal Ala             | rm       |           |         |            |             |

|     |         |     | 2.1.            | 6. Ca            | rrier Cu             | irrent T | ransmitt  | er Rece | eiver      |             |

|     |         | 2.  |                 | SE COM<br>ISISTO |                      | System   | EMPLOYIN  | G JUNCI | TION       | 22          |

2.2.1. Operating Principle.

|         |      |                                          |                     | =        |            |

|---------|------|------------------------------------------|---------------------|----------|------------|

|         | 2.3. | PROBLEM UNDER CONSI                      | DERATION            | • • •    | 25         |

| CHAPTER | 3    | DESIGNS                                  | •••                 | • • •    | 28         |

|         | 3.1. | COUPLING CAPACITOR                       | • • •               | • • •    | 28         |

|         | 3.2. | DRAINAGE COIL                            | • • •               | • • •    | 29         |

|         | 3.3. | LINE TRAP                                | •••                 | •••      | 30         |

|         | 3.4. | LINE TUNER                               |                     | •••      | 31         |

|         | 3.5. | COMPONENTS OF THE S                      | EQUENTIAL CIRCUIT   | • • •    | 32         |

|         |      | 3.5.1. Delta Connec                      |                     |          |            |

|         |      | 3.5.2. Transactors                       | r., r               |          |            |

|         | -    | 3.5.3. C.Ts.Tg and                       |                     |          |            |

|         |      | 3.5.4. C.Ts T <sub>2</sub> and 1         | 0                   |          |            |

|         |      | 3.5.5. Filter circu                      | •                   |          |            |

| CHAPTER | 4    | TRANSISTORISED CIRC                      |                     |          | 40         |

|         |      | THE STARTING CIRCUI                      |                     | •••      | 40         |

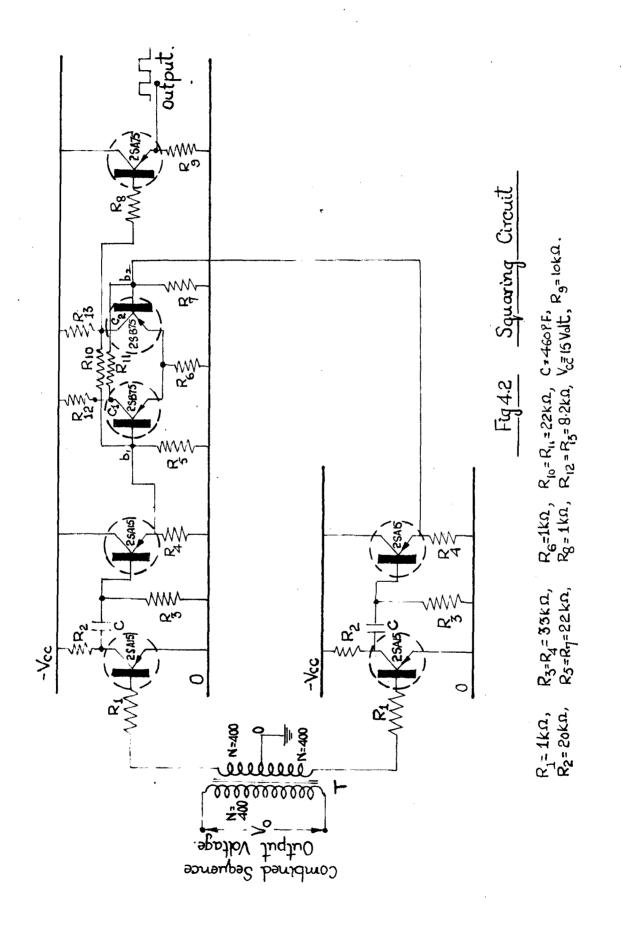

|         |      | SQUARING CIRCUIT                         |                     | •••      | 42         |

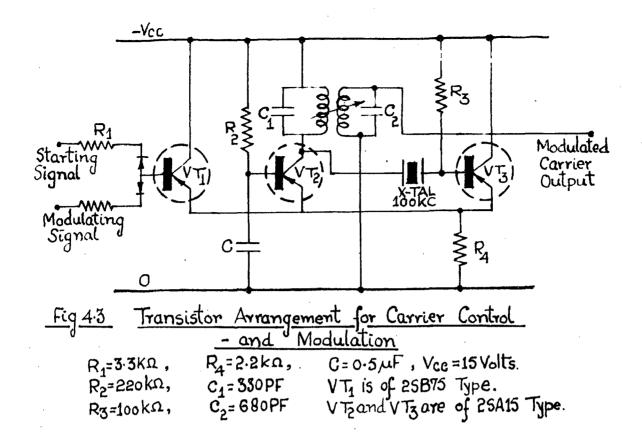

|         |      | CARRIER TRANSMITTER                      |                     |          | 44         |

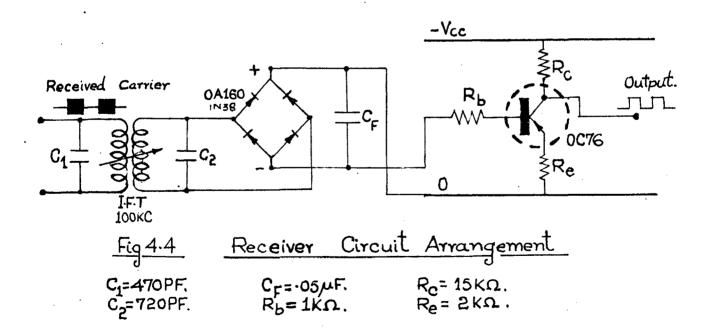

|         |      | RECEIVER CIRCUIT                         |                     |          | 44         |

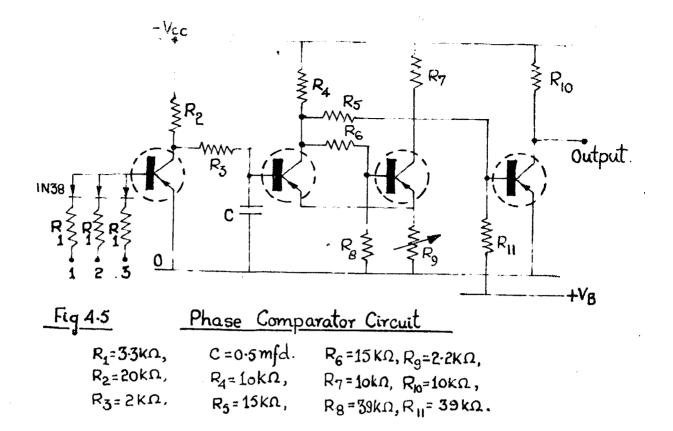

|         |      | PHASE COMPARATOR CI                      | •••<br>•••          | • • •    | 45         |

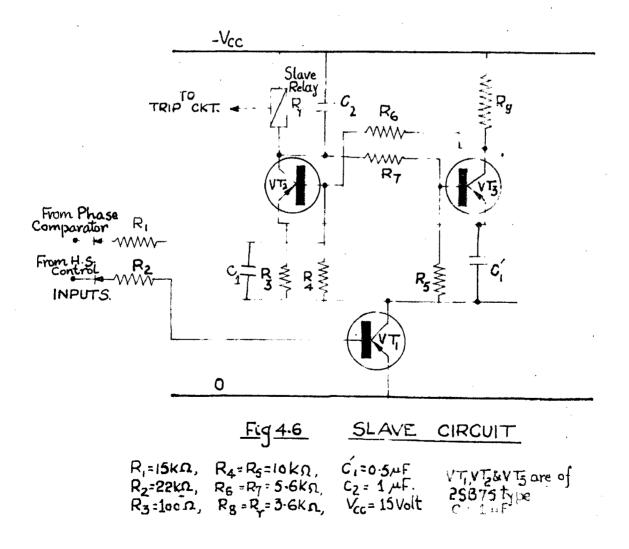

|         |      | SLAVE CIRCUIT                            |                     | • • •    | 46         |

|         | ±.0. | DIAVE CIRCUIT                            | • • •               | • • •    | 40         |

| CHAPTER | 5    | TESTING AND PERFORM                      | ANCE                | • • •    | 48         |

|         | 5.1. | TESTING                                  | •••                 | • • •    | 48         |

|         | 5.2. | PERFORMANCE ON INTE                      | RNAL FAULTS         | •••      | 49         |

|         | 5.3. | PERFORMANCE ON EXTE                      | RNAL FAULTS         | • • •    | 50         |

| CHAPTER | 6    | CONCLUSIONS                              | •••                 | • • •    | 52         |

|         | APPE | NDICES                                   | • • •               | • • •    | 56         |

|         |      | SELECTION OF PHASE                       | -                   | TIES     | 5 <b>6</b> |

|         | A    | A.1.1. Theoretical                       | -                   |          |            |

|         |      | A.1.2. Mathematical                      | •                   |          |            |

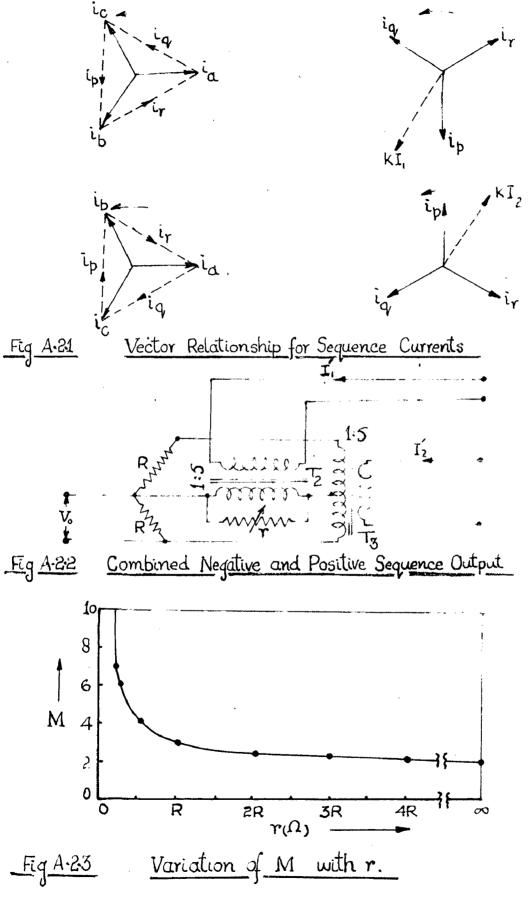

|         | A.2. | SELECTION AND CONTR<br>SEQUENCE CURRENTS | OL OF POSITIVE AND  | NEGATIVE | 71         |

|         | A.3. | FILTERING OF THE CO                      | MBINED SEQUENCE OUT | PUT      | -          |

|         | REFE | VOLTAGE<br>RENCES                        | •••                 | •••      | 72<br>74   |

|         |      |                                          | · -                 |          |            |

Page

`

# CHAPTER-1

IMPRODUCTIO I

#### 1.1. INTRODUCTION: TO CARRIER CURRENT RELAYING:

"he use of pover line carrier originated long back in 1918 but it was not applied to protection purposes till 1928. Power line carrier has become an accepted merium for the transmission of intelligence for High-Speed Relaying and several other functions between stations on a power system. Because of its versatility, it has been applied extensively to transmission networks of all voltage classes and all degrees of complexity. Viewed broadly, the situation is that with long lines, the transference of informat-, ion from one end to the other end is uneconomical for a unit type of protection if conventional pilot wires are used and it is possible to justify the cost and complexity of transforming information by means of carrier channels on the power conductors. Recent increase in the use of power line carrier equipment is directly connected with the increased load due to the power industry development and the development of long distance interconnectors on power grids. High speed protection, obtainable on long lines only through the use of carrier pilot relaying, increases the stability limit of transmission circuits so as to permit increased loading of existing lines. This factor alone, provides large savings in copper and other transmission line materials which, otherwise would be required by new construction or by the use of double circuit lines with slower relaying.

The major part of carrier equipment used for the protection forms part of the composite carrier communication equipment. Lately, transistorised audio frequency shift equipment has been employed for protection along with the single side band carrier communication equipment. Frequency shift technique is used to get over the problem of interference and to provide continuous supervision of carrier equipment. Interference problem can be solved by using

5

high power amplifiers and reducing the sensitivity of the receiver. Reliability and convenience of carrier telephone circuits for despatching permit existing generating and substation equipment to be operated nearer to maximum load and efficiency conditions.

Pilot wire relaying is particularly suited to large metropolitan areas where line sections are short and heased or private cable circuits are available. For longer power circuits and interconnectors, carrier current protection has an economic advantage in addition to the additional functions that it can provide. No other equipment generally provides instantaneous and simultaneous tripping of widely separated circuit breakers for all types of faults and all fault locations within the zone of protection. Such high-speed isolation of the fault contributes greatly to increased continuity of service of minimising fault damage, reducing outage time and generally improving system stability.

Carrier current equipment has greatly increased in reliability since its first development. Thermionic values, although greatly improved, have been the chief cause of outages. Unless a careful check is maintained on the tube performance, so that proper replacement can be made, failures are certain to occur. However, with the development of transistor technology, this difficulty has been overcome. By their very nature, transistors give promise of long life and therefore a means of eliminating the major cause of carrier failure from tubes. The overall operating time to trip the circuit breakers at both ends has been reduced to 2 cycles or lesser, by the application of transistorised equipment. One such system has been described in detail in the following chapters.

# 1.8. COMPAR REPUBLICATION A CARRIER PLANT SYSTEME:

In carrier current relaying, the principle of operation is

(2)

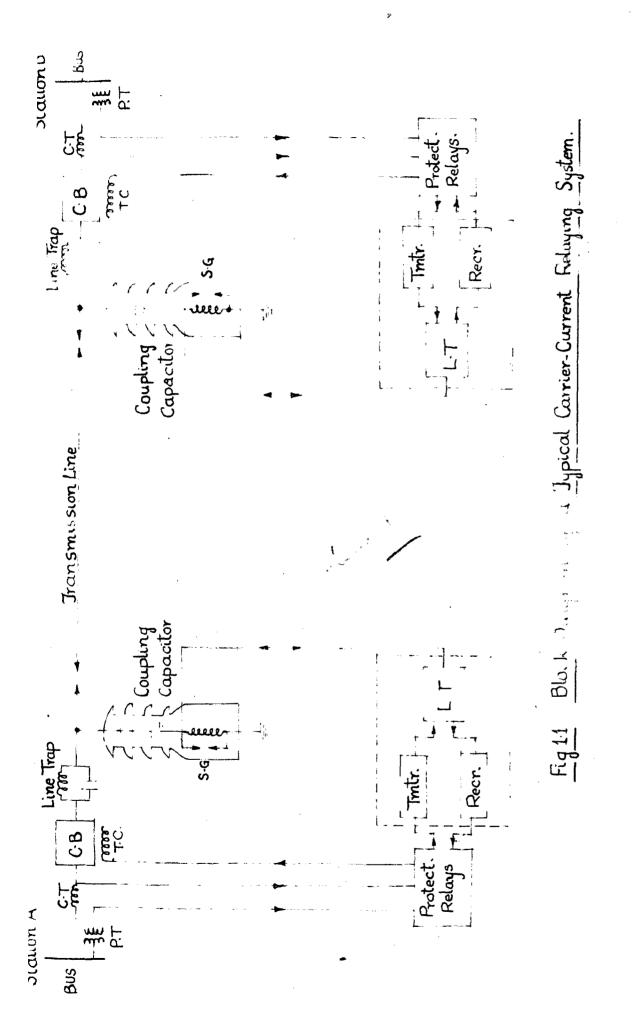

somewhat similar to the type of differential relaying employed in milot wire relaying. But, contrary to the common practice in pilot wire relaying, a quantitative comparison of the currents at the two ends of the line is not made in carrier relaying. Instead the simplest signal is transmitted, that is, the carrier is either on or off. Mence operation is not adversely affected by considerable variation in the strength of the received carrier signal. Fig.1.1 shows schematically the equipment required for a carrier current relaying system. At each end of the protected transmission line, there are protective relays, a transmitter-receiver unit, a coupling capacitor, line trop and line tuner.

The fundamental requirement imposed by the power system is that the means used to adapt the circuits for carrier channels shall not in any way interfere with the primary function of the power transmission. At the same time, the attain the desired degree of reliability, the carrier channels established should be free from interference or interruptions caused by the switching or normal operation of the power system and transient disturbances attributable to lightning or other causes. It is also essential that the carrier circuits should be sufe, thet is, they should be adequately insulated and protected analist normal and abnormal voltages and currents so as to impose no hazard to connected as maratus or to personnel using and maintaining the equipment.

One of the most important factors is the wide difference between the power frequency and carrier current frequency. Sincuit all onto the power presence which offer very low-impodence peths to noter "manuanies were appear as very high impolences at carrier frequencies and vice-versa. This phenomenon is largely responsible for the "gap impire" with that has attemped itself with the power line

(3)

$\mathcal{S}_{1}$

cerrior.

The physical and economic restrictions imposed by a high voltage normal system limit the devices that can be inserted directly in the power line to essentially only two, the coupling capacitor and the line trap. A little may be now said about the line coupling.

#### 1.2.1. Line Coupling:

There are several ways to couple the carrier terminal equipment with the line. Some of these, which are most componly employed are described below.

#### 1.º.1.1. Single Interphase coupling:

Single interphase coupling as shown in Fig.(1.2) uses two of the three power phases of the transmission line as a path for the carrier energy, consequently, it is not affected by high ground resistances or variations in the ground resistance as in any other type of coupling which requires a ground return path for the carrier energy.

In an interphase coupled carrier circuit, conditions on the phase virues to which coupling is not made have negligible effect on the operation of the carrier channel. In addition, this type of coupling provides a circuit having the most stable operating characteristics, the lowest attenuation and the lowest noise level. Its principal disadvantage lies in the cost and the construction complexity involved in providing coupling and line traps for two phases throughout the circuit, as well as the complexity of the line-tuning equipuent at terminals and by passes. It has been used most extensively for loss haul circuits where its efficiency justifies its higher cost.

(4)

#### 1.2.1.?. Cround Return Coupline:

Ground return coupling utilizes only one phase wire of the I transmission line and ground or any other suitable bath for the roturn side of the circuit, as illustrated in Fig.(1.3) If good grounds are present at the carrier terminals, or if a ground wire is carried between the terminals, this type of coupling compares very favourably, in respect to line attenuation losses, with interphase coupling.

The principal advantage of ground return coupling is that it generally requires only half the number of coupling capacitors and line traps as required for full metallic coupling as interphase. In addition, the line turning equipment required at terminals and bypasses is usually less complicated. Its main disadvantages is its somewhat higher attenuation and higher noise level as compared with the interphase circuit.

For many types of carrier channels, the disadvantages of the ground meturn circuit are greatly outweighed by its simplicity and lower cost. It is almost universally used for all pilot relay channels and extensively used on medium and short haul circuits for all other types of carrier channels.

#### 1.2.1.3. Interphase-Coupling:

'here a double circuit transmission line is available between carrier terminal stations, it is sometimes desirable to use both lines for the carrier circuit to ensure its continuity when the tither line is taken out of service. The intercircuit coupling arrangement shown in Fig.(1.4) is used sometimes to provide this feature.

This is a form of interphese coupling in which coupling is made to one phase fire of one line and to a different phase wire of the other line of a double circuit power line. It is only applicable on double circuit lines which are incapable of being sectionalized between

(5)

the carrier terminals. There a suitable frequency is available to perrit the operation of the carrier channel with the increased number switching configurations possible on the double line channel, as compared with a single line channel, this double circuit type of coupling will provide uninterrupted carrier service with all phases of either line solidly grounded at any point. In this respect, it will provide most of the advantages of double circuit interphase coupling but with half the coupling capacitors and line tuning assemblies required by double interphase coupling.

#### 1.2.2. Coupling Capacitors:

Covering a considerable range in dielectric material and physical shape, the coupling capacitor has attained the status of a standardized and highly dependable piece of equipment, universally accepted as the standard means for connecting carrier circuits to high voltage lines. In its modern form, it consists of an assembly of one or more porcelain shell, oil filled paper dielectric capacitor units together with a base unit containing a grounding switch and protective equipment. The individual capacitor units are co-ordinated as to capacitance and voltage rating, so that they may be connected in series to form assemblies for any standard circuit voltage.

The inclusion of the protective equipment in the capacitor base is now a standard practice. This protective equipment usually consists of a gap and a nower frequency drainage coil as shown in Fig.(1.1). The drainage coil ordinarily consists of an inductor connecting the low- voltage side of the capacitor to ground. This coil which has an impedance of over 50,000 ohms at carrier frequencion and loos than 100 ohms at power frequencies, serves to provide a path for the power frequency current of for a so through the capacitor to ground and thus maintains the lead to the carrier

(6)

equipment at a normal power frequency of less than 5 volts. The gap, which is connected across the drainage coil, limits the voltage which can be built up on the carrier lead during transient voltage disturbances.

From the standpoint of power transmission system, it is essential that the insulation level of the capacitor assembly, in terms of inpulse, wet and dry flash over withstand voltages, be coordinated with that of associated power line apparatus. From the standpoint of the carrier circuit, it is desirable that the capacitance be as large as possible, consistant with an economic design, preferably at least .001 pF.

Also, from the carrier circuit standpoint, it is essential that the carrier lead brought out from the base of the capacitor assembly be well insulated so as to maintain low capacitance and high leakage resistance to ground between the capacitor and the line tuning equipment.

#### 1.º.3. Line-Trap:

In its simplest form this device consists of an air core reactor with a fixed or tapped capacitor connected in parallel to form a parallel resonant circuit. It is used in series with a conductor of the transmission circuit to provide a high impedance or trap for the currents of the carrier frequency to which the resonant circuit is tuned.

In this position, the reactor of the trap must carry not only the normal line current but all abnormal or short circuit currents that the line itself is expected to carry. Its position in the line also exposes it to transient high voltage disturbances attributable to lightning and switching, and adequate lightning arrestors must be provided across both capacitor and reactor.

(7)

Practical considerations of size, weight and cost have limited largely the maximum inductance available in the line trap reactor to approximately 250 micro-henries. There it is necessary to trap more than two widely separated channels in single line conductor, additional traps are generally used.

More specifically, the principal applications of line traps may be listed as follows:

1. To reduce transmission losses in irrelevant branch-lines.

2. To minimize the effect of low impedance whunts.

3. To prevent interruption attributable to external faults or

<sup>7</sup> intentionally conlied grounds.

4. To isolate the carrier channel effectively.

#### 1.2.4. Line-Tuner:

1

This equipment, located in the circuit between the coupling capacitor and the carrier terminal equipment, performs the primary function of tuning or resonating with the capacitive reactance of the coupling capacitor to provide a low loss path for carrier frequency between the terminal equipment and the power line. The combination of the line tuning equipment and coupling capacitor may be thought of as forming a filter of the band bass type, passing or offering a low loss path for the desired carrier frequencies or channels and rejecting or offering a high loss path for the power frequency and undesired frequencies in the carrier band.

The most commonly used line tuning equipment is available in standard units, having various arrangements of variable inductors and capacitors that can be combined to form resonant circuits for one or more channels in the normal range of 50 to 150KC.

In its simplast form, for a single frequency or channel, the line tuning equipment may consiste of a single veriable inductor

(8)

connected in series with the coupling conacitor to form a series resonant circuit for the carrier frequency used. Buch a circuit is shown in Tip.(1.5) where for simplicity a ground between the caracitor and the line tuning inductor operates at high carrier frequency impedance (to ground) it is highly desirable that shunt caracitance or leakage to ground in this lead be kept to a minimum for maximum efficiency. For this reason it is usually desirable to locate the line tuning equipment as close to the coupling caracitor as possible, in order to keep the length of this lead-in conductor to a minimum.

More recent practice is to install all terminal equipment indoors and to carry the circuit in from line tuning equipment through a special low loss concentric cable.

#### 1.2.5. Transmitter-Roceiver Unit:

The transmitter-receiver unit resembles a simple radiotelegraph transmitter and receiver. The transmitter consists of a master oscillator and a power suplifier. Its output is from 5 to 40 watts at a frequency which may be adjusted to any value between 50 and 150 kilo cycles per second. The output of receiver goes to the protective relays. Each receiver on a two terminal line is tuned to the same frequency as the transmitter at the other terminal. Tither the same frequency may be used for transmission in both directions or a different frequency may be used in each direction if this is desired for the non-relaying functions of the carrier channel. On a multiter dual line, however, all transmitters and receivers should be tuned to the same frequency so that each receiver will respond to the transmitter at any other terminal, and incidently to the transmitter at the same terminal.

(9)

#### 1.2.6. Carrier-Frequency:

The frequency range from 50 to 150 kilocycles per second has been recognised as standard for power line carrier equipment for a number of years; for this reason, the bulk of application effort is devoted to carrier channels in this range only. There are several factors that should be considered in selecting a frequency for a new channel. If there are already carrier channels in use on the system or on adjoining interconnected systems, the question of possible interference with these other channels is usually of primary importance. The spacing of channels is largely dependent on the type of channels involved, the selectivity characteristics of the carrier receivers and the carrier power levels.

For some types of channels such as are used for single frequency party line telephone systems, reflections attributable to untrapped branch lines or short tap lines may limit the choice of frequencies that will give satisfactory transmission between all stations under a variety of line configuration conditions. Often, in these cases, it is necessary to make, circuit frequency characteristic measurements before the best frequency can be selected. For most medium and short transmission lines, however, reasonable judgement in the use of line traps will usually permit a wide choice of frequencies. In order to reduce the interference on the adjacent carrier systems to a minimum, a carrier frequency map should be maintained from which all new frequency allocations are coordinated.

#### 1.2.7. Attenuation:

The attenuation or dissipation of the carrier frequency energy in the course of its transmission from a carrier transmitter at one terminal to a carrier receiver at another terminal

#### (10)

may be considered as analogus to voltage drop in 50 cycle power a transmission. An attenuation of 40 db, is not uncommon in transmitting carrier energy over long lines. With this amount of attenuat ion, a transmitted power of 16W would appear at the receiver as only 0.001 vatt. The principal attenuation components have been described in the following lines.

#### 1.2.7.1. Attenuation in Lead-in Cable at Transmitter Terminal:

This component is the loss in the concentric cable between [ the transmitter terminals and the terminals of the line-tuning equipment or coupling equipment. When the line tuning equipment is located with the coupling capacitor and the cable is properly matched through an impedance matching transformer at the tuning unit, this loss is determined by multiplying the cable length by the attenuation per 1000feet indicated for the carrier frequency selected.

When both the terminal and the line tuning equipment are mounted together and are located near the coupling capacitor, no loss is included for this component.

# 1.2.7.2. Line Tuning and Coupling losses at Transmitter-Terminal:

The losses in the line tuning and coupling equipment will vary somewhat with the complexity of the tuning circuit and the frequency used. However, since this loss is small and usually less than one decibel, the usual practice is to take this loss as 1 db. The same holds good for such losses at the receiver terminal.

## 1.2.7.3. Transmission Line Attenuation:

The attentuation of the carrier energy, in transmission over the power line itself, is influenced by a number of factors, principal among these are size, spacing, insulation, and disposition of line conductors, the carrier frequency used, the type of coupling used, that is, whether it is ground return or intervhase and so on.

(11)

7

For practical purposes, some of these variables can be neglected and others combined to form a set of curves, which give attenuation in dbs per mile of transmission line corresponding to the carrier frequency chosen.

#### 1.2.7.4. Attentation Attributable to Connected Power Apparatus:

Most high voltage power transformers appear to the carrier circuit as a relatively high capacitive reactance, and a line terminating in a transformer behaves at carrier frequencies essentially as though it were terminated in an open circuit. Such a shall amount of carrier energy is transmitted through a transformer that it is seldom necessary to trap it. It is most convenien to include this shall amount of loss in the line loss itself.

#### 1.2.7.5. Attenuation in lead-in Cable at Receiver "erminal:

This loss is also considered in the same way, as the loss at the transmitter terminal as indicated previously.

#### 1.2.7.6. <u>Multiplying factors:</u>

The increase in attenuation of a power line carrier circuias a result of formation of ice, snow or frost on the line conductors and insultors has not as yet been determined accurately. However the most satisfactory method of accomodating these variations is through the use of multiplying factors<sup>8</sup> ranging nearly from 1.2 to 1.7.

### 1.3. TYP 13 OF CARRIER CURRENT RELAXING SCHIDISS:

There are two main schemes to employ the carrier current relaying for the purpose of protection. These are, the Directional comparison and the phase comparison relaying. Each of these has been discussed in the following lines.

#### 1.3.1. <u>Vinctional Comparison Scheme:</u>

Invriar hilot relay schemes of the directional comparison type

operate according to the "ollowing principle.

Upon the occurrence of fault, either in the protected section of line or in a nearby section, non directional fault detector relays are actuated at each line terminal through which power is fed to the fault. The fault detector relay turns on the carrier current transmittor at its own terminal. If however, the directional relay at any torminal shows that the fault is flowing into the protected section, thet relay turns off the carrier current transmitter. The presence of carrier on the line serves to block tripping 't all terminals. During an external fault, nover will flow out of the line at one terminal, and a carrier signal transmitted from that terminal will prevent tripping at other terminals, where poor is floring in. During an internal fault, on the other, and, house will usually "low into the line from all terminals, with the result that all carrier transmitters will be turned off and the relays at all tarrials will be free to trip instantaneously. If, at the time of an internal fault, a breaker is already open at one terminal or if there is no power source there, then the fault detector will not turn on the carrier transmitter there, thus tribing will not be provente' by the fact that no power flows in that that terminal to make the directional relay turn off the carrier transmitter Ture. The bilot have is a blocking pilot, since the reception of a pilot signal is not manuired to marrit tripping.

The directional comparison carrier pilot relay schemes in current use are built around standard 3-zone step type distance relays. These relays act in the usual manner to clear the first zone faults instantaneously, and for back up protection, to clear third zone fa-ults with time delay; but time delay is avoided for end zone phase faults through bypassing the second zone timer

(73)

contacts by carrier controlled contacts. Separate carrier and back up relays are used for ground faults.

#### 1.3.2. Phase Comparison Scheme:

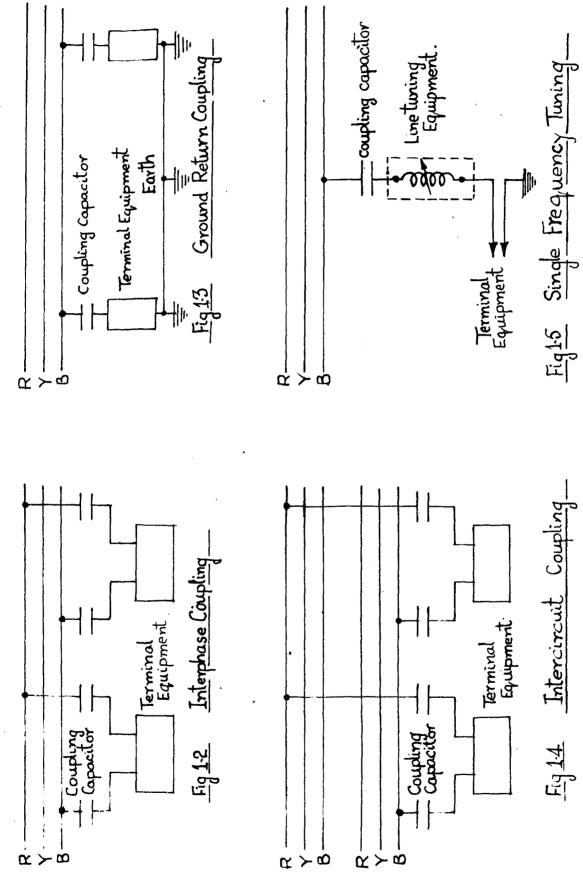

Phase comparison relaying equipment uses its pilot to compare the phase relation between current entering one terminal of a transmission line section and the current leaving the other. Like some pilot wire relays, this scheme utilizes a single phase relaying quantity, which is obtained by linear combination of the line currents through a filter circuit. The phase difference between the relaying quantities at the opposite ends of the protected transmission line determines whether the circuit breaker should be tripped. During normal conditions or during external faults, the currents entering the line at one end are substantially equal to those leaving the line at the other end, or in other words, the currents entering the line at one end differ in phase by approximately 180° from those entering the line at the other end. During an internal fault, however, the relaying quantities at the two ends of the line have some other phase difference (usually near zero). The existence, at either end of the line of a relaying quantity large enough to indicate the presence of a fault will trip the circuit breaker.

The existence of a fault of any type of the protected line or on a neighbouring circuit produces a large enough output from the filter to actuate a fault detector relay. This relay turns on the Carrier current transmitter, which, however transmits only during alternate half cycles. If the fault is external, the transmitter at the other end transmits during the half cycles when the local transmitter is inactive, and a blocking signal is received all the time, alternately from the near end and from the far end. If the fault is internal, the carrier signal received from the far end more nearly coincides

(14)

with the local signal, and there are substantial portions of each cycle during which no blocking signal is present. Under this condition, the local circuit breaker is tripped. The same action occurs at each end of the line unless the fault is fed from only one end. With feed from one end only, no carrier is transmitted from the other end, and the breaker there is not tripped, while at the feeding end, no blocking signal is received and the breaker is tripped.

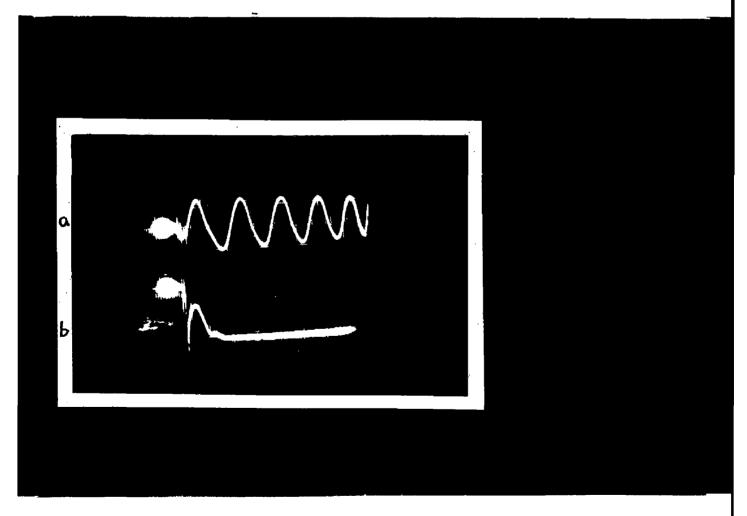

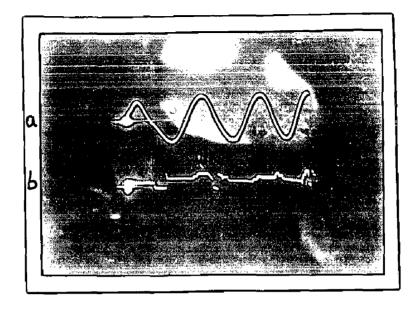

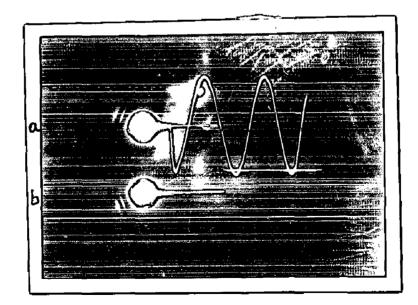

Information regarding the phase angle of the derived current at each end of the system, is transmitted by a carrier signal modulated by square waves of equal mark/space ratio, the carrier is thus inject. ed into the power lines at each end simultaneously in blocks corresponding to alternate half cycles at the power frequency. During the half cycles at each end when carrier is not being transmitted, tripping is locally effected unless it is blocked by carrier received from the remote end. An arrangement is commonly adopted in which the blocks of nodulated carrier injected at each end are in phase opposition for the case of through fault; blocking carrier is thus received at each end during its tripping half cycle, and tripping does not take place in this condition. In the ideal case, the blocks of the modulated carrier appearing on the line from each end are coincident for the case of an internal fault; the circuit breakers will operate since no blocking signal is received during a tripping half-cycle at either end. These arrangements have been indicated in Fig.(1.6).

#### 1.4. RELATIVE PROPERTIES OF DIRECTIONAL AND PHASE COMPARISON SCHEMES:

On the surface the directional comparison scheme appears more complicated, but this is because the back up elements are combined with the carrier elements. Disregarding back up elements, the directional comparison scheme has more mechanical parts and contacts

(15)

and fewer electronic circuits, while the phase comparison scheme has fewer mechanical elements and contacts and more electronic circuits. The choice of systems on this score alone is largely a matter of whether one prefers electronic or mechanical parts. On the basis of equivalent back up protection, the two systems occupy approximately the same amount of switchboard space.

The absence of inherent back up protection in the phase comparison scheme is an advantage in applications where the carrier system is used to supplement existing slover speed relays. There is merit in having two independent relay systems, with the phase comparison carrier system as the first line of protection and another system for backup.

A major advantage of the phase comparison system is that no potential transformers or potential devices are required for its operation. This advantage is mullified to a large extent if potentia sources are already available or if the back up system requires potential sources. Distance type relays, whether used in the directional comparison carrier scheme or for back up protection require a source of 3-phase potential on the protected line or the associated bus.

Because the phase comparison system operates from the line currents alone, it is immune to out of step conditions. The current entering an infaulted line section at one end is always equal to that leaving at the other, regardless of system swings. On the other hand, the distance elements used in the directional comparison scheme may operate on out of step conditions or system swings. This occurs whenever the impedance, that is, the ratio of voltage to swing current falls within the tripping area of the relay.

(16)

Other advantages of the phase comparison scheme are its immunity to false operation as a result of the following:

1. Zero sequence induction from parallel lines.

2. Unequal closure of C.B. Poles

3. Loss of potential due to blown potential transformer fuses or other causes.

However, directional comparison system is the best suited one for the protection of multiterminal lines, whereas, the phase comparison system has restricted application to multiterminal or tapped lines.

From the two basic systems, the relay protection engineer must select the system best suited to his particular application, taking into account such factors as economics, system operating requirements, previous experience, and the available indications of faults or troubles. It is these factors that make each relaying problem different from the previous ones and make protective relaying as much an art as it is a science.

## CHAPTER-2

.

۰,

.

. ••

PHASE COMPARISON SYSTEMS

.

#### 2.0. PHASE COMPARISON SCHEMES:

Phase comparison carrier current elaying itself can be divided into two types of systems, oneutilizing the thermionic valves and the other employing junction transistors. During the early years when the phase comparison carrier current was brought into practice for the first time, only thermionic valves were used, but, with the advancement in transistor technology, the transistorised scheme of phase comparison carrier current protection is coming up rapidly because of the inherent advantages of reliability, long life, quick operation etc. Both of these schemes have been described in the following lines.

#### 2.1. PHASE COMPARISON SYSTEM EMPLOYING THERMIONIC VALVES:

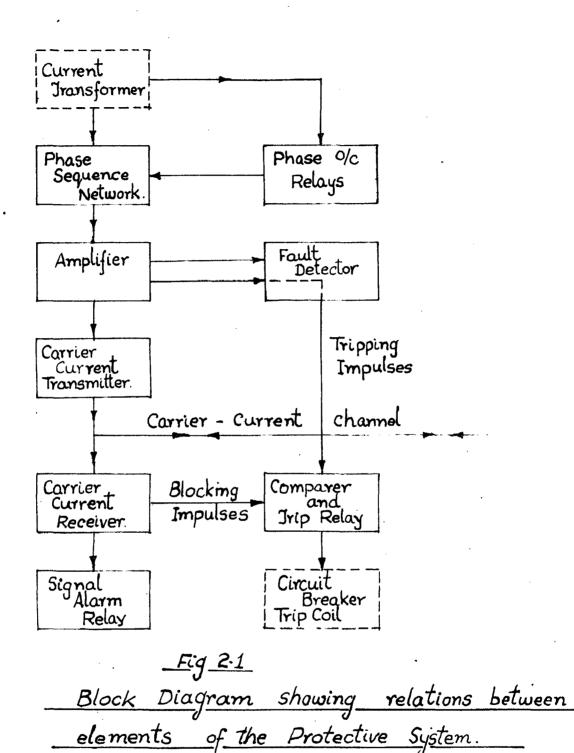

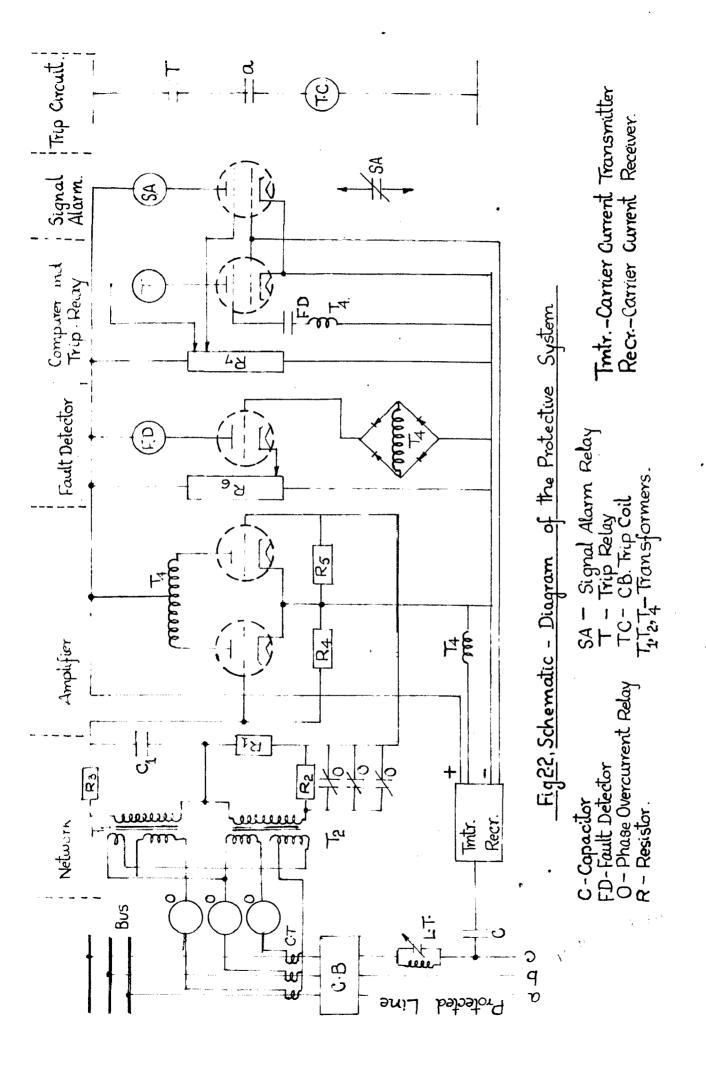

Fundamentally, the operating principle of this system is exactly similar to what has been discussed in article 1.32 in Chapter 1. The relationship of various elements are shown in block diagram in Fig.(2.1) and Fig.(2.2) gives a simplified circuit diagram.

In order to obtain the best method of combination of individual plase currents into a single quantity for comparison, various sequence currents present during different types of faults are considered. Since the use of negative phase sequence current appears desirable for all types of faults, the equipment uses negative phase sequence network with provision for developing a network output on three phase faults as has been shown in Fig.(2.2). This provision consists of three phase-over current relays, oper tion of all three shifting the network so as to introduce a positive phase sequence component into the network output. Thus the equipment functions on three phase faults at a current magnitude above full load, but for unbalanced faults, phase currents of less than full load magnitude will cause operation.

(18)

Any relaying system for the general application must provide high sensitivity during ground fault conditions. If, because of possible unbalancedloading, the desired high sensitivity is not attained by means of negative phase sequence current alone, then, zero phase sequence current may also be used to obtain the desired network output. This will make the network output of the form  $I_2 + KI_0$ .

#### 2.1.1. Description of the Relaying Equipment:

All of the tubes are of the type 25B6G like those used in the associated carrier current transmitter receiver. All the auxiliary relays except the seal in relay are of the telephone type oper ting at their normal contact pressures, thus ensuring reliability proved by long experience.

With reference to Fig. (2.2) the network is housed in a case and consists of transformers  $T_1$  and  $T_2$ , resistors  $R_1$ ,  $R_2$  and  $R_3$ and Capacitor  $C_1$ .  $T_1$  and  $T_2$  are fed from phases a dnd c respectively and  $R_3$  and  $C_1$  provide a 60° phase shift of the output of  $T_1$  so that, with balanced load, the voltage across  $C_1$  is in phase with the output of  $T_2$ , which is then adjusted to equal magnitude by  $R_2$ , so that, the vector difference is zero. Zero phase sequence current is neutralized by ground-current windings, one of which has taps for adjustment of K. The output of such a network is proportional to negative sequence current and zero sequence currents only, and independent of positive sequence current. On a phase to phase fault, such a network gives the same magnitude of output voltage regardless of which pair of phases is involved. In order to provide for a three phase fault, overcurrent relays in the three phases, marked as 0 in Fig.(2.2) are so connected that if all three pick up, they change the setting of  $R_1$  so as to unbalance the network and thus introduce

a positive sequence component in the output.

#### 2.1.2. Amplifier:

The amplifier allows the use of low burden network by permitting it to operate into a high impedance, and provides energy to drive the carrier current transmitter. Also the amplifier output controls the fault detector and provides the comparer with a local voltage for comparison with the incoming carrier current signal. It consists of two tubes operating in push-pull through an output transformer which provides a match with the load resistance consiting principally of the transmitter screen grids.

#### 2.1.3. Fault-Detector:

This element is necessary to ensure (on an external fault) that the network output is sufficient to drive the transmitter and produce an adequate blocking signal at the remote terminal, before permitting any attempt to trip. If the same carrier channel is used for communication, the fault detector also serves to transfer control of the channel temporarily from communication to relaying for the duration of a fault.

The fault detector, as shown in Fig.(2.2) consists of a voltage divider resistor, a full wave rectifier, a tube, and an auxiliary relay for its plate circuit. The rectifier is supplied from a separate vinding on the amplifier output transformer. The use of fault detector tube permits compensation, by proper biasing, for the reduction of the amplifier output voltage with d.c. supply voltage, thus providing a fault detector pick-up which is substantially constant over an adequate range of d.c. supply voltage.

#### 2.1.4. Comparer and Trip-Relay:

The comparer makes the decision whether to trip the circuit

(20)

breaker or not, depending upon the signals that it receives.

The comparer consists of a tube, a voltage divider resistor to adjust its plate voltage and the trip relay in its plate circuit. The tube is mounted on the relay auxiliary unit in the carrier cabinet to minimize the pick up in the lead from the carrier receiver to the comparer control grid. The other elements are mounted in the tripping relay case. A winding of the amolifier output transformer  $T_4$ , energizes the screen grid of the comparer tube, positive relative to the cathode, during one half cycle, and negative during the other half cycle, During the positive-half cycle, the comparer tube will conduct and cause the trip relay to operate if no incoming carrier current signal during that half cycle causes a negative voltage (rectified carrier signal) to be applied to the control grid, thereby blocking tube conduction, and consequently, the trip relay operates.

#### 2.1.5. Signal Alarm:

This element consists of a tube, a voltage divider resistor to adjust its screen grid voltage, and an auxiliary relay in the plate circuit. The screen grid voltage is adjusted so that the signal alarm tube normally carries enough current to pick up the signal alarm relay. When carrier current is received, the same negotive voltage that served as blocking voltage in the comparer is applied to the control grid, reducing the signal-alarm plate current, thereby causing the auxiliary relay to drop out and close the external alarm circuit.

#### 2.1.6. Carrier Current Transmitter-Receiver:

The transmitter is controlled by the voltage on the screen grids of the tubes, During standby conditions, this voltage is

(21)

zero and no carrier is transmitted. When 50 cycles excitation voltage from the network amplifier is applied to the screen grid circuit, the transmitter sends a signal on the positive half cycle and is definitely blocked during the negative half cycle of the excitation wave.

The carrier current receiver rectifies and filters the incoming carrier wave and thus provides a pulsuating D.C. blocking voltage which is applied to the control grid of the comparer tube. A twin diode tube is used in the receiver; one of the diodes is used for the relaying function while the other is used to drive an audioamplifier for telephone or other service employing audio modulation. These diodes operate on opposite half waves of the carrier frequency cycle to obtain a balanced load on the receiver circuit and to reduce interaction between the two circuits.

#### 2.2. PHASE COMPARISON SYSTEM EMPLOYING JUNCTION TRANSISTORS:

The problem of applying transistors to phase comparison carrier protection has been investigated extensively during the past few years. Although, in its operation, this scheme resembles the one using thermionic values, yet there is a lot of difference involved in the circuit ry. There is no question of taking normal electronic carrier equipment and replacing it with transistor equivalents. Substantial economy can be gained by this method, in addition to the advantages associated with power drain, h.t. and heater supplies and the final equipment has got the following features of major interest.

(a) It is wholly electronic from the starting circuit onwards, with the exception of the final slave relay, and consists of a number of separate functional units each arranged as a plug-in sub-assembly. In particular electromagnetic relay arrangements for control of

(22)

carrier starting and also for tripping, which are a normal feature of valve operated carrier systems, have been eliminated.

(b) Valves have been eliminated in all circuits including the transmitter- receiver circuit. The valve circuits of conventional carrier arrangements bear no affinity to the transistor circuits which have been used, and in many instances they have an entirely different functional role; transistors are used throughout as individual switches, as phase inverters and/or isolating stages, or as component parts of trigger circuits and only rarely as amplifiers and then in such a way that changes in gain are immaterial.

(c) Means have been adopted for ensuring uniform speed of operation for any fault within the protected section, irrespective of d.c. symmetry in the wave of the fault current.

(d) A method can be adopted for utilizing intertripping facilities in the event of marginal conditions, which comes in for certain phase angles and fault currents, and in the event of fault current being fed from one end of the protected section only.

(e) The system is designed for automatic resetting subsequent to fault clearance.

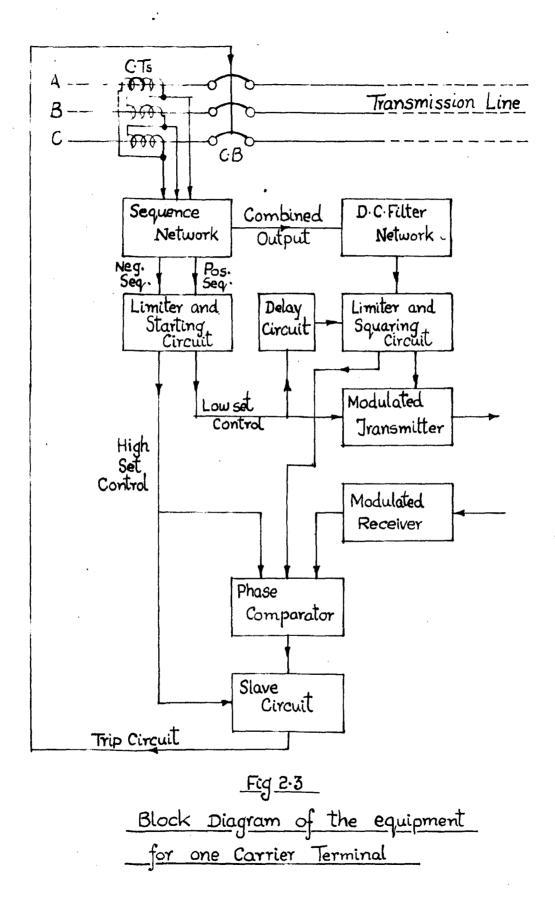

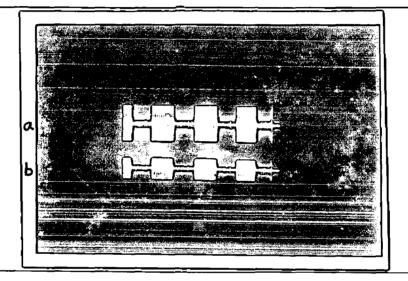

#### 2.2.1. Operating Principle:

Fig.(2.3) shows a block diagram of the equipment at one end of the protected section. The outputs from the delta connected secondary windings of the main C.Ts. are fed to a sequence network which produces independent positive and negative sequence outputs. These components are fed in parallel to a starting circuit through isolating diodes. Whilst a combination of them is fed to the squaring circuit through a filter which eliminates any harmonic and d.c. transient which may be present. The starting circuit will pick

(23)

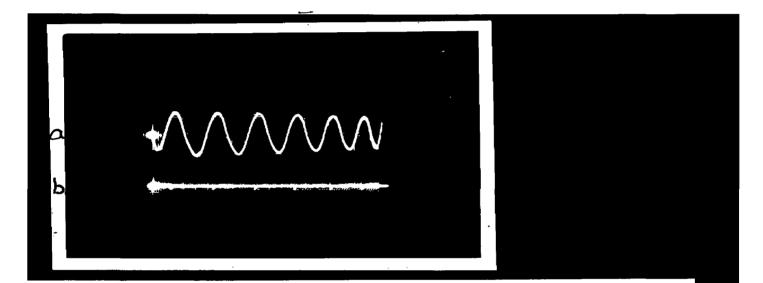

up when the amplitude of the negative sequence component exceeds a predetermined level, or alternatively, when both the amplitude and rate of increase of the positive sequence component exceeds a predetermined level. The only difference between these two starting arrangements is that, with negative sequence starting reset only occurs with fault clearance, whilst the other method has automatic reset after a predetermined time unless reset has occured earlier as a consequence of fault clearance. Then the starting circuit picks up it produces four stePfunction outputs which are fed to delay circuit, modulated carrier circuit, phase comparator and slave relay circuit.

The starting input is preponderant throughout the apparatus; each individual unit which is controlled by a starting signal does not respond to any other input(s) unless starting has occured. The squaring circuit produces two square waves, one of these is fed to the modulated carrier control circuit and the other to phase comparato for comparison with the derived square wave from the remote end. The phase comparator decides whether the fault is internal and if so it produces output which when fed to slave circuit which must have received the starting signal, trips the circuit breakers. The starting circuit signal to the delay circuit causes, in its turn, to produce a time lagged output sufficient to allow clearance in the normal way. The delay circuit output is fed to the last stage of the squaring circuit, where it stops only the square wave fed to the modulated carrier control circuit. This together with the previous existence of the starting signal, causes continuous carrier to be transmitted which blocks tripping at the remote end, thus safeguardin- against false tripping when an external fault is being cleared. The same sequence of events then occurs at the remote end and

(24)

continuous carrier is transmitted to the nearer and with the same effect.

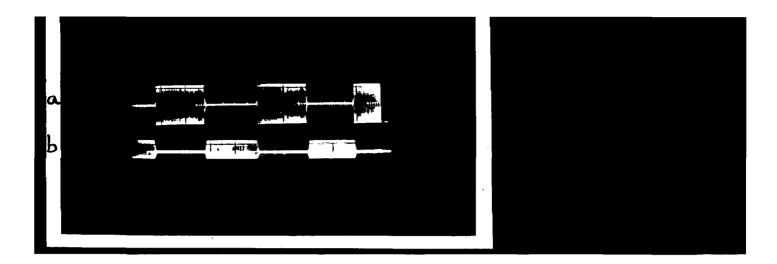

#### 2.3. PROBLEM UNDER CONSIDERATION:

A three phase, 120 mile long transmission line has been represented by a lumped inductance of about 15 ohms in each phase, which has been subdivided into three sections of 5 ohms each and further mid point of each has been tapped to vary the line reactance according to need. Similar impedance has also been chosen for the neutral wire. A three phase, 440V, 50 c/s power supply has been fed from both ends of the line through three phase contactors which close simultaneously through a closing switch. At the middle of the line, provision has been made to create any type of fault by a fault switch which operates a fault producing contactor. Indicatingslampsoto indicate the presence of the a.c. and d.c. power supply and the presence of a fault have also been provided. Line terminals have been taken out at the panel face so that the line connections can be modified and checked up, as and when desired. Similarly transmitter, receiver connections have been brought out, to check the presence of carrier signal whenever the need arises. A photograph of the so connected panel has been shown in Fig.(2.4).

The problem then is to design a transistorized phase comparison, Carrier output protection system for the above mentioned artificial line. Refering to Fig.(2.3) we see that the first step on our way, would be to design a sequential circuit which nicely represents the phase of the current combination at each end and also gives a suitable pick up signal to the starting circuit whenever a fault comes-in Three various combinations of sequence currents have been considered to select the best phase representing quantity, a detailed analysis of which has been given in Appendix A.1, and a graphic plot of the

Pig. (B.4) Cot up of the Corrier current roleying FOR PAIRL. same is shown in Figs. (A.11 to A.16). From these plots we may sum up as follows:

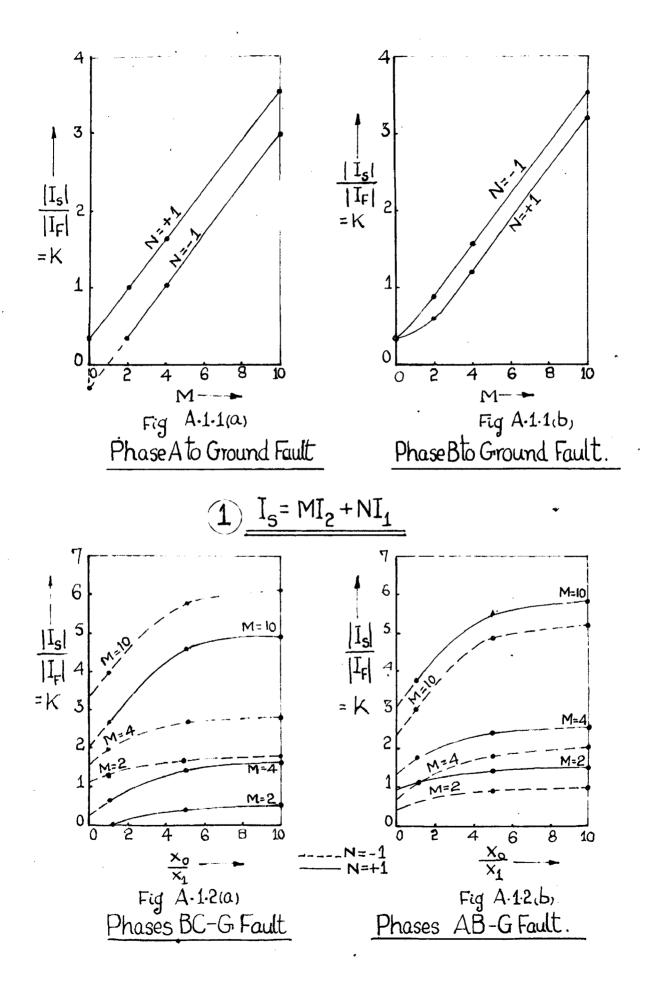

(i) Considering sequential combination  $MI_2 + MI_1$  we see that the percentage output K (=  $|I_s| / |I_F|$ ) increases as M is increased. However, the condition for K = 0 can be averted if proper values of M and N are chosen.

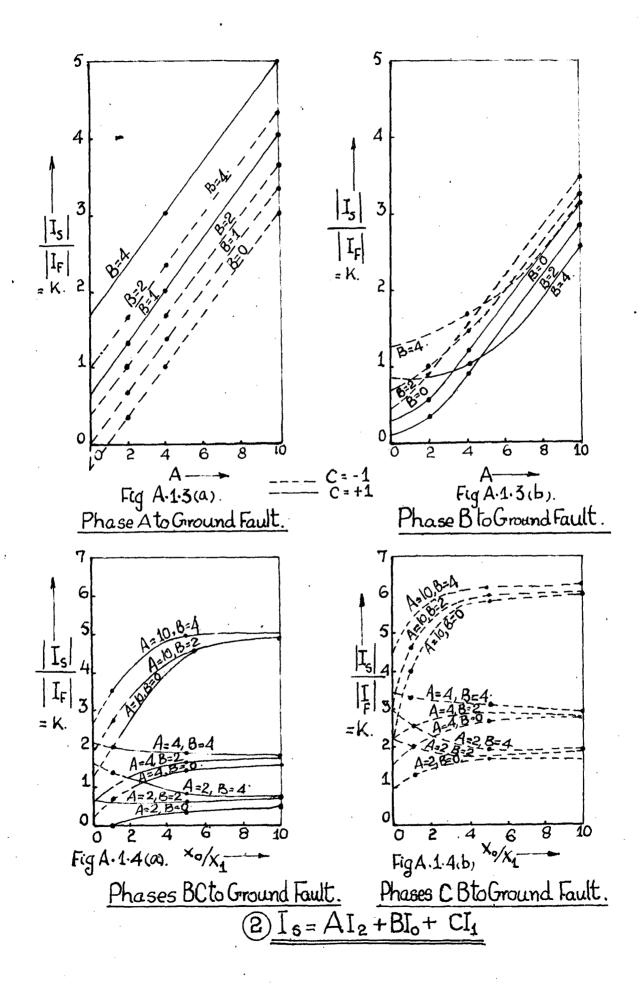

(ii) Considering the sequence combination AI<sub>2</sub>+BI<sub>0</sub>+CI<sub>1</sub>, it is seen that K increases as either A or B is increased, but the increase in A gives more effective increase in the output than the increase in B. Here also K attains zero value for the two cases shown in Figs.(A.L3a and A.L4a) but this also can be avoided by properly selecting the values of A and C.

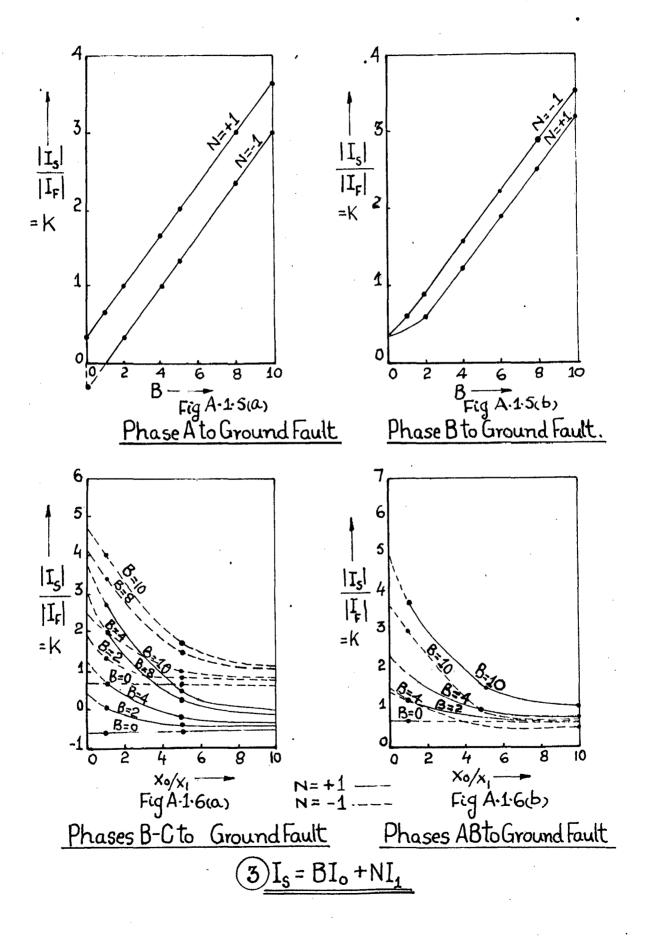

(iii) Looking into the sequence combination  $\mathrm{BI}_{0} + \mathrm{M}_{1}$  it is seen that K increases with increase in B, but it does not reach the levels obtained in the previous two cases. Moreover for double line to ground fault there is a sharp decrease in K, in an effective range of  $X_{0}/X_{1}$ .

Finally comparing the above three cases we find that the combinat ion  $\mathrm{BI}_{0} + \mathrm{MI}_{1}$  does not give satisfactory output for double line to ground faults and is hence rejected. In the second combination  $\mathrm{AI}_{2}^{+}$  $\mathrm{BI}_{0} + \mathrm{CI}_{1}$ , we find that value of K even decreases for some mid values of A and B for double line to ground fault. Moreover, the output leve does not increase beyond the one obtained with the combination  $\mathrm{MI}_{2} + \mathrm{MI}_{1}$  even for A = 10. Since one does not find much of advantage in including the component  $\mathrm{SI}_{0}$  in  $\mathrm{AI}_{2} + \mathrm{BI}_{0} + \mathrm{CI}_{1}$ , it is economic to select the combination  $\mathrm{MI}_{2} + \mathrm{MI}_{1}$  which does not need any elements to derive the zero sequence current. However, we can easily avoid the condition of K reducing to zero by fixing values of M greater than 2.

Also, regarding the selection of N, we find that for N =+1 and  $X_0/X_1$  =14 a case which can arise in practice) in Fig.(A.12a), K becomes zero. Hence N = -1 will be selected.

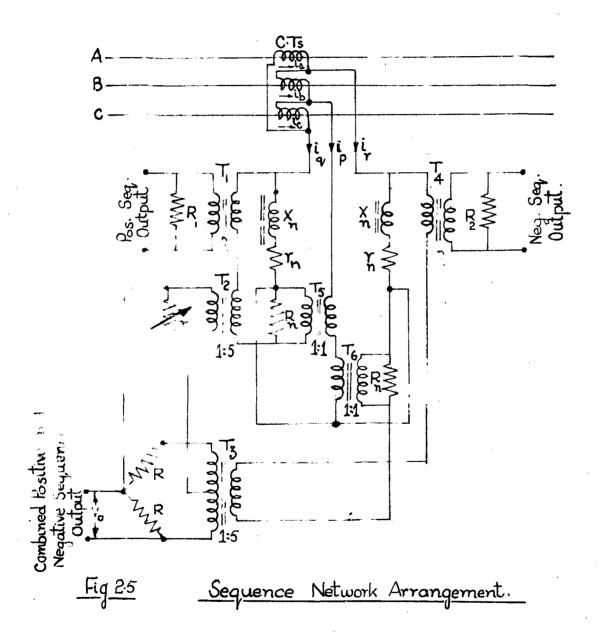

Summing up,  $MI_2 + NI_1$  is the best possible sequence combination, and based on this output and the individual positive and negative sequence output that is needed for the starting circuit, a sequential circuit shown in Fig.(2.5) has been designed, the design details being given in Chapter 3.

Next, as is required in the problem, a transistorised scheme has been used to build up the starting circuit, squaring circuit, transmitter, receiver, phase comparator and slave circuit. A detailed report of this scheme has been given in Chapter 4. A carrier frequency of 100 Kilocycles has been used for both way transmission of carrier.

### CHAPTER-3

.

.

•

DESIGNS

•

.

#### 3.0. <u>DESIGNS</u>:

Based on the requirements of the terminal equipment for the carrier current whose comparison scheme under consideration, as has been described in the previous chapters, the design of each component has been considered in this Chapter. Although the results obtained in practice do not coincide with the calculated results exactly, yet provision has been made to obtain the outputs of various components according to the requirements. For example tappings have been provided in the Transactor secondaries, Line tuner etc. to obtain the desired results. All the C.Ts. have been designed for maximum possible burden. The design procedure has been described in detail in the following paras.

#### 3.1. COUPLING CAPACITOR:

Keeping in view the factors necessary for the design of coupling capacitors, as has been discussed in Chapter I, the design of the coupling capacitor for the experimental problem under consideration may be carried out as under:

Line Voltage = 440 Volts. Let C be the capacitance of the coupling capacitor, and let it be arbitrarily chosen as .001 pr.

# • Impedance offered by the capacitor to power frequency 50 c/s. = $\frac{10^6}{2\pi x 50 x \cdot 001}$

Impedance offered by the capacitor to carrier frequency 100 Kc/s.  $= \frac{10^6}{2\pi \times 10^5 \times .001}$

#### = 1590 ohms

= 3.18 Megaohms.

Now, if we put C = .002  $\mu$  F. the above two impedances change

#### (28)

to 1.6 mega-ohm and 800 ohm values respectively. If we increase the capacitance C to a value of 0.1/uF, we see that the impedance offered to power frequency is .032 megaohms and 16 ohms respectively. Keeping in view the advantage of higher Capacitance C, and the low phase voltage of 230V available for the experimentation, a current of 8mA can flow to ground at power frequency, which is quite negligible. Hence C has been chosen as 0.1/uF for the experiment.

#### 3.2. DRAINAGE COIL:

To keep down the losses in the inductor, air cored type has been wound. Since, the current through the reactor will be of the order of a few milliamperes only, a 30SWG enamelled wire has been used to wind it.

A suitable value of the inductance to keep the carrier signal isolated from the ground and yet connected to the line, will be 100 mH.

We have,  $L = \frac{0.03948 a^2 n^2 K}{b} \mu H$ where, a is the radius of the sole wid in Cms. n the no.of turns. K a factor depending upon diameter/length. b the solenoid wound length in cms. and Using the available former, coil dia. = 7/4"•• a = 2.22.cms. Length b = 39/8" = 12.88 cms. Dia./length = 0.359.which gives value of K as 0.867 from tables.  $. 100 \times 10^{3} = \frac{.03948 \times (2.22)^{2} n^{2} \times 0.867}{12.22}$ or  $n^2 = 735 \times 10^4$ = 2720 turns. n

The tested value of inductance given by the inductor =104mH. Two such coils have been round, and each used at one end of the line.

#### 3.3. LINE TRAP:

As mentioned already line trapwill be a parallel combination of an inductor and cepacitor, the design of which follows:

#### 3.3.1. <u>Reactor</u>:

The value of inductance has been arbitrarily chosen as 2 milli-henries, and the value of capacitance needed will be considered on its bases.

A, Area of cross-section of the core = 3" x 3"

1, length of the winding = 6"

conductor size ... = 16 SVG

Now,  $L = 1.26 \frac{MA}{1} \times N^2 \times 10^{-5} \text{mH}$

where A and 1 are in centimeter scale, and N is the number of turns to be wound for the reactor.

Since, the reactor will be an air cored one, we can take u=1.

$$\therefore 2 = \frac{1.26 \text{ x9x}(2.54)^2 \text{ xN}^2 \text{x10}^{-5}}{6 \text{x} 2.54}$$

$$\therefore N^2 = 41000$$

$$\therefore N = \underline{202}$$

#### 3.3.2. Capacitor:

For perallel resonance, the capacitance C<sub>lt</sub> of the parallel capacitor is given by-

$$C_{lt} = \frac{1}{4 \pi^2 f^2 \cdot L}.$$

f being the carrier frequency of 10<sup>5</sup> c/s.

...

$$C_{1t} = \frac{1}{4\pi^2 \times 10^{10} \times 2 \times 10^{-3}}$$

Farads. = .00125 µF.

(31)

This value of Capacitance has been fulfilled by two evailable standard capacitors  $C_1$  and  $C_2$  in parallel, such that,

$C_1 = .001 \,\mu F$  and  $C_2 = 250 \,\mu F$ .

#### 3.4. LINE TUVER:

Since the line tuner must neutralize the impedance of the coupling capacitor at carrier frequency, we have-

$$\omega C = \frac{1}{\omega L_{T}}$$

where  $L_{\boldsymbol{\pi}}$  is the inductance of the line-tuner.

:

$$C = 0.1 \ \mu F = 10^{-7} \ Farads$$

:  $L_T = \frac{1}{(2\pi \ x 10^5)^2 \ x 10^{-7}}$

$$= 0.254 \text{ mH}.$$

To calculate the number of turns needed for this purpose, we have,

$$L_{T} = 1.26 \frac{MA}{l} \times N^{2} \times 10^{-5} \text{ mH}$$

or  $N^{2} = \frac{1L_{T} \times 10^{5}}{1.26 / \text{uA}}$

$= \frac{(.025)10^{5}}{1.26 \times 2.54}$  (taking A = 4 sq.inch & l=4 inches)

= 780.

... = 27 turns.

However, to make this inductor variable four tappings at intermediate values have been taken out, so that it matches the coupling capacitor perfectly. A 26 SWG wire has been used to wind the inductor.

### 3.5. CONPONENTS OF THE SERVENTIAL CIRCUIT:

3.5.1. Delta Connected Current Transformer:

Based on actual creation of fault and the calculated values of fault currents, the following current magnitudes were obtained for different faults.

| Phase to  | ground fault         | • • • | 15 Amps. |

|-----------|----------------------|-------|----------|

| Phase to  | phase <b>f</b> ault  | • • • | 25 Amps. |

| Double li | ne to <b>ro</b> und. | fault | 27 Amps. |

| Three-pha | se fault             | • • • | 30 Amps. |

Based on these values, now, a current transformation rat o of 1:5 has been chosen. Let the secondary burden for each of these C.Ts. be taken as 4 ohms maximum.

Voltage across the secondary for maximum current-

$= 6 \times 4 = 24$  volts.

For further safety, let this voltage be taken as 30volts. Then from the e.m.f. equation-

$V = 4.44 \text{ B.A.N.f.10}^{-8} \text{ Volts}$  where, N is the number of secondary turns. The flux density in lines/sq.inch. A the area of cross-section of core in sq.inches. f the frequency in cycles per second. Taking B = 45,000 lines/sq.inch A = 1 sq.inch f = 50 c/s. I =  $\frac{30 \times 10^8}{4.44 \times 45000 \times 1000} = 300.$ . Under of primary turns,  $V_p = \frac{300}{5}$ = 60.

Since the fault current is expected to flow only for a

wind the secondary. The selection of 1:50.1. ratio here, satisfies the design limits of transactors so that these need not be designed for transfer impedance of more than 4 ohms or so, which would otherwise increase the size of the transactor.

Maximum current flowing in each ".

phase of Delta connected C.C.secondary = 6 and.

. Maximum, value of the currents  $i_p, i_q$  or  $i_r$  ... =  $6\sqrt{3}$ = <u>10.4 amos</u>.

In the sequential circuit, resistance  $R_n$  has been chosen as 4 ohrs (maximum) as this will directly from the burden for 1:10.7. as shown in Fir.(2.5).

> .  $R_n = 4 \text{ ohms}$   $R_n / \frac{30^\circ}{2} = 4 (\frac{1}{2} + j \cdot \frac{\sqrt{3}}{2}) \text{ ohms}.$ = 2 + j3.46 ohms

Now, to obtain a reactance of 3.46 ohms, an iron core reactor with adjustable air-gap and 300 turns of 20510 superenammelled copper wire has been constructed.

### 3.5.2. Transactors T1, T4:

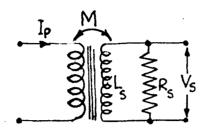

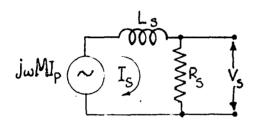

Transactor rives an output voltage ( $V_s$ ) proportional to input current ( $I_p$ ) or vice-versa. The ratio of voltage  $V_s$  to the current  $I_p$  is termed as transfor or deplice-Impedance  $Z_R$  say.

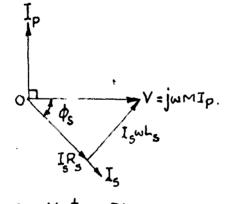

Refering to Fig. (3.1), the transactor secondary has been shown resistance loaded. Foot the diagram we can write the following equations.

1a) Circuit Diagram.

(C) Vector Diagram

Fig 31 TRANSACTOR

$$Z_{R} = \frac{V_{s}}{I_{p}} \qquad (34)$$

$$V_{s} = I_{s} \cdot R_{s} \qquad (1)$$

$$I_{s} = \frac{j \omega M I_{p} \cdot M}{R_{s} + j \omega L_{s}} \qquad (3)$$

where M is the mutual inductance between primary and secondary windings.

$$\frac{V_{s}}{I_{p}} = Z_{R} = \frac{j\omega M. R_{s}}{\sqrt{R_{s}^{2} + (\omega L_{s})^{2}} \cdot \sqrt{\beta s}}$$

$$= \frac{\omega MR_{s} \cdot \sqrt{\beta 2} - \beta_{s}}{\sqrt{R_{s}^{2} + (\omega L_{s})^{2}}} \dots (4)$$

Now, in equation (4) if  $\omega L_s \ll R_s$ , we can neglect  $L_s$  and rewrite equation (4) as-

$$\frac{V_{s}}{I_{p}} = Z_{R} = \omega_{M} / \gamma_{2} - \rho_{s} \qquad \dots (5)$$

Assuming unity coupling ratio between the two windings, we can write for mutual inductance M as-

$$M = 1.26 N_1 N_2 \cdot \frac{4A}{1} \cdot 10^{-3} \text{ Henries} \dots (6)$$

· here,

$N_1 = no.of$  turns of the primary

$N_2$  = no.of turns on the secondary

**A** = the area of crossesection of the core in  $cm^2$ and **L** = length of core in Cms.

Serlecting the phase-angle in equation (5) we have

$$M = \frac{Z_R}{\omega} = \frac{Z_R}{314} \qquad \dots \qquad \dots \qquad (7)$$

Now, voltage  $V_s$ , as applicable to the starting circuit described in Chapter 4 must be of about 20 volt magnitude. Next, the selection of  $Z_R$  will depend on the magnitude of positive sequence current and so we may write :-

$Z_{R} = \frac{V_{s}}{I_{L}}, \text{ where } I_{L}^{i} \text{ is the positive sequence currant.}$ Now, Reactance of 1:1 C.T. = j 0.3 ohms. (referred to secondary) Parallel equivalent of  $R_{n}$  and this reactance -  $= \frac{-4 \times 10.3}{4 + 30.3}$   $= \frac{.02 + 30.3 \text{ ohms}}{2 + 33.47}$ Now,  $I_{1}^{i} = I_{p} \cdot \frac{4}{6 + 33.47} + I_{r} \cdot \frac{2 + 33.47}{2 + 33.77}$ Taking  $I_{p}$  as reference,  $I_{r} = I_{p} / 120^{\circ}$  and considering the maximum value of the current:-  $I_{1}^{i} = 10.4 (0.05 + 0.5)$ or  $[I_{1}^{i}] = 5.2 \text{ amps.} \dots \dots (3)$

If current  $I_p$  is absent, as say in A-C. fault, then the fault current in the line will drop to 15 amps.:-

and

$$I'_1 = 3(\frac{2 + j3.47}{2 + j3.77})$$

or  $[I'_1] = 2.8 \text{ amps.} \dots$  (9)

Based on the above values of  $I_1'$  we obtain  $Z_R$  equal to 3.8 and 7.0 ohms respectively. However, since the starting circuit picks up even at a voltage of less than 10 volts, let  $Z_R$  be chosen as 5.0 ohms which will be well within the margin for even the least fault-current.

From equation (7) therefore,

$$ll = \frac{5.0}{314}$$

and from equation (6),

(36)

$$U_2 = \frac{\text{Nx} \text{lx} 10^8}{1.26 \text{x} \text{N}_1 \text{x} / \text{ux} \text{A}}$$

Taking a gap length of 3 mms. and area of Cross-section of the core as I sq.inch.

$$I_{2} = \frac{5 \times 10^{8} \times 0.3}{314 \times 1.26 \times N_{1} \times 1 \times 6.45}$$

=  $\frac{60 \times 10^{3}}{N_{1}}$  ... (10)

From equ tion (10),

for  $N_1 = 40$  turns,  $N_2 = 1500$  turns for  $N_1 = 50$  turns,  $N_2 = 1200$  turns and for  $N_1 = 60$  turns,  $N_2 = 1000$  turns

Super-enamelled copper wire of 18 SWG has been used to wind the primary and since a negligible current flows in the secondary, it has been wound with 30 SWG wire. Depending on the wire-size and window space available  $N_1$  has been taken as 50 and hence  $N_2$ as 1200. However, provision has been made to increase the air-gap upto 1.5 cmps, the value of  $Z_R$  decreasing for increase in the air-gap. Moreover six intermediate tappings have been taken out on the secondary, so that appropriate value of  $Z_R$  is obtained.

The above data has been described for the design of transactor  $T_1$  and the same holds cood for  $T_4$ .

## 3.5.3. <u>CTs. T<sub>5</sub> and T<sub>6</sub></u>:

As shown in Fig.(2.5) we need 1:1 CTs. in the sequence. Notwork to transfer current  $i_p$  to positive and negative sequence networks. Since a maximum burden  $R_n$  of 4 ohms is connected heross the secondary, it has been designed on the same basis.

Maximum value of  $i_p = 10.4$  amps.

. Voltage across secondary = 40 volts.

Again, taking Area A = 1" x 5/4" and B = 45,000 lines/sq.inch 40 = 4.44 x 45,000 x  $\frac{5}{4}$  x 50 x 10<sup>-8</sup> x N

$$\cdot \cdot N = \frac{160 \times 10^{\circ}}{4.44 \times 45,000 \times 250}$$

= <u>320</u>.

. Vence, both primary and secondary has been wound with 320 number of turns and a 18 SWG super enamelled copper wire has been used for winding.

### 3.5.4. <u>CTs</u>, <u>T<sub>2</sub> and T<sub>3</sub></u>:

Referring to Fig.(2.5) again, we find that the output voltage  $V_0$  depends on the way  $I_1$  and  $I_2$  are combined and also on the values of resistances r and R. This is also observed from equations (iii) and (iv) derived in Appendix.

Now, since the voltage  $V_0$  is to be fed to the squaring circuit, which also limits this voltage, its magnitude may be any where between say 10 volts and 30 volts. After booking into the various magnitudes and phase shifts in the currents  $I_1$  and  $I_2$ (for different types of faults), a CT ratio of 5:1 and a value 8 to 12 ohms for resistance R has been chosen, whereas resistance r has been made variable so that proper output is obtained with the variation in M.

(a) Considering first the transformer  $T_2$ , it is evident that its burden will depend upon the parallel combination of r and 3/2, since at the mid point of the secondary of transformer  $T_3$ , the two equi-impedence peths of R ohms each are met by the portion of  $I_1$ flowing to transformer  $T_3$ . If r is made infinite, burden on  $T_2$  will simply be 3/2 ohms and as r is decreased, this burden will go on decreasing. Keeping this in view a maximum burden of 6 ohms may be considered for the design.

Maximum voltage across secondary = 6 volts.

Again from equation for e.m.f. already used, taking A = 1 sq.inch we can write,

$6 = 4.44 \times 45,000 \times 1 \times 50 \times 10^{-8} \times N,$

$I = \frac{6 \times 10^8}{4.44 \times 45000 \times 50}$

= <u>70 turns</u>

Hence, no.of turns needed on the primary =  $\frac{70}{5}$  = <u>14 turns</u>

Super enamelled copper wire of 18 and 26 SWG has been used to wind the primary and secondary respectively.

(b) Vext, let us consider the design of C.T.T.3. It is clear from Fig.(2.5) that the burden for the secondary of this C.T. will be 23 ohms i.e. say 24 ohms.

. . Haximum voltage across secondary = 24 Volts.

Acain taking A = 1 sq.inch, we can write-

$$X = \frac{24 \times 10^3}{4.44 \times 45,000 \times 50}$$

= 280 turns

Mence number of turns on the primary = 280/5

#### = 56 turns

Super enamelled conver wire of 18 and 26 3"G has been used to wind the printry and the centre tapped secondary respectively.

It may be pointed out that such a type of centre-tapped current transformer and bridge connection has been chosen specially, in order that the feedback between positive and negative sequence outputs be avoided.

#### 3.5.5. Filty Circuit:

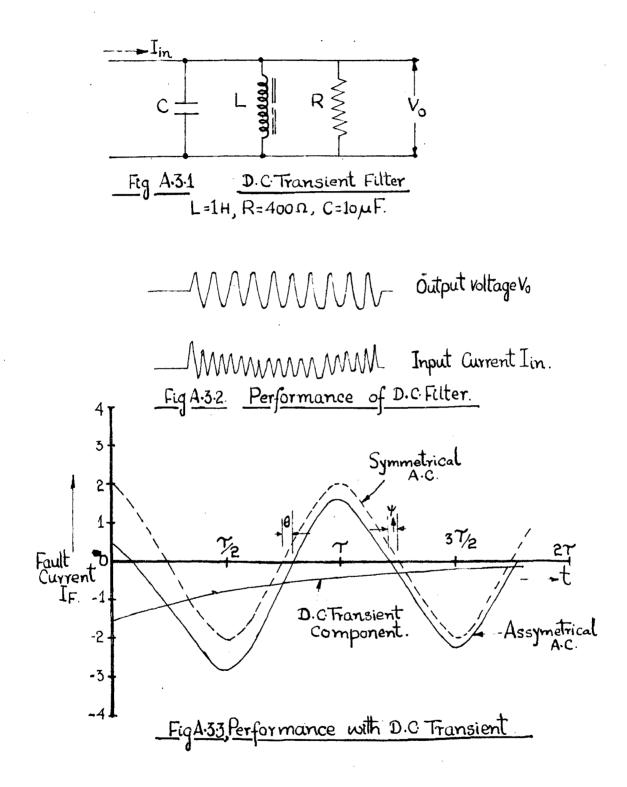

The importance of filtering the combined positive and negative sequence output has been described in Appendix A.3. Let an inductance of 1 headry be connected as shown in Fig.A.31.

The v-lue of capacitance  $C_F$  that will be needed to match this inductance at power frequency is given by:-

$$C_{\rm F} = \frac{1}{(2 \pi f)^2 \times L}$$

Farads.

=  $\frac{1}{(2 \pi \times 50)^2 \times 1}$  Farads.

=  $\frac{10}{4}$  MF

Considering the available former section of 1 sq.in. crosssection, assuming an air-cap of O.l cm. and neglecting the ampere turns for iron path, the no. of turns N needed to wind the above inductor is given by-

$$N^{2} = \frac{L \cdot 1 \cdot 10^{8}}{1 \cdot 26 / 4A}$$

$$= \frac{1 \times 0 \cdot 1 \times 10^{8}}{1 \cdot 26 \times (2 \cdot 54)^{2}}$$

= 1000,000.

$\cdot \cdot N = 1000 \text{ turns}$ .

Since the current drawn by the inductor will be very small, a 30 SWG wire has been used to wind it. A 400 ohms shunting resistor has been used, so that the time constant of the parasatic oscillation is 8 milli-seconds, i.e. less than a half cycle. 3 more tappings have been taken to suit the capicitance perfectly.

## <u>CHAPTER-4</u>

•

.

•

### TRAVSISTORISED CIRCUITS

### (40)

#### 4. TRANSISTORISED CIRCUITS:

Since the principle of transistors was discovered more than 15 years ago, there has been growing interest in this device. Experience has shown that when an application is made which keeps the transistors working inside their design limits, the reliability will be exceptionally good. It has been inevitable to consider transistors for use in power system protection as a means for increasing sensitivity, reducing operating time, and eliminating mechanical movement.

A review of the various kinds of relaying led to the conclusion that the phase comparison transmission-line protective relay offered an excellent opportunity to gain experience without introducing radically new concepts in operating principles and circuitry. The primary reasons for this are:

1. Transmission line faults occur more frequently than any other kind of fault.

2. The phase comparison relaying that was formerly used was based upon vacuum tubes, and these have met with disfavour because of their lack of reliability and tendency to change characteristics after a period of time.

An application of p-n-p type junction transistors has been made in all the terminal equipments described in the following lines. Transistors of the type 0C71, 0C76, 2SB75, 2SB77, 2N632, 2N363, 2N482, 2SA15 and 2SA12 have been used, the last two types being better suited for high frequency operation.

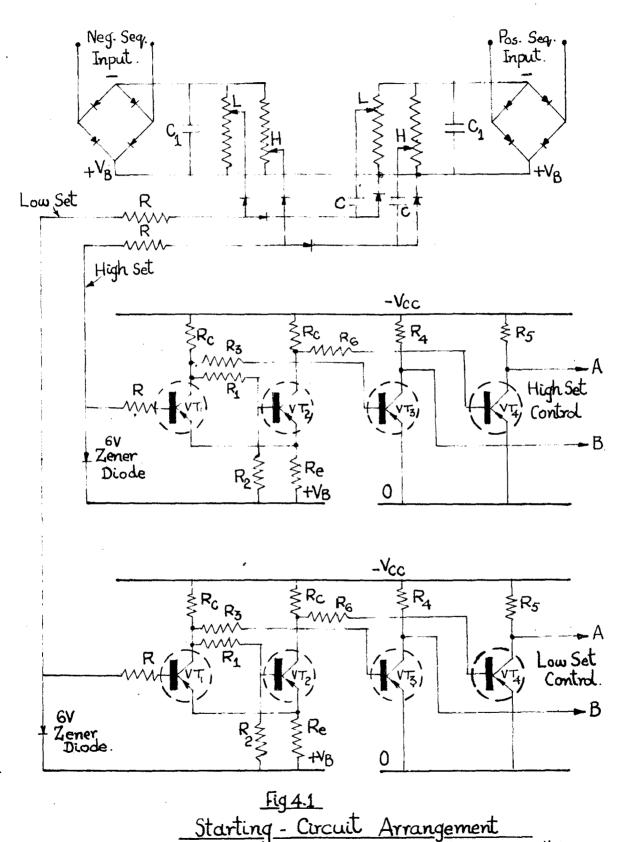

#### 4.1. THE STARTING CIRCUIT:

As mentioned earlier, the starting circuit picks up in response either to the amplitude of negative sequence component of

the fault current for an unbalanced fault, or both the amplitude and rate of rise of the positive sequence component for a balanced fault. The complete starting circuit arrangement has been shown in Fig. (4.1.), there each of the negative and positive sequence components, as produced by the sequence network of Fig. (2.5) is rectified by a full-wave rectifier bridge. The rectified d.c. outputs corresponding to the negative sequence component are taken, at high and low levels of voltage, from the potentiometers marked H and L, which controls settings, and fed directly to the low and high set starting circui's, respectively, throughisolating diodes. The rectified d.c. output corresponding to the positive sequence component are fed to pulse circuits, each consisting of a capacitor C and a discharging diode shuntin this cap citor to  $+V_{\rm R}$  supply. Any sudden change in the positive sequence input signal is instantaneously produced at the output and subsequent decay of this output takes place as the capacitor charges. The diodes shunting the capacitors to the  $+V_{2}$ supply cause them to discharge rapidly after fault clearance, thereby making pulse circuits ready to perform their functions immediately in any subsequent operation. The outputs of the impulse circuits are fed to the low and high set starting circuits through isolating diodes in the sine manner as those corresponding to the negative sequence components.

The low and high set starting circuit arrangements are identical, apart from being fed from the low and high voltage tappings, respectively on the potentiometer settings. Each circuit consists of a level detector which has been shown as a conion emitter trigger circuit, incorporating transistors  $VT_1$  and  $VT_2$  Fig.(4.1) followed by an output stage incorporating transistors  $VT_3$  and  $VT_4$ . Each level

(41)

detector and output stage uses two transistors, i.e. a total of eight transistors, together with four isolating diodes, two discharge diodes and eight diodes which form the two rectifier bridges. It may be mentioned here that with the available IM38 diodes, the rectification was not perfect and these were finally replaced by a 24 volt, selenium rectifier. The bick up and drop out voltages of the level detector have been adjusted at almost same value by inserting proper values of resistances in the emitters of transistors  $VT_1$  and  $VT_2$ .