# ADAPTIVE CONTROL OF CONVERTER FED D.C. DRIVE

### A DISSERTATION

submitted in partial fulfilment of the requirements for the award of the degree of MASTER OF ENGINEERING in ELECTRICAL ENGINEERING (Power Apparatus and Electric Drives)

P. S. PUTTASWAMY

By

DEPARTMENT OF ELECTRICAL ENGINEERING UNIVERSITY OF ROORKEE ROORKEE-247 667 (INDIA)

SEPTEMBER, 1989

#### CANDIDATE'S DECLARATION

I hereby certify that the work which is being presented in the dissertation entitled, ADAPTIVE CONTROL OF CONVERTER FED D.C. DRIVE, in partial fulfilment of the requirements for the award of the degree of MASTER OF ENGINEERING IN ELECTRICAL ENGINEERING with specialization in POWER APPARATUS AND ELECTRIC DRIVES, submitted in the Department of Electrical Engineering, University of Roorkee, Roorkee, is an authentic record of my own work carried out for a period of about seven months from August 1988 to Feb 1989 under the supervision of Dr.BHIM SINGH and Dr.AMBRISH CHANDRA, Readers in Electrical Engineering, University of Roorkee, Roorkee.

The matter embodied in this dissertation has not been submitted by me for the award of any other degree or diploma.

(CANDIDATE S SIGNATURE)

Date: 16.9.89

This is to certify that the above statement made by the candidate is correct to the best of my knowledge.

Ambrich Chandr.

Dr.AMBRISH CHANDRA Reader Department of Electrical Engg. Department of Electrical Engg. University of Roorkee Roorkee-247667

Dr.BHIM SINGH

्र वर्षे ग्र

Reader University of Roorkee Roorkee-247667

#### ACKNOWLEDGEMENTS

I wish to express my deep sense of gratitude and indebtedness to myguides, Dr.BHIM SINGH and Dr.AMBRISH CHANDRA, Readers in Electrical Engineering for invaluable assistance, excellent guidence and sincere advice given by them during this thesis work.

I am highly thankful to Dr.R.B.SAXENA, Professor and Head of the Department of Electrical Engineering, University of Roorkee, Roorkee for providing laboratory facilities.

faculty Ι much grateful to our member very am Dr.V.K.VERMA his invaluable suggestions and kind for co-operation during the work. Ι also grateful to am Mr.M.K.VASANTHA, Mr.Y.P.SINGH and Mr.PRAMOD AGARWAL for their kind suggestions.

I am highly thankful to my wife N.NALINI for her constant encouragement and co-operation during this work.

I am also thankful to P.E.S.COLLEGE OF ENGINEERING, Mandya, for sponsoring to this M.E. Course.

I am deeply grateful to all the laboratory staff for their co-operation during the fabrication of this work.

Thanks are also due to those who helped me directly or indirectly in preparing this dissertation.

(P.S.PUTTASWAMY)

#### SYNOPSIS

This dissertation deals with the experimental studies on self tuning control of a closed loop variable speed d.c. motor drive system.

A self tuning controller for speed control is developed and realised through software on IBM PC. And thyristorized three phase fully controlled converter, microprocessor controlled firing circuit, current controller (PI) and digital speed measurement circuit have been designed, fabricated and tested.

Chapter-I consists of literature review and brings out the advantages of self tuning control over other control schemes. Chapter-II gives the complete details of self tuning controller design. Chapter-III deals with the study of motor speed control and system hardware. Chapter-IV describes the system software and their flow charts. Chapter-V deals with the experimental results. In the last chapter-VI conclusions and scope of further work have been described.

# CONTENTS

|         |                                         | РА    | GE NO. |  |  |  |

|---------|-----------------------------------------|-------|--------|--|--|--|

|         | CANDIDATE DECLARATION                   | ••    | (i)    |  |  |  |

| r.      | ACKNOWLEDGEMENTS                        | ••    | (ii)   |  |  |  |

|         | SYNOPSIS                                | • •   | (iii)  |  |  |  |

| CHAPTER |                                         |       |        |  |  |  |

| 1       | INTRODUCTION                            |       |        |  |  |  |

|         | l.l General                             |       | 1      |  |  |  |

|         | 1.2 Literature Survey Review            | ••    | -      |  |  |  |

|         | 1.2.1 Adaptive control schemes          | • •   | 5      |  |  |  |

|         | 1.2.2 Firing and control schemes        | ••    | 8      |  |  |  |

|         | 1.3 Scope of the Present Work           | ••    | 13     |  |  |  |

|         | 1.4 Outline of Chapters                 | ••    | . 14   |  |  |  |

| 2       | ADAPTIVE CONTROLLER                     |       |        |  |  |  |

|         | 2.1 General                             | ••    | 16     |  |  |  |

|         | 2.2 System Model                        | ••    | 16     |  |  |  |

|         | 2.3 Test Signals                        | ••    | 18     |  |  |  |

| •       | 2.4 System Identification               | ••    | 19     |  |  |  |

| • • = • | 2.5 Control Stratagies                  | • • • | .23    |  |  |  |

|         | 2.6 Self Tuning Control                 | ••    | .24    |  |  |  |

|         | 2.7 Algorithm                           | ••    | 25     |  |  |  |

|         | 2.8 Conclusions                         | • •   | 26     |  |  |  |

| 3       | HARDWARE IMPLEMENTATION                 |       |        |  |  |  |

|         | 3.1 General                             | ••    | 28     |  |  |  |

|         | 3.2 System Description                  | •, •  | 28     |  |  |  |

|         | 3.3 Based Self Tuning Controller        | ••    | 30     |  |  |  |

|         | 3.4 Power Circuit and Its Working       | ••    | 30     |  |  |  |

|         | 3.5 Microprocessor Based Control Scheme | ••    | 2      |  |  |  |

|         |                                         |       |        |  |  |  |

2

Contd..

CHAPTER

4

· · -

ş

|                |       | 3.5.1             | Synchronizing technique                 | • • | 36              |

|----------------|-------|-------------------|-----------------------------------------|-----|-----------------|

|                |       | 3.5.2             | Pulse amplifier circuit                 | ••  | 38              |

|                | 3.6   | Conclus           | sions                                   | • • | 39              |

|                | SYST  | em softv          | VARE IMPLEMENTATION                     |     |                 |

|                | AND 2 | FLOW CHA          | ARTS                                    |     |                 |

| и              | 4.1   | General           | L                                       | ••  | 40              |

|                | 4.2   |                   | re Implementation of Self<br>Controller | ••  | 40 -            |

|                | 4.3   | Softwar<br>System | ce for 8085 Microprocessor              | ••  |                 |

|                |       | 4.3.1             | Main program                            | ••  | 41              |

|                |       | 4.3.2             | Closed loop initialization              | ••  | 44 <sup>·</sup> |

|                |       | 4.3.3             | ADC Subroutine                          | ••  | 44              |

| ۰ <sup>۲</sup> |       | 4.3.4             | Constrained current error subroutine    | • • | 46              |

|                |       | 4.3.5             | PI current controller<br>subroutine     | ••  | 47              |

|                |       | 4.3.7             | Constrained voltage subroutine          | • • | 50              |

|                |       | 4.3.8             | Look up subroutine                      | • • | 51              |

|                |       | 4.3.9             | mode selection subroutine               | • • | 54              |

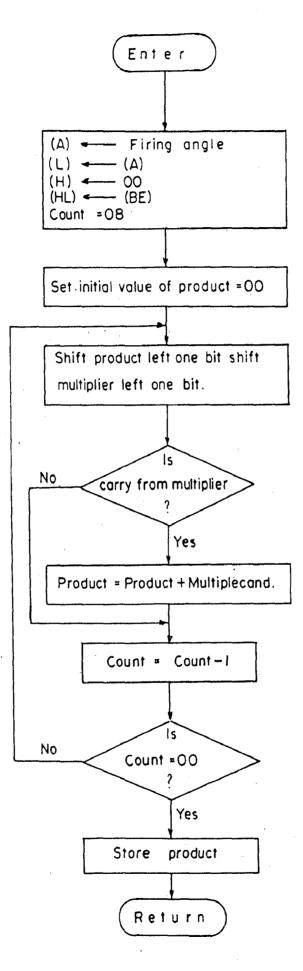

|                |       | 4.3.10            | Multiplication subroutine               | • • | 55              |

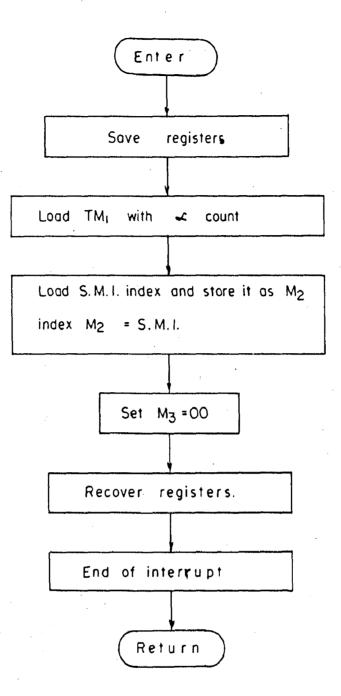

|                | · -   | 4.3.11            | IR interrupt subroutine                 | • • | 55              |

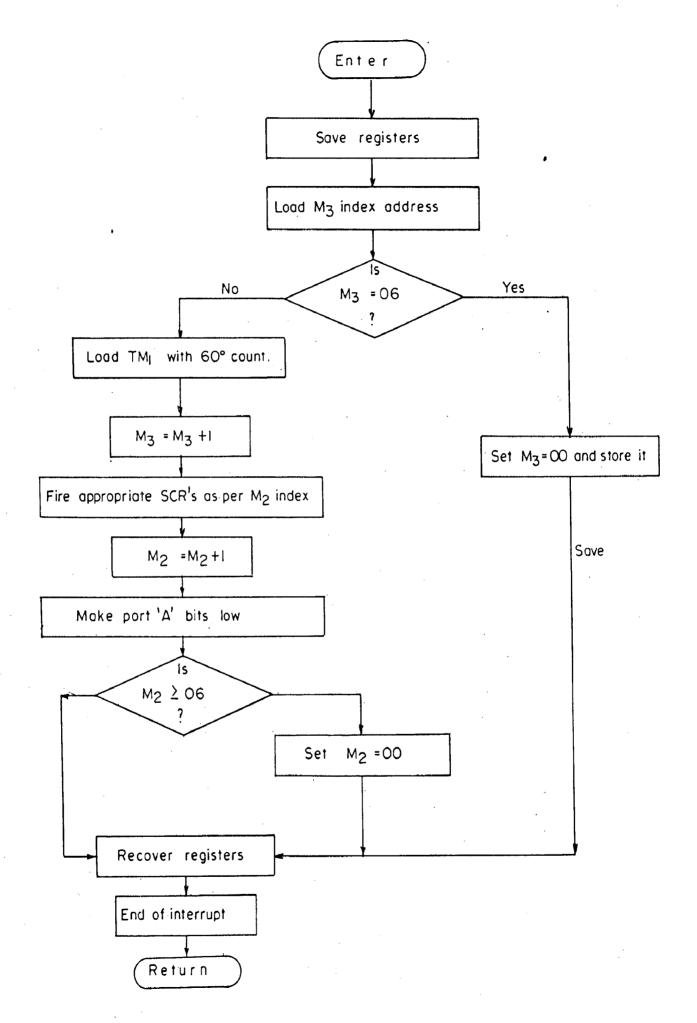

|                |       | 4.3.12            | IR <sub>1</sub> interrupt subroutine    | ••  | 56              |

|                | 4.4   | Conclu            | sions                                   | ••  | 57              |

|                | PERF  | ORMANCE           | OF THE SYSTEM                           |     |                 |

|                | 5.1   | Genera            | 1                                       | ••  | 59              |

|                | 5.2   | Experi            | mentation                               | ••  | 59              |

|                | 5.3   | Discus            | sion of Results                         | ••  | 61              |

|                | 5.4   | Conclu            | sions                                   | ••  | 63              |

|                |       |                   |                                         |     |                 |

|                |       |                   |                                         |     |                 |

6

|        | CONCLUSIONS AND SUGGESTIONS FOR<br>FURTHER WORK |    |  |  |  |  |  |  |

|--------|-------------------------------------------------|----|--|--|--|--|--|--|

| 6.1 Ma | in Conclusions                                  | 65 |  |  |  |  |  |  |

| 6.2 Su | ggestions for Further Work                      |    |  |  |  |  |  |  |

|        |                                                 |    |  |  |  |  |  |  |

| APP.A  | Chip Details                                    |    |  |  |  |  |  |  |

| APP.B  | Pin Details                                     | :  |  |  |  |  |  |  |

| APP.C  | PI Controller Design                            |    |  |  |  |  |  |  |

| APP.D  | STC Software                                    |    |  |  |  |  |  |  |

| APP.E  | μp Software Program                             |    |  |  |  |  |  |  |

| APP. F | MP and its PeriPherials.                        |    |  |  |  |  |  |  |

| REFERE | NCES                                            | 69 |  |  |  |  |  |  |

#### CHAPTER-1

#### INTRODUCTION

#### 1.1 GENERAL

Many modern variable speed drives require a precise and smooth control of speed with longterm stability and good transient performance. From the very beginning, the conventional d.c. motors have been used as variable speed drives in many industrial applications due to the following\_ advantages.

- D.C. motors can provide high starting torque which are required for several applications such as traction drives.

- (ii) D.C. motor's speed can be controlled easily over a wide range both below and above rated speed.

- (iii) The methods of control are similar and less expensive than those of a.c. motors.

In modern d.c. drives, the classical motor-generator set has been replaced by a solidstate controlled d.c. drive which has numerous advantages such as minimum maintenance, less bulk and weight, higher efficiency, faster time response and above all low cost[1].

For a reversible drive with continuous speed control over a wide range, the d.c. motor drive is the most popular solution. The speed of the d.c. motor can be controlled by controlling either armature voltage or the field current. Former is for speed control below the rated value and the latter is for speed control above the rated value of speed of the motor. D.C. motors can closely match the needs of the application as the speed-torque characteristics can be varied to any useful form, for both motoring and regenerating applications. Dynamic or regenerative braking is easily obtainable with the d.c. motors for application, requiring quick stopping or speed reversals.

As mentioned earlier, d.c. motors are easily adaptable to variable speed drives. The speed characteristics of a seperately excited d.c. motor is given by

$$N = (V_a - I_a R_a) | KI_f$$

The seperately excited d.c. motor is rapidly and efficiently controlled by the variation of armature voltage and field current.

Solid state controllers enable in developing more accurate, efficient and compact control scheme for d c. motors [1.2]. In addition they help in obtaining variable characteristics of these motors. The conventional methods of speed control are gradually being replaced by thyristor control. The use of thyristors for power control affords considerable advantages over conventional methods owing to the possibilities of obtaining better economy, efficiency.

reliability fastness facilities and their compatibility to adopt for closed loop system of speed control.

Now a days, the speed control of a d.c. drives is also tried with adaptive controllers. Adaptive control has been a challenge for control engineers for a long time [3]. It has been their dream for more than a quarter of a century. It arose from a desire and need for improved performance of complex engineering systems with large increasingly uncertainties. This is specially important in system with many unknown parameters that change with time. An adaptive system is one that continually monitors the changes and adjusts the control parameters automatically to maintain good performance. Hence, adaptive systems can be considered as a class of control systems that have been made deliberately non-linear.

The tuning problem is one reason for using adaptive control. It is a well known fact that many processes can be regulated satisfactorily with proportional integral (PI) or proportional integral derivative (PID) regulators. It is fairly easy to tune a PI regulator which only has two parameters to adjust. However, for an installation which has several hundred regulators, it is a substantial task to keep all regulators well tuned. A PID regulator which has three or four parameters is not always easy to tune particularly if the process dynamics is slow. The derivative action is

therefore frequently switched off in industrial controllers. Since many control loops are not critical, three term controllers will be extensively used in future too.

Conventional control theory deals with the control of dynamical systems whose mathematical representations are completely known. In contrast to this adaptive control it refers to the control of partially known systems. For many years, there has been an increasing interest in adaptive control which can be attributed to the fact that there is invariably some uncertainity in the dynamic characteristics of most practical systems. The tools of conventional control theory, even when used efficiently in the design of controllers for such systems, are inadequate to achieve satisfactory performance in the entire range over which the characteristics of the system vary.

While feedback, in general, improves the performance of a system it could also make the system unstable [3]. Since adaptive control systems are non-linear feedback systems, there is the distinct possibility that such system can become unstable.

Research on adaptive control was very active in the fifties. It was motivated by the need of autopilots for high performance aircraft. The work was characterized by a lot of enthusiasm, bad hardware, and nonexisting theory. Interest in the area diminished due to lack of well developed stability theory and a fight disaster. Due to some recent developments

in the stability theory of such systems, the application of adaptive control to practical systems is being attempted on a large scale [3,4].

#### 1.2 LITERATURE SURVEY REVIEW

#### 1.2.1 Adaptive Control Schemes

The adaptive control of systems has been a dream of control system theorists and practitioners for atleast a quarter of a century. In the past decade the progress of adaptive control has been slow in coming to fruition. The early schemes for adaptive control, though ingeneous, did not gaurantee the stability of the system. Globally stable adaptive control algorithm have been developed very recently. With recent advances in microprocessor technology, it has become feasible to implement adaptive control algorithms efficiently in real time at reasonable cost.

To understand the recent developments in theory and the keen interest shown by industries in adaptive control promoted to organise the workshop on applications to the adaptive cotrol. Many workshops have been held to bringout the fruitful application [3].

Clarke and Gawtrop [5] have discussed the closed loop properties of various classes of selftuner, convergence concepts and results. They have suggested a new technique to design a selftuning controller which does not appear to suffer excessively from the disadvantages of previous adaptive methods. Some of the technical problems involved with implementing selftuners on small computers or microprocessors are also discussed.

6

have discussed a selftuning Allidina and Hughes [6] controler that minimises cost function incorporating system input, output and setpoint variations, and adapts in such a way that the closed loop poles are located on prespecified locations. The link between classical control strategy of pole assignment and the suboptimal strategy of the selftuning demonstrated and made use to produce controller is generalised controller which possesses the advantages of The proposed controller combines the robustness of a both. pole assignment regulator with the ease of reference tracking. Simulation methods for first and second order systems are also discussed.

Gawtrop [7] has discussed the design of selftuning controller including rational transfer function terms in the associated cost function. Two interpretations of the selftuning controller, a model reference adaptive control and a selftuning least square predictor in conjunction with conventional compensation are examined in detail. Using standard form of techniques, the discrete time systems with step responses are determined. The proposed controller shows the advantages over Smith Control law. Brickwedde [8] has discussed the application of microprocessor based adaptive control for electric drives. For its implementation as an on-line adaptive control system, the recursive least squares algorithm for the on line parameter identification combined with a pole assignment procedure is suggested. The proposed controller is implemented on a 16 bit microprocessor to control the speed of a 40 k.w d.c. drive. Experimental results of a drive under load conditions are also discussed.

A robust selftuning controller that can track a constant reference and rejects load disturbance developed by Balasubramanian and Kong Hung Wong [9], proposed controller is implemented on a microprocessor to control the speed of a d.c. motor under varying load and operating conditions. Experimental results are also discussed, which confirm the controller excellent adaption capability as well as transient recovery under load changing conditions.

Stephan et.al. [10] have discussed a cascade speed control strategy for a thyristor fed d.c. motor subjected to parameter variations. This is called as dual mode used with inner current loop and outer speed loop. The scheme is implemented on a 16 bit microprocessor using a floating point coprocessor to control the speed of a l.l k.w d.c. motor, and experimental results are also given. The proposed controller makes the behaviour of armature circuit practically

independent of the current conduction mode. Response is extremely fast and it gaurantee the stability and predefined performance under all operating conditions.

Liu et.al. [11] have discussed a controller design based on the placement of poles and zeros of the state tracking error transfer function. The problem formulation, parameter and state estimation, considering noisy and noise free systems are discussed. The proposed self tuning control is found very effective for both regulation and reference tracking signal.

A common problem in the d.c. motor drives is torque saturation. In order to overcome this, a generalised predictive control is suggested by Tsang and Clarke [12], which, shows improvements in performance without major increase in computations.

Cluett et.al. [13] have discussed the consolidation of stability and robustness results based on input-output theory for discrete adaptive control systems. In this, an algorithm for a generic direct discrete time adaptive controller is presented. To obtain the stability of the system normalisation, and weighting of the polynomials are suggested.

#### 1.2.2 Firing and Control Schemes

Ilango et.al. [14] have discussed the compact firing'

scheme for three phase bridge rectifiers using minimum integrated circuit components. The proposed scheme had shown fast response for triggering angle and gives a fullrange of voltage, because the response of the firing angle to control voltage is almost instantaneous.

Alimirbod and Ahmed el-amawy [15] discussed a general purpose microprocessor based control circuit for a three phase controlled rectifier. For the proper operation of controlled rectifiers, the gating patterns are synchronized with the zero crossing of line to line voltage by properly compensating the effect of source impedance by compensation circuit. The proposed controller exihibited superior performance to previously presented circuits. The hardware and software implementation on 8086 microprocessor are discussed.

A firing scheme based on microprocessor to control an antiparallel connected 3 phase thyristor dual converter is discussed by Tang et.al. [16]. Look up algorithm is used to speed up the response, which gives full range control of the firing angle between  $0-180^{\circ}$  for both positive and negative current control. The proposed scheme is reported to give good dynamic response and high system reliability.

Independently of the method of algorithm used to control thyristor firing of a three phase static converter, the signals that synchronize them with a.c. supply are always

necessary. A microprocessor based scheme is proposed [17] for this purpose. This scheme is tested as a part of the complete digital current control system feeding a 5 k.w d.c. motor also in a rectifier system fed by a 13 KVA synchronous generator. The results obtained are very good, and for a self controlled synchronous motor system, this scheme is more precise than a set of selective filters.

Remy Simard and Rajagopalan [18] have discussed a simple equidistant pulse firing scheme. The proposed scheme is economical to use with individual phase control circuits for industrial applications. Experimental results obtained on a laboratory d.c. drive are also discussed.

El-Bolok [19] has described a novel microprocessor based scheme for constant angle triggering operating under a variable anode frequency, in which the triggering angle is controllable by software. Implementation and testing of this scheme had shown a fast response to changes in anode supply frequency. This scheme is not affected by the number of phases of the supply voltage and/or its phase sequence.

Mario Benedetti and Carlos F. Christiansen [20] have described the design of a trigger system for full or half controlled thyristor converter upto 6 pulses using 8 bit microprocessor. This scheme provides more flexibility in which the triggering angle may take any value from 0 to 180° between pulses, thus achieving the maximum rate of change of

the output voltage. The necessary hardware is also reduced to minimum. The design procedure and experimental setup are discussed.

Thadiappan Krishnan and Bellamkonda Ramaswami [21] proposed the design construction and testing of thyristorized speed control unit for a seperately excited d.c. motor. The motor is fed from a three phase six pulse fully controlled thyristor bridge. The speed and current loops are used to maintain the desired speed and to provide fast response overcoming the effect of disturbances. But this scheme is useful for only one direction of rotation.

Soon Chan Hong and Min ho Park [22] have described a . method to improve the efficiency of d.c. motors based upon the field control. The power circuits and the control loops are suggested to realise the principle, and the real time control is implemented with a microprocessor. Experimental results had shown the remarkable improvement in efficiency as - well-as stability. -

Sule et.al. [23] have proposed a digital speed control system for a d.c. motor with a pulse tachogenerator for speed sensing. The scheme provides a fast and accurate digital speed measurement and control by means of a microprocessor system. The measurement accuracy obtained is  $\pm$  0.0125 percent with reference to maximum speed and the time constant is approximately 8 m.s.

Plant et.al. [24] have proposed a suitable method for microprocessor implementation of controlling the speed of an S.C.R. controlled d.c. motor drive which uses a halfwave single phase supply, and realisation by a microprocessor. The determination of the necessary control requires only table look up operations and computations are kept minimum. The control algorithm, using the table look up, becomes simple, meets the real time requirement, and its implementation is well within the capability of the present day microprocessors. Experimental results of a 3HP d.c. motor. control are also discussed.

Guyolvier et.al. [25] have discussed the operation of the modified thyristor bridge converter, the control algorithm and microprocessor implementation. The proposed scheme is shown to have faster response, precise and equidistant control of the thyristor triggerings.

Verma and Agarwal [26] have described the design and experimental studies of variable d.c. drive, fed from a single phase dual converter. The drive incorporates an inner current loop (PI) and outer speed loop (PI). The analytical and experimental studies had shown good transient and steady state drive performance.

Tadashi Egame and Takeshi Tsuchiya [27] have discussed a partial state and an output feedback control system synthesis method with feedforward compensation. It

doesn't make use of the state observer procedure. The proposed scheme can be applied to all control systems and its effectiveness tested experimentally.

Nandam and Sen [28] have discussed the comparative study of proportional and integral proportional schemes, for the speed control of a d.c. drive using both analog and microprocessor based digital system. It is confirmed that IP control has distinct advantages over PI control. Experimental and simulation results are discussed.

1.3 SCOPE OF THE PRESENT WORK

The exhaustive literature survey reveals that little research work has been reported on the performance of converter fed d.c. drive using adaptive controller. Therefore, a need is felt to investigate the variable speed operation and performance of a adaptive control of the d.c. drive.

In the proposed scheme, a three phase a.c. supply of fixed frequency and voltage is converted into a variable voltage d.c. supply which is being fed to a d.c. motor. The commutation of thyristor converter is achieved by line commutation. Self tuning controller suggested by Clarke and Gawtrop [5] is used to control the speed of a d.c. drive.

The objectives of the proposed work are the following:

- (i) To design a self tuning controller for the speed control of a d.c. drive.

- (ii) To design and develop a suitable firing scheme and control schemes for operating the converter.

- (iii) To design proportional plus integral control for current loop processing.

- (iv) To study the feasibility of the whole system as a variable speed drive and to obtain experimentally its no load and load characteristics.

The whole scheme has been fabricated and tested in a laboratory and the performance of the motor is obtained experimentally.

#### 1.4 OUT LINE OF CHAPTERS

In Chapter-II, the various aspects of different types of adaptive controllers are described. The algorithm involved in the design of self tuning controller is also discussed.

In Chapter-III, the complete hardware of the present scheme is described in detail. The design of power circuit, microprocessor based firing control circuit using reduced hardware components and pulse amplifier circuit are also given in this chapter.

The implementation of software and flow charts of the

seperately excited d.c. motor speed control is illustrated in Chapter-IV. The various subroutines used in conjunction with the main program such as ADC subroutine, MODE selection subroutine, MULT subroutine, SMULT subroutine, PI processing subroutine  $V_{dc}^*$  CONSTRAINED subroutine, IR<sub>0</sub> interrupt subroutine, IR<sub>1</sub> interrupt subroutine are also developed in this chapter.

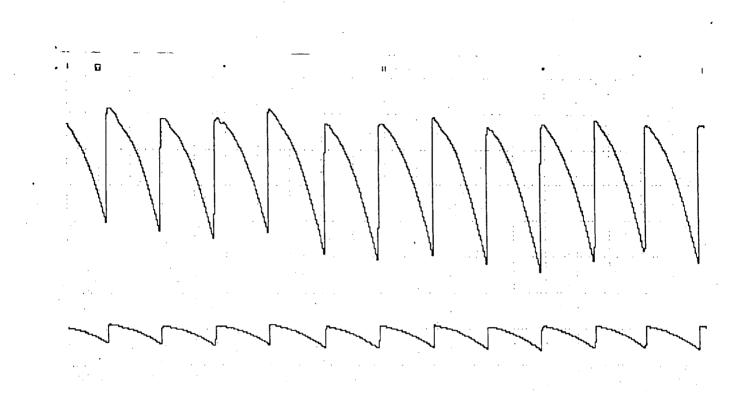

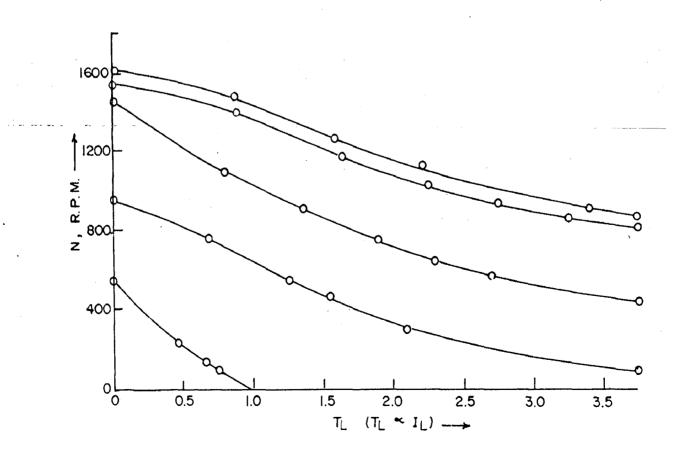

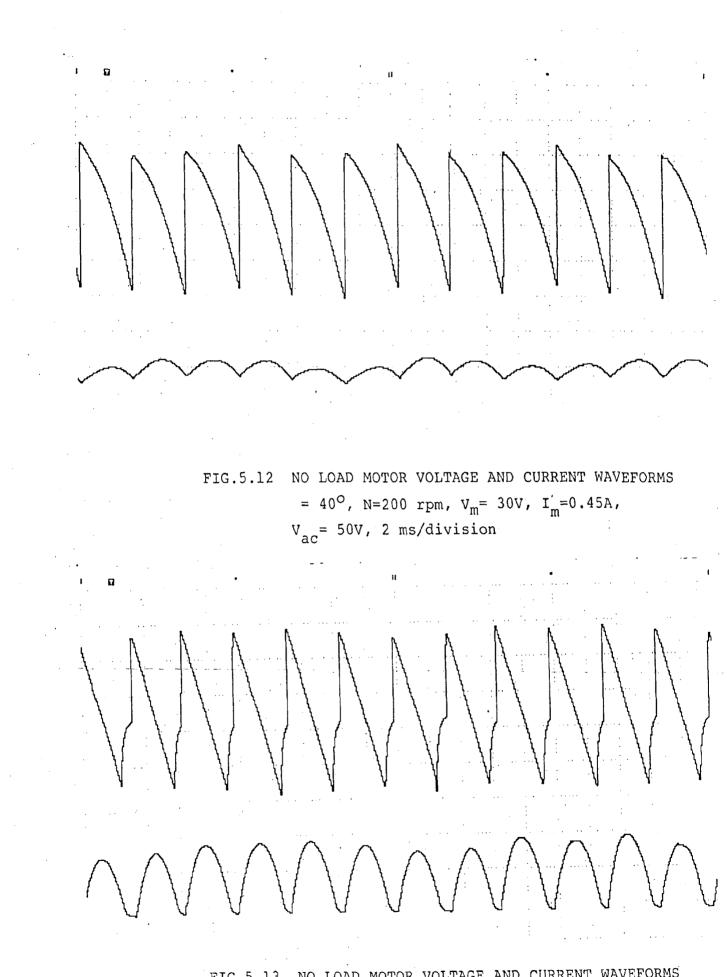

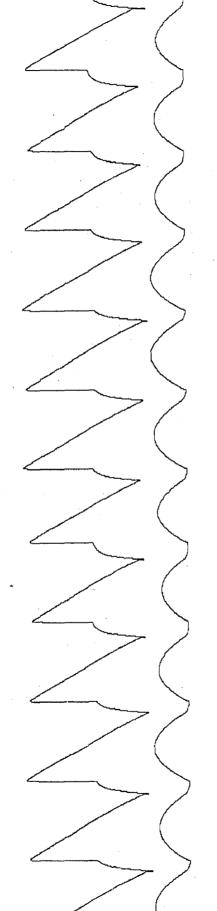

The behaviour of a drive on no load as well as on load condition is described in detail along with the performance characteristics in Chapter-V.

The suggestions are proposed to improve the drive performance is given in Chapter-VI.

The pin detail connections and function of various chips, the design of PI controller for current loop, basic language program for the selftuning controller and machine level language program for microprocessor system are given in appendices.

#### CHAPTER-2

#### ADAPTIVE CONTROLLER

#### 2.1 GENERAL

Different types of controllers are suggested in literature to control the speed of a d.c. motor. In this work, adaptive selftuning controller (STC) is used for this purpose. An adaptive controller is one that continuously monitors the change in system parameters and adjusts its control parameters automatically to give good performance. In this chapter, selftuning controller algorithm is discussed in detail.

#### 2.2 SYSTEM MODEL

A physical object, in whose behaviour we are interested in studying, affecting or controlling is known as system. The knowledge of the properties of a system is generally called a model. The concept of a mathematical model is necessary when complex problems are treated. A mathematical model of a given system can build up by two approaches. In the first approach, by looking directly into the mechanisms of the system that generate signals and variables inside the system and construct a mathematical model. In second approach, knowledge of the systems mechanism is incomplete or system properties are inpredictable, in those cases, signals produced by the system can be measured and be used to construct a mathematical model.

A practical system can be either single input/single output or multi input/multi output. But as for as d.c. motor is concerned, it can be regarded as single input/single output. Therefore, in this investigation, only the single input single output system is discussed. The mathematic modelconsidered, in this work, is of the discrete form (difference equation) due to digital computer application. Many types of discrete mathematical model such as ARMA (Auto Regressive Moving Average), ARMAX (Auto Regressive Exogeneous), and LR (Linear Regression) are used in adaptive control techniques. ARMA model is not suitable for the present problem because it has no control over input. ARMAX model which uses the principal property of Recursive least square identification is not holds good because the prediction error is Therefore uncorrelated. to overcome this difficulty, 'Recursive extended Least squares' (RELS) identification is used with this type of model. RELS is not robust as that of RLS and the convergence can not be proved for all cases, it also increases the computational burden and hence it may create problems in real time implementation. That is why linear regression model is considered here due to its suitability and simplicity.

The system model is assumed to be of the form

$$A(Z^{-1}) y(t) = Z^{-k}B(Z^{-1}) u(t) + \xi(t)$$

.. (2.1)

Where A and B are polynomials in  $Z^{-1}$  (backward shift operator) defined as

$$A(Z^{-1}) = a_{0} + a_{1}Z^{-1} + \dots + a_{n_{a}}Z^{-n_{a}}$$

$$B(Z^{-1}) = b_{0} + b_{1}Z^{-1} + \dots + b_{n_{b}}Z^{-n_{b}}$$

Where  $n_a$  and  $n_b$ , are the orders of polynomials A and B respectively. K represents the system time delay in sample ~ intervals. y and u are the system output and input, with  $\xi(t)$  an uncorrelated random sequence of zero mean which disturbs the system.

#### 2.3 TEST SIGNALS

To obtain the information about the system and to identify it, the system should be excited by some input signal. Several researchers have treated the design of input signal for enhancing the parameter estimation for discrete time processes used in adaptive control techniques. The input signal should excite all models of the system to guarantee, the estimated parameters converge to the reasonably correct values. The signal having this quality is called 'rich enough' (having sufficiently rich frequency content) or persistently existing.' While doing literature survey it is found that most of researchers have considered white noise as a suitable signal. Hence, in this work, white noise is chosen for excitation purpose [5].

#### 2.4 SYSTEM IDENTIFICATION

The type of a model mainly depends upon the method of identification. identification of a system model The provides the essential aspects of an existing system and represents the knowledge of that system in useful form. Identification may be either 'on-line' (recursive) or 'off-line' algorithm. On-line identification has two main disadvantages in comparison to 'off-line' identification. Firstly, a decision must be made regarding the structure of the model before starting the identification. Secondly, since 'off-line' methods can reprocess data many times, they are more accurate than recursive methods. Recursive least square identification algorithm is the most popular technique which has been used successfully in many applications. Therefore, in the thesis, this algorithm has been used and is briefly discussed below.

The RLS identification technique is mainly used to treat the LR model (eqn.2.1) defining the parameter vector:

$$\hat{\Theta}^{T}(t) = [a_{1}, \dots, a_{n_{a}}, b_{0}, b_{1}, \dots, b_{n_{b}}] \dots (2.2)$$

and  $x^{T}(t) = [-y(t-1), \dots, -y(t-n_{a}), u(t-k), \dots, u(t-k-n_{b})] \dots (2.3)$

Vector containing measured data.

Vector containing measured data.

Therefore, the equation (2.1) can be written as:

$$y(t) = \hat{\Theta}^{T}(t) x(t) + \not \in (t)$$

... (2.4)

Let y(t) be an estimate of y(t) based on  $\hat{\theta}(t)$  and x(t) and it is as:

$$\hat{y}(t) = \hat{\Theta}^{T}(t) x(t)$$

... (2.5)

There may be an error in the estimation because the data may be complicated by random measurement of noise, error in the model or combination of both. It is given by:

$$\xi(t) = y(t) - \hat{y}(t) = \xi(t)$$

.. (2.6)

Now  $\hat{\theta}$  is chosen in such a way that the criterion J is minimized.

$$J = \sum_{t=1}^{m} \epsilon^{2}(t)$$

... (2.7)

Expressing  $J = (y - \hat{\Theta}^T x)^T (y - \hat{\Theta}^T x)$

$$y^{T}y - y^{T}\hat{\Theta}^{T}x - x^{T}\hat{\Theta}y + x^{T}\hat{\Theta}\hat{\Theta}^{T}x$$

where

$X = \begin{bmatrix} x^{T}(t) \\ x^{T}(t+1) \\ \vdots \\ \vdots \\ x^{T}(t+m) \end{bmatrix}$

$$-y(t-1) \dots -y(t-n_{a}), u(t-k) \dots u(t-k-n_{b})$$

$$-y(t) \dots -y(t-n_{a}+1), u(t-k+1) \dots u(t-k-n_{b}+1)$$

$$\vdots$$

$$-y(t+m-1) \dots -y(t-n_{a}+m-1), u(t-k+m-1) \dots u(t-k-n_{b}+m-1)$$

and

a da ser a ser

$$Y = [y(t), y(t+1), \dots, y(t+m)]^{T}$$

$$m = number of samples$$

$$\frac{\delta J}{\delta \hat{\Theta}} = -2 x^{T} y + 2 x^{T} x \hat{\Theta} = 0$$

$$x^{T} x \hat{\Theta} = x^{T} y$$

$$\hat{\Theta} = (x^{T} x)^{-1} x^{T} y$$

...(2.8)

The above result represents the least square estimator of  $\theta$ , and the least square estimates can be computed recursively as:

$$\hat{\Theta}(t) = \hat{\Theta}(t-1) + k(t) [y(t) - \hat{\Theta}^{T}(t-1) x(t)]$$

.. (2.9)

$$k(t) = \frac{P(t-1) x (t)}{[1 + x^{T}(t) P(t-1) x(t)]} \dots (2.10)$$

$$P(t) = [1 - k^{T} x(t)] P(t-1) \dots (2.11)$$

where k(t) is considered as the gain matrix and P(t) is proportional to the error covariance matrix.

From equation (2.9) it is evident that the estimated parameter  $\hat{\Theta}(t)$  is the weighted sum of the last. estimation and prediction error  $\in (t)$ . As time increases, in case of

time in-variant system  $\Theta(t)$  converges to its true value along with prediction error  $\in (t)$ , gain vector k(t) and covariance matrix P(t) tend to zero. But this new information is not making any contribution to the parameter estimation. In time variant system, if the estimated parameter reach its true value once the above problem is eliminated, but affects the parameter tracking.

The algorithm which is derived above based on criterion J considering equal weightage for every error. -For time varying system the above criterion gives an estimate of the average behaviour during the period  $1 \le t \le m$ . As the time increases the number of measurements becomes very large and the contribution of each individual measurements to the parameter estimation tends to zero.

In order to increase the tracking capability, it is necessary to consider a criterion in which older values are discounted by an exponential weighting scheme which places heavy emphasis on more recent data.

Consider a criterion

$$J = \sum_{i=1}^{m} \beta^{n-i} t^{2}(i), \ 0 < \beta < 1$$

In this criterion the later errors are given more weight than earlier ones.

Therefore, the algorithm explained above can be modified by changing equation (2.11) to

$$P(t) = \frac{[1-K^{T}(t) x(t)] P(t-1)}{\beta} \qquad .. (2.12)$$

If  $\sqrt{3} < 1$  then P(t) will not tend to zero and the algorithm is more capable of tracking the parameter variation.

#### 2.5 CONTROL STRATAGIES

1)

Adaptive Control can be classified into two categories Model reference adaptive control (MRAC)

• •

2) Self tuning control (STC)

The choice of reference model is the first step in case of MRAC. The controller parameters are adjusted so that the output co-ordinate of the system agrees with that of the reference model. To perform parameter adjustemnt the value of mismatch between the controlled co-ordinates of the system and the model is to be used. The main problem associated with MRAC is that, to obtain a closed loop response, the system zeros must be cancelled by controller poles. Hence it 'is not useful for the systems outside the stability region [6]. It is also found that the discrete time cancellation of zeros by poles that correspond to oscillatory continuous time functions can lead to unacceptable intersample behaviour. Therefore this technique is not very much suitable for d.c. motor systems.

The STC consisting with two loops an inner loop or the control loop and an outer loop that adjusts the control

parameters in the inner loop. STC deals with discrete systems and is applicable to a wider class of problems though the stability of such schemes may be harder to prove. Self tuning controller gained more popularity because of some advantages over MRAC. In this thesis self tuning controller [5] is used and here it is discussed in detail.

#### 2.6 SELF TUNING CONTROL

Kalman probably was the first to propose selftuning under the title 'self optimizing'. It had little immediate consequence at the time due to lack of suitable technology. Moreover, MRAC could be implemented using analog hardware encouraging more work on its development. With the development of microprocessor technology there have been stimulating developments in self tuning control, although no guarantee that self tuning would be successful in practical applications, because the theory is proven for small cases only and even under the favourable conditions there is no guarantee of convergence.

with Even the incompleteness of established theoritical results, there is a development work on selftuning controller. The popularity of this control can be gauged from the number of paper published and the succesful applications reported in the literature. Now а days selftuning controller is mostly preferred because of the following reasons:

- i) The algorithms used are very simple.

- ii) It is derived in discrete form which can be readily implemented on microcomputers.

- iii) It has been found possible to establish some theoretical results which, although incomplete indicate that satisfactory stable performance can be expected.

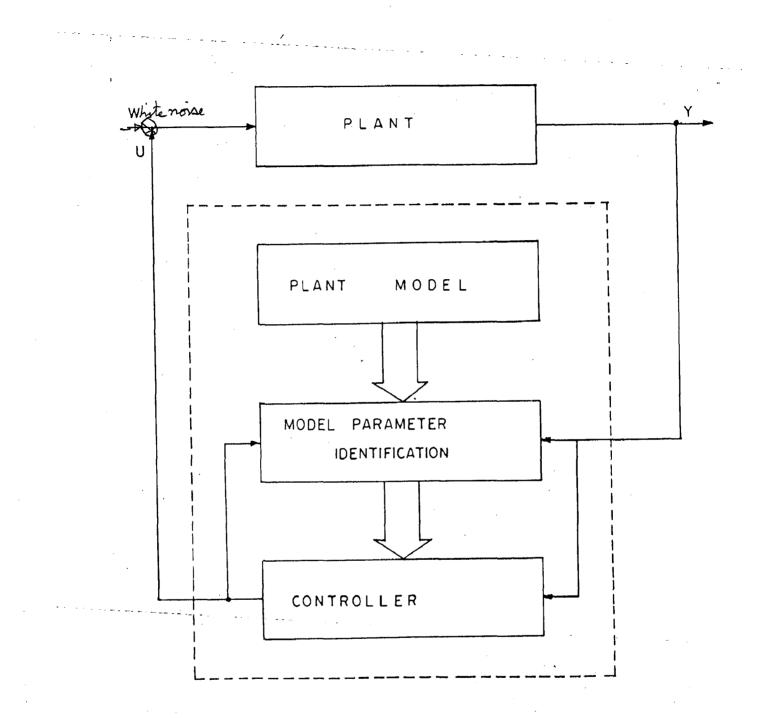

The controlled system parameters are identified in these techniques, on line and the control is calculated using a preselected strategy as shown in Fig. 2.1.

### 2.7 ALGORITHM

The algorithm for the generalised selftuning controller [5], used in this work can be summarized as follows:

- i) Form a generalised cost function (k=1)  $\phi(t) = Py(t) + Qu(t-1) - Rw(t-1)$

- ii) Estimate the control parameters,  $\Theta(t)$  by a standard recursive least square algorithm

- $\hat{\Theta}(t) = \hat{\Theta}(t-1) + k(t) \left[\phi(t) \hat{\Theta}^{T}(t) x(t)\right]$

$$k(t) = \frac{P(t-1) x(t)}{[1 + x^{T}(t) P(t-1) x(t)]}$$

$$P(t) = \frac{[1 - k^{T}(t) x(t)] P(t-1)]}{\beta}$$

# FIG.2.I BLOCK DIAGRAM OF A SELF TUNING CONTROLLER.

where

$$\theta(t) = [h_0, h_1, \dots, h_{n_H}, g_0, g_1, \dots, g_{n_G}, e_0, e_1, \dots, e_{n_E}]$$

h, g and e are the co-efficients of the general polynomials  $H(z^{-1})$ ,  $G(z^{-1})$  and  $E(z^{-1})$  of order  $n_{\rm H}^{}$ ,  $n_{\rm G}^{}$  and  $n_{\rm F}^{}$  respectively.

The data vector is,

x(t) = [u(t), u(t-1)..., y(t), y(t-1), ..., w(t), w(t-1),

P(t) is a matrix proportional to the covariance of estimated parameters.

k(t) is the updating gain matrix, and is forgetting factor for exponential weighting of last data values.

iii) Compute Control Form

$u(t) = -[g_0 y(t) + g_1 y(t) + \dots + e_0 w(t) + e_1 w(t-1) + \dots$ .... + h\_1 u(t-1) + ... ] / h\_0

iv) Repeat from (i) for the incremented value of 't'.

The algorithm may be started with  $P_0$  of polynomial P set equal to unity and the rest of the co-efficients of R and Q polynomials set to any arbitrary values. Generally 'R' is equal to 'P'.

#### 2.8 CONCLUSIONS

In this chapter, the selection of system model, test

....]

signal, system parameter identification techniques and briefly about MRAC & STC strategies have been described. The reasons to use STC instead of MRAC are also discussed. The complete algorithm of selftuning control, used in this work, is also explained.

#### CHAPTER-, 3.

#### HARDWARE IMPLEMENTATION

#### 3.1 GENERAL

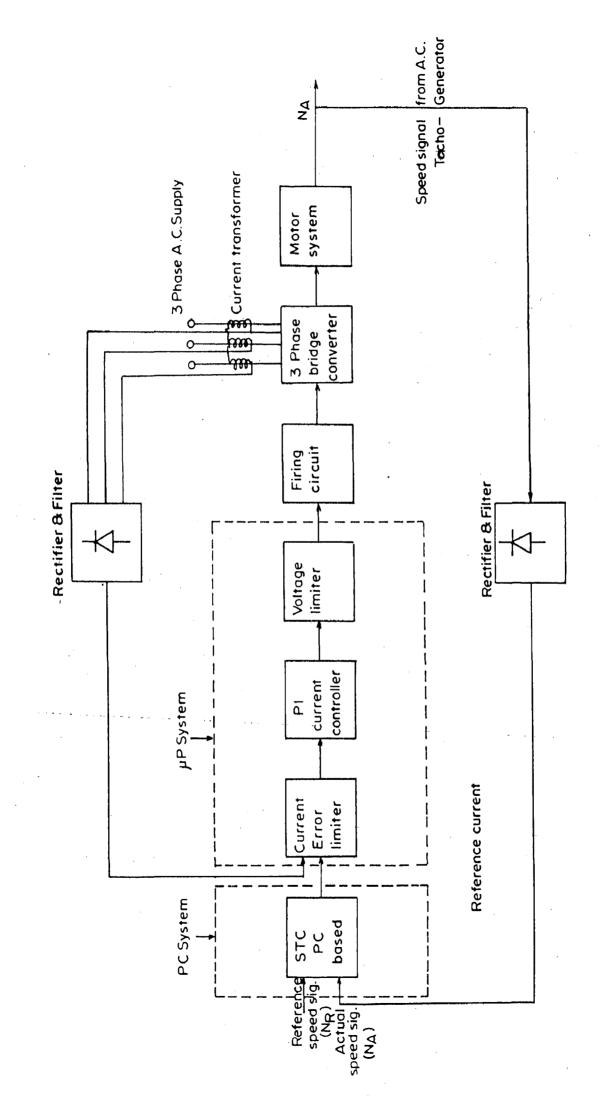

The complete scheme for adaptive speed cotrol of the seperately excited d.c. motor is discussed in this chapter. The power converter used is a three phase fully controlled bridge converter. A adaptive controller based on selftuning, control is realised on IBM personal computer. Microprocessor based scheme for its firing angle control is discussed in detail, together with the hardware requirements. An 8085 microprocessor based system is used for the current error software proportional processing by plus integral а controller (PI) and personal computer (PC) is used to process the software of self tuning controller (STC) which helps in controlling the speed of a d.c. motor.

## 3.2 SYSTEM DESCRIPTION

The complete block diagram of the system is shown in Figure 3.1. The system implementation is started with the reference speed signal and the speed of the machine has to follow this signal. The controller (STC) parameters are computed in real time on line with IBM personal computer which are essential to calculate the controller output,

FIG.3.I SYSTEM BLOCK DIAGRAM.

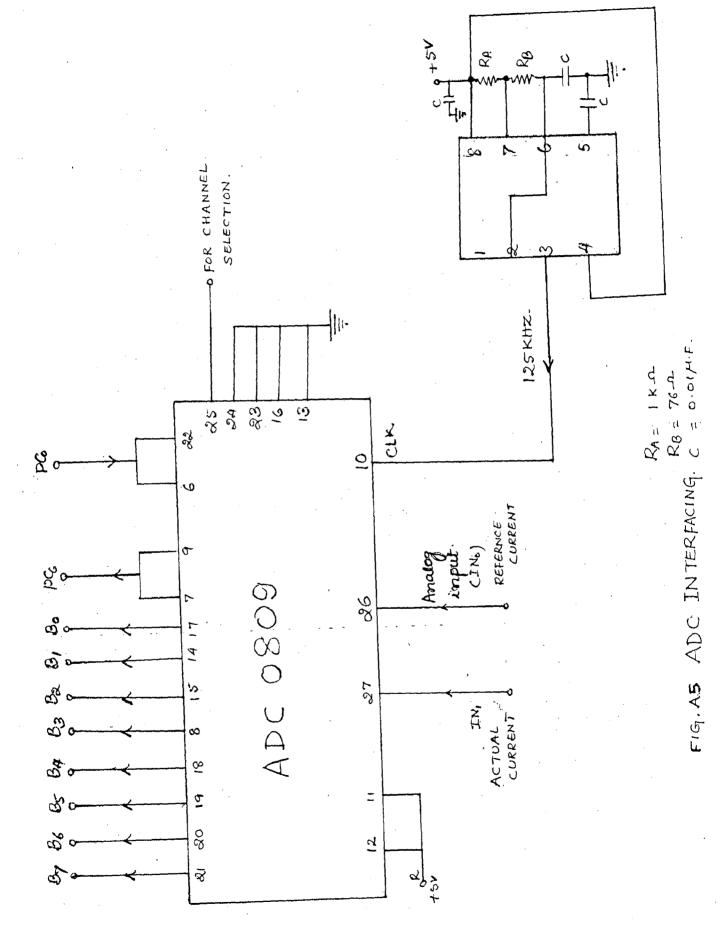

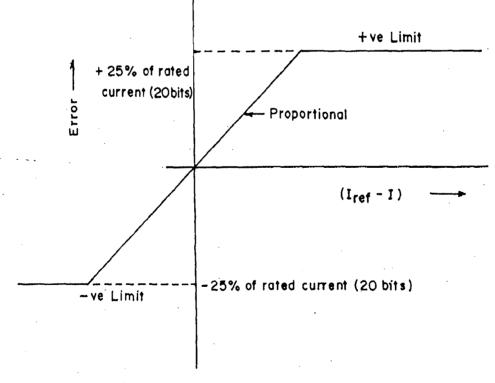

obtained from personal computer (P.C.) in analog form through DAC is considered as current reference signal  $(I_{dc}^*)$  and it is converted into digital signal through 8 bit ADC 0809 which is being fed to the microcomputer 8085. The actual current signal corresponding to motor current is also fed to another channel of ADC 0809. The current error is generated by comparing the reference and actual current signals. This error may be either positive or negative and it is limited to a corresponding to about  $\pm 25$ % of full load current of the motor.

RECIBURI controlling signal The is generated bv а microprocessor according to the current error using proportional plus integral (PI) control algorithm. The PI controller processing is carried out through microp rocessor software. The control algorithm implemented in the microprocessor is a simple computation rule so that the response of the system can be fast. The PI control algorithm is easy to implement and does not need too much time to compute the controlling signals. Depending on this signal, constrained value is obtained from which corresponding firing angle is selected from the lookup algorithm. Using this firing angle first pair of the thyristors are fired and the remaining five pairs are fired at 60° interval. The converter output voltage is fed to a d.c. motor system. The speed of the machine being adjusted through self tuning controller in such a way that irrespective of the load

condition the actual speed of the machine has to follow the reference speed signal. The design of PI controller is given in Appendix C.

# 3.3 PC BASED SELF TUNING CONTROLLER

Clarke and Gawthrop algorithm is used to develop the selftuning controller and it is realised through software on IBM personal computer (PC). Reference speed signal is set through a potential divider and is being fed to PC via one channel of 12 bit ADC. Actual motor speed signal is fed to PC via second channel of ADC. Depending on the difference between these two values, the controller parameters are generated which are essential in obtaining the controller output (u). This controller output is outputted through a channel of DAC which has been considered as the reference current signal to the microprocessor system for the processing of PI current controller

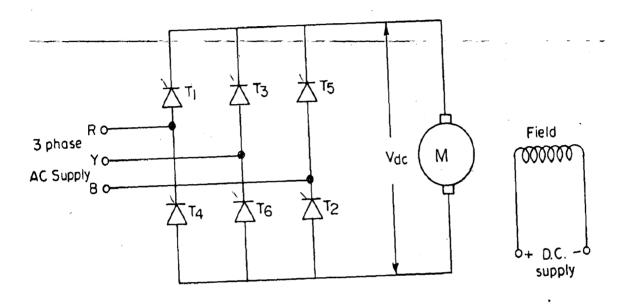

### 3.4 POWER CIRCUIT AND ITS WORKING [1,30,31]

For the experimental purpose, a 1 H.P., 220 V, 1500 RPM d.c. machine is used. The fullwave thyristor bridge rectifier is employed to feed the proposed machine. The ratio of PIV and line to neutral voltage is given by  $E_{PIV}/E_{LN} = 2.45$ . Therefore

$$E_{PIV} = 2.45 \times \frac{400}{\sqrt{3}} = 566 V$$

Taking a factor of safety 2, a 1200 PIV Thyristors are used for the rectifier.

The output average d.c. voltage of a full wave rectifier is given by  $V_{dc} = 3\sqrt{6} /\pi \quad \cos \propto$ . The output voltage is taken equal to the rated voltage of the machine corresponding to minimum firing angle i.e.  $V_{dc} = 220$  V. Assuming the efficiency of 70% of d.c. motor the input power (P/n) is as

$$P_I = V_{dc} I_{dc} = P/n = 746/0.7 = 1065$$

Watts

$I_{dc} = \frac{1065}{220} = 4.85 \approx 5$  Amps.

Taking a factor of safety 2 the thyristor current rating  $I_m = 2x5 = 10$  Amps

So the thyristor of 12 Amp, 1200 V can be selected to meet the requirements. However the available thyristors of 16 A and 1200 PIV are used.

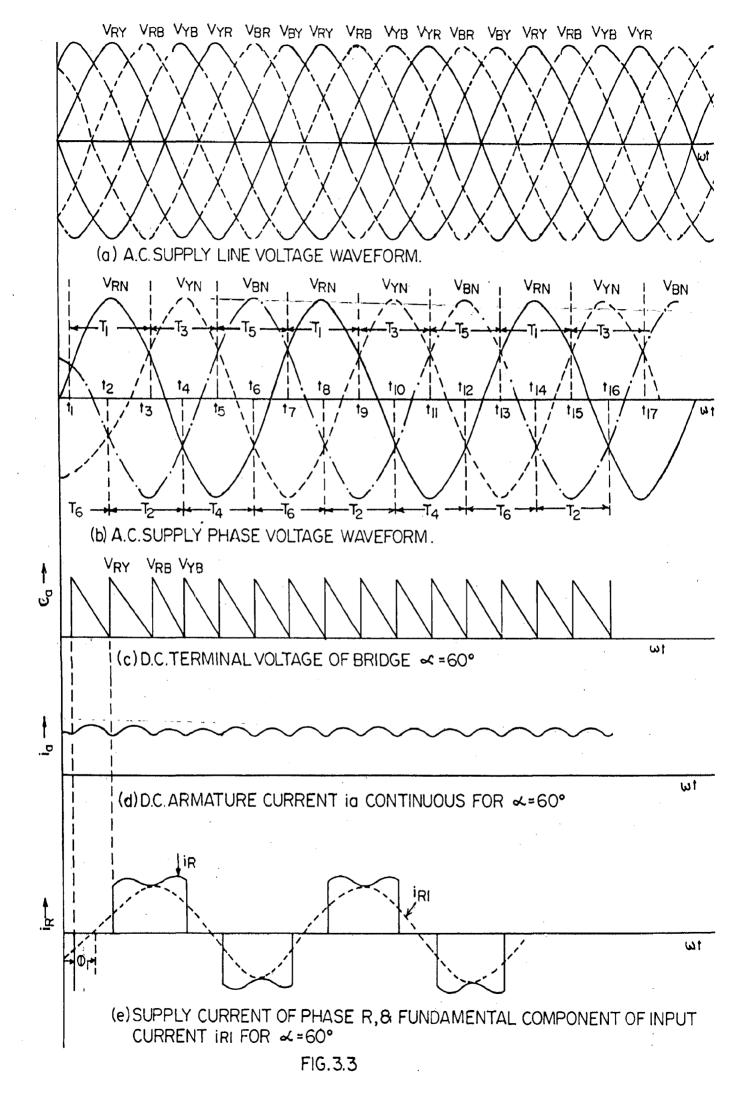

Figure 3.2 shows a three phase fully controlled converter. It consists of six thyristors connected in the form of bridge configuration These thyristors are connected to phases RYB will be denoted by  $(T_1, T_4)$   $(T_3, T_6)$  and  $(T_5, T_2)$ . Each thyristor conducts for 1/3 of a cycle i.e for  $120^\circ$

FIG.3.2 POWER CIRCUIT CONFIGURATION.

duration, and at any instant of time two thyristors are conducting. With respect to phase sequence RYB,  $T_1$ commutates with  $T_3$ ,  $T_3$  with  $T_5$  and  $T_5$  with  $T_1$ . On the other side  $T_6$  commutates with  $T_2$ ,  $T_2$  with  $T_4$  and  $T_4$  with  $T_6$ . Commutation from one thyristor to other occurs when two anodes pass-through-the-same-potential-,-one-going up takes over\_from the other going down. This is called natural commutation. Thyristors are switched faster in three phase converters and therefore the time available for any current delay is less compared to the single phase case. This tends to make the motor current continuous.

Figure 3.2(a) shows the input supply line voltages and 3.2 (b) shows at which instants, the particular pair of thyristors are conducting. In this work six sequence of operation is assumed which can be understand from the following table.

| Sequence          | 0     | í     | 2     | 3     | 4     | 5     |

|-------------------|-------|-------|-------|-------|-------|-------|

| Conducting SCR's  | (6,1) | (1,2) | (2,3) | (3,4) | (4,5) | (5,6) |

| SCR's to be fired | 1 ·   | 2     | 3     | · 4   | . 5   | 6     |

| Outgoing SCR      | 6     | 1     | 2     | 3     | 4     | 5     |

The above firing sequence is used when the firing angle is less than  $60^{\circ}$ . If the firing angle becomes greater than  $60^{\circ}$  then the following sequence is used.

0 1 2 3 5 Sequence (5,6) (6,1) (1,2) (2,3) (3,4) (4,5) Conducting SCR's 6 1 2 3 4 5 SCR's to be fired 1 2 5 3 4 6 Outgoing SCR

If the firing angle becomes greater than  $120^{\circ}$  the following sequence is used

| •                 | · ·   |       |       |       |       |       |

|-------------------|-------|-------|-------|-------|-------|-------|

| Sequence          | 0     | 1     | 2     | 3     | 4     | 5     |

| Conducting SCR's  | (4,5) | (5,6) | (6,1) | (1,2) | (2,3) | (3,4) |

| SCR's to be fired | 5     | 6     | 1     | 2     | 3     | 4     |

| Outgoing SCR      | 4     | 5     | 6     | 1     | 2     | 3     |

To maintain a symmetrical waveform of the input current the firing sequences are necessary. The frequency of firing will be six times the supply frequency.

The average output voltage of a fully controlled converter is given by

$V_{dc} = \frac{3\sqrt{6}}{\pi} V \cos \alpha$  ... (3.1)

If  $\propto = 0^{\circ}$  then  $V_{dc} = V_{max}$  and if  $\propto = 90^{\circ}$  then  $V_{dc} = 0$ .

Therefore equation (3.1) shows the output voltage depends upon the firing angle information.

For a seperately excited d.c. motor the back e.m.f.  $E_g = K_a \phi N$ In terms of average voltages

Equation (3.2) represents the average speed.

In a seperately excited d.c. motor  $T = K_a \phi I_a$  and motor speed (N) is

$$N = \frac{V_{dc}}{K_a \phi} - \frac{R_a}{(K_a \phi)^2} T \qquad .. (3.3)$$

The first term in equation (3.3) represents the ideal no load speed (T $\approx$ 0), which, therefore, depends on V<sub>dc</sub>. If the motor current is assumed continuous, motor terminal voltage  ${\tt V}_{\rm dc}$  depends only on the firing angle  $\ll$  . The variation of  $V_{dc}$  with  $\propto$  for continuous motor current is shown in Fig.3.3(c). These curves also represent the theoritical no load speed as a function of firing angle. The second term in equation (3.3) represents the decrease in speed as the motor torque increases. Since the armature resistance is small, the decrease in speed is small. In large motors, the motor current at no load (i.e. motor idling) is not small, and if a three phase converter is used the motor current is likely to be continuous even at no load condition. Therefore, three phase converter fed dc drives provide better speed regulation and improved performance as compared to single phase converter fed dc drives.

The motor terminal voltage can become negative for the triggering angle  $=120^{\circ}$ . This is the inversion mode of operation of the converter. If the motor voltage is reversed

with a reversing contactor or by reversing the field current, power can be transferred from the motor to the a.c. supply. That is what commonly known as regeneration. The motor will slow down due to power feeding back, and thus the motor voltage decreases. Therefore, as the motor slows down, the firing angle of the converter is to be adjusted to keep the current up and to regenerate power.

#### 3.5 MICROPROCESSOR BASED CONTROL SCHEME

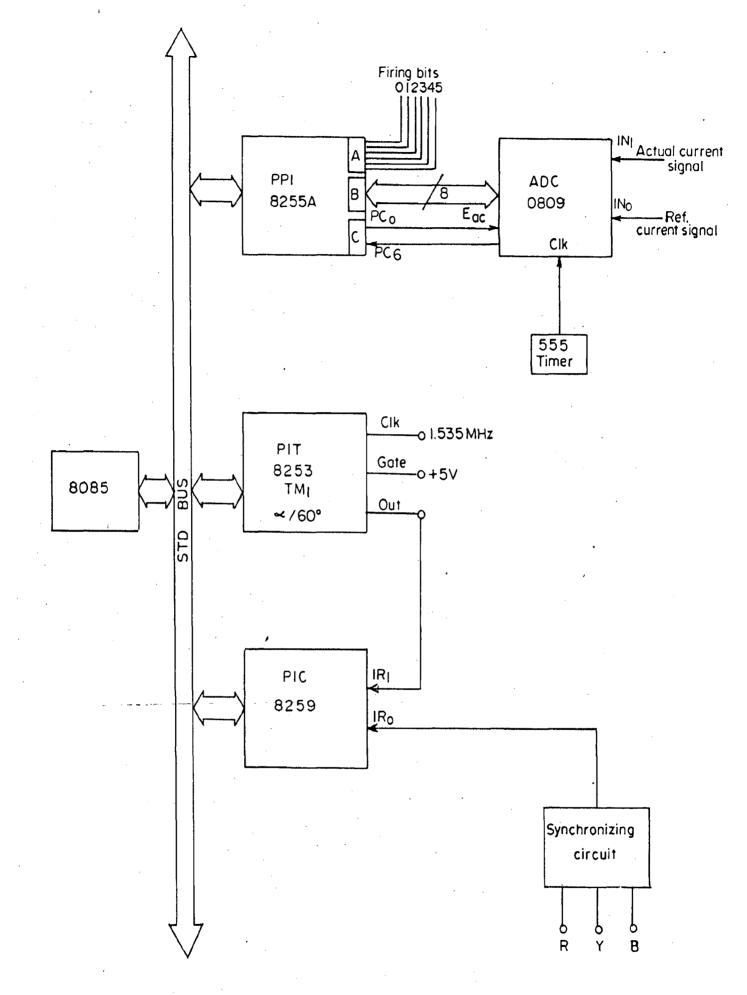

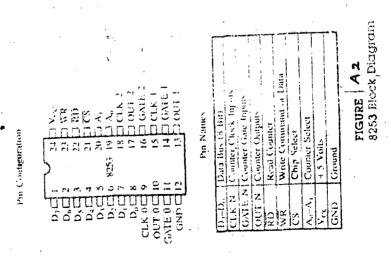

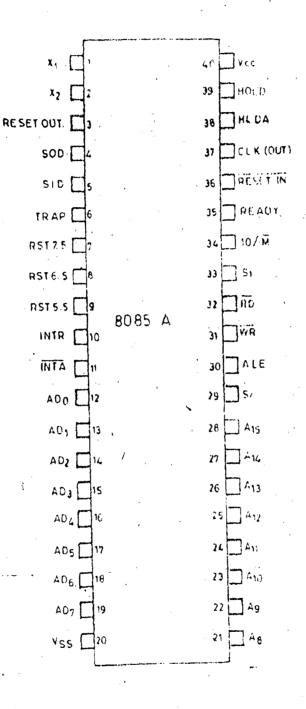

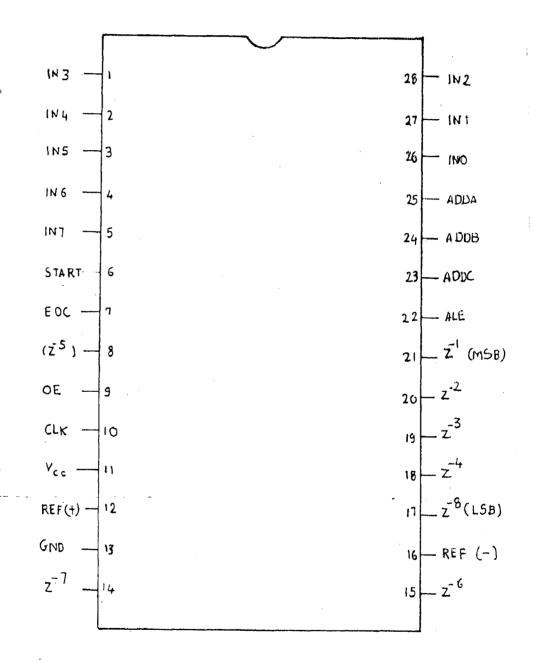

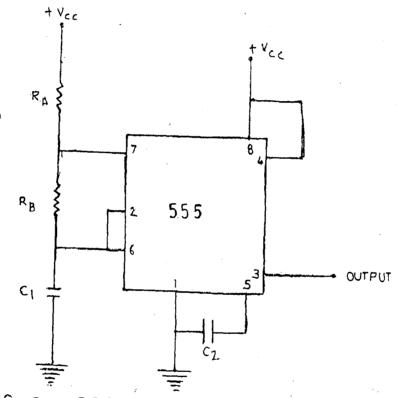

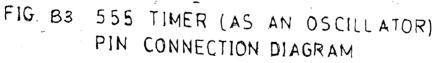

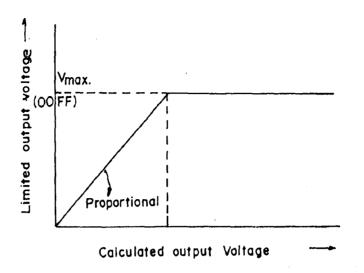

Microprocessor based firing scheme is shown in Fig.3.4 and it is used for generating the firing pulses for converter thyristor in proper sequence decided by the control circuit and software. This scheme has several advantages over the analog firing control schemes. This scheme requires less number of hardware components and simple synchronizing technique. For this, one programmable peripheral interface 8255, one programmable interval timer and one programmable interrupt controller 8259. The pin diagram and operational details of these ICs are given in Appendices A and B . The synchronizing signal which is obtained from synchronizing circuit is inputted to IR interrupt. Gate of timer TM, is always made high by connecting it to +5V. Counter  $TM_1(1)$  get the clock of 1.535 MHZ from µP. ADC 0809 is interfaced to microprocessor through port B and port C of 8255. ADC provides the information about the reference current and actual current. The firing angle information is obtained

FIG. 3.4 MICROPROCESSOR BASED SYSTEM CONFIGURATION.

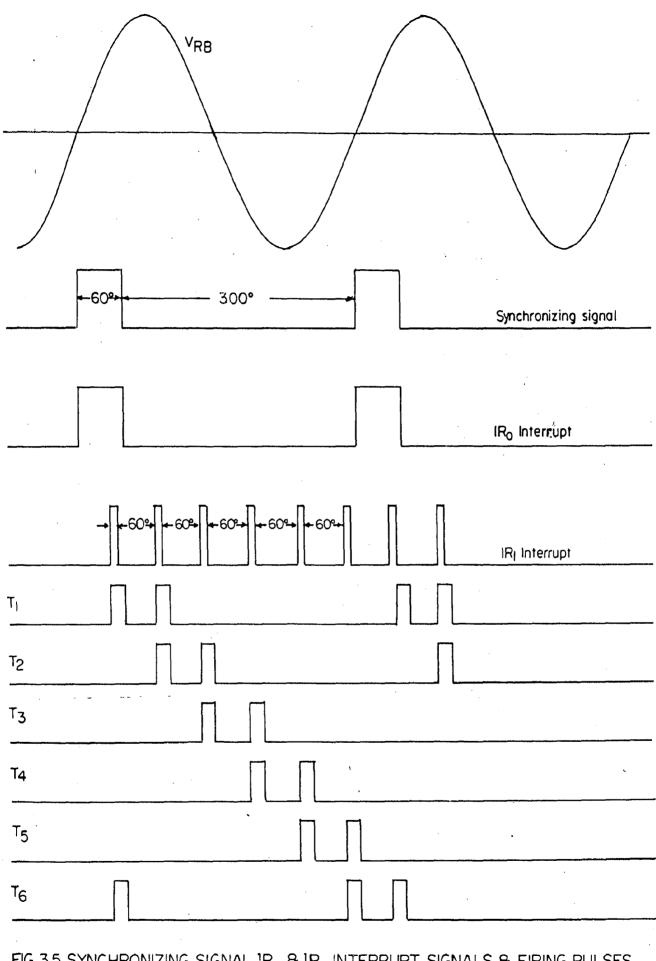

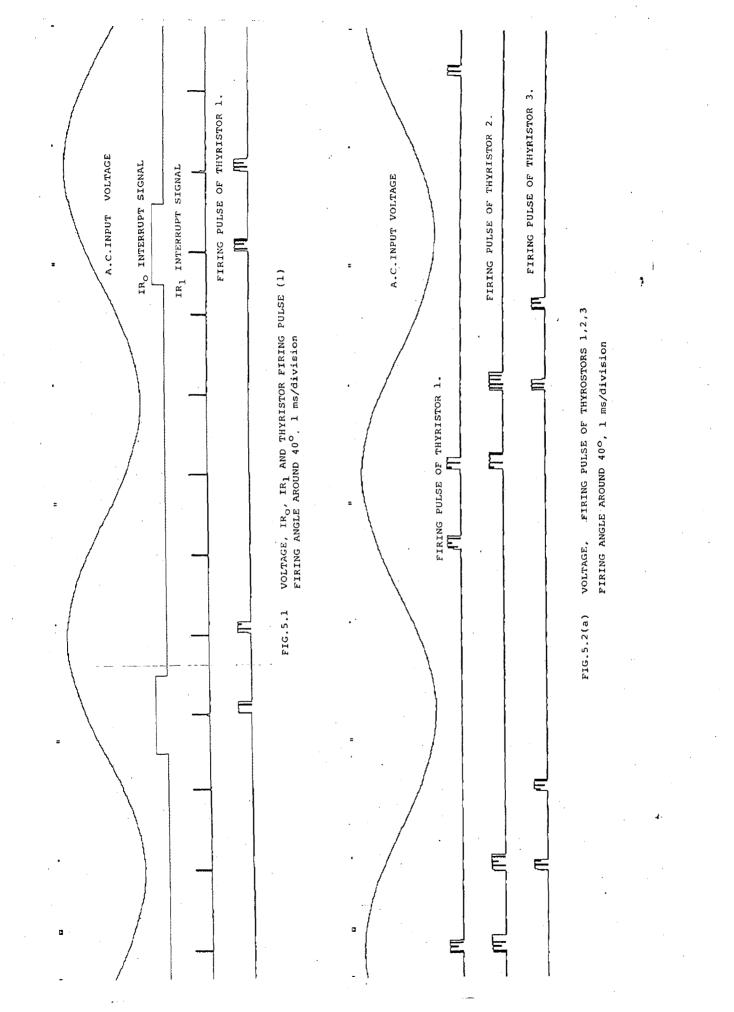

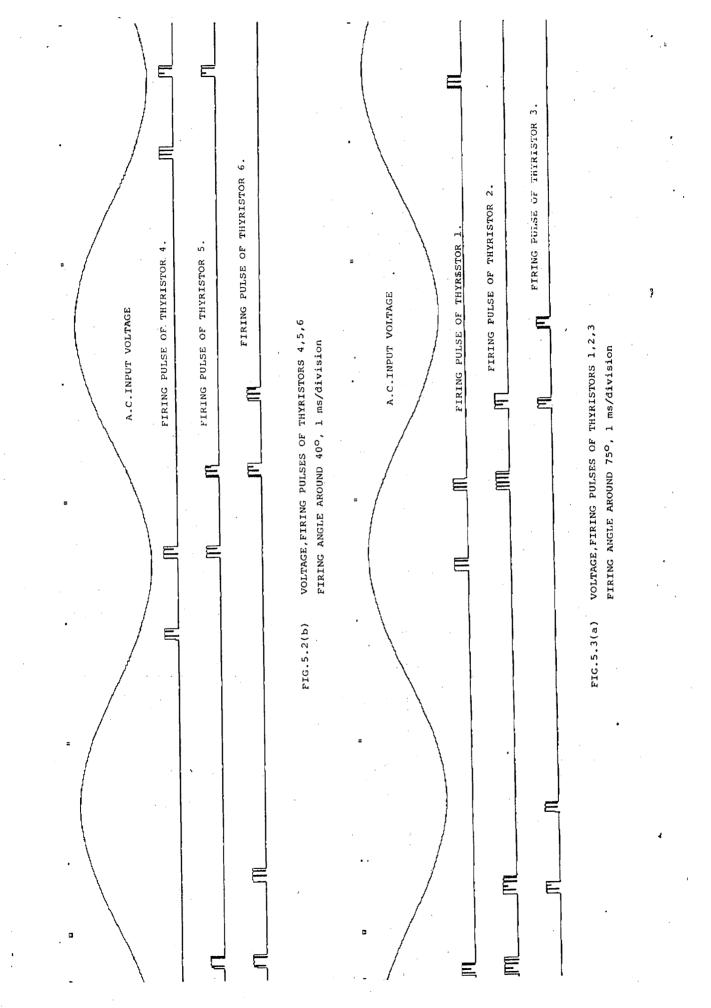

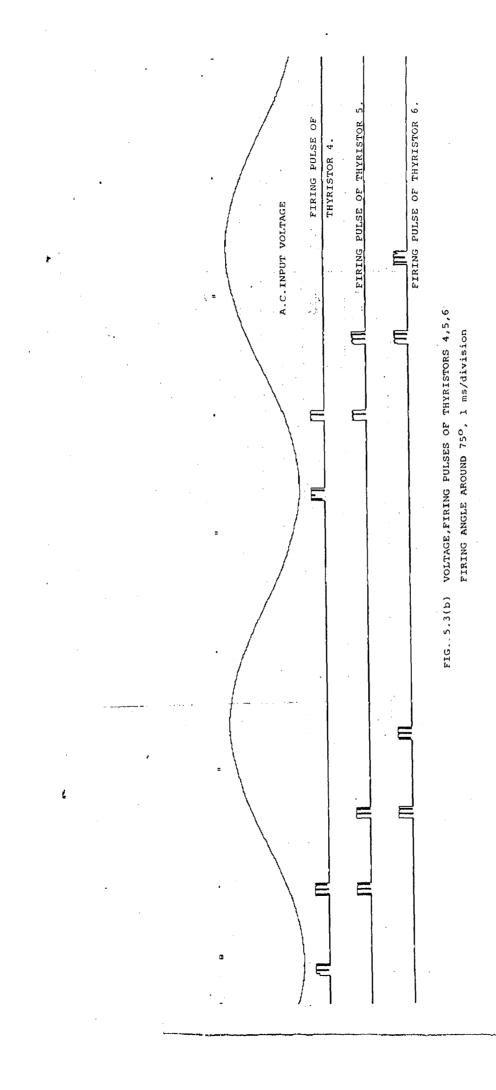

from the lookup table, and the pulses are outputted through port A of 8255 as per firing command. Different wave shapes for interrupt signals are given in Figure 3.5.

## 3.5.1 Synchronizing Technique

Independently of the method or algorithm used to control thyristors firing of a three phase static power converter, the signals that synchronize them with the alternating supply voltages are always necessary. For a three phase converter, there are six such logical signals, each one associated with a thyristor and defined from the natural commutation instant i.e. at the intersection of two phase to phase voltages, which coincides with zero crossing of the other one. The zerc crossing voltage detector fulfills two different functions, the synchronization of the thyristor circuit to the input line frequency and the phase sequence identification.

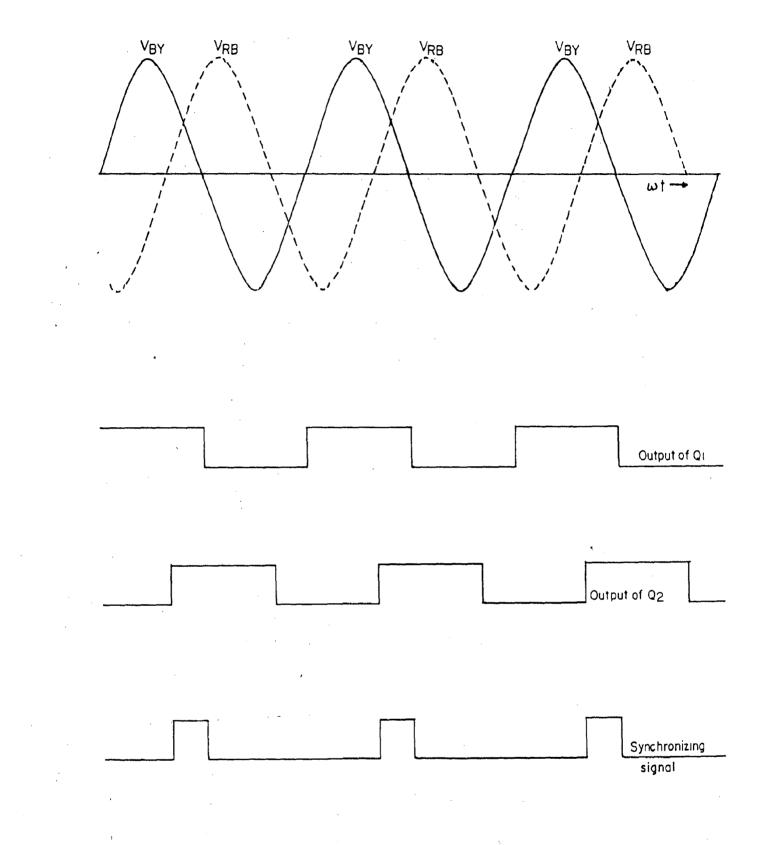

Synchronizing signal is generated by sensing line to line voltages  $V_{RB}$  and  $V_{BY}$  of the supply mains. This signal has pulses of 60° duration corresponding to supply voltage frequency at every 360° interval. This signal provides the information about frequency of supply voltage and the instant of loading a counter of PIT 8253 with firing angle delay count. Synchronizing signal is required for generating firing pulses for converter thyristor in proper sequence.

FIG.3.5 SYNCHRONIZING SIGNAL,  $R_0 \otimes R_1$  INTERRUPT SIGNALS & FIRING PULSES IN PROPER SEQUENCE.

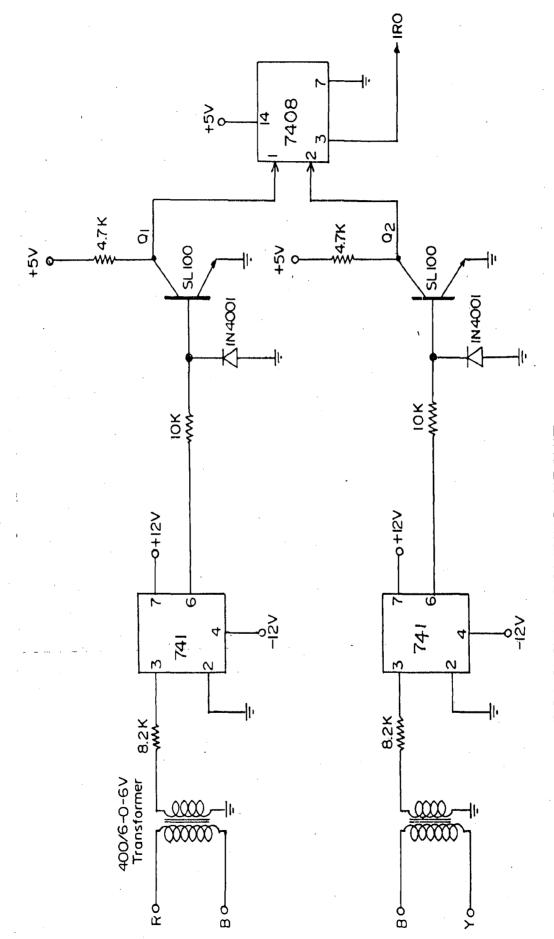

Synchronizing circuit uses less number of components and is shown in Figure 3.6. This circuit consists of the following components.

i) Step down transformer

ii) Comparator

iii) Transistor drive

iv) AND gate

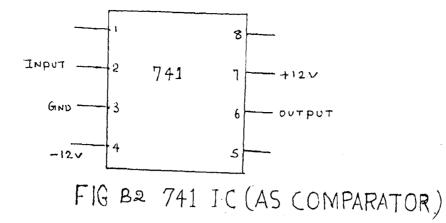

Stepdown transformer is a single phase 440 V/6 V transformer to realise voltage sensor for a wide range of frequency. The primary and secondary connections are made in such a way that secondary voltage is 180° out of phase with respect to the primary voltage. Comparator circuit is realised with the help of operational amplifier IC 741. The inverting terminal of IC 741 is connected to common ground. The output of the comparator ideally swings between +12V to -12V at zero crossing of supply voltages and frequency is same as supply frequency. The output of comparator is reduced to a lower voltage by a series connected resistor and applied to the base of the transistor. Transistor stage is very important and required to interface the analog system to a digital system. Transistor is used to control the state of the TTL input. TTL outputs of transistors are shown in Figure 3.7.

The diode in the base circuit protects the base against excessive reverse voltage. Since the negative output

FIG.3.6 SYNCHRONIZING CIRCUIT

FIG.3.7 VOLTAGE WAVEFORM AT DIFFERENT POINTS OF SYNCHRONIZING SIGNAL .

of the comparator approaches -12V, we need to use a protective diode between the base and ground. This diode clamps the base voltage at approximately -0.7V on the negative swing. AND gate is used for necessary AND operation. The synchronizing signal is obtained after ANDING two output signals of the transistors. The microcomputer makes use of this signal for generating firing pulses in proper sequence and firing angle control.

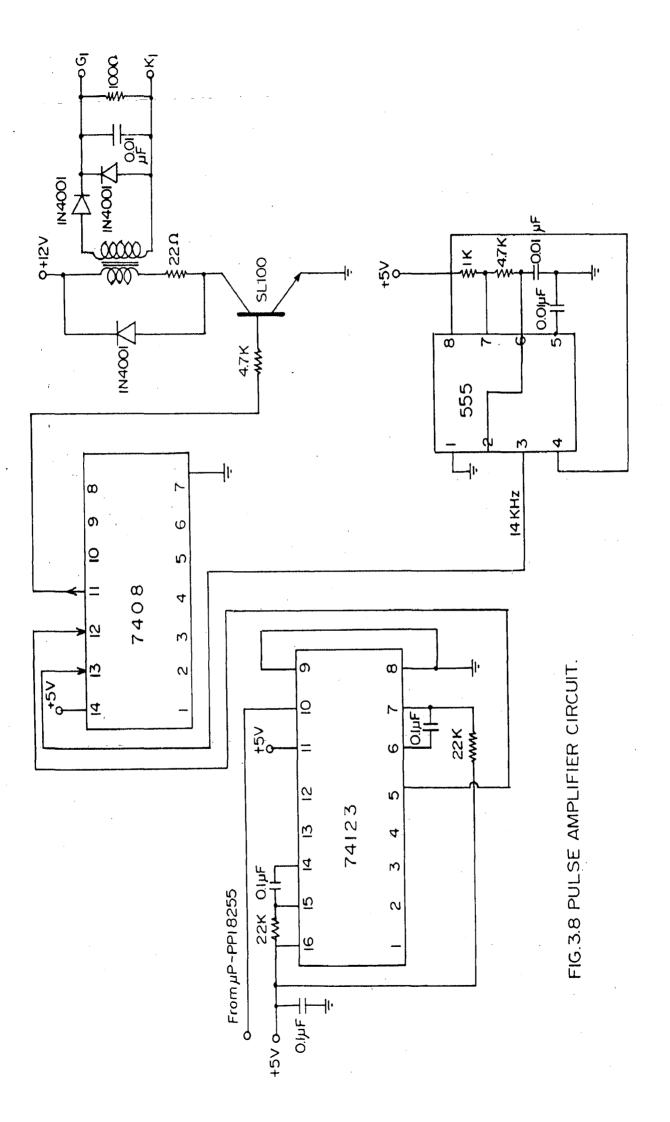

### 3.5.2 Pulse Amplifier Circuit

The duration of firing pulses generated by the microprocessor via port A is not sufficient to trigger converter thyristors. The required pulse width is obtained using monostable circuit. The output of the monostable is applied to the pulse amplifier circuit as shown in Figure 3.8.

A pulse transformer is used for electrical isolation between control circuit and power circuit. The pulse at the transistor collector is the amplified inverted form of the input signal. But the isolating transformer connection are made in such a way that the final firing pulses has no phase shift with respect to the input pulse. A diode is connected across the transformer primary to avoid saturation of the pulse transformer. Another diode is connected in series with the secondary of the pulse transformer to block negative pulses. The diode across the primary also serves to protect

the transistor. The capacitor at the secondary prevents any spurious high frequency from triggering the thyristor. The gate of the thyristor can be protected from long reverse voltage by connecting a diode across the gate as shown in Figure 3.8.

## 3.6 CONCLUSIONS

In this chapter, the complete hardware philosophy of the speed control of a d.c. motor has been described using self tuning controller. The STC adaptive controller for speed control loop has been realised on IBM PC system and current control loop using PI controller has been realised through 8085 microprocessor based system. The design of power circuit and synchronizing circuit has been developed. The details of microcomputer based firing control scheme has been described in detail.

### CHAPTER - 4

#### SYSTEM SOFTWARE IMPLEMENTATION AND FLOW CHARTS

### 4.1 GENERAL

In this chapter, the complete software for self tuning controller (STC) based closed loop speed control of thyristor converter fed d.c. motor is described. The self tuning controller is realised through IBM personal computer (PC) in which speed feedback and reference speed signals are inputted through 12 bit 16 channel ADC Card and output of controller (STC) is obtained through a DAC channel of same card from The analog output of self tuning personal computer. controller is considered as current reference signal and inputted to 8085 based microcomputer system via 8 bit 8 channel ADC 0809 along with motor current feedback signal. A current proportional integral (PI) controller is realized through software on 8085 based system which also provides various firing commands for thyristors of converter in proper synchronization with mains through various hardware interrupts. The complete software for microprocessor 8085 based system is explained through main programme and associated various subroutines.

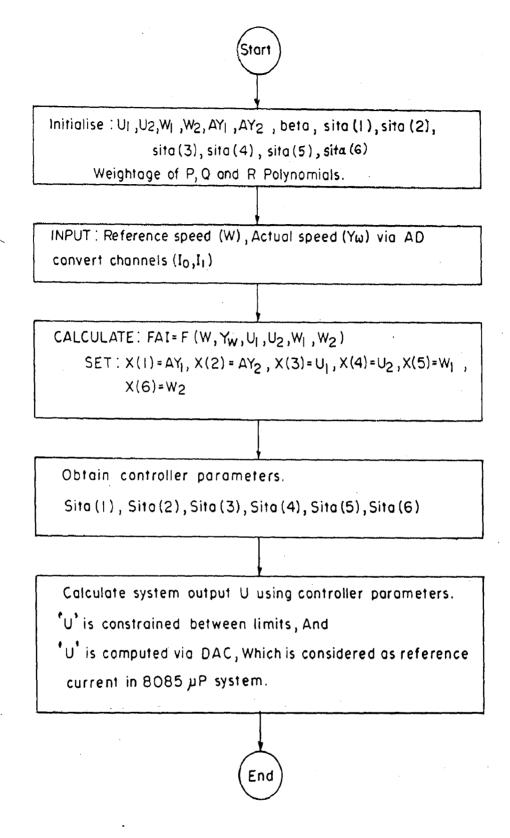

### 4.2 SOFTWARE IMPLEMENTATION OF SELF TUNING CONTROLLER

In the present work, the speed control of a d.c. motor is achieved by self tuning controller. The flowchart of implementation of STC algorithm is given in Fig.4.1. The program starts with the initialization of variables which are necessary to carryout the processing in order to obtain controller parameters and controller output. Proper weightage of polynomials P,Q and R is considered. Reference speed is set through the potential divider, and actual speed signal of a d.c. motor is measured through a.c. tachogenerator after rectifying and filtering. These two signals are taken as input via AD converter channels ( $I_0$  and  $I_1$ ) of ADC card of IBM (PC). Depending on these signals the controller parameters are estimated which adjust the controller output (U). The value of 'U' is computed and limited in the manner as demanded by controller to maintain constant speed of a d.c. motor irrespective of the load conditions. The developed basic language program for self tuning controller is given in appendix 'D'.

# 4.3 SOFTWARE FOR 8085 MICROPROCESSOR SYSTEM

#### 4.3.1 Main Program

The flow chart of the main program is shown in Fig.4.2. The program is started with initialization of STACK pointer and input-output ports. In the 8085 system, two timers of PIT 8253, six input-output ports with two PPI 8255 and one interrupt controller PIC 8259 are available to the user at  $J_1, J_2$  and  $J_3$  space. In the present work, one timer  $TM_1$  is used for loading firing angle as well as  $60^{\circ}$  count. Out of

FIG.4.1 FLOW CHART OF SELF TUNING CONTROLLER.

Initialise stack pointer, 8255, 8253 and 8259 with their modes, starting cycle index (s). Call closed loop initialization subroutine.

Select INo channel of ADC, Read reference current from PC via DAC. Select INi channel of ADC, Read actual current.

Call constrained current error subroutine, call PI current controller subroutine. Call constrained voltage subroutine.

Call look up : select corresponding firing . .

Call mode selection subroutine. Call multiplication subroutine, Get firing angle count.

Is starting index = 00 Yes Enable of interrupt. Incrementing starting cycle index = 01

FIG.4.2 FLOW CHART OF MAIN PROGRAM.

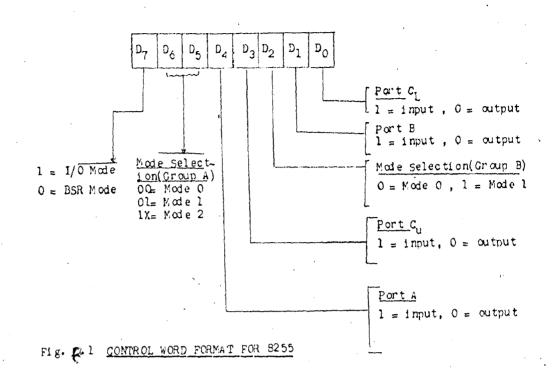

six input-output ports, three input-output ports of PPI 8255(1) are used in the present work. It is initialized as follows:

| 8255(1) | (Control word | registor = (        | )3H)                |               |

|---------|---------------|---------------------|---------------------|---------------|

| PORT A  | PORT B        | port c <sub>u</sub> | port C <sub>l</sub> | •             |

| OUT     | IN            | IN                  | OUT                 | 10001010 = 8A |

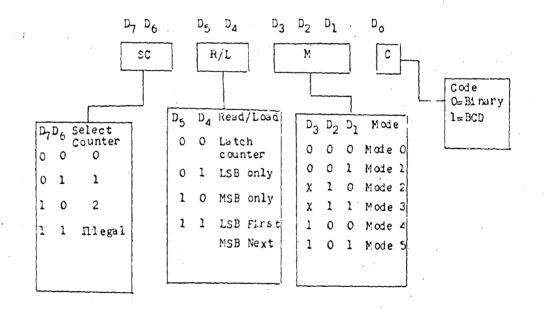

Figure 3.4 given in the previous chapter shows the configuration of the microprocessor based control scheme. Port A is used for firing the converter thyristors (Bits  $PA_0$  to  $PA_5$ ), port B is used for inputting digital output of ADC. Port C is used to send start of convertion (SOC) and end of conversion (EOC) signals. The timer  $TM_1$  is used for loading both firing angle count as well as  $60^{\circ}$  count for triggering converter thyristors. The timer is initialised as follows.

| TM1 | (11H) in mode ' | 0'     |                      |

|-----|-----------------|--------|----------------------|

| TMl | R/L             | MODE 0 | CODE                 |

| 01  | 11              | 000    | 0 = 70H <sub>+</sub> |

After initialization of all the necessary chips, all firing bits are made low and the status of output ports are stored. Starting cycle index 'S' is stored with initial value as OOH and the  $60^{\circ}$  count value is also stored. The PIC is initialized for the vector addresses of the interrupts  $IR_{0}$ ,  $IR_{1}$ . All interrupts are considered edge triggered.

After initialization process, two ADC channels are inputted one by one by selecting channels through port  $C_{\rm L}$ . Reference current is inputted by selecting IN<sub>0</sub> channel of ADC 0809 from personal computer (PC) via DAC, actual current is inputted by selecting IN<sub>1</sub> channel of ADC 0809.

After the measurement of reference and actual currents, the current error is constrained and stored at the end of constrained current error subroutine. Now, it enters PI subroutine.

In the PI control part, the change in error is calculated from the constrained current error and previous constrained current error. This change in error is used to obtain the new output unconstrained voltage of 2 byte, and then program enters constrained voltage subroutine.

In the constrained voltage part, previously obtained unconstrained voltage of 2 byte is considered to one byte only, because the voltage values stored are of one byte. This value of constrained voltage is limited between minimum (00H) to maximum (FFH) output voltage (Vdn), then it enters lookup algorithm to select the corresponding firing angle.

The firing angle which has been selected through look up subroutine is used to select the particular sequence of firing the thyristors of converter. This is being done in 'MODE SELECTION' subroutine. The above obtained firing angle

FIG.4.3 FLOW CHART OF CLOSED LOOP INITIALIZATION.

is converted into its equivalent counts by multiplying it with 'K' counts using 'MULT' subroutine. This firing angle count is used to load the timer  $(TM_1)$ .

After this starting cycle index 'S' is checked. If it is found as zero then the interrupt are enabled and increment index 'S' to one, otherwise jump back to 'CALL ADC' and carryout other processings.

The IR<sub>o</sub> interrupt service susbroutine is used to load the timer with firing angle count once in every cycle and  $IR_1$ interrupt service subroutine is used to load the timer with  $60^{\circ}$  count five times in every cycle, and to issue all six firing commands.

The machine level language programs are given in Appendix E.

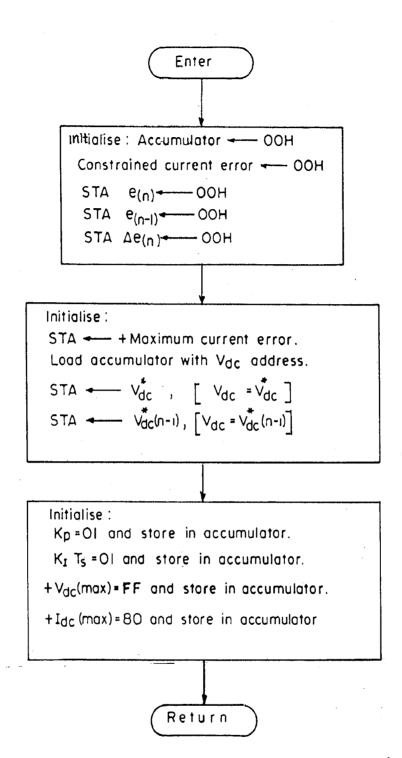

## 4.3.2 Close Loop Initialization

In order to carryout the PI processing it is necessary to initialise some of the variables such as error, change in error, maximum voltage, maximum current, controller constant etc. This is done using closed loop initialization subroutine. The self explainatory of which is shown in Figure 4.3.

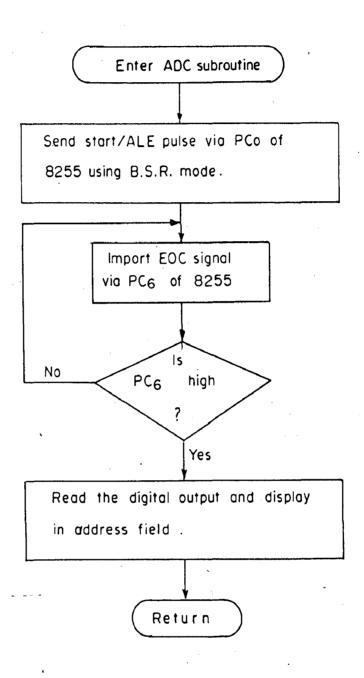

#### 4.3.3 ADC Subroutine

Reference current is measured and stored through this

subroutine. The self tuning controller output from PC via DAC converter is considered the value of reference current. An ADC converts this analog signal into digital signal. This ADC conversion is done once in every cycle of the main programme.

ADC clock in is given from a timer of 380 KHz frequency. ADC starts converting the analog signal into digital signal at the instant, when the start conversion (SOC) bit of ADC goes from low to high to low. ADC sends a signal to I/O port through end of conversion (EOC) bit going high, indicating that the conversion process is over. The ADC count is measured and stored in the memory location alloted for reference current. The flow diagram of ADC subroutine is shown in Fig. 4.4.

NAME OF SUBROUTINE

: ADC SUBROUTINE

: Input to DAC through AD/DA converter from PC via channel IN<sub>o</sub> which is selected.

: Reference current I dc

: None

: A, F

: This subroutine measures the reference current  $I_{dc}^{\star}$ . The result is stored in the reference current  $I_{dc}^{\star}$  at the end of subroutine, and it is displayed in the address field.

OUTPUTS CALLS DESTROYS

DESCRIPTION

FIG.4.4 FLOW CHART FOR ADC SUBROUTINE.

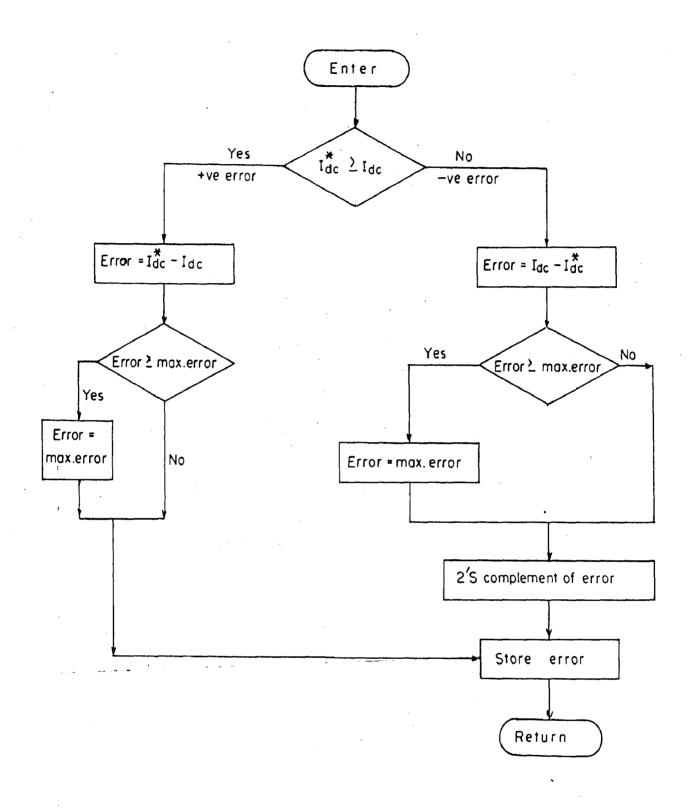

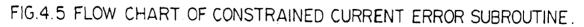

# 4.3.4 Constrained Current Error Subroutine

This subroutine is used to limit the magnitude of current error corresponding to actual current and reference The maximum magnitude of current error is decided current. initialization routine. Difference between in the CLI reference current and actual current results in error, this error is being limited not to cross the specified limits. The error may be positive or negative, if the magnitude of the current error is greater than the maximum current error, then the error is set equal to maximum current error, if the magnitude of -ve current error is greater than the maximum current error then error is set equal to maximum value and 2's complement of it. This value is the constrained value of current error. The flow chart of this subroutine is given in Fig. 4.5.

NAME OF SUBROUTINE

- : Constrained Current Error Subroutine.

- : Reference Current I<sup>\*</sup><sub>dc</sub> Actual 1 byte Current Idc each

- : Constrained Current Error

- (1 byte 2's Complement)

- : A, F, H, L.

- : This subroutine limits the current error between minimum and maximum error.

OUTPUT

INPUTS

DESTROYS

DESCRIPTION.

#### 4.3.5. PI Current Controller Subroutine

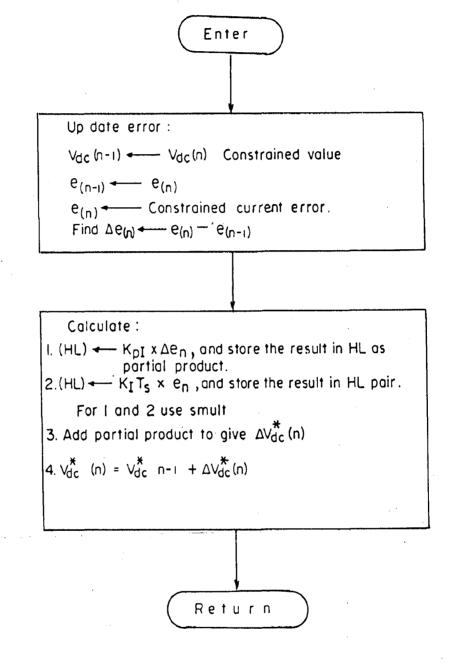

This subroutine computes and stores the unconstrained voltage  $V_{dn}^{\star}$ . During the execution of this subroutine, voltage and current error is updated. The constrained current error is considered as present status of error, which is used along with integral gain to obtain  $K_{I}e_{n}$ , the change in error is used with proportional gain  $K_{p} \bigtriangleup e_{n}$ . In both these case 'SMULT' subroutine is used, resulting in partial product. The product being added to get change in voltage. This change in voltage is added with previous voltage to obtain present status of voltage which is unconstrained 2-byte in 2's complement and is stored in the alloted memory location. The flow chart of it is given in Fig.4.6.

NAME OF SUBROUTINE

INPUTS

: PI Subroutine

: V<sup>\*</sup>dn

: V<sup>\*</sup><sub>dn-1</sub>

one byte each

: e<sub>n</sub> [ 1 byte 2's complement form] : e<sub>n-1</sub> [ 1 byte 2's complement form] : e<sub>n</sub> [ 1 byte 2's complement form] : Constrained current error [1 byte 2's complement form]

- : Unconstrained V<sup>\*</sup>

- : SMULT

- ALL

: This subroutine measures and stores the unconstrained  $V_{dn}^{*}$  value

OUTPUT

CALLS

DESTROYS

DESCRIPTION

FIG.4.6 FLOW CHART OF PI CONTROLLER OF CURRENT ERROR.

[2 byte 2's complement] in  $V_{dn}^*$  address at the end of Subroutine.

#### 4.3.6 Subroutine SMULT

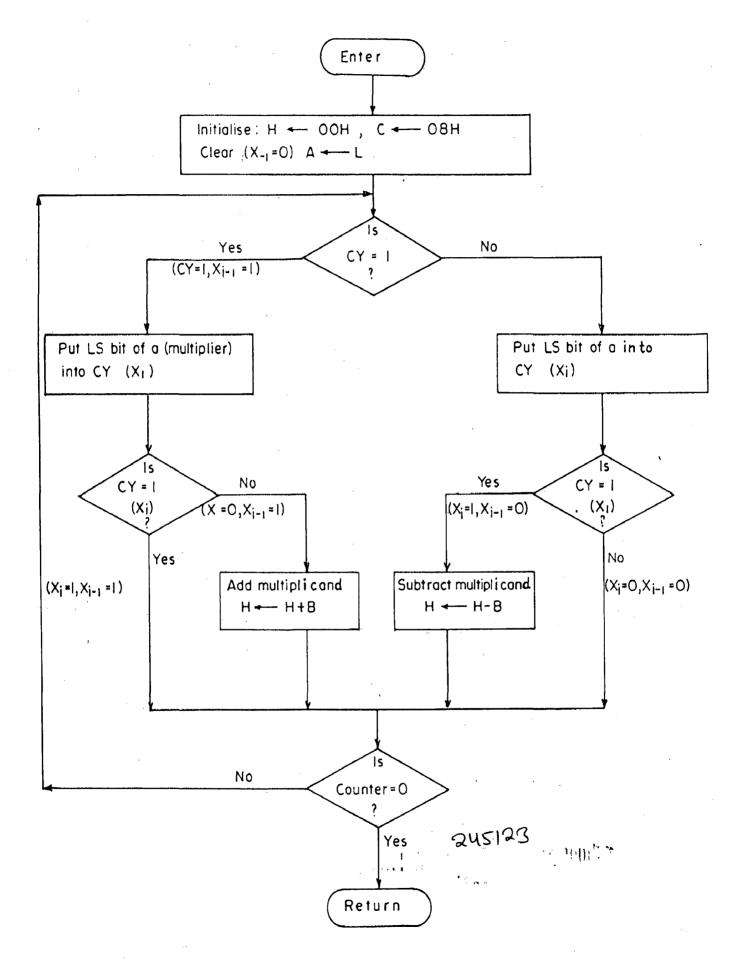

Two's complement numbers can not be multiplied with the algorithm for unsigned binary numbers, because if either or - both the operands are negative, the result is incorrect. In one of the methods for multiplying two's complement number, first determine and save the signs of operands. Negative operands are made positive, and the operands are multiplied using the add and shift algorithm. If the operand signs are different, then the two's complement of the product is taken.

Booth's algorithm is direct а mere method of multiplying two's complement numbers. Booth's algorithm is based on the fact that a string of zeros in the multiplier requires no addition, just shifting and string of 1's running from  $2^p$  to  $2^q$  is treated as  $2^{q+1} - 2^p$ . In Booth's algorithm, the multiplication requires only two operations in addition to the shifts, one subtraction and one addition. This results in a faster multiplication because fewer operations are required.

Booth's algorithm is used which is as follows. Let  $X_i$  be the i<sup>th</sup> bit of an n-bit multiplier. But  $X_{n-1}$  is the most significant bit and  $X_0$  the least significant bit. A bit  $X_{-1}=0$

is assumed. The multiplicant is Y. Starting with i=0,  $X_{i}$  and  $X_{i-1}$  are compared. Depending on the comparison, one of the following action occurs.

| Xi | × <sub>i-1</sub> | operation                                       |

|----|------------------|-------------------------------------------------|

| 0  | 0                | Shift Y (left with respect to partial product)  |

| 0  | 1                | Add Y to partial product and Shift Y.           |

| 1  | 0                | Subtract Y from partial product<br>and Shift Y. |

| 1  | 1                | Shift Y                                         |

This process is repeated unitl n comparisons are made completing the multiplication.

The flow chart of subroutine is given in Fig.4.7 which implements Booth's algorithm for an 8-bit multiplicand and 8-bit multiplier. The subroutine is entered with the multiplicand in register D and the multiplier in register C. The 16 bit product is retained in register pair HL. This susbroutine is called in the PI subroutine for software implementation of PI controller.

NAME OF SUBROUTINE : SMULT

INPUTS

: Register B has multiplicand, Regist L has multiplier, Register C is used as counter.

FIG.4.7 FLOW CHART FOR SMULT SUBROUTINE.

OUTPUT

CALLS DESTROYS DESCRIPTION Register pair HL has the 16 bit product of the multiplication.

: None

:

- : A,F,B,C,H,L Registers.

- : This susbroutine multiplies two numbers (1 byte each), which are in 2's complement form. It stores the result of multiplication in register pair HL. This subroutine can be used for both unsigned numbers multiplication and for 2's complement numbers multiplication.

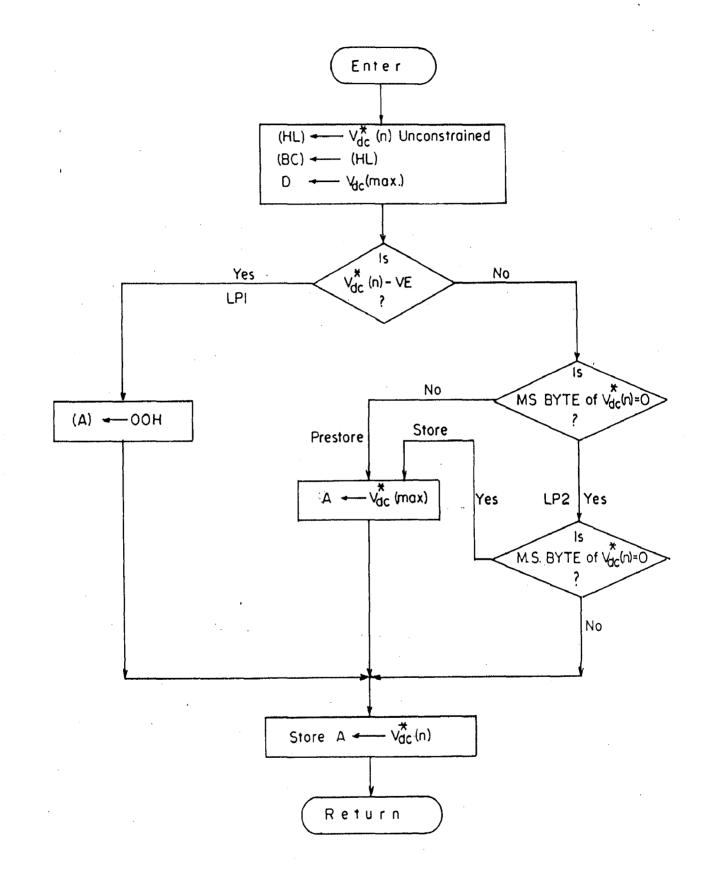

## 4.3.7 Constrained Voltage Subroutine

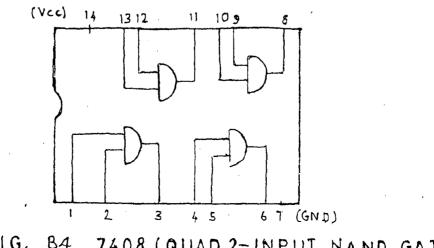

As mentioned in Appendix-C, in the design of PI controller, the maximum value of output voltage is to be limited between maximum and minimum specified limits. In the case of fully controlled converter, the normalised output voltage 00H corresponds to the maximum firing angle i.e.  $90^{\circ}$ , and FFH corresponds to the minimum firing angle i.e.  $0^{\circ}$ . The maximum and minimum value of output voltage is limited between FFH and 00H.

The flow diagram of it is given in Fig.4.8. The value of 00H if  $V_{dn}$  value to 00H if  $V_{dn}$  unconstrained is positive also greater than maximum voltage.

NAME OF SUBROUTINE : Constrained Voltage Subroutine.

· •

# FIG.4.8 FLOW CHART OF CONSTRAINED VOLTAGE SUBROUTINE.

OUTPUT

CALLS

DESTROYS

DESCRIPTION

: V<sup>\*</sup><sub>dn</sub> unconstrained

[2 byte data in 2's complement form]

v<sub>dn</sub> maximum voltage [1 byte]

: Constrained V<sup>\*</sup><sub>dn</sub> @[1 byte]

then it is set as FFH.

: None

: All

: This subroutine limits  $V_{dn}$  value between 00H and FFH, i.e. if  $V_{dn}$  is negative,  $V_{dn}$  is set as 00H, and if  $V_{dn}$  is positive and greater than FFH,

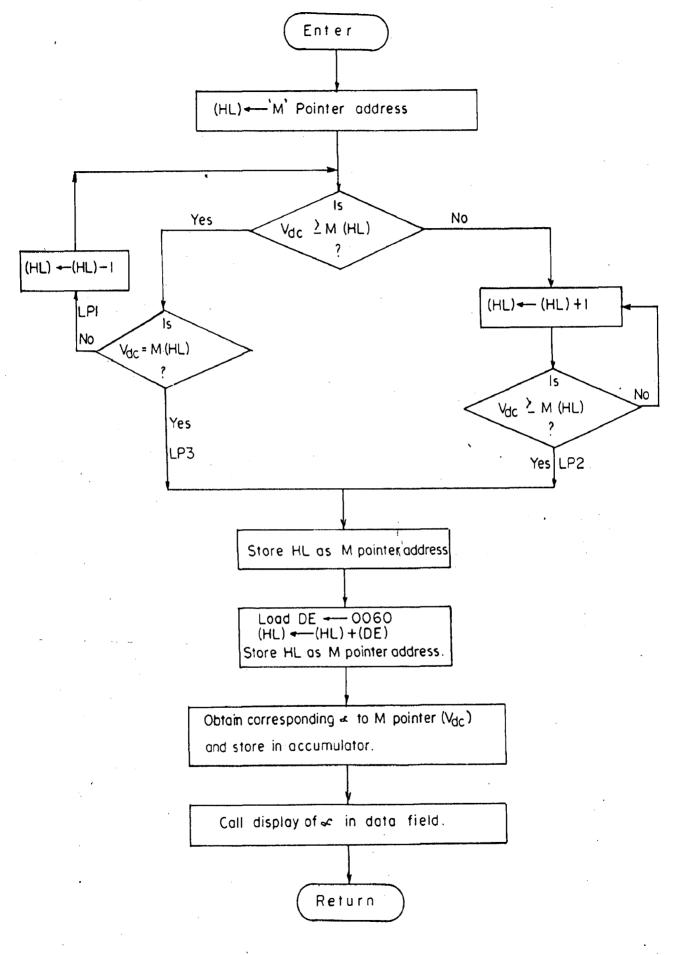

#### 4.3.8 Lookup algorithm Subroutine

While microprocessors potentially offer more flexibility and economy than the analog circuits, their relatively limited real time capabilities restrict their functions to table lookups and simple arithmatic operations. The determination of the necessary control requires only table lookup operations and computations are kept to a minimum. The control algorithm using the table lookup, becomes simple, meets the real time requirements, and its implementation is well within the capability of the present day microprocessors.

## Determination of lookup table values:

Assuming (1) continuous conduction mode of thyristor bridge converter.

- (2) Ignoring overlap period.

- (3) Fixed sequence R-Y-B of R.M.S. input voltage with constant frequency.

FIG.4.9 FLOW CHART FOR LOOK UP TABLE.

For a three phase fully controlled converter, D.C. . output voltage

$$V_{dc} = \frac{3\sqrt{6}}{\pi} V \cos \alpha$$

where V = RMS phase voltage

$\propto$  = Firing angle Maximum value of V<sub>dc</sub> occurs at  $\propto$  = 0<sup>0</sup>

$$V_{dc}$$

(max) =  $\frac{3\sqrt{6}}{11}$  V

Therefore

$$\frac{V_{dc}}{V_{dc}(max)} = \frac{\frac{3\sqrt{6}}{7T} \vee \cos \alpha}{\frac{3\sqrt{6}}{T} \vee} = \cos \alpha$$

$V_{dc}$  (normalised or  $V_{dn}$ ) varies from 'l' to '0' as firing angle ' $\propto$ ' is varied from 0<sup>°</sup> to 90<sup>°</sup>. The  $V_{dn}$  is represented by a one byte number and have  $V_{dn}$  (max) equal to 256 states. Therefore one state is of 1/256 equal to 0.003911 units.

For ' $\propto$ ' count;

360° corresponds to 20 m sec, Hence

$1^{\circ}$  corresponds to 20/360 m sec = 20/360 x  $10^{-3}$  sec.

Clock frequency of timer = 1.535 MHz

$$= 1.535 \times 10^{6} Hz$$

Time for one 'T' State =  $\frac{1}{1.535 \times 10^6}$  Secs

· · · Sec corresponds to 1.535 x  $10^6$  'T' States.

.:  $\frac{20}{360} \times 10^{-3}$  Sec corresponds to 1.535 x 10<sup>6</sup> x  $\frac{20}{360} \times 10^{3}$  'T' State

= 82.57 'T' States

l<sup>o</sup> count corresponds to 82.57 'T' States (Decimal)

l<sup>o</sup> count corresponds to 55H 'T' States (Hexa)

$\therefore \alpha_{\rm C} = \alpha^{\rm O} \times 55 {\rm H}$

The value of  $%_{\rm C}$  and  $V_{\rm dn}$  are formulated from the above equations for every 1° variation of firing angle in the range of 0° to 90°. The calculated value of  $\propto$ o and  $V_{\rm dc}$  are converted into Hexadecimal form and stored in the memory locations.

$V_{dn}$  is of one byte and  $\propto^{\circ}$  is also one byte. So in the look up table  $V_{dn}$  takes 90 memory locations and corresponding  $\propto^{\circ}$  takes 90 memory locations for storing.

The look up table consider here in which the  $V_{dn}$  values in decreasing order are stored at higher memory locations. The flowchart of it is shown in Fig.4.9.

NAME OF SUBROUTINE : Lookup INPUTS :

Constrained  $V_{dn}$  which is of 1 byte stored at CVDC address. Its 'm' pointer is loaded with the address having the starting address of  $V_{dn}$ .

It stores 'm' pointer (lookup) table address of  $V_{dn}$  (new) at

OUTPUTS

: 'm' address and also stores  $\propto^{\circ}$  corresponding to this voltage.

CALLS : None

DESTROYS : A, F, H, L

DESCRIPTION

: This subroutine stores lookup table address of  $V_{dn}$  (new) at 'm' address, and also stores  $\propto^{\circ}$  corresponds to  $V_{dn}$  (new) which is displayed in data field.

## 4.3.9 Mode Selection Subroutine

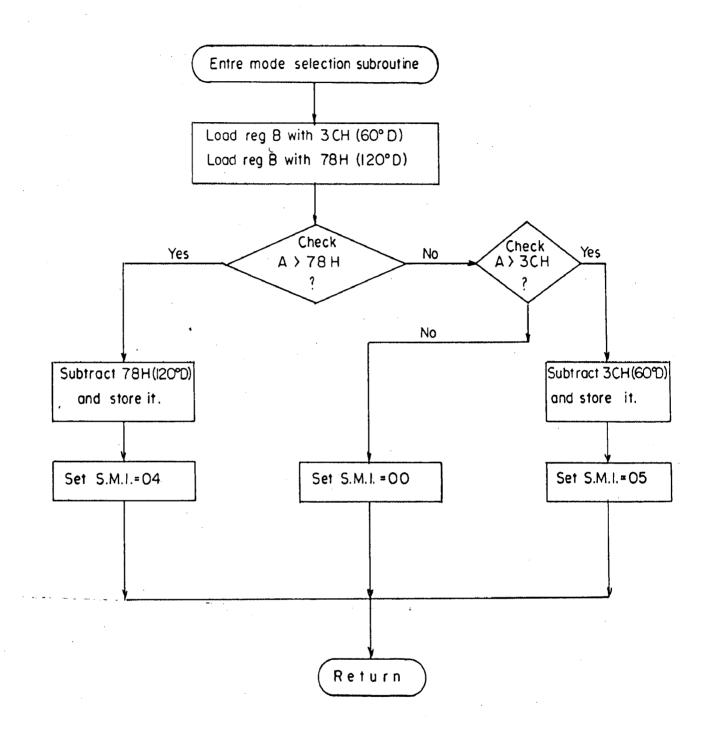

Depending upon the firing angle, it is necessary to fix up the sequence of thyristor firing. This is being done using Mode Selection Subroutine. If the firing angle is between  $0^{\circ}$  to  $60^{\circ}$  then Mode '0' is selected which specifies thyristor pair (6,1) has to be fired first and then the remaining pairs. If the firing angle is between  $60^{\circ}$  to  $120^{\circ}$ , then  $60^{\circ}$  is subtracted from it and Mode '5' being selected which specifies Thyristors pair (5,6) has to be fired first and then the remaining pairs. If the firing angle is between  $120^{\circ}$  to  $180^{\circ}$ , then  $120^{\circ}$  is subtracted from it and Mode '4' being selected which specifies thyristor pair (4,5) has to be fired first and the remaining pairs. Therefore, the mode selection helps us in fixing up the particular sequence of firing of thyristor.

NAME OF SUBROUTINE : MODE

INPUTS

Register B has 60° count.

Register C has 120° count.

Accumulator is having an 8 bit value of selected mode index.

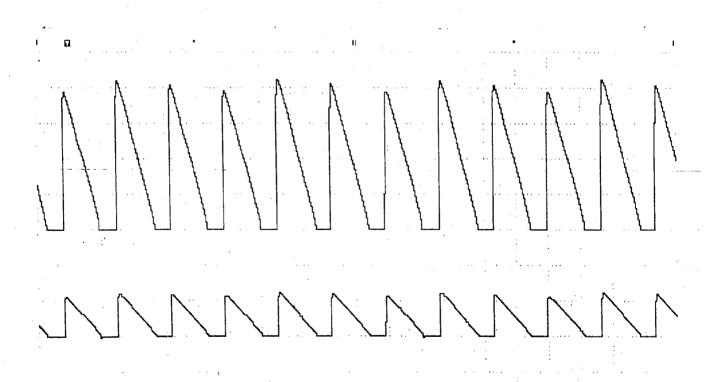

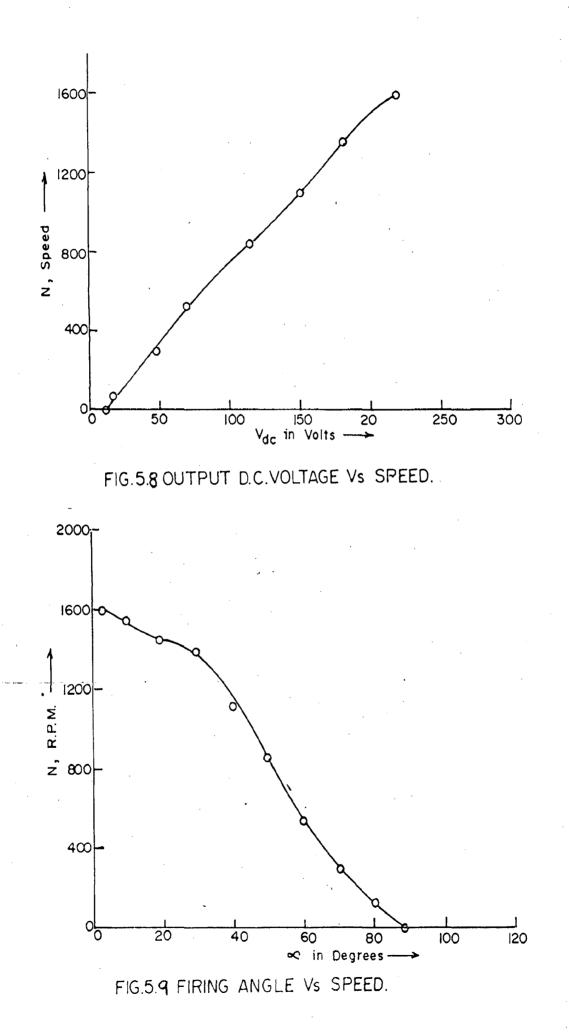

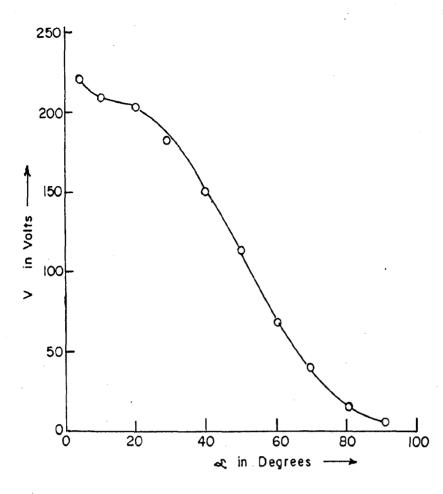

OUTPUTS