# "DEVELOPMENT OF MICROPROCESSOR BASED COMMUTATORLESS CONSTANT POWER KRAMER DRIVE"

## **A DISSERTATION**

Submitted in partial fulfilment of the requirements for the award of the degree

of

MASTER OF ENGINEERING

in

ELECTRICAL ENGINEERING

By

K. ALICE MARY

DEPARTMENT OF ELECTRICAL ENGINEERING UVIVERSITY OF ROORKEE ROORKEE-247 667 (INDIA) JUNE, 1989

## CANDIDATE'S DECLARATION

I hereby certify that the work which is being presented in the dissertation entitled DEVELOPMENT OF MICROPROCESSOR BASED COMMUTATORLESS CONSTANT POWER KRAMER DRIVE, in partial fulfilment of the requirement for the award of the degree of Master of Engineering in Electrical Engineering, University of Roorkee, Roorkee, is an authentic record of my own work carried out for a period of about seven months from August, 1988 to Feb ruary 1989 under the supervision of Dr. S.P.Gupta, Reader and Dr. Bhim Singh, Reader, Department of Electrical Engineering, University of Roorkee, Roorkee, India.

The matter embodied in the dissertation has not been submitted by me for the award of any other degree or diploma.

Dated June 23, 1989

This is to certify that the above statement made by the candidate is correct to the best of our knowledge.

(Dr. Bhim Singh) Reader Dept. of Electrical Engg. University of Roorkee, Roorkee-,247667,India

S. P. Cuple

(Dr. S.P.Gupta) Reader Dept. of Electrical Engg. University of Roorkee, Roorkee-247667, India

#### ACKNOWLEDGEMENT

I wish to express my deep sense of gratitude and indebtedness to my guides Dr. S.P.Gupta, Reader, Electrical Engineering Department, University of Roorkee, Roorkee and Dr. Bhim Singh, Reader, Electrical Engineering Department, University of Roorkee, Roorkee for constant guidance, encouragement and valuable suggestions at all stages to complete this work.

I am very grateful to Dr. R.B.Saxena, Professor and Head, Electrical Engineering Department, University of Roorkee, Roorkee for providing necessary facilities to carry out this work. I am grateful to the Principal, B.V.B.College of Engineering and Technology, Hubli for deputing me to persue this work. I am also thankful to the Ministry of Education, Government of India, for providing the financial assistance through the Q.I.P.Centre, University of Roorkee, Roorkee.

My sincere thanks should be paid to Dr. V.K.Verma, Professor, Electrical Engineering Department, Roorkee and Shri M.K.Vasantha, Reader Electrical Engineering Department, University of Roorkee, Roorkee for fulfilling the requirements in respect of the experimental set up.

contd...

A word of thanks goes to Mr. Shugun Giri and Mr. Tyagi working staff of the P.G.Lab. and Mr. Kalyan Singh and Mr. Rajender Singh working staff of the Microprocessor and Computer lab., Electrical Engineering Department, University of Roorkee, Roorkee, for their excellent co-operation during lab timings.

I am sincerely grateful to Sri P.S.Dothlhal, Research Scholar, Electrical Engineering Department, University of Roorkee, Roorkee for his kind advise/directions from time to time and sparing his valuable time for extending his help as and when needed.

The author also wishes to thank the many individuals especially my sister Capt. S.Vinodhini and my brother in law Dr. S.Pawan Kumar, Miss Indra Gupta, Miss Anupama Singhal and Miss Ila Kattiar, who deserve credit for assisting in preparation of this dissertation.

It is my pleasure to acknowledge my mother Smt. Kamalamma and my husband Dr. D.Koteshwara Rao, for their continuous prays and encouragement for completing this dissertation work.

Thanks are also due to Sh. D.C.Bhardwaj for his excellent and time bound typing of this thesis.

(Smt. K. ALTCE MARY)

## ABSTRACT

The dissertation concerns the Development of Micro processor Based Commutatorless Constant Power Kramer Drive which consists of a wound rotor Induction motor and a commutatorless motor. The slip power extracted from the stator terminals of the induction motor is rectified and converted to mechanical power by the commutatorless motor which is coupled mechanically to the induction motor shaft forming a constant power drive. The d.c. link consists of a rectifier, a chopper, and a commutatorless motor (CLM). The CLM is popularly known as commutatorless motor (CLM). The CLM is among the earliest attempts to replace the mechanical commutator of D.C.motor.

Speed control in the entire sub-synchronous region is accomplished by either varying the field current of ' the CLM, or the duty cycle of the chopper. By reducing the duty cycle of the chopper, the effective armature voltage of the CLM and hence the speed of the drive is reduced.

The firing pulses of the thyristors of ICI and chopper are generated by the microprocessor. The firing angle of LCI is kept constant through out the operation. The system description, principle of operation and imple mentation of the system software and flowcharts are presented. The performance characteristics of chopper controlled commutatorless Kramer drive are studied on a laboratory size experimental set up. It is shown that the voltage and current waveforms obtained with this scheme are sinusoidal and are almost free from harmonics.

## CONTENTS

CANDIDATE'S DECLARATION

ACKNOWLEDGEMENT

ABSTRACT

| CHAP | PAGE NO                                             |        |

|------|-----------------------------------------------------|--------|

| I.   | IN TRODUC TI ON                                     | ··· 1  |

|      | 1.1 GENERAL                                         | ••• 1  |

|      | 1.2 LITERATURE SURVEY                               | ••• 7  |

|      | 1.3 SCOPE OF THE PRESENT WORK                       | 11     |

|      | 1.4 OUTLINE OF THE CHAPTERS                         | 12     |

| II.  | DESCRIPTION OF THE SYSTEM                           | ••• 14 |

|      | 2.1 GENERAL                                         | ••• 14 |

|      | 2.2 PRINCIPLE OF OPERATION                          | ••• 14 |

|      | 2.3 SYSTEM DESCRIPTION                              | 16     |

|      | 2.4 POWER AMPLIFIER CIRCUIT                         | 21     |

|      | 2.5 INTERFACING OF 8253                             | 23     |

|      | 2.6 INTERFACING OF ADC                              | 24     |

|      | 2.7 DESIGN OF POWER CIRCUIT                         | 25     |

|      | 2.8 CONCLUSIONS                                     | 27     |

| III. | IMPLEMENTATION OF SYSTEM SOFTWARE<br>AND FLOWCHARTS | 28     |

|      | 3.1 GENERAL                                         | 28     |

|      | 3.2 MAIN PROGRAM ROUTINE                            | 28     |

|      | 3.3 ADC SUBROUTINE                                  | 31     |

|      | 3.4 MULT SUBROUTINE                                 | 31     |

|      | 3.5 IRO INTERRUPT SUBROUTINE                        | ••• 32 |

| •    | 3,6 IR2 INTERRUPT SUBROUTINE                        | 32     |

|      | 3.7 IR5 INTERRUPT SUBROUTINE                        | ••• 33 |

|      | 3.8 CONCLUSTONS                                     | 33     |

contd..

| CHAP TERS                                                                                                            | PAGE NO                    |  |  |

|----------------------------------------------------------------------------------------------------------------------|----------------------------|--|--|

| IV. STEADY STATE PERFORMANCE OF THE DRIVE<br>SYSTEM                                                                  | ••• 35                     |  |  |

| 4.1 GENERAL                                                                                                          | ••• 35                     |  |  |

| 4.2 EXPERIMENTAL INVESTIGATIONS                                                                                      | ••• 35                     |  |  |

| 4.2.1 Starting of Chopper Controlled<br>Commutatorless Kramer drive                                                  | ••• 36                     |  |  |

| 4.2.2 Tests at No Load                                                                                               | ••• 38                     |  |  |

| 4.2.3 Tests at load                                                                                                  | ••• 38                     |  |  |

| 4.3 RESULTS AND DISCUSSIONS                                                                                          | ••• 39                     |  |  |

| 4.4 CONCLUSIONS                                                                                                      | ••• 43                     |  |  |

| CHAPTER<br>V. CONCLUSIONS AND SUGGESTIONS FOR<br>FURTHER WORK<br>5.1 CONCLUSIONS<br>5.2 SUGGESTIONS FOR FURTHER WORK | ••• 44<br>••• 45<br>••• 46 |  |  |

| REFERENCES                                                                                                           | . 40                       |  |  |

APPENDIX - I DETAILS OF MACHINES USED

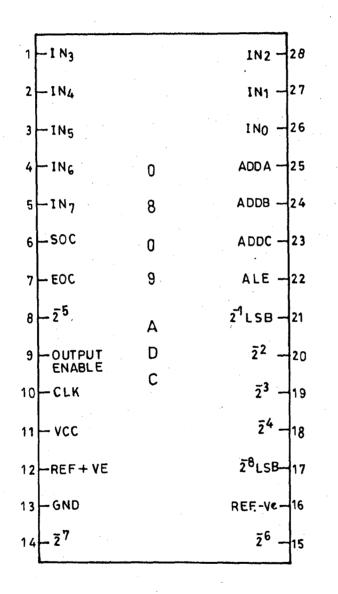

APPENDIX - II DETAILS OF ADC 0809 PIN CONFIGURATIONS

APPENDIX -III ASSEMBLY LANGUAGE PROGRAM DEVELOPED FOR FIRING THYRISTORS OF LCI AND CHOPPER

APPENDIX - IV PHOTOGRAPHS OF THE EXPERIMENTAL SET UP

## CHAPTER - 1

#### INTRODUCTION

#### 1.1 GENERAL

Variable speed drives may be realised by using d.c. motor or a.c. motor as the drive motor. A d.c. motor offers simpler means for stepless speed control below and above the base speed in comparison with a.c. motor. However, the d.c. motor suffers from the disadvantages, listed below, on account of its commutator.

- (a) It limits the power rating and speed of the machines that can be built.

- (b) It imposes restrictions on the ambient conditions,

- (c) It prevents full targue at standstill for more than a few seconds.

- (d) It increases the length, weight and inertia of the motor which are the disadvantages for several applications such as traction, servo drives etc.

Furthermore, D.C. machines are of complicated mechanical construction and hence more expensive. For these reasons engineers have investigated for a long time, the possibilities of variable speed drives which use A.C.motors.

Some of the advantages of A.C. motors over D.C. motors are -

(i) simple and robust construction.

- (ii) no commutator and hence sparking problems are not present. Hence, a.c. motors can perform much better in explosive atmospheric conditions.

- (iii) higher power/weight ratio.

- (iv) less maintenance and hence running cost.

- (v) Though a.c. motor is considerably cheap compared to D.C.motor, cost of static inverter is comparatively much higher than converter. In general, above 50 KVA, the difference in cost of motors is more dominating and hence now-a-days a.c. drives are recommended on economic considerations.

With numerous other merits available with a.c. drives, present trend is to use a.c. drives [1-3].

Two basic modes of operation of variable speed a.c. drives have been identified as synchronous and non-synchronous and two basic methods of control namely frequency control and control of rotor voltage, Synchronous motor drives can only be frequency controlled. Now - synchronous drives can be controlled by either method.

The induction machine is most commonly used in adjustable speed a.c. drive system. Between the two classes of induction machines-squibbel cage and wound rotor, the former is always preferred, because the wound rotor machine is more bulky and expensive and has the additional disadvantages due to the

presence of slip-rings and brushes. The wound rotor machines had long been used for inexpensive speed control by mechanically varying the rotor circuit rheostats. One advantage of this type of machines is that slip power becomes available which can be controlled to control the speed of the machine. For limited range speed-control applications, where the slip power is only a fraction of the total power of the machine, the converter cost reduction may be substantial. The advantage of this system is that the slip power can be controlled to flow either cut of the rotor  $_{\Lambda}^{\text{or}}$  to the rotor and thus super-synchronous regions with motoring can also be achieved.

#### ROTOR RESISTANCE CONTROL

The speed of a wound rotor machine can be varied by varying the rotor circuit resistance through an externally connected resistor bank. Also thyristor chopper circuit is used [4-15] on the rotor side for the speed control of slipring induction motor drive. This control scheme provides contactless and continuous variation of rotor resistance. Rotor resistance control is very inefficient because the slipenergy is wasted in the rotor circuit resistance.

#### SLIP POWER RECOVERY

Instead of washing the slip-power in the rotor circuit resistance, it can be either converted to a.c. and pumped back to the supply lines forming a constant torque type

system or used more directly by converting it into mechanical power and adding the same to the main shaft, thus forming a constant power type system.[6,7]. The former method, where the slip power is recovered back to the line through a converter cascade is known as static Kramer drive [8-11].

The digital Kramer drive system used a rotory converter instead of a diode rectifier and fed power to a d.c. motor coupled to the Induction machine shaft. After the second world war, a modified Kramer Revival' using a transformer/mercuryarc rectifier combination as a converter was successfully applied to several mine ventillating fon drives [12-14]. This drive system is not only efficient but the converter power rating is low, because it has to handle only the slip power. This power rating becomes lower for a more restricted speed range near the synchronous speed. The additional advantages are that the drive system has characteristics like d.c. machine and the control circuit is simple. These advantages off set to some extent the disadvantages of the wound-rotor machine and poor power factor characteristics.

The static Kramer systems do not have the regenerative mode of operation. This feature requires that the slip power in the rotor should flow in the reverse direction. If the diode bridge rectifier is replaced by thyristor bridge, the slip power flow can be controlled in either direction. Such a static Kramer system with a bi-directional slip-power flow

can be controlled for motoring and regeneration both in sub-synchronous and super-synchronous ranges of speed. The dual converter system in a static Kramer drive can be replaced by a single - phase controlled line commutated cycloconverter to permit the slip-power flow in either direction, such a scheme is known as a Static Scherbius drive. This type of drive has poor power factor characteristics.

The use of inverter circuits [16-18] so far reported for speed control of induction motor are ussually of forced commutated type and the risk of commutation failure is more because of high instantaneous currents and steep rise in voltages at the time of commutation. The use of cyclo converter circuits gives limited variations in frequency and requires complicated trigger circuits. Because of these limitations, these circuits are not reliable in case of group drive applications, such as intraction system and textile industry. To overcome some of these disadvantages of forced commutated inverter circuits. a d.c. link inverter consisting of inverter - synchronous machine combination as a variable frequency source is been discussed by Ranganadhachari et.al. [19]. The d.c. link inverter and synchronous machine combination is popularly known as commutatorless D.C. machine (CLM). This drive system is comparable to the variable speed d.c. drive and some of the limitations of variable speed d.c.

machines that is, commutator effect at higher speed can be overcome in this system.

A scheme for power factor improvement for very high power applications is known as the commutatorless Kramer system [20-25] for large capacity induction motors. The speed and torque of the drive system are controlled by the inverter firing angle and field current so that the line commutation of the inverter is possible at optimum firing angle on different speeds. As a characteristic of the line commutated inverter drive, speed control is not possible at a low value of speed because of insufficient counter emf.

To reduce the speed of the drive down to almost zero a chopper is included in the armature circuit of the D.C. motor of the Kramer drive. The use of thyristor chopper is very favourable because of high efficiency, flexibility in control, small size and quick response to very low speeds. The output voltage of the chopper can be controlled by using thyristor firing techniques to produce time ratio control or current limit control. The chopper may then be operated either at a constant frequency or at a constant ON or OFF time abd variable frequency. Between the different methods of time-ratio control, the one with variable ON-time and constant frequency is preferable because it permits a choice of frequency suitable to the supply. The commutation circuit, the filter circuit and the load ensuring fast response.

By controlling the duty cycle of the chopper, the effective armature voltage of the d.c. motor is controlled and it is possible to reduce the speed of the drive down to almost zero [26-28].

The firing circuit for a 3-phase variable frequency thyristor bridge is developed by Naik et.al [29]. The microprocessor has opened up an existing range of opportunities to the variable speed drives [31-35]. In the present work, a microprocessor based chopper controlled commutatorless Kramer drive is considered to study the performance of the drive system.

#### 1.2 LI TERATURE SURVEY

A larger volume of research work has been published on the Kramer drive. From the literature review it is found that not much work has so far been reported on chopper controlled commutatorless Kramer drive. Bose [1] reviewed the present status of ac drive technology in which the salient technical features of ac machines, converters, controls and performances of the integrated drive systems are described. Jones and Brown [2] outlined the control of speed of electrical machines from the earlier methods to their modern equivalents using electronic control.

The variable speed ac drives are identified as Induction motors and synchronous motor drives. The wound rotor machines were long been used for speed control by

verying the rotor circuit rheostates. The speed control of slip ring induction motor is also reported using thyristor chopper controlled resistance in the rotor circuit [4 and 5]. This control scheme provides contactless and continuous variation of rotor resistance.

Instead of wasting the power in the rotor circuit as heat, the slip power may be either returned to the shaft of the main motor or returned to the supply after modifying its frequency to be equal to supply frequency. Shepherd and Khalil [6] investigated the improvement of the power factor using capacitor in the rotor circuit of slip energy recovery system and also using two sets windings in the rotor [7]. Mittle and Venkatesan [8 and 9] determined stability and instability region of a static slip region of a static slip-power recovery drive. Doradla et.al.[11] investigated a new slip-power recovery scheme with a PWM converter with the improved supply power factor. The speed and torque characteristics of this drive were similar to those of a separately excited d.c. motor.

The basic Kramer combination developed some 80 years ago, used a rotary converter to provide the mecessary slipfrequency ac to dc conversion. But the cost of providing, maintenance, multiplicity of machines and brush gear naturally told rather heavily against this type of drive. Clapham and Griffin [12] have described the usefulness of modified Kramer system

for large power outputs using a transformer/mercury are rectifier combination as a converter. The only limitation is that the rectifier in the Kramer combination constitutes a non-return value and this prevents the bi-directional power flow possible in the a.c. commutator motor. In consequence, power can be abstracted (only) from the rotor and not supplied to it and thus the speed range is extended from just under synchronous speed down to half synchronous speed and below [13 and 14].

When the applications of conventional d.c. machines are limited by their commutator they can be replaced by an equivalent system of a static convertor and an a.c. machine the combination of a synchronous motor and a load commutated inverter is well adopted to high power levels and is popularly known as commutatorless motor (CIM). The inverter circuit is a fully controlled thyristor bridge [16-18], triggered synchronously with the revolution of the rotor of the machine. Ranganadhachari et al [19] attempted for the feasibility of a CLM as a variable frequency source to the induction motor. The main feature of this variable frequency operation of induction motor is that it provides continuous control over a wide range of speed and is efficient. Okuyama [21] has discussed the effects of machine constants on steady state and transient characteristics of commutatorless motors. Nacto [22] discussed the effect of field current fluctuations on operating performance of the CLM.

Kuniomi Oguchi [24] proposed the speed control of a brushless static Kramer system. He discussed the various control methods such as field control method, chopper control method, and advance angle control method on the drive system. He showed that the smooth speed variation is possible by chopper control. Wakabayashi [25] described the commutatorless Kramer control system and applied commercially for driving large capacity pumps. Venkatesan and Gupta [26 and 28] suggested a method to extend the speed range in the sub synchronous region down to almost zero by including a chopper in the modified Kramer system. The steady state performance of this system is also discussed [27].

A firing circuit for the 3-phase variable frequency thyristor bridge inverter is given by Naik et.al. [29].The firing pulses for the thyristors of the ICI and the chopper are generated by a microprocessor. Richter [34] have discussed the microprocessor controlled inverter-fed synchronous motor. The important advantage of microprocessor control is that of flexibility. No hardware changes are required if it is desirable or necessary to make control modifications. Chakaraborty [35] has discussed the microprocessor controlled commutatorless d.c. series motor by using induced voltage commutated inverter along with the induced voltage sensor.

In the present work, a microprocessor based chopper controlled commutatorless constant power Kramer drive is fabricated and experimental performance characteristics are obtained.

#### 1.3 SCOPE OF THE PRESENT WORK

The present work is concerned with the development of the microprocessor based commutatorless constant power Kramer drive. Which consists of a wound roter induction motor (main motor) and a synchronous motor (auxiliary motor) mechanically coupled to the same shaft of the main motor and load. The slip power extracted from the stator terminals of the induction motor is rectified by an uncontrolled rectifier bridge. The d.c. link consists of a d.c. chopper and an inductor which are connected to the load commutated inverter which supplies power from the d.c. source to the synchronous motor. The d.c. link inverter-synchronous motor combination is popularly known as commutatorless d.c. motor (CLM). This drive system is comparable to the variable speed d.c. drive and some of the limitations of variable speed d.c. machines, namely, the commutator effect at higher speed can be overcome in this system. The function of the inductor on the dc side is to smooth out current undulations and to make the current continuous in the circuit.

The speed of the drive system can be either varied by varying the duty cycle of the chopper thus varying the

d.c. link voltage or by varying the field excitation of the synchronous motor. Speed control in a wide range from synchronous down to almost zero could be obtained. However, the field weakening of the CLM causes commutation failure due to insufficient induced emf available at synchronous motor terminals. So field current should not be reduced to very low values.

A simple microprocessor based firing control scheme using reduced hardware components are designed, fabricated and tested. The no load test is carried out on the chopper controlled commutatorless constant power Kramer drive by varying the field current of the separately excited CLM with constant duty cycle of the chopper&varying the duty cycle with constant field current of the CLM. The load test is performed on the drive at different duty cycle and field current settings and the steady state performance of the drive is obtained experimentally. The waveforms and oscillograms at different points of the control circuit and power circuit are recorded and discussed.

#### 1.4 OUTLINE OF THE CHAPTERS

In chapter II, the complete hardware of the present scheme is discussed in detail. The design of power circuit, microprocessor based firing control circuit using less hardware componebts, pulse amplifier and ADC circuits are presented in this chapter.

The implementation of software and flowcharts of the chopper controlled commutatorless Kramer drive is discussed in Chapter III. The various subroutines used in conjunction with the main program such as ADC, subroutine, MULT subroutine,  $IR_0$ ,  $IR_2$  and  $IR_5$  interrupt subroutine are also developed in this chapter.

Chapter IV deals with the experimental steady state performance of the drive system. Conclusions and suggestions for further work are discussed in chapter V.

The rating of the machine pin details and connection diagram of ADC chip and assembly language program for steady state performance of the drive are given in APPENDICES.

## CHAPTER - II

## DESCRIPTION OF THE SYSTEM

## 2.1 GENERAL

A chopper controlled commutatorless kramer drive system presents a constant power type **slip** energy recovery drive, which is different with respect to the conventional Kramer drive, in that the d.c. motor is replaced by commutatorless d.c. motor. The commutatorless d.c.motor is obtained by feeding a synchronous motor from a 3-phase inverter whose firing constants are synchronized with its speed and which is naturally commutated by the 3-phase voltages available at its output terminals in the form of induced emf of the synchronous motor. A chopper is included in the d.c. link to effectively control armature voltage of the d.c. motor and thereby control the shaft speed in sub-synchronous region.A microprocessor based control scheme for line commutated inverter and the time ratio control of the chopper is described in detail.

## 2.2 PRINCIPLE OF OPERATION

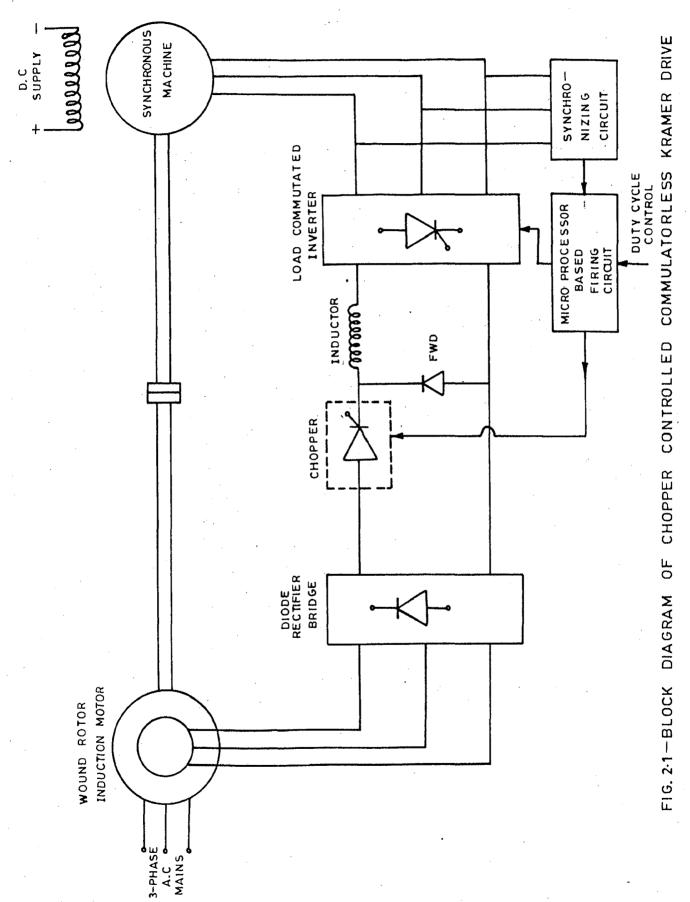

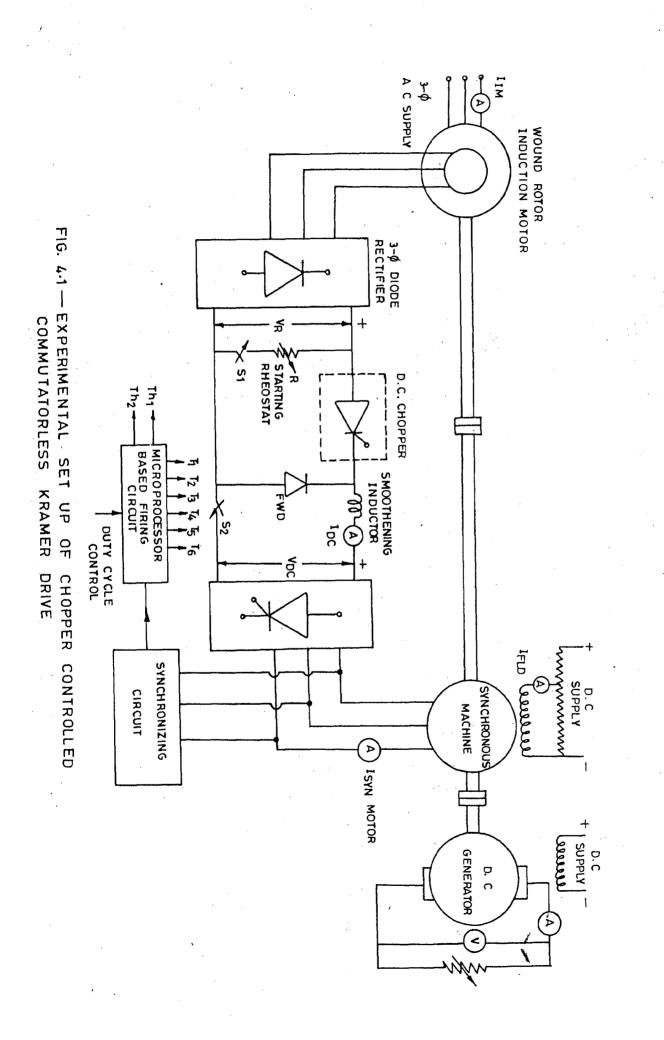

A block diagram of the system considered is shown in Fig. 2.1. It consists of a wound rotor Induction motor, an uncontrolled diode bridge rectifier, a smoothening d.c. link inductor, a series connected chopper, a line commutated inverter and a synchronous motor whose field is separately excited. The rectifier bridge along with the d.c. chopper

and the d.c. link inductor forms the variable d.c. source. The variable d.c. voltage is impressed at the d.c. input terminals of the line commutated inverter (ICI). The ICI supplies power from the D.C. source to the synchronous machine. It is a three phase fully controlled SCR bridge and can be operated in an inverter mode by suitably chosing the firing angle between  $90^{\circ}$  and  $180^{\circ}$ . The synchronous machine is a conventional one. The inverter-synchronous machine along with the synchronising gating circuit constitutes a commutatorless d.c. motor (GIM)

The system is started by running the synchronous machine as a synchronous generator with Induction motor acting as prime mover and the firing pulses for invertor thyristors are derived from the generated emf of the synchronous machine stator by the induced voltage sensor. The firing pulses are generated by means of microprocessor to the thyristors of the inverter and the chopper. The input power to LCI is in creased by duty cycle so that the inverter input d.c. voltage increases and power is pushed through LCI from d.c. side to a.c. side. The synchronous machine now operates as a motor offering characteristics of a separately excited d.c. motor. control of this commutatorless Kramer drive is The speed obtained either by varying the d.c. input voltage which is achieved by varying the duty cycle of the chopper or by changing the field excitation of the synchronous motor. By controlling the duty cycle of the chopper, it is possible to reduce the speed of the drive down to very close to zero.

## 2.3 SYSTEM DESCRIPTION

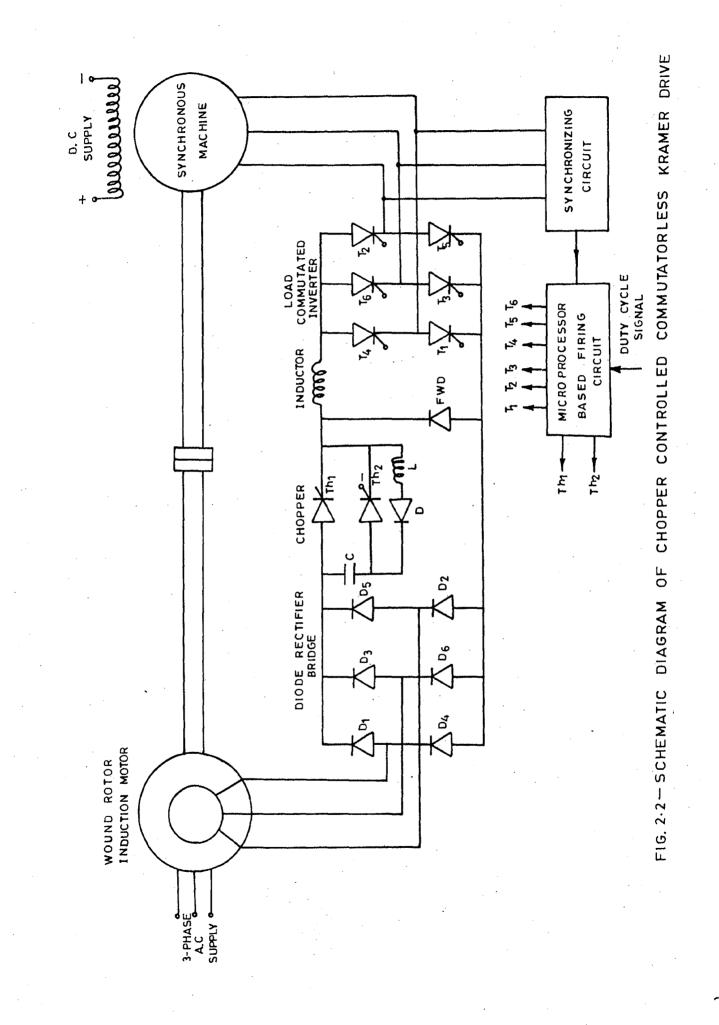

The schematic diagram of the chopper controlled commutatorless Kramer drive using induced voltage commutation along with the voltage sensor for synchronization is shown in Fig. 2.2. The major components comprising the system are briefly discussed as under.

(i) Three phase wound rotor Induction motor.

It is a conventional Induction motor whose sliprings are connected to an uncontrolled diode rectifier bridge. The slip power is extracted and then rectified supply is fed to the commutator less machine which is coupled to the same shaft of the Induction motor, thus obtaining a constant power drive system.

(ii) Uncontrolled diode bridge rectifier.

The function of the diode rectifier is to rectify the rotor frequency ac voltage to a dc voltage and the bridge configuration gives better utilization of the motor giving a six pulse output.

(iii) D.C.Chopper

Choppers are widely used for speed control of separately excited D.C.motor as they offer high efficiency quick response, wide speed control range down to very low speeds. The firing pulses are generated by the microcomputer to trigger the main and euxiliary thyristors TH<sub>1</sub> and Th<sub>2</sub>, of

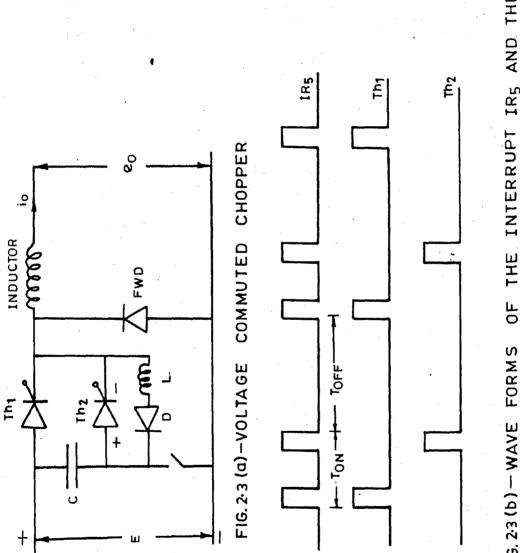

the chopper. The main thyristor in a chopper has to be turned off by auxiliary commutation circuitary. The voltage commutation circuit comprises an auxiliary thyristor Th, a diode D, an inductor I, and capacitor C. To start the circuit, capacitor C is initially charged by firing the thyristor Th2, charging is now from the source via Th, and loadwith the charging thyristor turning off CS the charging current decays to zero. Fig 2.3 shows the voltage commutated chopper. The output voltage of chopper is usually controlled either by using time ratio control(IRC) or by using current limit control (CLC). In IRC. the ON to OFF time ratio is adjusted. The chopper may then be 👐 operated either at a fixed frequency and variable ON ar OFF time ar at a variable frequency and fixed ON or OFF time. In CLC, the load current is restricted between specified maximum and minimum values by using suitable firing techniques Although both the schemes have relative advantages and limitations, choppers with variable ON time and fixed frequency are preferable because these are simple and provide flexibility in control.

(iv) D.C. link inductor.

The function of the D.C. link inductor is to smooth out the current undulations and to make the current continuous in the circuit. Hence a large value of inductance is connected in the d.c. link of the system.

FIRING PULSES FOR MAIN AND AUXILIARY THYRISTORS FIG. 23 (b) - WAVE FORMS OF THE INTERRUPT IR5 AND THE

(v) Line commutated inverter (LCI)

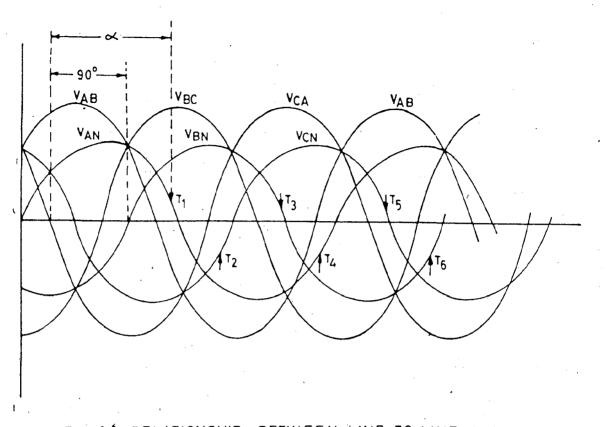

It is a simple three phase thyristorized inverter bridge. It converts the d.c. voltage into ac voltage of variable amplitude and frequency. The induced voltage in the stator of the synchronous machine is utilised to gene rate the firing pulses for inverter thyristors. The relationship between line to line and line to neutral voltages at synchronous machine terminals along with the firing instants of the thyristors are shown in Fig. 2.4. The thyristors T<sub>1</sub>, T<sub>3</sub>, T<sub>5</sub> are called positive group since they are turned on when the machine terminal voltages are positive, similarly the thyristors  $T_{\mu}$ ,  $T_{5}$ ,  $T_{2}$  are called negative group SCRs. Sime they are triggered when the machine voltages are negative. The firing angle of the inverter is always greater than  $90^{\circ}$  and measured from the instant of crossing point of two phase voltages as shown in Fig. 2.4. In the normal operation, always two thyristors one from positive group and another from negative group will remain in conduction. Thyristors are triggered at 60° interval with respect to the terminal voltage frequency. Each thyristor conducts for a period of  $120^{\circ}$  and the frequency of current is same as that of machine terminal voltage. In case of LCI, machine current always leads the corresponding phase voltage. The d.c. output voltage of a fully controlled converter is given by the following equation.

FIG. 24-RELATIONSHIP BETWEEN LINE TO LINE AND LINE TO NEUTRAL VOLTAGE ALONG WITH INSTANT OF FIRING

÷

ł

ł

L

| × |                                   |        | TABLE    | 2.1              |          |           |                    |

|---|-----------------------------------|--------|----------|------------------|----------|-----------|--------------------|

|   | CONDUCTION<br>DURATION            | 0° 60° | 60°-120° | 120 <sup>°</sup> | 180°240° | 240 - 300 | 300 <b>°</b> –360° |

|   | FIRING<br>SEQUENCE                | 1      | 2        | 3                | 4        | 5         | 6                  |

|   | THYRISTOR<br>PAIR TO BE<br>FIRIED | 6,1    | 1,2      | 2,3              | 3,4      | 4,5       | 5,6                |

$$V_{dc} = \frac{3/6}{\pi} V \cos \alpha = Em \cos \alpha$$

where V = per phase ac voltage.

If a d.c. voltage source is connected to the inverter bridge in proper polarity and magnitude (>  $V_{dc}$ ) then it will feed the power to the A.C. system through the controlled circuit.

(vi) Synchronous motor

It is a conventional synchronous motor and operated as a variable speed motor. The back emf of synchronous motor is used for natural commutation of the inverter thyristors. The frequency of the inverter is a function of the motor speed.

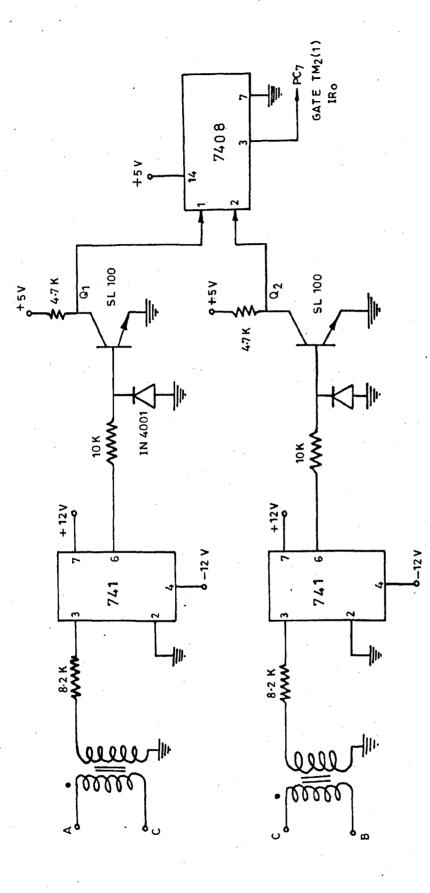

(vii) Synchronizing circuit

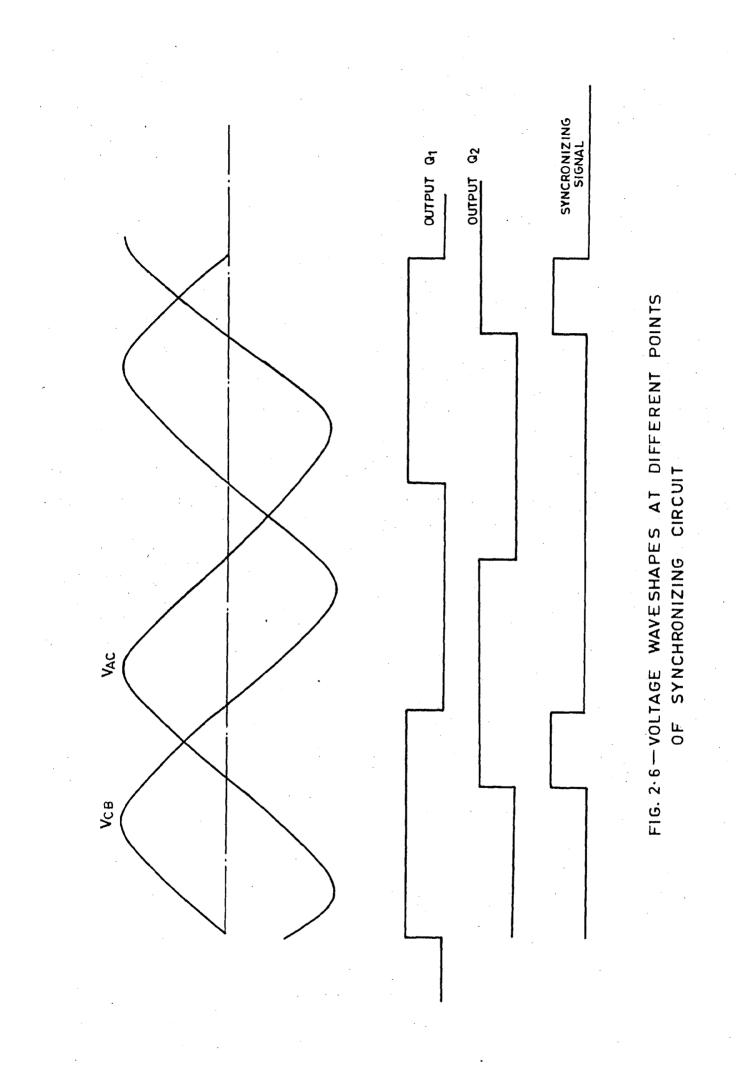

It consists of step down transformers, comparator, switching transistor, and AND gate. Synchronizing signal is derived from the line to line terminal voltages of the synchronous machine  $V_{AC}$  and  $V_{CB}$  and it is of 60° pulse width of the machine frequency at every cycle. This signal gives information about the operating frequency of the machine terminal voltage and 60° delay count.

Fig. 2.5 shows a zero-crossing detector circuit using IC 741.IC 741 is a voltage comparator. The output of which is a square wave on the principle of voltage comparison, that is the output swings ideally between +12V and -12V at every zero crossing of machine voltage frequency. The output of comparator

FIG. 2.5-SYNCHRONIZING CIRCUIT

J

- 1

is reduced to a lower voltage by a series connected resistor at the base of the transistor. The positive swing drives the transistor in to saturation producing a TTL input of approximately 0 volts and the negative swing drives the transistor in to cut-off producing an input of +5 volts. Thus the transistor inverts the input control signal. The diode in the base circuit protects the base against excessive reverse voltage as the negative output of the comparator approaches -12 volts. The two output signals of the transistor are ANDed in two input AND gate, IC 7408. It gives the required synchronizing signal of  $60^{\circ}$  pulse width as shown in Fig. 2.6 which is used to generate the firing pulses by the microprocessor.

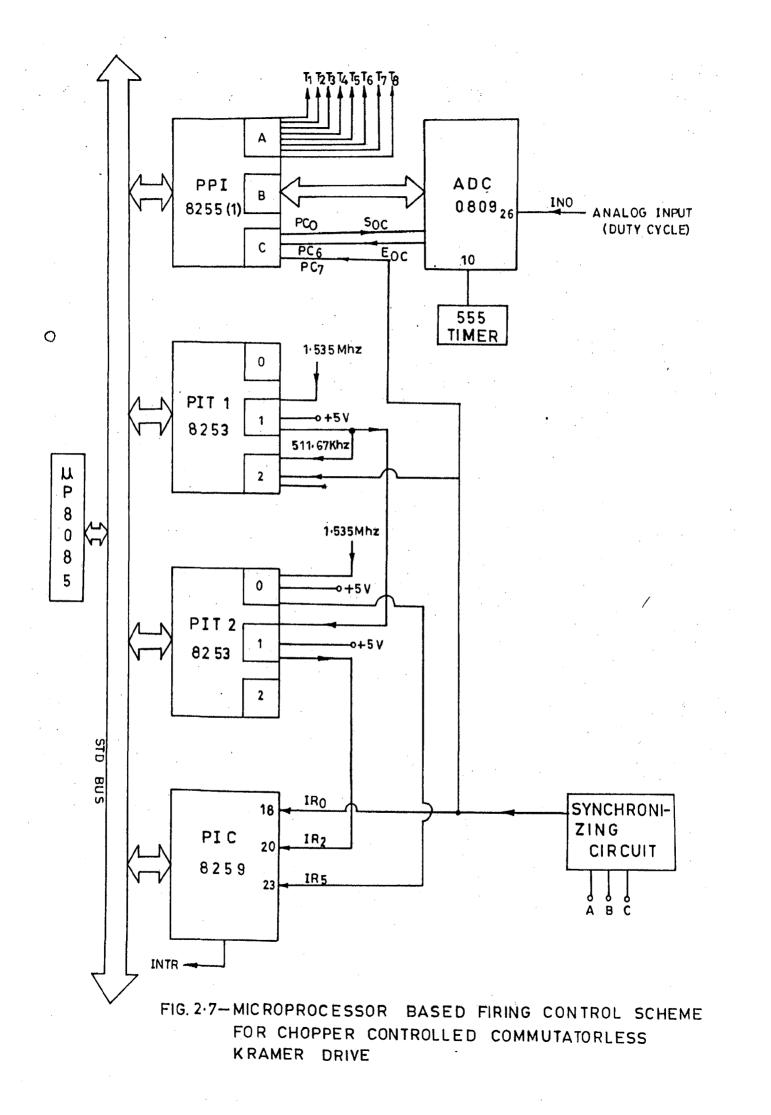

## (viii) Microprocessor based control circuit

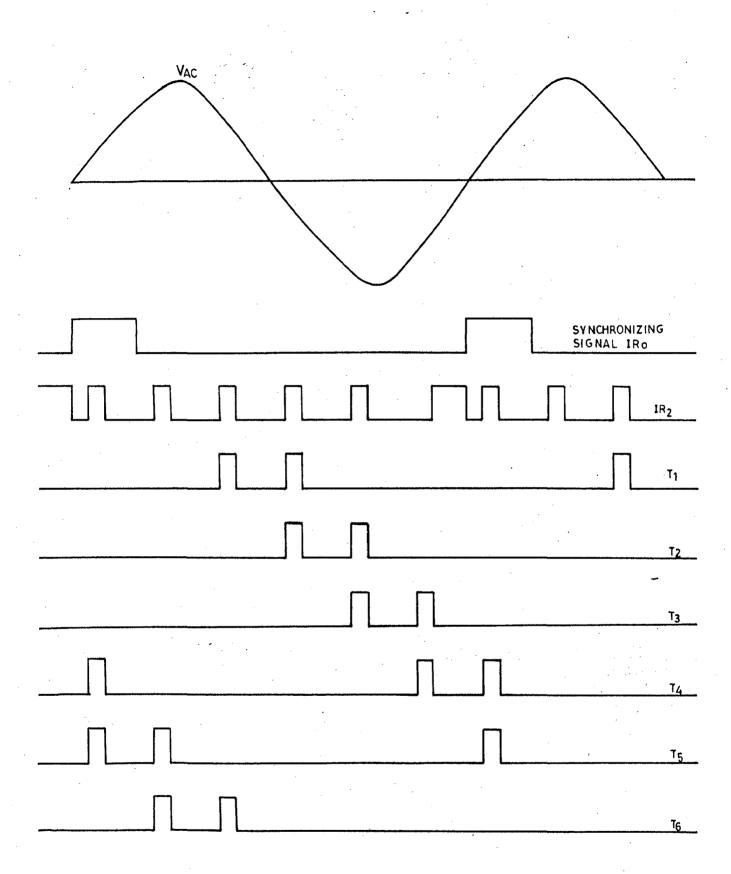

The control circuit to generate the firing pulses for thyristors of LCI and chopper has two programmable interval timer (PIT -8253A), one programmable interrupt controller (PIC-8259) which is shown in Fig. 2.7. The synchronizing signal derived from machine terminal voltages is inputted to PC<sub>7</sub> of programmable peripheral interface (PPI-8255), gate of counter<sub>2</sub>(1) and IRO pin of 8259A. The status of PC<sub>7</sub> is checked at every instant by the microprocessor to load the counter TM<sub>2</sub>(1) with FFFF H for the calculation of  $60^{\circ}$  count. A clock of 511.67 KHz is generated by operating TM<sub>1</sub>(1) in mode 2 from a clock of 1.535 MHz. This clock is provided to the TM<sub>2</sub>(1) and TM<sub>1</sub>(2). All the counters except TM<sub>7</sub>(1)

FIG.2.8-SYNCHRONIZING SIGNAL, IR2, FIRING PULSES IN PROPER SEQUENCE OF SIX CHANNELS

are programmed in mode 0. Counter  $TM_{1}(2)$  is used to load  $(\alpha-120^{\circ})$  count for the first time to generate firing pulses for (4.5) thyristors of the inverter and then the same counter  $IM_{1}(2)$  is used to load  $60^{\circ}$  count to generate firing pulses for the other next five pairs of thyristors of the inverter. Counter  $\text{TM}_{0}(2)$  is used to load  $\text{T}_{ON}/(\text{T}_{OFF})$  period in mode 0, at the clock frequency of 1.535 MHz to fire the auxiliary and main thyristors of the chopper accordingly. ADC 0809 is interfaced to the microprocessor through port B and port C of 8255A. ADC provides information about duty cycle of the chopper. The duty cycle can be changed linearly by varying analog input to the ADC through a 4.7K pot connected in series to a 8.2 K resistor. The firing pulses for the Thyristors are outputted through port A of 8255A as per the firing command word. The output of counter  $IM_1(2)$ , synchronizing signal and generation of firing pulses are shown in Fig. 2.8. The duration of firing pulses generated by the microcomputer via 8255A is very small. The firing pulse duration is increased to 0.72 m seconds through a monostable multivibrator circuit. These firing pulses are amplified using a pulse amplifier circuit which is described in the following section.

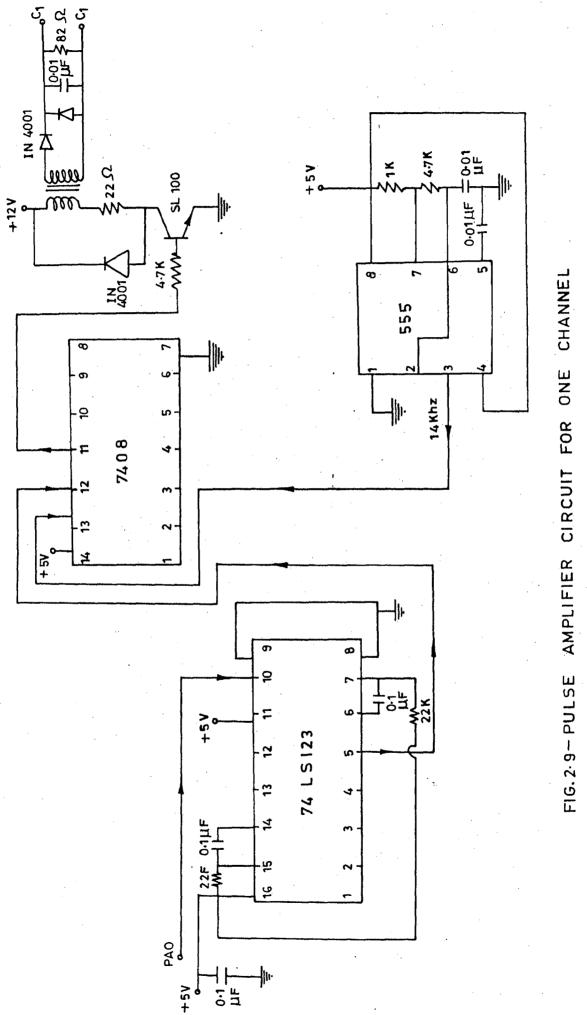

#### 2.4 POWER AMPLIFIER CIRCUIT

Fig. 2.9 shows the power amplifier circuit for one channel. It consists of

- (a) Monostable multivibrator

- (b) Oscillator

- (c) AND gate

- (d) Pulse amplifier.

# (a) Monostable multivibrator

An output pulse of 0.73 in seconds width is produced by a 74123 retriggerable monostable multibrator. This pulse width is decided by the externally connected R and C which is given by the formula

$T_{\rm W} = 0.33 \ {\rm Rc}$

where, R and C are selected as 22 K ohm and 0.1 uF.

#### (b) Oscillator

IC 555 timer is used as oscillator. The frequency of timer is given by

$$f = \frac{1.44}{(R_A + 2R_B) CT}$$

where

$R_A = 1K$ ,  $R_B = 4.7$  K and CT = 0.01 uF which gives a frequency of 14 KHz.

#### (c) AND gate

The output pulses from the monostable multivibrator are at low frequency, hence they are ANDed with a high frequency modulating signal obtained from IC 555 oscillator with a frequency of 14 KHz. This prevents the saturation of pulse transformer in the pulse amplifier circuit.

# (d) <u>Pulse amplifier</u>

The strength of the AND gate output pulses is amplified using the pulse amplifier circuit. A pulse transformer is used for electrical isolation between control circuit and power circuit as shown in Fig. 2.9. The diode across the primary windings of the transformer avoids the saturation of the pulse transformer, and also protects the transistor. A diode in series with the secondary winding blocks the negative pulse. A diode across the secondary of the transormer protects the gate of the thyristor from long reverse voltages. The capacitor across the secondary prevents any spurious high frequency from tri ggering the thyristors.

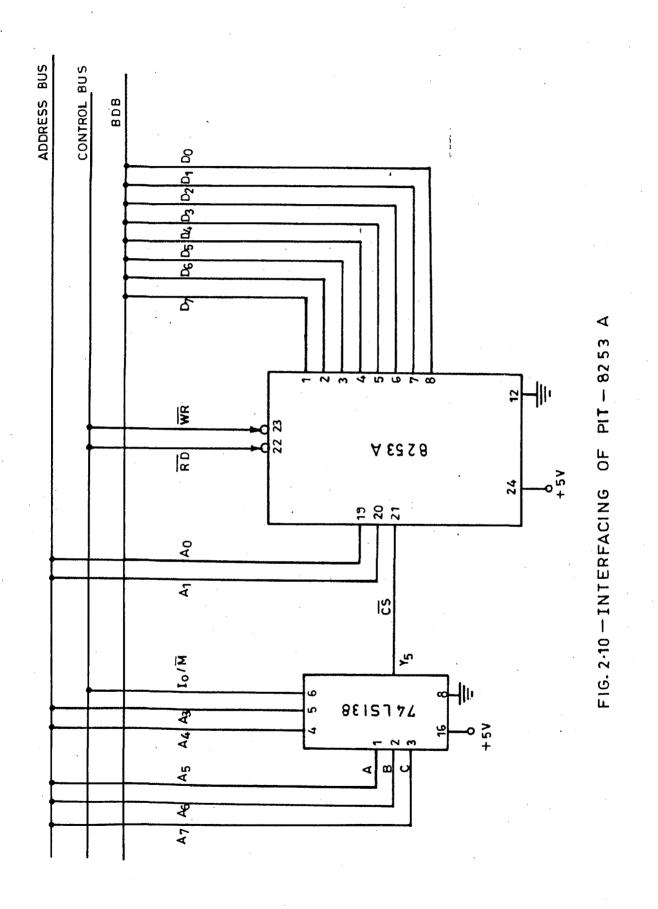

#### 2.5 INTERFACING OF PROGRAMMABLE INTERVAL TIMER8253A

Fig. 2.10 shows the interfacing of PIT 8253A. It consists of a 3 line to 8 line decoder 74IS138 which derives the the chip select  $\overline{CS}$  signal to 8253A. The select inputs  $A_0$  and  $A_1$  are connected to the  $A_0$  and  $A_1$  address bus signals of the CPU respectively.  $\overline{RD}$ ,  $\overline{WR}$  and  $I_0/\overline{M}$  control signals are derived directly from the control bus of the microprocessor. The port addresses for the 8253A are selected as under.

> antral Library University of "Corker ROOBREE

| A.7 | AG | А <sub>5</sub> | A <sub>4</sub> | A3. | $A_2$ | Al | $\mathtt{A}_{O}$ |                |                   |

|-----|----|----------------|----------------|-----|-------|----|------------------|----------------|-------------------|

| l   | 0  | 1              | 0              | Ņ   | 0     | 0  | 0                | Ao             | TM <sub>O</sub>   |

| l   | 00 | 1              | 0              | 0   | 0     | 0  | l                | A <sub>l</sub> | TM1               |

| l   | 0  | ב              | 0              | 0   | 0     | l  | 0                | A <sub>2</sub> | TM <sub>2</sub>   |

| ב'  | 0  | l              | 0              | 0   | 0     | ו  | 1                | A3             | CONTROL WORD      |

| 1   | 0  | 1              | 0              | 0   | 1.    | 0  | 0                | A <sub>4</sub> | IMo               |

| l   | 0  | 1              | 0              | 0   | 1     | 0  | 1                | A5             | $\mathrm{TM}_{1}$ |

| ļ   | 0  | 1              | 0              | 0   | 1     | 1  | 0                | A <sub>G</sub> | TM2               |

| 1   | 0  | 1              | 0              | 0   | ı,    | 1  | 1                | A-7            | CONTROL WORE      |

Thus the interfacing circuit meets the requirement of the extra counters other than from the  $\mu$  8085 system.

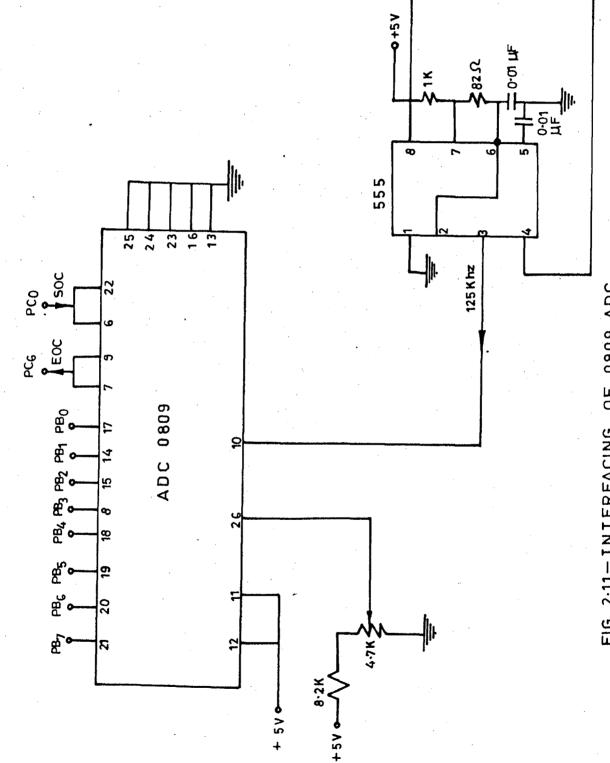

# 2.6 INTER FACING OF ADC CIRCUIT

Fig. 2.11 shows ADC 0809 interfacing circuit. The ADC 0809 is an 8 bit A/D converter with 8 channel multiplexer operating with a single +5 volts d.c. An analog input of 4.7 K potential divider connected in series to a 8.2 K resistor is connected to INO of ADC. A suitable clock of 125 KHz for conversion time is obtained from an oscillator IC 555. The firing pulses for the thyristors are outputted through port A of 8255A as per firing command word. The duty cycle of chopper can be changed linearly by varying the analog input to the ADC. The details of pin configuration of 0809 is given in Appendix - I.

FIG. 2-11-INTERFACING OF 0809 ADC

#### 2.7 DESIGN OF POWER CIRCUIT

The power circuit for the proposed scheme consists of the following parts.

i. Three-phase diode bridge.

ii. Three-phase fully controlled LCI.

iii. D.C.chopper

iv. D.C. LINK inductor

The design ratings of SCRs and diodes for the bridges must be such that they should not be exceeded when maximum power is being delivered by the circuit.

i. Choice of ratings of rectifier bridge diodes.

The power circuit has been designed to supply an active load of  $I_{RMS} = 10$  A. at voltage = 400V input to the bridge rectifier. Thus the d.c. link current for this a.c. current can be obtained from

$I_{RMS} = 1.22 I dc$

•• I<sub>DC</sub> = 0.816 I<sub>RMS</sub>

$I_{DC} = 8.16$  A

The voltage rating of diodes of the uncontrolled bridge have to be selected with the considerations of the peak inverse voltage appearing across the devices, this in turn depends upon the maximum three phase input line voltage to the bridge.

Therefore the PIV across each diode is

$$V_{PIV} = \frac{\pi}{3} \times \frac{3/6}{\pi} V_{IN}$$

= 2.45 V<sub>IN</sub>

$$V_{PIV} = 2.45 \times \frac{400}{\sqrt{3}} = 566 V$$

A safety factor of 2 is kept, so that the diodes can easily take reasonable over voltages. Thus the diodes of rating 16A, 1200 PIV can be selected to meet the requirements.

# (ii) <u>Selection of rating of thyristors</u>

For a 3-phase bridge the ratio of PIV and line to neutral voltages is given by

$$\frac{E_{PIV}}{E_{IN}} = 2.45$$

$$E_{PIV} = 2.45 \times E_{IN} = 2.45 \times \frac{400}{73}$$

$$= 566 V$$

As the rated current of a synchronous motor is 10A, we have

$$\frac{I_{RMS}}{I_{DC}} = 1.22$$

$I_{DC} = 0.816 \times 10 = 8.16 \text{ A}$

Allowing a safety factor 2, a rating of 16A, 1200  $\rm P_{IV}$  can be used.

(iii) Selection of commutating capacitor and Inductor of chopper.

The rated rotor voltages of the WRIM = 140 V. Rated rotor current = 22A. At rectifier output the voltage  $= 1.35 \times 140$

and I<sub>dc</sub> the current

= 189 V = 1.28 x 22 = 28 A

= 20 micro secs

Taking Turn off time

$$C = \frac{2I_{dc} T_{OFF}}{V_{R}}$$

where

V<sub>R</sub>= average value for rectified slip voltage

$$189 + \frac{189}{2} = 141.75 V$$

: C = 7.9 micro. F  $\simeq$  8 micro.F. V<sub>R</sub>  $\neq \frac{1}{C/L} = \frac{I_{dc}}{2}$

.L = 0.81 mH

Hence a capacitor of 8 micro Farads and an inductor of 0.81 milli Henry are used in the auxiliary circuit of voltage commutated chopper.

# 2.8 <u>CONCLUSIONS</u>

The details of the microprocessor based firing control scheme for the inverter bridge and the firing pulses for chopper thyristors has been discussed in this chapter. The design of power circuit and synchronising circuit are also developed. The interfacing of ADC circuit and PIT -8253A has also been described.

# CHAPTER - III

#### IMPLEMENTATION OF SYSTEM SOFTWARE AND FLOWCHARTS

#### 3.1 GENERAL

In this chapter, mainly, the development of system software and flowcharts is described. The complete logic of the control scheme is discussed in the main program routine. The other subroutines along with the main programme are also given in this chapter.

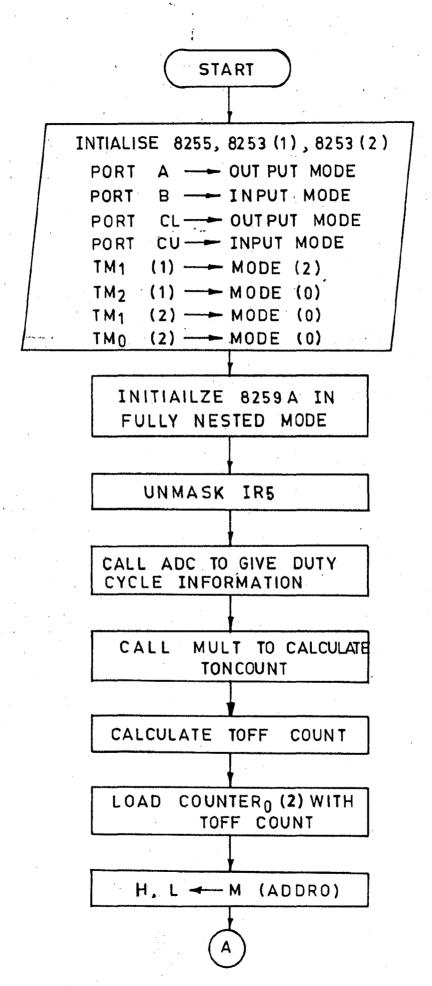

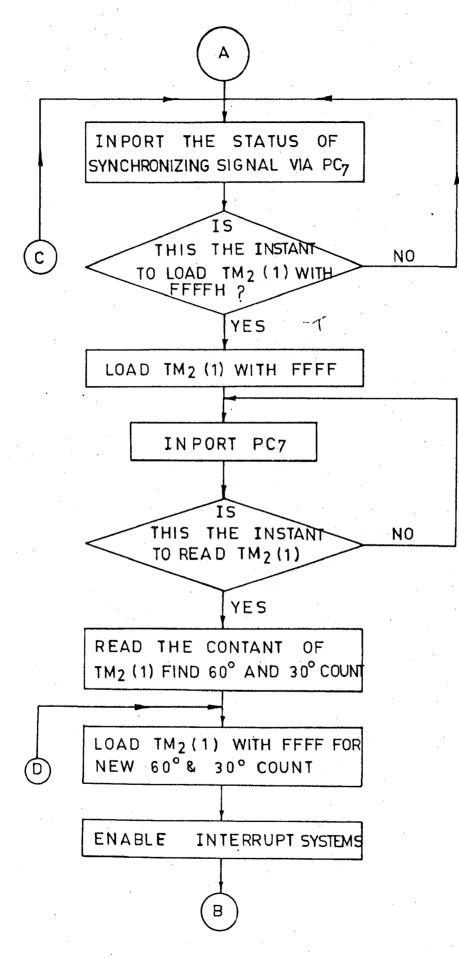

#### 3.2 MAIN PROGRAM ROUTINE

The flow chart for the main program is shown in Fig. 3.1. The program is started with the initialization of programmable peripheral devices in suitable mode according to the requirements for the present scheme. The port A of 8255A (the programmable peripheral interface) is programmed in output mode for outputting the firing pulses as per the firing command word. The port B is the input mode for inputting the data from ADC output. The port CL is in output mode and port Cu is in input mode.

In the uP 8085 system, two counters of programmable interval timer (PIT-8253A) are available for the user through connector  $J_1$ . Counter  $TM_1(1)$  is programmed in mode 2 for generating the clock of 511.67 KHz by using the clock of 1.535 MHz and all the other counters are in mode (0.)  $TM_2(1)$  is used for providing count corresponding to  $60^\circ$  with a clock of 511.67 KHz.  $T_{MO}(2)$  of the interfaced PIT -8253A is used for providing  $T_{ON}$  C and  $T_{OFFC}$  for the chopper and  $TM_1(2)$  is used for providing count for 30<sup>°</sup> initially and then count for 60<sup>°</sup> delay to generate the firing pulses in sequence with 60<sup>°</sup> delay for inverter thyristors. The output of  $TM_1(2)$  and  $TM_0(2)$  are used as  $IR_2$  and  $IR_5$  interrupt request for gene - rating the firing pulses.

The programmable interrupt controller (PIC -8259A) is initialized in fully nested mode, in which IRo has the highest priority and  $IR_7$  has the lowest priority. In the present scheme three interrupt lines  $IR_0$ ,  $IR_2$  and  $IR_5$  are used.

After the initialization of 8253(1), the  $TM_1(1)$  is loaded with a countOH to generate a clock of 511.67 KHz. Continuously. The microprocessor checks the status of the synchronizing signal imported through PC<sub>7</sub>. If it is found to be low then FFFF H is loaded into the  $TM_2(1)$ . The synchronizing signal is also inputted continuously to the Gate of  $TM_2(1)$  and counting becomes enable as soon as the digitized signal goes to high. The counter starts decrementing the count value (FFFF H) as long as the synchronizing signal remains high and counting becomes disable as soon as the synchronizing signal goes to low. Now the count value for  $60^{\circ}$ duration of terminal voltage of synchronous machine is calculated. Then the  $30^{\circ}$  count value is calculated and loaded in to the  $TM_4(2)$  whose gate is made permanently high. After

calculating the count for  $60^{\circ}$  and  $30^{\circ}$ , the programme jumps to ADC subroutine. ADC converts a particular analog input to it through the channel IN<sub>0</sub> into its equivalent digital signal and this output is stored in the memory location address (Add 6). This digital output contains the information about the duty cycle of the chopper. Next, the programme moves to multiplication subroutine. In this subroutine the value of K in hexadecimal is multiplied by the ADC output for calculation of TON<sub>c</sub> and T<sub>OFFc</sub> as shown below.

| TaN     | = ADC x K                                              | (3.1) |

|---------|--------------------------------------------------------|-------|

| where K | clock frequency                                        |       |

|         | f <sub>CH</sub> 100                                    |       |

| К       | $= \frac{1}{300} \times \frac{1.5 \times 10^{6}}{100}$ | . *   |

| K       | $=(50)_{10} = (32)_{H}$                                | (3.2) |

| TOF     | $F_c = (64_H - ADC) K$                                 | (3.3) |

where the frequency of the chopper

$f_{CH}$  is considered as 300 hz.

The equation (3.1) and (3.3) clearly indicates that by varying analog input to the ADC, the duty cycle of the chopper can be controlled easily during the operation of the system. After calculating the  $T_{ON_c}$  and  $T_{OFF_c}$  the interrupt system is made enable and  $TM_o(2)$  is loaded initially with  $T_{OFF_c}$  to generate IR<sub>5</sub> interrupt. Then the microprocessor waits in the Halt state for the interrupt signal IR<sub>5</sub>, as only IR<sub>5</sub> is unmasked in the begining, when IR<sub>5</sub> is saved the programme

FIG. 3-1-FLOW CHART FOR MAIN PROGRAM

FIG.  $3 \cdot 1 - CONTD.$

# FIG. 3-1-CONTD.

moves to enable IRo interrupt as IRo,  $IR_2$  and  $IR_5$  are unmasked. After all the interrupts are served, the interrupt system is made disabled and the firing sequence is tested. If the firing sequence '6' is over then the microprocessor reads the content of counter<sub>2</sub>(1) for new 60° and 30° count and goes to Halt state after enabling interrupt system.

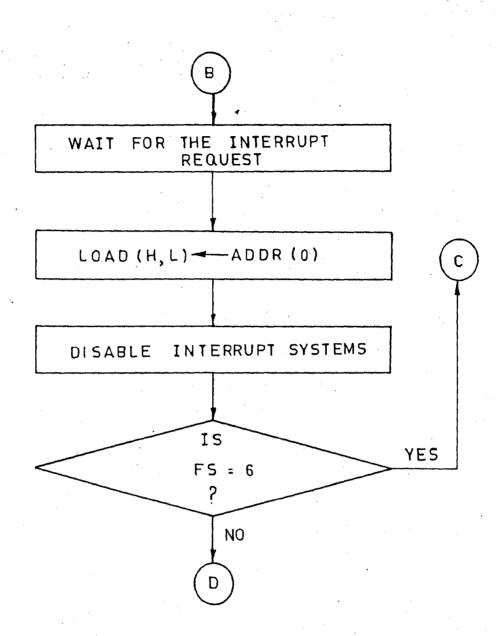

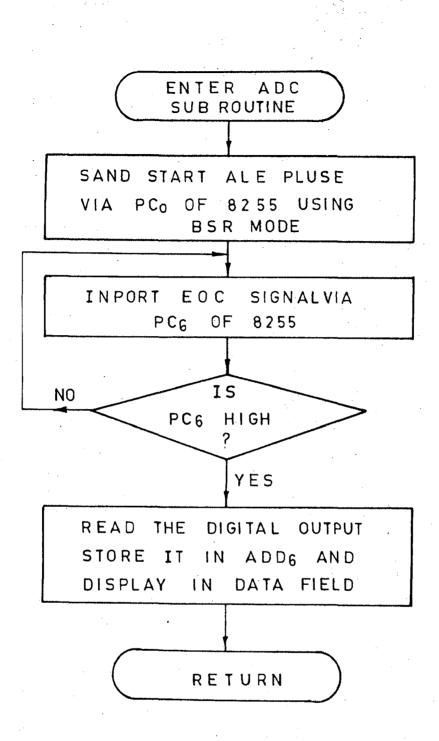

#### 3.3 ADC SUBROUTINE

This subroutine is used to provide duty cycle infor mation for the chopper. This is executed once in every cycle of the machine frequency. ADC converts the analog input to its digital equivalent at the instant, when the start of conversion (SOC) bit of ADC goes from low to high. SOC pulse is issued by the microprocessor through PC<sub>o</sub> bit of 8255A. The duty cycle can be changed by varying the analog input to ADC through a potential divider. The flow chart for ADC subroutine is shown in Fig. 3.2. ADC clock in is given from an oscillator developed with 555 timer at 125 KHz. The digital output is stored in memory location Add 6 and displayed in data field by the microprocessor.

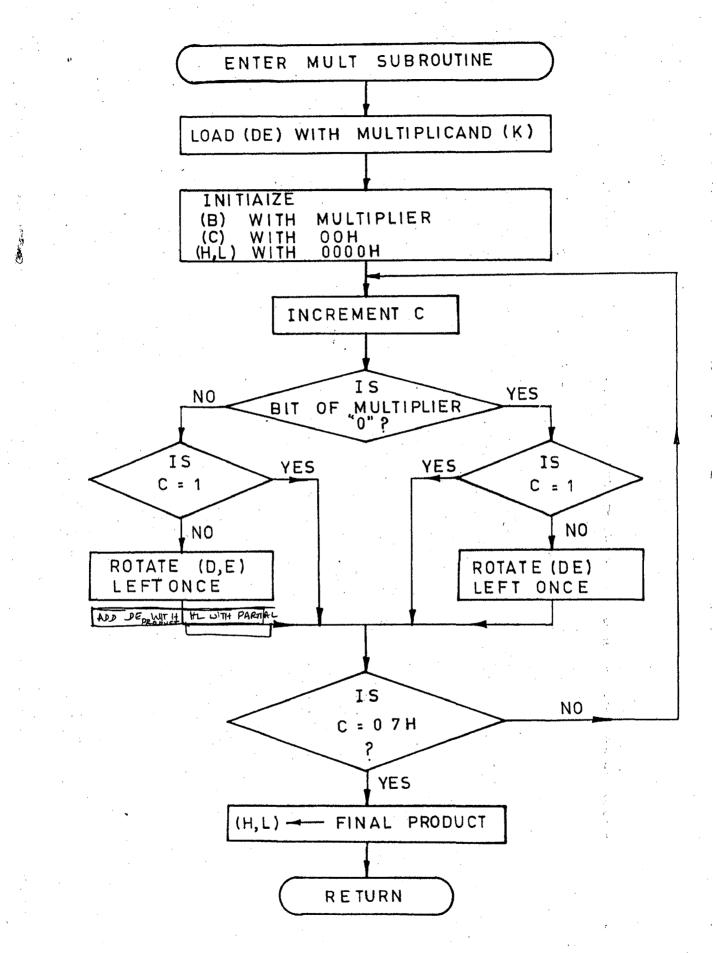

#### 3.4 MULT SUBROUTINE

The flow chart for MULT subroutine is shown in Fig.3.3. In this subroutine the value of K is multiplied by the digital output of the ADC for  $T_{ONC}$  and (64H - ADC) for  $T_{OFFC}$ . The register pair (DE) contains the multiplicand which is the value of the K = 32H corresponding to the clock of 1.535 MHz. Register B contains the multiplier and Register C

FIG. 3.2-FLOW CHART FOR ADC SUBROUTINE

FIG. 3-3-FLOW CHART FOR MULT SUB ROUTINE

is used to indicate the bit position of multiplier. Register pair HL will contain the partial product or final product.Since the binary digits may be either 1 or 0, the multiplier may be examined on a bit by bit basis for 1 or 0, starting from right to left. If a 1 is found the multiplicand is shifted in proper position and added to the accumulating result. If a 0 is found nothing is added to the partial product. In the present case all bits of multiplier are to be tested and the product is stored in HL pair.

#### 3.5 IRO INTERRUPT SUBROUTINE

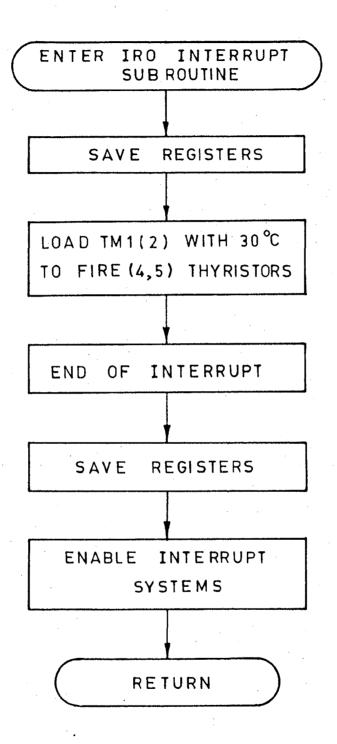

Fig. 3.4 shows the flow chart of  $IR_0$  interrupt service subroutine. In this subroutine  $30^\circ$  count corresponding to 511.67 KHz. is loaded in to the counter<sub>1</sub>(2) to trigger the (4,5) pair of thyristors of the load commutated inverter. The  $IM_1(2)$  is loaded with a count for  $30^\circ$ once in every cycle. Counter output goes high on the terminal count and this output is used as  $IR_2$  interrupt request input. The microprocessor enables the interrupt systems at the end of subroutine before returning to the main programme.

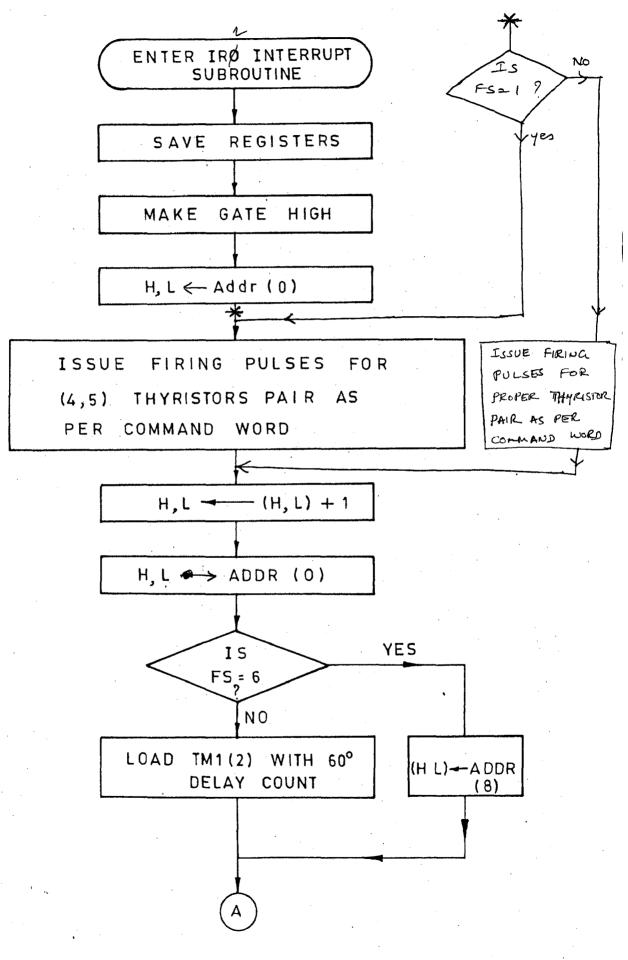

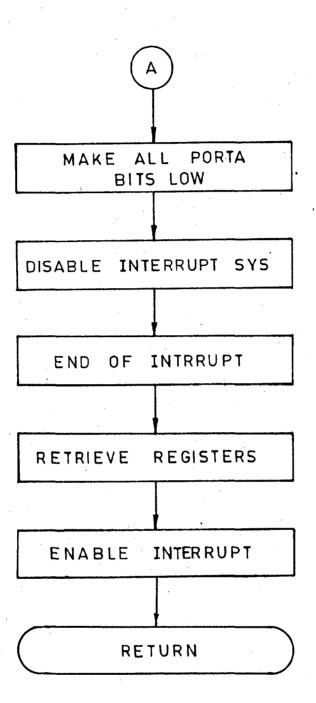

#### 3.6 IR INTERRUPT SUBROUTINE

Fig. 3.5 shows the flow chart for  $IR_2$  service routine. HL is loaded directly with the firing command address to point the correct address to fire (4,5) thyristor pair and incremented with a count for  $60^\circ$  delay loaded in the same

# FIG.3.4 -- FLOW CHART FOR IRO INTERRUPT SERVICE ROUTINE

FIG. 3.5 - FLOW CHART FOR IR 2 INTERRUPT

CUC DOUT INF

FIG. 3.5 - CONTD.

$TM_1(2)$ . Then the firing sequence 6 is over, then HL is reloaded with the starting address of the firing command table. The migroprocessor retrieves the registers and enables interrupt systems at the end of the subroutine before retur ning to the interrupted programme.

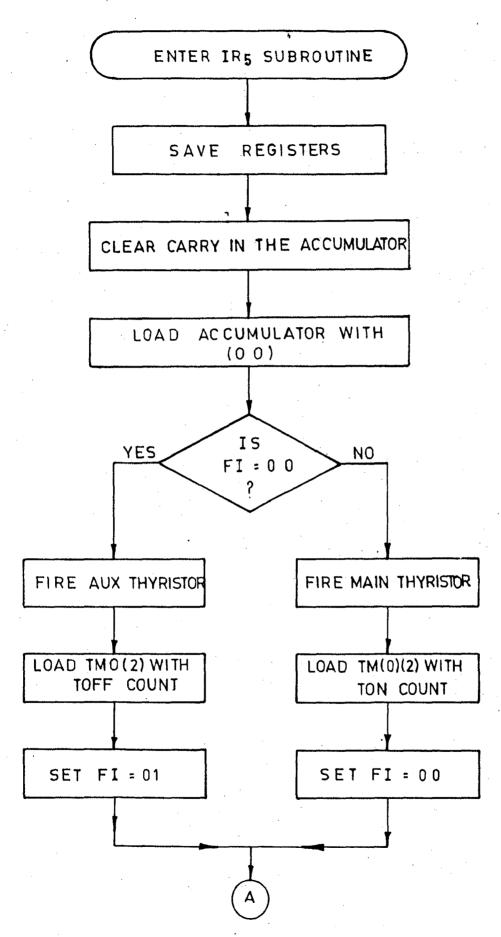

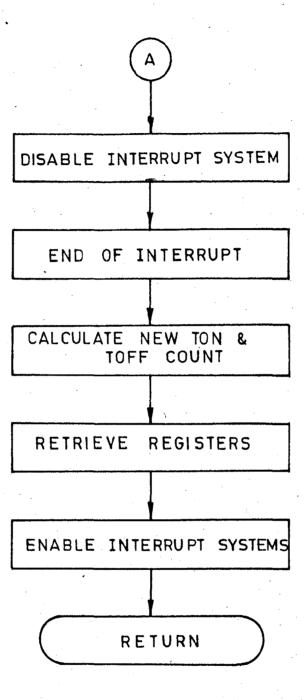

# 3.7 IR. INTERRUPT SUBROUTINE

Fig. 3.6 shows the flow chart for  $IR_5$  interrupt subroutine. This subroutine is used to generate firing pulses for the main and auxiliary thyristors of the chopper. At the begining of the subroutine, the registers are saved and firing index (FI) is checked for OO. If it is OO, the auxiliary thyristor is fired by loading the  $TM_0(2)$  with  $T_{OFF}$  c. If the (FI) is found to be Ol then the main thyristor is fired by loading  $TM_0(2)$  with  $T_{ON c}$  and making the particular bit high. The  $TM_0(2)$  is loaded once with  $T_{OFF}$  and next with  $T_{ONC}$ once in every cucle. The microprocessor retrieves the registers and enables the interrupt system after calculating the new  $T_{ON}$  and  $T_{OFFC}$  for the next cycle before retrieving to the interrupted main programme. The output of  $TM_0(2)$  on the terminal count is used as  $IR_5$  interrupt request.

3.8 CONCLUSIONS

In this chapter the main program with various sub routines have been discussed in detail.

Subroutines discussed are ADC, MULT,  $IR_0$ ,  $IR_2$  and  $IR_5$  subroutines.

FIG. 3-6-FLOW CHART FOR IR5 INTERRUPT SUBROUTNE

.

FIG. 3-6-CONTD.

ADC subroutine provides the duty cycle information for the chopper. MULT subroutine performs the calculations for  $T_{\rm CN~c}$  and  $T_{\rm OFFc}$ .  $IR_{\rm O}$  interrupt subroutine is used to load the  $TM_1(2)$  with a count for  $30^{\circ}$  and  $IR_2$  interrupt subroutine is used to generate the firing pulses for the thyristor of inverter in proper sequence with a count of  $60^{\circ}$  delay.  $IR_5$  interrupt subroutine is used to generate the firing pulses for the main and auxiliary thyristors of chopper by loading the  $TM_0(2)$  with  $T_{\rm CN~c}$  and  $T_{\rm OFF~c}$ respectively.

The main routine and various software subroutine programs have been tested individually and altogether on microprocessor 8085 based system for implementing the present scheme.

#### CHAPTER - IV

# STEADY STATE PERFORMANCE OF THE

DRIVE SYSTEM

# 4.1 GENERAL

This chapter deals with the experimental studies on the microprocessor based chopper controlled commutatorless Kramer drive. The steady state performance of this drive system have been studied on no load and on load. The speed control is obtained by varying the field current and duty cycle of the chopper. The oscillograms of the induction machine terminal voltage, stator current, d.c. link voltage and current, synchronous machine voltage and current and voltage waveforms at different points of the firing control circuit are also given.

# 4.2 EXPERIMENTAL INVESTIGATIONS

The main objective of the experimental investigations is to study the steady state performance characteristics of the chopper controlled commutatorless Kramer drive. The details of the machines used in the system i.e. the induction motor, synchronous motor and d.c. generator used for loading are given in Appendix-I. To obtain the steady state performance of the drive system, the various tests have been performed on no load and on load.

# 4.2.1 Starting of the chopper controlled commutatorless

Kramer drive

Under stand still conditions, synchronous machine terminal voltage is zero and therefore firing pulse generation for load commutated inverter (LCI) is not possible. The d.c. supply is given to the field of the synchronous machine and it is run as a generator by means of the wound rotor Induction motor by closing switch  $S_1$  in Fig. 4.1. The voltage induced at the stator terminals of the synchronous machine is used to generate the firing pulses for the thyristors of LCI by microprocessor. In the present work, a manual starting method shown in Fig. 4.1 is adopted. The manual method of starting chopper controlled commutatorless Kramer system involves the following steps.

- (i) The induction motor is started to drive the synchronous machine as a generator at a very low speed.

At low speed, the electromotive force of the synchronous machine is small. So proper synchronizing signal will not be generated from this low voltage.

- (ii) A variable resistor, R shown in Fig. 4.1 is connected across the bridge rectifier to accelerate the motor upto a speed where the voltage induced at the stator terminals of the synchronous machine is sufficient to generate the firing pulses for the thyristors of the LCI by the microprocessor.

- (iii) Also the firing pulses for the main and auxiliary thyristors of the chopper are generated by the microprocessor. The output voltage of the chopper is varied by varying the duty cycle of the chopper with the help of the ADC input.

- (iv) The starting Rheostat R is gradually cut out from the circuit and switch  $S_{\gamma}$  is opened.

- (v) The upper terminal of the D.C. link is positive and the lower one negative when sufficient power is being pushed from d.c. side to the a.c terminals of the synchronous motor ( $V_R$  becoming greater, than the  $V_{dc}$ ).

- (vi) A series resistor connected in series with the inductor (not shown in Fig. 4.1) is gradually reduced to the minimum value to enhance the power to the motor. This resistor is placed in the circuit to reduce the speed of operation to a value which gives sufficient slip voltage SE<sub>2</sub> which is necessary for commutation of the chopper.

- (vii) A very low value of capacitor (not shown in Fig.4.1) is placed at the ac terminals of the inverter bridge to improve the reactive power.

- (viii) The slip power from the rotor of the wound rotor Induction motor flows from the d.c side to the synchronous motor when the bridge rectifier voltage

becomes greater than the inverter do voltage thus following the Kramer operation.

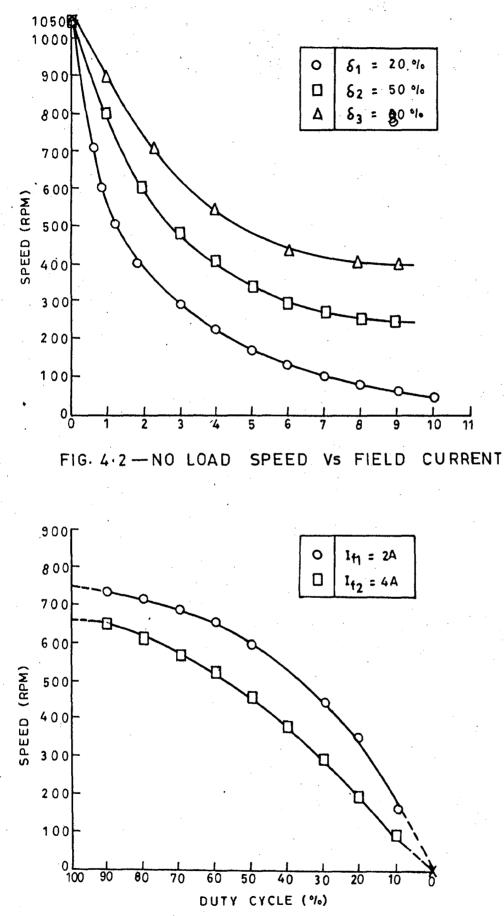

# 4.2.2 Tests at no load

These tests are carried out by varying the chopper duty cycle with constant field current and changing field current with constant duty cycle. The firing angle of the LCI has been chosen to be 150° through out the operation. From the results of no load tests the following no-load steady state characteristics are obtained.

- (i) Speed vs field current for different duty cycles of the chopper.

- (ii) Speed vs duty cycle of the chopper for different values of the field current.

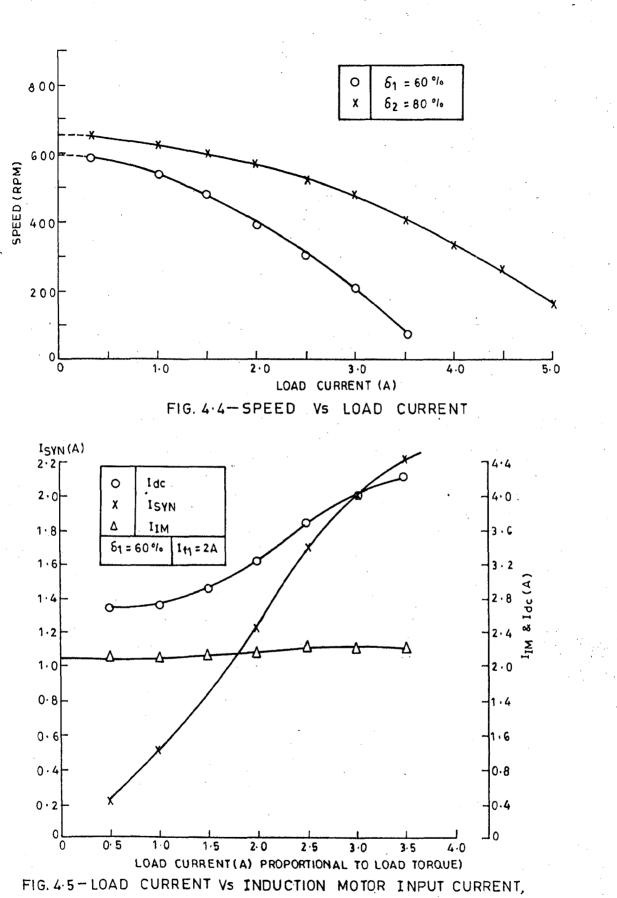

#### 4.2.3 Tests at load

The experimental performance under load of the commutatorless Kramer system is obtained with the help of a coupled d.c. machine running as a separately excited generator. Load test is carried out by varying the load on the drive system at a field current with constant duty cycle. From the experimental results the following characteristics are obtained.

- (i) Speed vs load current.

- (ii) Input current of the induction motor vs the load current.

(iii) Synchronous motor current vs load current.

(iv) D.C. link current vs load current.

(v) Net power output vs load current.

# 4.3 RESULTS AND DISCUSSIONS

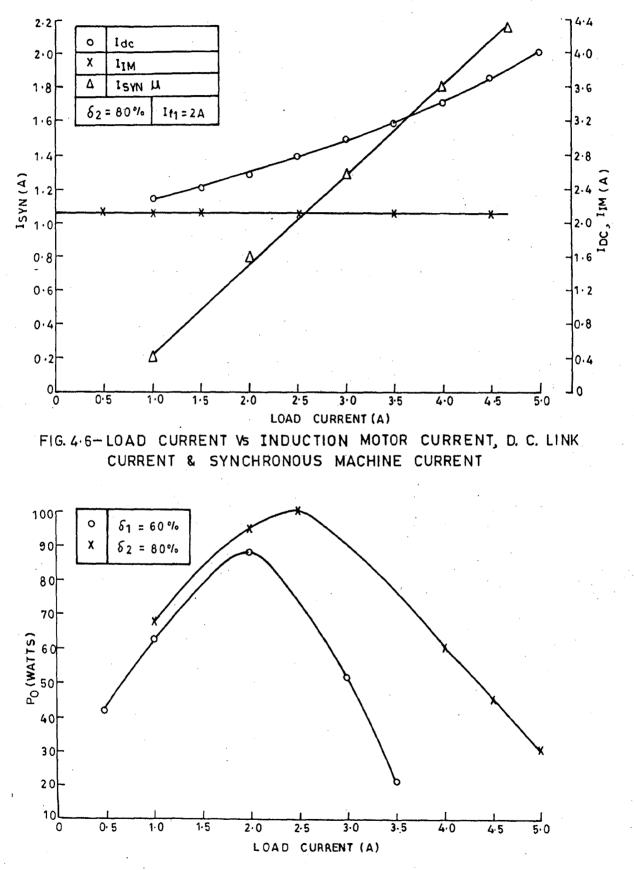

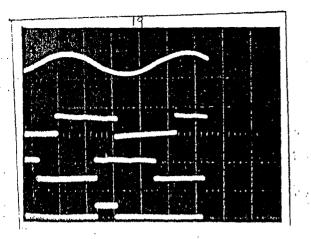

The experimental characteristics of chopper entrolled commutatorless Kramer drive at no load and load conditions are shown in Figs. 4.2 to 4.7. The oscillograms of the waveshapes at different points of the control cireuit for inverter bridge and chopper, machine terminal voltage and current, chopper input voltage and current, chopper output voltage and current, D.C. link voltage and current after the smoothening inductor are recorded at no load and loaded conditions and are shown in Figs. 4.8 to 4.12.

The following salient features on the performance of chopper controlled commutatorless Kramer drive are observed from the results.

(i) The effect of field current on speed is shown in Fig. 4.2 for three settings of chopper duty cycle which are 20 percent, 50 percent and 90 percent. It is observed that speed falls as field current increases. Further, at a given field current setting, speed rises with increase in chopper duty cycle Fig. (4.3). The maximum speed with 5 = 90 percent is seen from Fig. 4.2 to be around 1000 rpm. Normally, the speed should approach synchronous speed (1500 rpm in present case)

39

$\delta = 1.0$  and  $I_f = 0.0$ . However, it is due to inclusion of a resistance in series with the d.c. link inductor. The reason for including the resistor has already been explained.

- (ii) It is observed from Fig. 4.4 that the commutatorless Kramer drive exhibits similar drooping load current vs speed characteristics like a conventional d.c. motor. Also that the characteristic shifts upword as the duty cycle is increased. The load current (d.c. generator armature current) is proportional to load torque since field current of d.c. generator is kept constant. The load current is therefore chosen as independent variable in plotting the characteristic.

- (iii) It is observed from the Fig.4.5 and 4.6 for duty cycle settings of 60 percent and 80 percent respectively that the variation of d.c. link current with load current is similar to the armature current vs load ourrent characteristic of a conventional d.c. motor. D.C. link current increases almost linearly with the load current.

Synchronous motor current also shows the rising trend which is almost linear. This is expected on account of the rising trend of the d.c. link current.

FIG. 4.3-NO LOAD SPEED VS DUTY CYCLE

.

D. C. LINK CURRENT AND SYNCHRONOUS MACHINE CURRENT

FIG. 4.7-LOAD CURRENT VS NET POWER OUTPUT

..

It is observed that the induction motor current remains almost constant with increase of load current. This is due to the fact that amount of loading is rather low (about 100 w only) and therefore the current drawn by the Induction motor increases only marginally.

- (iv) The loading is done by a direct coupled fully excited d.c. generator, its armature voltage drops significantly under load conditions due to fall in speed. Its power output therefore falls at high load current. The power output is already low for low load currents. Thus the loading ability of the arrangement is as depicted in Fig. 4.7 for a field current set at 2 Amps and the chopper duty cycle set at (i) 60 % (ii) 80 %.

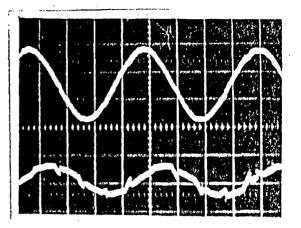

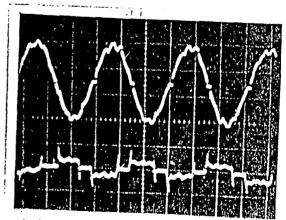

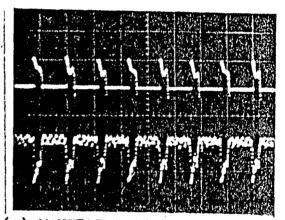

- (v) The oscillograms of synchronous machine terminal voltage  $V_{AC}$ , the two output signals of the voltage comparator, the synchronizing signal of  $60^{\circ}$  pulse width are shown in Fig. 4.8.

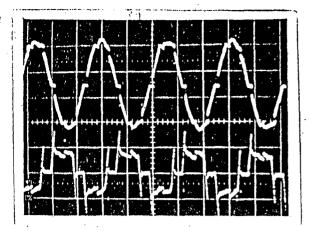

- (a) They are exactly similar to the theoretical ones given in Chapter II. Fig. 4.8(b) shows the terminal voltage  $V_{AC}$ , synchronizing signal, the output of  $IM_1(2)$ and the firing pulses for  $Th_1$  of LCI. Fig. 4.8(c and d) shows the terminal voltage  $V_{AC}$  and the firing pulses for LCI thyristors in proper sequence at an interval of  $60^{\circ}$  for the six channels. Fig. 4.8(e) shows the output of  $IM_0(2)$  and the firing pulses of the main and auxiliary thyristors of the chopper at  $f = 70^{\circ}/.$

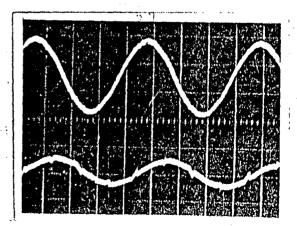

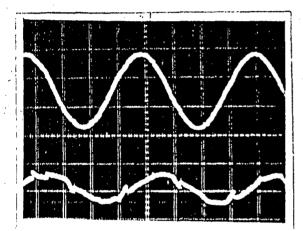

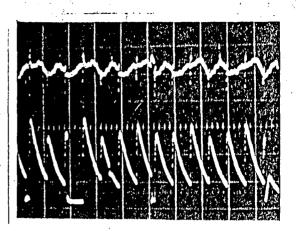

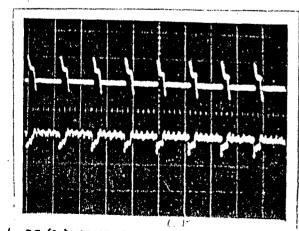

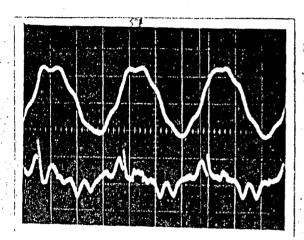

(iv) The oscillograms of stator input voltage and current of induction motor at no load and loaded conditions of the drive are shown in Figs. 4.9(a) to 4.9(d) for two different values of field currents.  $I_{f_1}$  and  $I_{f_2}$ respectively. Chopper duty cycle is set at 50 percent that the current waveform is very nearly sinusoidal with super posed notches. 6 per cycle.

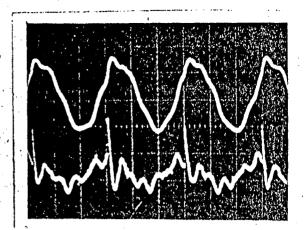

The rotor voltage (at slip frequency) and current of wound rotor Induction motor under no load and loaded conditions at the field currents  $I_{f_1}$  and  $I_{f_2}$  respectively are shown in Figs. 4.9(e),(f),(g) and (h) chopper duty cycle is set at 50 percent. The voltage waveforms are sinusoidal with notches at  $60^{\circ}$  interval due to the commutation of thyristors. The current waveform is quasisquare with  $120^{\circ}$  pulse width due to the diode bridge rectifier.

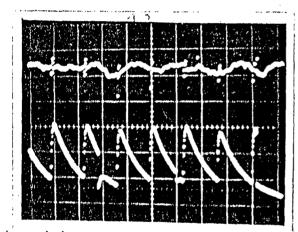

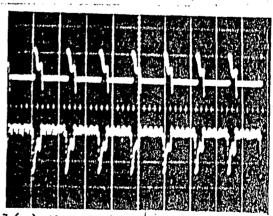

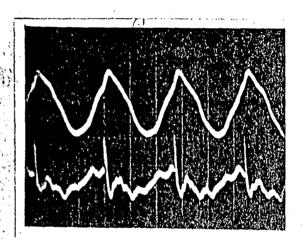

- (vii) The oscillograms of the voltage and current under no load and load are shown in Fig. 4.10(a) and (b). The field current is set at  $I_{f_1}$  at a duty cycle of 50 %.

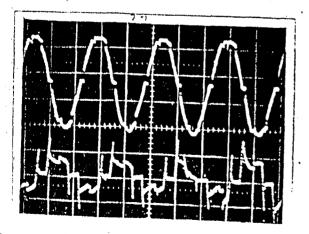

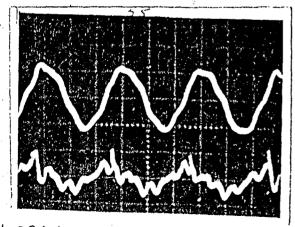

- (viii)The oscillograms of d.c. link voltage and current under no load and loaded conditions with two values I<sub>f</sub> and I<sub>f</sub> are shown in Figs. 4.11 (a),(b),(c) and (d).

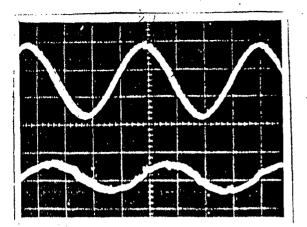

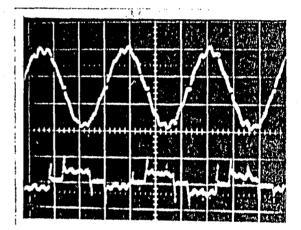

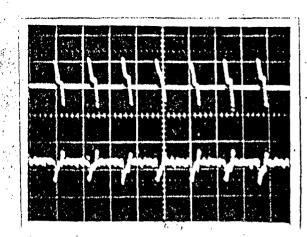

- (ix) The stator current and voltage of synchronous motor under no load and loaded conditions are shown in Figs. 4.12(a), (b), (c) and (d). The voltage and current waveforms of synchronous motor are almost sinusoidal because of the capacitor at the input terminals of the motor.

The chopper controlled commutatorless Kramer drive at no load and load conditions works satisfactorily and will find good applications in various industries for wide speed range of sub-synchronous region.

## 4.4 CONCIUSIONS

The present scheme works satisfactorily at no load and loaded conditions. Microprocessor based firing controlled circuit generates firing pulses for thyristors of LCI and the chopper in proper sequence and the duty cycle of the chopper. through ADC has been achieved. The commutatorless D.C.motor behaves exactly similar in its characteristics of that of a conventional d.c. motor in the Kramer system.

4.8(a) WAVEFORMS OF MACHINE TERMINAL VOLTAGE VAC, OUTPUTS OF THE VOLTAGE COMPARATORS AND THE SYNCHRONIZING SIGNAL.

4.8(b) WAVEFORMS OF SYNCHRONOUS MACHINE TERMINAL VOLTAGE VAC, SYNCHRONIZING SIGNAL, OUTPUT OF TM<sub>1</sub>(2 AND FIRING PULSES OF T1.

4.8(c) WAVEFORMS OF SYNCHRONOUS MACHINE TERMINAL VOLTAGE VAC, FIRING PULSES OF T1, T2 and T3.

4.8(d) WAVEFORMS OF SYNCH RONOUS MACHINE TERMINAL VOLTAGE, FIRING PULSES OF T4, T5, and T6.

4.8(e) WAVEFORMS OF OUTPUT OF  $TM_{o}(2)$ , FIRING PULSES OF  $Th_{MAIN}$  and  $Th_{AUX}$  FOR CHOPPER

4.9(a) WAVEFORMS OF STATOR VOLTAGE (400V) AND CURRENT (2.1A) OF WRIM AT NOLOAD, SPEED (580 RPM) AND FIELD CURRENT ( $I_{f_1} = 2A$ )

4.9(b) WAVEFORMS OF STATOR VOLTAGE (400V and CURRENT (2.2A) OF WRIM AT 10AD, SPEED (520 RPM) AND CLM FIELD CURRENT  $(I_{f_1}=2A) \cdot (d=50\%)$

4.9(d) WAVEFORMS OF STATOR VOLTAGE (400V) AND CURRENT (2.2A) OF WRIM AT LOAD, SPEED (430 RPM) AND CLM FIELD CURRENT (If2=4A).

4.9(c) WAVEFORMS OF STATOR VOLTAGE (400V) AND CURRENT (2.1A) OF WRIM AT NOLOAD, SPEED (480 RPM) AND FIELD CURRENT (If<sub>2</sub>=4A),  $\delta$ =50 percent. FIELD CURRENT (If<sub>1</sub>=2A)

4.9(f) WAVEFORMS OF ROTOR VOLTAGE (116V) AND CURRENT (2.5A) OF WRIM AT LOAD, SPEED (300 RPM)  $AND(I_{f_1}=2A)$ .

4.9(e) WAVE FORMS OF ROTOR VOLTAGE (88V) AND CURRENT (1.0A) OF WRIM AT NOLOAD, SPEED (530 RPM) AND

4.9(g) WAVEFORMS OF ROTOR VOI TAGE (124V) AND CURRENT (1.4A) OF WRIM AT NOLOAD, SPEED (500 RPM) AND  $(I_{f_2} = 4A)$ .

3.

4.9(h) WAVEFORMS OF ROTOR VOLTAGE (132V) AND CURRENT (3.0A) OF WRIM AT 10AD, SPEED (300 RPM) AND  $I_{f2}=4A$ .

4.10(a) WAVEFORMS OF CHOPPER INPUT VOLTAGE (130V) AND CURRENT (1.1A) AT NO LOAD, SPEED (540 RPM) AND If<sub>1</sub>(2A) WITH DUTY CYCLE (50 percent), 2 msec/ div (SCALE)

4.10(b) WAVEFORMS OF CHOPPER INPUT VOLTAGE (140V) AND CURRENT (1.4A) AT 10AD, SPEED (500 RPM) AND  $I_{f_1}(2A)$ , 2 msec/div (SCALE)

4.11(a) WAVEFORMS OF DC LINK VOLTAGE (30V) AND CURRENT (1.1A) AT NOLOAD SPEED (520 RPM) AND If (2A), SCALE (50 m secs/div.)

4.11(b) WAVEFORMS OF D.C.IINK VOLTAGE (25V) AND CURRENT (2.1A) AT 10AD SPEED (520 RPM) AND I (2A) SCALE (50 m secs/div.)1

4.11(c) WAVEFORMS OF D.C.LINK VOLTAGE (25V) AND CURRENT (1.1A) AT NOLOAD, SPEED (495RPM) and  $I_{f2}(4A)$ , SCALE (50 m sec/div).

4-

4.11(d) WAVEFORMS OF D.C.LINK VOLTAGE (20V) AND CURRENT (2.2A)AT 10AD, SPEED (470 RPM) AND If<sub>2</sub>(4A), SCALE(50 msecs/div.)

4.12(b) WAVEFORMS OF STATOR VOLTAGE (95V) AND CURRENT (1.5A) OF SYNCHRONOUS MACHINE AT 10AD, SPEED (520 RPM) AND  $I_{f_7}(2A)$ .

4.12(a) WAVEFORMS OF SATOR VOLTAGE (72V) AND CURRENT (0.6A) OF SYNCHRONOUS MACHINE AT INOLOAD, SPEED (560 RPM) AND If, (2A).

4.12(c) WAVEFORMS OF STATOR VOLTAGE (85V) AND CURRENT (0.5A) OF SYNCHRONOUS MACHINE AT NO 10AD, SPEED (520 RPM) AND If<sub>2</sub> (4A)

4.12(d) WAVEFORMS OF STATOR VOLTAGE (92V) AND CURRENT (1.85A) OF SYNCHRONOUS MACHINE AT 10AD, 3PEED (475 RPM) AND If (4A).

## CHAPTER - 5

### CONCLUSIONS AND SUGGESTIONS

### FOR

#### FURTHER WORK

#### 5.1 CONCLUSIONS

The work presented in this thesis covers the design and fabrication of a microprocessor controlled firing schemes for line commutated inverter, d.c. link the chopper and the experimental investigations on the performance of chopper controlled commutatorless Kramer drive. The main conclusions of the present work are summarized as follows.

- 1. The power circuits and an open loop firing angle control scheme using only few hardware components have been designed and fabricated. The firing circuits works satisfactorily despite the presence of commutation spikes in the terminal voltage of the synchronous machine.

- 2. The terminal voltage of synchronous motor is observed sinusoidal under all conditions with small notches spaced at 60° interval occuring due to the commutation of the thyristors of load commutated inverter. The duration of the spikes is equal to the commutation over lap angle and is quite small.

From the experimental investigations, it is observed that the system is stable at no load as well as loaded conditions. The variation of speed beyond half - synchronous speed is obtained by reducing duty cycle of the chopper, which is equivalent to reducing armature voltage of the commutatorless motor. It is also verified that commutationless dc motor exhibits the characteristics similar to the conventional D.C.motor,

3.

4. The main advantage of the present work with the microprocessor control over the analogue control is that of flexibility, saving in cabling by use of twisted pairs, easier fault diagnostics, as well as remote information is available to the microprocessor allowing a decision and display to take place, easier sequence modifications without hardwire changes and longer life of hardwire as these equipments are ompletely solid state.

Compared with other systems of speed control of would rotor, Induction motor, the preferred system is commutatorless and therefore has advantage of less maintenance, higher reliability and also of causing fewer of the harnful effects that harmonic currents and the reactive power of the inverter have on power supplies. The experimental results are obtained on a laboratory size chopper

45

controlled commutatorless Kramer drive which verifies the Kramer principle. This system is suitable for applications such as large pump and fan type of drives which have a limited speed control range.

#### 5.2 SUGGESTIONS FOR FURTHER WORK

During the course of investigations, some problems have arisen which would require further investigations. Therefore this work can be extended, on following aspects.

- 1. The synchronous machine in the present work is basically a slipring induction motor such as a synchronous machine. Hence better performance of the drive system may be expected by using a conventional synchronous machine.

- The steady state analysis of the drive may be developed to correlate the experimental results.

A dynamic model may also be developed to study the transient and dynamic performance of the drive.

The speed control of the would rotor Induction motor may also be attempted by varying the firing angle of the inverter bridge.

46

#### REFERENCES

- [1] Bose, B.K., Adjustable speed AC drives' A technology status review, proceedings of the IEEE, Feb. 1982.

- [2] Jones, B.I. and Brown, J.E. Electrical variable speed drives, IEE Proceedings, Vol. 131, Pt.A. Sept. 1984.

- [3] Werner leonard, Adjustable speed AC drives, proceedings of the IEEE, April 1988.

- [4] Sen, P.C. and Ma, K.H.J., Rotor chopper control for induction motor drive, TRC stratrgy, IEEE Transactions, Ind. Applications, IA-11, No.1, pp. 43-44, 1975.

- [5] Wa N.S. and Ramamoorthy, M., 'Chopper controlled slipring Induction motor', IEEE Trans. on Ind. Electronics and Control instrumentations, Vol. IECI-24, Nc.2, pp. 153-161 1977.

- [6] Shepherd, W. and Khalil, A.Q. 'Capacitive compensation of thyristor controlled slip-ring recovery systems', Proceeding Inst., Elect. Engg., Vol. 117, No. 5, pp. 948-956, May 1970.

- [7] Shepherd, W. and Stanway, J., 'Slip energy recovery in an induction motor by the use of a thyristor inverter', IEEE Transmission, Ind. Gen.Applications, Vol. IGA-5, No. 1, pp. 74-82, Jan./Fab. 1969.

- [8] Mittle, V.N., Venkatesan, K. and Gupta, S.C., Stability analysis of a constant torque static slip power recovery drive, IEEE Transactions on industry applications, Vol. IA-16, No. 1, pp. 119-126, Jan./Feb. 1980.

- [9] Mittle, V.N., venkatesan, K. and Gupta, S.C. 'Determination of instability region for a static slip-power recovery drive'. JIE (India), Vol. 59, pt. EI1. pp.59-63,1978.

- [10] Tainguchi, K., Takeda, T and Hirasa, T. 'High performance slip-power recovery-induction motor', IEEE proceedings-B, Electric power applications, Vol. 134, Part-B, No. 4, pp. 193-198, July 1984.

- [11] Seshogiri, R. Dorodla, Chakravorty, S. and Kashinath, E. Holk, "A new slip-power recovery scheme with improved supply power factor", IEEE transactions on power electronics, Vol.3, No.2, pp.200, April 1988.

- [12] Clapham, H.E. and Griffin, J., Modified Kramer combination part and 2°, Electrical Times, pp.335-339 and 386-389, March 1967.

- [13] Bland, R.J., Hancock, N.P. and Whitehead, R.W., Considerations concerning modified Kramer system', Proceedings IEE, Vol.110, No.12, pp.2228-2232, 1963.

- [14] Goldhammer, A.B., Modern Kramer system, Electrical Review, pp. 164-169, 1967.

- [15] Davoine, J., Perreot, R. and Hoang-Le-Huy, 'Operation of a self controlled synchronous motor without a shaft position sensor', IEEE Trans. on Ind.Applications, Vol.IA-19, No.2, pp.212-223, March/April 1983.

- [16] Pelly, B.R., 'Thyristor phase controlled converters and cycloconverters', Wiley- New York 1971.

- [17] Murphy, J.M.D., 'Thyristor control and their applications', Oxford, Pergamon Press, 1973.

- [18] Bose, B.K., Adjustable speed drive systems", New York, IEEE Press, 1987.

- [19] Ranganadachari, M.V.S.S., Singh B.P., Aubarasu, R. and Arockiasamy, R., \* Experimental investigations on steady-state performances of commutatorless machine induction motor systems, Journal of the Institution of Engineers (India), Vol.64, Part EL -3, Dec. 1983, Electrical Engg. Division.

- [20] Lavi, A. and Polge, R.J., 'Induction motor speed control with static inverter in the rotor', IEEE Transactions, Power Apparatus Sys. Vol.PAS-85, pp.76-84, Jan. 1966.

- [21] Okuyama, T. et al., 'Effects of machine constants on steady state and transient characteristics of commutatorless motors', Conf. Rec.IEEE/IAS Annual meet, pp. 272-279, 1977.

- [22] Nacto, H., Effect of field current fluctuations on operating performance of thyristor commutatorless motors, Electrical Engg. in Japan, Vol.102, No.4, pp. 469-476, 1982.

- [23] Miyata, T. Speed control of wound rotor type induction motor by thyristor Kramer system, Journal of Elect. Engg. in Japan, Vol. 96, No.5, pp.408-411, 1976.

- [24] Kuniomi Oguchi, 'Speed control of a brushless static Kramer system', IEEE Transactions on inductry applications, Vol. IA-17, No.1, Jan/Feb. 1981.

- [25] Wakabayashi, T.Hori, T., Shimizu, K. and Yoshicka, T., Commutatorless Kramer control system for large capacity induction motors for driving water service pumps, IEEE/IAS Annual meeting conference, Rec.papers, pp.822-828, 1976.

- [26] Venkatesan, K. and Gupta, S.P., 'Chopper controlled Kramer drive', Journal of the Institution of Engineer (India), Elect. Engg.Division, Vol.60, Pt.EL -3, Dec.1979, pp.102.

- [27] Gupta, S.P. and Verma, V.K., "Chopper controlled slipenergy recovery drive steady-state performance", International conference on Electrical Machines 1984, Lansone, Switzerland.

- [28] Gupta, S.P., 'Chopper controlled Kramer drive', Ph.D. Thesis, Electrical Engg.Deptt., University of Roorkee, Roorkee, 1985.

- [29] Naik, K.B., Bhim Singh, Agarwal, P. and Goel A.K., 'Firing circuit for 3-phase variable frequency thyristor bridge inverter', Journal of the Institution of Engineers, Vol.63, Part EL-4, Feb. 1988, Electrical Engg.Division.

- [30] Doraipandy, S. and Arockiasamy, R., A noval trigger scheme for thyristor operating under variable frequency anode supply, IEEE Transactions, Vol.IECI-22, pp.83, 1975.

- [31] Gaonkar, S., Microprocessor and their applications, Wiley Eastern Limited.

- [32] Ram, B., 'Fundamentals of microprocessors and Microcomputers', Published by Dhanpat Rai and Sons.

- [33] Spencer, P.T., Microprocessor applied to variablespeed drive system, Electronics power, Vol.29, No.2, pp.140, Feb. 1983.

- [34] Richter, W., 'Microprocessor controlled inverter fed synchronous motor drive', Proceedings of IEE.Conf. on Variable speed drives, pp.161, 1979