# FABRICATION AND EXPERIMENTAL INVESTIGATIONS ON MICROPROCESSOR BASED SELF CONTROLLED SYNCHRONOUS MOTOR DRIVE

# A DISSERTATION

# submitted in partial fulfilment of the requirements for the award of the degree

of

# MASTER OF ENGINEERING

ín

# ELECTRICAL ENGINEERING (Power Apparatus and Electric Drives)

By

# C. L. PUTTA SWAMY

# DEPARTMENT OF ELECTRICAL ENGINEERING UNIVERSITY OF ROORKEE ROORKEE-247667 (INDIA)

February, 1988

### CANDIDATE'S DECLARATION

I hereby certify that the work which is being presented in the 'FABRICATION AND dissertation entitled / EXPERIMENTAL INVESTIGATIONS ON MICROPROCESSOR BASED SELF CONTROLLED SYNCHRONOUS MOTOR DRIVE' in partial fulfilment of the requirements for the award of the Degree of Master of Egineering in Electrical Engineering with Specialization in POWER APPRATUS AND ELECTRICAL DRIVES, submitted in the Department of Electrical Engineering, University of Roorkee, Roorkee (India), is an authentic record of my own work carried out for a period of about six months, from August 1987 to January 1988 under the supervision of Dr. V.K.VERMA, Professor and Dr. BHIM SINGH, Lecturer, Department of Electrical Engineering, University of Roorkee, Roorkee, India.

The matter embodied in this dissertation has not been submitted by me for the award of any other degree or diploma.

Dated : Feb. 6<sup>th</sup> 1988

This is to certify that the above statement made by the candidate is correct to the best of our knowledge.

(Dr.BHIM SINGH) LECTURER ELECTRICAL ENGG, DEPTT, UNIVERSITY OF ROORKEE ROORKEE-247 667 INDIA

(Dr. PROFESSOR ENGG DEPTT

UNIVERSITY OF ROORKEE ROORKEE-247 667 INDIA

#### ACKNOWLEDGEMENTS

I wish to express my profound sense of gratitude and indebtness to my guides, Dr. V.K.VERMA, Professor, Electrical Engineering Department, University of Roorkee, Roorkee and Dr. BHIM SINGH, Lecturer, Electrical Engineering Department, University of Roorkee, Roorkee. It was a pleasure and a previlege to have worked under them during the tenure of this work.

I am highly thankful to Dr. P. MUKHOPADHYA, Professor & Head of the Department of Electrical Engineering, University of Roorkee, Roorkee for providing laboratory facilities.

I am deeply grateful to all the laboratory staff for their cooperation during the fabrication of this work.

I am highly thankful to P.E.S. COLLEGE OF ENGINEERING, MANDYA, KARNATAKA for sponsoring to this M.E. course.

Special thanks to my wife V. GEETHA for her constant source of inspiration throughout this work.

Thanks are also to those who helped directly or indirectly in preparing this dissertation.

C.L.PUTTASWAMY

### SYNOPSIS

iii

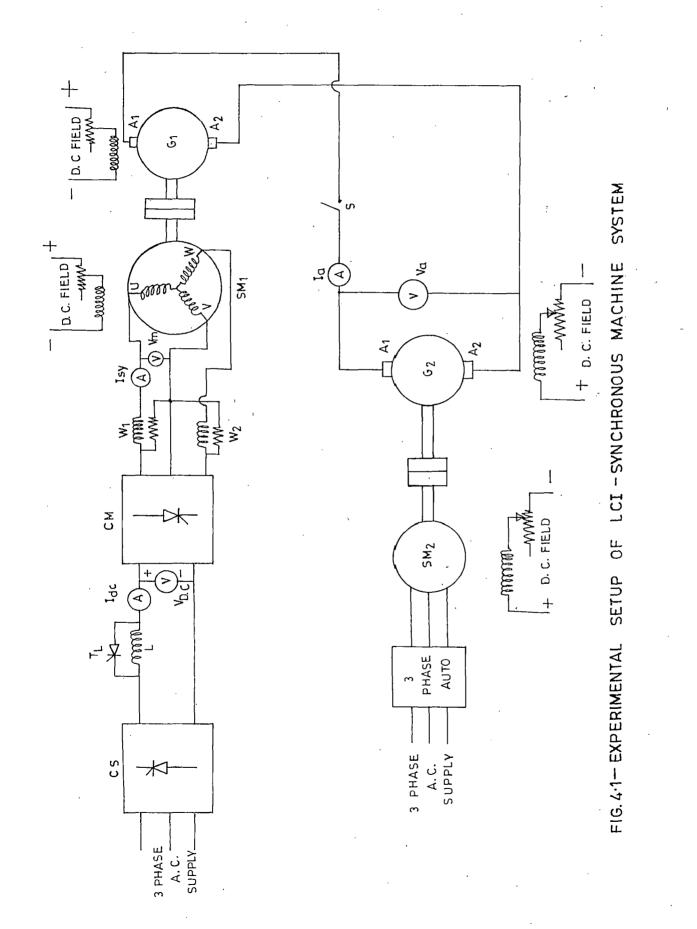

This dissertation deals with the experimental studies on a microcomputer based Line-Commutated inverter fed synchronous motor drive system.

Two three phase fully controlled thyristor bridges, one for rectifier and another for inverter, microprocessor controlled firing circuits, zero crossing circuits and digital speed measurement circuit have been designed fabricated and tested.

Chapter 1 consists of introduction, literature review and brings out the different methods of starting of Line-commutated Inverter fed synchronous motor drive. In Chapter 2, the princile of operation of LCI synchronous motor drive, philosophy of its speed control and system hardware have been discussed. Chapter 3 describes the system software and the various flow charts. Chapter 4 deals with the experimental results. Conclusions and scope of future work have been given in Chapter

5.

CONTENTS

|           | CERTIFICATE                                                           | •• • | ĩ   |  |

|-----------|-----------------------------------------------------------------------|------|-----|--|

|           | ACKNOWLEDGEMENT                                                       | ••   | ii  |  |

| · · ·     | SYNOPSIS                                                              | ••   | iii |  |

| CHAPTER-1 | INTRODUCTION                                                          | ••   | 1   |  |

| 1.1       | GENERAL                                                               | ••   | .1  |  |

| 1.2       | CYCLOCONVERTERS                                                       | •• / | 2   |  |

| 1.3       | VOLTAGE SOURCE INVERTER (VSI)                                         | • •  | 3   |  |

| 1.4       | CURRENT SOURCE INVERTER (CSI)                                         | ••   | 3   |  |

| 1.5       | LCI SYNCHRONOUS MOTOR SYSTEM (CLM)                                    | ••   | 5   |  |

| 1.6       | LITERATURE SURVEY                                                     | ••   | 6   |  |

| 1.7       | DIGITAL CONTROL AND ITS MERITS                                        | ••   | 9   |  |

| 1.8       | REVIEW OF STARTING OF SYNCHRONOUS MOTOR                               | ••   | 10  |  |

| 1.9       | SCOPE OF PRESENT WORK                                                 | • •  | 15  |  |

| CHAPTER-2 | PRINCIPLE OF OPERATION                                                | ••   | 16  |  |

| 2.1       | GENERAL                                                               | ••   | 16  |  |

| 2.2       | PRINCIPLE OF OPERATION OF CLM                                         | ••   | 16  |  |

| 2,3       | SPEED CONTROL OF CLM                                                  | ••.  | 18  |  |

| 2.4       | STARTING OF COMMUTATORLESS MOTOR                                      | ••   | 19  |  |

| 2.5       | STARTING WITHOUT AN AUXILIARY SCR                                     | • •  | 20  |  |

| 2.6       | STARTING WITH AN AUXILIARY SCR IN PARALLEL<br>WITH D.C. LINK INDUCTOR | ••   | 20  |  |

| •         |                                                                       |      |     |  |

| Pa | qe | ·No |  |

|----|----|-----|--|

|    |    |     |  |

|          | '    | · ·                                                                                  |      |             |

|----------|------|--------------------------------------------------------------------------------------|------|-------------|

| 2        | .7   | DISCONTINUOUS LINK CURRENT MODE OF OPERATION                                         | • •  | 22          |

| <b>2</b> | .8   | THREE PHASE SCR BRIDGE (LCI)                                                         | ••   | 23          |

| 2        | .9   | SYNCHRONIZATION AND ZERO CROSSING DETECTION<br>FOR CM CONVERTER                      | ••   | 24          |

| 2        | .10  | GATING FOR THREE PHASE FULLY CONTROLLED THYRISTOR CONVERTER                          | ••   | 27          |

| 2        | .11  | ZERO CROSSING CIRCUIT FOR CS CONVERTER                                               | ••   | 28          |

| 2        | .12  | DESIGN OF FIXING CIRCUIT                                                             | ••   | <b>29</b> . |

| 2.       | .13  | DIGITAL SPEED MEASUREMENT SYSTEM                                                     | ••   | 30          |

| 2        | .14  | MICROCOMPUTER BASED CONTROL SCHEME                                                   | ••   | 31          |

| 2        | .15  | CONCLUSIONS                                                                          | ••   | 31          |

| CHAPTER  | -3   | SYSTEM SOFTWARE IMPLEMENTATION AND FLOW CHARTS                                       | ••   | 33          |

| 3        | .1   | GENERAL                                                                              | ••   | 33          |

| 3        | .2   | GENERAL PURPOSE PROGRAMMABLE PERIPHERAL<br>DEVICES                                   | ••   | 34          |

| 3        | .3   | MAIN PROGRAMME                                                                       | ••   | 35          |

| 3        | •4 · | ADC SUBROUTINE                                                                       | • •  | .39         |

| 3        | .5   | FREQUENCY ADJUSTMENT AND ACTUAL SPEED<br>MEASUREMENT SUBROUTINE                      | • •  | 41          |

| 3        | .6   | IR <sub>o</sub> (∝CS) INTERRUPT ROUTINE                                              | •• • | 42 ,        |

| 3        | .7   | IR <sub>1</sub> (60°CS) INTERRUPT SUBROUTINE                                         | ••   | 44          |

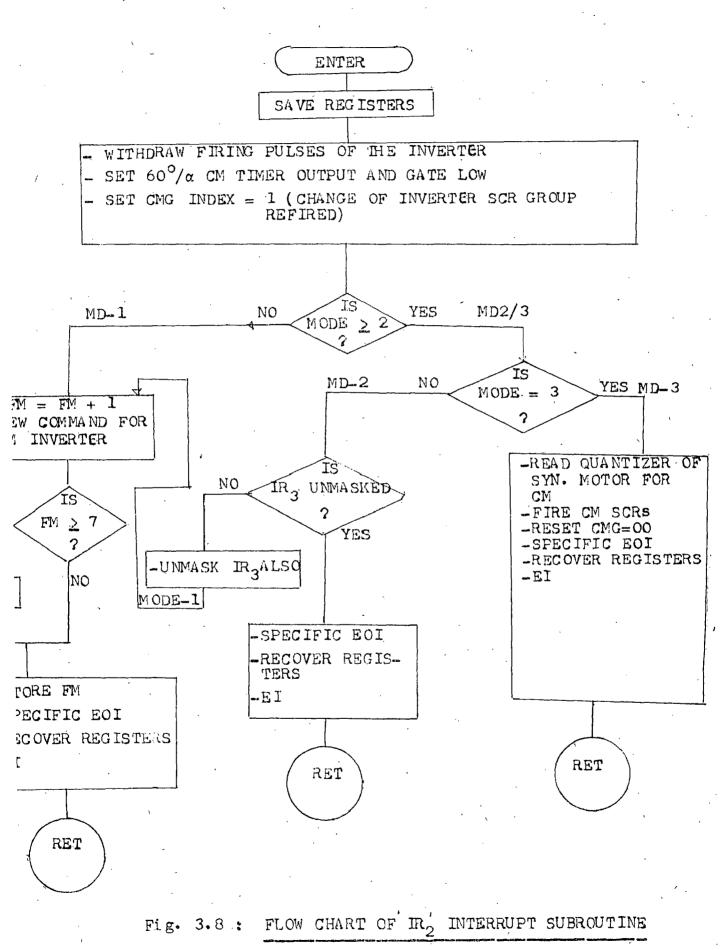

| 3        | .8   | IR <sub>2</sub> INTERRUPT SUBROUTINE                                                 |      | 46          |

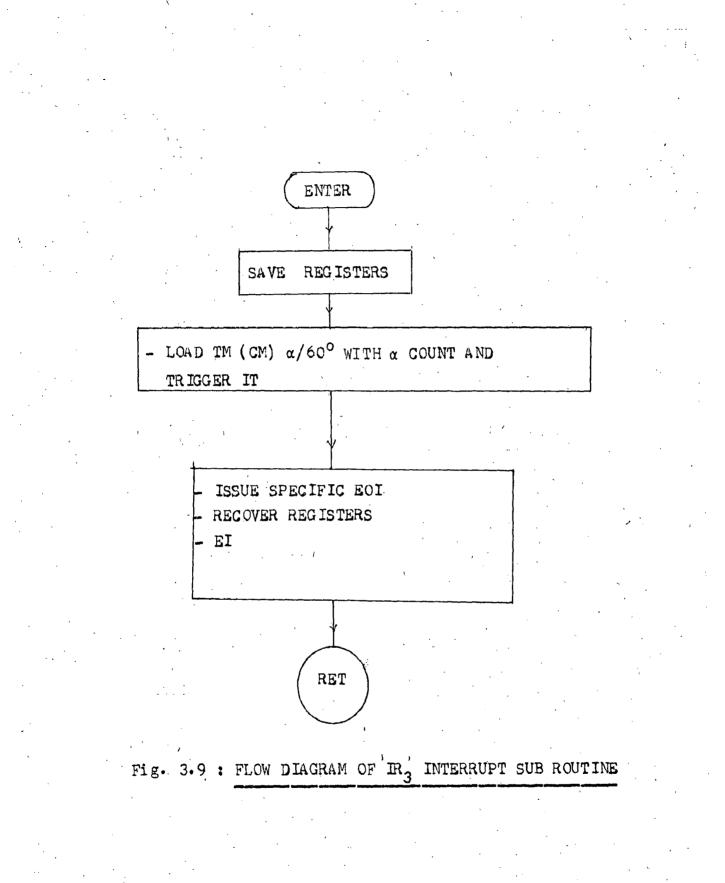

| 3        | .9   | IR <sub>3</sub> (3 PHASE SYNCHRONOUS MACHINE ZERO CROSSING)<br>ISS (BASE INTERRUPTS) | ••   | 47          |

|          |      |                                                                                      |      |             |

i

Page No.

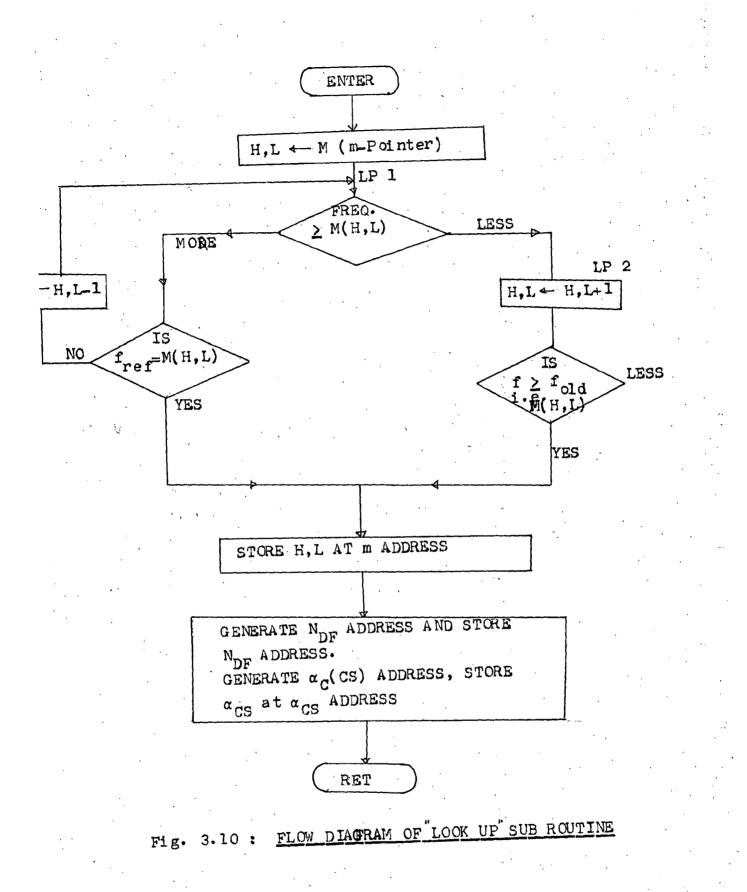

| 3.10      | 'LOOK' SUBROUTINE                                                                             | ••       | 48 |

|-----------|-----------------------------------------------------------------------------------------------|----------|----|

| 3.11      | DETERMINATION OF LOOK UP VALUES                                                               | ••       | 49 |

| 3.12      | CONCLUSIONS                                                                                   | •••      | 52 |

| CHAPTER-4 | SYSTEM PERFORMANCE AND EXPERIMENTAL RESULTS                                                   | ••       | 53 |

| 4.1       | GENERAL                                                                                       |          | 53 |

| 4.2       | EXPERIMENTAL INVESTIGATIONS FOR STEADY<br>STATE PERFORMANCE OF LCI-SYNCHRONOUS MOTOR<br>DRIVE | ••       | 53 |

| 4.3       | AUTOMATIC STARTING OF THE LCI-SYNCHRONOUS<br>MOTOR SYSTEM                                     | ••       | 54 |

| 4.4       | STARTING OF THE LCI-SYNCHRONOUS MOTOR<br>SYSTEM                                               | ••       | 56 |

| 4.5       | RESULTS AND DISCUSSIONS                                                                       | • •      | 57 |

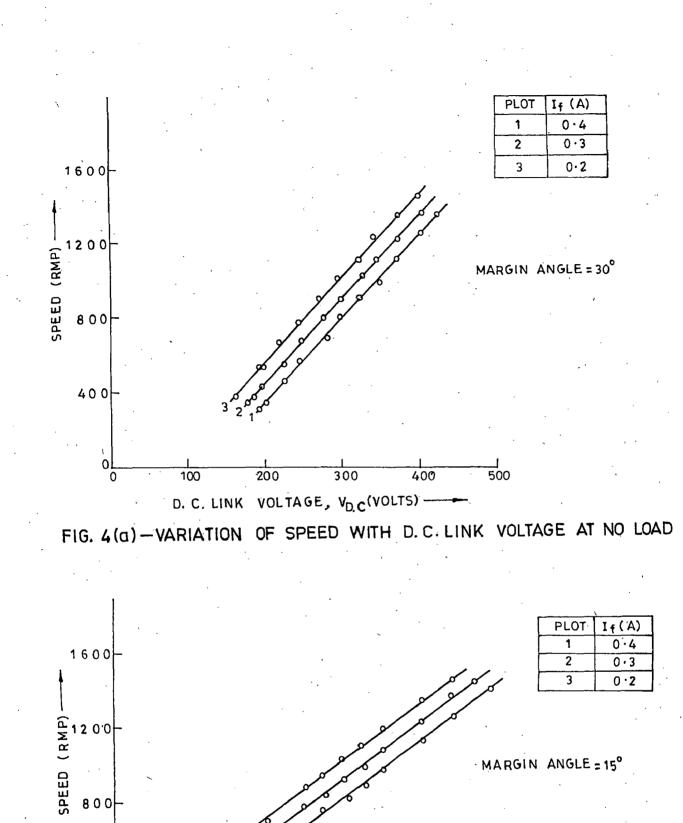

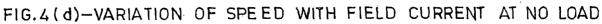

| · .       | 4.5.1 Effect of Variation of D.C. Link<br>Voltage on Speed                                    | ••       | 57 |

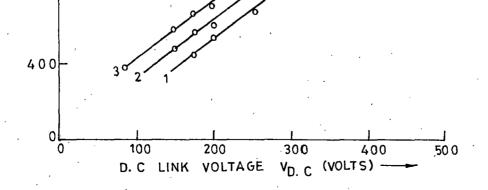

|           | 4.5.2 Effect of Variation of D.C. Link<br>Voltage on Speed                                    | •••      | 58 |

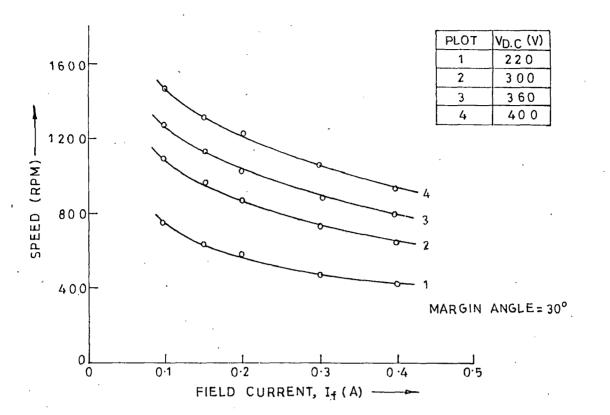

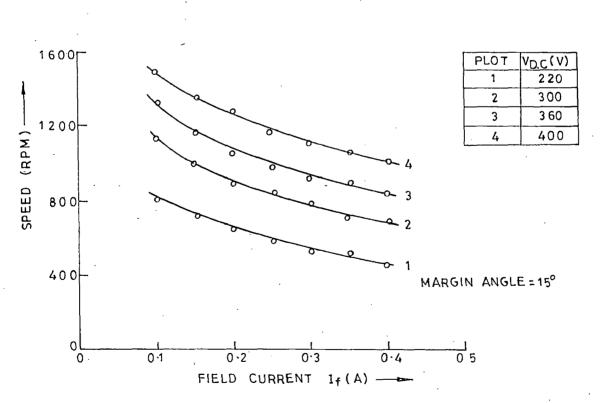

|           | 4.5.3 Effect of Variation of Torque on Speed                                                  | •••      | 59 |

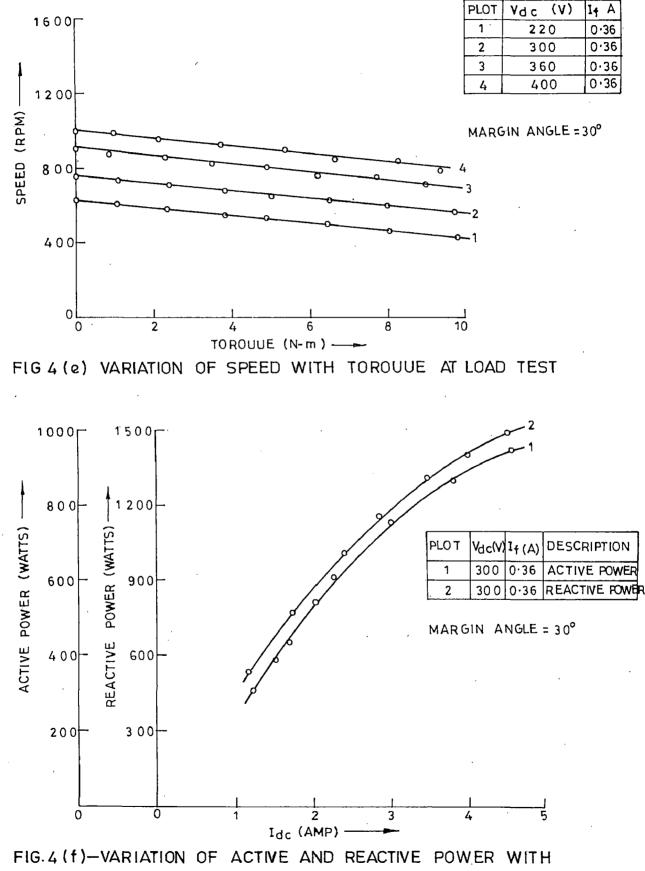

| •         | 4.5.4 Effect of I <sub>dc</sub> on Active and Reactive<br>Power                               | ••       | 59 |

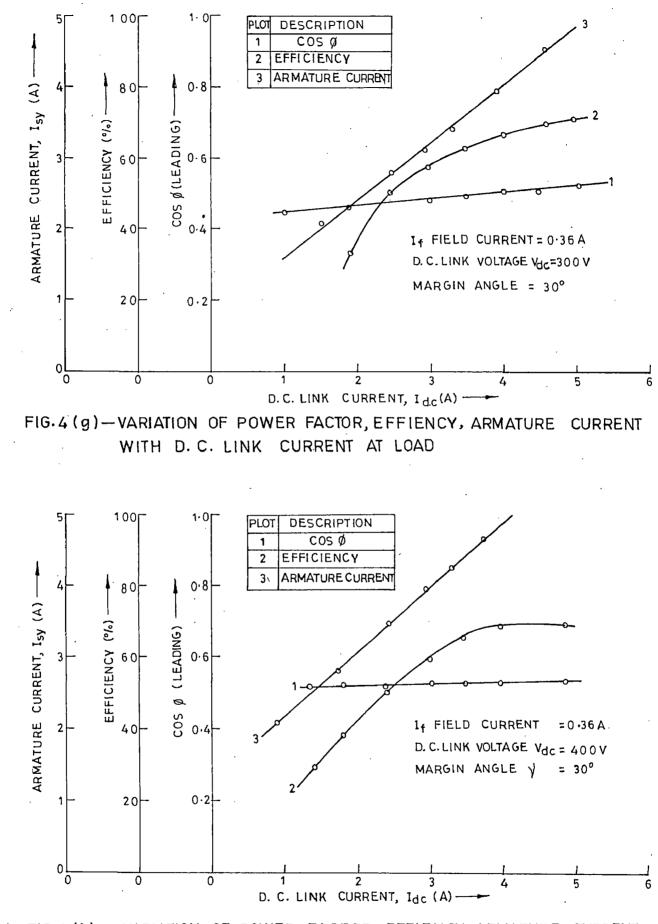

|           | 4.5.5 Load Current Efficiency and Powerfactor<br>Versus DC Link Current Cnaracteristics       | ••       | 59 |

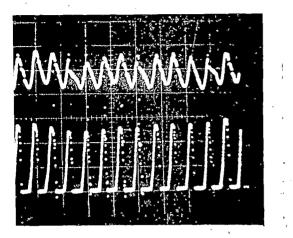

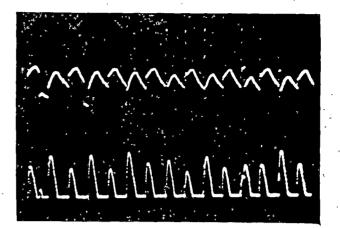

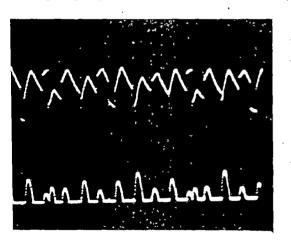

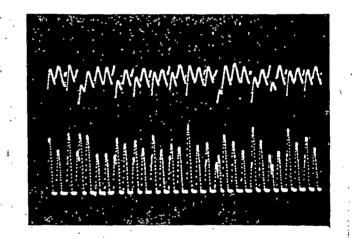

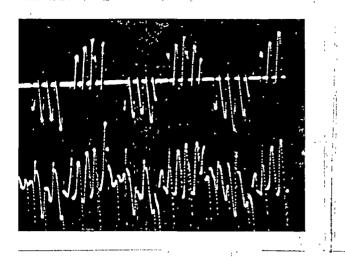

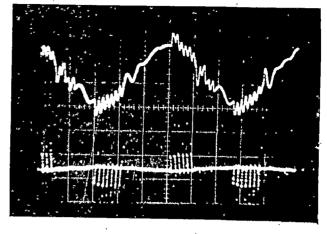

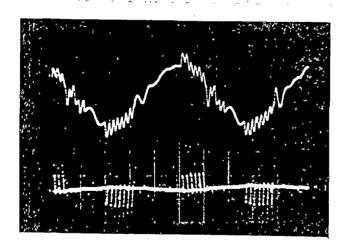

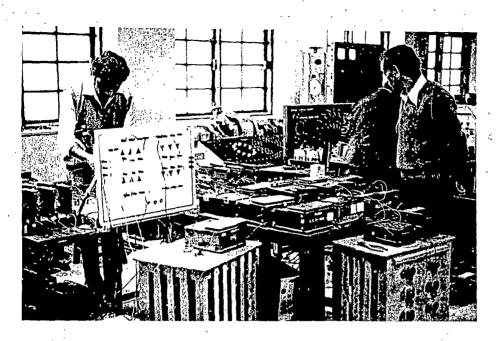

| 4.6       | DESCRIPTION OF PHOTOGRAPHS FOR NO LOAD<br>AND LOAD CONDITIONS                                 | •••      | 60 |

| 4.7       | CONCLUSIONS                                                                                   | ,<br>• • | 62 |

i

3- ....

Page No.

| CHAPTER-5 | CONCLUSIONS                           | ••  | 63  |

|-----------|---------------------------------------|-----|-----|

| 5.1       | MAIN CONCLUSIONS                      | ••  | 63  |

| 5.2       | SUGGESTIONS FOR FURTHER WORK          | ••  | 65  |

|           | · · · · · · · · · · · · · · · · · · · |     |     |

|           | REFERENCES                            | ••  | 67  |

|           | APPENDIX-A                            | ••  | A-1 |

|           | APPENDIX-B                            | ••  | B-1 |

|           | APPENDIX-C                            | • • | C-1 |

|           |                                       |     |     |

-

. .

.

· · · ·

# CHAPTER - 1

#### INTRODUCTION

### 1.1 GENERAL

Variable speed d.c. drives used in most of the cases are being fed by static converters using rectifier bridges. The use of d.c. motors in these drives has a number of mechanical and electrical limitations caused by the necessity of fitting a mechanical commutator.

The construction of the mechanical commutator has to be extremely delicate and finally the actual power is limited in the region of 10 MW for rated speed of 1,000 RPM and 500 KW for 500 RPM. The use of these machines is absolutely impossible in explosive, corrosive, or dust-filled atmosphere [1]. The cage induction motor on the other hand, has the robust rotor construction which permits reliable and almost maintenance free operation. Inspite of these advantages the inherent limitation of constant speed of operation has been the main bottleneck in its widespread use as a variable speed drive.

Of the various methods of a.c. motor speed control, its operation at variable frequency is becoming more and more popular, since it is possible to obtain variable speed as well as good regulation and high efficiency. The static variable frequency converters are expensive but are advantageous interms of accuracy and reliability. The current research in adjustable speed a.c. drives is focussed on the cost reduction of the converter and control equipment [2]. The

variable frequency a.c. drives becomes particularly attractive in multimotor drive. Such multimotor drives find applications in textiles, synthetic fibre, paper industries, traction etc.

The solid state variable frequency sources for a.c. drives can be broadly classified into two types :

(i) Cycloconverters

(ii) D.C. link converters which include

a) Voltage source inverters (VSI)

b) Current source inverters (CSI)

c) Line commutated inverters (LCI)

### **1.2 CYCLOCONVERTERS**

A cycloconverter [2] converts a.c.supply of fixed frequency to a lower output frequency through a one step conversion process. The output frequency range is limited to about one third of the supply frequency and therefore the drives employing cycloconverters are suitable only for operation at lower frequency. The output voltage of cycloconverter contains complex harmonic patterns. However, one advantage drives is that the SCRs are naturally commutated of cyclo converter and regeneration is simple. The system can be easily designed for four quadrant operation. The cost and complexity of power and control circuits however, make them uncompetitive with other classes of drives. Two prominent applications of cycloconverter are traction vehicles and gearless rotary kilns.

# 1.3 VOLTAGE SOURCE INVERTER (VSI)

The VSI's are generally classified into two types, square wave inverters and pulse width modulated inverters. The square wave output voltage leads to a number of undesirable effects, such as additional harmonic power losses and torque pulsations in motors. The harmonic currents flowing in stator and rotor contribute to extra copper losses and some amount of iron losses. The commutating capacitor in the voltage source inverter is usually charged by the d.c. link voltage; hence, commutating capability decreases as the d.c. link voltage decreases. The inverter requires six commutating cycles per cycle of fundamental, leading to increased commutation losses and requires complex control circuitry.

The voltage fed square wave inverter drives are normally used in low to medium horse power ratings where speed ratio is usually limited to 10:1. This type of drive has been largely superceded by PWM drives.

In PWM inverters the thyristors are switched on and off many times within a half cycle to generate a variable voltage output which is normally low in harmonic contents. Among the PWM techniques sinusoidal PWM technique reduces the harmonic losses but it suffers from low inverter efficiency [3].

### 1.4 CURRENT SOURCE INVERTER (CSI)

The current source inverter converts power between an adjustable current source and a single or three phase a.c. load. Since

the primary input power is usually supplied at a constant voltage, the inverter system consists of two stages:

- (i) The 'current source' which receives the power from a fixed voltage a.c. or d.c. and supplies an adjustable d.c. current at the output terminals.

- (ii) The CSI is connected in cascade with the current source. It converts the d.c. current at the input to an a.c. current at the output terminals.

The CSI drives has many good features. They are [4]:

- (i) Regeneration is possible.

- (ii) There is no possibility of shoot through fault

- (iii) The fault current on the inverter side rises very slowly

(iv) Commutation losses are less

(v) The inverter can be designed with low speed SCRs.

Against the above merits, the CSI drives have the following limitations :

- (i) The frequency range of inverter is lower and it cannot operate on no load,

- (ii) The large size of d.c. link inductor and the commutating capacitor makes the inverter expensive,

(iii) The drive has instability problems and sluggish response at light loads and high speeds.

A line-commutated inverter is obtained by operating an SCR bridge in continuous current mode with firing angle greater than 90°. The sequential commutation of SCR is obtained with the help of three phase line voltages.

The line commutated inverter overcomes all the problems of forced commutated inverters as well as cycloconverters. Some of the characteristic features of LCI are :

(i) No harmonics in the output voltage waveform

(ii) Commutating components are not required

(iii) The firing circuit requirements are simpler.

### 1.5 LCI SYNCHRONOUS MOTOR SYSTEM (CLM)

The Line Commutated Inverter (LCI) Synchronous machine combination gives the characteristics of a d.c. motor. The commutation of SCRs is controlled by the sinusoidal induced voltage in stator due 'to rotating field of rotor. This combination is popularly known as the commutatorless d.c. motor (CLM). This type of drives is used for starting of large rating gas turbine sets, boiler feed pumps etc. Where precise simultaneous speed control of a number of motors is required, a system using a synchronous motor offers a practical approach. Further, a synchronous machine responds more quickly than an induction machine to change in load torque. Also a variable frequency synchronous motor drive offers the possibility of simple precise position control [4].

The commutatorless motor has been generally used by industry in following cases :

(i) When high speeds up to 7,000 RPM are required

(ii) When high ratings up to 10,000 KW are required

(iii) When high efficiency is required.

### 1.6 LITERATURE SURVEY

Extensive literature is available on LCI-Synchronous machine system operating as a commutatorless motor. GORDON and S.B. DEWAN [4] have described the steady state properties of a variable speed drive using a synchronous motor fed by a controlled current source inverter. The performance is evaluated using equivalent circuit model and results are confirmed by experiment. They also discussed the advantages of LCI fed synchronous machine system.

Hoang Le Huy, Jakubowicz and Perret [5] have discussed a current source self controlled synchronous motor drive, in which the motor terminal voltage is used to synchronize the inverter triggering pulses. The implementation of microprocessor based control system is also described.

In the paper by R. Venkataraman and B. Ramaswamy [6] the authors described the development, design and construction of a variable speed drive using a synchronous motor. The operation of motor with a current-fed motor-emf commutated inverter is explained. It has also been shown that the digital simulation based on simplified block diagram is accurate enough for obtaining the responses of the system to step changes in speed reference and load on motor.

Ranganadhachari, B.P. Singh et al presented a paper [7] which describes the operation principle, characteristics and limitations of variable frequency source in which a line commutated thyristor bridge inverter acts in combination with a synchronous machine as a variable frequency source. Experimental results and performance curves are also discussed.

Peichang Tang, Snui-Snong Lu, and Yung-Chun Wu [8] presented a paper describing a firing scheme based on a microprocessor to control an antiparallel connected three phase thyristor dual feed converter. Using table look-up algorithm to speed up the response, a full range control of firing angle between 0° to 180° for both positive and negative current control is achieved. The maximum time delay required to correct the firing angle is one sixth period of the a.c. power source. The firing angle between 120° and 180° is used for the regeneration braking to achieve the required dynamic performance in four quadrants. Together with software algorithm in microprocessor, the digitised a.c. power signals are used to find the correct firing output signals. This scheme uses less hardware components and has higner dynamic performance in four quadrant operation.

A.C. Williamson and K.M.S. Al-Khalidi [9] describe the naturally commutated converter fed synchronous machine drive of very high rating. At standstill and at very low speeds commutation is achieved by pulsing the current in the d.c. link between the supply and the machine converters. However, this gives rise to significant low frequency disturbances to the supply system. The paper also describes an alternative

method using a discontinuous current mode of operation, which gives smoother operation and less disturbance to the system. An analysis is given which shows that this starting method can give an average torque as high as 1.0 per unit.

Gerson H. Pfitscher has given [11] the microprocessor based scheme that generate the necessary synchronization signals for 3 phase static power converter control system. The problem of detecting the phase to phase voltage zero crossing in presence of noise generated by thyristor commutation in constant and variable frequency supplies is discussed, and a microcomputer software solution is proposed.

Chandrasekhar Namuduri and P.C. Sen presented a paper [13] which describes a digital simulation method for the self controlled synchronous motor in time domain. They also discussed the performance of the synchronous machine with non-sinusoidal voltage and currents under both steady state and transient conditions. The effect of the damper winding, and saliency on the torque, and voltage and current wave forms are also discussed using the digital simulation technique when the machine is operated from a voltage source inverter and a current source inverter.

Mario Beneditti and Carlos F. Christiansen presented a paper which describe the design of a trigger system [16] for full or half controlled thyrister converters of up to 6 pulses, using 8 bit micro processor. The device is independent from the sequence of the main voltage and from the circuit configuration of the system. The trigger angle may take any value from  $\Upsilon = 0^\circ$  to  $\Lambda = 180^\circ$  between pulses, thus achieving the maximum possible rate of change of the output voltage.

An outstanding aspect of the design described here is the new method of obtaining the synchronization signal.

### 1.7 DIGITAL CONTROL AND ITS MERITS

The result of rapid progress in semiconductor technology by planar processing and LSI has made digital electronics devices much smaller in size and cheaper. The drastic advance, in semiconductor technology have made smaller and faster microprocessors available at lower costs, thereby increasing the number of industrial applications in which they can be used. In industrial process control, it is at time necessary to adjust a motor's speed over a wide range with good resolution and reproducibility. They also require to have fewer components, to cost less, to be maintained easily, and to be more generally applicable. In order to achieve the above needs microprocessor is more suitable [19]. A closed loop control is usually necessary to often the necessary speed accuracy. It is possible to obtain greater accuracy, improved dynamic response and reduced effect of disturbances such as loading in closed loop or feedback systems.

A speed regulating system with a fast response can be realized by speeding up the current controller and speed controller with the use of microprocessor based system. In driving a.c. motor with a three phase bridge inverter, control processing must be performed during extremely short periods. Such a fast processing can be realized with certain modifications in the existing microprocessor software. The control algorithms are simple and can be easily implemented in real time on a microcomputer [20]. The analog control methods have several

disadvan tages, such as nonlinearity in the analog speed transducer, difficulty in accurately transmitting the analog signal errors due to temperature, component aging and so on.

A digital control system on the other hand is free from above disadvantages. A microprocessor based control system for motor drives distinct advantages such as flexibility, improved several promises Foremost among these economic viability. is the performance, and implemented in the software flexibility. The control scheme is Therefore, to change the control scheme in order to obtain a different drive characteristic or introduce a new control function only software needs to be modified, with minimal or no change in the hardware. A microprocessor based control system can be completely digitalised, with its sensitivity to external influence thereby decreased. microprocessor based control system requires few discrete components and less wiring, which will improve the reliability of the system. A microprocessor based drive is expected to give high accuracy, better time response, and better speed regulation provided. advanced control As the cost of microprocessors and their adopted. technique is associated peripherals continue to fall, microprocessor based control system will become cost competitive. In the near future micro-processors will be incorporated in industrial. drives requiring high levels of performance.

# 1.8 REVIEW OF STARTING OF SYNCHRONOUS MOTOR

The major drawback with the CLM is its inability to start from standstill because the gating signals of inverter SCRs are controlled

by the synchronous motor itself, and the commutation voltage necessary for machine commutation of LCI is not available. Hence, some other methods of commutation of current from one SCR to another is necessary. Several methods are known for this purpose. Some of these methods are discussed here.

Low Speed Operation

The machine-converter thyristor firing angles can be controlled by reference to either a.c. terminal voltages or rotor position or a combination of each, although the latter has advantages at low speeds, with the usual limit on current capability when inverting as dictated by device recovery time. The machine, when motoring, always takes a fundamental current at leading power factor.

The major difficulty during starting may be solved by application of forced commutation or by a cycloconverter. However, both these schemes involve complicated circuits and hence demand a large number of thyristors.

A usual technique to overcome this is to pulse the input direct current.

When the input d.c. voltage is chopped by inactivating the gate signal or by increasing the control delay angle by more than 90 degree, a negative voltage is applied to the ON thyristors, and the current decreases to zero [22]. After a short time, the thyristor will obtain a forward blocking ability. The relevant pair of thyristors at machine inverter will go off due to link current being zero. The

supply side rectifier will be refired and the next cycle pair of thyristors of machine-side converter will be fired. By repeating such a process several times, the motor will be accelarated to a speed sufficient to produce commutation EMF.

Low Speed comutation by Field Pulsing

A new method of low speed commutation of an inverter fed synchronous motor (CLM) makes use of transformer action between rotor and stator, the rotor being supplied from halfwave rectified a.c. commutation is automatic and require simple control circuits.

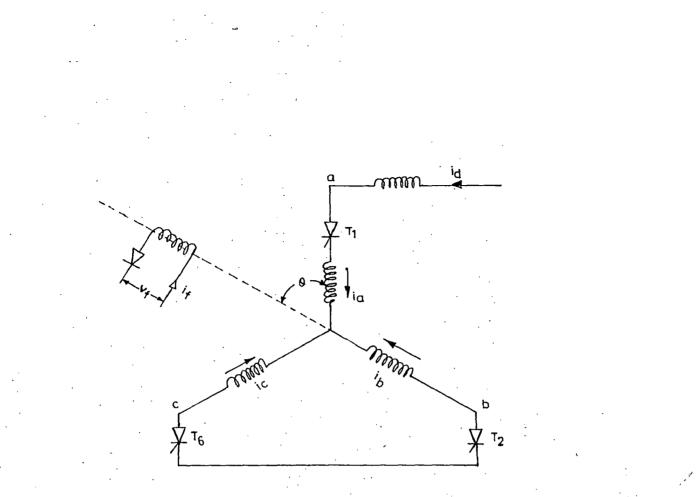

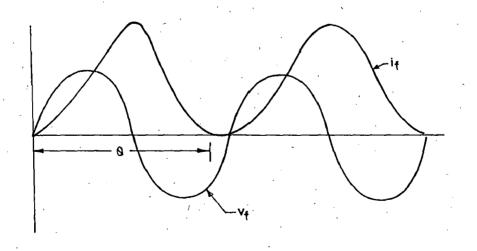

With reference to the Fig. 1.1 consider a particular stator winding current conduction pattern with field winding axis at angle ' $\theta$ ' to that at phase a, and the link current  $I_d$  conducting through thyristers  $T_1$  and  $T_6$ , so that  $i_1 = -i_b = I_d$  and  $i_c = 0$ . It is required to commutate from  $T_6$  to  $T_2$  so that  $i_a = -i_c = I_d$  and  $i_b = 0$ . For starting and low speeds this new scheme utilizes halfwave rectification of the field current if from an alternating voltage  $v_f$ . A typical waveform is shown in Fig. 1.2.

The process of commutation is achieved automatically when the firing pulses (derived from rotor position in the usual manner) are applied to the machine inverter thyristors. No additional control components are required, and only simple power electronic components are required in the field circuit [21].

FIG.1-1-TYPICAL COEFFICIANT ON FOR COMMUTATION PERIOD

# FIG.1-2-TYPICAL WAVEFORMS OF HALF RECTIFIER FIELD CURRENT

### Stand Still Rotor Position Detection

As explained above, at low speed (upto about 10% of the rated speed) the natural commutation cannot be applied because of lack of sufficient induced emf developed. Problem also arises to start the motor. In these drives a shaft position sensor is usually required for synchronizing the inverter triggering pulses to the rotor position. The stand-still rotor position provides the correct initial firing order for starting in the desired direction with maximum torque. Several methods can be applied i.e. (1) adding a simple optical or Hall effect position. detector which is used only for initial position sensing, (2) injecting a signal of some KHz is an auxiliary winding and analyzing the induced stator voltage.

Lately a method has been developed in which the induced emf in stator is analyzed when a step voltage is applied to the field winding. After a field supply is applied, the microcomputer sequentially samples the three stator induced voltages every 25  $\mu$ s so as to obtain their peak values and polarities. The rotor position is determined by the phase voltage with highest peak value and by the polarity of this voltage. This is sufficient to determine the correct thyristor pair to be triggred in order to create maximum torque in the desired direction.

### Starting Without an Auxiliary SCR

In this method, commutation is accomplished by forcing the rectifier bridge in to inverter mode during a short instant so as to interrupt the d.c. link current and reduce it to zero. The terminal

voltage is sensed and at each interval forced commutation is obtained as follows:

- (i) Inverter triggering pulses are stopped

- (ii) Rectifier (3 phase) firing is fixed at an angle greater than90°

- (iii) D.C. link current is monitored till it becomes zero

- (iv) Rectifier normal operation is then reestablished and the following SCR pair is triggered.

The main advantage of this technique is that no additional commutating component is required. However, during each commutation interval the motor current reduced to zero, so that instantaneous torque is zero during this period. This method is undesirable in case of high starting torque requirements.

### Starting with an Auxiliary SCR

This method of automatic starting is simplified when microcomputer control scheme is implemented. It requires two fully controlled 3 phase bridges and an additional SCR in parallel with d.c. link inductor. Forced commutation during each commutation cycle is achieved from the following steps :

- (i) Firing pulses to the two fully controlled bridges are inhibited.

- (ii) The auxiliary SCR is gated.

(iii) The current in the DC link is deviated through the auxiliary SCR and thus forced commutation at LCI SCRs is achieved[9].

The method overcomes the disadvantage of zero torque during commutation interval. In the present thesis an attempt has been made to start the motor using this method. The detail of the method is discussed in the Chapter-2.

### 1.9 SCOPE OF PRESENT WORK

In the present work an attempt has been made in the investigation to study the steady state performance of a synchronous motor fed from an LCI with a microcomputer control scheme. In this scheme a 3 phase a.c. supply of fixed frequency and voltage is converted into variable voltage d.c. supply to feed LCI using a fully controlled 3 phase bridge rectifier.

The present work has the following objectives:

- (i) Design and fabrication of two fully controlled converters,one acting as a rectifier and other as an inverter.

- (ii) Development of microcomputer base firing scheme for both converters.

- (iii) Design and Development of zero crossing scheme for both converters.

- (iv) An attempt to self starting of the line commutated synchronous motor.

- (v) Experimental investigation of LCI synchronous motor systemperformance under steady state conditions.

### CHAPTER - 2

# PRINCIPLE OF OPERATION

### 2.1 GENERAL

This chapter mainly deals with the principle of operation of power and control circuits. The design of rectifier-inverter circuits, firing circuits and zero crossing circuits is also given in this chapter. The advantages of the microcomputer based control circuit, the determination of conduction intervals of individual SCRs for both converters and the sequence of firing is also clearly discussed for both starting and running modes of the drive.

# 2.2 PRINCIPLE OF OPERATION OF CLM

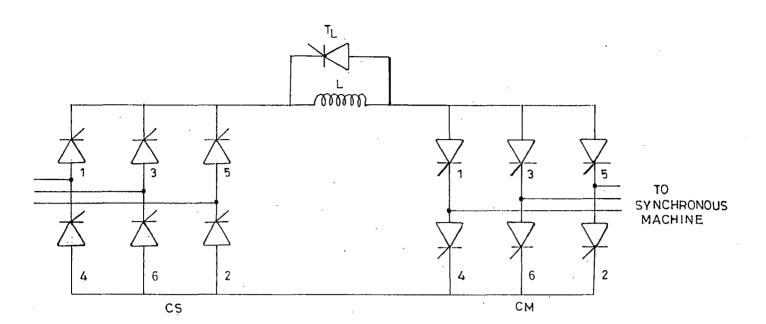

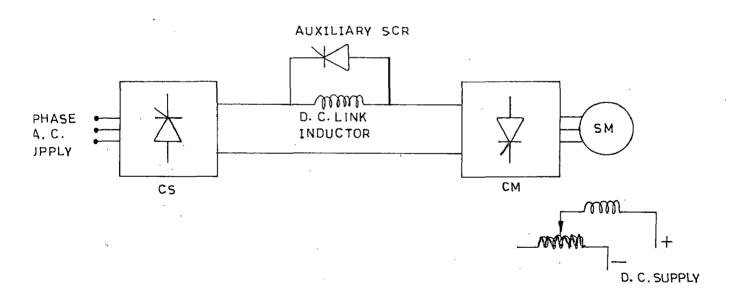

A commutatorless motor (CLM) consists of the following essential parts. The block diagram of CLM is as shown in Fig. 2.1.

- (i) A rectifier (fully controlled) (CS)

- (ii) An inverter (LCI) (CM)

- (iii) A d.c. link inductor (L)

- (iv) A link thyristor  $(T_1)$

- (v) A synchronous motor (over excited) (SM)

- (vi) Firing and control circuits for both converters.

Rectifier (supply) CS

This is a 3 phase fully controlled SCR bridge converter. The main function of the bridge is to supply variable d.c. link voltage from

a three phase a.c. supply. The output voltage of the converter is carried by changing the firing angle ( $\propto$ ) in case of fully controlled converters. The advantage of fully controlled operation of two bridges is that regeneration is possible by exchanging the mode of operation of the two bridges i.e. rectifier becomes inverter and inverter becomes rectifier.

Inverter (Machine Converter) CM

Inverter is also a 3 phase fully controlled bridge. It is used to convert d.c. power into a.c. power at desired output voltage and frquency. The output voltage can be changed by changing the firing angle ( $\propto$ ) and frequency by changing the gating frequency of SCRs.

D.C. Link Inductor

The inductor plays the role of smoothening out the ripples in the d.c. voltage of inverter input terminals. The value of the inductor plays a decisive role on the system performance. If the value of the link inductance is sufficiently high then the current becomes continuous under LCI operation.

Synchronous Motor SM

The LCI and synchronous motor constitutes a commutatorless d.c. motor. The synchronous motor is overexcited and supplies leading reactive power to the inverter. The inverter provides the active power to the synchronous motor for the load applied to it, and to overcome its losses.

The CLM motors can be realised, depending upon the placement of the field winding as :

(a) Series CLM

(b) Shunt CLM, or

(c) Separately excited CLM

2.3 SPEED CONTROL OF CLM

The speed of the drive can be changed by varying any one of the following parameters:

(i) d.c. link voltage; V<sub>dc</sub>

(ii) inverter firing angle; '\alpha'

(iii) synchronous motor field current; I<sub>f</sub>

The frequency of the output terminal voltage of the inverter can be given by

$f = k.V_{dc}/I_{f} \cos \alpha$

In the present work control of firing angle and the d.c. link voltage is obtained with the help of microcomputer based firing scheme.

The digital control scheme based on microcomputer is used because the analog firing schemes have the following demerits:

(i) Variation of firing angle  $\propto$  is limited to 90° by using cosine firing angle.

(ii) The harmonic content of the voltage waveforms can disturb the firing pulse instants, leading to misfiring of SCRs. (iii) Hard wired logic circuitry fixes the firing scheme philosophy and any change, if necessary, cannot be included without changing the circuit.

### 2.4 STARTING OF COMMUTATORLESS MOTOR

Variable speed drives (VSDs) using the synchronous motor as prime mover have several advantages in their favour compared with VSDs employing other types of motors. Firstly, the synchronous motors are rugged, reliable and free from troublesome commutator maintenance problems. Secondly, the power circuit configuration for a.c. to d.c. conversion and variable frequency generation needs no more than twelve thyristors of converter grade and is quite simple in structure. Thirdly, the drive can be operated at high speeds, an advantage not possessed by drives with other types of motor [6].

Synchronous motor drives have a few draw backs :

(i) Starting of the drive needs some types of auxiliary arrangement

(ii) If the motor emf is to be used for commutation of inverter thyristors, then the inverter must be current - fed and this necessitates use of a large link inductance.

The automatic starting of CLM is more simplified when the microcomputer control is implemented. This method of starting requires two fully controlled bridges, one operating as a fully controlled rectifier supplying D.C. link voltage to CLM and another as a machine commutated inverter (LCI).

The automatic starting schemes can be broadly classified into two types :

(i) Starting without an auxiliary thyristor across D.C. link inductor.

(ii) Starting with an auxiliary SCR across D.C. link inductor.

### 2.5 STARTING WITHOUT AN AUXILIARY SCR

In this method, commutation is accomplished by forcing the rectifier bridge into inversion mode during a short instant so as to interrupt the d.c. link current and reduce it to zero. The terminal voltage is sensed and at each interval forced commutation is obtained as follows :

(i) Inverter triggering pulses are stopped.

(ii) Rectifier firing is fixed at  $\propto = 150^{\circ}$

(iii) D.C. link current is monitored till it becomes zero.

(iv) Rectifier normal operation is then re-established and the following SCR pair is triggered.

The main advantage of this technique is that no additional commutating component is required. However, during each commutation interval the motor current is reduced to zero, so that instantaneous torque is zero during this period. This method is undesirable in case of high starting torque requirements.

### 2.6 STARTING WITH AN AUXILIARY SCR IN PARALLEL WITH D.C. LINK INDUCTOR

This method of automatic starting also requires two fully

controlled three phase bridges and an additional SCR in parallel with d.c. link inductor as shown in Fig. 2.2.

The naturally commutated, converter fed synchronous machine is being used for drives at very high rating and speed in which range there are only mechanical alternatives. At standstill and at very low speed, commutation is achieved by pulsing the current in the d.c. link between the supply and the machine converters [9], and this gives rise to significant low frequency disturbance to the supply system. Forced commutation during each commutation cycle is achieved as follows :

(i) Firing pulses to the two fully controlled bridges i.e. rectifier and inverter are inhibited.

(ii) The auxiliary SCR is gated, and

(iii) .

The current through the d.c. link is deviated through the auxiliary SCR and thus forced commutation of LCI SCRs is achieved.

This method overcomes the disadvantage of zero torque during commutation interval obtained in the previous method.

During normal operation, converter (CS) and d.c. link choke(L) provide a controlled current source for the machine converter (CM), which absorbs the link power by operating in the inversion mode, and is naturally commutated by the machine winding voltage at rotational frequency. Natural commutation is possible provided that the firing angle of converter CM is suitably controlled and the winding voltages are adequate, however, such operation is not possible at standstill and very low speeds.

# FIG. 2-1-POWER COMPONENTS OF CIRCUIT

CS = SUPPLY CONVERTER (RECTIFIER) CM = MACHINE CONVERTER (INVERTER)

FIG. 2-2 - POWER CIRCUIT FOR AUTOMATIC STARTING OF SYNCHRONOUS MOTOR USING AUXILIARY SCR IN D.C.LINK

### 2.7 DISCONTINUOUS LINK CURRENT MODE OF OPERATION

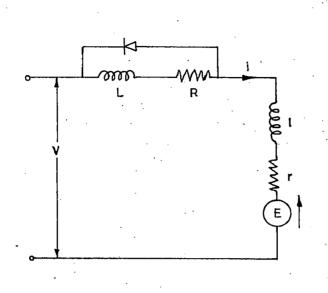

At very low machine speeds, the average link voltage is very low, and consequently the converter CS output voltage contains a high ripple at six times supply frequency. With no link inductance, the voltage ripple would be applied directly line to line across the machine winding through two triggered thyristors of converter CM. The effective circuit inductance would be low and the current discontinuous for high average values [9].

If the link current is discontinuous, pulsating at six times supply frequency, the all devices of converter CM will be reverse biased at the same frequency. Consequently, a change in firing pattern will result in automatic change in conduction pattern at the next ripple.

Such conditions can be approached if the link thyristor  $(T_L)$  is triggered continuously during the starting period, and this is easily effected without great control complexity. In this way the choke protects against rapid rate of rise of average link current.

Analysis of Current Ripple

The circuit of Fig. 2.1 can be approximated to the equivalent circuit of Fig. 2.3 for the case where the machine winding frequency is much less than the supply frequency. If the thyristor  $T_L$  is triggered continuously during the starting mode, it will behave as a diode across the choke (of inductance L and resistance R) as shown in Fig. The inductance  $\lambda$  is that presented by the machine to current variations at six times supply frequency, flowing through two phases, with the rotor

FIG. 2.4-EXPECTED VARIATION OF CURRENT IN LINK

at low speed. The machine converter will show a voltage E, which is assumed constant at this stage.

The voltage v, of output of the supply converter, will vary with converter firing angle  $\propto$ . Assuming the overlap in the supply converter to be negligible, v will be given by

$$v = V \cos(wt + \alpha - \pi/6)$$

for  $0 < wt < \pi/3$

whére,

V = peak line-line supply voltage =  $\sqrt{2}$  V<sub>1</sub>

w =  $2\pi \times \text{supply}$  frequency, and this repeats at six times per cycle.

In a steady state condition, therefore, the behaviour shown by Fig.2.4 can be expected, assuming current i to be discontinuous.

If  $\theta$  = wt then, at  $\theta$  = 0, i = 0, and the choke current is freee wheeling. The voltage v-E, being effectively applied to inductance 1, causes i to increase rapidly. At  $\theta = \beta$ , i becomes equal to the choke current, the thyristor blocks and any further rise in current i is opposed by inductance 1. At  $\theta = \epsilon$ , the voltage across the thyristor reverses,  $\sigma$ it conducts, and i drops to zero at  $\theta = \eta$ , with  $\eta < \pi/3$  for discontinuous current.

### 2.8 THREE-PHASE SCR BRIDGE (LCI)

A three phase SCR bridge has been used as a line commutated inverter. The commutation of the bridge is achieved by the back emf of the synchronous machine connected to the 3 phase output of the bridge.

The firing angle of the bridge is adjusted between 90° to 180° so as to obtain the inverter mode of operation. In the inverter mode, the direction of current flow through the bridge remains the same however, the d.c. terminal voltage of the bridge reverses polarity. Thus, the LCI is nothing but a three phase fully controlled converter with firing angle between 90° to 180°. The sequence of firing of SCRs and the conduction intervals can be explained with the help of a detailed description of 3 phase fully controlled converter.

The thyristors  $T_1$ ,  $T_3$  and  $T_5$  are called positive group SCRs because they are connected to the positive terminal of the d.c. link supply. While the thyristors.  $T_4$ ,  $T_6$ ,  $T_2$  are called negative groups SCRs because they are connected to the negative terminal of the d.c. link supply.

In one cycle of the a.c. supply wave there are six conducting intervals, each of 60° in which a pair of SCRs conducts. These intervals are as given in Table 2.1.

### TABLE 2.1

| Time in degrees; | 0°  | 60° | 120° | 180° | 240° | 300° |

|------------------|-----|-----|------|------|------|------|

| Firing sequence; | 1   | 2   | 3    | 4    | 5    | 6    |

| Conducting SCRs; | 6,1 | 1,2 | 2,3  | 3,4  | 4,5  | 5,6  |

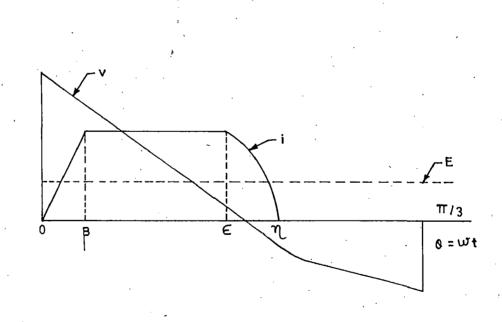

### 2.9 SYNCHRONIZATION AND ZERO CROSSING DETECTION FOR CM CONVERTER

Independently of the method or algorithm used to control thyristors firing of a three phase static power converter, the signals

that synchronize them with the alternating supply voltages are always necessary. For a three phase fully controlled converter there are six such logical signals each one associated with a thyristor and defined from the natural commutation instant, i.e. at the intersection of the two line to line voltages, which coincides with the zero crossing of another one. The zero voltage detector fulfils two different functions; the synchronization of the thyristor firing circuit to the input line frequency and the phase sequence identification.

The synchronous machine terminal voltage is isolated and fetched by three single phase transformers. From the secondary winding of these step-down control transformers, the digitized three phase power signals,  $\beta_R$ ,  $\beta_Y$  and  $\beta_B$  are obtained. These  $\beta_R$ ,  $\beta_Y$  and  $\beta_B$  signals are copnasal to the machine line voltages  $V_{RY}$ ,  $V_{YB}$  and  $V_{BR}$  respectively, and these three signals are displaced by 120° from each other. These digitised signals are sent to the microcomputer. The relationships between line voltages  $V_{RY}$ ,  $V_{YB}$ ,  $V_{BR}$  and these digitised signals are snown in Fig. 2.5.

Taking into account the digitised power signals, for a full  $360^{\circ}$  time range of synchronous machine a.c. cycle, a firing command data table is prepared on the basis of the number of the thyristors that are to be fired, for an  $\ll_{\rm CM}$  firing angle in 120° to 180° range, or 90° to 120° range. This firing command data table denotes the numbers of thyristors that are to be fired, for a particular type of digitised power signals which are high in a particular time interval.

The quantization signal  $\emptyset_R$ ,  $\emptyset_Y$  and  $\emptyset_B$  will be read via bits PA<sub>2</sub>, PA<sub>1</sub> and PA<sub>0</sub> of part A (8255-2). In the table 2.2, the quantizer signals are arranged in increasing order (001 at lowest address and

110 at the highest address). Thus, for a given firing angle range of  $\sim_{\rm CM}$  and the quantization signal read, the address of the firing command is easily determined and the same is tabulated in Table 2.2.

#### TABLE 2.2: FIRING COMMAND DATA FOR CM CONVERTER

(A) FOR  $\propto_{\rm CM}$  IN THE RANGE OF 120° TO 180° (AS INVERTER)

|                | •              |                |           |                  |                |

|----------------|----------------|----------------|-----------|------------------|----------------|

| Ø <sub>R</sub> | Ø <sub>Y</sub> | Ø <sub>B</sub> | Quantizer | SCRs to be fired | Firing command |

| 0              | 0              | 1              | 1         | 5,6              | 30H            |

| 0              | 1              | 0              | 2         | 3,4              | OCH            |

| 0              | 1              | 1              | 3         | 4,5              | 18H            |

| 1 .            | 0              | 0              | ,<br>4    | 1,2              | 03H            |

| 1              | 0              | 1              | 5         | 6,1              | 21H            |

| 1              | 1              | 0              | 6         | 2,3              | 06H            |

|                |                |                |           |                  |                |

, (B) FOR  $lpha_{\rm CM}$  IN THE RANGE OF 90° TO 120° (AS INVERTER)

| Ω | 1           | · 1                      | . 1.6                                                                                           | 21H                      |

|---|-------------|--------------------------|-------------------------------------------------------------------------------------------------|--------------------------|

| 0 | T           | T                        | . 1,0                                                                                           | . 2111                   |

| 1 | · 0         | 2                        | 4,5                                                                                             | 18H                      |

| 1 | 1           | 3                        | 5,6                                                                                             | 30Н                      |

| 0 | . 0         | . 4                      | 2,3                                                                                             | 06 H                     |

| 0 | 1           | 5                        | 1,2                                                                                             | 03 H                     |

| 1 | 0           | 6                        |                                                                                                 | OC H                     |

|   | 1<br>0<br>0 | 1 0<br>1 1<br>0 0<br>0 1 | 1       0       2         1       1       3         0       0       4         0       1       5 | 1024,51135,60042,30151,2 |

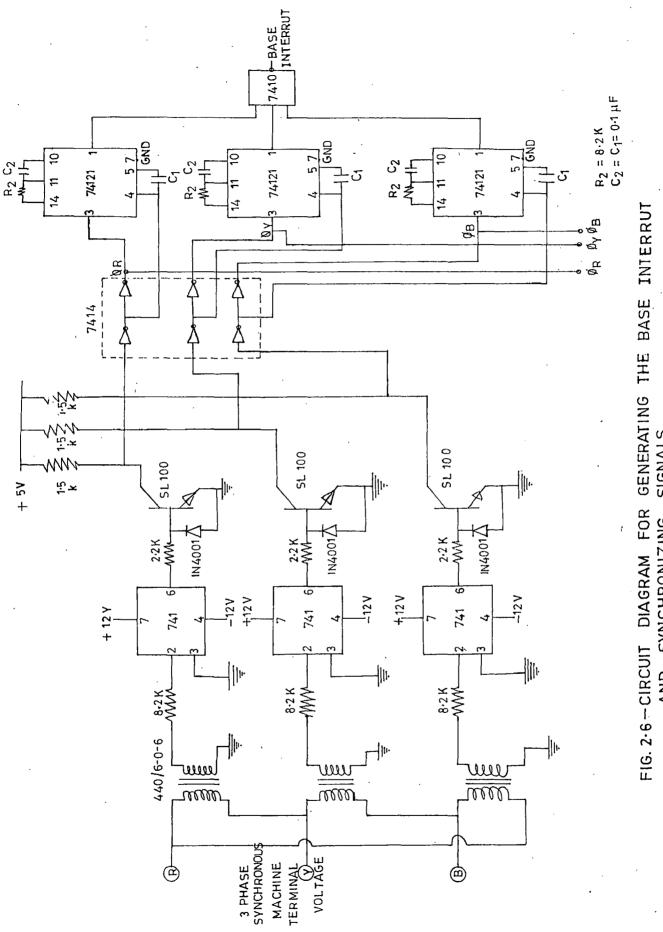

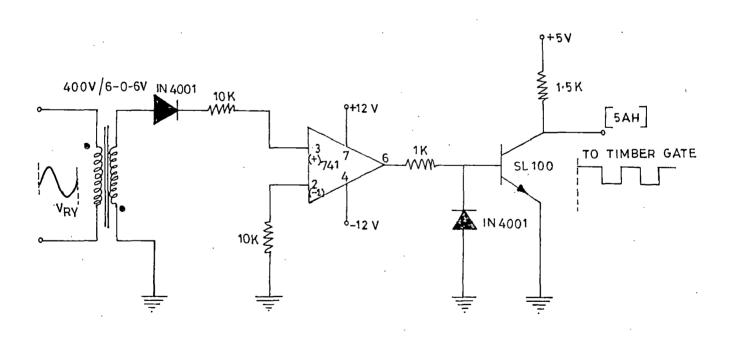

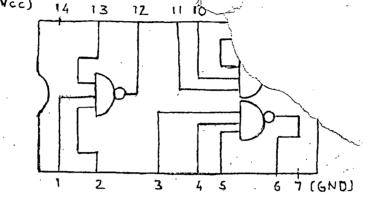

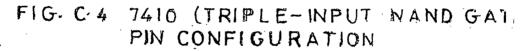

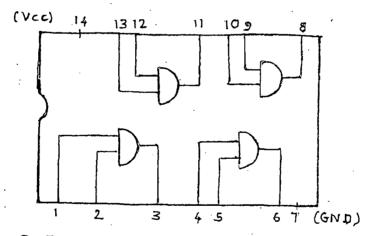

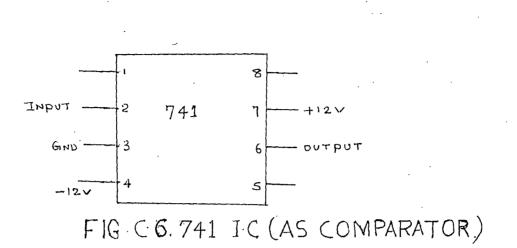

The circuit diagram for zero crossing detection (Base interrupt) and synchronization  $(\emptyset_R, \emptyset_\gamma, \emptyset_B)$  is given in Fig. 2.6. An I.C. 741 is used as a comparator. It compares the stepped down voltages obtained from synchronous machine terminals connected to pin No. 2.

SIGNALS SYNCHRONIZING AND

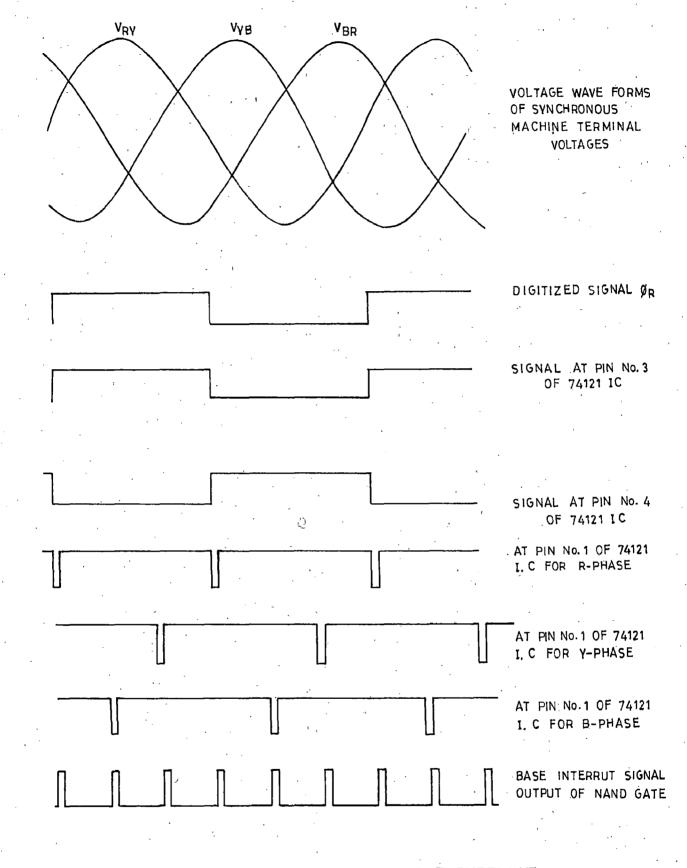

A manostable multivibrator is used to produce two pulses, one at the rising edge and another at the falling edge of each digitized signal. Combining these sets of pulse signals from the three phases, a base interrupt signal, B.I. is obtained. The base interrupt signal, B.I. has a frequency six times that of synchronous machine frequency. The interrupt signal occurs at each of six phase angles, 0°, 60°, 120°, 180°, 240° and 300° of the a.c. voltage of synchronous machine. A new firing cycle is started at the falling<sup>1</sup> edge of the base interrupt signal, B.I. The utilization of the base interrupt signal for interrupting the CPU and for generation of firing pulses for the correct thyristors is explained in the system software implementation. The theoretical waveforms for base interrupt circuit are given in Fig. 2.7.

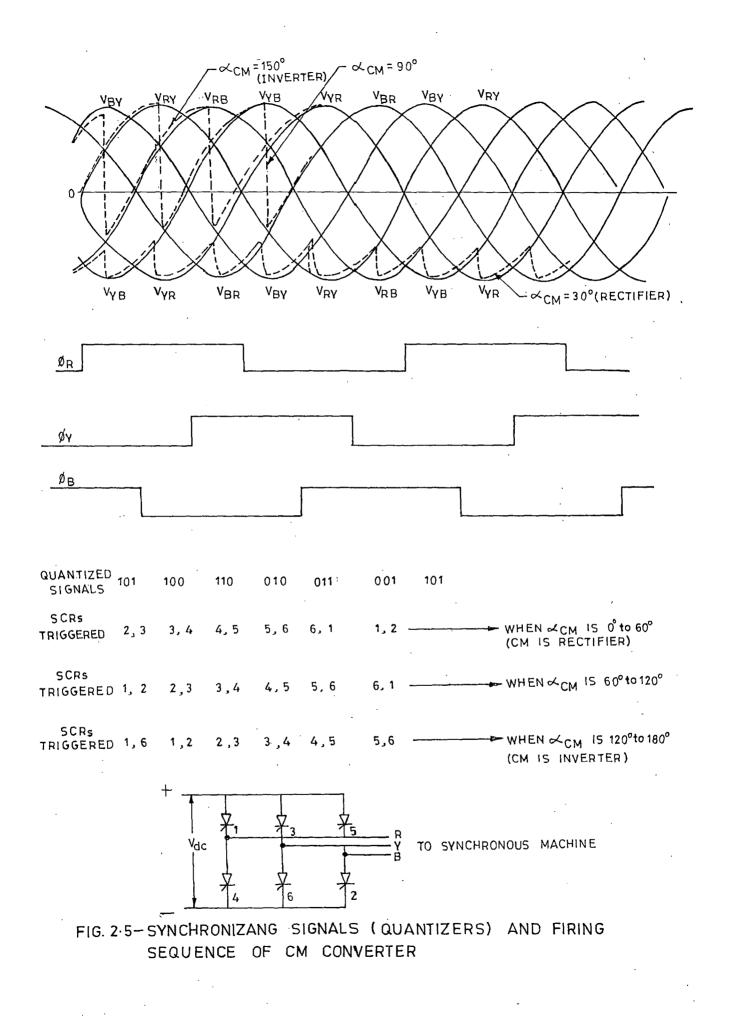

### 2.10 GATING FOR THREE PHASE FULLY CONTROLLED THYRISTOR CONVERTER

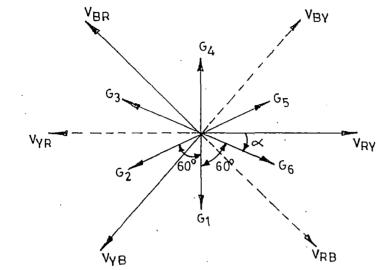

The operation of the three-phase bridge converter is explained earlier. There are six thyristors  $T_1$  to  $T_6$  which have to be triggered into conduction in a particular sequence. If the output current is assumed constant, the output voltage at any instant is equal to one of the six line to line voltages;  $V_{RY}$ ,  $V_{RB}$ ,  $V_{YB}$ ,  $V_{YR}$ ,  $V_{BR}$ ,  $V_{BY}$ . This requires that two thyristors one in the positive group  $(T_1, T_3, T_5)$  and one in the negative group  $(T_4, T_6, T_2)$  be gated simultaneously. In order to vary the average value of the output dc voltage, the instant of gate pulses to thyristor pairs must be controlled. Fig. 2.8 shows the phasor relation ship between the voltages and gating signals[1]. The line voltages are displaced from each other by 60°. The thyristors are gated in pairs forming six groups, i.e.  $(T_1, T_2)$ ,  $(T_2, T_3)$ ,  $(T_3, T_4)$ ,  $(T_4, T_5)$ ,  $(T_5, T_6)$ and  $(T_6, T_1)$ . The interval for each group is 60° and each thyristor

# FIG. 2.7 - THEORITICAL WAVEFORMS FOR BASE INTERRUT GENERATION CIRCUIT

conducts for two periods. The thyristor  $T_6$  is gated  $\swarrow^{\circ}$  after the zero crossing of  $V_{RY}$  voltage;  $T_1$  is gated 60° after gating of  $T_6$  and so on.

For satisfactory performance of the converter at firing angles varying from 0 to 90°, the gate pulses of 120° width are considered in the control circuit over the entire range of the firing angle. A control transformer is used to obtain an isolated, low level synchronizing signal which is in phase with the R-Y line to line voltage. It should be noted that the gating signals are sensitive to the phase sequence of the synchronizing signal. Therefore care must be taken in connecting the a.c. line to the synchronizing transformer in the correct phase sequence.

### 2.11 ZERO CROSSING CIRCUIT FOR CS CONVERTER

There are numerous approaches of designing gate pulses at required delay angle. The Fig. 2.9 shows the zero crossing circuit the for CS rectifier operation. The synchronizing line voltage  $V_{RY}$  is quantized to logic voltage level. A rectangular pulse is produced at the output 0f the comparator. The output of the comparator is given to the transistor The quantizer obtained from the transistor collector is directly base. given to the gate of the timer TM<sub>2</sub> (5 AH) loaded with  $\propto$  count. The output of the down counter gives an out pulse (interrupt) after the counting is completed. This is the instant for firing the SCR pair 5 and 6. Since input of the rectifier is operated with fixed frequency, only one the synchronizing signal is sufficient to produce the instants to fire a certain pair (5 & 6) of SCRs. The other pairs of SCRs will be find at every 60 degree subsequently by another timer TM $_2$  (59 H) working in mode '0' (interrupts on termian1 count). The firing pulses are kept

Y ZERO CROSSING (REFERENCE)

FIG.2.8-PHASOR RELATIONSHIP OF LINE VOLTAGES (ZERO CROSSINGS) AND GATING INSTANTS

FIG. 2.9-ZERO CROSSING CIRCUIT FOR RECTIFIER CS

120° wide through software. With bits 0 to 5 of part B (8255-1) for firing SCRs 1 to 6 of the CS converter (rectifier) and bit 7 (Part B) for firing the d.c. link SCR  $(T_L)$ , the sequential firing command, FS=1 to 6 are as follows :

| Fs                            | 1  | 2    | 3  | 4  | 5  | 6  |

|-------------------------------|----|------|----|----|----|----|

| Firing<br>Command<br>in (Hex) | BO | . A1 | 83 | 86 | 8C | 98 |

A bit is 'high' for issuing the firing signal.

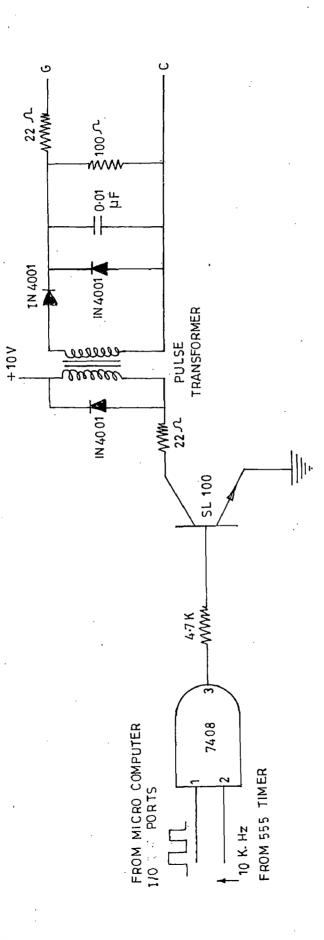

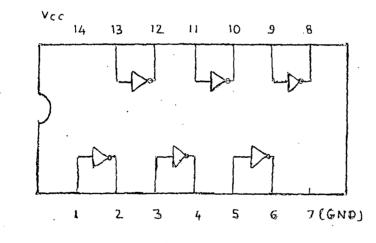

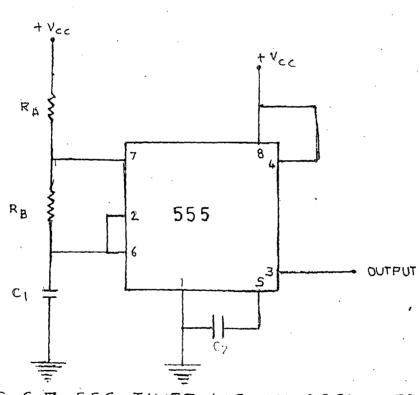

#### 2.12 DESIGN OF FIRING CIRCUIT

The pulses issued from the microcomputer I/O part may not be strong enough to turn on an SCR. Besides the gate and cathode terminals of the SCR are at higher potentials of power circuit, and the control circuit should not be directly connected to the power circuit. A pulse transformer is used to provide physical isolation between the control circuit and the power circuit. The firing pulse from the I/O part and an all time high signal (i.e. +SVDC) are 'ANDED' (to avoid µp loading), amplified and fed to the pulse transformer. For the inverter pulse µp firing command is ANDED with high frequency. This modulated/reduces the gate dessipation in the SCR. A diode is connected across the pulse transformer primary, to avoid the saturation of pulse transformer.

Gate protection is required for over voltage and over current. Because of the low power level of the control circuitry, this protection can be provided by simple means. The gate can be protected against over voltage by connecting a diode across gate and cathode and against overcurrent by connecting a resistance in series with the pulse transformer

input. A common problem encountered in the SCR circuitry is spurious firing of the device. Trigger pulses may be induced at the gates due to turn on or turn off of a neighbouring SCR or transients in the power circuit. These undesirable trigger pulses may turn on the device, thus causing improper operation of the circuit. Gates are protected against such spurious firing by using shielded cables or twisted gate lead connections. A capacitor is connected across the gate to cathode to bypass the noise pulses. The pulse amplifier circuit is shown in Fig. 2.10.

#### 2.13 DIGITAL SPEED MEASUREMENT SYSTEM

In industrial process control it is frequently necessary to adjust a motor's speed over a wide range with good speed resolution and reproducibility. Conventional analog control methods suffer on several accounts, including nonlinearity in the analog speed transducer and difficulty in accurately transmitting the analog signal after it has been obtained from the transducer. Errors also occured due to temperature, component aging and extraneous disturbances.

A digital speed measurement and control is superior in that there is no nonlinearity in the speed transducer, the digital signal representing speed can be transmitted long distances with no degradation of the original accuracy, and the digitally developed control signal is not subjected to temperature variations, component changes, or noise.

In the present thesis the actual speed is measured through an a.c. tachogenerator which is coupled to the motor. The a.c. voltage available through the tachogenrator is converted in to d.c. voltage

FIG. 2.10 - PULSE AMPLIFIER CIRCUIT

using a bridge rectifier and filter. The filtered d.c. voltage is reduced to a range of 5 volts (for max speed) using resistor and variable potential divider. The ADC interfacing directly displays the speed in HEX in the address field of the  $\mu p$  trainer via  $IN_1$  channel by implementation of software.

This digital speed measurement system is fabricated and tested individually. The scale is adjusted such that one bit represents 8 rpm. It shows satisfactory accuracy of the speed measurement by µp programme.

#### 2.14 MICROCOMPUTER BASED CONTROL SCHEME

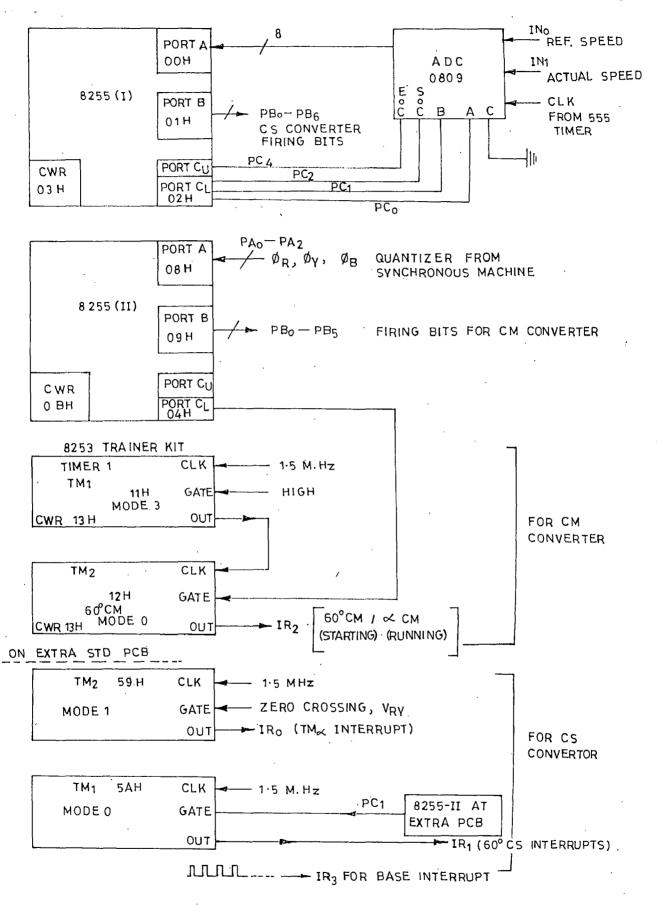

The VMC-85/9 microprocessor trainer is used for the system development. The various I/O parts and timer or counters, and their configuration are shown in Fig. 2.11

The scheme used for generating the firing pulses is shown in block diagram of Fig. 2.11. It consists of following parts :

- (a) Four signal transformers, each single phase 400 V/6 V

- (b) Two zero crossing circuits, one for rectifier (CS) and other for inverter (CM)

- (c) Timer card

- (d) Pulse amplifier circuits

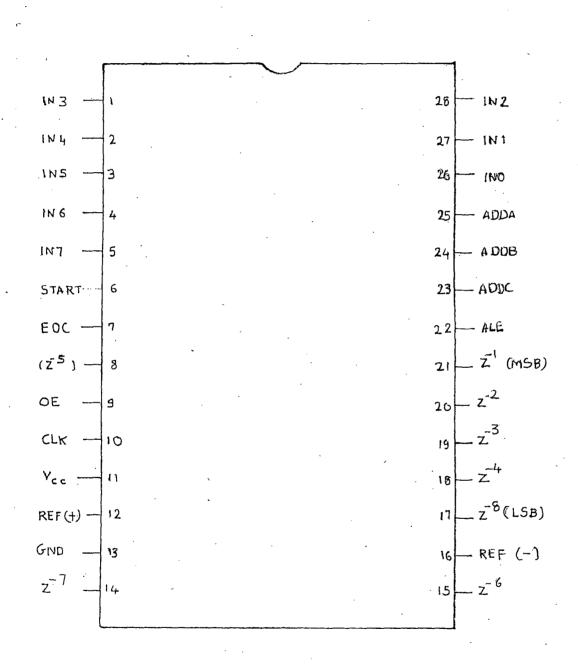

- (e) ADC interfacing circuit

- (f) Digital speed measurement system

#### 2.15 CONCLUSION

In this chapter the complete philosophy of microprocessor based speed control of self controlled synchronous motor drives is

FIG. 2-11-MICROPROCESSOR BASED SYSTEM CONFIGURATION

discussed. The power circuit, i.e. two three-phase fully controlled converters, the microprocessor based firing scheme, digital speed measurement, zero crossing circuits and ADC interfacing have been fabricated and tested.

# SYSTEM SOFTWARE IMPLEMENTATION AND FLOW CHARTS

CHAPTER

### 3.1 GENERAL

In this chapter mainly the overview of the microprocessor, its peripheral I.C. chips, development of system software and necessary flowcharts are described. The complete logic of speed control scheme of the self controlled synchronous motor drive is discussed in the main programme. The various subroutines used in conjuction with the main programme are also discussed.

#### Overview of Microprocessor

The digital control scheme for the synchronous motor drive has been developed using Vinytics Microprocessor Development System VMDS-85/9. This system is based on INTEL'S most popular microprocessor, the 8085. It is available in a 19" card cage having the facility of interfacing a number of STD Bus based cards. The three basic cards on which the VMDS-85/9 system is based are:

| (i)   |       | CPU ca | rd   |

|-------|-------|--------|------|

| (ii)  |       | RAMCa  | rd   |

| (įii) | ••••• | EPROM  | Caro |

The system can be easily expanded to accomodate some special purpose STD Bus based cards, e.g. Input-output and Timer card.

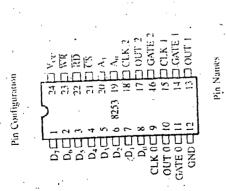

### 3.2 GENERAL PURPOSE PROGRAMMABLE PERIPHERAL DEVICES

To facilitate parallel data transfer between  $\mu p$  and I/O devices, certain programmable, general purpose devices (support chips) are used. These devices can act as an output port latching the data sent by the  $\mu p$  for the output device. They can act as an input port which is a tri-stated buffer to read data from the inputting device. These devices can generate an interrupt signal and receive/transmit certain control signals for data communicating between  $\mu p$  and I/O devices.

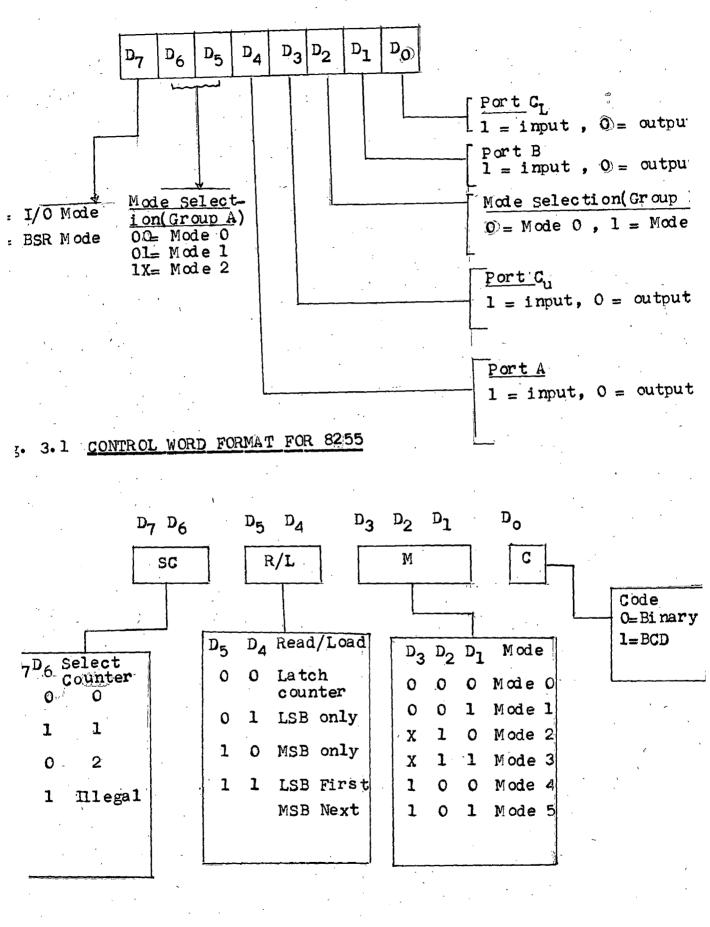

The 8255, a programmable peripheral interface (PPI) is one supporting device by INTEL. It can be programmed to transfer data under various conditions, from simple I/O to interrupt I/O. It has 24 I/O pins that can be grouped primarily in two 8 bit parallel parts: A and B, with the remaining eight bits as port C. The eight bits of port C can be used as individual bits or be grouped in two 4 bit ports :  $C_{\rm upper}$  (Cu) and  $C_{\rm lower}$  (C<sub>L</sub>). There are 3 major modes of operation. In the first mode (Mode O), each group of 12 I/O pins may be programmed in sets of 8 pins (port A or B) and 4 pins (half port) to be input or output. In Mode 1, the second mode, each group may be programmed to have 8 lines of input or output with the remaining 4 pins, 3 are used for hand shaking and interrupt control signals. The third mode of operation (Mode 2) is a bidirectional bus mode.

The control word format of 8255 is as shown in Fig. 3.1.

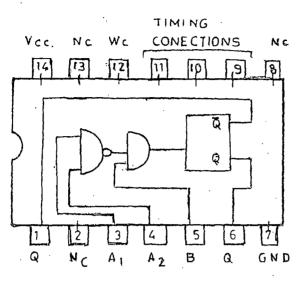

Another often used support chip is the 8253 programmable Interval Timer. It is a programmable counter/timer chip having 3 indepen-

Fig. 3.2 : CONTROL WORD FORMAT OF 8253

·· ·

dent 16 bit counters, each with a count rate of upto 2 MHz. The counter can count either in binary or BCD. Each counter has two input signals CLOCK and GATE, and one output signal OUT. At the CLOCK input pin is connected a clocking signal of suitable frequency. Depending upon the mode of operation of the timer/counter, logic high voltage or low to high voltage transition at gate initiates or enables counting process. Each counter can be programmed in any one of 6 possible modes of operation. These modes are : Mode 0 - Interrupt on terminal count, Mode 1 - programmable one shot, Mode 2 - Rate generator or divide by N counter, Mode 3 - Square wave generator, Mode 4 - Software triggered strobe, Mode 5 - Hardware triggered strobe.

The control word format of 8253 is as shown in Fig. 3.2.

The 8259 is a programmable interrupt contoller (PIC) designed to work with 8085/8086. The 8259 can manage eight interrupts according instructions written in the control word register. It can also to individually. Τo implement mask/unmask each interrupt request interrupts, the Interrupt Enable flip-flop in the microprocessor should be enabled by writing the EI instruction, and the 8259 should be initialised by writing control words in the control register. The 8259 requires two types of control words: Initialization command words (ICWS) and operational command words (OCWS). The ICWS are used to setup the proper conditions and specify RST vector addresses. The OCWS are used to perform functions such as masking interrupts.

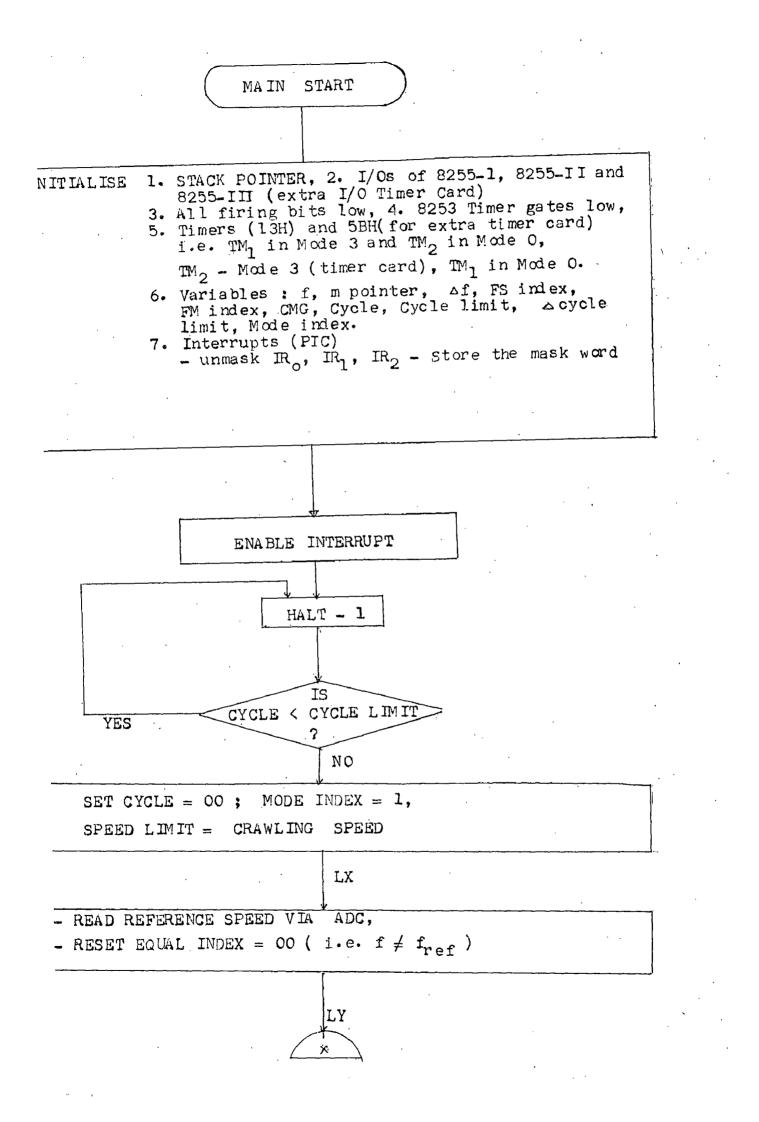

#### 3.3 MAIN PROGRAMME

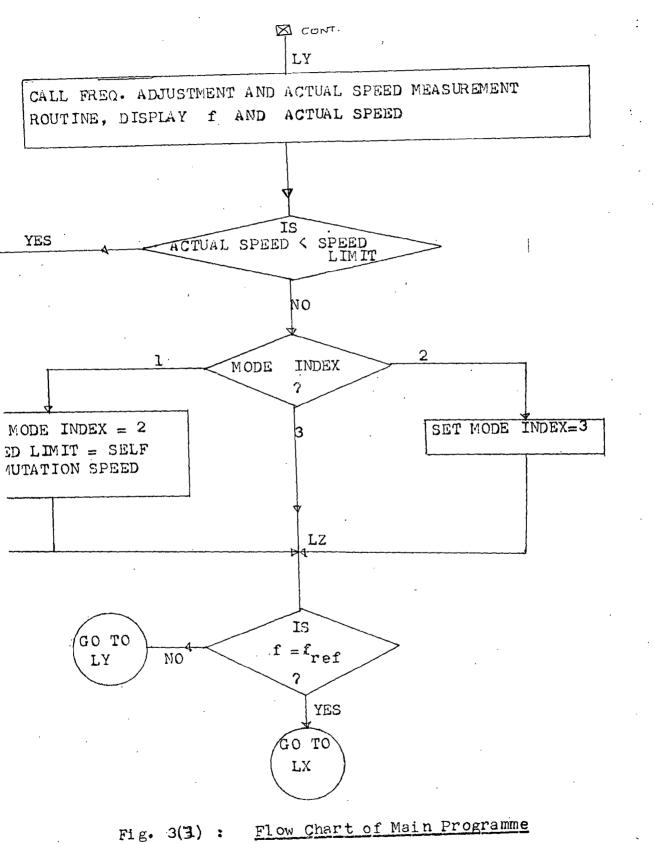

The flow chart of the main programme is shown in Fig. 3.3 Usually the program is started with the initialization of I/O ports,

(er.: Library University of Rob. and

which can be programmed as input parts or output parts according to the requirements.

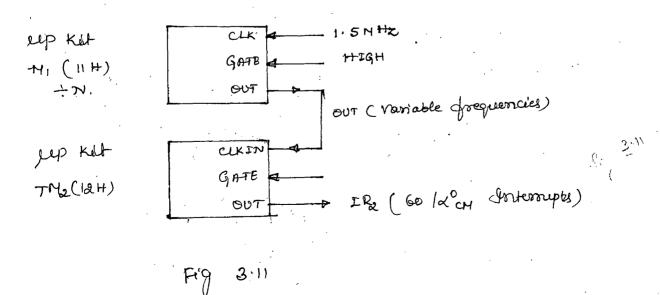

In the VMC 85/9 Vinytic Kit 3 timers and 6 I/O ports are available to the user at space  $J_1$ ,  $J_2$  and  $J_3$  respectively. In the present work 4 timers are used, they are  $TM_1$ ,  $TM_2$  of  $\mu p$  trainer kit and  $TM_1$ and  $TM_2$  of extra I/O timer card interconnected via the STD Bus of the kit. The  $TM_1$  and  $TM_2$  of extra I/O timer card are used in control scheme of rectifier and  $TM_1$  and  $TM_2$  of  $\mu p$  kit for inverter operation. The 8255s are initialised as follows:

8255-1 (CWR=03H)

i.e PORTA PORT B C<sub>11</sub> C<sub>1</sub>

IN OUT IN OUT 1001 1000=98H

8255-2 (CWR=OBH)

PORT A PORT B CU CL

IN OUT = 1001,0000 = 90H

8255-3 (CWR=87H in extra I/O timer card)

PORT A PORT B C C

x x 0UT = 1000 0000 = 80H

The Fig. 2.11 given earlier show the configuration of system hardware. In 8255-I, port A is for inputting the ADC data, port B is used for firing the CS converter (rectifier) thyristors and port C is for generating handshaking signals. In 8255-II,port A is for inputting quantizers, port B for firing CM converter (inverter) thyristors and port C for timer gate. The other 8255-III is used for giving gate signal for timer as shown in the diagram. The timers are initialised as follows:

$TM_1(11H)$  (µp trainer) in Mode 3, because this timer acts as a frequency divider. This can be moded as

TM<sub>1</sub> R/L Mode 3 Code

0 1 1 1 0 1 1 0 = 76H

$TM_{2}$  (12H) (µp trainer) is in Mode O to generate an interrupt on terminal count. This can be moded as

TM<sub>2</sub> P/L Mode 0 Code

$1 0 1 1 0 0 0 = B\emptyset H$

This timer is used to load 60° to trigger CM group SCRs.

TM<sub>1</sub> (extra timer card) (59H) can be initialised in Mode O as follows :

> TM<sub>1</sub> R/L Mode 0 Code 0 1 1 1 0 0 0 0 = 70H

This timer will create an  $IR_0$  interrupt, which is the first interrupt in the system due to L-L-zero crossing of a.c. supply. This timer is loaded with the  $\propto$  count of the CS converter (rectifier).

$TM_2$  (extra card) (5AH) is initialised in Mode 1 (programmable one-shot) :

| TM <sub>2</sub> | R/L | Mode | Code | !      |

|-----------------|-----|------|------|--------|

| 10              | 1 1 | 001, | 0    | = 82H. |

This timer will creat  $IR_1$  interrupt and timer is loaded by 60° to trigger CS converter group thyristors.

After initialization of all the necessary chips, all firing bits are first made low. Some of the values for which the processing is done during the program execution are also to be initialised with suitable values namely initial frequency ( $f_{start}$ ), m-pointer, small incremental frequency ( $\Delta f$ ), firing sequence index of both converter and inverter, (FS and FM index), Inverter group change index (CMG), first time start, cycle limit,  $\Delta$  cycle limit, mode index, value of the firing angle 60° etc. Meaning of these terms is explained later in detailed flow charts. The PIC is next initialised for the vector address of the interrupts  $IR_0$ ,  $IR_1$  and  $IR_2$ . All interrupts are edge triggered.

After initialization process is over, interrupts are enabled and the processor comes to HALT state. Here it waits for first interrupt,  $IR_o$  to occur. After the HALT (after returning from  $IR_o$ ) it compares the real time measured in number of power frequency periods termed here as 'cycle' with a certain maximum value called 'cycle limit'. If 'cycle' is less than the 'cycle limit' program goes back to HALT state and waits. If it is greater, it will set real time 'cycle' = 0 0 and mode index = 1 (i.e. asynchronous starting). The upper limit of the speed a 'speed limit' in asynchronous mode is called crawling speed and is initialised to about 2Hz synchronous speed value. The reference speed is then read via ADC. The programme now calls the frequency adjustment and actual speed measurement sub-routine which includes displaying the actual inverter frequency under starting

(transients) conditions or reference frequency under steady state and the actual motor speed. Both actual (or reference) frequency and the actual speed are displayed in the data field and address field respectively. If the actual speed is less than the speed limit then programme will directly compare the actual frequency. if both are not equal then again it jumps to frequency adjustment and speed measurement subroutine. If the actual speed is more than the speed limit, then it will check the mode index. If mode index earlier was one, it set mode index as 2 with new speed limit set equal to self commutation speed. In mode 2, the motor is running synchronously but its speed is less than the required speed for self commutation of inverter SCRs.

If the mode is already two then it set mode index as three (LCI mode). Again actual frequency is compared with the reference frequency. Thus, whatever be the set value of frequency through the reference pot, the program keeps on increasing drive frequency till both are equal. If once both are equal then the new reference frequency, is re-read and the program adjusts the actual frequency to the new reference value.

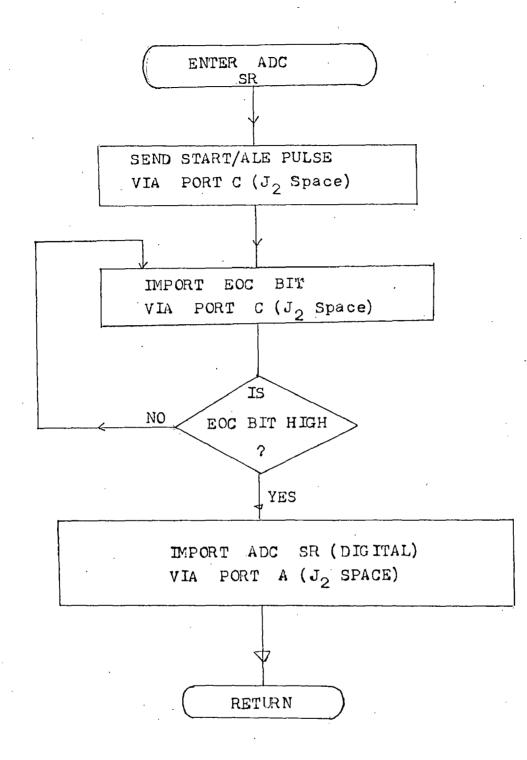

#### 3.4 ADC SUBROUTINE

Actual speed and reference frequency are measured and stored in memory through this subroutine. The reference frequency is set to a value from the pot and fed to ADC via the input channel  $I_{NO}$ . The actual speed signal is fed via channel  $I_{N1}$  of the ADC. The ADC converts analog voltage into a digital count. The reference

frequency measurement is done once in every looping of the main programme. The ADC clock-in is given from a 555 timer of 100 KHz frequency. ADC starts converting the analog input signal into digital value at the instant, when the start of conversion (SOC) bit of ADC goes from LOW to HIGH to LOW. ADC sends a signal to I/O port through END OF CONVERSION (EOC) bit going high, indicating that the conversion process is over. The digital value is read and stored. The channel selection is always done in the calling programme. The flow diagram is shown in Fig. 3.4

NAME OF SUBROUTINE

#### INPUTS

OUTPUTS

CALLS

NOTE

Destroys

Description

Input to ADC through I<sub>NO</sub>/I<sub>N1</sub> channel Reference frequency or actual speed

None

in Hex in reg A.

ADC SR

A11

This subroutine measures the reference frequency via  $I_{NO}$  channel and actual speed via  $IN_1$  channel. The channel selection is done in the calling program.

ADC clock-in of 100 KHz is given from 555 timer.

(2) Scale factor are:

Hz : 04H for reference frequency;

8 RPM=01H for actual speed.

## Fig. 3.4 : FLOW CHART FOR ADC SR.

.

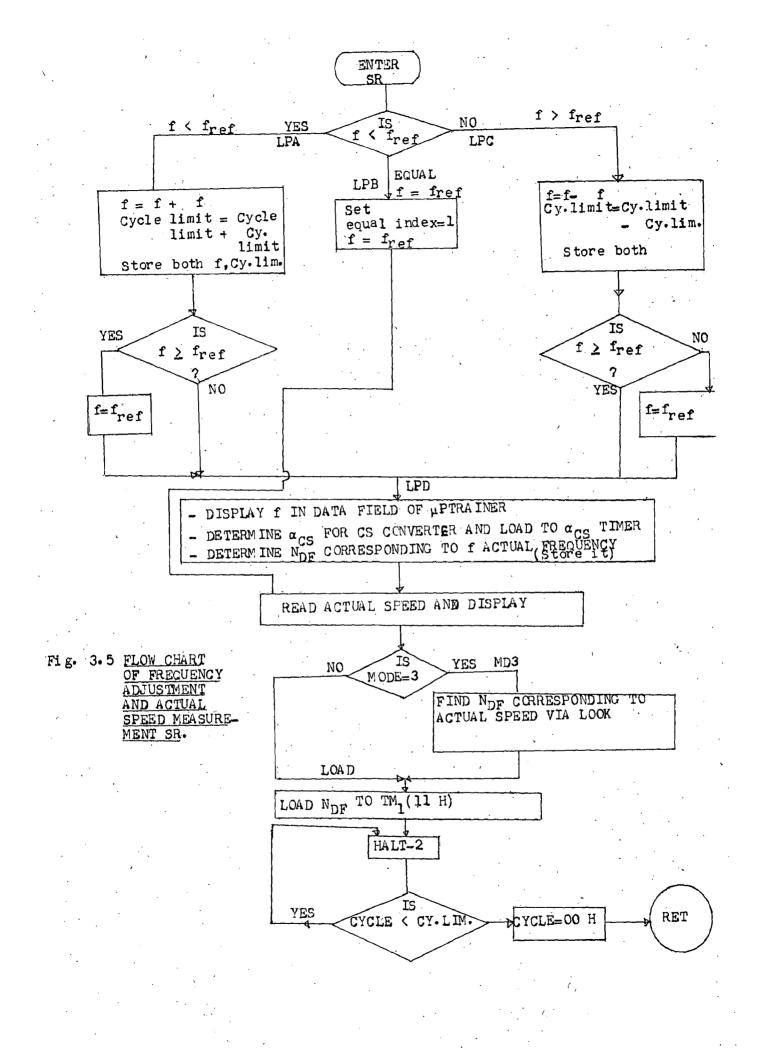

#### 3.5 FREQUENCY ADJUSTMENT AND ACTUAL SPEED MEASUREMENT SUBROUTINE

This subroutine mainly adjusts the actual inverter frequency to the reference frequency. It also measures the actual speed and display the actual speed, and actual frequency under non-LCI modes (or ref. freq. under LCI mode) in the address field and data field respectively. The flow chart is shown in the Fig. 3 [5].

The reference frequency is earlier measured before calling this subroutine; it is compared with actual frequency. If the actual \_frequency is less than reference frequency then the actual frequency is incremented by a small value  $\Delta f$  and then again compared with reference frequency to check whether actual frequency has become greater stored than reference frequency. If it is less, it is / in actual frequency address. If it is greater than reference frequency, then it is limited to the reference frequency value and stored at the actual frequency address. Now the program jumps to read actual speed (by calling the ADC S.R.) and displays the actual speed.

If the actual frequency when compared to reference frequency is found more, then the actual frequency is decremented by a small incremental value  $\Delta f$ . Now this new actual frequency is once again compared with the reference frequency to check whether the actual frequency has gone less than reference frequency. If the actual frequency has become less than reference frequency, then the actual frequency is limited to reference frequency and stored. This logic is to prevent the oscillations in a actual frequency about the reference frequency.

After correcting the actual frequency towards the reference value, the firing angle  $\propto$  CS of the rectifier is determined via a

.

Look-up table to maintain V/f ratio constant under starting conditions. Further the division factor  $N_{DF}$  is also determined via Look up table;  $^{N}D_{F}$  acts as loading to the variable frequency timer where frequency is always maintained proportional to the actual frequency of motor.

After the above frequency adjustment is over, program reads the actual speed and displays both. If drive is in mode 3 (LCI mode) then it will determine the  $N_{DF}$  factor from actual motor speed via the Look up table and load it to the timer for variable frequency generator. Program now comes to HALT state. Here it compares real time 'cycle' with cycle limit. If cycle is less than cycle limit, again it will go to HALT state or else it sets cycle = 0 0 and returns.

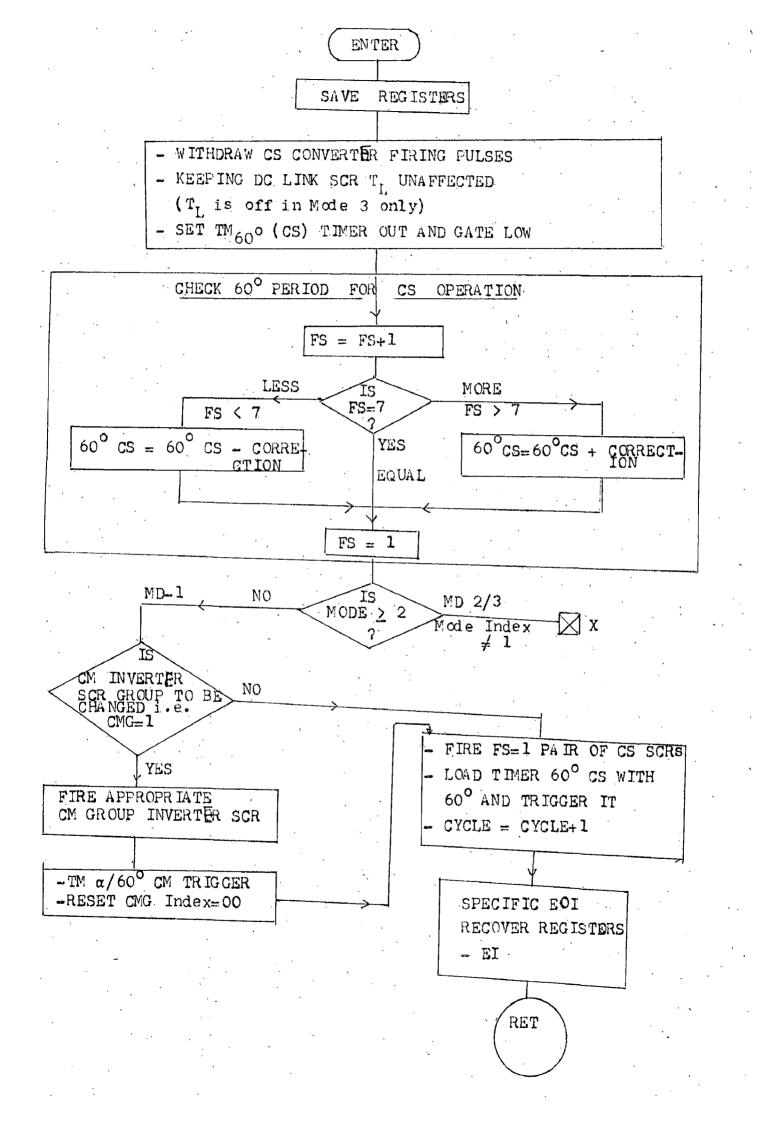

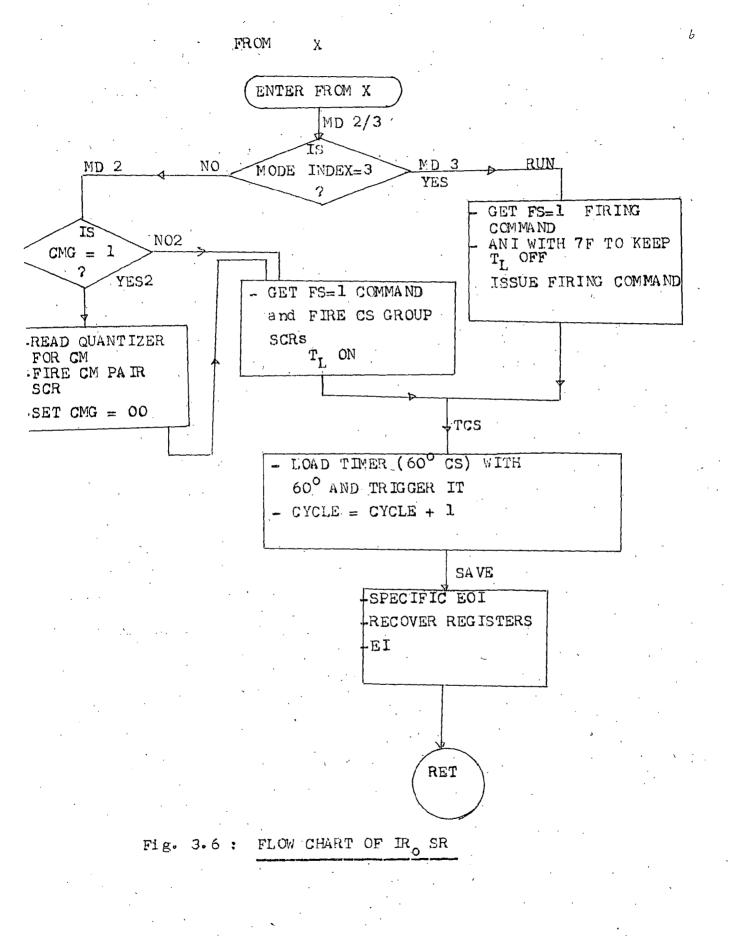

## 3.6 IR ( $\propto$ CS) INTERRUPT ROUTINE

This is the first interrupt occuring in the control scheme. The flow chart is shown in Fig. 3.6. This interrupt subroutine starts with saving the registers. The interrupt is used to serve the first firing command to the CS converter after  $\triangleleft$  angle from the zero-crossing of RY line voltage of ac power source. It withdraws first all the firing pulses and sets the GATE and 'OUT' of timer TM<sub>1</sub> (59 H in mode 0) low. The 60° count for rectifier (CS) operation is corrected. The firing commands are already stored in sequential memory locations and picked up properly with the help of firing index FS. Firing index points to the address of the firing command to be next executed. Once the proper firing command is picked up, the microprocessor outputs the firing command through six bits of port B (8255-1).

In this SR, FS is set = 1 (to the SCR pair 4 & 5 of CS), the program checks up the mode index. If mode index is one, it will

.

.

•

set the inverter group change index = 1 and fire the appropriate CM group SCRs. The timer  $TM_2$  (12H) is loaded with 60° (CM) value and triggered. The program jump to issue a firing command to CS converter (rectifier) and loads the timer  $TM_1$  ( 59H ) with 60° and triggers it. Afterwards 'cycle' (i.e. the real time index) is incremented and stored. The end of the interrupt command is issued and the program returns after recovering the registers.

If Mode index is either 2 or 3 then it checks the mode index whether it is three or not. If it is three, then it issues the firing command (FS = 1) to CS group thyristors. In mode 2, it asks if the CMG index is one (i.e., if new pair of CM group thyristers are to be fired). If CMG index = 1, the three quantizers from synchronous machine terminal voltages are read and appropriate CM Group SCRs are fired. The CMG index is now set as CMG = 0 0. Then program jumps to issue the firing command for CS group. If the CMG index earlier was zero, CM group thyrister pair firing is not changed. Now 60° is loaded to the timer  $TM_2$  (5AH) program returns after, incrementing the 'cycle', recovering the registers and issuing the end of interrupt command.

NAME OF SR

INPUTS

IR ISS

power frequency zero crossing signals from R to Y line voltage is inputted through gate of  $TM_2$  (5 AH) and quantizer signals are also inputted to port A of 8255-2, for reading the quantizer value.

The 60° CS timer is loaded and triggered to generate the interrupt signal IR<sub>1</sub> at

OUTPUTS

every 60° for CS operation. FS=1 firing command for CS converter is issued. If required, CM inverter new SCR pair is also triggered and action is taken to set next 60° (CM) instants.

None

PSW, B, C, H, L

This subroutine issues the firing command to SCR pair 4 and 5 of CS converter after  $\propto^{\circ}$  from the zero crossing of R-Y / voltage of 50 Hz power supply. It loads the timer TM<sub>1</sub> (59H) with 60° for next firing instants. If required, it also fires appropriate SCR pair of CM inverter and loads TM<sub>2</sub> ( timer ) (  $\propto/60^{\circ}$  CM timer) to identify next instants for firing CM group SCRs.

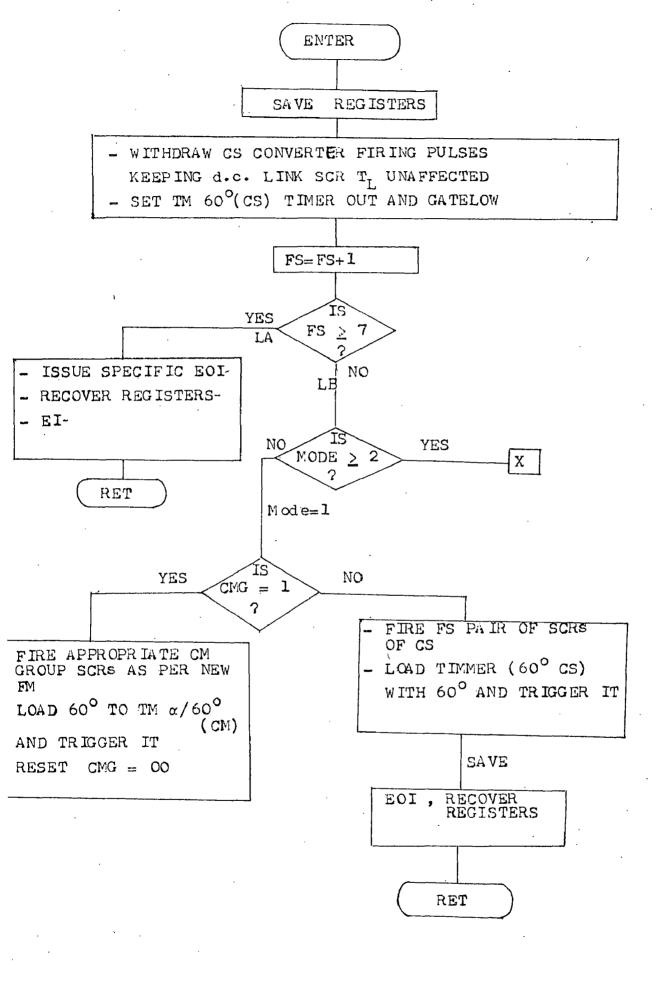

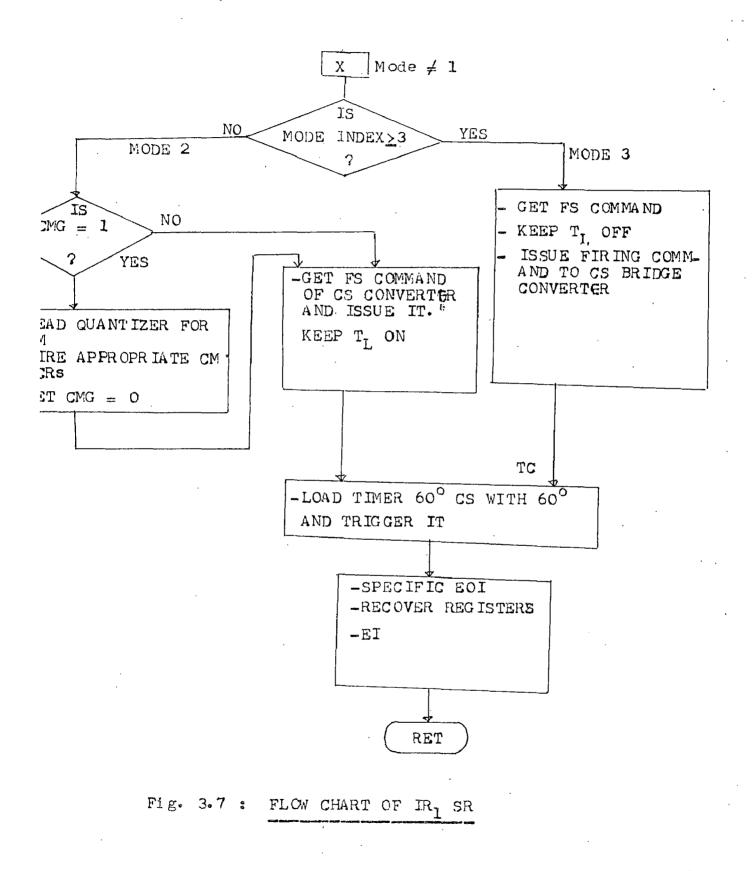

3.7 IR<sub>1</sub> (60° CS) INTERRUPT SUBROUTINE

CALLS

Destroys

Description

The flow chart of this interrupt subroutine is shown in Fig. 3.7. This interrupt SR is used to fire a new pair thyristors of CS converter at every  $60^{\circ}$  after the IR<sub>0</sub> interrupts. The program is entered by saving the registers. It first withdraws all the firing pulses to thyristors of CS converter (rectifier). Here the firing commands are always stored in sequential memory locations. After incrementing the old firing index FS, check is first made if it is an invalid command (FS > 7). In case of valid FS commands (FS < 7)

. .

the mode is next determined. If mode is 1, the CMG index is checked. If CMG is one then the appropriate CM group SCRs are fired, and the timer  $TM_2$  (12H) is loaded with 60° (CM) and triggered. The CMG Is reset as CMG = 0 0. If CMG is not one then it will issue the command to fire CS group SCRs only. The timer  $TM_1$  (59H) is reloaded with 60° and triggered to generate next  $IR_1$  interrupts.

If mode index is 2 or 3 , then the program jumps ahead to determine the mode index. If mode is two, it checks if CMG = 1. If CMG = 1 it reads the quantizers and fire the appropriate CM group thyristors. The CMG is reset as CMG = 0 0 and the firing command is issued to fire the CS converter group as per FS index. The timer  $TM_1$ (59 H) with 60° and triggered. If the mode index is already three, then it will issue the firing command to fire only CS group thyristors as per FS index. After issuing the EOI instruction and recovering the registers the program returns.

NAME OF SR

INPUTS

OUTPUTS

# IR<sub>1</sub>(60° CS) ISS