# OPTIMAL COMPONENT PLACEMENT ON PRINTED CIRCUIT BOARDS

### A DISSERTATION

submitted in partial fulfilment of the requirements for the award of the degree of MASTER OF ENGINEERING

in

ELECTRICAL ENGINEERING (System Engineering and Operations Research)

By

MANOJ JAIN

DEPARTMENT OF ELECTRICAL ENGINEERING UNIVERSITY OF ROORKEE ROORKEE-247667 (INDIA)

January, 1988

### CERTIFICATE

Certified that the dissertation entitled 'OPTIMAL COMPONENT PLACEMENT ON PRINTED CIRCUIT BOARDS' being submitted by Shri Manoj Jain in partial fulfilment of the requirements for the award of the degree of MASTER OF ENGI-NEERING in ELECTRICAL ENGINEERING with specialization in SYSTEM ENGINEERING AND OPERATIONS RESEARCH of the University of Roorkee, Roorkee [India], is an authentic record of his own work carried out by him under our supervision and guidance. The matter embodied in this dissertation has not been submitted for award of any other Degree or Diploma.

This is to further certify that he has worked for a period of about six months from August 1987 to January 1988 for preparing this dissertation.

[ Dr. H.O.GUPTA ] Reader Electrical Engineering Department University of Roorkee, Roorkee-247 667, India

[ Dr. A.K.PANT ] Professor Electrical Engineering Deptt. University of Roorkee, Roorkee-247 667, India.

Dated : 1, 2, 88.

### ABSTRACT

The circuit layout problem is an important facet of physical design of electrical circuits as the cost, performance, maintenance and reliability of any electronic circuit also depend on the placement of circuit components on the printed circuit board. The partitioning and layout of printed circuit boards is a very important phase in making a good physical design of an electronic system.

In this dissertation methods have been developed to obtain optimal component placement on double and multilayer printed circuit boards. The component placement is obtained such that the design avoids the congested area, excess crossovers or holes, long etches, strong capacitance, temperature rise of components due to thermal coupling and improves the reliability of the circuit. An efficient iterative algorithm based on sensitivity analysis is presented to achieve optimal placement of circuit components (similar or dissimilar in size). A technique for obtaining a good initial placement of components is also developed. The formulation of via assignment problem for multilayer printed circuit board has been dealt with and a refined heuristic algorithm is developed for its solution.

### ACKNOWLEDGEMENTS

I am deeply grateful and indebted to my guides Dr. A.K. Pant, Professor and Dr. H.O.Gupta, Reader in Electrical Engineering Department, University of Roorkee for their expert guidance. The stimulating and thought provoking discussions with them at every stage has facilitated the timely submission of this dissertation.

The continuous support and encouragement of Dr. J.D. Sharma and Shri M.K.Vasantha contributed in a very important way towards the completion of this dissertation. No words are sufficient to acknowledge their help.

I am thankful to the Head, Electrical Engineering Department, University of Roorkee for providing the necessary facilities.

Thanks are due to my friends Mr. C.B.Raje and Mr. V.Sharma for their help and cooperation at various stages of this work.

Thanks are also due to the Roorkee University Regional Computer Centre staff for their cooperation. Last but not least I thank Shri D.C.Bhardwaj for having accurately and neatly typed this dissertation.

MANOJ JAIN

ROORKEE January 30th, 1988 TABLE OF CONTENTS

| CHAP | TER                                                          | PAGE        |

|------|--------------------------------------------------------------|-------------|

|      | Abstract                                                     |             |

|      | Acknowledgements                                             |             |

|      | Table of Contents                                            |             |

|      | List of Symbols                                              |             |

| 1.   | Introduction                                                 |             |

|      | l.l Overview                                                 | 1           |

|      | 1.2 Printed Circuit Board Design                             | 2           |

|      | 1.3 The Author's Contribution                                | 6           |

|      | 1.4 Organization of the Dissertation                         | 7           |

| 2.   | Component Placement on Double Layer<br>Printed Circuit Board |             |

|      | 2.1 Introduction                                             | 8           |

|      | 2.2 The Placement Problem                                    | 10          |

|      | 2.3 Assumptions                                              | 11          |

|      | 2.4 Approach to the Placement Problem                        | 11          |

|      | 2.4.1 Initial Placement                                      | 12          |

|      | 2.4.2 Iterative Placement Improvement                        | 20          |

|      | 2.4.2.1 Same Sized Components                                | 20          |

|      | 2.4.2.2 Components of Different                              |             |

|      | Sizes                                                        | 31          |

| 3.   | Multilayer Printed Circuit Board                             |             |

|      | 3.1 Introduction                                             | 40          |

|      | 3.2 Component Placement on MPC Board                         | 42          |

|      | 3.3 The Via Assignment Problem                               | 44          |

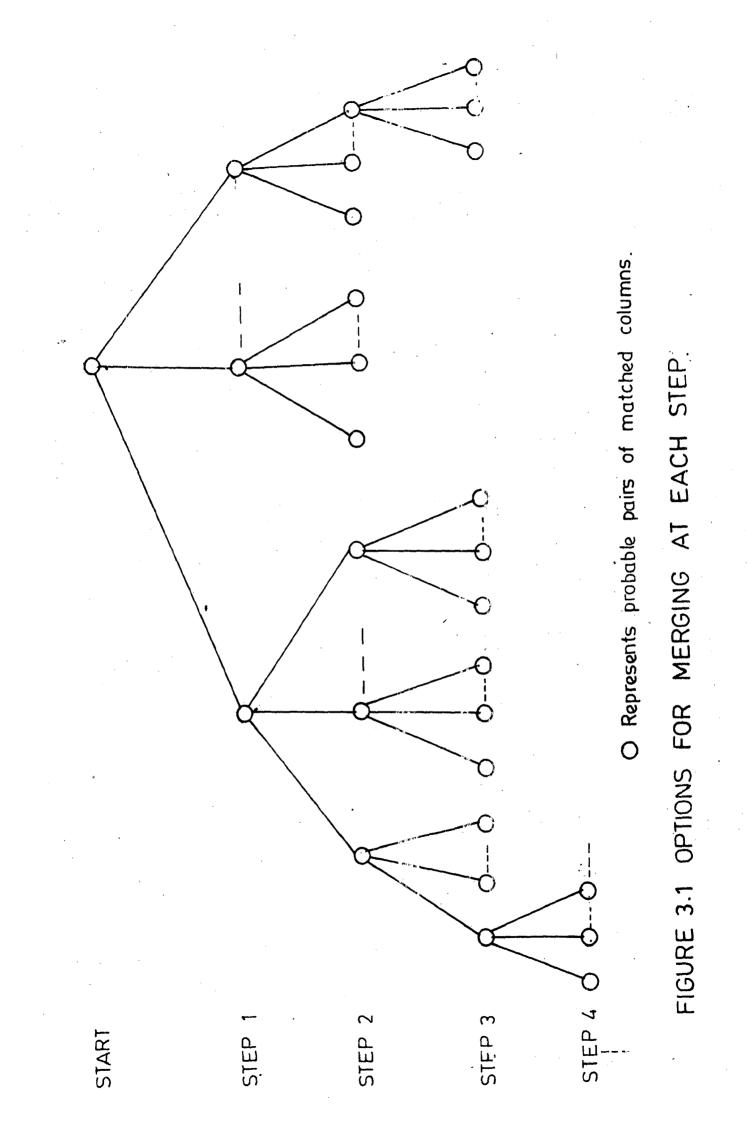

|      | 3.3.1 Column Merging                                         | . 46        |

|      | 3.3.2 Column Decomposition                                   | 47          |

|      | 3.4 Heuristic Algorithm                                      | <b>49</b> - |

|      | 3.4.1 Outline of the Algorithm                               | 50          |

|      | · · · ·                                                      |             |

contd...

## CHAPTER

PAGE

| 4. | Conclusions and Suggestions         |    |

|----|-------------------------------------|----|

|    | 4.1 Conclusions                     | 57 |

|    | 4.2 Suggestions for Future Research | 59 |

APPENDIX - A

APPENDIX - B

REFERENCES

### LIST OF SYMBOLS

| A                | initial via column matrix defined as                                                                                                                                    |  |  |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| . 1              | l, if net N <sub>j</sub> contains a pin in row i<br><sup>a</sup> ij = { 0, otherwise                                                                                    |  |  |  |  |  |  |  |  |

| Ao               | final via column matrix                                                                                                                                                 |  |  |  |  |  |  |  |  |

| a                | number of horizontal divisions on the board                                                                                                                             |  |  |  |  |  |  |  |  |

| b                | number of vertical divisions on the board                                                                                                                               |  |  |  |  |  |  |  |  |

| с                | connection matrix of order NXN defined as                                                                                                                               |  |  |  |  |  |  |  |  |

|                  | $c_{ij} = \begin{cases} \lambda, \text{ if components } E_i \text{ and } E_j \text{ are} \\ c_{onnected by } \lambda \text{ wires} \\ 0, \text{ otherwise} \end{cases}$ |  |  |  |  |  |  |  |  |

| Cp               | vector to indicate whether a component is placed on<br>the board such that                                                                                              |  |  |  |  |  |  |  |  |

|                  | $c_{p_i} = \{ 0, \text{ otherwise} \}$                                                                                                                                  |  |  |  |  |  |  |  |  |

| Ei               | component i, i=1,2,,N                                                                                                                                                   |  |  |  |  |  |  |  |  |

| E <sub>N+1</sub> | fictitious component placed in empty cell                                                                                                                               |  |  |  |  |  |  |  |  |

| `                | i=1,2,,ab-N                                                                                                                                                             |  |  |  |  |  |  |  |  |

| ea               | activation energy                                                                                                                                                       |  |  |  |  |  |  |  |  |

| F                | objective function to be minimized for placement                                                                                                                        |  |  |  |  |  |  |  |  |

| Fh               | number of holes                                                                                                                                                         |  |  |  |  |  |  |  |  |

| Fl               | wiring function related to the length of etches                                                                                                                         |  |  |  |  |  |  |  |  |

| Fd               | wiring function related to the interconnection                                                                                                                          |  |  |  |  |  |  |  |  |

|                  | densities, in horizontal and vertical sections of the                                                                                                                   |  |  |  |  |  |  |  |  |

|                  | board                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| Fc               | wiring function related to the stray capacitance                                                                                                                        |  |  |  |  |  |  |  |  |

| Fr               | objective function related to the temperature rise of                                                                                                                   |  |  |  |  |  |  |  |  |

| •                | components due to thermal coupling between them                                                                                                                         |  |  |  |  |  |  |  |  |

$\Delta F_i(s,t)$  increment in function  $F_i$  due to interchange of components  $E_s$  and  $E_t$  in the placement matrix P [G.H] matrix obtained from connection matrix C and

placement matrix P, such that

$$g_{ij} = \sum_{k=1}^{b} c_{i,p_{jk}} \qquad i=1,2,...,N \\ j=1,2,...,N \\ j=1,2,...,N \\ i=1,2,...,N \\ j=1,2,...,N \\ j=1,2,...,D$$

K Boltzmann's constant

L net matrix defined as

$\lambda_{i,j} = \begin{cases} N_k, & \text{if jth pin of component number } i/2 \\ & (\text{or } (i+1)/2) \text{ of the lower (or upper)} \\ & \text{pin row is connected to the net } N_k \end{cases}$

0, otherwise

matrix of the order NTXNT defined as

hb

ka

Ν

Ρ

length of the cell i.e.  $k_{\rm b/b}$

length of printed circuit board

М

$m_{ij}$  = distance between components  $E_i$  and  $E_j$ number of components to be placed

$N_{j}$  net,  $j=1,2,\ldots,NN$

NN total number of nets in the circuit

NP number of pins in each row of a component

NR total number of pin rows equal to (2 X a )

NT total number of slots on the board ( a X b)

placement matrix of order a X b and defined as

p<sub>ij=k</sub>, if component E<sub>k</sub> is placed in

position (i,j)

- Q set of components excluding fictitious components placed in rows 1,2,...,i

- R<sub>i</sub> thermal resistance of component E<sub>i</sub> when circuit board is assumed to be perfect insulator

- R<sub>ie</sub> thermal resistance of component E<sub>i</sub> when heat transfer in circuit board is taken into account

- $R_{ij}$  coupling thermal resistance between component  $E_i$ and  $E_j$

- S<sub>i</sub> set of components excluding fictitious components placed in columns 1,2,...,a

T absolute ambient temperature in K.

$T_i$  absolute junction temperature of component  $E_i$  in K $W_i$  power dissipation of component  $E_i$

- interconnection leads passing through ith horizontal section of the board

- interconnection leads passing through ith vertical section of the board

- <sup>w</sup>h<sub>i</sub>

w<sub>v</sub>i

W<sub>h</sub>i

$w_{\mathbf{v}_{\mathbf{i}}}$

interconnection density in ith horizontal section of the board i.e.  $Wh_{1/b}$

interconnection density in ith vertical section of the board i.e.  $W_{v_{e}}/W_{b}$

wb width of the board

$w_c$  width of the cell i.e.  $w_b/a$

$\lambda(T)$  failure rate of a component at absolute junction temperature T

### CHAPTER - 1

#### INTRODUCTION

#### 1.1 Overview

In the design of present day large scale electronic systems, high density packaging is achieved by proper design and interconnection of its subsystems. The design involves placement of components and interconnections at three different levels. At the lowest level, logic elements are to be placed and routed on a semiconductor wafer. A printed circuit board is used at the second level with ICs and other components instead of logic elements. Set of PCBs form the backplane which is the third level of the layout problem.

Printed circuit boards are certainly a very important ` element in the fabrication of electronic equipment. It is the design of properly laid out PCBs that determine many of the limiting properties with respect to noise immunity, fast pulse, high frequency and low level characteristics of the equipment. High power PCBs in their turn require a special design strategy. The design of PCB forms a distinct factor in electronic circuit performance and reliability. The producibility of a PCB and its assembly and serviceability also depend on the design. All these factors finally get reflected in the price for the 'electronic equipment, because PCBs constitute about 20 percent of the cost.

### 1.2 Printed Circuit Board Design

The magnitude and complexity of the PCB design problem is too large to solve en mass. Thus attempts are made to divide the problem into distinct phases which are individually handled. The circuit diagram of a particular electronic system is assumed to be available in the form of design diagrams. An independent physical component is considered as a module and each module has several pins which are to be connected electrically. Each such connection is said to form a Signal Net. A collection of such signal nets describing a complete layout is called a Net list. The individual components are given physical locations on the board surface, so that the electrical connections between them can be done. The positioning of the components can be done to optimize certain characteristics of the layout, such as total wire length, board area, total number of holes, expected congestion, time delay, maximum length of an etch, stray capacitance temperature rise due to thermal coupling etc. Goto and Kuh [4], Patnaik et.al. [10], Quinn and Breuer [11] and many authors use only total wire length as the optimization criterion for the placement of components. Gupta [5] has developed a refined iterative multicriteria optimization placement algorithm based on

1. criterion related to the length of etches,

2. minimization of interconnection wiring density,

3. minimization of stray capacitance,

-2-

- 4. minimization of the effect on the electrical performance and reliability of circuit due to thermal coupling between components.

- 5. minimization of total number of holes required for the realization of the circuit.

A placement problem is said to be solved if such an optimum physical positioning is achieved for all the components. Having assigned physical locations to electrical pins to be connected, the actual physical laying of conductor patterns is to be attempted. This problem is referred to as the routing problem. The interconnections must again be obtained satisfying certain physical constraints. For example the number of conductor patterns per unit area is limited by the available technology. Also, the number of tracks per unit area must be more or less same throughout the board. To provide the required interconnections between the circuit modules for assembling digital systems, multilayer printed wiring boards (PWB) are used very often. The design rules for these PWB's have been revolutionized with the recent advances in the micro electronics technology. In an ordinary dual in line package the number of etch paths between two consecutive pins is restricted. Kuh et.al [8] have derived necessary and sufficient conditions for minimum street congestion in single row routing. Tsukiyama et.al [16] have described an efficient routing algorithm for special cases of upper and lower street congestions upto two. The studies of single-row routing problems by Kuh et.al.[8]

-3-

and Tsukiyama et.al.[16] have been restricted to minimization of the total number of horizontal tracks needed for the realization of a given set of nets. Therefore it has been assumed that enough space exists between adjacent nodes to allow for the wiring. Due to this assumption, realizations obtained from these algorithms require a large number of vertical tracks between adjacent nodes. Du et.al [3] have discussed the single-row routing problem when the number of vertical tracks available between adjacent nodes is bounded by a positive integer called the cross-over bound.

The connections between the different layers in a multilayer wiring board is achieved by plated through holes. also called Vias. Ting et.al. [14] have suggested that a multilayer problem can be reduced to several single line single layer problems by the proper usage of vias. They have also discussed the via assignment problem with the objective of minimizing via columns. Some algorithms for its solution are also proposed. Tsukiyama et.al.[15] have formulated an optimization problem for finding the via assignment. A heuristic algorithm to this optimization problem is also proposed by them. The essence of the via assignment phase is to establish the fact, that the interconnections are feasible. This is accomplished by assigning appropriate vias in order to determine connection patterns of all the nets. A principal objective in this phase is to minimize the number of via columns, thus reducing the size of the board or alternatively increasing the routing area. A set of pins which belong to

the same net and which are located on the same row is called a Generalized pin. Thus individual pins which belong to a generalized pin of a net can be connected without use of vias. The connections for the generalized pins are made first, for the remaining interconnections vias must be used. The manner in which vias are selected is important. After the connection patterns are obtained, the problem of routing is reduced to much simpler problems with routing specifications on a single line basis.

After the preliminary realization one has the choice of perturbing the realization as long as the connection patterns are not disturbed. Because of the fixed placement, the pin locations can not be altered. However the via columns are less rigidly located. Patnaik et.al.[10] have stated the problem as finding the optimum placement of via columns for a given via assignment of a unidirectional routing so that the maximum number of horizontal tracks is minimized. Several available stratagies for permuting via columns are also suggested by Patnaik et.al.[10].

After via assignment and linear placement of via columns is carried out, the routing problem reduces to the much simpler problem of single line routing. At this stage the track availability must be considered. The objective of layering is to allow more layers for the purpose of evenly distributing the number of connecting wires on different layers. Chang and Du [2] and Han and Saini [6] have discussed some algorithms for the layering problem that arises when the single row routing approach of wire layout is used.

-5-

### 1.3 The Author's Contributions

The goals of this dissertation were to develop more realistic mathematical models and efficient methods for performance optimization of physical design of electronic circuits at various stages of the design process.

The algorithm proposed by Gupta [5] does not include any method for constructive initial placement. The initial placements has to be decided arbitrarily and then the algorithm iteratively optimizes the placement. For different initial placement different local optimal solutions may be obtained. The algorithm also does not incorporate the edge connector which is an important part of a printed circuit board. One of the assumptions made for the algorithm proposed by Gupta [5] is that all the components are similar, and dimensions of the components are such that all components require same area for their placement. This assumption poses severe limitations on the design. In this dissertation all these draw backs have been taken into account and the algorithm proposed by Gupta [5] is modified.

The important problem of multilayer PCB design has also been taken up for this dissertation. The heuristic algorithm for via assignment problem proposed by Tsukiyama et.al [15] assumes that the placement of pins is fixed. It finds the optimal assignment of via columns by repeated application of the process of column merging and column decomposition. This

-6-

algorithm has been modified to find the best placement of pins (or components). The best placement is achieved by the iterative algorithm using sensitivity analysis for which expressions have been derived with a view to reduce the computational effort. The algorithm proposed by Tsukiyama et.al [15] is modified such that an iteration is performed with a view to achieve best results in two consecutive iterations.

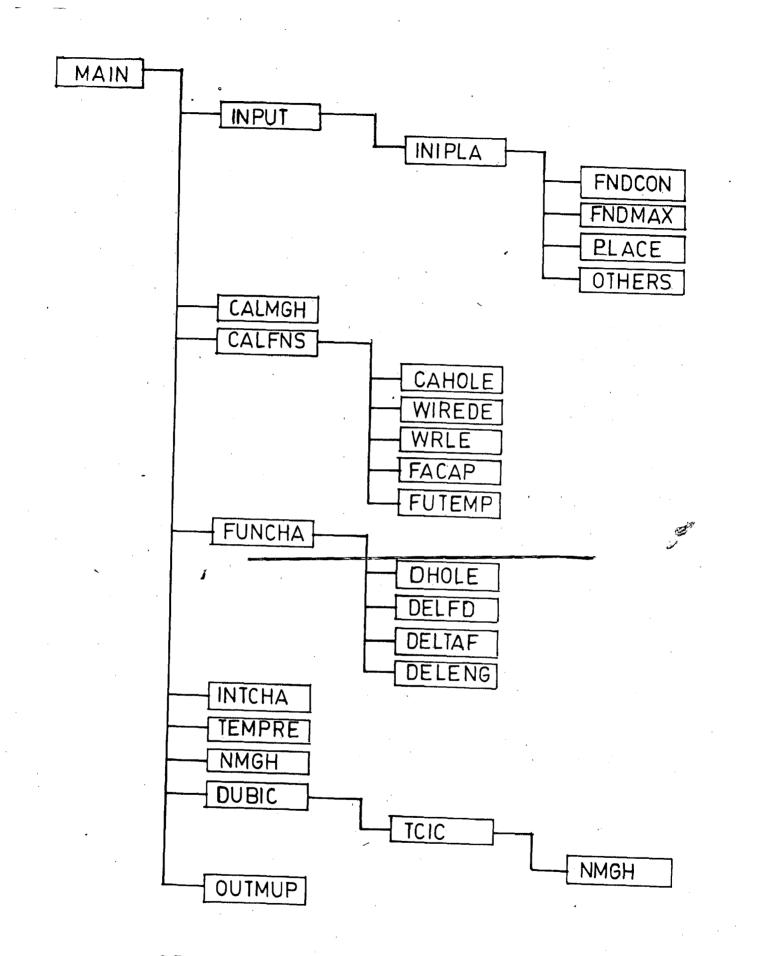

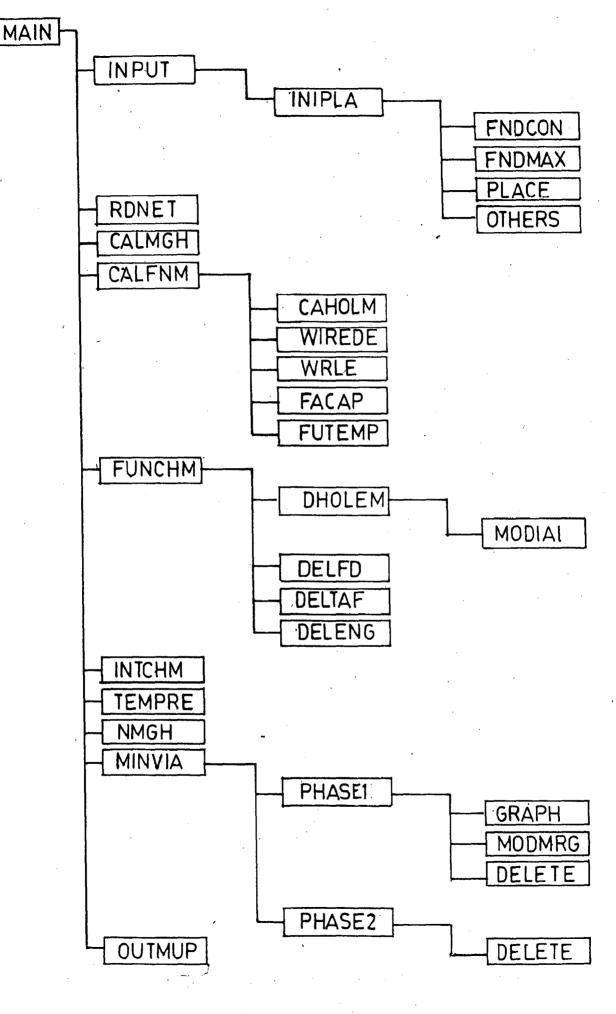

### 1.4 Organization of the dissertation

The problem of component placement on double layer printed circuit board has been dealt with in Chapter 2. Chapter 3 describes the problems associated with multilayer printed circuit boards. Finally Chapter 4 offers general conclusions and suggestions for further research work in this field. Computer programs in FORTRAN-IV have been developed on DEC-2050 which are briefly described in the Appendices.

-7-

#### CHAPTER - 2

### COMPONENT PLACEMENT ON DOUBLE LAYER PRINTED CIRCUIT BOARD

### 2.1 Introduction

The layout design of electronic circuits on printed circuit board is one of the most important and time consuming phases during equipment design process in all electronic industries. The problem of layout design is being made more and more complicated day by day with the advances in the. electronics technology. The functional capabilities, speed, frequency and accuracy of electronic circuits have been increasing exponentially.On the other hand, with the increase in all these the electronic components are being miniaturized and made more complex.

Allocation, placement and Routing are the three phases into which laying out of electronic circuits has been divided [5]. The partitioning of circuit components into groups and assignment of these groups to boards or modules is called allocation. To facilitate the routing, the circuit components are assigned to specific locations on the board, this is termed as placement. Routing is the process of laying out of etches on the board to make the interconnections between the individual circuit components. The interrelated problems of allocation, placement and routing are usually solved independently to ease the complex problem of laying out of electronic circuit.

The cost, performance, reliability and maintenance of any electronic circuit depend upon the placement of circuit components on the printed circuit board. The factors which directly effect the performance of electronic circuits are the interconnection length in high speed circuits, mutual interference and the thermal coupling between components.

-9.

The components are to be uniquely placed in an available location on the board. This placement is done in view of some objective function which is to be minimized. The total weighted routing length has been used by many authors [1.4.10.11] as a norm for minimization. The layout of the circuit having large number of holes, has poor reliability and high cost [5]. Therefore minimization of holes criterion is also used for placement of components. Interconnection density or the number of etches passing through a unit space is another factor which effect performance of the circuit. The placement based on this criteria avoids the congested area on the board, provides more space between etches which reduces stray capacitance. The stray capacitance and temperature rise due to thermal coupling between components should be minimum for better performance of a circuit. So placement of components should be achieved by using a combination of the following criteria [5].

- 1. Minimization of length of etches

- 2. Interconnection density minimization

- 3. Stray capacitance minimization

- 4. Minimization of the effect of thermal coupling between components on the electrical performance and reliability of the circuit.

- 5. Minimization of the number of holes.

In this chapter the iterative algorithm proposed by Gupta [5] based on the above criteria is discussed. The algorithm is extended for the placement of components which are not similar in size. A technique for a good initial placement of components is also developed.

### 2.2 The Placement Problem

The individual components are placed at appropriate locations on the board, such that the interconnection can be done easily. The locations assigned to the components on the board are called 'SLOTS. The components contain pins for connection by physical wires to form SIGNAL SETS. A signal set is a set of pins which must be interconnected to have the same potential. On the basis of a given interconnection the signal sets must be interconnected to form NETS. For the purpose of the placement problem, the pin locations on the components are ignored, and therefore, the signal set becomes a subset of the components. Since a component contains a number of connection pins, it may belong to more than one signal set. The complete interconnection is said to be specified, if all the signal sets have been specified.

So, given a set of components with signal sets defined on subsets of these components, and a set of slots, finding the optimal placement of all modules on the slots, with respect to some norm defined on the interconnections, is the definition of the placement problem.

-10-

### 2.3 Assumptions

- 1. The printed circuit board is rectangular and divided into aXb cells of equal size with coordinates (i,j), [i=1,2,...,a,j=1,2,...,b].

- 2. (NT-N) fictitious components with zero dissipation and no connection with any other component are also placed on the board. These components are not interchangeable with each other.

- 3. The input and output terminals appear on a specified edge (vertical) of the board. The position of required terminals on the edge is also determined iteratively with the placement of other components. The edge connector is divided in 'a' parts and each part is treated as a component. First 'a' components  $E_1$ ,  $E_2$ ,..., $E_a$  correspond to the parts of the edge connector.

- 4. The components are of two sizes. Dimension of the first type of components is such that each component require one and only one slot for its placement. The other type of component is double in size, that is they require two adjacent slots for their placement. The double sized components are treated as two different components with very high connectivity between them.

### 2.4 Approach to the placement problem

Following steps are followed for solving a complex placement problem.

### 2.4.1 Initial Placement

The constructive initial placement methods selects components, one at a time based on an evaluation function which measures signal set connectivity to components already selected and then decides which slot the components belong to. More specifically, a module is selected from the remaining components which has the maximum number of the interconnections with the components which are already selected. Next we assign the component to be a member of a row and a column. The first 'a' components corresponding to the edge connector are placed before placing the other components. Dummy components are assigned to the vacant slots after placement of all the components.

The steps of constructive algorithm to determine the initial placement configuration are as follows.

- 1. Find the initial placement of the first 'a' components corresponding to the edge connector by the following method.

- (i) Initialize the vector  $C_{p+0}$ .

- (ii) Find maximum connectivity between any two of first 'a' components

(iii) Place the corresponding components in the centre of the connector.

-12.

$$--13-$$

$$R = \{n/2, \text{ if a is even} \\ (n+1)/2, \text{ if a is odd} \\

PIR, b + k, F(IR+1), b - k \\ enter E_k and E_k in C_p \\ \circ_{P_K} - 1, \circ_{P_k} - 1 \\ \text{Set IK = 0} \\

(iv) \quad \text{If all of first 'a' components are placed} \\ i.e. \quad \circ_{P_1}|_{1=1,a} = 1 \\ \text{Stop} \\

(v) \quad \text{IK - IK+1} \\

(vi) \quad \text{Find} \\ \circ_{n,k} = \max_{i=1,a} [c_{1,k}] \\ \circ_{P_k} + 1 \\ P(IR-IK), b + n, k - n, \circ_{P_m} - 1 \\

(vii) \quad \text{If all of first 'a' components are placed} \\ i.e. \quad \circ_{P_1}|_{i=1,a} = 1 \\ \text{Stop} \\

(vii) \quad \text{If all of first 'a' components are placed} \\ i.e. \quad \circ_{P_1}|_{i=1,a} = 1 \\ \text{Stop} \\

(vii) \quad \text{If all of first 'a' components are placed} \\ i.e. \quad \circ_{P_1}|_{i=1,a} = 1 \\ \text{Stop} \\

(vii) \quad \text{If all of first 'a' components are placed} \\ i.e. \quad \circ_{P_1}|_{i=1,a} = 1 \\ \text{Stop} \\

(vii) \quad \text{If all of first 'a' components are placed} \\ i.e. \quad \circ_{P_1}|_{i=1,a} = 1 \\ \text{Stop} \\

(vii) \quad \text{Find} \\ \circ_{n,f} = \max_{i=1,a} [c_{1,f}] \\ i=1,a \\ \circ_{P_1} \neq i \\ P(IR+IK), b + n, f + n, \circ_{P_m} - 1 \\

(ix) \quad \text{Return to step (iv).} \\$$

`

Find the component which has maximum connectivity with the components already placed.

i.e. find k and k such that

3.

Place  $E_k$  in the slot nearest to the slot containing  $E_k$  by following the method given below

Initialize Ph and PV,  $ph_{i+0}$  and  $pv_{i+0}|_{i=1...max[a,v]}$ (i) (ii) Find m,n such that pm.n=K (iii) For all i=l to max [a,b] repeat steps (iv) to (xii) (iv)  $ph_1 \leftarrow m, ph_i \leftarrow m-q, ph_i (2q+1) q=1,i \leftarrow m+q$ (v)For all j =1 to (2i+1) repeat steps (vi) to (xii) (vi) p + ph (vii) If p < 1 or p > a, return to step (v) If p = (m-i) or p = (m+i), goto step (ix) If (n-i) <1 or  $p_{p_i(n-i)} \neq 0$ , goto step (viii)  $p_{p_{i}(n-i)} - k$ Stop. (viii)If (n+i) > b or  $p_{p,(n+i)} \neq 0$ , return to step (v) <sup>p</sup>p.(n-i) - k Stop

(x) For all 9 = 1 to (2i+1) repeat steps (xi) to (xii) (xi)  $q + Rv_0$ (xii) If q < 1, q > n or  $p_{p,q} \neq 0$ , return to step (x)  $p_{p,q} \div k$ stop

4. If

$$c_{p_{i|i=1,N}} = 1$$

, return to step 2.

5. Place dummy components in the remaining slots. For k = (N+1) to NT If p<sub>i,j</sub> = 0, i=1...a, j=1,...,t p<sub>ij</sub>+k

The constructive algorithm suggested above is a quick and straight forward method whose solution is not optimum but may be close to it. This methods gives good results for many applications. This placement confuguration is changed in iterative fashion to give better solutions.

Example 2.1 Consider that the board divided in 4 horizontal and 4 vertical divisions and there are six components to be placed with connection matrix as,

|     |   |   |   |   |   |   |   |   |   |    | t i |

|-----|---|---|---|---|---|---|---|---|---|----|-----|

|     | 0 | 3 | 4 | 2 | 4 | 0 | 0 | 3 | 2 | ·l |     |

|     | 3 | 0 | 0 | l | 0 | 2 | l | 0 | 0 | 4  |     |

|     | 4 | 0 | 0 | 2 | 3 | 0 | 9 | ĺ | 5 | 6  |     |

| С = | 2 | l | 2 | 0 | l | 7 | l | 4 | 0 | 0  |     |

|     | 4 | 0 | 3 | l | 0 | 4 | 8 | 0 | 0 | 3  | ļ   |

|     | 0 | 2 | 0 | 7 | 4 | 0 | 0 | 2 | 4 | 0  |     |

|     | 0 | l | 9 | l | 8 | 0 | 0 | 0 | 2 | l  |     |

|     | 3 | 0 | l | 4 | 0 | 2 | 0 | 0 | l | 2  |     |

|     | 2 | 0 | 5 | 0 | 0 | 4 | 2 | 1 | 0 | 9  |     |

|     | 1 | 4 | 6 | 0 | 3 | 0 | 1 | 2 | 9 | 0  | l   |

|     | ( |   |   |   |   |   |   |   |   |    |     |

$C_{ij}$  for i=1,4 and j=1,4 represent the components corresponding to the edge connector. So in effect there are 10 components to be placed out of which first 4 constitute the edge connector.

### Solution

$$P = \begin{bmatrix} 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 1 \\ 0 & 0 & 0 & 3 \\ 0 & 0 & 0 & 0 \end{bmatrix}$$

(v) IK - 1

(vi) <sup>c</sup> mk = <sup>c</sup>2, 1=<sup>3</sup>, <sup>p</sup>1, 4 - <sup>2</sup>, k - 2

C<sub>p</sub> = (1, 1, 1, 0, 0, 0, 0, 0, 0, 0)

P =

$$\begin{bmatrix} 0 & 0 & 0 & 2 \\ 0 & 0 & 1 \\ 0 & 0 & 3 \\ 0 & 0 & 0 \end{bmatrix}$$

(viii) <sup>c</sup>mf = <sup>9</sup>4, 3=<sup>2</sup>, <sup>p</sup>4, 4 - 4, f - 4

C<sub>p</sub> = (1, 1, 1, 1, 0, 0, 0, 0, 0, 0)

P =

$$\begin{bmatrix} 0 & 0 & 0 & 2 \\ 0 & 0 & 1 \\ 0 & 0 & 3 \\ 0 & 0 & 4 \end{bmatrix}$$

-16-

2.

$$c_{k,k} = c_{7,3} = P_9$$

,  $C_p = (1,1,1,1,0,0,1,0,0,0)$

3. (ii) m=3,

n=4

(iii) max [a,b] = 4, i=1

(iv) Ph<sub>1</sub>+3, Ph<sub>2</sub>+2, Ph<sub>3</sub>+4

(v) j = 1

(vi) p\_Ph\_1 = 3

(vii) P<sub>3,3</sub> = 7

P =  $\begin{bmatrix} 0 & 0 & 0 & 2 \\ 0 & 0 & 1 \\ 0 & 0 & 7 & 3 \\ 0 & 0 & 4 \end{bmatrix}$

2.  $c_{k/} = c_{5,7} = 8$ ,  $C_p = (1,1,1,1,1,0,1,0,0,0)$ 3. (ii) m = 3, n = 3(iii)  $i \leftarrow 1$ (iv)  $Ph_1 \leftarrow 3$ ,  $Ph_2 \leftarrow 2$ ,  $Ph_3 \leftarrow 4$ (v)  $j \leftarrow 1$ (vi)  $p \leftarrow Ph_1 = 3$ (vii)  $p_{3,2}, \leftarrow 5$

-17-

| •    |   |   | • | -18 | her |

|------|---|---|---|-----|-----|

|      |   |   |   | ~   | 1   |

|      | 0 | 0 | 0 | 2   |     |

| P -  | 0 | 0 | 0 | l   |     |

| * == | 0 | 5 | 7 | 3   |     |

|      | 0 | 0 | 0 | 4   |     |

2. 3.

2.

3.

$c_{k,\ell} = c_{6,4} = 7, \ C_{p} = (1,1,1,1,1,1,1,0,0,0)$ (ii) m = 4 n = 4 (iii) i + 1 (iv) Ph<sub>1</sub>+ 4, Ph<sub>2</sub>+ 3, Ph<sub>3</sub>+5 (v) j + 1 (vi) p + Ph<sub>1</sub> = 4 (vii) P<sub>4,3</sub>+6  $P = \begin{bmatrix} 0 & 0 & 2 \\ 0 & 0 & 1 \\ 0 & 5 & 7 & 3 \\ 0 & 0 & 6 & 4 \end{bmatrix}$   $c_{k,\ell} = c_{10,3}=6, \ C_{p} = (1,1,1,1,1,1,1,0,0,1)$ (ii) m=3, n=4 (iii) i + 1

- (iv)  $Ph_{1}-3$ ,  $Ph_{2}-2$ ,  $Ph_{3}-4$

- (v)  $p Ph_{1} = 3$

$$-19-$$

(v)  $d = 1$

(v1)  $p - Pb_1 = 3$

(v11)  $P_3, 3^{-7} \neq 0$

(v111)  $(n+1) = 5 > b$

(v)  $d = 2$

(v1)  $p - Pb_2 = 2$

(v11)  $p - Pb_2 = 2$

(v11)  $p - 2 = (n-1)$

(ix)  $Pv_1 + 4$ ,  $Pv_2 - 3$ ,  $Pv_3 + 5$

(x)  $0 - 1$

(x1)  $q - Pv_1 = 4$

(x11)  $P_{pq} = P_{2,4} = 1 \neq 0$

(x)  $0 - 2$

(x1)  $q - Pv_2 = 3$

(x11)  $P_{2,3} - 10$

$$P = \begin{bmatrix} 0 & 0 & 0 & 2 \\ 0 & 0 & 1 & 1 \\ 0 & 5 & 7 & 3 \\ 0 & 0 & 4 \end{bmatrix}$$

2.  $0 k_f = 2g_{1,0} = 9$ ,  $0 = p(-1, 1, 1, 1, 1, 1, 1, 0, 1, 1)$

3. (i1)  $n = 2$ ,  $n = 3$

(i11)  $i = 1$

(v)  $Pr_2 - 3$ ,  $Pr_3 = 5$

(v)  $d = 1$

(v1)  $P = Pr_1 = 2$

(v11)  $P_{2,2} = 9$

$$P = \begin{bmatrix} 0 & 0 & 0 & 2 \\ 0 & 0 & 10 & 1 \\ 0 & 5 & 7 & 3 \\ 0 & 0 & 4 \end{bmatrix}$$

2.4.2 <u>Iterative placement improvement</u> 2.4.2.1 <u>Same sized components</u>

For this phase it is assumed that dimension of the components are such that each component requires one and only one cell for its placement. In other words, the size of the components is practically the same. In this step, the placement configuration is changed in iterative fashion. A new placement configuration with a lower wiring function is obtained after each iteration.

-20-

Gupta [5] has derived expressions for calculating the wiring function F based on length of etches, interconnection density, stray capacitance, thermal coupling between components and number of holes. Expressions to determine an incremental set  $\Delta F = [\Delta F(s,t), s=1,2,...,$ N-1, t=(s+1), (s+2),...,NT] from sensitivity analysis are also derived. The strategy adaopted to change the placement configuration in the iteration is to calculate  $\Delta F$  until the first negative element is encountered and corresponding components are interchanged.

The expressions derived by Gupta [5] are stated below. The matrix [GH] is formed as

|         | g <sub>ll</sub> | g <sub>12</sub> | •••   | • <sup>g</sup> la | hll                         | h12             | •••   | h<br>lø          |

|---------|-----------------|-----------------|-------|-------------------|-----------------------------|-----------------|-------|------------------|

| [G:H] = | •               |                 |       |                   | hıı<br>:<br>h <sub>Nı</sub> |                 |       |                  |

|         | g <sub>Nl</sub> | g <sub>N2</sub> | • • • | • g <sub>Na</sub> | h <sub>Nl</sub>             | h <sub>N2</sub> | • • • | h <sub>Nb</sub>  |

|         |                 |                 |       |                   | $m = \sum_{k=1}^{a}$        |                 |       |                  |

|         |                 |                 | ¥     | ie: I 3,          | ¥j ε Il                     | and             | ¥m ε  | : I <sub>2</sub> |

I<sub>1</sub>=(1,2,...,a), I<sub>2</sub>=(1,2,...,b)

and  $I_3$  is a set of components  $(1,2,\ldots,N)$  $g_{ij}$  gives the total number of wires connecting  $E_i$  with the components in the jth row of placement matrix P.  $h_{im}$  gives the number of wires connecting components  $E_i$  with the components in the m th column of the matrix P.

-21-

### Objective function (F)

$F = n_{h}F_{h} + n_{\ell}F_{\ell} + n_{d}F_{d} + n_{c}F_{c} + n_{r}F_{r} \qquad (2.4.2.2)$ where  $n_{h}$ ,  $n_{c}$ ,  $n_{d}$ ,  $n_{c}$ ,  $n_{r}$  are the weightage given to the functions  $F_{h}$ ,  $F_{\ell}$ ,  $F_{d}$ ,  $F_{c}$  and  $F_{r}$  respectively.

$\Delta F(s,t)$  represents the increment in function F due to interchange of components  $E_s$  and  $E_t$  in the placement matrix.

$$\Delta F(s,t) = n_{H} \Delta F_{h}(s,t) + n_{f} \Delta F_{f}(s,t) + n_{d} \Delta F_{d}(s,t) + n_{c} \Delta F_{c}(s,t) + n_{r} \Delta F_{r}(s,t) (2.4.2.3)$$

### Calculation of number of holes $(F_h)$

For X-Y coordinate wiring, the number of holes which are formed from wires connecting  $E_5(j,k)$ , to the row  $t(t \neq j)$ is given by.

$$HR(s) = \sum_{t=1}^{a} (g_{st} - c_{s}, p_{tk}) - g_{sj} \qquad s=1,2,...,N$$

Then, total number of holes to minimize becomes

$$F_{h} = \frac{1}{2} \sum_{s=1}^{N} HR(s) \qquad (2.3.2.4)$$

<u>Theorem 1</u> When  $E_s(j,k)$  and  $E_t(\ell,m)$  are interchanged in the matrix P, the elements which change in matrix [G:H] are  $g_{ij}$ ,  $h_{ik}$ ,  $g_{i\ell}$ ,  $h_{im}$ , [i=1,2,...,N]. Their modified values become

$g'_{ij} = g_{ij} + A$   $h'_{ik} = h_{ik} + A'$   $g'_{ik} = g_{ik} - A$   $h'_{im} = h_{im} - A'$

(2.4.2.5)

$A = \begin{cases} c_{it} - c_{is} & \text{, if } j - k \neq 0 \\ 0 & \text{, if } k - j = 0 \end{cases}$

$$A' = \begin{cases} c_{it} - c_{is} & , if k-m \neq 0 \\ 0 & , if k-m = 0 \end{cases}$$

<u>Theorem 2</u> When  $E_s(j,k)$ ,  $E_t(f,m)$  are interchanged, the increment in wiring function  $F_h$  is given by

$$\Delta F_{h}(s,t) = g_{sj} + h_{sk} - (g_{s\ell} + h_{sm} - Z c_{st}) + g_{t\ell} + h_{tm} - (g_{tj} + h_{tk} - Z c_{ts})$$

(2.4.2.6)

where,

where

$$Z = \begin{cases} 1, & \text{if } (j-k)(k-m) = 0 \\ 2, & \text{otherwise} \end{cases}$$

Theorem 3 When

$$E_{s}(j,k)$$

and  $E_{t}(\not(n))$  are inter changed at

iteration (i-1),  $\Delta F_{h}^{i}(u,v)$  is given by

$\Delta F_{h}^{i}(u,v) = \begin{cases} \Delta F_{h}^{i-1}(u,v) & \text{if } n,q \neq j, \text{ and } p,r \neq k,m \\ & \Delta F_{h}^{i-1}(u,v) \div (c_{ut} - c_{us} - c_{vt} + c_{vs})(x_{1} - x_{2} + x_{3} - x_{4}), \\ & \text{otherwise} \end{cases}$

(2.4.2.7)

$u = 1, 2, ..., N; \quad u \neq s, t$   $v = u+1, u+2, ..., ab, v \neq s, t$ where  $E_u$ ,  $E_v$  are occupying position (n,p) and (q,r) respectively

$$x_{1} = \begin{cases} -1, & \text{if } n=j \\ -1, & \text{if } n=k \\ 0, & \text{otherwise} \end{cases}$$

1, if q=j

$$x_2 = \{ -1, if q = 1 \}$$

0, otherwise

-23-

l, if p=k

x.3 = {-1, if p=m

0, otherwise

l, if r=k

x4 = {-1, if r=m

0, otherwise

Calculation of length of etches ( $F_{\lambda}$ )

Symmetrical matrix M of the order ab X ab can be determined as

$$m_{ij} = k_c |k-p| + w_c |k-q|$$

M

Manhattan (rectilinear) distance between components  $E_i(k, l)$  and

$$E_{j}(p,q)$$

(2.4.2.8)

The total routing length is equal to

Total rectilinear weighted wiring length can also be determined from matrix [G:H]. Number of interconnection leads passing through ith horizontal and ith vertical sections are

$$W_{h_{1}} = \sum_{k=i+1}^{a} \sum_{j\in Q_{i}} g_{jk}, i=1,2,...,a-1 \quad (2.4.2.10)$$

$$W_{v_{1}} = \sum_{k=i+1}^{b} \sum_{j\in S_{i}} h_{jk}, i=1,2,...,b-1 \quad (2.4.2.11)$$

where

Q<sub>i</sub> is the set of components excluding fictitious components placed in rows 1,2,...,i.

S<sub>i</sub> is the set of components excluding fictitious components placed in columns 1,2,...,i.

$L_x$  and  $L_y$  are the total wiring length parallel to X-axis and Y-axis respectively, then total rectilinear wiring length is given by,

-24-

$$F_{\lambda} = L_{x} + L_{y} = W_{c} \sum_{i=1}^{a-1} W_{h_{i}} + \lambda_{c} \sum_{j=1}^{b-1} W_{v_{j}}$$

(2.4.2.12)

<u>Theorem 4</u> When components  $E_s(j,k)$  and  $E_t(\not m)$  are interchanged, the increments  $\Delta W_{h_i}$  (s,t) and  $\Delta W_{v_i}(s,t)$  in  $W_{h_i}$  and  $W_{v_i}$  respectively are given by

$\Delta W_{\mathbf{h}_{\mathbf{i}}}(\mathbf{s}, \mathbf{t}) = \begin{cases} K_{1} \begin{bmatrix} i \\ \Sigma \\ p=1 \end{bmatrix} (g_{sp}-g_{tp}) + \sum_{q=i+1}^{a} (g_{tq}-g_{sq}) + 2c_{st}, if \forall i \in I_{1} \\ 0 \text{ otherwise} \end{cases}$  (2.4.2.13)

and

$$\Delta W_{v_{\underline{1}}}(s,t) = \begin{cases} \sum_{p=1}^{k} (h_{sp}-h_{tp}) + \sum_{q=i+1}^{p} (h_{tq}-h_{sq}) + 2c_{st}, if \forall i \in I_{2} \\ 0, otherwise \end{cases}$$

(2.4.2.14)

where

$$\begin{array}{c} ---, --- \\ 0, \text{ if } m = k \end{array}$$

With the help of this theorem  $\Delta F_{k}(s,t)$  can be written as

$$\Delta F_{j}(s,t) = w_{c} \sum_{i \in I_{1}} \Delta W_{h_{i}}(s,t) + \int_{c} \sum_{j \in I_{2}} \Delta W_{v_{j}}(s,t)$$

$$s = 1, 2, \dots, N$$

$$t = s + 1, s + 2, \dots, ab$$

$$(2.4.2.15)$$

### Theorem 5

If components  $E_{s}(j,k)$  and  $E_{t}(\ell,m)$  are interchanged in placement matrix P at iteration (y-1), the values of  $\Delta W_{h_{i}}^{y}(u,v)$ and  $\Delta W_{v_{i}}^{y}(u,v)$  in terms of  $\Delta W_{h_{i}}^{y-1}(u,v)$  and  $\Delta W_{v_{i}}^{t-1}(u,v)$  can be given by

$$\Delta W_{h_{1}}^{y}(u,v) = \begin{cases} \Delta W_{h_{1}}^{v-1}(u,v) + 2K_{1}B_{1}(c_{ut}-c_{us}+c_{vs}-c_{vt}), \text{ if } i \in \mathbb{T}_{3} \\ y-1 \\ \Delta W_{h_{1}} \quad (u,v), \text{ otherwise} \\ i = 1, 2, \dots, a-1 \end{cases}$$

$$(2.4.2.16)$$

and (y-1)  $\Delta W_{v_1}$   $(u,v)+2K_2(c_{ut}-c_{us}+c_{vs}-c_{vt})$   $B_2$ , if icI<sub>4</sub>  $\Delta W_{v_1}$   $(u,v)_{=} \begin{cases} \Delta W_{v_1} (y-1)(u,v), \text{ otherwise} \end{cases}$  (2.4.2.17)

where

$I_{3} = [\max[\min(j, l), \min(n, q)], \dots, \min[\max(j, l), \max(n, q)]]$  $I_{4} = [\max[\min(k, m), \min(p, r)], \dots, \min[\max(k, m), \max(p, r)]]$

E<sub>u</sub> and E<sub>v</sub> are occupying the positions (n,p) and (q,r) respectively. From theorems 4 and 5  $\Delta F_{\chi}^{y}(u,v) = \Delta F_{\chi}^{y-1}(u,v) + (c_{ut}-c_{us}+c_{vs}-c_{vt})(2K_{1}B_{1}w_{c}|I_{3}| + 2K_{2}B_{2}k_{c}|I_{4}|)$ (2.4.2.18) u,v ≠ s,t

where, X is the number of elements in the set X.

### <u>Calculation of interconnection densities $(F_d)$ </u>

Wiring function  $(F_d)$  is taken as weighted everage interconnection density on the board.

$$F_{d} = \frac{1.0}{\ell_{b}(a-1) + W_{b}(b-1)} \begin{bmatrix} a^{-1} \\ \sum_{i=1}^{a} \beta_{h_{i}} \\ i=1 \end{bmatrix} W_{h_{i}} + \sum_{j=1}^{b-1} \beta_{v_{j}} \\ (2.4.2.19)$$

for even distribution of etches in horizontal and vertical sections of the board,  $\beta_{h_i} = W_{h_i}$ , [i=1,2,...,a-1] and  $\beta_{v_j} = W_{v_j}$ [j=1,2,...,b-1]  $\Delta F_d(s,t) = \frac{1.0}{f_b(a-1)+w_b(b-1)} \begin{bmatrix} a^{-1} \\ \Sigma \\ i=1 \end{bmatrix} \beta_{h_i} \Delta W_{h_i}(s,t) + \sum_{j=1}^{b-1} \beta_{v_j} \Delta W_{v_j}(s,t)$ ] s=1,2,...,N, t=s+1, s+2,...,ab(2.4.2.20)

If the components  $E_s(j,k)$  and  $E_t(n,m)$  are interchanged at iteration (i-1), the value of  $\Delta F_d^i$  (u,v) in terms of  $\Delta F_d^{i-1}$  (u,v) is given by

$$\Delta F_{d}^{i}(u,v) = \Delta F_{d}^{i-1}(u,v) + (c_{ut} - c_{us} + c_{vs} - c_{vt})[K_{1}B_{1}\sum_{n \in I_{3}}\beta_{n} + c_{s} + c_{vs} - c_{vt})[K_{1}B_{1}\sum_{n \in I_{3}}\beta_{n} + c_{s} + c_{s} + c_{vs} - c_{vt})[K_{1}B_{1}\sum_{n \in I_{3}}\beta_{n} + c_{s} + c_{s} + c_{vs} - c_{vt})[K_{1}B_{1}\sum_{n \in I_{3}}\beta_{n} + c_{s} + c_{s} + c_{vs} - c_{vt})[K_{1}B_{1}\sum_{n \in I_{3}}\beta_{n} + c_{s} + c_{vs} - c_{vt})[K_{1}B_{1}\sum_{n \in I_{3}}\beta_{n} + c_{s} + c_{vs} - c_{vt})[K_{1}B_{1}\sum_{n \in I_{3}}\beta_{n} + c_{vs} - c_{vt})[K_{1}B_{1}\sum_{n \in I_{3}}\beta_{n} + c_{vs} + c_$$

## Calculation of Stray Capacitance (Fc)

In X-Y coordinate wiring, total stray capacitance in the circuit will be minimized by minimizing.

$w_{c} \stackrel{a-l}{\underset{i=l}{\overset{\Sigma}{\overset{D}}}} W_{hi} \stackrel{w_{hi}}{,} \stackrel{*}{\not k}_{c} \stackrel{b-l}{\underset{j=l}{\overset{\Sigma}{\overset{D}}}} W_{v} \stackrel{w_{v}}{,} \frac{w_{v}}{j}$

or,

$$\min F_{c} = \frac{w_{c}}{k_{0}} \sum_{i=1}^{a-1} w_{h_{1}}^{2} + \frac{k_{c}}{w_{b}} \sum_{j=1}^{b-1} w_{j}^{2}$$

(2.4.2.22)

$$\Delta F_{c}(s,t) = \frac{w_{c}}{k_{b}} \sum_{i=1}^{a-1} [2.W_{h_{1}} \Delta W_{h_{1}}(s,t) + [\Delta W_{h_{1}}(s,t)]^{2}]$$

$$+ \frac{k_{c}}{w_{b}} \sum_{j=1}^{b-1} [2.W_{v_{j}} \Delta W_{v_{j}}(s,t) + [\Delta W_{v_{j}}(s,t)]^{2}]$$

(2.4.2.23)

$$s = 1, 2, \dots, N, t = s+1, s+2, \dots, ab$$

Calculation of temperature function  $(F_r)$

The failure rate of semiconductor devices is defined via an Arrehenius relation

$\chi(T) = \chi(T_a) \exp[(T_a^{-1} - T^{-1}) e_a/k]$  (2.4.2.24)

Components  $E_i$  and  $E_j$  are placed in slots having coordinates (k, /) and (p,q) respectively. The distance between components

$$E_{i} \text{ and } E_{j} \text{ is}$$

$$m_{ij} = \left[ \int_{c}^{2} (k-p)^{2} + w_{c}^{2} (\int_{c}^{-q})^{2} \right]^{1/2} \qquad (2.4.2.25)$$

The temperature function  $F_r$  is written as

$$F_{r} = \sum_{i=1}^{N} \sum_{j=1}^{R} R_{je} W_{j} \gamma_{i}/R_{ij} \qquad (2.4.2.26)$$

where,

$\Upsilon_{i} = (R_{ie} \cdot W_{i})^{n}$ , 0.5  $\leq n \leq 2$ . value of n decided from experience.  $R_{ij} = r_{ij}(m_{ij})^{n}$ , 0.4  $\leq n \leq 2.5$

Value of n depends upon the thermal conductivity and dimensions of the board, and heat transfer coefficient of the surface of circuit board.

# Theorem 6

When  $E_s$  and  $E_t$  are interchanged in the matrix P, the only elements which change in matrix M are  $m_{si}$ ,  $m_{ti}$ ,  $m_{is}$  and  $m_{it}$ , [i=1,2,...,ab]. These modified entries will be

$$m_{ts} = m'_{st} = m_{st}$$

$m'_{it} = m'_{ti} = m_{si}$

$m'_{si} = m'_{is} = m_{ti}$

$i=1,2,...,ab$  (2.4.2.27)

$(2.4.2.27)$

# Theorem 7

When components  $E_s$  and  $E_t$  are interchanged in matrix P, the change in function  $F_r$  will be equal to

## Theorem 8

If components  $E_s$  and  $E_t$  have been interchanged in iteration i, the value of  $\Delta F_r^{i+1}(u,v)$  in terms of  $\Delta F_r^i(u,v)$ is given by

$$\Delta F_{r}^{i+1}(u,v) = \Delta F^{i}(u,v) + (J_{s}-J_{t})[f^{-1}(m_{tv}^{i})-f^{-1}(m_{tu}^{i})-f^{-1}(m_{sv}^{i})+f^{-1}(m_{su}^{i})]$$

$$u=1,2,\ldots,N, v=(u+1), (u+2),\ldots,NT \qquad (2.4.2.29)$$

$$\neq s,t \qquad \neq s,t$$

where,

$$J_{s} = \Upsilon_{s} K_{su} + \Upsilon_{u} K_{us} - \delta_{1}(\Upsilon_{s}K_{sv} + \Upsilon_{v}K_{vs})$$

$$J_{t} = 2[\Upsilon_{t}K_{tu} + \Upsilon_{u} K_{ut} - \delta_{1}(\Upsilon_{t}K_{tv} + \Upsilon_{v}K_{vt})]$$

$$\delta_{1} = \{ \begin{array}{l} 1, \text{ if } v \leq N \\ 0, \text{ otherwise} \end{array} \}$$

$$\delta_{2} = \{ \begin{array}{l} 0, \text{ otherwise} \end{array} \}$$

# Algori thm

- (i) Calculate matrix [G.H] using (2.4.2.1), calculate functions  $F_{h}^{i}$ ,  $F_{\lambda}^{i}$ ,  $F_{d}^{i}$ ,  $F_{c}^{i}$  and  $F_{r}^{i}$  by equations (2.4.2.4), (2.4.2.12), (2.4.2.19), (2.4.2.22) and (2.4.2.26) respectively, set i=1.

- (ii) Calculate multi criteria function  $F^{i} = n_{h} F^{i}_{h} + n_{\chi} F^{i}_{\chi} + n_{c} F^{i}_{c} + n_{d} F^{i}_{d} + n_{r} F^{i}_{r}$  by equation (2.4.2.2).

(iii)Set s+0

- (iv) s + s+1

- (v) Set t = s+1

(vi) If  $(s \leq a \text{ and } t > a)$  or  $(s>a \text{ and } t \leq a)$  go to step (xiii)(vii)Calculate  $\Delta F_h^i(s,t)$ ,  $\Delta F_{\ell}^i(s,t)$ ,  $\Delta F_d^i(s,t)$ ,  $\Delta F_c^i(s,t)$ ,  $\Delta F_r^i(s,t)$

if i=1 by equations (2.4.2.6), (2.4.2.15), (2.4.2.20), (2.4.2.23), (2.4.2.28) and for i > 1 by equations

(2.4.2.7), (2.4.2.18), (2.4.2.21), (2.4.2.23) and (2.4.2.29) respectively.

(viii)Calculate  $\Delta F^{i}(s,t)$  by equation (2.4.2.3).

- -31-

- (ix) If  $\triangle F^{i}(s,t)$  is not negative goto step (xiii).

- (x) Find the matrix  $P^{i}$  after interchanging components  $E_{s}$  and  $E_{t}$ .

- (xi) Set i = i+l and calculate  $F^{i}$ .

- (xii) Calculate (G:H]<sup>i</sup> with the help of equation (2.4.2.5) and matrix M<sup>i</sup> with the help of equation (2.4.2.27) and goto step (iii).

(xiii)Set t = t+1.

- (xiv) If t is not greater than NT go to step (vi)

- (xv) If s is less than N go to step (iv).  $(\chi \sqrt{1})$  Stop

- 2.4.2.2 Components of different sizes

One of the assumptions while stating the placement problem is that the components are of two different sizes. Dimensions of first type being such that each component requires one and only one slot on the printed circuit board, and the second type of components are double the size of the first type. In other words, a double sized component requires two adjacent slots for its placement. The double sized component, for solving the placement problem are treated as two distinct components with very high connectivity between them. After performing the iterative improvement algorithm with all the components treated as occupying one slot, irrespective of the initial placement, it has been observed that the two components which correspond to a double sized component come closer and are placed in adjacent slots, because of the

Central Library University of Room

high connectivity between them. But the position of the slots occupied by the two components depend largely on the initial placement. Once the two components have come close in the adjacent slots during the iterative procedure it is not possible to move the two components to any other slot to improve the **o**jective function, unless the pair is moved together. That is, the position of the pair of components corresponding to double sized components are inter changed with another pair of components placed in some other slots.

The two slots occupied by the pair corresponding to the double sized components may be adjacent in either the same row or in the same column. So this phase of iterative improvement procedure is carried out in two stages. In the first stage all the possible pairs of components in a column can be interchanged with another pair of adjacent components in a column. For different combinations of two pairs that can be inter changed the objective function value is calculated using the equation (2.4.2.2). The pairs are interchanged if there is any improvement in the value of total objective function. For this stage the various combinations possible are-

$(p_{i_1,j_1}), (p_{i_2,j_2})$  interchanged with  $(p_{k_1,k_1}), (p_{k_2,k_2})$ for al for all and  $\begin{bmatrix} k_1 = i_1 \\ k_2 = i_2 \\ l_1 = l_2 = j_1 + 1, b - 1 \end{bmatrix}$ , if  $j_1 < b - 1$  $k_1 = k_2 = j_1 + 1, b - 1$ , if  $i_2 < a$  $k_1 = k_2 - 1$ ,  $j_1 = l_2 = 1, b - 1$ i<sub>2</sub> = 2,a  $i_1 = i_2 - 1$ j<sub>1</sub> = j<sub>2</sub>=1,b-1

-32-

The second stage is similar to the first stage except the possible pairs of components in a row are interchanged with another pair of adjacent components in a row, i.e.

$(p_{i_1, j_1}), (p_{i_2, j_2})$  can be interchanged with any of  $(p_{i_1, \ell_1}), (p_{k_2, \ell_2})$ where where,

$j_2=2, b=1 \qquad f_1=j_1 \\ j_1=j_2=1 \qquad f_2=j_2 , if i_1 < a \\ i_1=i_2=1, a \qquad k_1=k_2=i_1+1, a$

and

$$\lambda_{2}=j_{2}+1, b-1$$

$\lambda_{1}=\lambda_{2}-1, j_{2}

$k_{1}=k_{2}=1, a$$

#### Example 2.2

Consider a circuit containing 14 components. The components are to be placed on the printed circuit board of size 15 X 23 cms. As many as 36 components can be placed on the board. The board is divided into 6 horizontal and 6 vertical divisions. In all 20 components (14 plus 6 corresponding to the edge connector are to be placed on this board. Thermal resistances of all the components are  $400^{\circ}$ C/W. Failure rate of each component at  $100^{\circ}$ C (junction temperature) is 0.025 per 1000 hrs. Ambient temperature is  $27^{\circ}$ C. The power dissipation of each component is given in Table 2.1. Thermal resistance  $(R_{i,j})$  due to thermal coupling between two components  $E_i$  and  $E_j$  is assumed to be 5000  $m_{ij}$ , where  $m_{ij}$  is in cms, and  $\gamma_i = R_{ie} W_i [i=1,2,...20]$ . The values of weightages for different functions are taken as

$n_{h}=1, n_{f}=0.05, n_{d}=20.0, n_{c}=0.015, n_{r}=0.015$ Non zero elements of connection matrix C are  $c_{2,1}=1$ ,  $c_{3,1}=1, c_{4,1}=1, c_{6,2}=2, c_{7,2}=1, c_{8,2}=2, c_{6,3}=2, c_{7,3}=3$ ,  $c_{8,3}=2, c_{5,4}=1, c_{9,5}=1, c_{10,5}=4, c_{11,5}=3, c_{9,6}=2, c_{9,7}=100$ ,  $c_{10,7}=1, c_{11,8}=5, c_{12,9}=3, c_{3,10}=3, c_{14,11}=4, c_{15,12}=3$ ,  $c_{20,12}=100, c_{16,13}=4, c_{17,14}=100, c_{18,15}=1, c_{19,16}=5$ ,  $c_{20,17}=6$

Table 2.1

| Pov                                   | ver | dissi | pation                               | of compo                          | nents                        | of e                     | xampl | e 2.2 |    |     |

|---------------------------------------|-----|-------|--------------------------------------|-----------------------------------|------------------------------|--------------------------|-------|-------|----|-----|

|                                       |     |       |                                      |                                   |                              |                          |       |       |    |     |

| Component                             | 1   | 2     | 34                                   | 56                                | 7                            | 8                        | 9. 1  | .0    |    |     |

| ہیں ہے جو ہونے کا جاری کا             |     |       | na in a <sub>bad</sub> thi an Sti an | ی<br>ما ہوں ہیں میں 800 - 800 ہیں | , an <sup>100</sup> 100 m 10 | ست بلينا بينين وهه جين ۽ |       |       |    |     |

| Power<br>dissipation<br>in mw         |     | · · · |                                      |                                   | 160                          | 170 1                    | .80 8 | 0     |    |     |

| Componént                             | 11  | 12    | 13                                   | 14                                | 15                           | 16                       | 17    | 18    | 19 | 20  |

| Powe <b>r</b><br>dissipation<br>in mw | 85  | 120   | 130                                  | 140                               | 150                          | 160                      | 170   | · 60  | 80 | 130 |

Initial placement obtained by-the constructive algorithm.

|     | To  | 19 | 16 | 13 | 10 | 5 |

|-----|-----|----|----|----|----|---|

|     |     | ТĴ | 70 | жJ |    | - |

|     | 7   | 9  | 0  | 8  | 11 | 2 |

| D   | 15  | 12 | 20 | 17 | 14 | 6 |

| r = | 18  | 0  | 0  | 0  | 0  | 3 |

|     | 0   | 0  | 0  | 0  | 0  | l |

|     | 0 - | 0  | 0  | 0  | 0  | 4 |

Placement obtained by iteratively interchanging two individual components at a time (stage one) in 22 iterations

|     |    |   | •  |    |    |     |

|-----|----|---|----|----|----|-----|

|     | 13 | 7 | 16 | 19 | 8  | 3   |

|     | 10 | 9 | 12 | 0  | 11 | 5   |

|     | 0  | 0 | 20 | 0  | 17 | 6   |

| P = | o  | 0 | 0  | 0  | 14 | 2   |

|     | o  | С | 0  | 0  | O  | _ l |

|     | 18 | 0 | 15 | Ö  | 0  | 4   |

After iteratively interchanging a pair of components in same column with another pair of components in same column (stage two), the placement after two iterations is

|     |     |    |    |    |    | - 1 |  |

|-----|-----|----|----|----|----|-----|--|

|     | 7   | 19 | 16 | 13 | 8  | 3   |  |

|     | 9   | 0  | 12 | lC | 11 | 5   |  |

|     | 0   | 0  | 20 | 0  | 17 | 6   |  |

| P = | 0   | 0  | 0  | 0  | 14 | 2   |  |

|     | 0 - | 0  | 0  | 0  | 0  | l   |  |

|     | _18 | 0  | 15 | 0  | 0  | 4   |  |

There is no further improvement by interchanging a pair of component in same row with another pair in same row (stage three).

The function values at the end of each stage is compiled in Table 2.2.

Table 2.2 Results of example 2.2

÷

| Constructive<br>Placement $ 12$ $2.68$ $1542.67$ $10141.00$ $44.34$ $0.238$ $395.60$ $3 tage one$ $22$ $6$ $2.12$ $1219.67$ $4717.50$ $43.65$ $0.211$ $266.90$ $3 tage one$ $2$ $6$ $2.09$ $1204.33$ $4669.46$ $43.61$ $0.197$ $262.66$ $5 tage three$ $0$ $6$ $2.09$ $1204.33$ $4669.46$ $43.61$ $0.197$ $262.66$ |                   | Number<br>of<br>I terations | Number<br>of<br>Holes | Avg.<br>Wiring<br>Density<br>(ET/CM) | Total<br>Wiring<br>Length<br>(CM) | Capaci tance<br>Factor | Mean<br>Tempe-<br>rature<br>(oc) | Failure<br>Rate<br>(per<br>1000 hrs) | Failure Total<br>Rate Value<br>(per of<br>1000hrs) Function |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------|-----------------------|--------------------------------------|-----------------------------------|------------------------|----------------------------------|--------------------------------------|-------------------------------------------------------------|

| 22       6       2.12       1215.67       4717.50       43.65       0.211         2       6       2.09       1204.33       4669.46       43.61       0.197         0       6       2.09       1204.33       4669.46       43.61       0.197                                                                        | tructive<br>ement | 2                           | 21                    | 2 .68                                | 1542.67                           | l0141.00               | 44.34                            | 0.238                                | 395.60                                                      |

| 2 6 2.09 1204.33 4669.46 43.61 0.197<br>0 6 2.09 1204.33 4669.46 43.61 0.197                                                                                                                                                                                                                                       | e one             | 22                          | Q                     | 2.12                                 | 73.215.67                         | 4717-50                | 43.65                            | 0.211                                | 266.90                                                      |

| 0 6 2.09 1204.33 4669.46 43.61 0.197                                                                                                                                                                                                                                                                               | e two             | N                           | 9                     | 2.09                                 | 1204.33                           | 4669•46                | 43.61                            | 0.197                                | 262 •66                                                     |

|                                                                                                                                                                                                                                                                                                                    | e three           | 0                           | 9                     | 2.09                                 | 1204.33                           | 4669•46                | 43.61                            | 0.197                                | 262 •66                                                     |

-39-

## <u>CHAPTER - 3</u>

### MULTILAYER PRINTED CIRCUIT BOARD

### 3.1 Introduction

The sophisticated Integrated Circuit technology has facilitated the fabrication of complex circuits within small chips. For designing complex large scale electronic systems using these semiconductor chips as basic building blocks, multilayer printed circuit (MPC) boards are used as a medium for interconnecting these blocks. The components are mounted on top of the MPC board with terminals inserted in the drilled through holes called Pins. The blocks are interconnected by means of printed wires on different layers. Plated through holes called Vias, are used for inter layer connections, in order to connect wires on different layers. Determination of via locations and physical routes of printed wires for making the interconnections of the circuit constitute a MPC routing problem.

The routing of MPC boards is restricted by some physical constraints namely the size of the multilayer board, the feasible number of layers, the minimum width of conductor path and the necessary seperation between two adjacent parallel conductor paths. The basic assumptions as proposed by Ting et.al [14] for solving MPC routing problem are:

The geometrics of the pins and vias are at fixed locations.

Vias appear only columnwise.

2. Only points (pins and/or vias) on the same line can be connected directly and the physical routes must be confined within the channels on both sides of the line.

3. Connections for holes in a column are on one layer and for points (pins or vias) in a row are in other layers.

The problem of interconnection of circuit on different layers can be divided into three interrelated phases [15]. First to decompose the whole interconnection into the portions of each layer, second assignment of vias for each net. and finally laying out the wire patterns on each layer. Many algorithms have been developed [3,6,8,16] for solving single row (or unidirectional) routing problem. Based on the assumptions made above, the multilayer routing problem can be reduced to several single line routing problems [14]. From a general multilayer protlem, several single line single layer routing problems can be obtained by following three basic steps, firstly assigning Vias to form connections with pins on the board, secondly assignment of connection patterns to various layers, and finally realization of all the connections on the basis of single line, single layer problems.

While assigning vias to form connections with pins two main objectives are to be kept in mind [14], minimization of via usage and the minimization of via columns. Each additional via reduces the reliability of the circuit and via column adds to the size of the board and if the board size is kept constant, the area available for routing is reduced.

-41-

In this chapter the problem of component placement on multilayer printed circuit boards is discussed. The via assignment problem has also been described in detail. The formulation of optimization problem has been dealt with and then a refined heuristic algorithm is developed.

## 3.2 Component Placement on MPC Boards

For solving the problem of MPC board routing the first assumption is that, the geometrics of the pins are at fixed locations, which means that the pin locations have to be decided prior to solving the actual routing problem. In other words the component placement has to be fixed based on some optimization criteria. For the component placement on multilayer circuit boards also the same set of criteria are used as for the double layer PCBs (chapter-2). The criteria used for optimizing the component placement on MPC boards also is a combination of length of etches, Inter-connection density. Stray capacitance, effect of thermal coupling between components. and total number of holes. But the method of calculating the number of holes required for realizing a circuit on multilayer PCB is different from what it is for double layer PCBs. Since the need of multilayer PCBs arose from the development of components in DIP packages it is assumed that the pins of each components are in two horizontal rows.

From the definition of the matrix A it is evident that the non zero entries in a column of A represent that pins belonging to the net corresponding to the column are present

-42-

in a row. Further if the pin belonging to a net are present in more than one row Viasare required for its realization. So the total number of vias required for the realization of the whole circuit is calculated by counting the total number of vias needed for realizing each net. That is if a column of A has more than one nonzero entries then that number of holes are required for the realization of the corresponding net. So the total number of holes to be minimized becomes

$$F_{h} = \sum_{j=1,NN}^{NR} \text{ if } \sum_{k=1}^{NR} a_{kj} \geq 2$$

$$j=1,NN$$

$$i=1,NR$$

During the iterative procedure for finding the best component placement it is required to find the A matrix for each iteration. To avoid the calculation of whole of the A matrix the following approach can be used to modify the matrix A and hence save the computation time.

When  $E_s(j, n)$  and  $E_t(\lambda, m)$  are inter changed in the matrix P then the matrix A can be modified as follows.

no change if j = k

otherwise,

<sup>a</sup>(2j-1),L (2s-1),k k=1,NP

$$=0, \text{ if } L(2s-1),k \neq L(2xP_{j,0}-1),p$$

$$| \begin{array}{c} p=1,NP\\ \circ=1,b\\ \circ\neq n \end{array}$$

= 1, otherwise.

$$a_{2j} L_{2s,k} \Big|_{k=1,NP} = 0, \text{ if } L_{2s,k} \neq L_{(2xP_{j,0}), p} \Big|_{\substack{0=1, NP \\ 0=1, b \\ 0 \neq n}} \\ = 1, \text{ otherwise} \\ a_{(2(-1), L(2s-1), k} \Big|_{k=1,NP} = 1 \\ a_{(2(-1), L(2t-1), k} \Big|_{k=1,NP} = 0, \text{ if } L_{(2t-1), k} \neq L_{(2xP_{f,0}-1), p} \Big|_{\substack{0=1, NP \\ 0=1, b \\ 0 \neq m}} \\ = 1, \text{ otherwise} \\ a_{(2f' L_{2t, k})} \Big|_{k=1,NP} = 0, \text{ if } L_{2t, k} \neq L_{(2xP_{f,0}), p} \Big|_{\substack{0=1, NP \\ 0=1, b \\ 0 \neq m}} \\ = 1, \text{ otherwise} \\ a_{(2s-1), L_{(2t-1), k}} \Big|_{k=1,NP} = 1 \\ a_{(2s-1), L_{(2t-1), k}} \Big|_{k=1,NP} = 1 \\ a_{2s, L_{2t, k}} \Big|_{k=1,NP} = 1 \\ a_{$$

The nets associated with the components going out of the row are compared with other pins of the same row. If another pin in the row is belonging to the same net then the element of A corresponding to the row and the net is not changed other wise it is made zero. And the element of A corresponding to the row to which the component is entering and the corresponding nets is made equal to one.

# 3.3 The via Assignment Problem

For a circuit, one possible realization on a multilayer board is done by drawing the conductor paths connecting vias in the same column on one layer. Interconnections between pins and vias in the same row are drawn on the other

-44-

layers. This scheme of connecting pins or vias in the same row or column is termed as the single row single layer routing. This can be conducted only after determination of via assignment for each net.

If vias are assigned in a slightly different way, a totally different realization of the circuit on the board is obtained. Thus increase or decrease in the number of via columns is achieved by assigning vias to the nets differently. Hence it is very important to assign the vias for each net under the criteria that the number of via columns is reduced as much as possible.

In a circuit if there is a net with all the pins placed in the same row, then no vias are required for the interconnection of this net. So it is assumed that for the via assignment problem the circuit does not contain any such net.

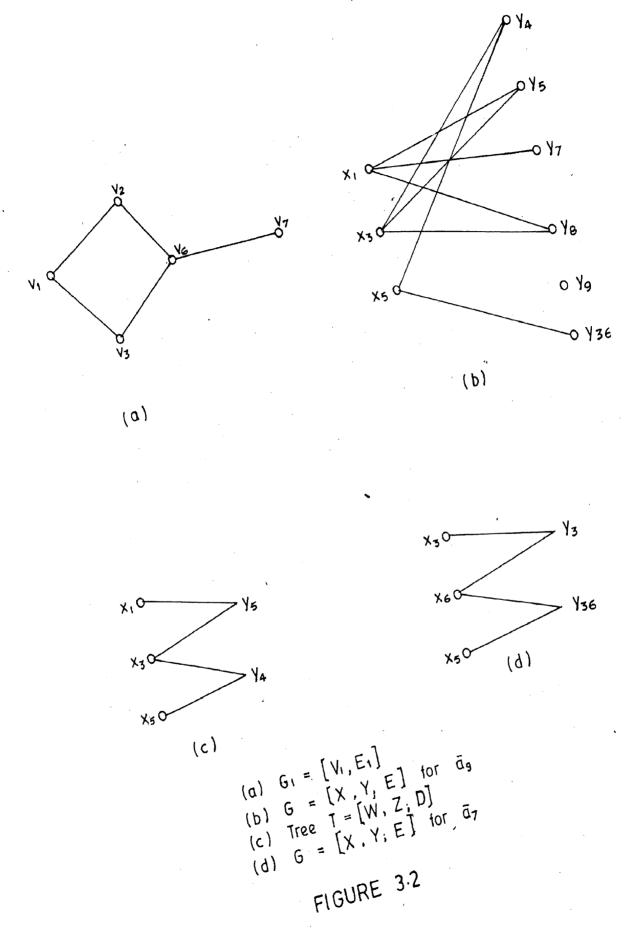

For a given net list  $L = \{N_1, N_2, \dots, N_n\}$  of n nets. Matrix A is defined as  $A = [a_{ij}] = [a_1, a_2, a_3, \dots, a_n]$  where each column  $a_j$  corresponds to a net  $N_j$  of the net list such that

$a_{ij} = \begin{cases} 1, \text{ if net } N_j \text{ contains a pin in row i} \\ 0, \text{ if net } N_j \text{ does not contain a pin in row i} \end{cases}$

It is not possible to connect two pins of a net, if they are placed in different rows by laying the connecting path on one layer when single-row single-layer routing is used. If there is a nonzero entry in the ith row of the column  $a_j$  of the matrix A, that is  $a_{ij}=1$  then at least one via in the ith row is required for interconnecting the net  $N_j$ , corresponding to the column  $\overline{a_j}$ . Hence it is deduced that the minimum number of via columns necessary for realizing a

given net list L, if q is the maximum number of ones in a row of A, is q.

If the rows  $i_1, i_2, \dots, i_k$  of the column  $a_j$  have non zero elements, vias are assigned in the rows  $i_1, i_2, \dots, i_k$ , for the net  $N_j$ , in the same via column, then all these vias are connected by single row single layer routing. Hence, if the number of columns of A is equal to n then maximum number of via columns that are sufficient for the realization of all the nets, is n.

# 3.3.1 Column Merging

Consider there are non zero elements in distinct rows of the columns  $\overline{a}_j$  and  $\overline{a}_k$  or in other words the scalar product of the columns  $\overline{a}_j$  and  $\overline{a}_k$  is equal to zero i.e.  $(\overline{a}_j, \overline{a}_k) \stackrel{\Delta}{=} \Sigma$  $\sum_{k=1}^{n} a_{k,l} = 0$ . The matching, M, is defined as the total number of nonzero elements in the two columns  $\overline{a}_j$  and  $\overline{a}_k$  vias in the same via column are assigned for nets N<sub>j</sub> and N<sub>k</sub> corresponding to  $\overline{a}_j$  and  $\overline{a}_k$  respectively. Thus if  $(\overline{a}_j, \overline{a}_k) = 0$ for two columns  $\overline{a}_j$  and  $\overline{a}_k$  in A, then vias in the same via column are assigned for the corresponding nets N<sub>j</sub> and N<sub>k</sub>.

-46-

The vias for any net are chosen from one single via column, but a via column may contain vias for more than one net. Hence the problem of assigning vias for each net with the minimum number of via columns may be stated as [15].

For a given O-l matrix  $A = \begin{bmatrix} a_1, a_2, \dots, a_n \end{bmatrix}$  minimize the number of columns in the matrix A by repeated application of the column merging process to A.

<u>Column Merging</u> - For a pair of columns  $a_i$  and  $a_j$  such that ( $\overline{a_i}$ ,  $\overline{a_j}$ ) = 0, merge  $\overline{a_i}$  and  $\overline{a_j}$  into a new column  $\overline{a_{ij}}$ =  $\overline{a_i}$ +  $\overline{a_j}$ . Delete  $\overline{a_i}$  and  $\overline{a_j}$  from the matrix A and add column  $\overline{a_{ij}}$ , to it.

After repeated application of column merging process on A, till no further merging is possible, the number of columns in the reduced A matrix is the upper bound on the number of via columns which have to be used for the assignment of vias for each net.

#### 3.3.2 Column Decomposition

The vias for a net are alternatively chosen from  $p(\geq 2)$ different via columns also. Consider a column  $\bar{a}_j$  of A corresponding to the net  $N_j$  having ones in rows  $i_1, i_2, \ldots, i_k$ . Denote I  $\triangleq \{i_1, i_2, \ldots, i_k\}$ , and decompose I into  $I_1$  and  $I_2$ such that  $I_1 \cup I_2 = I$  and  $I_1 \cap I_2$  has exactly one row  $i_a$ . Then for net  $N_j$  the vias in rows of  $I_1$  in one via column  $j_1$  and those in rows of  $I_2$  in another via column  $j_2$ , such that two different parts of routing for  $N_j$ , one in via column  $j_1$  and other in via column  $j_2$  are finally connected by means of two vias in row  $i_a$ . A different way for the assignment of vias in two different via columns for net  $N_j$  is to decompose I into two disjoint subsets  $J_1$  and  $J_2$  and then by adding some row  $i_b \in I$  to  $J_1$  and  $J_2$ , respectively for getting two sets  $I_1$  and  $I_2$ . Then vias for  $N_j$  can be assigned in two via column  $j_1$  and  $j_2$ .

The process of column decomposition for a column  $a_j$ of A is described as follows. The column  $a_j$  is decomposed into  $a_{j1}$  and  $a_{j2}$  where  $a_j$  has ones in rows of I and  $a_{j1}$  and  $a_{j2}$  have ones in the rows of  $I_1$  and  $I_2$ , respectively, such that ICI<sub>1</sub>UI<sub>2</sub> and  $|I_1 \cap I_2|=1$ , respectively. Then each of such decomposed columns,  $a_{j1}$  and  $a_{j2}$  are merged with other columns to give single columns through the process of column merging.

Column Decomposition - For a proper integer p(j), decompose a column  $a_j$  of A into  $\overline{a_{j1}}$ ,  $\overline{a_{j2}}$ ,..., $\overline{a_{jp}}(j)$  such that

i) a<sub>j</sub> ≤ a<sub>j1</sub> + a<sub>j2</sub> + ··· + a<sub>jp(j)</sub>

ii) for any K (2 ≤ K ≤ p(j)), there exists a column a<sub>jh</sub>(1 ≤ h < k) satisfying (a<sub>jk</sub>·a<sub>jh</sub>)=1, then replace a<sub>j</sub> by matrix [a<sub>j1</sub> a<sub>j2</sub>···a<sub>jp(j)</sub>] composed of the p(j) columns.

The replacement of  $a_j$  by  $[a_{j1}, a_{j2} \cdots a_{jp(j)}]$  indicates the decomposition of the net  $N_j$  into p(j) subnets  $N_{j1}, N_{j2}, \cdots$ ,  $N_{jp(j)}$ , where each  $N_{jk}$  corresponds to  $a_{jk}$ . These  $N_{jk}$  are realized in different via columns and are later interconnected by means of single row single layer routing. With the introduction of the process of column merging and column decomposition the problem of minimization of via columns while assigning vias is stated as [15].

Given a O-1 matrix  $A = \begin{bmatrix} a_1 & a_2 & \cdots & a_n \end{bmatrix}$ , by applying the process of column merging and column decomposition to A, minimize the number of columns in A.

#### 3.4 <u>Heuristic Algorithm</u>