# MICROPROCESSOR CONTROLLED COMMUTATORLESS DC SERIES MOTOR DRIVE

## A DISSERTATION

submitted in partial fulfilment of the requirements for the award of the degree

of

MASTER OF ENGINEERING

in .

**ELECTRICAL ENGINEERING**

(Power Apparatus and Electric Drives)

CHECTED 1985

By

## TAPAN KUMAR CHAKRABORTY

DEPARTMENT OF ELECTRICAL ENGINEERING

UNIVERSITY OF ROORKEE

ROORKEE-247667 (INDIA)

February, 1988

#### CANDIDATE'S DECLARATION

I hereby certify that the work which is being presented in the dissertation entitled, MICROPROCESSOR CONTROLLED COMMUTATORLESS DC SERIES MOTOR DRIVE, in partial fulfilment of the requirements for the award of the degree of MASTER OF ENGINEER RING IN ELECTRICAL ENGINEERING with specialization in POWER APPARATUS AND ELECTRIC DRIVES, submitted in the Department of Electrical Engineering, University of Roorkee, Roorkee, is an authentic record of my own work carried out for a period of about seven months, from August, 1987 to February, 1988 under the supervision of Dr. S.P.Gupta, Reader and Dr. Bhim Singh, Lecturer, Department of Electrical Engineering, University of Roorkee, Roorkee, India.

The matter embodied in the dissertation has not been submitted by me for the award of any other degree or diploma.

Dated: February 25,1988

Lapon chakrabouty (TAPAN KUMAR CHAKRABORTX)

This is to certify that the above statement made by the candidate is correct to the best of our knowledge.

Dr. Bhim Singh

Lecturer

Department of Electrical

Engineering

University of Roorkee Roorkee, U.P., India

S. P. Couple

Dr. S.P. Gupta

Reader

Department of Electrical

Engineering

University of Roorkee Roorkee, U.P., India

## ACKNOWLEDGEMENT

I wish to express my deep sense of gratitude and indebtedness to my guides, Dr. S.P.Gupta, Reader, Electrical Engineering Department, University of Roorkee, Roorkee and Dr. Bhim Singh, Lecturer, Electrical Engineering Department, University of Roorkee, Roorkee for constant guidance, encouragement and valuable suggestions at all stages to complete this work.

I am very grateful to Dr. P.Mukhopadhyay, Professor & Head, Electrical Engineering Department, University of Roorkee, Roorkee for providing computer and laboratory facilities. I am very much thankful to faculty members Dr. V.K. Verma, Professor, Sri M.K. Vasantha, Reader, Sri Y.P. Singh, Lecturer and Sri Pramod Agarwal, Lecturer, Electrical Engineering Department, University of Roorkee, Roorkee, for their valuable suggestions given by them time to time.

Thanks are also due to Sri B.N.Sharma, Electrical Engineering Department for his efficient and time bound typing of the thesis.

In the last, I am also very much thankful to all the laboratory and workshop staff for their excellent co-operation during the work.

Lapon charrobody (TAPAN KUMAR CHAKRABORDY)

## ABSTRACT

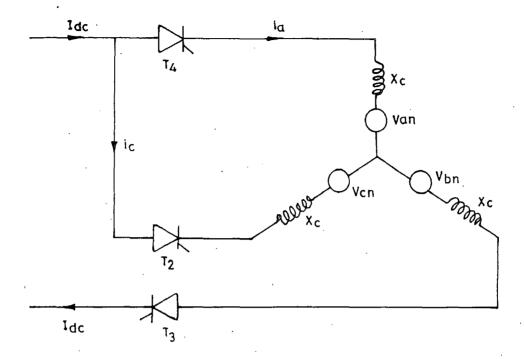

The dissertation concerns the design, fabrication and performance of the microprocessor controlled commutatorless d.c. series motor by using induced voltage commutated inverter along with induced voltage sensor. The firing pulses for thyristors of the inverter are generated by the microprocessor in proper sequence with the help of synchronizing signal derived from the terminal voltages of the synchronous machine. A three-phase synchronous motor supplied by a line commutated inverter (LCI) with the excitation winding connected in series to the d.c. link becomes equivalent to a simple commutatorless d.c. series motor which gives excellent d.c. series motor characteristics.

The steady state analytical model of the drive is developed by using steady state equivalent circuit and performance is computed therefrom. The performance is obtained experimentally also using the fabricated system and the experimental results have shown a good correlation with the computed results. The configuration of the firing angle control scheme used in present work is comparatively simple and requires less software and hardware in comparison to the earlier schemes.

## NOMENCLATURE

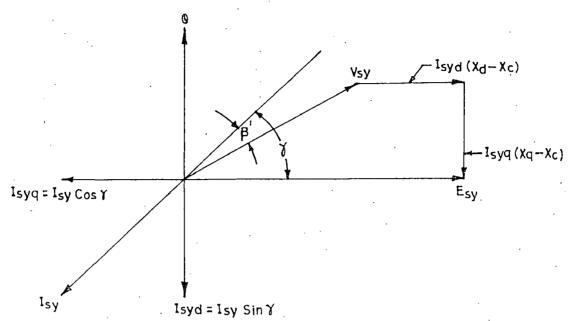

- $\mathbf{E_{sv}}$  The rms value of line to neutral no load terminal voltage

- $V_{\rm sv}$  The rms line to neutral machine terminal voltage.

- Isy The rms value of the fundamental component of the machine line current.

- $I_{\mathrm{syd}}$  Direct axis component of  $I_{\mathrm{sy}}$

- $I_{\mathrm{syq}}$  Quadrature axis component of  $I_{\mathrm{sy}}$ .

- Idc DC link current.

- Pac Real a.c. power fed to the machine.

- $P_{\mbox{dc}}$  DC power fed to the LCI.

- V<sub>d</sub> Average d.c. output voltage of the rectifier.

- Vdc Average d.c. input voltage to the LCI.

- $\mathbf{X}_{\mathrm{d}}$  Direct axis synchronous reactance.

- $X_{q}$  Quadrature axis synchronous reactance.

- X<sub>c</sub> Commutating reactance.

- X Adjusted direct axis synchronous reactance.

- q Ratio of adjusted quadrature to direct axis synchronous reactance.

- Flux per pole.

- N Machine speed in rpm.

- $N_{\rm S}$  Machine speed in rps.

- $R_{\mathbf{f}}$  Resistance of field winding of synchronous machine.

- $R_{\rm d}$  Resistance of the d.c. link inductor.

- $R_{sv}$  Stator resistance of synchronous machine.

- $\alpha$  Inverter firing angle in electrical degrees.

- β Inverter lead angle in electrical degrees.

- μ Commutation overlap angle in electrical degrees.

- Supplementary displacement angle of  $\mathbf{I}_{sy}$  with respect to  $\mathbf{V}_{sy}$  in electrical degrees.

- Supplementary displacement angle of  $I_{sy}$  with respect to  $E_{sy}$  in electrical degrees.

- $\delta$  Thyristor turn-off angle in electrical degrees.

## CONTENTS

|                 |       |                                                           | PAGE      |

|-----------------|-------|-----------------------------------------------------------|-----------|

|                 | Cand: | idate's Declaration                                       | (i)       |

|                 | Ackn  | owledgement                                               | (ii)      |

|                 | Abst: | ract                                                      | (iii)     |

|                 | Nome  | nclature                                                  | (iv)      |

| CH AP'          |       | INTRODUCTION                                              | 1         |

| Ģ.11 <b>1</b> 1 | ,     | General                                                   | . 1       |

|                 |       | •                                                         | .10       |

|                 |       | Literature Survey Scope of Present Work                   | 13        |

| CEL A EX        |       | I DESCRIPTION OF THE SYSTEM                               | 17        |

| CDAP.           |       |                                                           | ·         |

|                 |       | General                                                   | 17        |

|                 | 2.2   |                                                           | 17        |

|                 | 2.3   | System Description                                        | 19        |

|                 | , .   | 2.3.1 Design of Power Circuit                             | 25        |

|                 |       | 2.3.2 Programmable Peripheral Devices                     | 29        |

|                 |       | 2.3.3 Interfacing of Programmable Interval<br>Timer 8253A | 1 34      |

|                 |       | 2.3.4 Synchronizing Technique                             | 35        |

| `               |       | 2.3.5 Microprocessor Based Firing Control Scheme          | 37        |

|                 |       | 2.3.6 Design of Pulse Amplifier Circuit                   | 40        |

| •               | 2.4   | Starting Method of Commutatorless DC<br>Series Motor      | 43        |

|                 | 2.5   | Conclusions                                               | 45        |

| CH AP           | TER-I | II IMPLEMENTATION OF SYSTEM SOFTWARE AND FLOW CHARTS      | 46        |

|                 | 3.1   | General                                                   | 46        |

|                 | 3.2   | Main Program Routine                                      | 46        |

|                 | 3.3   |                                                           | . 5<br>52 |

|                 | 3.4   | DIVISION Subroutine                                       | 54        |

|                 | 3.5   |                                                           | 55        |

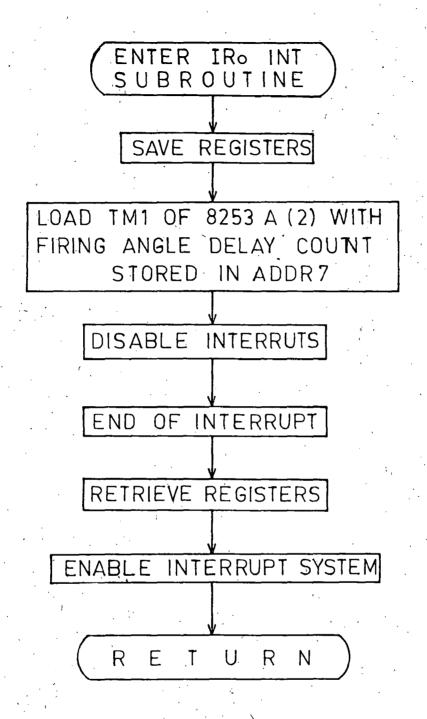

|                 | 3.6   | IR Interrupt Subroutine                                   | 57        |

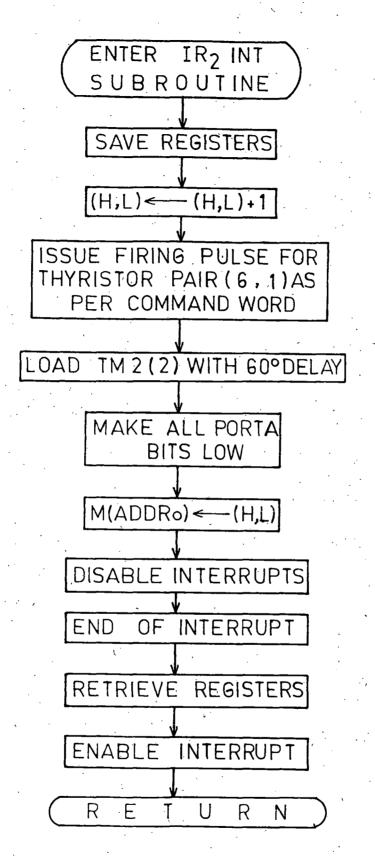

|                 | 3.7   | IR <sub>2</sub> Interrupt Subroutine                      | 58        |

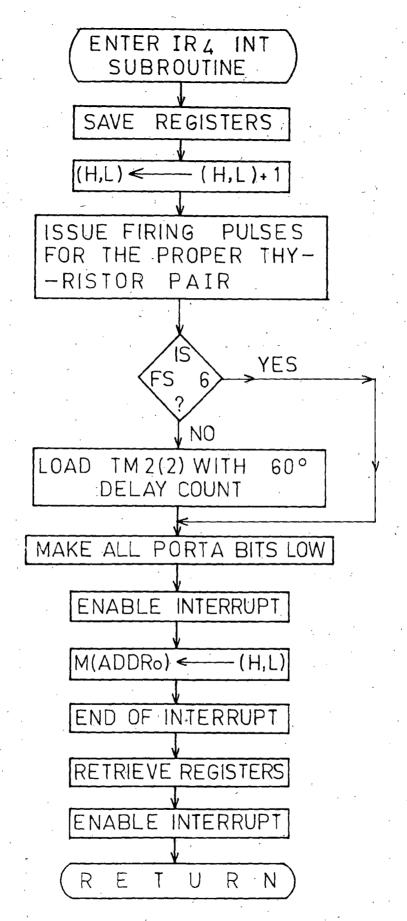

|                 | 3.8   | IR, Interrupt Subroutine                                  | 60        |

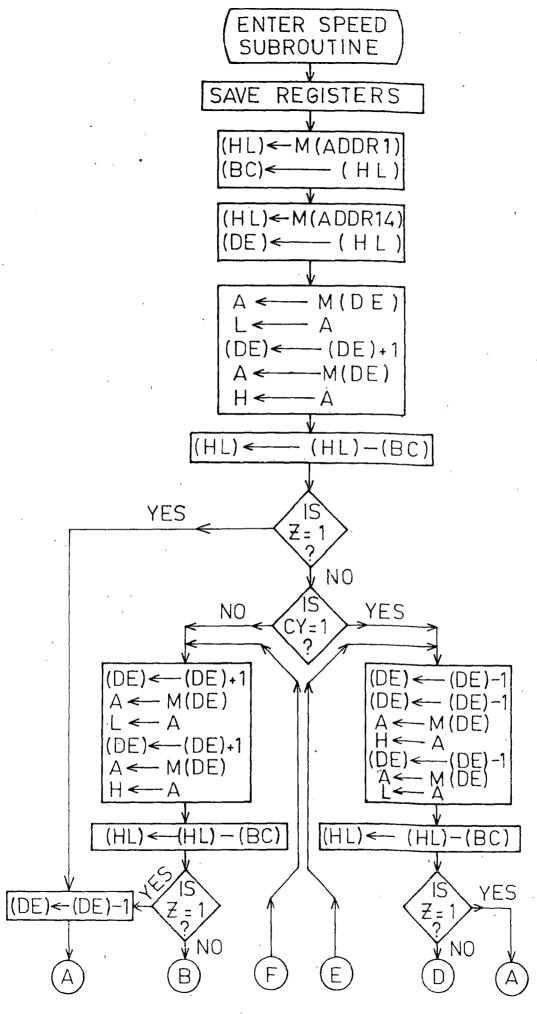

| 3.9 SPEED Subroutine                                                                                  | 61                                                  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--|--|--|--|--|--|

| 3.10 Conclusions                                                                                      | 63 .                                                |  |  |  |  |  |  |

| CHAPTER-IV STEADY STATE ANALYSIS OF THE DRIVE                                                         | 65                                                  |  |  |  |  |  |  |

| 4.1 General                                                                                           | 65                                                  |  |  |  |  |  |  |

| 4.2 Analysis                                                                                          | 65                                                  |  |  |  |  |  |  |

| 4.2.1 System Considered<br>4.2.2 Analytical Model                                                     | 65<br>66                                            |  |  |  |  |  |  |

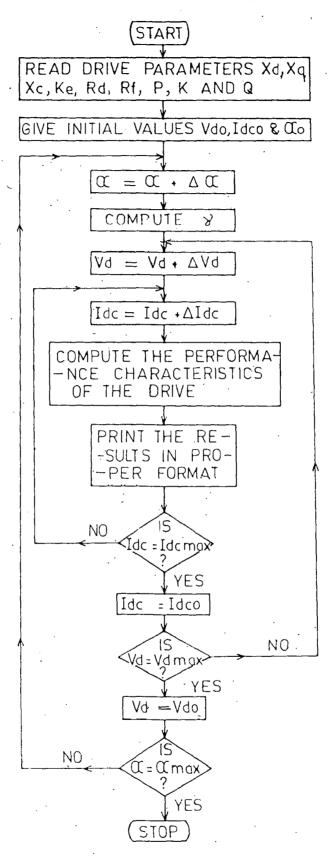

| 4.3 Computer Algorithm                                                                                | 79                                                  |  |  |  |  |  |  |

| 4.4 Conclusions                                                                                       | 80                                                  |  |  |  |  |  |  |

| CHAPTER-V STEADY STATE PERFORMANCE OF THE SYSTEM                                                      | 82 .                                                |  |  |  |  |  |  |

| 5.1 General                                                                                           | 82                                                  |  |  |  |  |  |  |

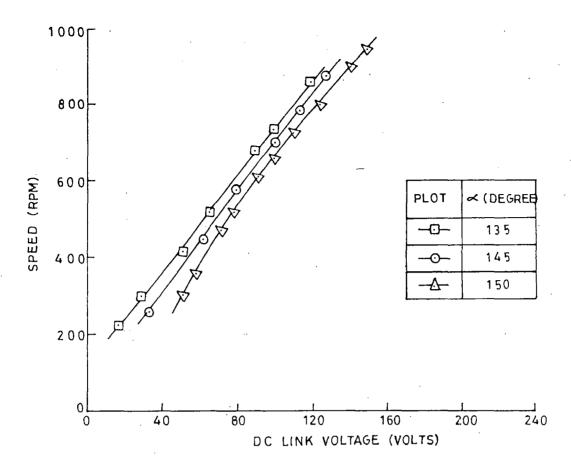

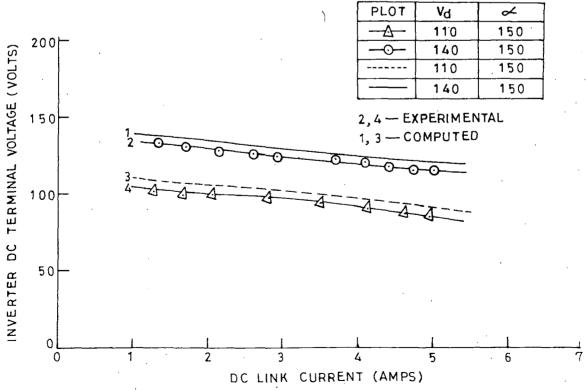

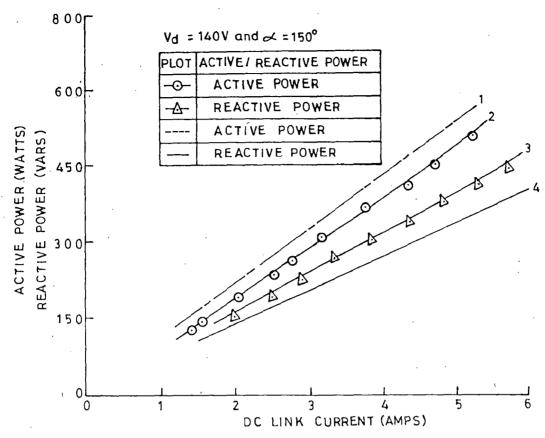

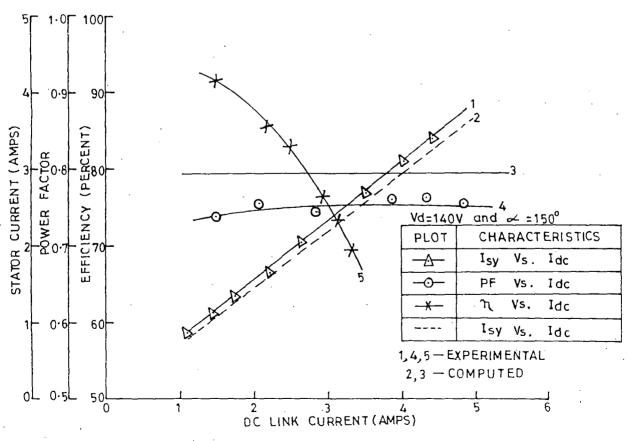

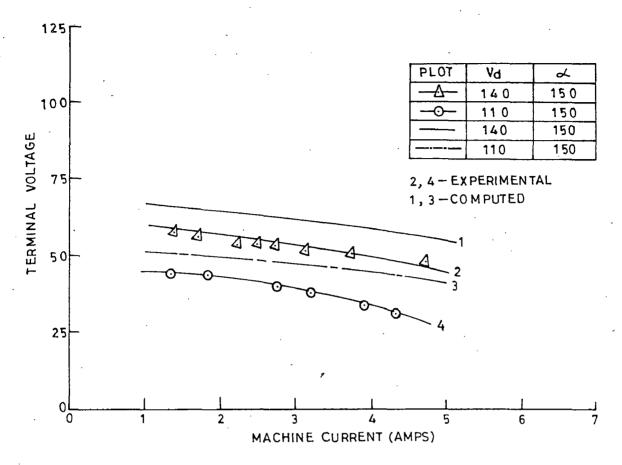

| 5.2 Computation of Performance Characteristics and Their Experimental Verifications                   | 82                                                  |  |  |  |  |  |  |

| 5.2.1 Computation of Characteristics                                                                  | 82                                                  |  |  |  |  |  |  |

| 5.2.2 Experimental Investigations                                                                     | 83                                                  |  |  |  |  |  |  |

| 5.3 Results and Discussions                                                                           | 85                                                  |  |  |  |  |  |  |

| 5.4 Conclusions                                                                                       | 88                                                  |  |  |  |  |  |  |

| CHAPTER-VI CONCLUSIONS AND SUGGESTIONS FOR FURTHER WORK                                               | 90                                                  |  |  |  |  |  |  |

| 6.1 Main Conclusions                                                                                  | 90                                                  |  |  |  |  |  |  |

| 6.2 Suggestions for Further Work                                                                      | 92                                                  |  |  |  |  |  |  |

| REFERENCES                                                                                            | 94                                                  |  |  |  |  |  |  |

| APPENDICES                                                                                            |                                                     |  |  |  |  |  |  |

| Appendix-I Details & Parameters of Machines Use                                                       | ed                                                  |  |  |  |  |  |  |

| <u> </u>                                                                                              | Appendix-II Details of ADC 0809 Interfacing Circuit |  |  |  |  |  |  |

| Appendix-III Assembly Language Program Developed for Firing Control of LCI and Displing Machine Speed |                                                     |  |  |  |  |  |  |

| Appendix-IV Fortran Program for Steady State Ana<br>of the Drive                                      | alysis                                              |  |  |  |  |  |  |

| Appendix-V Fortran Program to Prepare a Look Up<br>for Machine Speed Measurement                      | Table                                               |  |  |  |  |  |  |

| Appendix-VI Photographs of the Experimental Setu                                                      | цр                                                  |  |  |  |  |  |  |

## CHAPTER - I

## INTRODUCTION

## 1.1 GENERAL

Many modern variable speed drives require a precise and smooth control of speed with Long term stability and good transient performance. From the very beginning, the conventional D.C. motors have been used as variable speed drives in many industrial applications. However, for reliable operation of the system, the D.C. motor drives are not advisable in many cases due to the following drawbacks [1]:

- i) Mechanical commutator needs regular maintenance.

- ii) The commutator construction increases the cost of the Drive.

- iii) Power/weight ratio is reduced.

- iv) Brush and commutator wear occurs , due to sparking and friction.

- v) The mica insulation limits the voltage between the segments.

- vi) Unsuitable to operate in dusty and explosive environments.

Commutatorless D.C. motor [2-13] drives which uses synchronous motor can be used most economically as variable speed drives in place of conventional D.C. motor drives, over a wide range of speed. Synchronous motor fed by a line commutated inverter (LCI) acts like a commutatorless

D.C. motor. This drive has several advantages in their favour compared with variable speed drives using other types of motors. Synchronous motors are rugged reliable and free of trouble some commutator maintenance. Power circuit and firing circuit configuration of LCI are quite simple in structure. Moreover, this drive provides the variable speed characteristics like those of conventional D.C. motor [5,7].

Forced commutated inverters have been widely used as variable frequency source for speed control of synchronous machine. However, this scheme needs complicated power and control circuits [14]. As a result of availability of improved voltage and current rating thyristors and with their prices coming down, people have shown considerable interest in synchronous type machines used as commutatorless D.C. motors instead of conventional D.C. motor for variable speed drives.

The rotating type of frequency converters were used previously to obtain variable frequency output from fixed frequency source, but now they are absolute at the advent of silicon-controlled rectifier and are replaced by the solid state frequency converters [1]. The solid state variable frequency source available at present for A.C. drives can be classified into three categories:

- i) cycloconverter

- ii) voltage source inverter

- iii) current source inverter

A cycloconverter converts a.c. power of fixed frequency to a lower output frequency in a single conversion step. output frequency range is preferably limited to one third of the supply frequency [15] and therefore the drives employing cycloconverters are suitable only for operation at low frequency. It can be designed to produce variable frequency, variable voltage power to drive a.c. motors. It is inherently capable of power transfer in either direction between source and load. The cycloconverter delivers a high quality sinusoidal waveform at low output frequencies. One important advantage of cycloconverter drive is that regeneration is simple and the system can be designed for four quadrant operation. commutation of SCRs in a cycloconverter is natural but it requires a large number of thyristors and its control circuit The cycloconverter has a low input power is more complex. Such drives are normally used in very large power applications. But the cost and complexity of power and control circuits make them uncompetitive with other classes of drives. Voltage source inverters are generally clasified into two types:

- a) Square wave inverters

- b) Pulse width modulated (PWM) inverters

Square wave inverter drive utilizes a controlled rectifier to transform the incoming a.c. voltage to variable D.C. voltage. This is followed by an inverter section. The frequency of the output is controlled by

sequentially switching the transistors or thyristors in the inverter section in six discrete steps. Square wave inverter has a number of undesirable effects such as additional harmonic power losses and torque pulsations in the motors. It requires large amount of d.c. filter components. Which consists of the d.c. inductors and filter capacitors. The commutating capacitor in the VSI is usually charged by the d.c. link voltage, hence commutating capability decreases as the D.C. voltage decreases [16]. This type of inverter causes increased commutation losses and requires complex firing control circuitry.

The PWM drive generally utilizes, a diode rectifier to provide a constant D.C. voltage. The inverter section in this type of drive therefore controls both voltage and frequency. In PWM inverters, thyristors are switched on and off many times in each half cycle to generate variable voltage output. There are many techniques to achieve PWM. But sinusoidal PWM techniques [1] is most common. This technique reduces the harmonic losses to a great extent but it suffers from low inverter efficiency. Since a PWM inverter presents a closer simulation of sine wave power to the motor, less power filter components are required [16]. However, the complex switching waveforms in the inverter require the most complex regulator and losses due to switching can be high.

The commutating circuitry increases the cost of the inverters. The PWM drive has near-unity power factor due to the diode rectifier input and constant patential d.c. link.

A current source inverter drive also uses a controlled rectifier to convert a.c. to variable patential d.c. The inverter section produces variable frequency six-step current and the voltage follows the current with commutation spikes due to thyristor firing. The current source inverter fed a.c. drive has the following favourable features [17, 18]:

- i) This drive has the ability to control the motor current which results in complete torque control.

- ii) Commutation losses are lower than in VSI drives

- iii) Regeneration is possible

- iv) The inverter can be designed with low speed SCRs.

- v) Fault current on the inverter side rises very slowly.

- vi) The CSI controller tends to maintain a higher level of efficiency than that in VSI drive.

However, against the above mentioned features, the CSI fed drives have the following draw backs:

i) The current controlling characteristic of the drive necessitates a large filter inductors due to the necessity of controlling the motor solely by current.

- ii) The frequency range of inverter is lower and it can not operate at no load condition.

- iii) The drive has instability problems and sluggish response at light loads and high speeds.

- iv) The commutation is dependent upon the machine subtransient inductance which adds large transient over voltages at machine terminals.

The line commutated inverter overcomes all the problems of forced commutated inverters (VSI or CSI) as well as cycloconverters. A line commutated inverter is obtained by operating an SCR bridge in continuous current mode with firing angle greater than 90°. The sequential commutation of SCRs is performed naturally with the help of terminal voltages of the synchronous machine connected on a.c. side of the inverter. The line commutated inverter requires reactive power for commutation. This reactive power is supplied by the synchronous machine operating at leading power factor. Some of the favourable characteristics features of LCI are [14,19]:

- i) Commutating components are not required. As a result inverter **cost** is reduced to a great extent.

- ii) Harmonics in the output voltage wave form are reduced.

- iii) The triggering circuit requirements are comparatively simple.

- iv) Commutation losses are reduced.

- v) Line commutated inverter fed synchronous motor can be efficiently used as a variable frequency source to drive other a.c. motors.

- vi) LCI drives provide stable operation within the desired range of speed.

Against the above mentioned features, line commutated inverter fed synchronous motor drive has the following limitations [17,20]:

- i) It is not self starting. Extra starting arrangements are required to start the synchronous motor which increase the cost of the drive.

- ii) Commutation failure occurs at lower speed and the range of speed is therefore limited by this factor.

- iii) Since the sinusoidal emf of the synchronous machine is available at the a.c. terminals of the inverter for commutation of inverter thyristors, the inverter must be current fed and this necessitates the use of large link inductance.

- iv) The inverter can not recover after a commutation failure.

In the present work, a line commutated inverter has been proposed to realize the commutatorless D.C. series motor drive.

The commutatorless D.C. motor system uses a conventional synchronous motor which is interfaced to

a d.c. power supply by a variable frequency thyristorized inverter. The inverter switches the power to the appropriate stator windings of the machine. The inverter firing is controlled by the synchronizing signals obtained from an induced voltage sensor or a rotor position sensor. Induced voltage sensor uses a step down transformer for sensing the terminal voltage of the synchronous motor and it is simple as compared to rotor position sensor. The combination of sensor and inverter replaces the commutator of conventional d.c. motor and inverter frequency is a function of the motor speed. Thus the synchronous motor itself is the controller, much the same as a conventional d.c. motor.

Starting of commutatorless motor is another important factor to be considered. Commutatorless motor is unable to start from standstill condition. Extra starting arrangements are necessary to start the motor from standstill. This is the major drawback of LCI fed synchronous motor drives. Several methods are known for starting purpose. Some of these techniques [20] reported so far are as follows:

- i) Starting with an auxiliary thyristor in parallel with D.C. link inductor.

- ii) Starting without an auxiliary thyristor

- iii) Starting using an auxiliary motor.

Since the combination of LCI and synchronous motor constitute a commutatorless d.c. motor, hence three types of CLM can be realized by placing the field winding in different positions.

- i) Separately excited commutatorless d.c. motor

- ii) Shunt commutatorless d.c. motor

- iii) Series commutatorless d.c. motor

The commutatorless motor of induced voltage commutation type is very practical due to its simple structures. However, in case of shunt type CLM the commutation angle increases with the load current resulting in the decrease of margin angle (8) which often causes commutation failure [13]. This type of commutatorless motor has limited overload capacity as compared to the series type CLM [5]. series type CLM, the field winding of the synchronous machis connected in series with the d.c. link. Commutatorless D.C. series motor exhibits the characteristics [5,7] similar to that of a conventional d.c. series motor. In case of series type CLM using natural commutation, overlap angle (u) and commutation margin angle (8) are independent of both the load current and machine speed provided the magnetic saturation and armature reaction are negligible [4,5,7]. For this reason, it operates without commutation problems even in overload condition

In the present work, microprocessor based commutatorless d.c. series motor has been designed, fabricated and tested.

## 1.2 LITERATURE SURVEY

A large volume of research has been done on the shunt type commutatorless d.c. motors. From literature review, it is found that not much work has so far been reported in the field of series commutatorless d.c. motor.

Kenji Watanabe, Katsuji Oyamori and Noriaki Sato [4] have discussed the effect of magnetic saturation on the operating characteristics of series commutatorless motor. They have also verified that operating region of the CLM can be widened by attaching compensating winding.

F.C.Brockhurst [5] has sestablished performance equation for D.C. commutatorless motors using salient-pole synchronous-type machines in terms of machine inductances. Speed independent equations for commutation angle, commutating current, critical angle, safety angle, torques and instantaneous damper currents have been developed G.H. Pfitscher [21] has developed a microprocessor based scheme that generates the necessary synchronization logical signals for three phase static power converter control systems. The problem of detecting the phase-to-phase voltage zero-crossing in presence of noise generated by thyristor commutations in constant and in variable frequency

voltage and from the circuit configuration of the system. The firing angle may take any value from  $0^{\circ}$  to  $180^{\circ}$ . Ajay Kumar, R. Anbarsu and B.P.Singh [7] have analyzed the steady state performance of series commutatorless D.C. motor using induced voltage sensor. It has been experimentally verified that overlap angle, power factor and armature reaction angle are independent of frequency and load current.

H. Naito, K. Iwamoto and Funio Harashima [12] has determined analytically and verified the dynamic characteristics of lead angle controlled commutatorless motor and have pointed out the instability problems, associated with this type of control method. Tokeda, S.Monimoto and T.Hirasa [13] have discussed the generalized analysis for steady state characteristics of D.C. commutaturless motor. The variation of commutation angle, shift angle, demagnetization due to armature reaction, safety margin angle, average torque and speed with mean input current are examined quantitatively for cylindrical and salient pole motors.

M.V.S.S. Ranganadhachari, B.P. Singh, R. Anbarasu and R. Arockiasamy [14] have presented experimental investigation on line commutated inverter synchronous machine as a variable frequency source. It has been verified experimentally that inverter synchronous machine scheme works quitesatisfactorily as a variable frequency source for both

static and dynamic loads. Chandrasekhar Namuduri and P.C. Sen [25] have described a digital simulation method for the self controlled synchronous motor in time domain. The effects of damper windings and saliency on the torque, and voltage and current waveforms are also studied using digital simulation technique whon the machine is operated from a voltage power inverter and a current source inverter. Performance of the synchronous machine with nonsinusoidal voltages and currents is simulated under both steady state and transient conditions.

In 1983, J. Davoine, R. Perret and Hoang-Le-Huy [1] have discussed the microcomputer controlled operation of self-controlled synchronous motor employing terminal voltage sensing technique. In this scheme the standstill position of rotor is computed by microcomputer by analysing and sampling the induced voltage in the stator when a step voltage is applied to the field winding. The microcomputer also takes care of starting the motor from standstill by using auxiliary thyristor in parallel of D.C. link inductor.

# 1.3 SCOPE OF PRESENT WORK

A salient type synchronous motor fed from a machine voltage commutated inverter is considered for realizing a series type commutatorless D.C. motor. Three phase uncontrolled rectifier, thyristorized line commutated inverter

and a simple microprocessor based firing control scheme using less hardware components are designed, fabricated and experimentally tested.

An interfacing circuit of the programmable interval timer 8253A is designed and fabricated for using in the present scheme. A look up table method for displaying speed in the address field without any extra hardware is developed. The system software is implemented and tested.

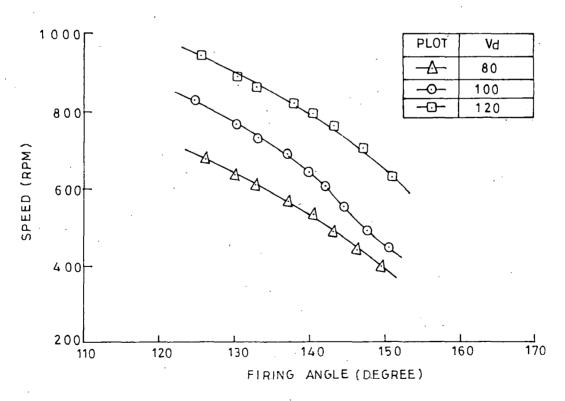

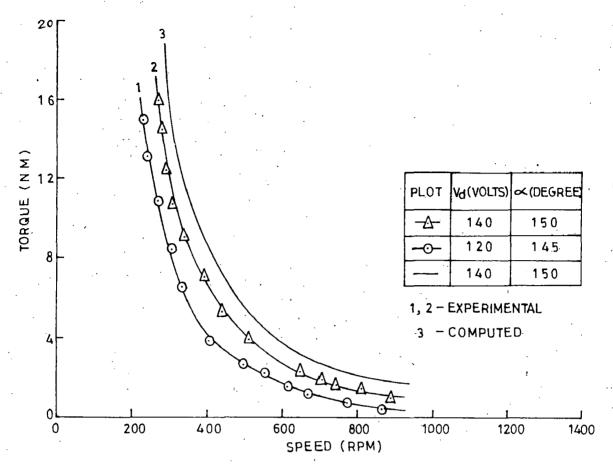

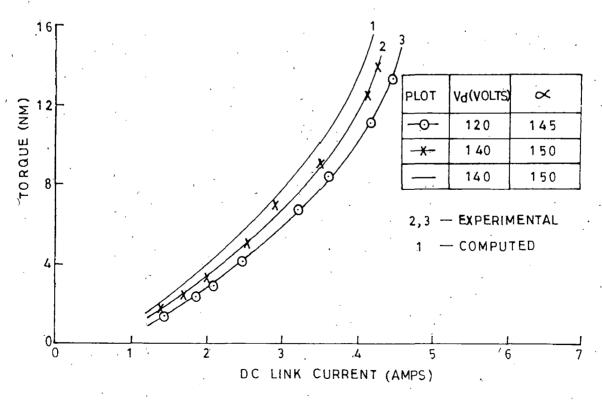

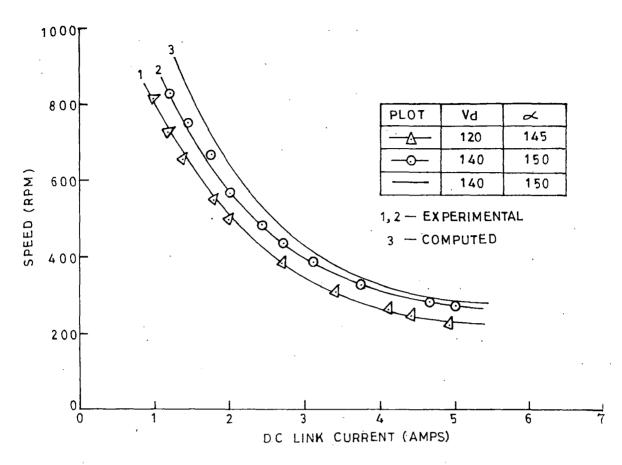

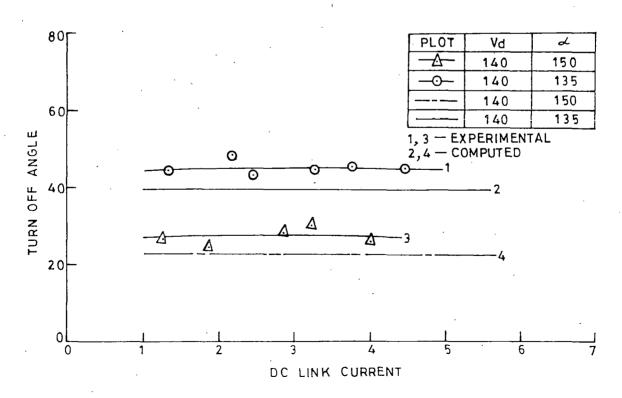

The steady state analysis of the commutatorless D.C. series motor is developed by using equivalent circuit and vector diagram of the drive. The steady state performance characteristics of the drive are computed such as machine terminal voltage, machine current, power factor, commutation angle, safety margin angle, active and reactive power, speed and torque by varying D.C. link current at different D.C. link voltage and firing angle using DEC-2050 mainframe digital computer.

The performance of the line commutated inverter is investigated. The no load test is carried out on the SCLM system by varying D.C. link voltage with constant firing angle or varying firing angle with constant D.C. link voltage. The load test is performed on the drive at different D.C. link voltage and firing angle and the steady state performance of the drive is obtained experimentally. The experimental results are compared with the theoretical

ones and the discrepancies between the two are discussed.

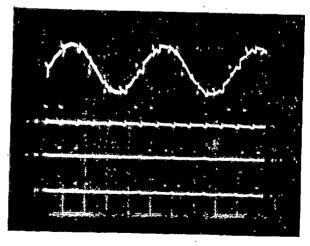

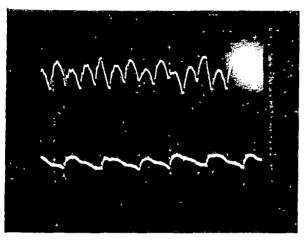

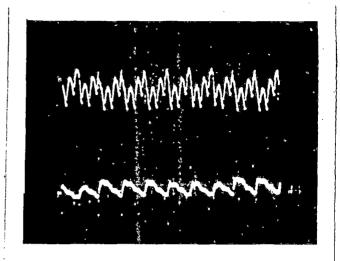

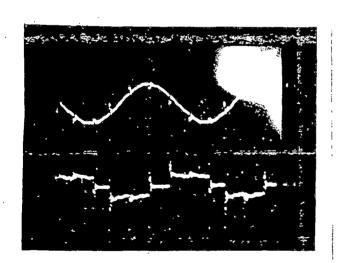

The oscillograms of machine terminal voltage, machine current, D.C. link voltage, D.C. link current at no load and load conditions and waveshapes at different points of the firing circuit are recorded and discussed.

## Outline of Chapters:

In chapter II, the complete hardware of the present scheme is discussed in detail. The design of power circuit, microprocessor based firing control circuit using less hardware components and pulse amplifier circuit are presented in this chapter. The interfacing technique of the programmable interval timer 8253A is also discussed.

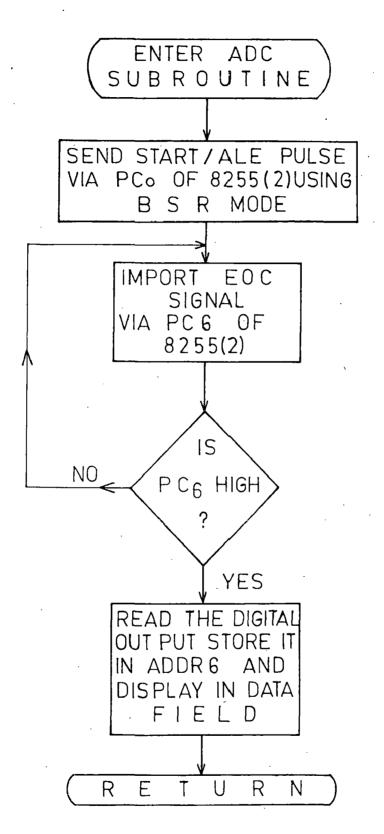

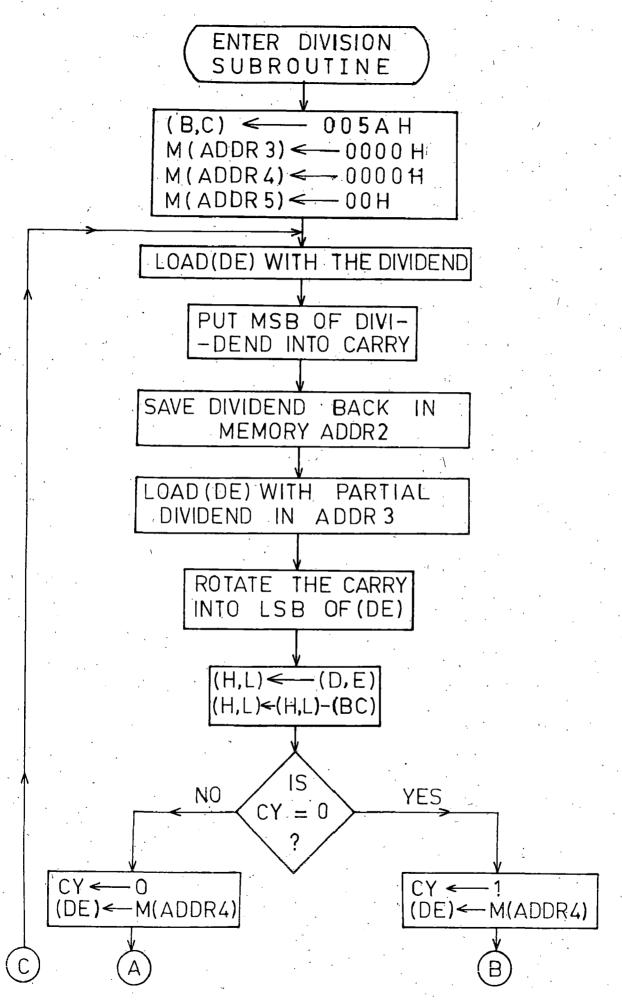

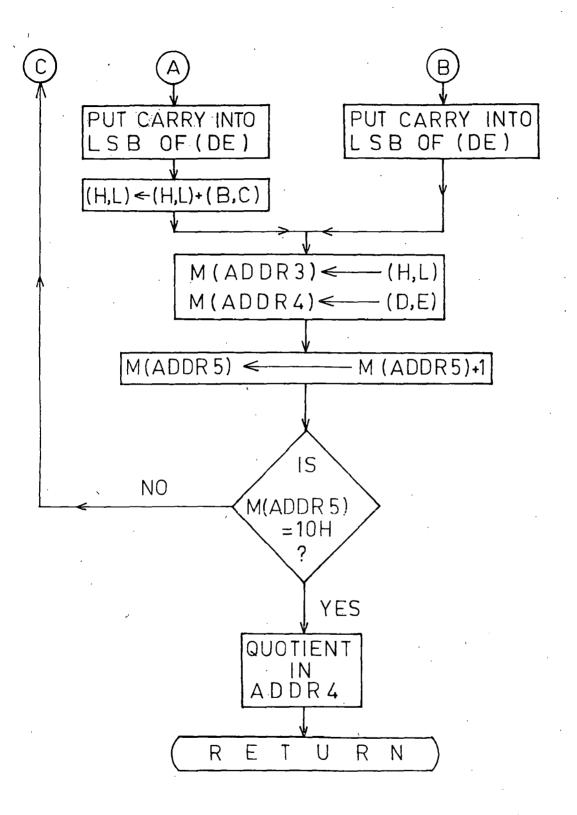

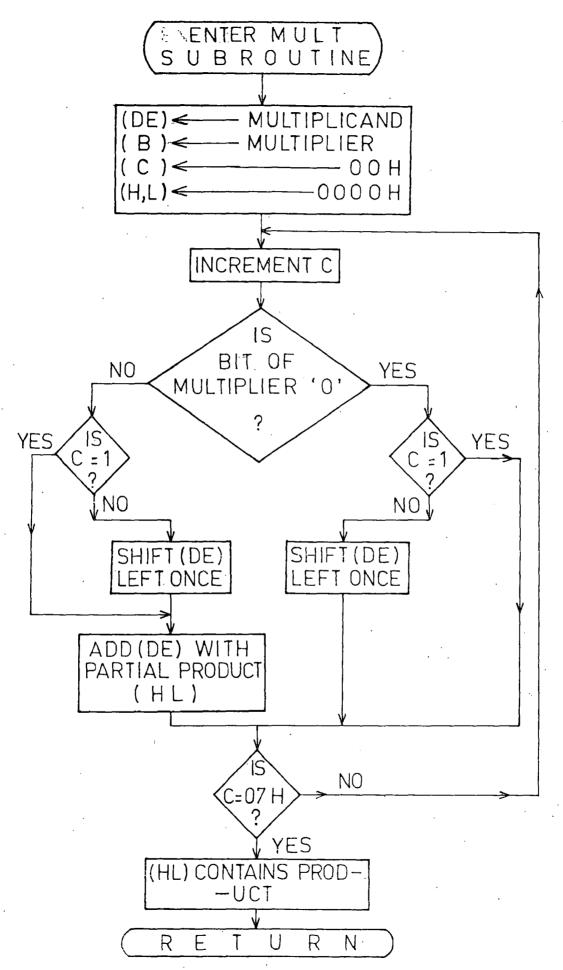

The implementation of software and flowcharts of the commutatorless D.C. series motor is discussed in chapter III. The various subroutines used in conjunction with the main program such as ADC subroutine, DIVISION subroutine, MULT subroutine, IR<sub>0</sub> interrupt subroutine, IR<sub>2</sub> interrupt subroutine, IR<sub>4</sub> interrupt subroutine and SPEED subroutine are also developed in this chapter.

Chapter IV deals with the steady state analysis of the drive. The mathematical equations for steady state analysis are obtained by using equivalent circuit and vector diagram of the SCLM system. The results of experimental investigation of the fabricated system are

presented in chapter V. In the last chapter, main conclusions and suggestions for further works are discussed.

The ratings of the machine, pin details and connection diagrams of different IC chip, assembly language program for firing control of LCI and fortran program for steady state analysis of the drive are given in Appendices.

## DESCRIPTION OF THE SYSTEM

## 2.1 GENERAL

The complete scheme for realizing a commutatorless D.C. series motor is described in this chapter. A microprocessor based LCI firing angle control scheme philosophy is discussed in depth together with the hardware requirements. The synchronizing signal is generated by sensing two line to line voltages from synchronous machine terminals. This signal is used as an interrupt and at the same time to store the frequency information of the machine voltage. The interfacing technique of the programmable interval timer 8253A is also given in this chapter.

## 2.2 PRINCIPLE OF OPERATION

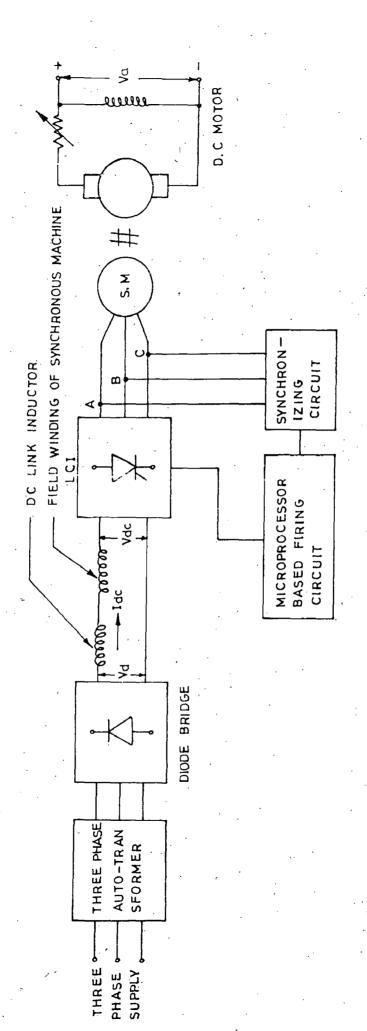

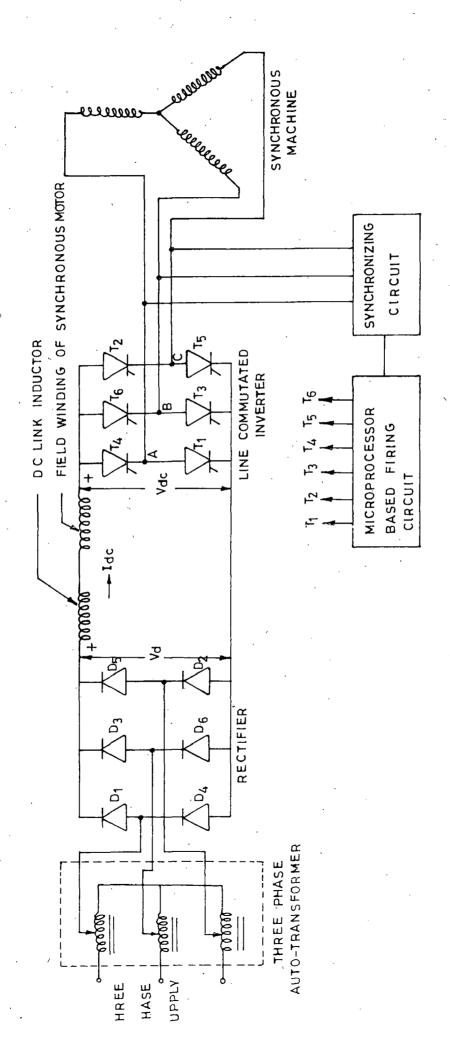

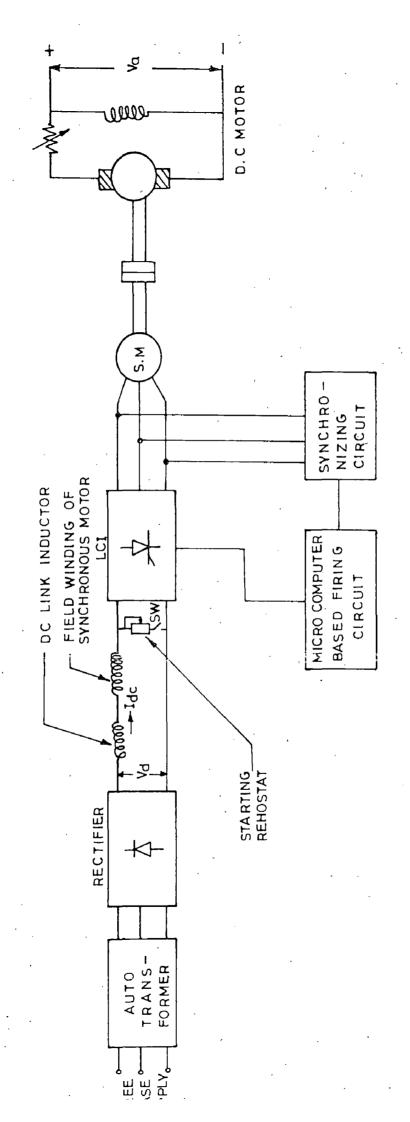

The block diagram of the commutatorless d.c. series motor is shown in Fig. 2.1. It basically consists of an autotransformer, an uncontrolled rectifier bridge, d.c. link smoothing inductor, series field winding, line commutated inverter and a 3-phase synchronous machine. The uncontrolled rectifier, together with the smoothing inductor, acts as a d.c. current source. Its output  $I_{\rm dc}$  is impressed at the d.c. input of the machine voltage commutated inverter.

FIG. 2-1 - BLOCK DIAGRAM OF COMMUTATORLESS DC SERIES MOTOR

The synchronous machine is interfaced with a d.c. power supply by a variable frequency static inverter which switches the power to the appropriate stator windings of the synchronous machine. The excitation winding of the synchronous motor is connected in series to the input of the inverter and therefore the excitation current is directly proportional to the load current like a conventional d.c. series motor.

A synchronizing signal of  $60^{\circ}$  pulse width of the machine voltage is generated from the terminal voltage of the synchronous machine. This synchronizing signal is in putted to the port C of 8255, Gate of TM2 of PIT 8253A(1) and IRO interrupt pin of PIC 8259A for generating firing pulses for the inverter thyristors. The firing angle of line commutated inverter is always kept between 90° to 180° and is approximately equal to the power factor of the synchronous machine. The triggering angle of the inverter can be adjusted at any valve between  $90^{\circ}$  to  $180^{\circ}$  by changing ADC output. In this scheme, the terminal voltage of the synchronous machine commutate the thyristor of LCI with the help of firing pulses in sequence provided by the trigger circuit. The three-phase autotransformer provides variable a.c. input voltage to the uncontrolled bridge rectifier to produce variable d.c. output voltage. trolled d.c. source supplies active power required for the synchronous machine.

The speed of commutatorless D.C. series motor may be expressed as [7]

$$N = \frac{V_{d} - I_{dc} R_{dc}}{K_{N} I_{dc} Cos \beta}$$

where  $V_d$  = dc link voltage,  $I_{dc}$  = dc link current and  $\beta$  = Lead angle=  $\pi$  -  $\alpha$

The frequency of the inverter output is controllable and is given by.

$$= \frac{P}{120} \qquad \frac{V_d - I_{dc} R_{dc}}{K_N I_{dc} Cos\beta}$$

Since the combination of inverter and synchronous motor with field winding connected in series to the d.c. link works as a series commutatorless D.C. motor, its speed can be varied in the following ways:

- I) Varying the input d.c. voltage to the inverter like a d.c. series motor

- II) Changing the trigger angle of the line commutated inverter just like the speed change of a conventional d.c. series motor by shifting the brush position.

## 2.3 SYSTEM DESCRIPTION

The schematic diagram of the commutatorless D.C. series motor using induced voltage commutation along with the voltage sensor for synchronization is shown in

SERIES MOTOR DIAGRAM OF COMMUTATORLESS DC FIG. 2.2-SCHEMATIC

Fig. 2.2. This type of series motor makes use of conventional three-phase synchronous machine. The well known equation relating commutation lead angle ( $\beta$ ), commutation overlap angle ( $\mu$ ) and input d.c. link current is given by

$$\cos (\beta - \mu) - \cos \beta = \frac{\sqrt{2}}{3} \frac{I_{dc} X_{c}}{E_{s_{v}}}$$

where  $X_C$  = Commutating reactance.

For commutationless d.c. series motor the resultant flux is proportional to input d.c. current ( $I_{dc}$ ) of the inverter and therefore internal induced voltage  $E_{sy}$  is proportional to the product of  $I_{dc}$  and N . Hence the above equation can be rewritten as

Cos (

$$\beta - \mu$$

) - Cos  $\beta$  =  $K_s L_c$

Where K<sub>S</sub> is a constant. This equation indicates that commutation overlap angle varies with firing angle and commutation inductance which is fixed by the design of the synchronous machine and it is independent of input d.c. current and motor speed. This is an important feature of the commutatorless d.c. series motor. For better understanding of the system operation, the major components are discussed briefly as under:

# (I) Uncontrolled Diode Bridge:

The function of the diode bridge is to rectify the fixed frequency a.c. supply to a d.c. voltage and supply the

in the comparison of the comparison of the engineer

It is a three phase full wave diode bridge rectifier and its output is controlled by using an auto transformer at the a.c. supply. The active power requirements of the synchronous machine is met by this controlled d.c. source.

## (II) D.C. Link Inductor:

The function of the d.c. link inductor is to suppress the harmonics contained in the output of the bridge rectifier. The combination of uncontrolled rectifier and D.C. link inductor acts as a current source. Its output is fed to the d.c. input of the line commutated inverter and excitation winding of the synchronous motor. For this purpose, choke is required to be of large inductance and keep the current continuous in the circuit.

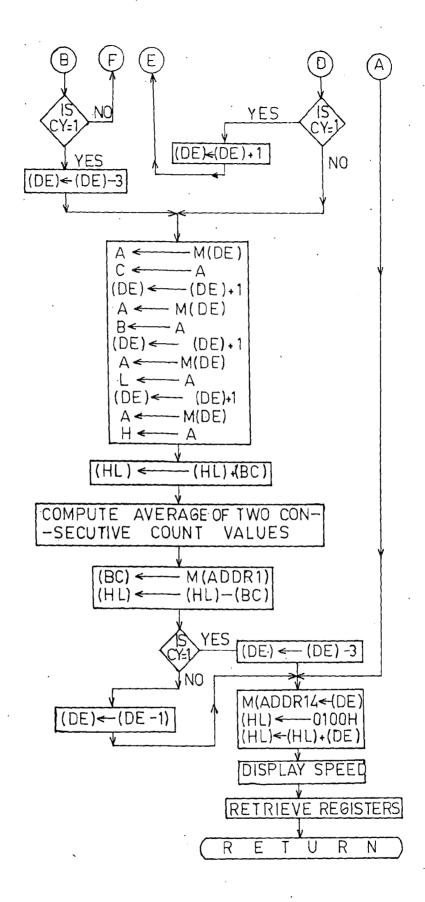

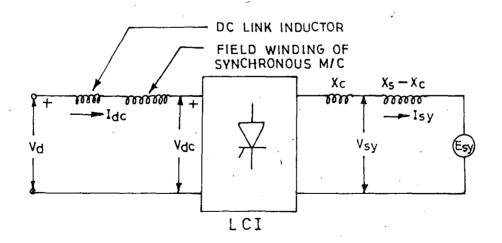

## (III) Line Commutated Inverter:

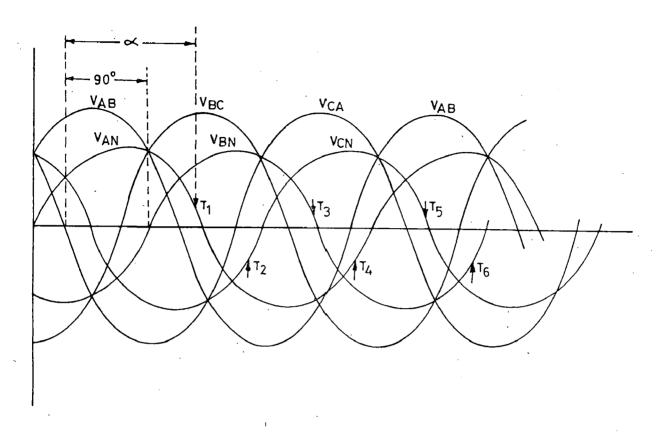

It is a simple three-phase thyristorized inverter bridge. The function of the inverter is to convert the d.c. voltage into a.c. voltage of variable amplitude and frequency. The commutation of inverter thyristor is performed by the voltage induced in the stator winding of the synchronous machine, which is seen by the inverter as a three-phase a.c. source of terminal voltage  $V_{\rm Sy}$ . For clear understanding of the line commutated inverter, the relation-ship between line to line voltages and line to neutral voltages of synchronous machine terminal along with firing instants

FIG. 2-3-RELATIONSHIP BETWEEN LINE TO LINE AND LINE

TO NEUTRAL VOLTAGE ALONG WITH INSTANT OF FIRING

TABLE 2.1

| CONDUCTION                  | o°— 60° | 60°-120° | 120°-180° | 180~240 | 240°-300° | 300°—360° |

|-----------------------------|---------|----------|-----------|---------|-----------|-----------|

| FIRING<br>SEQUENCE          | 1       | 2        | 3         | - 4     | 5         | . 6       |

| THYRISTOR PAIR TO BE FIRIED | 6,1     | 1,2      | 2,3       | 3,4     | 4,5       | 5,6       |

of the thyristors is shown in Fig. 2.3.

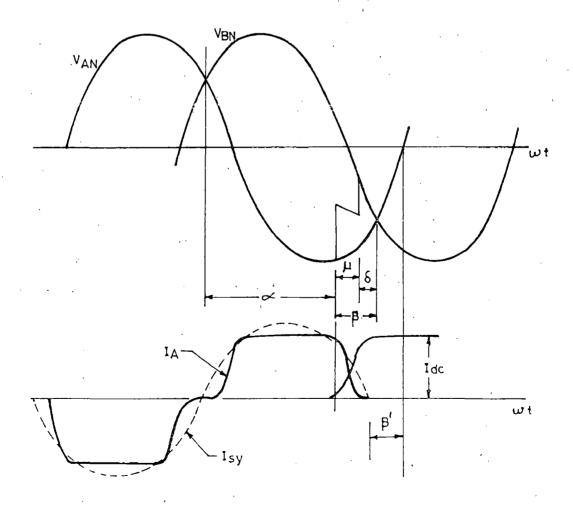

The thyristors  $T_1$ ,  $T_3$ ,  $T_5$  are called positive group since they are turned on when the machine terminal voltages are positive similarly the thyristors are called negative group SCRs. Since they are triggered when the machine voltages are negative. The firing angle of the inverter is always greater than  $90^{\circ}$  and measured from the instant of crossing point of two phase voltages as shown in Fig. 2.3. The firing angle for the thyristor measured from the crossing point of positive going phase voltage  $V_{\mbox{AN}}$  and negative going phase voltage  $V_{\mbox{CN}}.$ zero crossing instant of positive going line to line voltage  ${

m V}_{

m AC}$  coincides with the crossing point of  ${

m V}_{

m AN}$  and  ${

m V}_{

m CN}$ . as reference for measuring firing angle of the thyristor  ${

m T_1}$  and similarly for other thyristors. During normal operation, always two thyristors one from positive group SCR and another from negative group SCR will remain in conduction. Thyristors are triggered at 60° interval of terminal voltage frequency. Each thyristor conducts the positive current for 120° and negative current for 120° and the frequency of the current is same as that of machine terminal voltage. In case of line commutated inverter, machine current always leads the corresponding phase voltage. Let us consider the commutation phenomenon from  $T_1$  to  $T_3$  to make clear about the induced voltage commutation.

thyristor  $T_3$  from positive group is fired, thyristor  $T_1$  gets reverse biased by the voltage,  $V_{AB} = V_{AN} - V_{BN}$  and current is commutated from  $T_1$  to  $T_3$ .

The presence of large source inductance many result in an appreciable modification in the process of commutating current from one thyristor to the other. When thyristor becomes turn off or turn on, current can not decay to zero or increase to a certain valve instantaneously due to presence of inductance. So in the process of commutation both incoming and outpgoing thyristor remain in conduction simultaneously for some moment. The period during which both thyristor remain in conduction is known as overlap period. The firing angle of the inverter is limited to a valve such that the angle  $o = (\beta - \mu)$  is enough for proper commutation. Angle ( $\pi$  -0) is referred to as the extinction angle of the inverter. The angle b is known as Turn off angle or safety margin angle. The firing is adjusted to a suitable value and normally keep constant through out the operation. The inverter normally operates at a constant margin angle.

The d.c. output voltage of a fully controlled converter is related to firing angle  $\alpha$  by the following equation:

$$V_{dc} = \frac{3\sqrt{6} V}{\pi} \cos \alpha = V_{do} \cos \alpha$$

where V = per phase a.c. voltage

For firing angle between  $0^{\circ}$  to  $90^{\circ}$ , average d.c. voltage across the bridge is positive. If the firing angle  $\alpha$  for the line commutated inverter is more than  $90^{\circ}$ , the d.c. voltage across the bridge will be negative. Thus, if a D.C. voltage source is connected across the inverter bridge in proper polarity and the d.c. voltage induced across the inverter bridge is less than the applied D.C. source, it will feed power to the A.C. system through the controlled circuit. For LCI, the waveform for the alternating line current closely resembles a rectangular wave. The output power factor angle will be approximately  $(\beta - \mu/2)$  leading and the output power factor will be close to  $Cos(\beta - \mu/2)$  or  $-Cos(\alpha + \mu/2)$ .

# (IV) Synchronous Motor:

The synchronous motor is a conventional one and it is operated as a variable speed motor. The field winding of the machine is connected in series to the input of the LCI for realizing commutatorless D.C. series motor. The motor runs at synchronous speed corresponding to the frequency of the motor terminal voltage. The inverter a.c. terminals are connected to the synchronous machine and therefore, back emf of synchronous motor is available for natural commutation of the inverter thyristors. In the present scheme, the inverter switching is essentially controlled by the synchronous motor itself and the inverter frequency is a function of the motor speed. In series CLM, power factor

is independent of load and speed. It only depends on the firing angle of the line commutated inverter. The torque developed by the synchronous motor is directly proportional to the square of the d.c. link current for constant firing angle operation just like a conventional d.c. series motor.

## (V) Synchronizing Circuit:

Synchronizing Circuit consists of step down transformer, comparator, switching transistor and AND gate. Synchronizing signal is of 60° pulse width of the machine frequency and derived from two line to line terminal voltages. The signal is fed to microcomputer for firing pulse generation in proper sequence and trigger angle control. The details of synchronizing circuit has been given later on.

# (VI) Microprocessor Based Firing Circuit:

The synchronizing signal derived from the machine terminal voltages is fed to microcomputer for firing control of the inverter thyristors in proper sequence. This scheme uses less hardware components and overcomes most of the drawbacks of the analog firing scheme. The details of microprocessor based firing circuit has been discussed later on. The details of conduction duration, firing sequence and conducting thyristors are shown in Table 2.1.

# 2.3.1 Design of Power Circuit:

The power circuit is designed to meet the require-

ments of synchronous machine whose ratings are given in Appendix-I. The power circuit for the proposed scheme consists of the following parts:

- i) Three phase diode bridge

- ii) Three phase fully controlled line commutated inverter

- iii) D.C. link inductor

#### CHOICE OF RATINGS OF DIODES

The voltage rating of the diodes of the uncontrolled bridge have to be selected with the consideration of the peak inverse voltage appearing across the devices, this in turn depends upon the maximum three phase input line voltage to the bridge. For a three phase bridge, the ratio of peak inverse voltage to line to neutral voltage is calculated as |26|

$$\begin{aligned} \mathbf{V}_{\mathrm{PIV}} &= \frac{\pi}{3} \ \mathbf{V}_{\mathrm{do}} \\ \text{where} \ \mathbf{V}_{\mathrm{do}} &= \frac{3}{\pi} \frac{2}{} \ \mathbf{V}_{\mathrm{L-L}} &= \frac{3-2}{\pi} \cdot \sqrt{3} \cdot \mathbf{V}_{\mathrm{LN}} \\ &= \frac{3-6}{\pi} \ \mathbf{V}_{\mathrm{LN}} \end{aligned}$$

Therefore

$$\frac{V_{PIV}}{V_{LN}} = \frac{\pi}{3} \times \frac{3.76}{\pi} = 2.45$$

For input line voltage 400V at 50Hz, peak in  $\mathbf{v}$ erse voltage across the diode is

$$V_{PIV} = 2.45 V_{LN} = 2.45 x \frac{400}{\sqrt{3}} = 566 \text{ volts}$$

A safety factor of 2 is allowed so that the diode can easily take reasonable over voltage.

The diode bridge has to supply 7 KW for the proposed synchronous machine

$$V_d I_{dc} = 3 V_{sy} I_{sy} Cos \beta' = 7000$$

$$I_{dc} = \frac{7000}{V_d}$$

The output average d.c. voltage of a full wave diode bridge is given by

$$V_{d} = \frac{3 \int_{6} V}{\pi}$$

where V is the per phase rms input voltage. For 400V, 50Hz input voltage, the output of diode bridge becomes

$$V_d$$

=  $\frac{3\sqrt{6}}{\pi} \times \frac{400}{\sqrt{3}}$  = 540 Volts

i.e.  $I_{dc} = \frac{7000}{540}$  = 12.96  $\approx$  13 Amp.

The current through the diode is given by

$$I_d = \frac{12.96}{3} = 4.32 \approx 5 \text{ Amp.}$$

Allowing a safety factor of 2, the diode current rating can be taken as

$$I_{d} = 5 \times 2 = 10 \text{ Amp}.$$

So the diode of rating 12 Amp, 1200 PIV can be selected to meet the requirements.

#### SELECTION OF RATINGS OF THYRISTOR

The following factors have to be considered for selecting the ratings of SCR.

- Maximum PIV appearing across thyristor

- ii) Power circuit configuration

- iii) Conduction angle of individual thyristor

- Current wave form iv)

- v) Average current

For a three phase bridge, the ratio of PIV and line to neutral voltage is given by

$$\frac{E_{PIV}}{E_{IN}} = 2.45$$

$$\frac{E_{PIV}}{E_{LN}} = 2.45$$

$E_{PIV} = 2.45 \times E_{LN} = 2.45 \times \frac{400}{\sqrt{3}}$

$= 566 \text{ V}$

Taking a safety factor of 2, a 1200 PIV SCR is required.

For 7KW, 400V, 0.8 p.f synchronous motor, stator current is

$$I_A = \frac{7000}{\sqrt{3} \times 400 \times 0.8} = 12.63 \approx 12 \text{ Amp.}$$

Since each SCR conducts for 120° in each cycle, current through SCR is

$$I_T = \frac{12.63}{3} = 4.2098 \approx 5 \text{ Amp.}$$

Allowing a safety factor of 2, current rating of thyristor can be taken as  $5 \times 2 = 10$  Amp.

So thyristor of Rating 12 Amp, 1200 PIV can be selected for this purpose. Each thyristor should be provided with over current, over voltage,  $\frac{di}{dt}$  and  $\frac{dv}{dt}$  protections. Over current protection can be made by connecting a fuse or a circuit breaker in series with the thyristor. Over voltage protection can be provided by using the thyrector diode across the thyristor. A voltage suppression network, commonly called a snubber circuit, consists of a series-connected resistor and a capacitor connected across the SCR, is used for protection against large  $\frac{dv}{dt} \cdot \frac{di}{dt}$  protection can be provided by placing a inductor having very low inductance in series with the thyristor.

# 2.3.2 Programmable Peripheral Devices:

Peripheral devices are required for organizing a microcomputer system. These components are organized around a

common communication path called system bus which carry bits

between the microprocessor and peripheral devices. The

present microprocessor based control system makes use of

8253A interval timer, 8255A peripheral interface and 8259A

interrupt controller. These are widely used general purpose

programmable peripheral devices and completely compatible

with any microprocessor. For better understanding and programming of these peripheral devices, a brief description

is given below:

### 8253A PROGRAMMABLE INTERVAL TIMER

Intel 8253A is a very popular device specially designed for microcomputer applications which require timing and counting operation. This device can be used for application such as an event counter, a real time clock, a programmable one shat, a square wave generator and a complex wave form generator. The 8253A has three identical and independent 16 bit counters which may be operated in various modes by proper software programming. The counter can count either in binary or BCD and in addition a count can be read by the microprocessor while the counting is going on. Each counter is a negative edge-triggered down counter. Each counter has two input signals-clock (CLK) and GATE and one output signal - OUT.

Address line  $A_0$  and  $A_1$  of the microprocessor are connected to lines  $A_0$  and  $A_1$  of the 8253 and  $\overline{CS}$  is tied to a decoded address.  $A_0$  and  $A_1$  input signals, in conjunction with the status of RD and WR inputs, control the selection of counter or the control word register.

| CS  | RD  | ·WR | A <sub>1</sub> | $^{A}O$    |                    |

|-----|-----|-----|----------------|------------|--------------------|

| Q   | 1   | 0   | 0 .            | <b>3</b> , | LOAD TMO           |

| 0   | 1   | 0   | 0              | 1          | LOAD TM1.          |

| Ö   | 1   | 0 . | 1              | 0          | LOAD TM2           |

| D   | 1   | 0   | 1 .            | 1          | DATA BUS - CONTROL |

| p   | 0   | 1   | 0              | 0          | READ TMO           |

| Þ   | 0 . | . 1 | 0              | 4          | READ TM1           |

| D D | 0   | 1 1 | 1              | 0          | READ TM2           |

| 0 . | 0 | 1 | 1          | 1            | DATA BUS  | TRISTATE |

|-----|---|---|------------|--------------|-----------|----------|

| 1.  | x | x | x          | x            | DATA BUS  | TRISTATE |

| 0   | 1 | 1 | x          | x            | DATA BUS  | TRISTATE |

| 0   | 0 | Ο | ` <b>x</b> | $\mathbf{x}$ | ILLEGEL C | NOITION  |

Each counter is initialized by writing a proper control word in the control word register. The control word includes the following important features:

- i) Mode of operation

- ii) 16 bit or 8 bit data to be read or write

- iii) 16 bit binary counter or 4 digit BCD counter operation.

The control word format for choosing the above features is given below:

| <sup>D</sup> 7 | D <sub>6</sub> | D <sub>5</sub> | $D_{L_4}$ | D <sub>3</sub> | $D_2$ | $D_1$ | $D_{O}$ |

|----------------|----------------|----------------|-----------|----------------|-------|-------|---------|

| SC1            | SCO            | RL1            | RL2       | М2             | М1    | MO    | BCD     |

| SC1 | SCO |         |         |    |

|-----|-----|---------|---------|----|

| 0   | 0   | Select  | counter | 0  |

| 0   | 1   | Select  | counter | 1  |

| 1   | Ò   | Select  | counter | 2  |

| . 1 | 1   | Illegel | conditi | on |

| RL1 | RLO | · ·                                     |

|-----|-----|-----------------------------------------|

| 0 . | 0   | Counter latching operation              |

| 0   | 1   | Read/load least significant byte only   |

| 1   | 0   | Read/load most significant byte only    |

| 1   | 1   | Read/load least significant byte first, |

|     |     | then the most significant byte.         |

| M <sub>2</sub> | $M_1$ | $^{\mathrm{M}}$ O |        |   |

|----------------|-------|-------------------|--------|---|

| Ο.             | 0     | 0                 | Mode   | 0 |

| 0              | 0     | 1                 | Mode   | 1 |

| x`             | 1     | 0                 | · Mode | 2 |

| x              | 1     | 1                 | Mode   | 3 |

| 1 .            | 0     | 0                 | Mode   | 4 |

| 1              | 0     | 1                 | Mode   | 5 |

### BCD

- 0 16 bit binary counting

- 1 4 digit BCD counting

## 8255A PROGRAMMABLE PERIPHERAL INTERFACE

Intel 8255A is a widely used general purpose programmable parallel input/output device. It can be programmed to transfer data under various conditions, from simple I/O to interrupt I/O. It is fexible, versatile, economical and can be used with almost any microprocessor. 8255A has three 8 bit parallel ports: PORTA, PORTB & PORTC. The eight bit of port C can be used as individual bits or be grouped in two 4 bit ports:  $C_{\rm upper}$  ( $C_{\rm upper}$ ) and  $C_{\rm lower}$  ( $C_{\rm L}$ ).

$\rm A_{O}$  and  $\rm A_{1}$  input signals, in conjunction with the RD and WR inputs, control the selection of one of the three ports or the control word register as follows:

| M <sub>2</sub> | $M_1$ | $^{\mathrm{M}}$ O |       |   |

|----------------|-------|-------------------|-------|---|

| Ο.             | 0     | 0                 | Mode  | 0 |

| 0              | 0     | 1                 | Mode  | 1 |

| x`             | 1     | 0                 | ·Mode | 2 |

| x              | 1     | 1                 | Mode  | 3 |

| 1 .            | 0     | 0                 | Mode  | 4 |

| 1              | 0     | 1                 | Mode  | 5 |

### BCD

- 0 16 bit binary counting

- 1 4 digit BCD counting

### 8255A PROGRAMMABLE PERIPHERAL INTERFACE

Intel 8255A is a widely used general purpose programmable parallel input/output device. It can be programmed to transfer data under various conditions, from simple I/O to interrupt I/O. It is fexible, versatile, economical and can be used with almost any microprocessor. 8255A has three 8 bit parallel ports: PORTA, PORTB & PORTC. The eight bit of port C can be used as individual bits or be grouped in two 4 bit ports:  $C_{\rm upper}$  ( $C_{\rm u}$ ) and  $C_{\rm lower}$  ( $C_{\rm L}$ ).

${\rm A}_0$  and  ${\rm A}_1$  input signals, in conjunction with the RD and WR inputs, control the selection of one of the three ports or the control word register as follows:

| CS | RD | WR         | <sup>A</sup> 1 | AO  | · ,                 |

|----|----|------------|----------------|-----|---------------------|

| 0  | 0  | <u>.</u> 1 | . 0            | 0   | PORTA → DATA BUS    |

| 0  | 0  | 1          | 0              | 1   | PORTB -> DATA BUS   |

| 0  | 0  | 1          | 1              | 0 . | PORTC → DATA BUS    |

| 0  | 1  | 0          | 0              | 0   | DATA BUS→ PORTA     |

| 0  | 1  | . O        | 0              | 1 ; | DATA BUS→ PORTB     |

| 0  | 1  | 0          | 1              | 0   | DATA BUS→ PORTC     |

| 0  | 1  | 0          | 1 `            | 1   | DATA BUS→ CONTROL   |

| 0  | x  | X          | x              | x   | DATA BUS→TRISTATE   |

| 0  | 0  | 1          | 1              | · 1 | ILLEGEL CONDITION   |

| 0  | 1  | 1          | x              | x   | DATA BUS - TRISTATE |

Each of the ports of 8255A can be initiatized in various mode by writing a proper control format in the control word register.

### 8259A PROGRAMMABLE INTERRUPT CONTROLLER

The intel 8259A programmable interrupt controller can manage eight interrupts according to the instruction written into its control registers. 8259A is designed to minimize the software and real time overhead in handling multi-level priority interrupts.

For programming, 8259A requires two types of command words. Initialization command words (ICWS) and operational command words (OCWS). The 8259A can be initialized with four ICWS; the first two are essential, and the other two are optional based on the modes being used. These words must be issued in a given sequence. Once initialized,

the 8259A can be set up to operate in various modes by using three different OCWS. These modes are:

- i) Fully rested mode

- ii) Rotating priority mode

- iii) Specified mask mode

- iv) Polled mode.

If the 8259Å is programmed in fully rested mode,  ${\rm IR}_{\rm O}$  has the highest priority and  ${\rm IR}_{\rm 7}$  has the lowest priority.

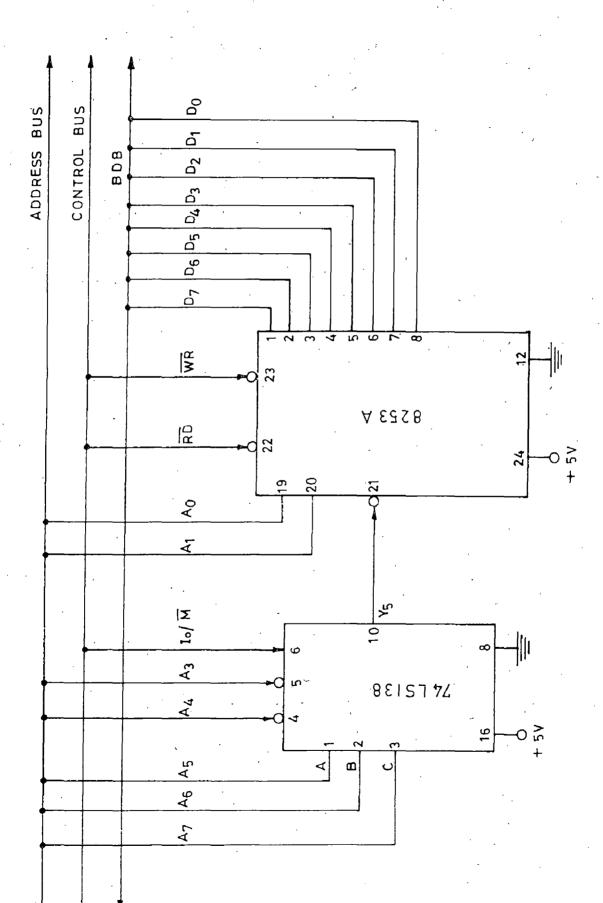

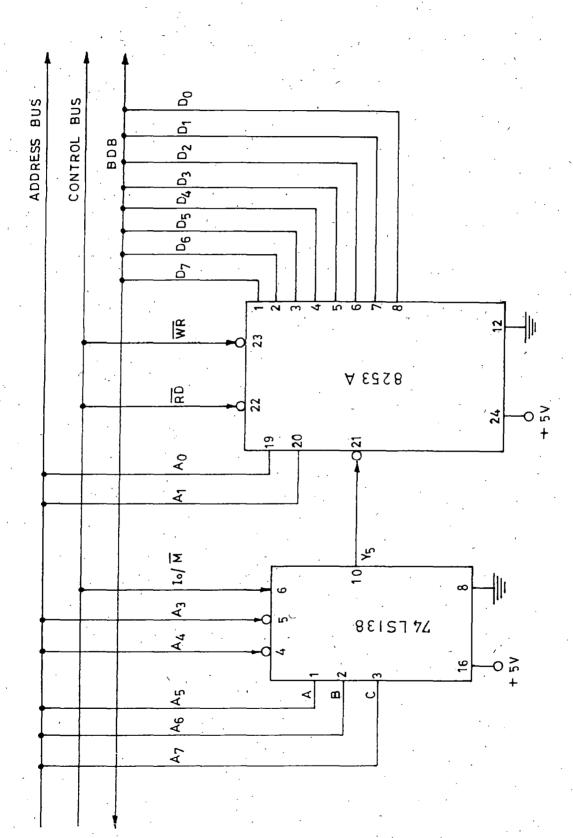

# 2.3.3 Interfacing of Programmable Interval Timer 8253A:

The present scheme requires four counters. In the vinytics VMC-85 trainer kit, two counters of 8253A are available to the user through connector  $J_1$ . An intel 8253A programmable interval timer is therefore interfaced with 8085A microprocessor using minimum hardware components to meet the requirements of the counters. The interfacing circuit is shown in Fig. 2.4. The  $\overline{\text{CS}}$  signal is derived from a 3 line to 8 line decoder 74L\$138. The  $A_3$ ,  $A_4$ ,  $A_5$ ,  $A_6$  &  $A_7$  address lines of 8085A are connected directly to the required pins of 74L\$138. The  $\overline{\text{RD}}$ ,  $\overline{\text{WR}}$  and  $\overline{\text{IO/M}}$  control signals are derived directly from the control bus of the microprocessor. The select inputs  $A_0$ ,  $A_1$  are connected to the  $A_0$ ,  $A_1$  address bus signals of the CPU. The ports addresses for the 8253A are selected as follows:

8253 A FIG. 2.4-INTERFACING OF PROGRAMMEABLE INTERVAL TIMER

OF PROGRAMMEABLE INTERVAL TIMER 8253 A FIG. 2-4-INTERFACING

| <sup>A</sup> 7 | <sup>A</sup> 6 | A <sub>5</sub> | $A_{L_{+}}$ | A <sub>3</sub> | $A_2$ | A <sub>1</sub> | $^{\rm A}{_{ m O}}$ |      |               |

|----------------|----------------|----------------|-------------|----------------|-------|----------------|---------------------|------|---------------|

|                |                |                |             |                |       |                |                     |      |               |

| 1              | 0              | 1              | O           | 0              | 0     | 0              | 0                   | AO   | TMO           |

| 1.             | 0              | 1              | 0           | 0              | 0     | 0              | 1                   | A1   | TM1           |

| 1              | 0              | 1              | 0           | 0              | 0     | 1              | 0                   | A2   | TM2           |

| 1              | 0              | 1              | 0           | .0             | 0     | 1              | 1                   | A3   | CONTROL WORD  |

| 1              | 0              | 1              | 0           | 0              | 1     | O              | Ο                   | A4   | TMO           |

| 1              | 0 .            | 1              | 0           | 0              | 1     | 0              | 1                   | A5   | TM1           |

| 1              | 0              | 1              | 0           | 0              | 1     | 1              | Ο                   | . A6 | TM2           |

| 1 :            | 0              | 1              | 0           | Ο.             | 1     | 1              | 1                   | A7   | COUNTROL WORD |

#### PORT ADDRESS

AO and A4  $\rightarrow$  TMO

A1 and A5  $\rightarrow$  TM1

A2 and A6  $\rightarrow$  TM2

A3 and A7 → CONTROL WORD

# 2.3.4 Synchronizing Technique:

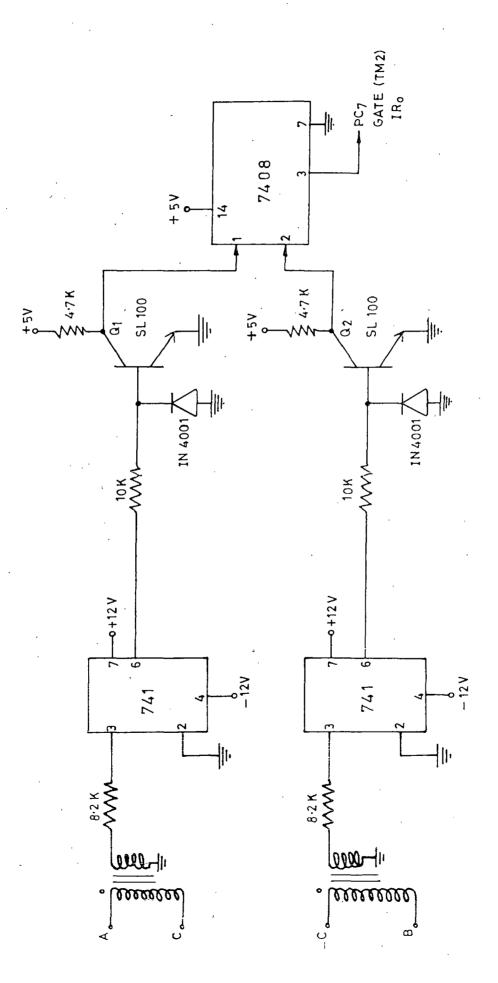

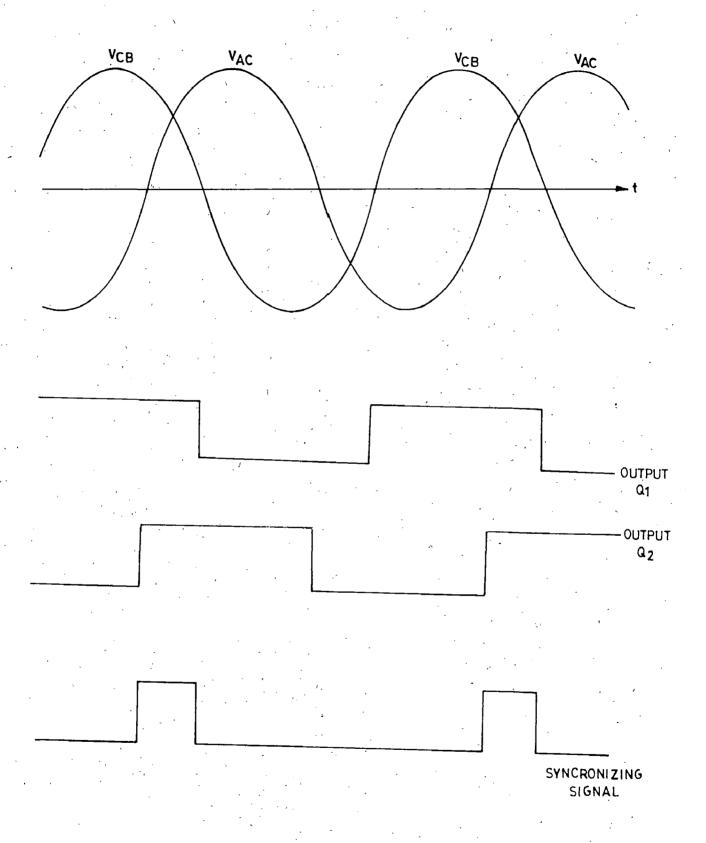

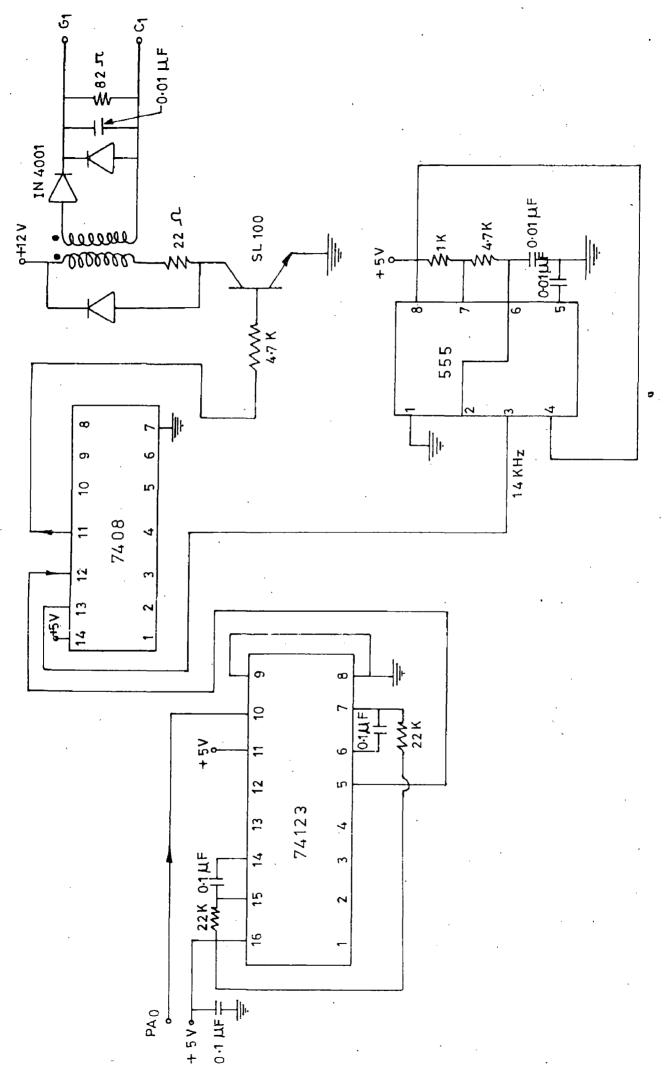

Synchronizing signal is generated by sensing line to line voltages  $V_{\rm AC}$  and  $V_{\rm CB}$  of the synchronous machine terminals. This signal has pulses of  $60^{\circ}$  duration corresponding to machine voltage frequency at every  $360^{\circ}$  interval. This signal provide the informations about frequency of the machine voltage, direct  $60^{\circ}$  delay count and instant of loading a counter of 8253A with firing angle delay count. Synchronizing signal is required for generating firing pulses for inverter thyristors in proper sequence. Synchronizing circuit uses less no of components and is shown in Fig. 2.5. This circuit consists of the following components.

FIG. 2-5-SYNCHRONIZING CIRCUIT

- i) Step down transformer

- ii) Comparator

- iii) Transistor drive

- iv) AND gate

### (i) Step Down Transformer:

This is a single phase 440/6V transformer to realize voltage sensor for a wide range of frequency. The primary winding is connected directly to the machine terminals and secondary goes to non-inverting terminal of the comparator. Primary and secondary connections are made in such a way so that secondary voltage is 180° out of phase with respect to primary voltage. One terminal of the secondary of both transformer is connected to system ground.

# (ii) Comparator:

Comparator circuit has been made with the help of operational amplifier IC 741. The inverting terminal of IC 741 is connected to common ground. The output of the comparator ideally swings between +12 to -12V at every zero crossing of machine terminal voltages and output frequency is the same as the machine voltage frequency. The output of comparator is reduced to a lower voltage by a series connected register and applied to the base of the transistor.

### (iii) Transistor Drive:

The stage is very important and required to interface the analog system to a digital system. Transistor

FIG. 2-6-VOLTAGE WAVE SHAPES AT DIFFERENT POINTS OF SYCHRONIZING CIRCUIT.

is used to control the state of the TTL input. The output of the op amp swings from +12V to -12V. The positive swing drives the transistor into saturation, producing a TTL input of approximately OV. The negative swing drives the transistor into cut-off, producing a TTL input of +5V. Thus the transistor inverts the input control signal. TTL outputs of transistors are shown in Fig. 2.6.

The diode in the base circuit protects the base against excessive reverse voltage. Since the negative output of the comparator approaches -12V, we need to use a protective diode as shown in Fig. 2.5 between the base and ground. This diode clamps the base voltage at approximately -0.7V on the negative swing.

#### (iv) AND Gate:

IC 7408 two input AND gate is used for necessary AND operation. The synchronizing signal is obtained after ANDING two output signals of the transistors. The microcomputer makes use of this signal for generating firing pulses in proper sequence and firing angle control.

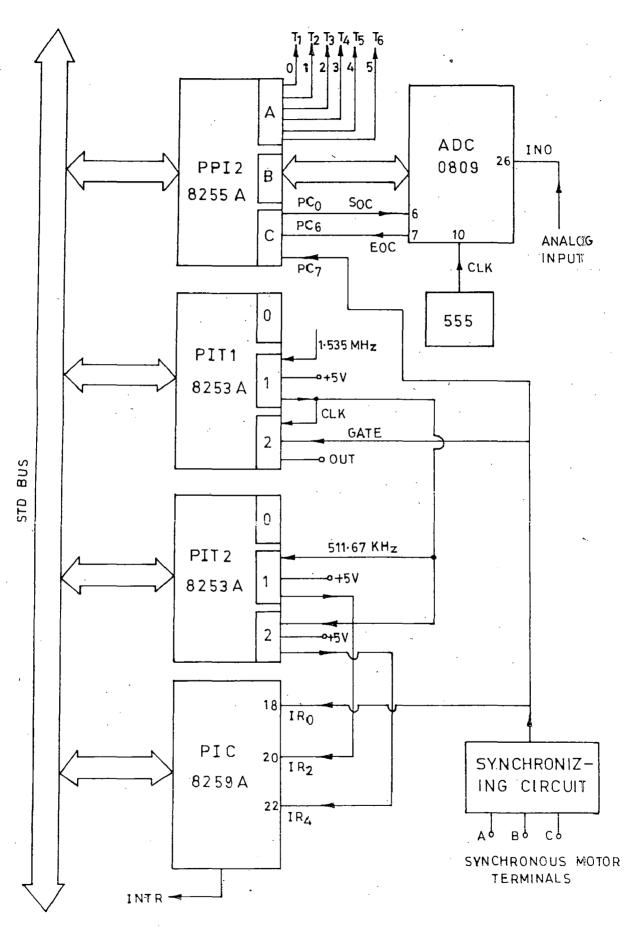

## 2.3.5 Microprocessor Based Firing Control Scheme:

Microprocessor based firing scheme is used for generating the firing pulses for inverter thyristors in proper sequence decided by the control circuit and system software. This scheme has several advantages over the analog

firing control scheme. An analog firing scheme using voltage sensor used for the line commutated inverter fed synchronous machine has the following disadvantages:

- i) Non-linear variation of firing angle using cosine wave crossing firing control.

- ii) The commutation spike in the machine terminal voltages can generate additional firing pulses leading to mis-firing of thyristor.

- iii) Variation of firing angle is limited to 90° by using cosine firing scheme.

- iv) Hard wired logic circuitry fixes the firing scheme philosophy and any change, if necessary, cannot be made without changing the circuit.

These drawbacks of the analog firing scheme can be overcome by using a microprocessor based firing control The hardware configuration of the microcomputer scheme. based scheme is shown in Fig. 2.7. This scheme is developed using vinytics VMC-85 trainer kit. This scheme requires less number of hardware components and simple synchronizing technique. The microcomputer uses two programmable interval timers 8253A, one programmable peripheral interface 8255A and one programmable interrupt controller 8259A. The synchronizing signal derived from machine terminal voltages is inputted to PC7 of 8255A, Gate2 of 8253A(1) and IRO pin of 8259A. Microprocessor checks up the status of the synchronizing signal through PC7 bit just after the initialization of all programmable peripheral devices such as 8253A,

FIG. 2.7—MICROPROCESSOR BASED FIRING CONTROL SCHEME FOR COMMUTATORLESS DC SERIES MOTOR

8255A and 8259A to fix up the proper instant of loading the counter TM2 of PIT1 with FFFFH during the execution of the main program.

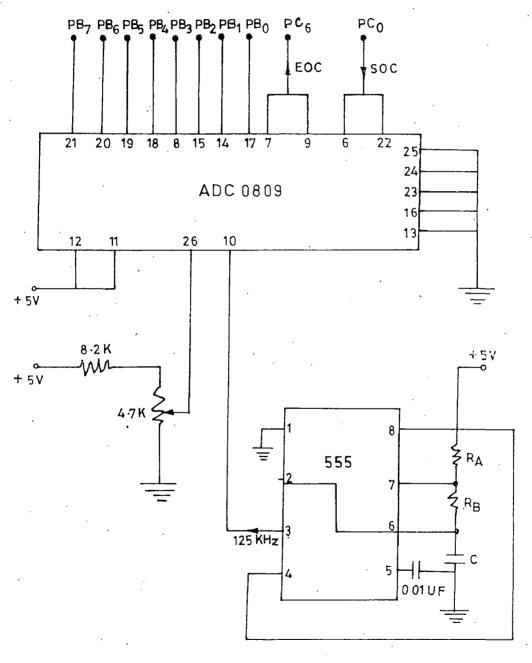

Counter TM2(1), TM1(2) and TM2(2) get the same clock of 511.67 KHz. This clock is obtained by operating the counter TM1(1) in mode 2 from a clock of 1.535 MHz. ADC 0809 is interfaced to the microprocessor through port B and port C of 8255A. ADC provides information about firing angle of the inverter. The details of ADC 0809 interfacing have been given in Appendix - II. The firing pulses for the inverter thyristors are outputted through port A of 8255A as per firing command word. The firing angle can be changed linearly by varying analog input to the ADC through a 4.7K pot connected in series to a 8.2K resistor.

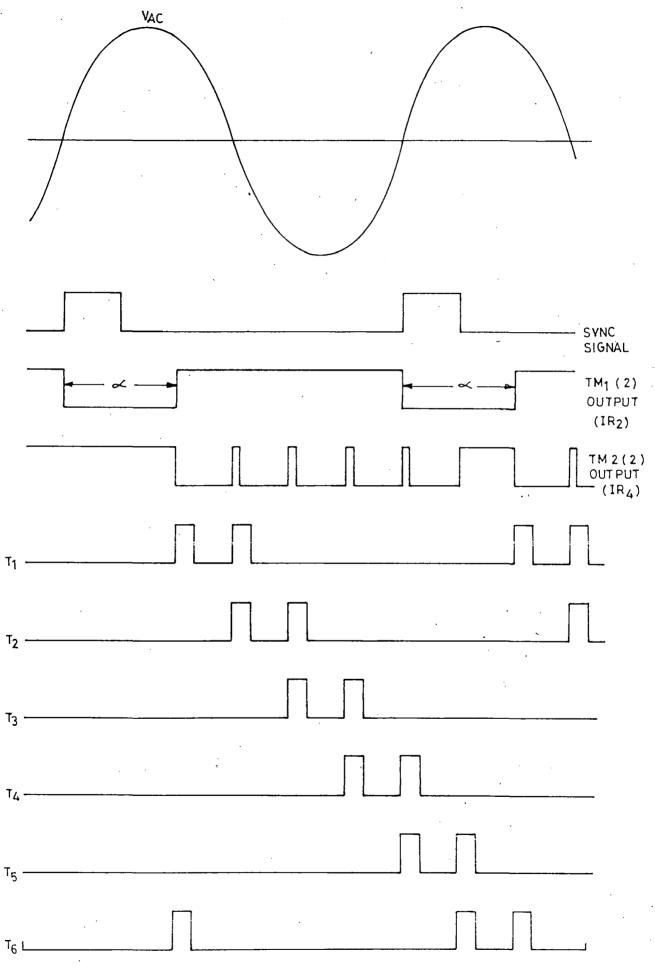

All the counters except TM1(1) are programmed in mode 0. TM2(1) provides the  $60^{\circ}$  count corresponding to the clock 511.67  $KH_Z$ . Counter TM1(2) is used to load firing angle delay count and its output provides the  $IR_2$  interrupt control signal input. Counter TM2(2) is loaded with  $60^{\circ}$  delay count at proper instant by software control and its output on the terminal count is used as  $IR_4$  interrupt signal input for 8259A. The outputs of counter TM1(2) and TM2(2), synchronizing signal and generation of firing pulses are shown in Fig. 2.8. The duration of firing pulses generated by the microcomputer via 8255A is very small. The firing pulse duration is increased to 0.72 ms through a monostable

FIG. 2-8-SYNCHRONIZING SIGNAL, IR2 & IR4 INTERRUPT SIGNALS AND FIRING PULSES IN PROPER SEQUENCE

circuit. These firing pulses are amplified using a pulse amplifier circuit which is described in the following section. In LCI, each thyristor has to conduct for two consecutive modes of  $60^{\circ}$  duration. This scheme uses gating of each SCR twice at the interval of  $60^{\circ}$ . This avoid the possibility of failure of inverter operation in the presence of discontinuous operation.

## 2.3.6 Design of Pulse Amplifier Circuit:

The duration of firing pulses generated by the microprocessor via port A of 8255A is not sufficient to trigger

inverter thyristors. The required pulse width is obtained

using monostable circuit. If the firing pulse width is

programmed to be 0.73 ms through software, microprocessor

will remain in the delay routine for this duration and therefore in the higher frequency, it may not be able to execute

the whole program. This difficulty is over-come by using

monostable circuit. The output of the monostable is applied

to the pulse amplifier circuit Pulse amplifier circuit

consists of the following components:

- i) Monostable multivibrator

- ii) Oscillator

- iii) AND gate

- iv) Pulse amplifier

Pulse amplifier circuit for one channel is shown in Fig. 2.9.

FIG. 2-9-PULSE AMPLIFIER CIRCUIT FOR ONE CHANNEL

### (i) Monostable Multivibrator:

A 74123 retriggerable monostable multivibrator is used to produce an output pulse of 0.73 m sec. The values of the externally connected elements R and C of the pulse forming circuit of 74123 determine, the pulse width. The monostable is designed to operate in rising edge triggering mode. For 74123, the pulse duration is given by

$$T_W = 0.33 RC$$

The elements R and C are selected as 22K ohm and 0.1 uF respectively to give a pulse width of 0.72 m sec.

## (ii) Oscillator:

IC 555 timer is used for oscillator. The external capacitor and resistor  ${\rm R}_{\rm A}$  and  ${\rm R}_{\rm B}$  determine the frequency of oscillation. The duty cycle may be set precisely by the ratio of these two resistors. For IC 555 timer frequency is given by

$$f = \frac{1.44}{(R_A + 2R_B) C_T}$$

Let the oscillator frequency be 14 KHz taking C\_T = 0.01  $\mu$ F, the values of R\_A and R\_B are obtained as follows:

$$R_A = 1K \text{ and } R_B = 4.7K$$

# (iii) AND Gate:

The output of the monostable multivibrator and oscillator is ANDED in the AND gate. IC 7408 two input

AND gate is used for AND operation. The reason for high frequency modulation is obvious. If the pulse is long, they may saturate the pulse transformer and the firing pulse may be distorted. The duty cycle is kept less than 50 percent, so that flux in the transformer can reset. The modulated pulse also reduces the gate dissipation.

# (iv) Pulse Amplifier:

The output of the AND gate is applied to the base of the transistor through 4.7K resistor. The input signal is amplified through the amplifier as shown in Fig. 2.9.

The gate and cathode terminals of SCR are connected to the power circuit of higher patentials. Therefore, the control circuit should not be directly connected to the power circuit. A pulse transformer is used for electrical isolation between control circuit and power circuit as shown in Fig. 2.9. The pulses at the transistor collector is the amplified inverted form of the input signal. But the isolating transformer connection are made in such a way so that the final firing pulse has no phase shift with respect to input pulse. A diode is connected across the transformer primary to avoid saturation of the pulse transformer. Another diode is connected in series with secondary of pulse transformer to block negative pulse. The diode across the primary also serves to protect the transistor. The capacitor at the secondary prevents any spurious high

frequency from triggering the thyristor. The gate of the thyristor can be protected from long reverse voltage by connecting a diode across the gate.

# 2.4 STARTING METHOD OF COMMUTATORLESS D.C. SERIES MOTOR

Under standstill condition, synchronous motor terminal voltage is zero and therefore firing pulse generation is not possible. So the synchronous motor is unable to start from standstill condition. Extra starting methods are necessary to start the synchronous machine from standstill. This is the major drawback of induced voltage commutated inverter fed synchronous motor drives. For commutatorless d.c. series motor, field winding is connected in series with the d.c. link inductor. So d.c. link current and machine speed must be necessary to induce sufficient voltage in the stator winding for generating firing pulses. Several methods are known for starting purpose. But in the present work, a manual starting method shown in Fig. 2.10 has been adopted. The manual method of starting commutatorless D.C. series motor involved the following steps:

A D.C. motor is started to drive the synchronous machine as a generator at a lower speed of about 1000 r.p.m. Now d.c. link current is zero and the induced voltage due to residual magnetism is very small. So proper synchronizing signal will not be generated from this low voltage.

MOTOR SERIES  $\Omega$ C OF COMMUTATORLESS FIG. 2-10-STARTING

- connected across the inverter to allow current flowing through the field winding of the synchronous motor during starting. Now switch SW is closed and some d.c. current is passed through field winding by controlling d.c. link voltage by a three phase auto transformer.

- iii) Synchronizing signal is now generated from the no load induced emf of the generator. Microcomputer proceeds to execute the software program for generating firing pulses according to firing command word.

- iv) A d.c. voltage is produced at the d.c. terminal of the inverter bridge. As the firing angle is greater than 90°, upper terminal is positive and lower one is negative. The D.C. link voltage is increased gradually and power flows from d.c. side to the synchronous machine when the bridge rectifier voltage becomes greater than the inverter output voltage.

- v) The current flowing into the inverter is indicated by the D.C. link ammeter, Thus the synchronous machine starts drawing active power from the D.C. link resulting in a corresponding decrease of D.C. motor current.

vi) Power supply to the D.C. motor is switched off and the resistance of the starting resistor is gradually increased. The switch SW is made off later on and the system works as a commutatorless D.C. series motor.

In this scheme, the no load induced voltage is always greater than the terminal voltage of the synchronous machine. Therefore, the synchronous motor operates like an over excited mode drawing current at leading power factor.

## 2.5 CONCLUSIONS

The details of microcomputer based firing control scheme for the commutatorless D.C. series motor using induced voltage commutation technique has been discussed in this chapter. The design of power circuit and synchronizing circuit are also developed. A special explanation of interfacing a programmable interval timer 8253A has been given in this chapter. The manual method of starting commutatorless D.C. series motor is also discussed.

### CHAPTER - III

### IMPLEMENTATION OF SYSTEM SOFTWARE AND FLOW CHARTS

# 3.1 GENERAL

The development of system software and flow-charts for the microprocessor based firing control scheme is discussed in this chapter. The complete logic of the scheme is described in the main program, routine. The various subroutines used in conjunction with the main program are also discussed in this chapter.

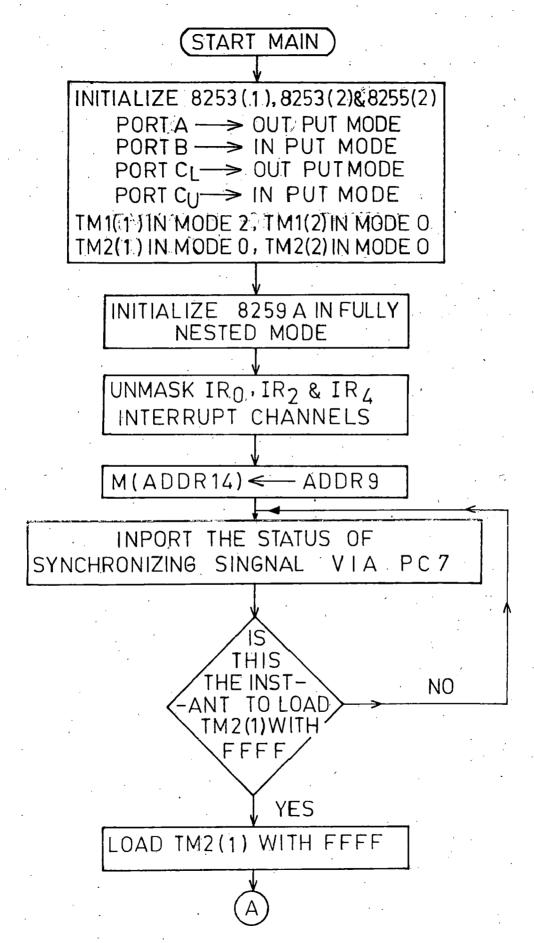

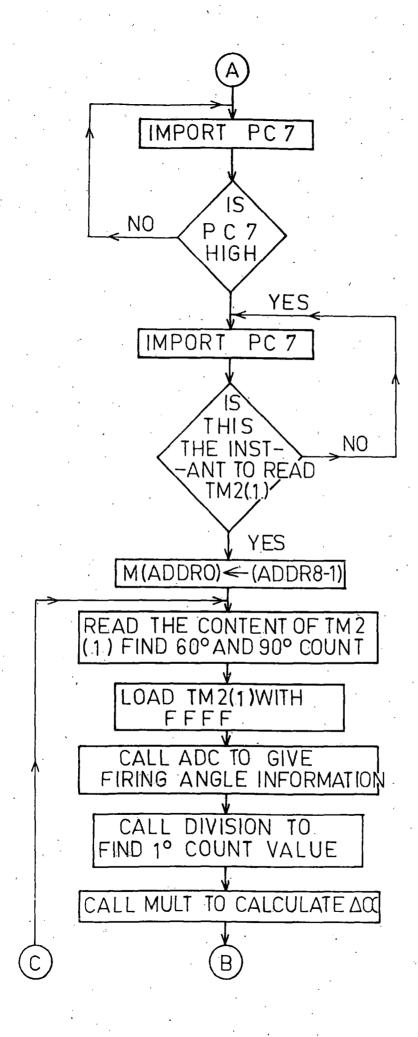

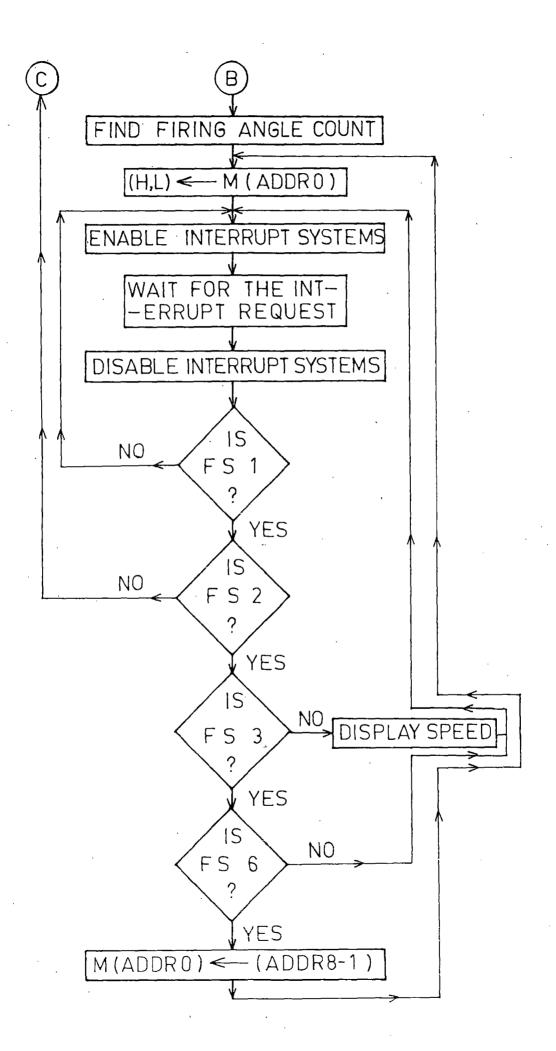

# 3.2 MAIN PROGRAM ROUTINE

The flow-chart for the main program is shown in Fig.3.1. The program is started with the initialization of programmable peripheral interface 8255A. The ports of 8255A are programmed as input mode or output mode according to the requirements for the present scheme. The port A is programmed for outputting firing pulses as per firing command word. The port B is programmed to import the ADC output. The port CL is selected as output mode and port CU as input mode. The counters of programmable interval timer 8253A also are to initialized in the suitable mode as required by the user. In the vinytics VMC-85 up trainer, one counter of 8253A is used for single step operation and two other counters are available to the user through connector J1. Out of

FIG. 3.1 FLOW CHART FOR MAIN PROGRAM

these counters, TM1(1) is programmed in mode 2 for generating the clock of 511.67 kH $_{\rm Z}$  by using the clock of 1.535 MH $_{\rm Z}$  and other counter TM2(1) programmed in mode 0 for providing 60 $^{\rm O}$  count corresponding to clock 511.67 kH $_{\rm Z}$ . The counter TM1(2) and TM2(2) of another programmable interval timer 8253A interfaced by the author are initialized in mode. 0. The output of TM1(2) and TM2(2) are used as IR $_{\rm Z}$  and IR $_{\rm Z}$  interrupt requests for generating firing pulses.

After the initialization of 8255A in simple input/output mode and counters of 8253A(1) and 8253A(2) in mode 0, all port bits and counter outputs become low. After the initialization of 8253(1), the counter TM1(2) is loaded with count 03H to generate the clock of 511.67  $KH_Z$  continuously and this clock remains at a constant frequency of 511.67  $KH_Z$  duration the operation of the system.

The programmable interrupt controller 8259A is initialized in fully nested mode. All the interrupt input pins of 8259A are available to the user through the connector  $J_1$ . In fully nested mode  $IR_0$  has the highest priority and  $IR_7$  has the lowest priority. In the present scheme three interrupt lines:  $IR_0$ ,  $IR_2$  and  $IR_4$  are used. After the initialization of 8255, 8253 and 8259, three interrupt input channels are enabled through operational control word 1 (OCW1).

Now the microprocessor checks the status of the synchronizing signal imported via PC7. If it is found

to be low then FFFF<sub>16</sub> is loaded into the counter TM2 of 8253A(1). Synchronizing signal is inputted continuously to the gate of TM2(1) and counting becomes enable as soon as the digitized signal goes to high. The counter starts decrementing the count value FFFFH with respect to the clock of 511.67 KH<sub>z</sub>. The counter continues counting as long as synchronizing signal remains high and counting becomes disable as soon as synchronizing signal goes to low. Under this condition counter output remains low.

The address, ADDR8-1 is stored in the memory location ADDRO where ADDR8 is the starting address of the firing command table. Now the present content of the counter TM2(1) is read and the count value for 600 duration of terminal voltage of the synchronous machine is calculated. The 30° count value is found by rotating right the 60° count value by one bit in register pair HL. The 90° count value is calculated by adding 30° count value with 60° count value. These 60° and 90° counts exactly correspond to the 60° and 90° durations of the synchronous machine terminal voltage. Memory location ADDR1 and ADDR2 are used to store the 60° and 90° count value respectively which will be used later on. The counter TM2(1) is reloaded with FFFFH for the next synchronizing pulse of 60° duration. angle delay count is calculated according to the following equation: