## "DEVELOPMENT OF ELECTRONIC LOW FREQUENCY MEASURING INSTRUMENT"

#### A DISSERTATION

Submitted in partial fulfilment of the requirements for the award of the degree

of

#### MASTER OF ENGINEERING

in

ELECTRICAL ENGINEERING (Measurements and Instrumentation)

> CHECKED 1925

AJAI KUMAR JAIN

Ey

DEPARTMENT OF ELECTRICAL ENGINEERING UNIVERSITY OF ROORKEE ROORKEE-247 667 (INDIA)

January, 1987

### DECLARATION

I hereby certify that the work which is being presented in the thesis entitled "DEVELOPMENT OF ELECTRONIC LOW-FRRQUENCY MEASURING INSTRUMENT" in partial fulfilment of the requirement for the award of the Degree of MASTER OF ENGINEERING in Electrical Engineering with the specializati zation in " Measurements and Instrumentation," submitted in the Department of Electrical Engineering, University of Roorkee, is an authentic record of my own work carried-out during the period: Jav' 86 to Jav' 87

Under the supervision of Dr.R.N.Mishra and Sri S.Mukherjee.

The matter embodied in this thesis has not been submitted by me for the award of any other degree.

Ablains

(A.K. JAIN) SIGNATURE OF THE CANDIDATE

This is to certify that the above statement made by the Candidate is correct to the best of my knowledge, and belief.

DATE 2.1. 1987

(ゟ. MUKHERJEE ) L E C T U R E R

R.N. Mishva.

( Dr.R.N. MISHRA) R E A D E R DEPARTMENT OF ELECTRICAL

DEPARTMENT OF ELECTRICAL ENGINEERING:

ENGINEERING:

UNIVERSITY OF ROORKEE ROORKEE

#### ACKNOWLEDGEMENT

The author is highly indebted to Dr.R.N.Mishra, Reader in Electrical Engineering Department, University of Roorkee, and Sri S.Mukherjee, Lecturer in Electrical Engineering Department, University of Roorkee, Roorkee for their unfailing help and able guidance.

The author is thankful to Dr.P.Mukhopadhayaya, Professor and Head, Electrical Engineering Department for providing necessary facility and encouragement from time to time, The author is also thankful to Dr.K.N.Khattri, Professor, department of Earth Sciences, for providing necessary facility and timely help.

He would like to take this opportunity to pay his sincere thanks to all those who in some way or the other encouraged, inspired and helped him during the preparation of this dissertation work.

(A.K. JAIN) SIGNATURE OF CANDIDATE

DATED - JANUARY 1987

\*\*\*\*

ABSTRACT

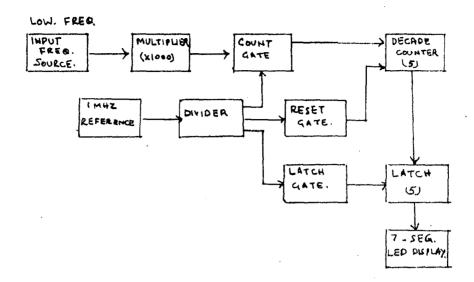

Low Frequencies are, generally, measured by using period measurement. The method, however, inherits inaccuracy as one have to take reciprocal of time period to measure frequency. Here frequency multiplying technique using PLL is used to multiply the low frequency and this multiplied frequency is, then, counted using frequency comparision: scheme.Thus display counters will display directly in terms of frequency.with proper decimal adjustment.

\*\*\*\*

## CONTENTS

| CHA | CHAPTER                                       |                 |                    | PAGE NO. |

|-----|-----------------------------------------------|-----------------|--------------------|----------|

|     | DECLARATION                                   | · · ·           |                    |          |

|     | ACKNOLLEDG EM EN T                            |                 | •                  |          |

|     | ÁBSTRACT                                      |                 |                    |          |

| 1-  | INTRODUCTION                                  |                 |                    | 1-1      |

| 2-  | MEASUREMENT OF<br>A REVIEW                    | LOW FREQUENCY S | IGNAL:             | 2-1      |

| 3-  | FREQUENCY MULTIPLYING TECHNIQUES;<br>A REVIEW |                 |                    | 3-1      |

| 4-  | PLL - THEORY AND                              | DESCRIPTION     |                    | 4 – 1    |

| 5-  | LOW FREQUENCY <sup>M</sup> e<br>And testing:  | TER-DESIGN, FAB | RICATION           | 5-1      |

| 6-  | RESULTS                                       |                 | <b>e</b> ™ gen gen | 6-1      |

| 7-  | CONCLUSIONS                                   |                 |                    | 7-1      |

|     |                                               |                 |                    |          |

-<u>~~</u>~~---

۲

.

# LIST OF FIGURES

| FIGURE               | DESCRIPTION                                                                                                                         | PAGE                                                                                    |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| (2·1.a)              | FREQUENCY SELECTIVE BRIDGE USING ACTIVE RC QUADRATURE]                                                                              | (2.1. P)                                                                                |

| (2 2 a)              | BLOCK DIAGRAM OF SINGLE & MULTIPLE PERIOD MEASUREMENTS.                                                                             | ζ, ·                                                                                    |

| (2·3.a)              | BLOCK DIAGRAM OF SCHEME {2.3}                                                                                                       |                                                                                         |

| (2.4.a)              | BLOCK DIAGRAM OF SCHEME {2.43.                                                                                                      | (24.8)                                                                                  |

| (2.5.0,6)            | BLOCK DIAGRAM & WAVEFORMS OF SCHEME {2.5}                                                                                           | (2·7.P)                                                                                 |

| (2.6.a,b,c,d)        | BLOCK DIAGRAMS & CURVE OF SCHEME {2.6}                                                                                              | (2 9 P)                                                                                 |

| (2.7. a, b, c)       | BLOCK DIAGRAMS & WAVESHAPES OF SCHEME {2.7}                                                                                         | (2.12.P)                                                                                |

| (3.1. a, b)          | BLOCK DIAGRAM & WAVESHAPES OF SCHEME \$3.13                                                                                         | · (3.1.p)                                                                               |

| (3.2.a,b,c)          | BLOCK DIAGRAM, PRINCIPLE & WAVESHAPES OF SCHEME \$3.23                                                                              | (3.2.P)                                                                                 |

| (3.3.a)              | CIRCUIT SCHEMATIC OF MULTIPLIER                                                                                                     | Z - '7(3.4.p)'                                                                          |

| (3.4.a)              | CIRCUIT SCHEMATIC OF SCHEME 3.4}                                                                                                    | $\left( \begin{array}{c} \cdot \cdot (3, \mathbf{\mu}, \mathbf{p}) \end{array} \right)$ |

| (3.4.6)              | HIGH SPEED FREQ. MULTIPLIER                                                                                                         |                                                                                         |

| (3·5. a)             | BLUCK DIA GRAM OF NEW FREQ. MULTIPLIER (3.53                                                                                        | (                                                                                       |

| (3.6. a)             | SCHEME USED IN {3.6}                                                                                                                |                                                                                         |

| (37.4)               | SIMPLE FRED DOUBLER                                                                                                                 | (3.10. P)                                                                               |

| (3.8.a,b)            | CIRCUIT SCHEMATIC & WAYEFORMS OF \$3.83                                                                                             | ·· (3.14.P)                                                                             |

| (3·9.a)              | FRED. DOUBLING SCHMITT TRIGGER SCHEMATIC                                                                                            | .7                                                                                      |

| (3.10.0)             | CONSTANT DUTY CYCLE DIGITAL FREQ. DOUBLER                                                                                           | (3.18.P)                                                                                |

| (3.11. 9,6)          | BLOCK DIAGRAM & WAYEFORMS OF SCHEME [3.1]}                                                                                          |                                                                                         |

| (3·12-a)<br>(3·13.a) | FUNCTIONAL FREQ. MULTIPLIER                                                                                                         | ·· } (3.22.P)                                                                           |

| (3.14 a, b, c)       |                                                                                                                                     |                                                                                         |

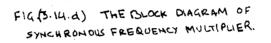

| (3.14. d)            | BLOCK DIAGRAMS & WAVEFORMS OF SCHEME \$3.143                                                                                        |                                                                                         |

| (2.15. 9)            | BLOCK DIAGRAM OF SCHEME \$3.14}                                                                                                     | (3.27. P)                                                                               |

| (3.16 9,6)           | PRINCIPLE & SCHEMATIC OF {3.16}                                                                                                     |                                                                                         |

| (3.17 . a)           | IC PIN CONNECTION DIAGRAM OF SCHEME {3.173                                                                                          | (3.30.P)                                                                                |

| (4.1.9,4)2.a)        | BLOCK DIAGRAM OF PLL & PHASE DETECTORS                                                                                              |                                                                                         |

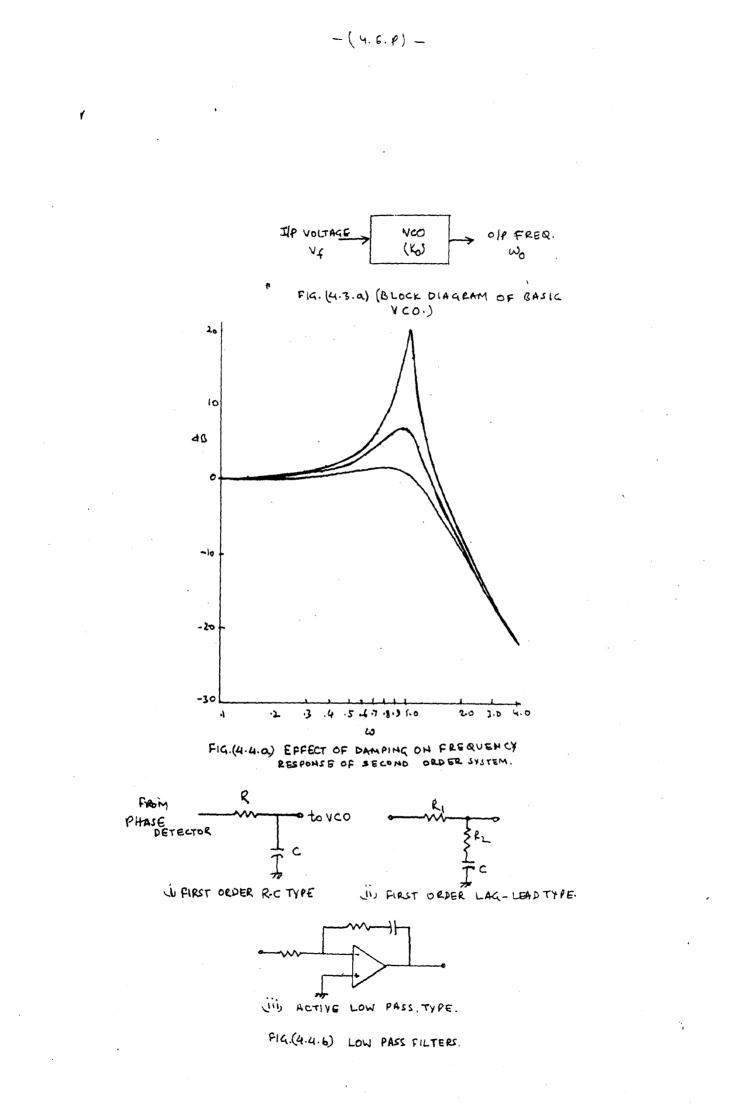

| (4.3. a)             | BLOCK DIAGRAM OFVCO                                                                                                                 | - 7                                                                                     |

| (4.4 0,6)            | BLOCK DIAGRAM OFVICO<br>CHARACTERSTIC CURVE OF 2nd ORDER SYSTEM & CKTS OF LOW DI<br>TRANSIENT RESPONSE DAMPING FACTOR DETERMINATION | ASS P 9.6.P                                                                             |

| (4.4.c)              | TRANSIENT RESPONSE DAMPING FACTOR DETERMINATION                                                                                     | 7                                                                                       |

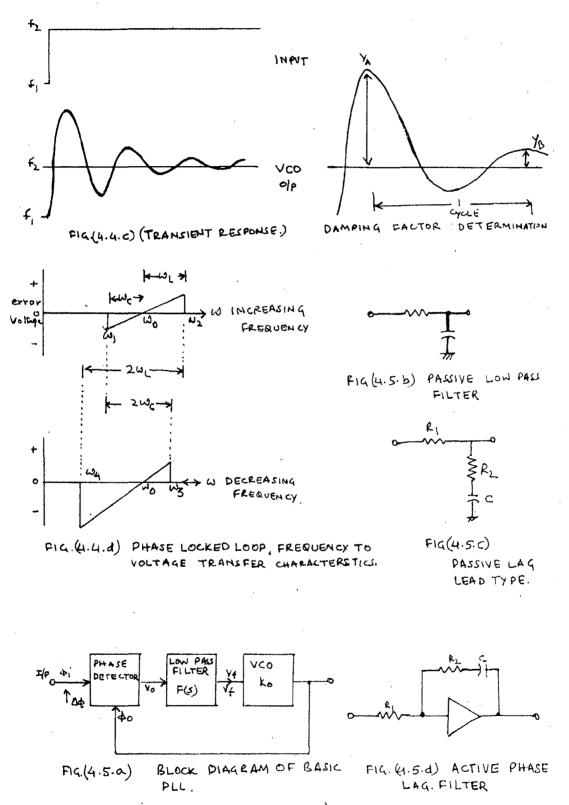

| (4.4.d)<br>(4.5.a)   | PLL FRED/ VOLTAGE TRANSFER CHARACTERSTICS<br>BLOCK DIAGRAM OF PLL                                                                   | 4.13.P                                                                                  |

|                      |                                                                                                                                     | 1                                                                                       |

-. (1-1)

### CHAPTER-1

## INTRODUCTION

Frequency Measurements has always been an interesting problem. **problem.** Simplest frequency measurement was started by counting the number of cycles of given operation e.g.slow swing of pendulam. With the progress in Science a Yumber of new techniques of frequency measurement has come into existence Now-a-days digitaltechniques have evolved out which are highly accurate so far. Digitally frequency can be measured in two mode mode (1) Frequency comparision mode (2) Period measurement made.

Till now, the simplest technique of low frequency(below-20H<sub>z</sub>) measurement was period measurement. But this, was at the cost of accuracy. However, the accuracy could be improved by using more gate opening period but then, at the cost of time i.e.process becomes quite slow.

Now, there is no need of using period measurement scheme for low frequency comparision scheme. Here input frequency, which is quite low (e.g. 1-6H<sub>z</sub>), is multiplied by some suitable multiplying factor N (Here N = 1000) and then this multiplied frequency is commuted by the same frequency comparision scheme.

The meter should find application in measuring physiological pulse rates, slow moving physical systems(such as low shaft speed measurement).

~\*\*\***\***\*

#### -. (2-1)

#### CHAPTER-2

#### MEASUREMENT OF LOW FREQUENCY SIGNAL: A REVIEW

Following are the few general techniques when we go for frequency measurements:

- (a) ANALOL TECHNIQUES-

- 1- Mechanical Resonance type or Vibrating reed type.

- 2- Electrical Resonance type.

- 3- Electro Dyname meter type.

- 4- Weston type.

- 5- Ratio meter type.

- 6- Saturable Core type.

- 7- Frequency bridges.

- 8- Stroboscopic Methods.

- 9- C.R.O. Methods.

## (b) DIGITAL TECHNIQUES OF FREQUENCY MEASUREMENTS

But for measurement of low frequency there are some well known methods which can be categorized in two main categories.

- (a) Analogue Techniques

- (b) Digital Techniques.

#### (a) ANALOG: TECHNIQUES-

# 2.1 AN ACTIVE FREQUENCY METER

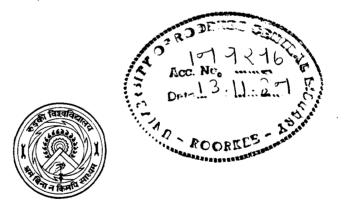

## Principle - Ref.Fig. (2.1-a)

Here the basic scheme employs frequency selective bridge which uses a guradrature amplifier (QA). The emplifier provides an output voltage which is equal to the input voltage

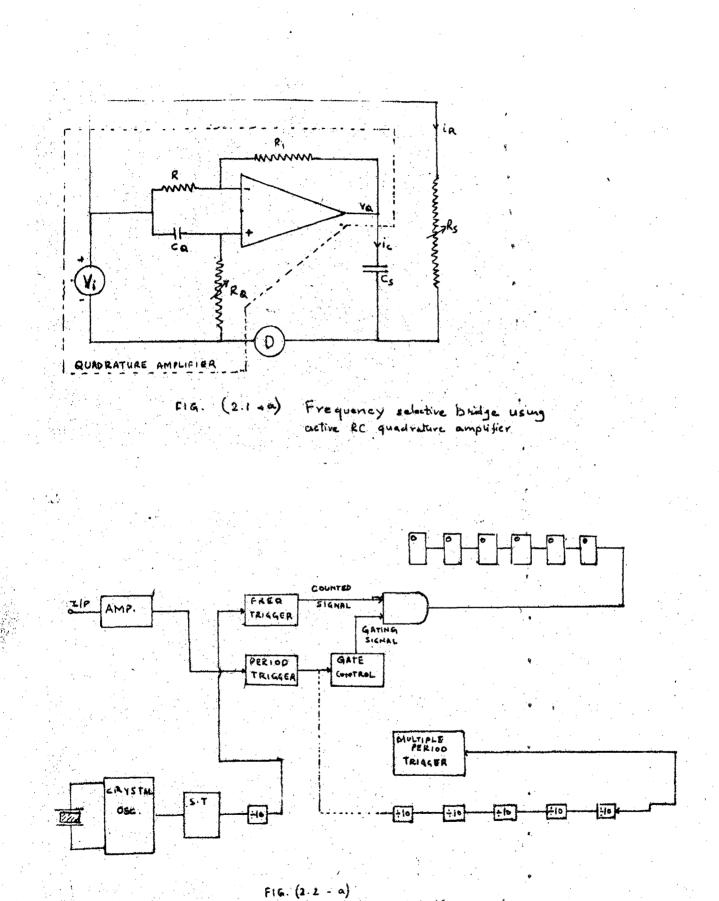

Block diagram of Eingle & multiple period Mensurement.

F-1

in magnitude but 90° out of phase. The standard resistor (Rs ) and capacitor Cs are compared. A low impedance current detector D is used in the frequency meter. At balance resistive and capacitive current ic and in must balance each other and current through detector should be zero i.e.

$i_{c} + i_{R} = 0$  (2.1.1)  $\frac{jV}{-j/Wc_{s}} = 0$  (2.1.2)

On solving equation (2.1.2) we find the final balance condias -

$WC_{\rm s}R_{\rm s} = 1$  -- (2.1.3)

The equation(2.13) shows that the frequency can be measured in terms of the resistance and capacitance.

#### COMMENTS: -

- This frequency selective bridge using an RC active QA can be used to measure frequency in the range of 10 H<sub>2</sub> - 100 KH<sub>2</sub> in four decade ranges.

- 2) It has low component count.

- 3) It requires only one acjustment for balance.

- 4) Basically being an RC type bridge errors due to skin effect and eddy current are absent.

- 5) It has higher current sensitivity than Wein's bridge.

- 6) The shielding arrangement used is simple and perfect.Most of the stray capacitances among the Shields and

-. (2-3) .-

earths appear either across supply or detector, where as in Wein's bridge these appear across ratio arms.

7) With resistor and capacitor of tight tolerance the frequency meter can give accuracy of measurement better than 0.1% in the entire frequency range.

2883

8) It can also be used for frequency control.

)

## b DIGITAL METHODS

2.2 PERIOD MEASUREMENT [2]

One of the basic trohnique used in low frequency measurement is period measurement instead of frequency, as measurement of frequency in low frequency range leads to low accuracy results.

(2-4)

We know, period of  $u_n$  known signal (with Frequency f) can be written as  $T = \frac{1}{f}$ . Therefore, what we do in period measurement, we simply interchange the function of the two input signals (namely standard and unknown) coming to the main gate. i.e.unknown frequency signals now determines duration of the signal (standard) in other words unknown frequency signal now acts as gating signal or Gate control element. On the other hand known frequency or standard frequency is allowed to pass through the gate under the control of gate control.

#### COMMENTS:

Here the main draw back in using period measurement is that to get accuracy at low frequencies. One must take reciprocal of the answer displayed by the display counters if **he** wants to know the input frequency. Also, at low frequencies reciprocal of a quantity does not produce accurate results i.e. 0.33 sec.will give a frequency as 3 H<sub>z</sub>, which /than should be more/3 H<sub>z</sub> similar is case with 7 H<sub>z</sub> period, measurement process will give us result as 0.14 sec. and reciprocal of this will be more than 7 H<sub>z</sub>. However, the accuracy -. (2-5) .-

of the scheme described above can be greatly increased by using multiple period average mode of operation. Here main gate is held open for more than one period of the unknown signal This can be done by using decade dividers. So that unknown frequency is divided by 10 or 100 or more. In other words period can be extended by a factor of 10, 10<sup>2</sup> or more depending upon the requirement.

COMMENTS:

- (1) The main drawback of the system lies in the fact that to open gate for 10 or 100 of cycles of unknown will take considerable time and signal might change (if eur unknown signal frequency is not steady enough )during this time.

- (2) Here digital display on the counter will show more digits of information thus increasing the accuracy. However, the decimal point location and measurement units are usually changed each time on additional decade divider is added so that display is always in terms of period of 1 cycle of input signal.

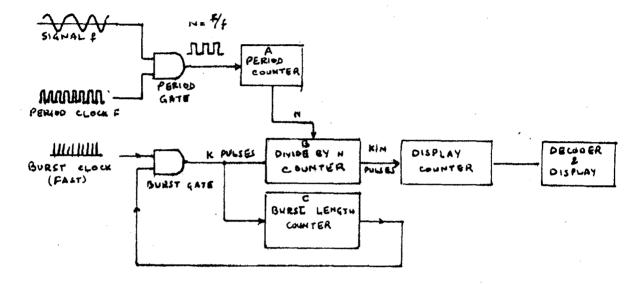

### [3] 2.3 COUNTER INVERTS PERIOD TO MEASURE LOW FREQUENCY-

The method described for one period measurement was less accurate and method described for multiple period measurement was more accurate but it is slow and there is problem to invert period also. Here is a scheme, where reciprocal of measured period is taken by means of standard binary and BCD (binary coded decimals ) counters.) Principle: - We must have four counters, A,E,C, and D numbers. The counter A measures the period of unknown

FIG (2.4-a)

.

-. (2-6) .-

signal by counting number of clock pulses, N,during a cycle. The number N programs.counter B which is programmable divide by N unit. Counter C creates a burst with a fixed number of pulses K.

This burst is applied to counter B which computes a number K/N. Thus taking reciprocal of period N and producing a number of pulses proportional to unknown signal frequency. Finally counter D accummulates these pulses to display the frequency.

#### COMMENTS:

- Circuit can measure frequency within a cycle of input and hence cycle to cycle variation of input can be observed.

- There are six steps in functioning of this counter. The The counter is not simple enough.

# 2.4 <u>A DIGITAL FREQUENCY METER FOR MEASURING LOW</u>

Ref. Fig. (2.4.a)

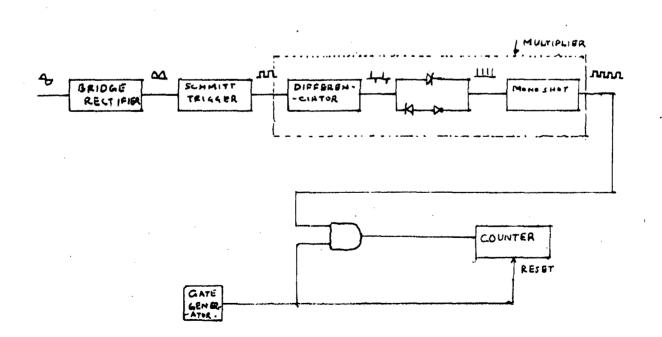

Here is another simple scheme which converts one input cycle into four pulses and therefore keeping the measurement time of signal to one cycle and increasing accuracy to four times. Here sinusoical input is rectified and then shaped into square pulses with the help of schmitt trigger circuit. Here we will get two square pulses.per input cycle. This square signal is differenciated by differenciator and then all differenciated pulses are made positive. impulses with the help of network of diodes and invertors. So that, at the output of net work we are left with four positive impulses per input cycle. Each impulse is used to trigger mono shot multivibrator and hence for each impulse, there is one pulse of fixed predetermined duration say, g and therefore, for every one cycle there are four fulses of duration g such that  $g \leq T/4$ . In 1(one) see there are 4 f pulses of duration g and thus a gate can be made to open for 4 fg second in 1 sec. If gate is fed a signal of N, H<sub>Z</sub> frequency. We can have 4 f $\delta$ N pulses to pass through gate in 1 sec., which can be fed to counter. Reacing of the counter can be interpreted directly in terms of input frequency.

#### COMMENTS:

- 1- Accuracy is four times increased without increasing the gate opening period.

- 2- Accuracy can be further increased if the some frequency multiplier is used to multiply input frequency.

### 2.5 <u>A MEASUREMENT TECHNIQUE FOR LOW FREQUENCY</u>

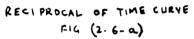

One more quite simple method to measure low frequency has been proposed in paper from T.V.R.Murthy and M.K. Kumar. This technique measures the frequency within a cycle of periodic input and is quite useful in quicker measurement for low frequencies.

LOW FREQUENCY MEASUREMENT CIRCUIT

sig. (2.5-a)

WAVE FORM BLACKAM AT DIFFERENT POINTS

FIG (1.5-b)

#### METHOD:

The major difficulty in measuring low frequency is to obtain reciprocal of period. The proposed method combines period measurement and reciprocating circuit.

(2-8)

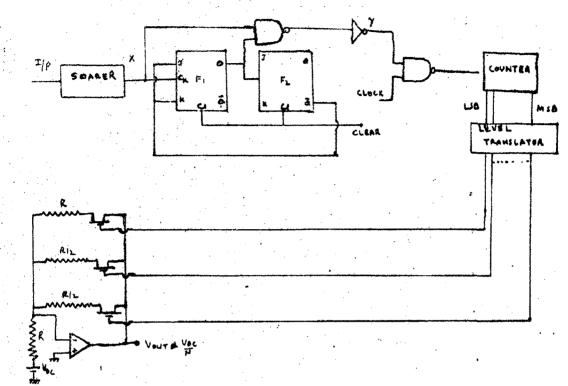

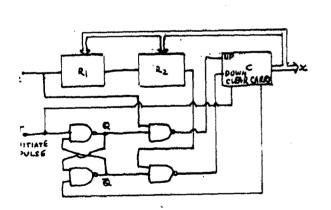

The circuit diagram is shown in Fig.(2.5.a) Flip Flop  $F_1$  and  $F_2$  are initially cleared. The input waveform is converted to a square wave by a squarer. Initially J & K of  $F_1$  are set to logic (1). Hence the input at Clock terminal of  $F_1$  will set  $F_1$ . The output of  $F_1$  is fed as clock to  $F_2$ . The falling edge of Q of  $F_1$  will set  $F_2$  thereby resetting  $F_1$ . The output of the inverter can be seen to be a single input pulse.

The signal pulse selected will enable the clock pulses to a counter which will store a number proportional to the period of the input. The counter output controls the ON-OFF states of the switches in th., feedback path of the amplifier. If, for example the counter output is 01011, then R, R/2 and R/8 will be connected in parallel, giving an output of VDC/11, which is proportional to frequency, the general the output voltage is VDC/N. where N is decimal equivalent of counter D/P. The output can be fed to a digital voltméter for the measurement of frequency. Waveform diagrams are given in Fig. (2.5.b). A fair child 3701 mos monolithic six channel switch offers typical ON resistance of 200  ${\it I\!L}$ and OFF resistance at 200 Gr providing OFF/ON resistance ratio of 10<sup>9</sup>.frequency measurements for a decade range with a resolution of 1 in 100, with an error of less than 1% can be achieved.

#### CONCLUSION

Here main advantage of this type of circuit is completing measurement within a cycle of input and hence the cycle to cycle variation in input frequency, can be displayed.

# 2.6 A DIGITAL INSTANTANEOUS FREQUENCY METER

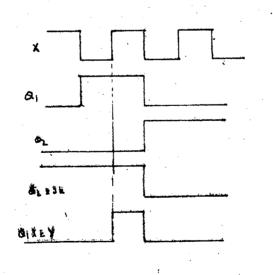

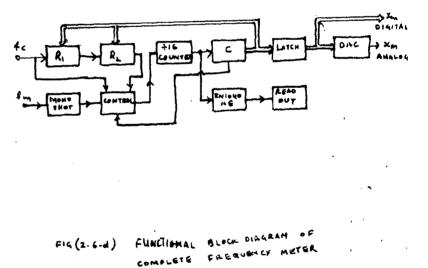

Here is a technique which describes a low frequency meter in which reciprocal of the time elapsed between successive pulses is continuously evaluating digitelly, and then sampled and held at the and of each cycle. Digital Reciprocal Time Generator.

The digital reciprocal time generator (D.R.T.G.). design is based on implementation of non linear differential equation-

$\frac{dx}{dt} + Kx^2 = 0 \qquad -- \qquad (2.6.1)$

The solution of this is

$$x = \frac{1}{Kt + \frac{1}{x_0}} -- (2.6.2)$$

where  $x_0$  is the initial value of  $x_{,>} 0$ , let  $x_0 \xrightarrow{} \infty$  (Fig.2.6A)

$$x = \frac{1}{Kt}$$

. . . (2.6.3)

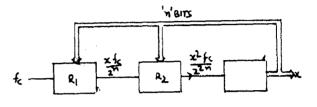

FIG(2.6-B) BASIC DIGITAL RECIPROCAL OF TIME GENERATOR

FIG-(2-6-C) DIGITAL RECIPRACAL OF TIME GENERATOR WITH UP/DOWN COUNTING

-. (2-10) .-

A pulse rate technique implementations or 2.6.1 using two binary rate multipliers ( $R_1$ ,  $R_2$ ) and a down counter (C) is shown in Fig.(2.6.b). The output of a binary rate multiplier is a frequency  $f_0$ , the average value of which is proportional to the product of a input frequency  $f_1$  and an 'n' bit parallel binary number y as follows:

$$f_0 = \frac{y}{2^n} f_1 --$$

(2.6.4)

Thus for Fig.(2.6-b) we can write

$$\frac{dx}{dt} + \frac{x^2 fc}{2^{2n}} = 0 - (2.6.5)$$

where  $f_c$  dock frequency. Therefore, assuming  $x_0 = \infty$

$$x = \frac{2^{2n}}{f_0 t} -- (2.6.6)$$

Clearly for low values of t, the max.counter output  $x = 2^{n}-1$  will be exceeded. Therefore, hyperbola must start at (A) in Fig.(2.6.a), and value of t must be gap greater than  $t_{0}$ .

For large " n "

$$t_{c} = \frac{2^{2n}}{(2^{n}-1)f_{c}} = \frac{2^{n}+1}{f_{c}} = \frac{2^{n}-1}{f_{c}} - (2.6.7)$$

Thus starting point A can be app.established by counting up from zero at rate fc until the counter is full.The counter "carry " pulse can then be used to initiate the down counting. The corresponding block diagram is shown in Fig.(2.6.6).where the counter C now has an up/down counting facility.

The finitiate" pulse corresponding to t = 0, clears the counter and sets the Q cutput of Flip Flop H1. Thus the pulse rate  $f_c$  is routed to the yp count terminal of the counter via NAND gate. When counter is full, the carry' pulse causes the flip flop  $\overline{Q}$  cutput to go HI thus, routing the gate output from  $R_2$  to the DOWN count terminal. The hyperbolic down count continues until the next "initiate" pulse occurs and the process is repeated. In practice, in order to prevent the counter from over-flowing and resetting to zero due to propagation delays, a delayed version of the "carry" pulse is used to set all the counters cutput H1 thus ensuring that the down count always starts from the counter full state.

#### Meter Frequency Range and Accuracy-

Clearly the absolute max.value of measured frequency is given by max. fm =  $\frac{1}{t_c} = \frac{f_c}{2^n} - 2.6.8$

Theoretically there is no limit, but in practice peer resolution obtaining as the period increases becomes the limiting factor. For n = 12, the theoritical accuracy is  $\pm 0.025\%$  FSD, i.e.  $\pm 1$  count. The accuracy expressed as percentage of reading decreases with  $f_m$ . Thus for an accuracy better than 0.25 percent of reading, the range of  $f_m$

-. (2-11) .

is from 0.1  $f_c \times 2^{-n}$  to  $f_c \times \overline{2}^n$ .

<u>**PERFORMANCE</u>** - Theoritical accuracy of this instrument is  $\pm$  1 count. To this must be added in-accuracies due to variation in clock frequency. To test the meter highly stable measured and clock signals are required. The accuracy obtained was only  $\pm$  several counts. This was primarily due to approximate method for setting point A on reciprocal (2.6-a) time curve Fig. The problem was readily over come by including a further 4 bit counter and increasing the clock frequency by a factor of 16. This in effect made the meter a 16 bit device, with the four best significant bits discarded. Tests now showed that the accuracy of the meter was  $\pm$  1 count cover the entire range.</u>

The meter should find application in measurement of frequencies e.g.low shaft speed, physiological pulse rates etc..

## 2.7 A DUAL SLOPE BASED DIGITAL FREQUENCY METER [7]

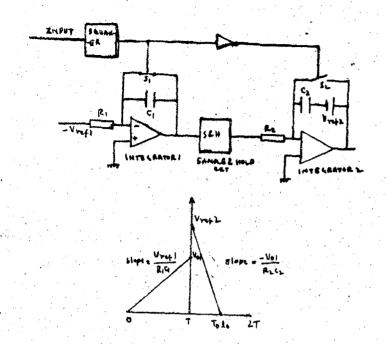

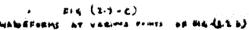

The Fig.(2.7-a) shows the basic configuration for digital frequency meter. In first interval, the first integrator I, is allowed to integrate the DC voltage  $V_{ref}$ , therefore, the output of this integrator at the and of cycle is given by -

$V_{01} = \frac{-1}{R_1 C_1} \int_{0-V_{ref} 1 dt.}^{T}$ =  $\frac{V_{ref1}}{R_1 C_1} -- (2.7.1)$

V

FIG (2.7- a) .: BASIC CONFIGURATION FOR A DUAL DIAITAL PREDUENCY METER RASED

THE DINTEL 65 FREQUENCY METCH

Through the second interval, the second integrator is allowed

to discharge, starting from another DC voltage  $V_{ref2}$ . The input for this integrator is made equal to  $V_{01}$ , therefore, the output of the second integrator  $I_2$  is given by-

$$V_{02} = V_{ref2} - 1/R_2C_2 T + t$$

=  $V_{ref2} - \frac{V_{01}}{R_2C_2} t$

at t = to,  $V_{02} = 0$

Therefore,

$$t_{0} = \left(\frac{V_{ref2}}{V_{ref1}}\right) R_{1}C_{1}R_{2}C_{2} \frac{1}{T}$$

= Kf -- (2.7.2)

where  $K = \begin{pmatrix} V_{ref 2} \\ V_{ref 1} \end{pmatrix} R_1 C_1 R_2 C_2$

Using a BCD counter to count through the period (T,T+to ) will produce a number given by-

N = to f<sub>C</sub>

Where f<sub>c</sub> is the clock freq.applied to counter-

$$N = f_{\rm C} K f_{\rm c}$$

(2.7.3)

Therefore, output number of counter is proportional to frequency of input.

-. (2-14) ...

#### RESULTS AND DISCUSSION

The CKt shown in Fig.(2.7.b) uses 741 OP-Amp for comparator, 4 x \$N749D as the four digital decade counter, 8 x \$N74175 as the latches, SG173 as single pole single through analog switch and SHM LM-2 as the S/Hckt.

This meter has been tested by measuring frequency between 1-10 Hz. For this range  $R_1 = 1 \text{ M } R_2 = 10\text{K}, C_1 = C_2 = 10\text{F}$ Vref1 = Vref2 = 2.5V,  $f_c = 200\text{KH}_z$ . This meter shows accuracy of 0.2%.

Range of measurement can be changed by changing  $R_1C_1$ (i.e.time constant) since saturation should not **occur** in 1st.interval, the lowest frequency that can be measured (fmin.) is given by-

$V_{o1} = \frac{1}{R_1 C_1} \qquad \frac{V_{ref 1}}{fmin} = V_{cc}$ or  $f_{min} = \frac{1}{R_1 C_1} \qquad (\frac{V_{ref 1}}{V_{cc}})$

Where Vcc is supply voltage:

However in 2nd interval, second integrator should reach a value less than V<sub>ref2</sub> therefore, the highest frequency that can be measured is given by-

$$V_{ref2} = \frac{1}{R_2 C_2} V_0 1 \frac{1}{f_{max}}; \text{ but } V_0 1 = \frac{1}{R_1 C_1} \frac{V_{ref1}}{f_{max}}$$

-. (2-15) .-

or

$$f_{max} = \frac{V_{ref1}}{V_{re12}} = \frac{1}{R_1 C_1 R_2 C_2}$$

Accuracy of this instrument is mainly dependent on integrators used for dual slope operation. It is a fast digital freq.meter and suitable for measuring low frequency such as those in audio frequency and power frequency range.

## 2.8 LOW FREQUENCY METER WITH LINEAR READ OUT

PRINCIPLE: The easiest way to obtain an expensential law from period is to measure the decay of a capacitor. In this circuit, it is achieved by charging, decaying, sampling and recharging a capacitor. Calibration can be achieved by adjusting the FSD pot and then setting the decay preset, then resetting the FSD and so on until the scale gives the correct law. Then, it is only necessary to trim the other range presets.

This circuit is capable of measuring very low frequency and it resolves after one cycle without drifting.

#### COMMENTS-

- 1- It can be used for many applications such as pulse rate monitoring.

- 2- The components marked with an asterisk should be low leakage polycarbonate or tantalum type capacitors.

-. (3-1) .-

#### CHAPTER-3

#### FREQUENCY MULTIPLYING TECHNIQUES -- A REVIEW

The frequency multiplication techniques have been described in many papers. The most common technique, however, is the use of phase lock loops (PLLs). Some of the main techniques are reviewed here as under:

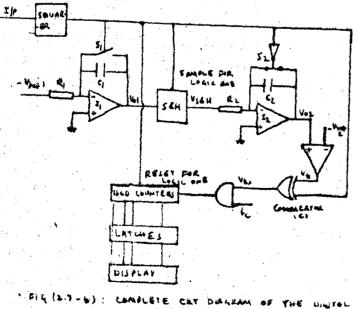

3.1 A METHOD FOR FREQUENCY MULTIPLICATION OF SQUARE WAVE:

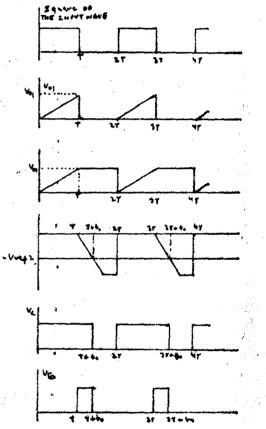

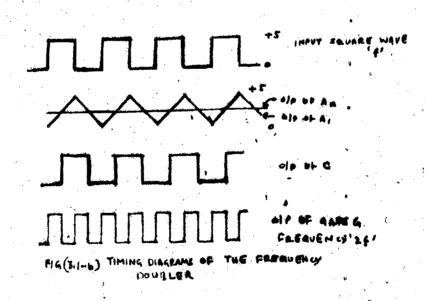

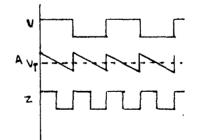

The method of multiplying the frequency by 2 (or powers of 2) is indicated in Fig (3.1-a). The system Fig (7.1-a) comprises a square generator integrator I, amplifier A, comparator C, averager A and an Exclusive OR gate G. The integrator provides an output which is propertional to the time integral of the input square wave signal.

The wave shape at the output of this integrator is triangular as shown in Fig.(3.1-b). This **k**riangular wave is amplified to the required amplitude by the amplifier A., the output of which is the input to comparator C. The other reference input to the comparator is the averaged output of the input square waveform. The two inputs to the exclusive OR Gate appear as shown in Fig.(3.1-a). The output of the Ex-OR gate corresponds to the frequency which is twice the input frequency (without any less synchronization). The timing diagrams are as shown in Fig.(3.1-b).

-. (3-1)

#### COMMENTS:

- 2) To multiply frequency by 2, if triangular wave input at comparator is made to vary from -3V to +3 V, then the reference voltage to the comparator is not required, if (reference point ) may be earthed.

- 3) For satisfactory centrol over pulse width, the reference voltage in both the circuits may be derived from a dc voltage ( A potentio meter adjust is preferable.).

- 4) This principle may be used for multiplying frequency by any number, subject of course to prectical limitations such as those imposed by IC elements particularly integrator.

## 3.2 FREQUENCY MULTIPLIER USES COMBINATIONAL LOGIC [10]

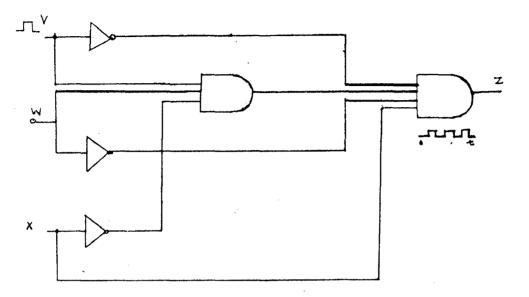

Relying on a technique that uses digital logic rather than high speed system clocks or non linear generators to perform frequency multiplication, these circuits derive square wave with an O/P frequency of up to four times that of the input signal.

Since the frequency doubler circuits are relatively simple and well known configurations exists, the logic technique is shown in Fig.(3.2-a) for frequency tripler. For frequency to be tripled input should travel three full cycles or six-half cycles (represented by states (101010) during the time of one input cycle (represented by 111000) at V. Thus the circuit must detect six different logic sta-

FIG. (3.2. a)

FIG(3.2.6)

FIG (3.2.C)

tes, and so a minimum of three input variables / U and X, is required.

ν.

(3**-2)**

Note, however, that the input signal at port V is the cnlywaveform available, and therefore, signals W and X whose logic states for a particular V are not yet known, must be derived from V itself. The particular values of W and X may be assigned to the truth table once it is realized that that the duty cycle of the three input variables are different and that the logic states of the dependent variables, W and X, must change at a faster rate than the independent variable, V. Once the logic states are assigned, the Boolean equation may be determined and the CKt synthesized with simple logic gates. Although several combinations of W and X may be assigned to a given V, the end result should be virtually the same in the Boolean Expression. However, it is important to assign the logic 1 states to W and X. Before the O states are assigned to them, because variables W and X not only change with the state of V but also vary with time when V is constant, as shown. Therefore, W and X can't be derived Directly from V in the digital domain. However, a negative going ramp voltage whose sweep rate is equal to twice the input frequency can with the aid of GP-Amp.threshold detectors, synthesize the digital signals required at W and X for the doubler, quatripler, quadrupler etc. (Fig. 3.1-c). COMMENTS-

There are several ways to generate the negative ramp voltage required, many of them constructed with multivibrators and OWP-Amps. -. (3-4) .-

The use of linear ramp (as shown in Fig. (3.2-b) allows easy determination of the threshold levels that must be detected in order to switch the logic elements at the proper times. Generally the number of comparator in the okt will be equal to N-1, where N is multiplication factor. Whose max.practical value is 8. The threshold voltage will be equally spaced if a linear ramp is used each voltage being equal to ME/N, where M is the comparator number and E is supply voltage:

# 3.3 FREQUENCY MULTIPLI, CATION USING FETS [11]

This method is based around the nonlinearities of a matched FETpair, involves forcing a ckt on the verge of regeneration into oscillation by injection of the I/P signal.

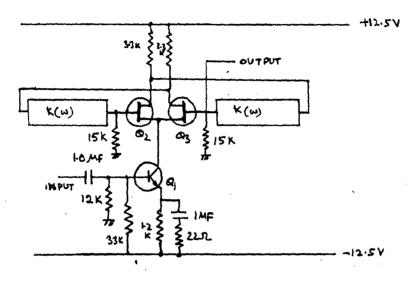

Here is a scheme for frequency multiplication using FET. Here positive feedback is applied Via two similar b and pass filters centred at the desired cutput frequency (K (W) in fig.(3.3ra)) If the input signal is square wave, then the modulated collector current of transistor  $Q_1$  is represented by the series:

$$I_{ac} = G_m \sum h_n e^{jnwt} n = 1,3,5 - (3.3.1)$$

Where G<sub>m</sub> is the trans-conductance of the bipolar transister Q<sub>1</sub>. Since the gate sourcevoltage is related to the root of the drain current in the junction f.e.t, the change

FIG B.4. A) JAMMING CIRCUIT DURING RESET TIME

in the common source voltage V may be represented by a Taylor series expanded about the d.c.biasing current of the form -

$$U = AI_{ac} + BI_{ac}^{2} + CI_{ac}^{3} + \dots$$

(3.3.2)

Where A, B,C are related to the 1st., 2nd and 3rd.order derivatives, the higher order terms being ignored. Sube Situation of equ.(3.3.1) into the above relationship yields-

$$U = \frac{AG_{M}}{z} \sum_{h_{n}e^{j_{n}wt}} + \frac{BG^{2}M}{4} \sum_{h_{n}e^{j_{n}wt}}^{2} + \frac{G_{m}^{3}}{4} \sum_{h_{n}e^{j_{n}wt}}^{2} + \frac{G_{m}^{3}}{4} \sum_{h_{n}e^{j_{n}wt}}^{2} + \frac{G_{m}^{3}}{4} \sum_{h_{n}e^{j_{n}wt}}^{3} = 1,3,5,7$$

$$= \sum_{a_{m}e}^{j_{m}wt} = 0,1,2... -- (3.3.3)$$

It is clear that, although the input signal contains only cod harmonics, both even and cod harmonics are present at the common source point. Expension of equation (3.3.3) shows that the even components are only generated by the squared term, while the odd components are produced by the linear and cubic terms. Note that each component am at the frequency mW is a series in which there are contributions from one or more of the three terms.

Stiftable manipulation of the mesh equations for the okt leads to a condition for regeneration at the O/P frequency mW, as given in (3.3.4).

$$1 = \left\{ g_{m} + \frac{1}{2} D(a_{2}m + a_{0}) \right\} K(w) R_{L} -- (3.3.4) \cdot$$

-. (3-6) .-

Where D is a constant and gm is the trans-conductance of thef.e.t. If the gain of the two filters is adjusted simultaneously, to a value just below the threshold of escillation, in the absence of an input signal, then the application of an input signal will force the okt into regeneration, due to the contribution of the agm and ar terms in equation (3.3.4). Since the input signal contains odd harmonies of the input frequency, regeneration at odd multiples is further added by the amplifying action of these input signal components, while regeneration at even multiples accurs only because of the variations in trans-conductance caused by the presence of the input signal. Larger output signals should thus be obtained for odd multiples of the input frequency due to this amplifying action within the escillator.

#### COMMENTS: -

1) A sinuscidal frequency multiplier, capable of operation at large multiples of the input frequency, has been constructed using the square low characteristics of a differential f.e.t.pair. As well as the advantage of sinuscidal output, high multiplication ratios and low jitter concontent, the okt also offers high input sensitivities e.g. the multiplier has been operated at signal levels as low as 5 mV(p-p).

2) Examination of the condition for regeneration shows that this excitation threshold may be reduced even further by selecting matched f.e.t.s with low pinch off voltages.

Central Library University of Roorkee

-. (3-7) ..

3) The #ynchronization band width of the okt depends stronly on the characteristics of the filters. A larger synchronizing Band width may be obtained by use of wider pass band higher selectivity filters, although this is not recommended for higher multiplies where two higher order harmonics are closely spaced in the frequency domain.

4) Demerit of the okt is that, in the look range phase of O/P depends on the I/P frequency. This is primarily due to the phase variations in the filter, as the required multiple deviates from the centre frequency, of the filters.Filter designs where phase variations in the pass band are minimised may be used to construct a multipliers where both frequency and phase remain synchronized to the I/P over its tracking range.

## 3.4 <u>A SYNCHRONIZED BROAD BAND SQUARE WAVE FREQUENCY</u> [12] MULTIPLIER

Here a circuit is described which produces simultaneeous cutput square wave whose frequencies are  $2^{i-1}(1 \le i \le N)$  times higher than the frequency of the original clock signal and are synchronized with it.

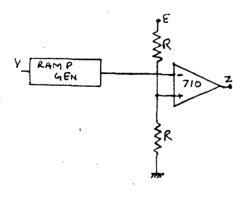

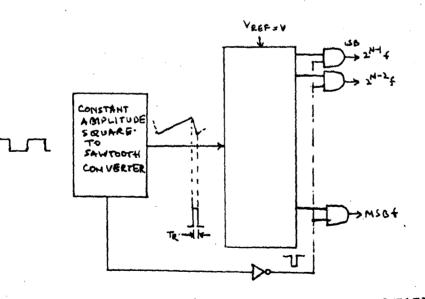

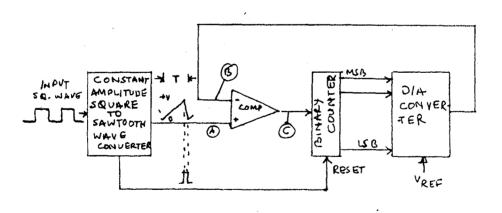

#### PRINCIPLE: Pl. ref.Fig.(3.4+a)

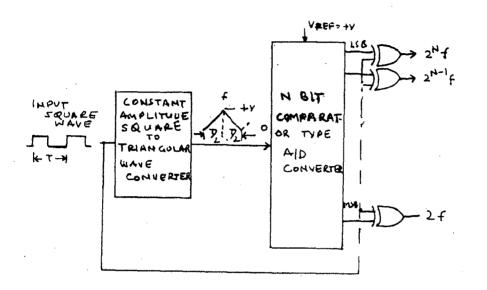

The input square wave of frequency f is first converted into a constant amplitude saw-tooth of the same frequency. This sawtooth is then fed into a comparator type (no clock) A/D converter. Each time the ramp is generated the MSB output changes state once at the mid time and once at the end time period to produce a symmetrical square wave of the same frequency f as the input wave.

The (MSB-1) output changes state at each quarter time period to produce a symmetrical square wave of frequency, 2f. Thus N simultaneous output signals are generated each having a frequency  $2^{i-1}(1 \le i \le N)$  times higher then incoming signal.

A finite duration reset pulse available from constant amplitude sawtooth wave generator is used as the jamming signal to eliminate undesirable change of states at the O/P of the A/D convertor during the finite time: It is to be noted that reset time  $t_R$  should be smaller than LSB O/P(period of highest frequency cutput).

#### COMMENTS:

1) To speed up multiplication, sawtooth generator can be replaced by triangular, wave generator. (Fig. 3.4-b ), Advantage of triangular wave is that no rapid transition is /the is required from the maximum to/minimum value. When the triangular wave reaches its maximum value the input square wave (50% duty cycle ) inverts the D/P states of the A/D converter. The result is same as if the ramp had been reset to zero with advantage of N bit A/D converter, the maximum frequency i.e.maximum frequency is increased or infact doubled.

2) By adding divide by N-counter at the proper O/P of the A/D converter some unusual multiplication factors can be obtained e.g.a divide by 3 counter is inserted on the

(3-8) .-

FIG (3.4.6) HIGH SPEED FREQUENCY MULTIPLIER

FIG (3.5.0.) BLOCK DIA GRAM OF THE NEW FREQUENCY MULTIPLER

-- (3-9) --

multiply by 8 0/P. The frequency at the O/P of the counter is new 8/3 times that of input signal. -3.5 -MODIFICATION [13]

Comparator type A/D convertor is not a common building block. This difficulty can be eliminated if we use D/A converter instead of A/D converter, i.e. The input square wave of frequency f is first transformed into sawt tooth wave form of frequency form the constant amplitude square to sawtooth wave converter as in Fig. (3.4-a). This sawtooth is then fed to comparator (Non-converting input) Comparator C/P is fed to Binary counters and outputs of binary counters are fed to D/A converters. The C/P of D/A converter is fed as feed-back signal to inverting input of comparator. (Fig. 3.5-a).

~\*\*\*\*

#### -= (3-10) .-

## 3.6 <u>A SIMPLE DESIGN FOR A DIGITAL PROGRAMMERE - FREQUENCY -</u> MULTIPLIER

[14]

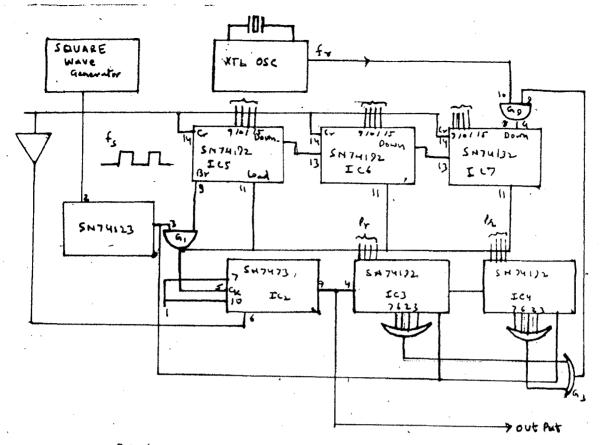

Here frequency multiplication is carried out by multiplying counters  $IC_5$ ,  $IC_6$ ,  $IC_7$  (SN 74192) at the upper part and by the control counters  $IC_2$ ,  $IC_3$ , IC4(SN7473) and SN-74192) at the lower part. The multiplying factor n can take values from 2 to 99 and can be extended to any value if the specification of the elements allow.

#### SEQUENCE OF OPERATION:

1- Frequency to be multiplied ( $f_s$ ) is generated by the square wave generator. The leading edge of the square-wave triggers a one shot multivibrator, IC<sub>1</sub> (SN 74123). Avery narrow negative pulse is produced by the D/P of Q ( $P_{in}^4$ ) to initiate the ckt operation. Simultaneously three actions occur.

(a) The O/P IC<sub>2</sub> from P<sub>in</sub>9 is initiated from reset 'O 'to logic '**1**' state by this negative clock pulse, which can be used as a synchronizing signal and a check pulse for every cycle.

(b) The multiplying counters  $IC_5$ ,  $IC_6$ ,  $IC_7$  are loaded with this negative pulse as they are previously preset to a value of the pins 9, 10, 1 and 15 in each decade counter. This preset value can be expressed as  $T_s/2n$  where  $T_s$  is

FIG. (3.6. a.)

FIG (3.7. a) SIMPLE Frequency Doubles

-- (3-**1**) .-

the period of the input frequency  $f_s$  and n, the factor of the desired multiplication.

(c) The control counters  $IC_2$ ,  $IC_3$ , and  $IC_4$  are also loaded with this signal to the previously preset value of n,where n has the same value as above.

2- As scon as the multiplying counters and control counters are loaded the multiplying counter begins to count down from the present value to zero. Since at this moment the AND gate G<sub>2</sub> is enabled by the OR gate G<sub>3</sub>.

3- When the contents of the decade counters of the multi-/zero, plying counter reach/a negative pulse is produced by the O/P borrow (Br) from the last stage of the decade counter. The O/P IC<sub>2</sub> from pin 9 is again changed from logic '1'to logic '0' state by this negative pulse, which, however,only loads the multiplying counter.

4- The contents of the centrel counters IC3 and IC4 will be decreased by one of the cutput IC2 completes one cycle. These processes will be repeated until the contents of the /output control counters reach zero, when the/IC2 complete i cycles. Then gate G2 is inhibited by gate G3 since the O/P G3 is logic 'O' as soon as the contents of all decade counters are zero.

5- The operation of the ckt is restarted by the input of /synchronous a/pulse which is produced by the leading edge of the source square wave. Even if, this synchronous signal is not coincident with the inhibited action, the inhibited state will be hald until the synchronous pulse occurs, Therefore, there is no accumulated error in this system.

(3-12) (3**-27)**

#### COMMENTS-

- 1) Reference frequency should be generated from cystal oscillator \$0 get good accuracy.

- 2) Reference frequency (f<sub>r</sub>) should be sufficiently higher than f<sub>s</sub>. Higher the frequency f<sub>r</sub> the greater the accuracy of 0/P frequency f<sub>n</sub>, Generally, f<sub>r</sub> > 100 fs.

- 3) When the input square wave has disappeared, this system is always inhibited by Gate  $G_2$  and no output wave form is produced from  $IC_2$ .

- 4) The multiplication factor n can take non integral values, such as n = 1.5, 2.5.

- 5) The elements of the ckt are simple and cheap, no linear devices are involved.

- 6) The hardware of the ckt does not change if n is changed.

- 7) The preset values for the multiplier n are easy and can be programmable. No reference voltages are required.

- B) The errors of the O/P wave forms are not accummulated. because a Synchronizing signal is produced in every cycle to check and initiate and multiplyin frequency.

- 9) The system can be extended by any number of multipliers subject to practical limitation such as the frequency response imposed by the I.C. elements.

#### -. (3-13) .-

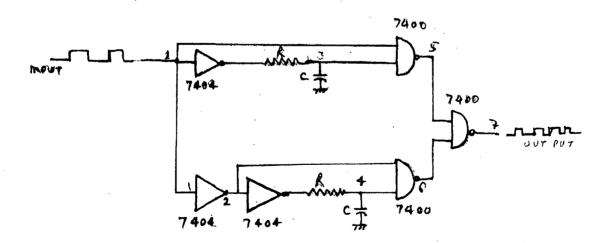

3.7 <u>A SIMPLE DIGITAL 2<sup>n</sup> FREQUENCY MULTIPLIER</u> [15] PRINCIPLE -

When the pulse input at point 1 is in the LOW state. the capacitor C at point 3 gets charged through a resistors R to HIGH level and the point 5 continues to be at logic level HIGH. As the pulse input under-goes transition from LOW to HIGH level, the point 5 changes to logic level LOW, meanwhile the capacitor C at print 3 starts discharging through resistor R, and as seen as potential at point 3 reaches VIL which is the maximum voltage level considered as as LOW at the input of TTL devices, point 5 goes to lotic level HIGH. Thus at point 5, a megative pulse of duration corresponding to the discharge time of capacitor C to Vy is produced and the cycle continues. The voltage pulse available at point 2 is 180° out of phase with that at the point 1. A similar sequence of operations produces negative pulse at point 6 but out of phase by 180° with those at point '5'. The cutput at point 7 is a combination of the pulse produced at point 5, and point 6 but with reversed polarity. Thus the O/P pulses have been produced at the leading as well as at the trailing edge of the input square wave, whereby frequency drubling is achieved. The pulse width and duty cycle of output pulses can be simply controlled by suitably selecting the resistance and capacitance values Fig.(3.7-a). We can obtain upto 50% duty cycle by choosing appropriate values of R and C for any given frequency. For Symmetrical cutput, R and C should have equal value.

-• (3-124) •-

#### COMMENTS: -

1) Frequency quacrupling can be achieved by feeding the input square wave directly to a frequency coubler, phase shifting the doubler O/P by 90<sup>0</sup> and combining the phase shifted output with doubler cutput in an Exclusive- OR gate. By varying  $R_T$  and  $C_T$  of the momeshet, the phase shift can be set according to  $180^{\circ}/2^{n-1}$  at any desired value [15]

2) Such a multiplier was tested over a frequency range of 1.5  $\text{KH}_z$ -10  $\text{MH}_z$  with R= 1K(pot); C = 470 PF, monoshot timing resistor R<sub>T</sub> = 5 K(Pot) and C<sub>T</sub> = 200PF.Output train of pulses of variable duty cycle (upto 50%) were obtained at twice and four times the input signal frequency over this frequency range.

3) RC time constant has to be  $\sqrt{1/2^{n+1}}$  and RT CT  $\leq 1/2^{n}$  where T is the time period of the input square wave. These constraints decide the limit of the operating frequency range of the multiplier.

4) This ckt can operate over a very wide frequency range and upto 50% duty cycle of the output pulses is achieved.

# 3.8 A FREQUENCY DOUBLER FOR RECTANGULAR INPUT

The main drawback of method described in **S**, is that values of R and C should be critical to obtain a square wave O/P from each stage. This restricts use of such multiplier to one single input frequency.

FIG(3.8.a) CIRCUIT SCHEMATIC OF FREQUENCY DOUBLER

WAVE FORMS PERTAINING TO OPERATION OF GROUT. This paper describes frequency doubler which first converts a given rectangular input signal to a square wave whose frequency can then be doubled easily. Hence the difficulty faced in [15] is eliminated.

#### PRINCIPLE:

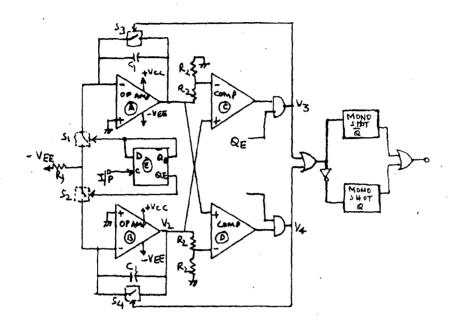

The first part of the ckt converts the rectangular input into a square wave Fig.(3.8-a). This part consists of two OP AMP integrators A and B, which alternately measure and store the period information of the input signal.

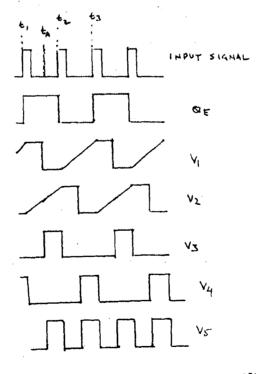

Referring to Fig.(3.8-b), the interval  $t_1$  to  $t_2$  represents one typical cycle of the input signal, whose peried is T. during the interval between  $t_1$  and  $t_2$ , the Q O/P of the toggle flip flop E is high and consequently the switch S<sub>1</sub> is opened and S<sub>2</sub> is closed.

At the instant  $t_1$ , the O/P voltage V<sub>2</sub> of the integrator B is zero, where-as the O/P V<sub>1</sub> of the integrator A is equal to the voltage integrated during the previous cycle and **is** given by-

$V_1(t_1) = \frac{T}{R_1C_1} V_{EE}$  -- (3.8.1)

During the interval  $t_1$  to  $t_2$ , the voltage V<sub>1</sub> remains constant whereas V<sub>2</sub> increases linearly as given by---

$$V_2(t) = \frac{(t-t_1)}{R_1 C_1} V_{EE}$$

-- (3.8.2)

In the beginning of this cycle  $V_2$  being small, the O/P of the comparator C is low and consequently  $V_3$  and  $V_5$  are also low. As seen as  $V_2$  becomes more than  $V_1/2$ , the O/P of the comparator C becomes high, thus making  $V_5$  to go high. The time constant  $t_A$  at which this happens is obviously given by (from equation (3.8.1) and (3.8.2):

$$t_A = t_1 + \frac{T}{1}$$

-- (3.8.3)

In other words  $t_A$  is the midpoint in the cycle. It is thus seen that  $V_5$  is low during the first half of the cycle and high, during the second half. Immediately after  $t_A$ , the switch  $S_3$  is closed, thus discharging the integrating capacitor of the integrator B.

During the next cycle (the interval  $t_2$  to  $t_3$ ) the Q O/P of the F/F, E gres low. Consequently,  $S_2$  is opened and  $S_1$  is closed. The voltage  $V_1$  now increases linearly whereas  $V_2$  retains the value integrated during the previous cycle (given by right hand side of equation (3.8.1).During this cycle the comparator D delivers a pulse of width T/2 to  $V_5$ .

It is thus **even** that the comparators C and D alternately deliver pulses of width T/2 to  $V_5$ , thus generating a square wave at a frequency equal to the input signal frequency. The frequency of this square wave is doubled using two monoshots, one triggered by its leading edge and the other by its trailing edge. The O/Ps of the two monoshots are combined in an OR gate to generate the frequency doubled signal. The duty cycle of this signal will be a function of the monoshot's period and the input signal period. This O/P can be converted into a square wave if necessary by

-. (3-16) .-

using any frequency doubling techniques; such as described in [157].

-. (3-17)

#### COMMENTS:

- 1) Here values of R and C are not critical.

- 2)  $R_1C_1$  time constant should be such that the maximum value attained by V<sub>1</sub> and V<sub>2</sub> is below the positive supply voltage even at the lowest frequency of the operation.

- 3) The maximum speed of operation of the okt is determined by the (gain X band- width ) products of the OP- AMPs and and the sensitivity of the comparators,

- 4) The duty cycle of the square wave at  $V_5$  can be trimmed by inserting two small variable resistors, one in series with  $S_1$  and the other in series with  $S_2$  (in fact only one of these resistors need be variable. The other can be a fixed resistor with a value equal to mid value of variable resistor ). This trimming will compensate for /between the two integrators capacitors and also any mis-match/in the two matched resistors pairs  $R_2$ .

- 5) This type of frequency dcubler was fabricated and tested. The OP- AMP used are IC 741 and comparator are IC 710. The switches used are CMOS switches and of CD4016 type. The logic gates and the monoshots are of the standard IIL-type. The time constant of the two integrat. Swas set to around 15 ms. The resistor R<sub>2</sub> were 10 Kr. The okt was tested in range of 100 H<sub>z</sub>- ZiKH, satisfactorily.

- -. (3-18) .-

- 6) This ckt works independently or the frequency and duty cycle of the input signal and does not need critical adjustment of the components. This makes the ckt versatile and useful in a wide range of explications.

- 7) A2<sup>n</sup> frequency multiplier can be constructed by casceding n such doublers.

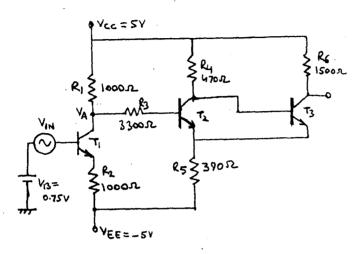

- 3.9. SIMPLE FREQUENCY DOUBLING SCHMITT TRIGGER CKT (Ref. Fig. (3.9-a)

Here in this circuit voltage comparison and frequency doubling functions are combined in an extremly simple circuit realization. Since only three transistors are required, it can be constructed with a single integrated nPn transistor array, such as the CA3086. With this ckt a sinuscidal input voltage is converted to a digital pulse train with one half the input period; or twice the frequency.

#### PRINCIPLE:

Here input stage is a full wave rectifier. Transistor  $T_1$  is biased with V<sub>B</sub> such that it is saturated. With  $R_1$  and  $R_2$  equal, symmetrical V<sub>CC</sub> and V<sub>EE</sub>, and a sinusoidal input  $V_{IN}$ , the voltage on collector of  $T_1$ ,  $V_A$ , will be a full wave rectified sine wave. As sinusoidal  $V_{IN}$  goes positive,  $T_1$  will be driven further into saturation. If we assume the collector emitter and base-emitter voltages in saturation to be nearly constant, then  $V_A$  will be approximately  $V_{IN}$ . As  $V_{IN}$  goes negative,  $T_1$  will be driven out of saturation and  $V_A$  will be approximately the magnitude of  $V_{IN}$  since  $R_1$  and  $R_2$  are equal. Thus,

FIG. (3-10. A) CONSTANT DUTY CYCLE DIGITAL FREQUENCY DOUBLER

. (3-19)

a full wave rectified sine wave will be developed at  $V_A$ . Distortion `in the rectified waveform from the ideal due to the variations in  $V_{BE}$  and  $V_{CE}$  in saturation with input signal amplitude, resistor mismatch, finite r and temperature dependence of function voltage and currents will be present but is not considered significant in this digital application. Transistors  $T_2$  and  $T_3$  form a simple schmitt trigger. Resistors  $R_4$ ,  $R_5$  and  $R_6$  are selected to yield the desired threshold voltages and hysteresis. For a voltage input  $V_A$  less than either threshold,  $T_2$  will be cut off and  $T_3$  will be operated in the forward active region or in saturation such that the low output state is TTL voltage compatible with  $V_{OUT}$  0.4V. As the voltage  $V_A$  increases above the upper threshold,  $T_2$  is turned on to the extent that  $T_3$  is **CM** to off, and  $V_{OUT}$  goes to its high state,  $V_{CC}$ . The upper threshold is approximately-

$$V_{TH_U} = V_{EE} + V_{BE} + \frac{(V_{E} - V_{EE})R_6}{R_6 \frac{R_4 R_5}{R_4 + R_5}} -- (3.9+1)$$

As the input continues through its cycle and decreases below the upper threshold, T<sub>2</sub> is again cut off and T<sub>3</sub> saturated when the lower threshold is encountered. The lower threshold is approximately -

$\mathbb{V}_{\text{TH}_{L}} = \frac{V_{\text{CC}}R_6 + V_{\text{EE}}R_4}{R_4 + R_6} + V_{\text{BE}} -- (3.9.2)$

Thus this simple three transistor circuit can develop a TTL voltage compatible digital pulse train with twice the frequency of the input.

#### COMMENTS: -

Choosing power supply voltage and resistor values 10% shown in Fig.(3.9-a), we obtain measured threshold voltages of about 0.6V and 0.9V and a TTL compatible output voltage swing of 0-5V. Typical wave forms are shown in Fig.(3.8-b) The centre wave form is the 2.4V peak to peak 2.5 KH<sub>2</sub>'sinu-soidal input,  $V_{IN}$ . The top trace is 1.1V peak-peak rectified waveform  $V_A$ . The bottom trace shows the approximately OV- 5V, 5 KH<sub>2</sub> O/P pulse train.

Thus this technique for developing a doubled pulse rate is effective and completely integrable in standard bipolar technologies. It can also be realized with a single integrated npn transistor array since only three transistors are required.

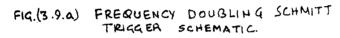

# 3.10 A SIMPLE CONSTANT-DUTY- CYCLE DIGITAL FREQUENCY [18]

#### PRINCIPLE - "' (3.10-a)

It consists of two units. The upper unit produces output pulses at the leading edges of the input pulses and the lower unit at the trailing edges. These two output pulse trains are then combined in a NAND gate. The duty cycle of the output pulses can be easily set at any desired value up to 50% by properly adjusting the potentiometers  $R_4$ . COMM ENTS:

1- Such frequency deobler modules having a constant duty cycle over large frequency range can be easily cascaded to obtain a higher order of frequency multiplication.

-. (3-21)

2- The transistor types and other values used are not critical.

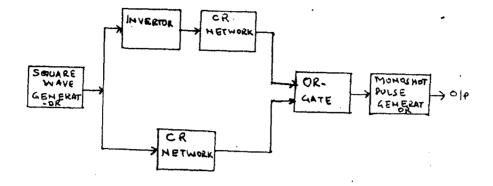

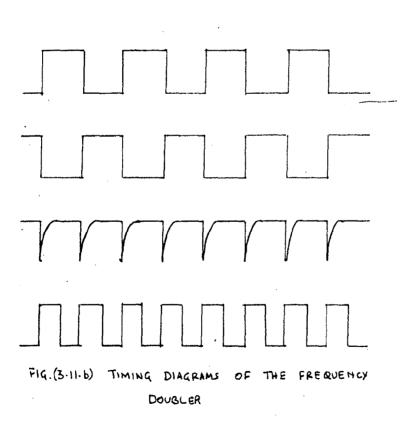

3.11 <u>A SYNCHRONIZED FREQUENCY MULTIPLIER FOR SQUARE WAVES</u>

The monoshot pulse generator is adjusted for a quarter, wave delay that given an O/P which is double the input frequency. The input is generated from 555 timer using as an astable multivibrator having a frequency of 1 KH<sub>z</sub> and the tuning components carefully choosen to obtain a duty cycle of 50%.

The scheme consists of square wave generator, an invertor (using a silicon np m transistor) two RC differenciating networks, an OR gate (Using two silicon diodes) and a monoshot pulse generator having a pulse width of T/4 where T is the period of the input square wave. The time constant of each R-C differentiating network should be much smaller than T. The O/P of the OR Gate is negative going trigger pulses (spikes) with a period of T/2 as shown in Fig. (3.11-b) and these are used as the external trigger pulse required to operate the monoshot pulse generator. The letter

.

has a square wave O/P with a frequency which is double the input frequency (Without loss of Synchronizations).Higher multiplication can also be achieved subject to the frequency limitations imposed by the 555 timer.

#### COMMENTS: -

- 1) The circuits were tested for input frequency of 1KH,

- 2) The circuits were tested as doubler and tripler and satisfactory results were achieved.

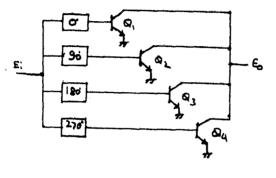

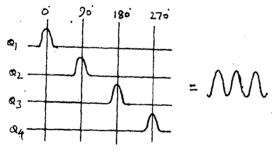

3.12 <u>PHASE SHIFTER SIMPLIFY FREQUENCY MULTIPLIER DESIGN</u> PRINCIPLE - (Ref. FIG. 3.12-a)

The phase shift frequency multipliers, unlike conventional multipliers can produce a spectrally pure O/P without filtering. However, by using wide band phaseddifference network for phase splitting, frequency independent multipliers over many octaves may be obtained. The Fig.(3.12-a) shows sine wave frequency is multiplied/timesby dividing input into N different phases that are equally spaced through  $360^{\circ}$ . These N phase drive N class C transisetrs whose outputs are combined to deliver a pulse every  $360^{\circ}$ /N. The use of N transisters allows the input power to the circuit to be N times as high as without saturating the transisters.

1) The phase shift frequency multipliers are superior to conventional multipliers at high frequency es in subharmonic suppression. A high frequency version of this

FIG. (3.12. a) QUADRUPLER.

PIG. (3.13.4) FRACTIOAL FREQ MULTIPLIER.

type of multiplier and quadrupler has also been given in [20] 2) An interesting property of this type of net-work is that when rectances are made equal, the phase shift between the input and output ports will always be  $90^{\circ}$ , regardless of the value of R. This property allows both amplitude (varying R ) and phase (varying L OR C ) control.

3) The inductance L is created by the primary winding of  $T_1$ , the secondary windings delivers a 90<sup>0</sup> and 270<sup>0</sup> phase shift of  $Q_1$  and  $Q_2$  respectively. The 0<sup>0</sup> and 180<sup>0</sup> phase shifts are provided by  $T_2$  to  $Q_3$  and  $Q_4$ .

4) In addition, the L-P<sub>i</sub> network at the O/P provides an optimum match to a 50r load and a little attenuation of subharmonics. This multiplier, unlike conventional ones, is capable of suppressing subharmonies and therefore, does not require O/P filt. ering.

5) A spectrum analyser display showed that the second and third harmonies could easily be reduced by more than 50 decibels below the desired fourth harmonies.

3.13 JOINING A PLL AND VCO FORMS PRACTIONAL FREQUENCY MULTI-PLIER: [21]

The conventional multiplication ekts employing PLL use either harmonic locking or a frequency divider between its VCO and phase comparator. Thus the O/P is only an integer multiple of the input. As a result if certain O/P frequency is desired, the input frequency must be carefully selected. Such exact choosing is no longer needed because this circuit can multiply pulse frequencies by any real number through the simple adjustment of two potentiometers. In addition, it operates over a wide input frequency range and has a more stable D/P than do conventional multipliers.

#### PRINCIPLE-

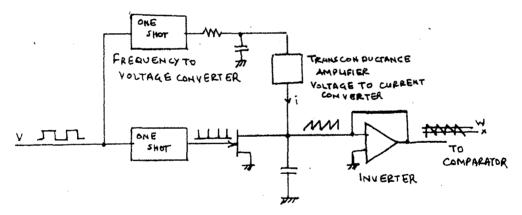

The design combines a PLL frequency to voltage converter and an external VCO for pulse frequency multiplication.

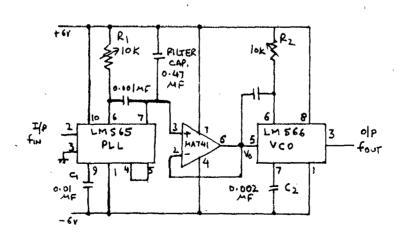

A PLL connected as a frequency demodulator, generates voltage Vd that is related to the input frequency by Vd = Kfin, where K is a constant and fin is the frequency of the input signal. In addition, the input frequency of the internal VCO (contained in the PLL ) is  $f_{in} = \frac{Vd}{VR_1C_1}$  where  $R_1$  and  $C_1$  are the frequency determining components of the internal VCO and V is the supply voltage.

Demcdulated voltage V<sub>d</sub> is fed to the control voltage input of the external VCD whose D/P frequency is  $f_c = V_d/VR_2C_2$  where  $R_2, C_2$  are frequency determining components of the external VCD, Solving for the D/P frequency,  $f_c = f_{in} R_1C_1/R_2C_2$  and thus  $n = \frac{\int_{R_2C_2}^{R_1C_1}$ . The multiplication factor n is only decided by the externally connected resistors and capacitors and therefore can be choosen for any value.

The ckt uses National Semi-conductor's general Purpose LM565 and LM 566 as PLL and VCO respectively. OP AMp  $\mu$ A741 serves as buffers between the two.

-. (3-2**5**) .

#### COMMENTS -

- Circuit with multiplication factor of 6.15 is tested for input frequency in the range of 2-6 KH<sub>7</sub>.

- 2) For stable operation  $R_1$  and  $C_1$  should be selected according to input frequency and  $R_2C_2$  should be choosen to general desired multiplication factor.

# 3.14 A SYNCHRONOUS FREQUENCY MULTIPLIER USING PLL

#### PRINCIPLE-

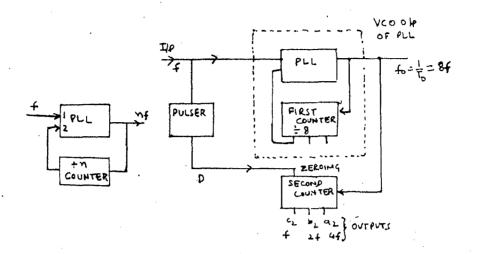

• PLL are the lower cost approach to frequency multiplication using a divide by n counter in the feedback part as shown in figure (3.14-a). In this arrangement, there is usually a phase difference between inputs 1 and 2 of the PLL. This difference does not have long time stability and may change because of the emplitude and the frequency variation of the input signal. That is why the PLL does not provide a synchronized O/P in this system.

To obtain a synchronized O/P one can consider a system like in Fig.(3.14-b). This uses a second counter equal to first one in the feedback loop and a pulser which produces pulse at the negative going edge of the input square wave.

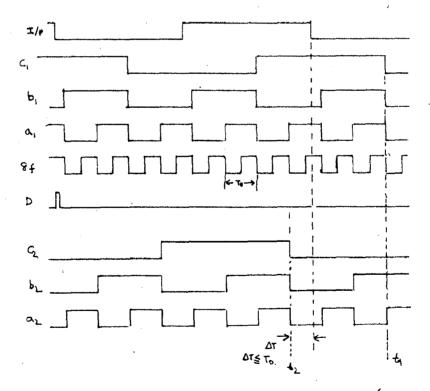

The operation of the ckt can be explained as follows w.r. to Fig.(3.14-C).Let  $t_1$  is the instant when  $a_1$ ,  $b_1$ ,  $c_1$  all go to negative simultaneously and  $t_2$  where  $a_2$ ,  $b_2$ ,  $c_2$  all go to negative simultaneously by the reset pulse coming from the pulser. As can be seen,  $t_2$  is always closer than  $t_1$  to the negative going edge of the input with an error  $T_0$ : which is the period

WAVE FORMS AT VARIOUS POINTS OF CKT (3-14-6) FIG. (3.14. C)

-. (3-2**6**) .

of the VCO O/P of the PLL. We thus can consider the O/Ps  $a_2, b_2$  coarsely or with an error-

$$t \leq t_0$$

-- (3.14.1)

synchronized with the input. It is to be noted  $C_2$  has smaller relative error than the O/Ps b2, a2. If we make-

▲ T < < < The multiple output period -- (3.14.2) or equal practically to zero we may accept the D/P synchromized with the input. The Fig.(3.14-d) shows PLL, divide by n counter and two equal divide by m counters and a pulser. Since the PLL has jitter, an undesirable change may occur every time the reset pulse is applied to the counter. The absolute error or jitter width is given by-

$\Delta t \leq$  the period of the VCO OPP =  $\frac{1}{mnf}$  -- (3.14.3) according to the above mentioned result (3.14.1). The max. relative error at the O/P can be expressed by -

$$e_{12} = \frac{t_{max}}{1/nf} = \frac{1}{m}$$

-- (3.14.4)

It is obvious that this error can be minimized by choosing m large enough. But because of the maximum frequency  $(f_{max})$  of VCO characteristics m is limited **SUP**h that-

By using(3.14.4) and (3.14.5) one can determine the maximum multiplication rate for a given frequency.

#### -. (3-27) .-

#### COMMENTS:

- 1) The ckt was tested for  $f_{in} = 50 \text{ H}_Z$ , n = 12 and m = 256. In these measurements jitter width has never exceeded 6.5 µS. This result satisfies the error squation(3.14.4). The maximum relative error at the O/P is 0.4%. It can be made even smaller by choosing a proper PLL.

- 2) The synchronization is only achieved in the tracking range of the PLL. The tracking range is =30% of the input frequency in the practical ckt.

- 3) The method can be regarded as a convenient one for low frequency synchronous frequency multiplication with an acceptable error.

- 4) The maximum multiplication ratio is limited by the maximum operating frequency of VCO characteristics and the given error limit.

- 5) The transient response to changes in the input frequency will be dependent on characteristics of the filter used in PLL.

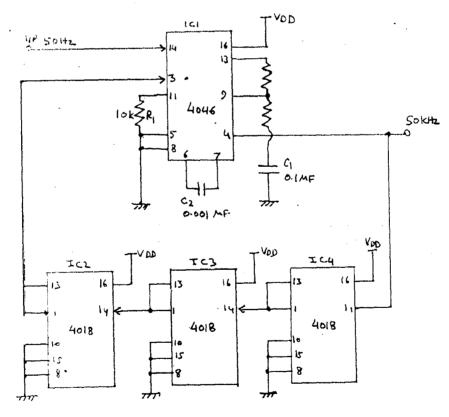

# 3.15 A HIGH RESOLUTION FREQUENCY METER FOR 50Hz [23]

The input signal (a sine wave of nominal frequency  $50H_z$  is amplified and limited to produce a square wave. This signal is applied to an inexponsive CMOS (PLL )IC (CD 4046 )

FREQUENCY MULTIPLIER .

. (3-28)

which contains a controlled **P**scillator. The **P**scillator cutput is divided and is applied to the PLL comparator input. The PLL will lock when the signal at the comparator input is in phase with the input signal to the PLL. Hence, if the input frequency is  $50H_z$ , the oscillator frequency will be 50 x 1000 = $50KH_z$ The 50 KH<sub>z</sub> signal may be applied to a conventional frequency counter which, by programming the decimal point, may be made to display the input frequency as 50000 with a gate time of -ever 1 sec., the resolution is how 1 part in 50,000 (0.002%).

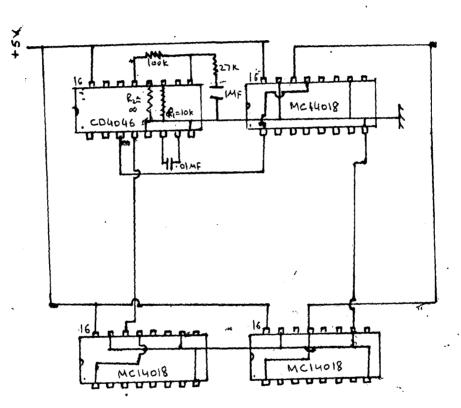

The Fig.(3.15-a) shows the practical realization of the above. The PLL is a CMOS 4046 and the dividers are 3 x CMOS 4018. With the component values showmand a supply voltage of 5V, the circuit had a locking range of app.30-70H<sub>z</sub>.

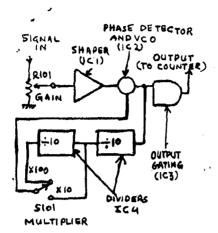

3-16 FREQUENCY MULTIPLIER FOR YOUR COUNTER

#### PRINCIPLE AND WORKING

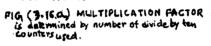

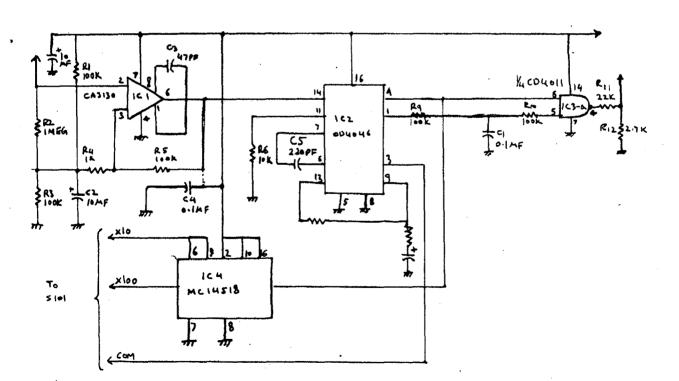

It is basically a PLL (phase lock loop ) circuit it has X 10 and X 100 cutputs. Low frequency signal appearing at the input pass through the GAIN potenticmeter, which permits the frequency multiplier to handle a very wide range of signal levels. Then, the attenuated signal drives IC<sub>1</sub>, which shapes it into a square wave. That signal drives phase detector IC<sub>2</sub>.

Another part of the same IC also serves as a VCO (voltage controlled oscillator). It accepts a DC Voltage from the phase detector and generates a square wave signal. The VCO can generate signals ranging from under 100  $H_z$  to over 400 KHz without any switching. From the VCO, the signal-path branches cut.

-----

A LOGIC HIGH OUTPUT from Pin1 of 102 indicates that the PLL is Locked

FIG. (3.16.6) : FREQUENCY MULTIPLYING SCHEME.

.

. . . .

**-.** (3--29) .-

One branch takes the signal to IC3, a NAND gate, that gate acts as a switch and allows signal to pass to the frequency counter only when the PLL is locked on to a good signal. That suppresses the stray readings one can normally get without an input signal, or with signals the device can't handle. The output from the VCD also drives two divide by ten counters, both or which are contained in IC4. The outputs from the dividers are selected by S101 the MULTIPLIER switch. The output selected drives the phase detector, which generates the DC control voltage for VCO. Thus a simple PLL circuit, that can generate free quencies ten times or a hundred times the input frequency, is formed.

ICI, the shaper amp consists of a fast CMOS CA3130 OP-AMP Its high frequency response is reduced by  $C_3$  so the circuit won't oscillate. You will have flat gain over its  $10H_z$  to  $40KH_z$ input range. The inputs of the OP-Amp are biased to half the supply voltage by  $R_1$  and  $R_3$ , eliminating the need for a split (positive and negative voltages) power supply.

Resisters  $R_4$  and  $R_5$  set the hystersis or "trip " point for the circuit, which is about 350 mV. The output signal is a 9.0 Volts square wave that drives the phase detector portion of IC<sub>2</sub>. The phase detector compares the signal with that from the MULTIPLIER switch, and outputs a DC voltage at pin 13 of the IC. That drives a network known as loop filter, which smooths out the pulses from the phase detector, giving a clean DC signal. -. (3-30) .-

The VCO input is at pin 9 of IC2 and the timing capacitor that sets the frequency range is 65. The VCO cutput appears at pin 4, and drives both IC 3 and IC4. Resistors  $R_q$  and capacitor C7 form another filter to "debounce" the signal from pin 1 of IC2 (which indicates that the PLL is locked on to the signal.). so that it can enable IC3-a's NAND gate whenever a good signal is present at pin 4 of IC2. Resistor R10 is included so that the charge on C7 won't blow IC3 when the power is turned off. The cutput of IC3 is reduced by R11 and R12 about 900 mV peak to caak, which is a comfortable level for most counters. The remaining circuitry consists of a standard CMOS dual divide by 10 counter IC4.

#### COMMENTS -

- One has to remember to mentally shift the decimal point one place to the left while using the X 10 range and two places to the left while using the X 100 range.

- 2) VCO range of unit is 100 H<sub>z</sub> 40 KH<sub>2</sub> MULTIPLIER Switch set at (X 10) position mean one can measure in the range of  $10H_z$ 4KH<sub>z</sub> and MULTIPLIER (Switch Set ) at (X 100 ) position means again **GNO** can measure in the range of  $10H_z - 4KH_z$ .

- 3) Gain can be increased by reducing  $R_4$ .

#### 25) 3.17 LOW FREQUENCY MEASURING CIRCUIT USING PLL

#### PRINCIPLE-

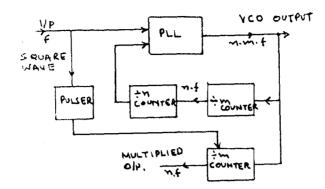

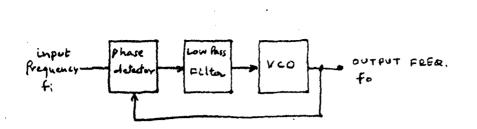

A PLL with a 3 decade dividers inserted into its feedback path creates a frequency multiplier that allows Us to measure low (e.g.power ling) frequencies accurately and quickly.

FIG. 3.17. (a)

-. (3-31) .-

The circuit in figure is set for  $50H_z$  and can be adjusted by R<sub>1</sub>, R<sub>2</sub> and C<sub>1</sub> to match power lime frequency.

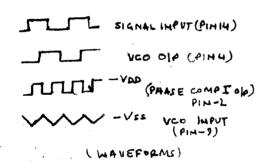

The VCO in ICI produces an cutput whose frequency is determined by the time constant of  $R_1$  and  $R_2$  (about 50 KHz for given component values), IG; s phase comparator modulates this frequency. The 3 decade counter comprising IC2 through IC4 divides the VCO'S O/P by 1000 and applies its cutput to one of the PLL'S phase comparator input; the input signal to be measured is applied to the other phase comparator input.

The VCO'S frequency is thus the input frequency X 1000 and this frequency can be measured using conventional methods.

~\*×

-. (4-1) .

#### CHAPTER-4

## PLL - THEORY AND DESCRIPTION [26], 27][28][29][كس)(كمر)[كس] BASIC PRINCIPLE -

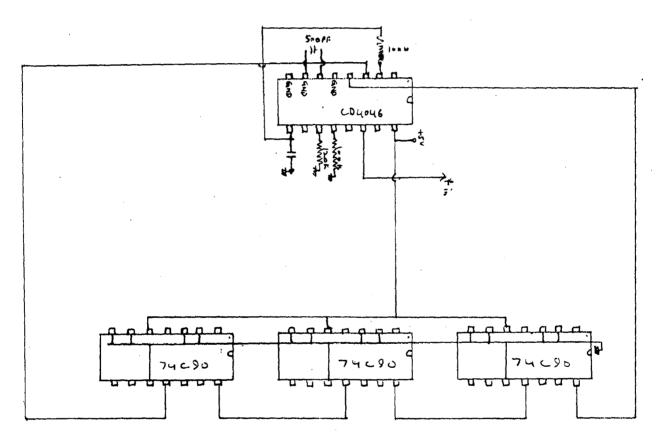

The phase lock loop is basically an electronic feed back loop system consisting of:

1- A phase detector or comparator

2- A low pass Filter

3- A Voltage controlled Oscillator (VCO ). (Ref. FIG.4.1-a)

The VCO is a free running oscillator, the frequency of which is normally determined by an external resistor-capacitor or an inductor-capacitor network. The VCO frequency  $f_0$  is fed back to the phase detector where it is compared with the frequency of the input signal (fi). The cutput of the phase detector is the error voltage, which is an average dc voltage proportional to the difference in fr quency(fi-fc) and phase  $\emptyset$  of the input and VCO.

The error voltage is then filtered, thus removing traces of higher frequency noise. This, in turn, is then fed to the VCO to complete the loop. In addition, the error voltages forces the frequency of VCO to change in a direction that reduces the frequency difference between the input and the VCO. Once the VCO starts to change frequency, the loop is in the capture range. This process continues until the VCO and the input frequencies are exactly the same. At this point, the loop is synchronized, or phase looked. During phase look, the VCO frequency is identical to the input of the loop, ex-(4.1.P) -

FIG (4.1. a.) BASIC PHASE LOCK LOOP SCHEME.

() TWO INDUT EX. OR GATE

except for a finite phase difference, which is required to generate the necessary error voltage that shifts the VCO frequency, keeing the loop in phase look. This repetitive action of the loop system then tracks, or follows, any change in the input frequency while phase looked. We can say that the phase looked loop has three distinct states:

1- Free running

2- Capture

3- Phase lrck.

The rance over which the loop system will follow changes in the input frequency is called the lock range. On the other /the loop hand, the frequency range in which/acquires phase lock is the capture range, and is never greater than the lock range. The dynamic characteristics of the phase lock loop are controlled primarily by Low Pass Filter. If the difference between the input and VCO frequencies is significantly large, the resultant signal may be too high to be passed by the filter. Consequently, the signal is out of the capture range of the lcop. Once the lcop is phase locked, the filter only limits the speed of the loop's ability to track changes in the input frequency. In addition, the loop filter provides a sort of short term memory, ensuring a rapid recapture of the signal if the system is thrown out of the lock by a noise transient.

#### 4.2 THE PHASE DETECTOR

All phase locked loop systems use a circuit called a phase detector or phase comparator. The phase detector

generates an average, or do, output voltage that is propertional to the phase difference between the input of phase . c looked loop and VCO. The output voltage is often referred to as the error voltage .The factor that convert phase difference into voltage is called the phase detector conversion gain, so that-

$V_{\rm C} = K \not a \not a \not a \qquad -- \qquad (4.2.1)$

Where,  $V_{0}$  is the average cutput voltage of the phase detector (V) KØ is the phase detector conversion gain in volts/radin,

ø is the input phase difference in radians.

NOTE - When working with PLL, it is customary to express phase difference in terms of radians.

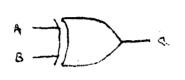

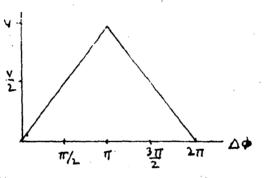

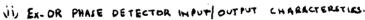

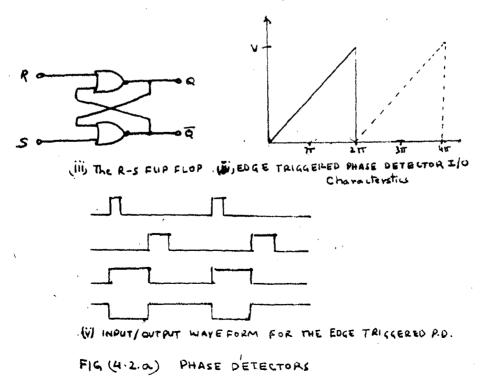

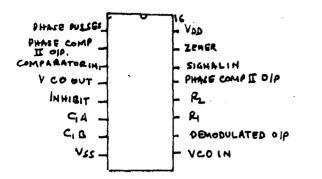

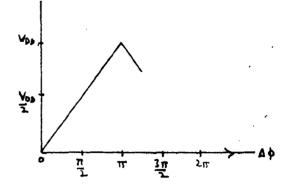

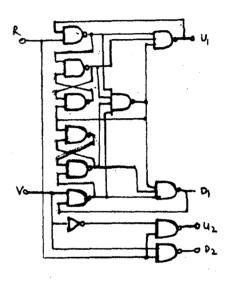

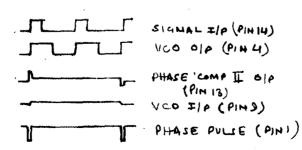

In digital phase locked loops we use either exclusive-OR or some type of edge triggered phase detector. Digital PLL most commonly used is CD 4046, it has both type of detectors. Phase detector I (Exclusive OR gate type ) and phase detector II(Edge triggered type ). Both phase detectors have same input i.e.both input of the I.C.CD4046 are in parallel, The cutputs, however, are brought out separately.

<u>Phase detector-I</u> (The Ex- OR phase detector ).