# MICROPROCESSOR CONTROL OF LINE COMMUTATED INVERTER FED INDUCTION MOTOR DRIVE

### A DISSERTATION

Submitted in partial fulfilment of the requirements for the award of the Degree

of

# MASTER OF ENGINEERING

in

### ELECTRICAL ENGINEERING (Power Apparatus and Electric Drives)

By

ANIL M. BHATIA

DEPARTMENT OF ELECTRICAL ENGINEERING UNIVERSITY OF ROORKEE ROORKEE-247 667 (INDIA) March, 1987

#### CANDIDATE'S DECLARATION

I hereby, certify that the work which is being presented in the dissertation entitled, MICROPROCESSOR CONTROL OF LINE COMMUTATED INVERTER FED INDUCTION MOTOR DRIVE in partial fulfilment of the requirements for the award of the degree of MASTER OF ENGINEERING in ELECTRICAL ENGINEERING with specialization in POWER APPARATUS AND ELECTRIC DRIVES, submitted in the Electrical Engineering Department, University of Roorkee, Roorkee[India], is an authentic record of my own work carried out for a period of about six months from September,1986 to March 1987, under the supervision of Dr. D.R. Kohli, Professor, Electrical Engineering Department, University of Roorkee and Sh. M.K. Vasantha, Reader, Electrical Engineering Department, University of Roorkee, Roorkee, India.

The matter embodied in this dissertation has not been submitted by me for the award of any other degree.

[ ANIL BHATIA ]

Dated

This is to certify that the above statement made by the candidate is correct to the best of our knowledge.  $\bigvee$

[ M.K. VASANTHA ] READER ELECTRICAL ENGINEERING DEPARTMENT UNIVERSITY OF ROORKEE ROORKEE 247 667, INDIA.

[DR. D.R. KOHLI] PROFESSOR ELECTRICAL ENGINEERING DEPARTMENT UNIVERSITY OF ROORKEE ROORKEE-247 667, INDIA.

#### ACKNOWLEDGEMENT

I wish to express my deep sense of gratitude to my guides, Dr. D.R. Kohli, Professor, Electrical Engineering Department, University of Roorkee, Roorkee and Shri M.K. Vasantha, Reader, Electrical Engineering Department, University of Roorkee, Roorkee, without whose cooperation and guidance it would have been impossible to complete the thesis.

Thanks are due to Shri N. Aterkar, M/s Soilex Consultants Pvt. Ltd., Roorkee for having helped me out of a number of difficulties and in getting various units of my thesis developed.

I would like to gratefully acknowledge the timely help and suggestions givenby Dr. Bhim Singh, Lecturer, Electrical Engineering Department, University of Roorkee, Roorkee, which enabled me in overcoming a number of problems coming up during the thesis work.

Thanks are also due to Dr. S.P. Gupta, Reader, Electrical Engineering Department and Other Staff Members, for direct or indirect role played by them , at various stages of the thesis work.

The completion of thesis with all the help available would not have been possible without thecooperation and advice of my close **friends**, Mr. R. Bhatnagar, Mr. C. Raje, Mr. G.C. Agnihotri, Mr. V. Pande who have been associated with the thesis work from the budding to completion stage. The up and Computer lab. staff, specially Mr. K. Singh, and Mr. R. Singh, who have played a role of prime importance in getting my thesis completed, also deserve a special word of thanks from me.

Thanks are also due to Mr. K.C. Khurana, Civil Engg. Department for his effecient and time bound typing of the thesis.

In the end, I am grateful to all whose name I have missed and who have played a part in seeing through the thesis to the final phase.

#### ANIL M. BHATIA

#### ABSTRACT

The line commutated inverter and synchronous motor system have the characteristic of a D.C. motor. This combination is popularly known as the commutatorless D.C. motor. The LCI-SM system can be used as a variable frequency source for induction motor Drive.

In the present thesis work the line commutated inverter has been fabricated and a microcomputer based firing scheme has been developed. The steady state performance characteristics of the LCI-SM system have been obtained using both analog and microcomputer based firing scheme. Finally, the feasibility of microcomputer controlled LCI-SM system as a variable frequency source for induction motors has been experimentally investigated.

From extensive tests carried out on the experimental setup of LCI-SM-IM system, it has been observed that the LCI-SM system works satisfactorily as a variable frequency source. The microcomputer control improves the system performance of the system by improving the stability and reliability of firing pulses.

### CONTENTS

PAGE

1

CERTIFICATE ACKNOWLEDGEMENT ABSTRACT

### CHAPTER

| I.  | INTR | ODUCT ION                                  |    |

|-----|------|--------------------------------------------|----|

|     | 1.1  | General                                    | 1  |

|     | 1.2  | Voltage Source Inverter (VSI)              | 2  |

|     | 1.3  | Current source Inverter (CSI)              | 4  |

|     | 1.4  | LCI-Synchronous Motor System (CLM)         | 5  |

|     | 1.5  | Scope of work in the Present Thesis        | 6  |

|     | 1.6  | Literature Survey                          | 7  |

|     | 1.7  | Principle of Operation of CLM              | 10 |

|     | 1.8  | Description of CLM-Induction Motor System  | 17 |

|     | 1.9  | Conclusion                                 | 17 |

| II  | DESI | GN OF ANALOG FIRING AND POWER CIRCUIT      |    |

|     | 2.1  | General                                    | 18 |

|     | 2.2  | Three Phase SCR Bridge(LCI)                | 18 |

|     | 2.3  | Discontinuous Current Mode •               | 20 |

|     | 2.4  | Continuous Current Mode                    | 21 |

|     | 2.5  | Effect of Source Inductance on Three       |    |

|     |      | Phase Bridge (LCI)                         | 22 |

|     | 2.6  | Design of Firing Circuit for LCI           | 24 |

|     | 2.7  | Design of Power Circuit                    | 28 |

|     | 2.8  | Conclusion                                 | 32 |

| III | MICR | O COMPUTER BASED FIRING SCHEME FOR LCI     |    |

|     | 3.1  | General                                    | 34 |

|     | 3.2  | Role of VCO in Microcomputer based Firing  |    |

| ·   |      | Scheme for LCI                             | 37 |

|     | 3.3  | Design of Zero Crossing Detector Circuit   | 43 |

|     | 3.4  | Voltage Controlled Oscillator              | 46 |

|     | 3.5  | Description of Micro Processor Development |    |

|     |      | System                                     | 50 |

|     |      |                                            |    |

| CHAPTER | P                                                | AGE          |

|---------|--------------------------------------------------|--------------|

|         | 3.6 System Software                              | 52           |

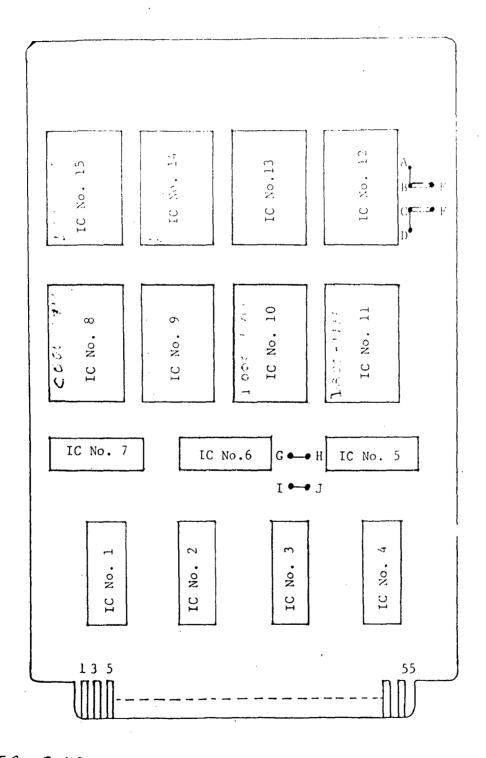

|         | 3.7 I/O and Timer Card                           | 56           |

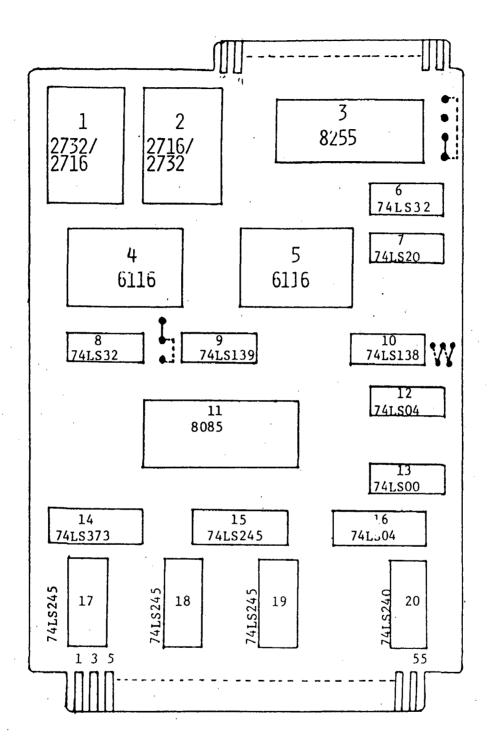

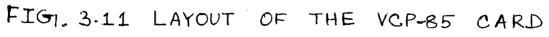

|         | 3.8 Data Terminal (VDT-85)                       | 59           |

|         | 3.9 Escape Sequence                              | 60           |

|         | 3.10 Functional Command Development              | 61           |

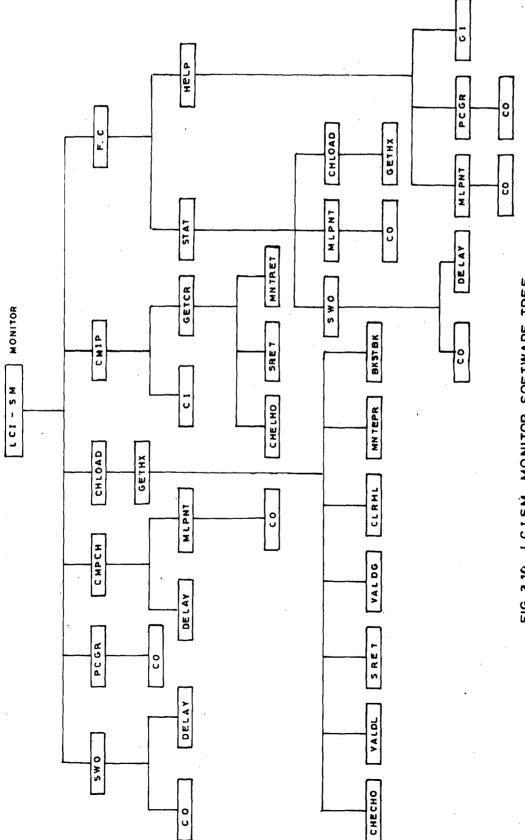

|         | 3.11 LCI-SM Monitor Routines                     | 62           |

|         | 3.12 Conclusion                                  | 70           |

| IV      | STEADY STATE PERFORMANCE OF LCI_SYNCHRONOUS      |              |

|         | MOTOR SYSTEM.                                    | 71           |

|         | 4.1 General                                      |              |

|         | 4.2 Analysis of LCI-Synchronous Machine System   | ר <b>ד</b> י |

|         | Operating as a Variable Frequency Drive          | 71           |

|         | 4.3 Experimental Investigations for Steady State | 76           |

|         | Performance of LCI_SM System                     |              |

|         | 4.4 Starting of LCI Synchronous motor System     | 78           |

|         | 4.5 Results and Discussions                      | 80           |

|         | 4.6 Conclusion                                   | 93           |

| V.      | STEADY STATE PERFORMANCE OF LCI_SM_INDUCTION     |              |

|         | MOTOR SYSTEM                                     |              |

|         | 5.1 General                                      | 94           |

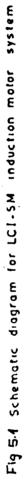

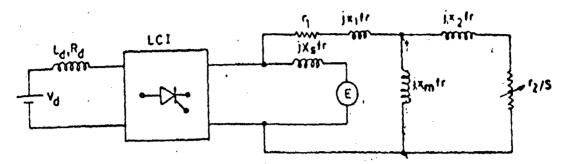

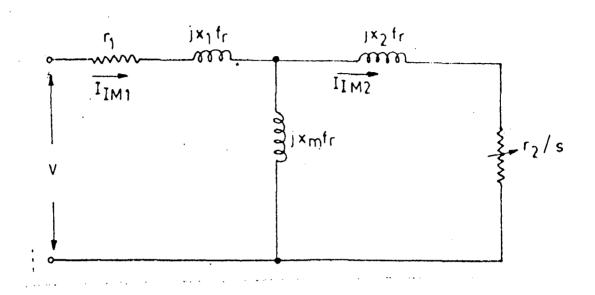

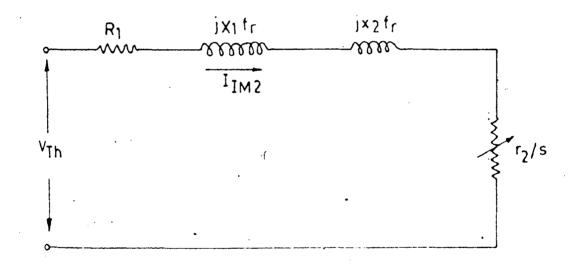

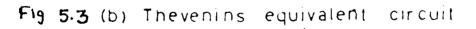

|         | 5.2 Development of Analytical Model              | 94           |

|         | 5.3 Derivation of Steady State Equations         |              |

|         | of the System                                    | 95           |

|         | 5.4 Performance Equation Interfacing the         |              |

|         | Operation of the LCI-Synchronous Machine         |              |

|         | and the Induction Motor                          | 98           |

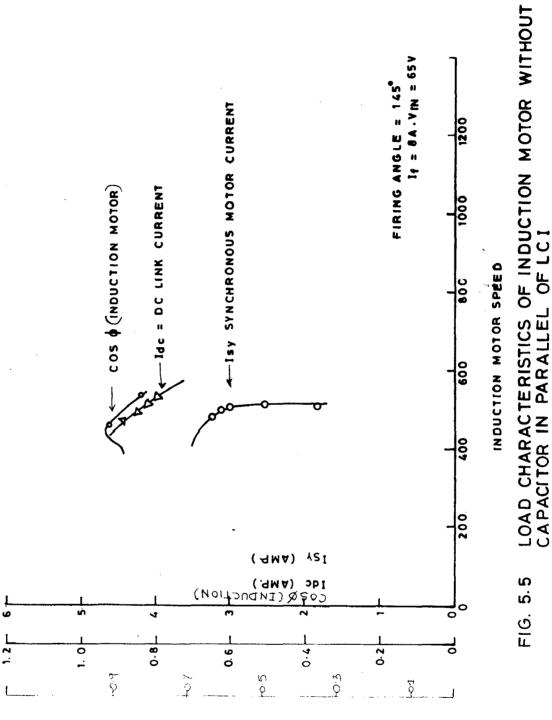

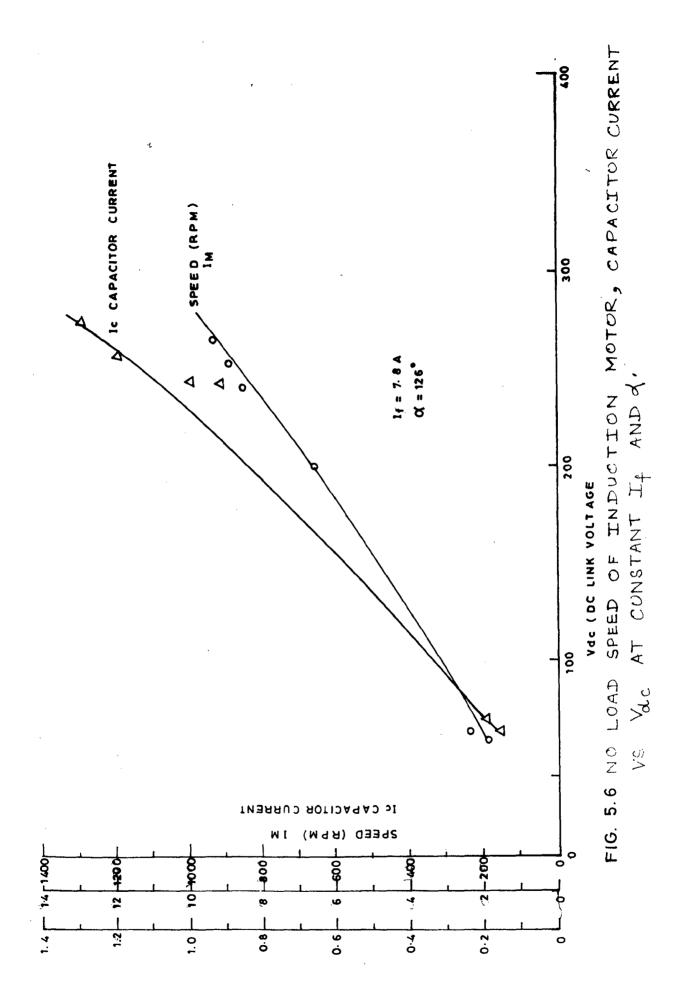

|         | 5.6 Results and Discussions                      | 100          |

|         | 5.7 Conclusion                                   | 103          |

| VI.     | CONCLUSION                                       |              |

|         | 6.1 General                                      | 104          |

|         | 6.2 Microcomputer Based Firing Scheme            | 104          |

|         | 6.3 Steady State Performance of LCI_SM           |              |

|         | System                                           | 105          |

|         |                                                  |              |

CHAPTER

| 6.4 Steady State Performance of LCI_SM_        |     |

|------------------------------------------------|-----|

| Induction Motor System                         | 107 |

| 6.5 Effect of Capacitor on System Performance  | 108 |

| 6.6 Scope for Further Work                     | 108 |

| APPENDIX I - Ratings of Motor Used for         |     |

| Experimental Work                              |     |

| APPENDIX II- Details of the 44 Pin Edge        |     |

| Connector of (VCP_85) Card                     |     |

| APPENDIX III-Assembly Language Listing of      |     |

| Programs Developed for LCI_SM                  |     |

| Monitor and of the LCI-FA .                    |     |

| Routine (i→e→ the Firing Angle                 |     |

| Control Routine of LCI) .                      |     |

| APPENDIX IV-System Specifications of Micro     |     |

| Development System (VMDS-85)                   |     |

| APPENDIX V -System Specifications of the       |     |

| Data Terminal (VDT-85)                         |     |

| APPENDIX VI-Pin Out Diagram and Specifications |     |

| of Various IC's Used in the                    |     |

| Theses.                                        |     |

| REFERENCES AND BIBLIOGRAPHY                    |     |

٠

PAGE

#### CHAPTER I

#### INTRODUCTION

#### 1.1 <u>GENERAL</u>:

D.C. machines have been the work horses in industry for variable speed applications since they satisfy the requirements of a wide range of speed control. However, it has the disadvantages inherent with a mechanical commutator.

The commutator limits the maximum power of the D.C. machine to 10,000 K.W. at 1000 RPM and to 500 KW at 5000 RPM. The brushes and the commutator not only limit the power output but also make it unsuitable for dusty and explosive environment. The induction motor on the other hand, has a robust rotor construction which permits a reliable and almost maintenance free operation. Inspite of these advantages the inherent limitation of constant speed of operation has been the main bottleneck in its widespread use as a variable speed drive.

The advent of semiconductor technology led to the development of solid state adjustable speed A.C. drives in 1960[]. Since then many innovations in devices, circuits, control theory, and signal electronics have made a considerable contribution to this technology. Of the various methods of A.C. motor speed control, its operation at variable frequency is becoming more and more popular, since it is possible to obtain variable speed as well as good regulation and efficiency. The static variable frequency converters are expensive but are

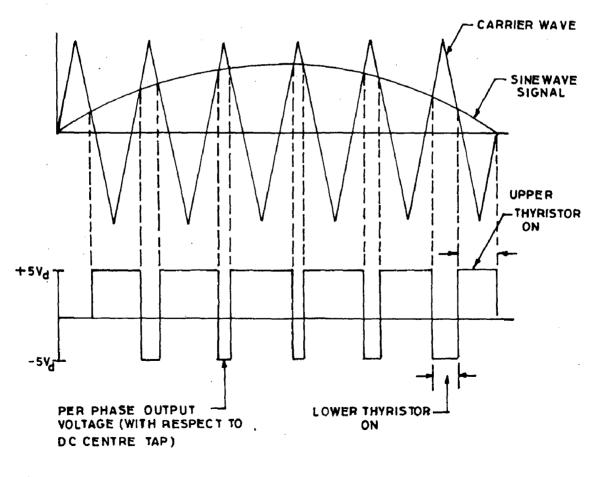

FIG. 1.2 PRINCIPLE OF PWM (SINUSOIDAL PWM TECHNIQUE) advantageous in terms of accuracy and reliability. The current research in adjustable speed A.C. drives is focussed on the cost reduction of the converter and control equipment. The variable frequency A.C. drives becomes particularly attractive in multimotor drive systems where a large number of small motors are supplied from one source. Such multimotor drives find applications in textile, synthetic fibre, paper making industries, traction, and in processing lines where exact speed coordination is essential in order to maintain the cuality of the product.

The solid state variable frequency sources for A.C. drives can be broadly classified into two types,

1. Cycloconverters,

#### 2. D.C. Link converters which include,

- (a) Voltage source inverters(VSI)

- (b) Current source inverters(CSI).

#### 1.2 VOLTAGE SOURCE INVERTER (VSI):

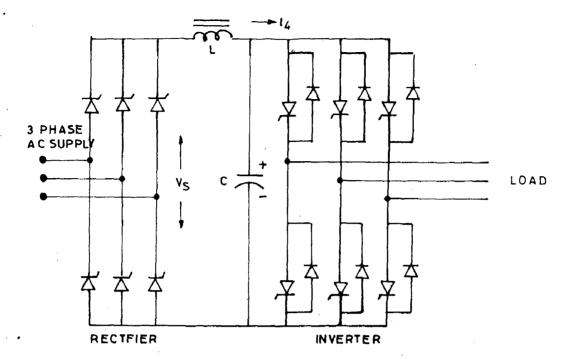

The VSI's are generally classified into two types, square wave inverters and pulse width modulated inverters. These type of inverters were introduced from the beginning of 1960's when a forced commutation technique was introduced[]. Fig 1.1 shows the conventional power circuit of a voltage source inverter. The squarewave output voltage leads to a number of undesirable effects, i.e. additional harmonic power losses and torque pulsuations in motors. The harmonic currents

- 2 -

flowing in stator and rotor contribute to extra copper losses and some amount of stray iron losses. The lopwer order of harmonics of the inverter. Voltage waveform can be eliminated by multiphasing. However, such an expensive technique is not justified for normal applications. The commutating capacitor in the voltage source inverters is ussually charged by the D.C. link voltage hence commutating capability decreases as the D.C. voltage decreases. The inverter requires six commutating cycles per cycle of fundamental, leading to increased commutation losses and requiring complex control circuitary as well as fast switching SCRs.

The voltage fed square wave inverter drives are normally used in low to medium horse power ratings where speed ratio is usually limited to 10:2. This type of drive has been largely superceded by PWM drives.

In PWM inverters the thyristors are switched on and off many times within a half cycle to generate a variable voltage output which is normally low in harmonic contents. Among the PWM techniques sinusoidal PWM technique is common and is shown in Fig 1.2. This technique reduces the harmonic losses but it suffers from low inverter efficiency. In low and medium power applications the thyristors in the inverter can be replaced by transistors leading to elemination of commutation and higher prequencies of operation.

- 3 -

#### (CS1)

### 1.3 CURRENT SOURCE INVERTER(CSI):

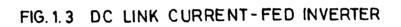

The current source inverter circuit is as shown in Fig 1.3. The CSI drive has many good features which can be summarised as follows:

- 1. Regeneration is possible,

- 2. There is no possibility of shoot through fault,

- 3. The fault current on the inverter side rises very slowly.

- 4. Commutation losses are lower than in VSI drives,

- 5. The inverter can be designed with low speed SCRs.

Against the above mentioned merits, the CSI drives have the following limitations:

- 1. The frequency range of inverter is lower and it cannot operate on no load,

- 2. The large size of D.C. link inductor and commutating capacitor make the inverter expensive,

- 3. The commutation is dependent upon machine subtransient inductance which adds large transient over voltages at machine terminals,

- 4. The drive has instability problems and sluggish response at light loads and high speeds.

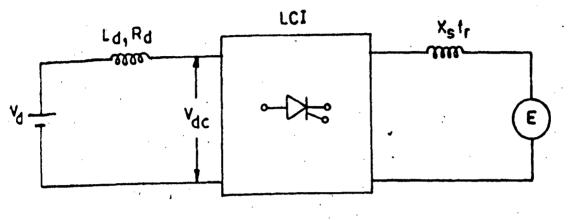

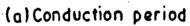

These factors limit the use of CSI to single motor, medium or high power drives. A line commutated inverter is obtained by operating an SCR bridge in continuous current mode with firing angle  $\alpha$  greater than 90°. The sequential commutation of SCRs is obtained with the help of three phase line voltages. The line commutated inverter requires reactive power for commutation. The reactive power required depends upon the firing angle of the inverter. The reactive power can be supplied by the following:

1. Line voltages,

2. Capacitors connected at the output of LCI,

3. Overexcited synchronous motor connected to the three phase output terminals of LCI.

The line commutated, *inverter* overcomes all the problems of forced commutated inverters as well as cycloconverters. Some of the characteristic features of LCI are:

1. No harmonics in output voltage waveform,

2. Commutating components are not required,

The triggering circuit requirements are comparitively simple.

### 1.4 LCI\_SYNCHRONOUS MOTOR SYSTEM(CLM):

The advent of SCRs in sixties led to the development of a static commutator for the D.C. maching using line commutated inverters. The LCI-synchronous machine combination gives the characteristics of a D.C. motor. The commutation of SCRs is controlled by the sinusoidal induced voltage in stator due to rotating field of rotor. This combination is is popularly known as the commutatorless D.C. motor. A large number of such drives have been commissioned by Siemens for starting of 80 MVA gas turbine generating sets, boiler feed pumps etc.

The commutatorless motor has been generally used by industry in following cases:

1. When high speeds upto 7,000 RPM are required,

2. When high ratings up to 10,000 H.P. are required.

3. When high efficiency is required.

The possible use of LCI and synchronous motor as a variable frequency source for induction motors was first reported by Brader[ 9] with possibility of applications in the field of traction and group drives, etc.<sup>R</sup>anganadhachari[32] investigated the performance of synchronous machine and LCI combination as a variable frequency source for multi induction motor drive and for static loads and has demonstrated the viability of the scheme. For the firing and control circuitary of LCIRanganadhachari has used analog schemes.

1.5 SCOPE OF WORK IN THE PRESENT THESIS:

In the present work an attempt has been made to compare and experimently verify the performance of a system consisting of LCI and synchronous motor combination, used as a variable frequency source feeding induction motors as a load with two types of firing schemes:

1. Analog firing scheme.

2. Digital scheme using microcomputer.

- 6 -

The present work has the following objectives:

- 1. Design and fabrication of converter inverter power circuit.

- Performance testing of LCI synchronous motor system using analog firing scheme,

- Development of micro computer based firing scheme for LCI.

- 4. Operation and testing of LCI synchronous motor system using digital scheme,

- 5. Performance of LCI synchronous motor system as a variable frequency source for induction motor.

#### 1.6 LITERATURE SURVEY:

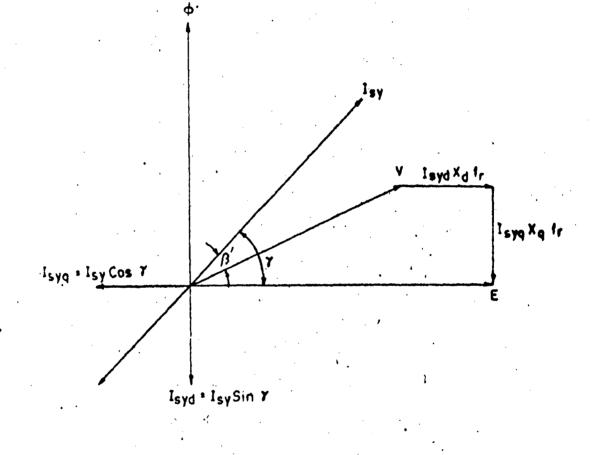

Extensive literature is available on LCI-synchronous machine system operating as a commutator-less motor.Tadakuma, Tamura and Tanaka[11] have described the driving characteristics of commutator-less motor controlled by induced voltage detectors. Rosa[12] has analysed a d.c. link type variable frequency synchronous motor drive, and discussed the utilization and ratings of such drives. Brochurst[19] presented the performance equations of D.C. commutatorless motor using salient pole type synchronous machine.

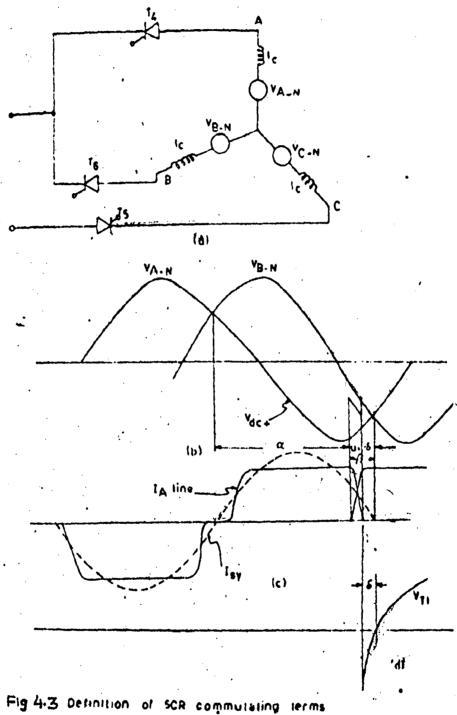

Tokeda, Morimoto and Hirasa[39] have discussed the generalised analysis for steady state characteristics of D.C. commutatorless motor. The variation of commutation angle, shiftangle, demagnetisation due to armature reaction, safety margin angle, average torque, and speed; with mean input current are examined quantitatively for cylindrical and salient pole motors.

Katoka [17] has given the steady state characteristics of current source inverter/ double wound synchronous motor system as a variable frequency A.C. power supply, with the help of an equivalent circuit. A method to keep output voltage and frequency constant has been discussed. A simple dynamic model of current fed synchronous motor operating with a constant angle between motor back e.m.f and input current is given by A. Jakubowicz[15]. This mode includes only two time constants, associated with rotor inertia and D.C. link inductance. Akagi and Nabae[30] have presented a control. scheme for compensating the torque transfer function of CLM. In this scheme the armature voltage phase and amplitude are altered during transients to compensate for slow response of the field current. H. Naito [28] has determined analytically and verified the dynamic characteristics of lead angle controlled commutatorless motor and has pointed out the instability problems associated with this type of control method. He has taken up a constant o-controlled CLM provided with a firing angle control scheme in which the leading firing angle is advanced according to the increase of load. A concept of commutation equivalent resistance has been introduced to show that the resistance will become negative in constant . d-control scheme leading to instability and lag of response and it has been pointed out that the feedback of D.C. link current is a counter measure for the above mentioned problem.

- 8 -

In 1983 microcomputer controlled operation of self-controlled synchronous motor employing terminal voltage sensing technique has been studied by Davoine and Perret[**38**]. In their scheme the standstill position of rotor is computed by microcomputer by analysing and sampling the induced voltage in stator when a step voltage is applied to the field winding. The microcomputer also takes care of starting the motor from standstill by using auxiliary thyristor in parallel of O.C. link inductor.

An attempt was made by Loreth to reduce the cost of CLM so as to make it suitable for low and medium power application by suggesting a novel type of CLM using slip ring induction motor. In this case the rotor is connected to the LCI. The stator windings perform the function of magnetising winding and damper winding.

Emil Levi[37] designed and tested a three phase resonant parallel inverter for induction motors. The commutation of thyristor after every  $60^{\circ}$  is achieved by the resonance in R-L-C network formed by D.C. link inductor and resistance, parallel capacitor, motor resistance and equivalent inductance.

A design of an induction machine having torque speed characteristics of an induction motor but leading power factor operating capability like an over excited synchronous motor, has been developed by Laithwaite[23]. this being known

- 9 -

SCHEMATIC DIAGRAM OF LINE COMMULATED INVERTER (LCI)-SYNCHRONOUS MACHINE SYSTEM (commulatoriess D.C. MOTOR) FIG. 1.4

as 9 pinch machine.

An LCI based induction motor drive using capacitors as reactive power sources has been fabricated and tested by B. Singh . The capacitor bank however becomes a source of constant KWAR, thus making the control of reactive power troublesome.

#### 1.7 PRINCIPLE OF OPERATION OF CLM

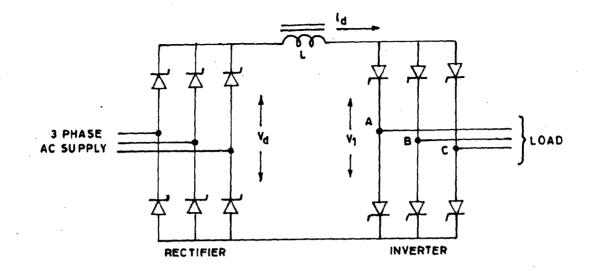

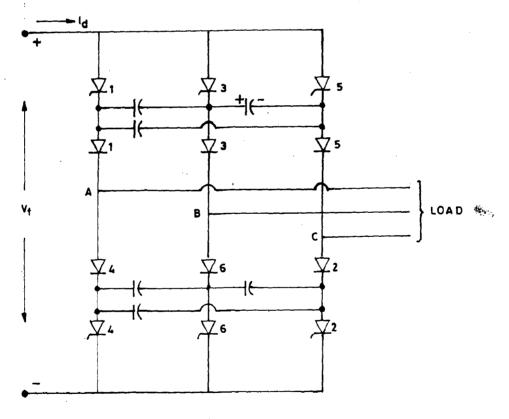

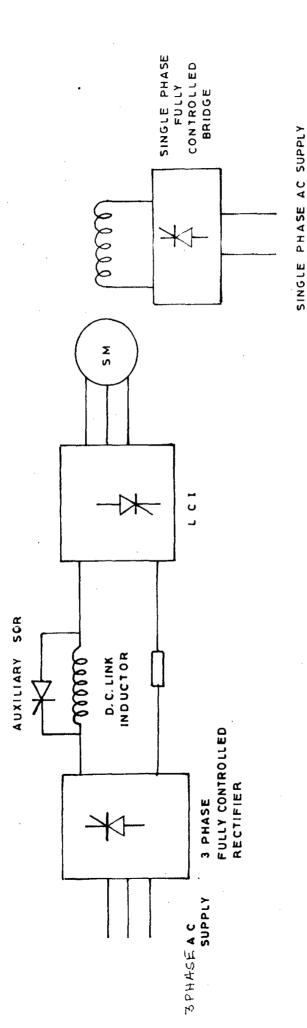

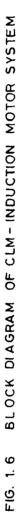

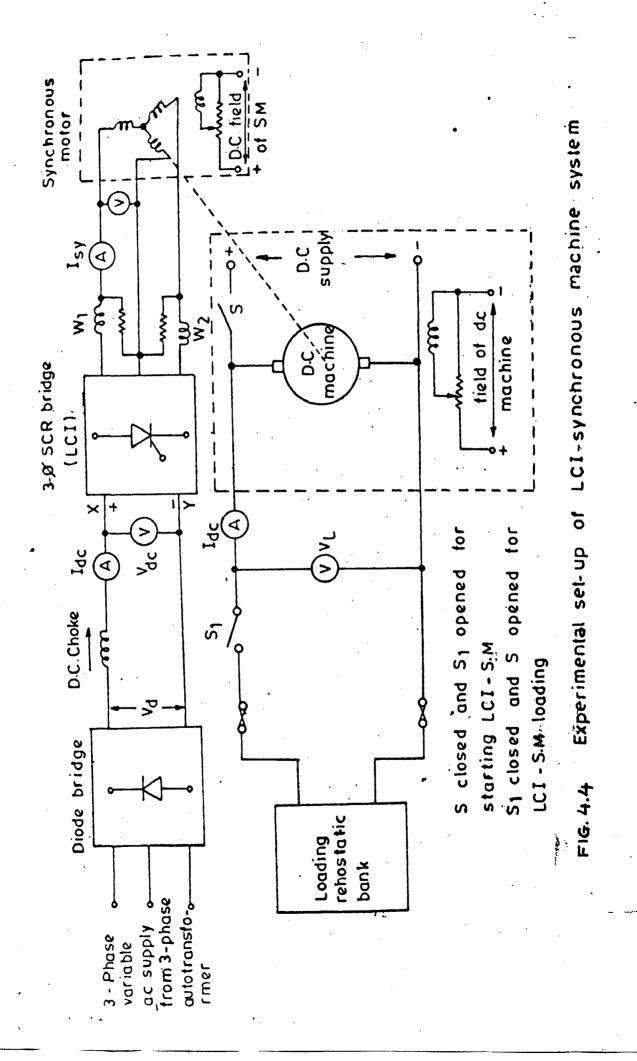

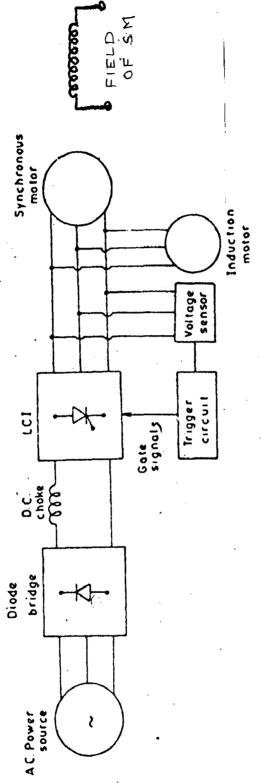

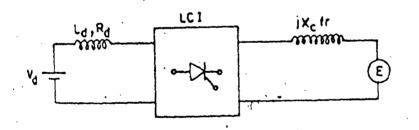

A commutatorless motor consists of the following essential parts. The block diagram of CLM is as shown in Fig.1.4.

- 1. A converter (controlled or uncontrolled)

- 2. An inverter (LCI).

- 3. A D.C. link inductor.

- 4. A synchronous motor (overexcited).

- 5. Firing and control circuits for converter and inverter.

#### CONVERTER:

This is a 3 phase diode or SCR bridge depending upon whether it is controlled, uncontrolled or semicontrolled. The main function of the bridge is to supply variable D.C. link voltage. The output voltage of converter is varied by changing the firing angle  $\alpha$  in case of semi or fully controlled converters, and with an input auto transformer in case of uncontrolled bridge. The advantage of fully controlled operation of the two bridges is that regeneration is possible by exchanging the mode of operation of the two bridges i.e. rectifier becomes inverter and inverter becomes rectifier. In the present work a 3 phase uncontrolled bridge with an input auto transformer has been used.

#### D.C. LINK INDUCTOR

This inductor plays the role of smoothening out the ripples in the D.C. link current. The value of this inductor plays a decisive role in the system performance.

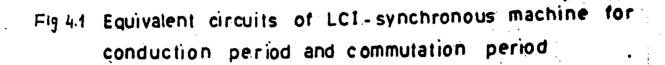

The LCI and synchronous motor constitute a commutatorless D.C. motor. The synchronous machine is over excited and supplies leading reactive power to the inverter. The inverter provides the active power to the synchronous motor for the load connected to it, and to overcome the friction and windage losses.

The firing of inverter SCRs has to be controlled in such a manner that the stator flux maintains a constant angle with rotor mmf. The firing pulses for the SCRs therefore can be derived from the synchronous motor. This can be done in two ways:

1. Rotor position sensor method.

2. Stator terminal voltage sensor method.

### ROTOR POSITION SENSOR METHOD

In this method the switching of D.C. link current from one stator phase to another is controlled by motor flux vector. This is dermined by a motor position sensor using optical encoder and a toothed disc mounted on the rotor shaft.

- 11 -

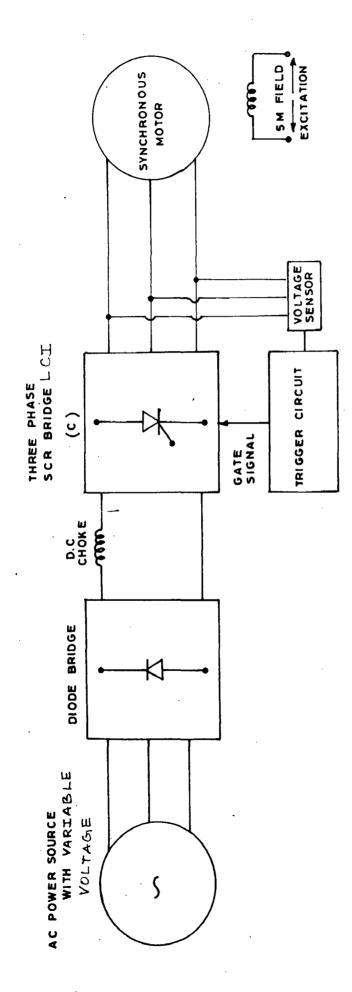

- IS STATOR CURRENT

- IF FIELD CURRENT

- IL MAGNETISING CURRENT

- V TERMINAL VOLTAGE

- E INDUCED STATOR VOLTAGE

- 5 LOAD ANGLE

- Er mmt ANGLE

- d FIRING ANGLE REFERRED TO V VECTOR

## FIG. 1. 5 VECTOR DIAGRAM FOR CYLINDRICAL ROTOR SYNCHRONOUS MOTOR

**N**Is

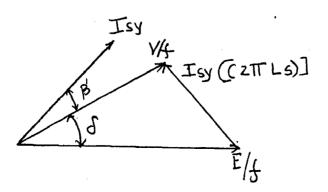

The characteristic feature of this method is that the angle between field mmf and stator mmf vector normally remains fixed. The vector diagram in Fig 1.5 shows the relationship between the firing angle  $\alpha$  and rotor angle  $\delta$  (angle between

terminal voltage of stator and induced e.m.f. in stator)from this vector diagram the inverter firing angle is obtained as,

$$\alpha = 90^{\circ} + \varepsilon_{\rm r} + {\rm o}$$

where,  $\epsilon_r$  is the angle between field mmg vector and stator m.m.f. vector.

A major drawback of this method is that as the load increases the rotor angle  $\delta$  increases hence firing angle increases by an equal amount. Thus there exists a possibility of the inverter crossing the inversion limit. This necessiates the fixing of upper limit of  $\alpha$ . This leads to poorer utilisation of inverter and motor. The rotor position sensors are also liable to be affected by the environment such as dust, etc. These disadvantages are not present in stator terminal voltage sensor method.

### 1.7.4 STATOR TERMINAL VOLTAGE SENSOR METHOD:

In this method the firing instants are derived from the terminal voltage of the synchronous machine. Except for the over lap angle effect this method is independent of the operating state of the machine in terms of load current etc.

The only drawback of this method is the inability to determine the firing pulse sequence at the starting instant, when there is no voltage induced in the stator windings. In case automatic starting of the CLM is required then a number of techniques have been proposed. Some of these are:

- Addition of a simple Hall effect position detector which is used only for initial position sensing.

- Injecting a signal of KHz frequency range in a auxilliary winding and analysing the induced stator voltages.

- 3. Analysing the induced voltages in the stator winding when a step voltage is applied to the field winding.

Since the combination of LCI and synchronous motor constitutes a CLM D.C. motor, hence three types of CLM D.C. motors can be realised depending upon the placement of the field winding

- 1. Series CLM [33]

- 2. Shunt CLM

- 3. Seperately excited CLM.

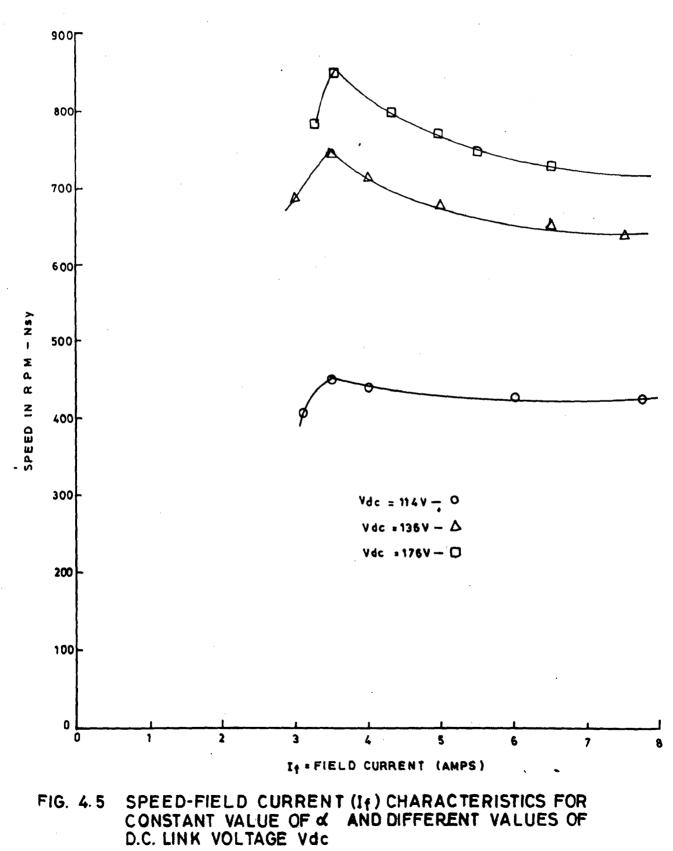

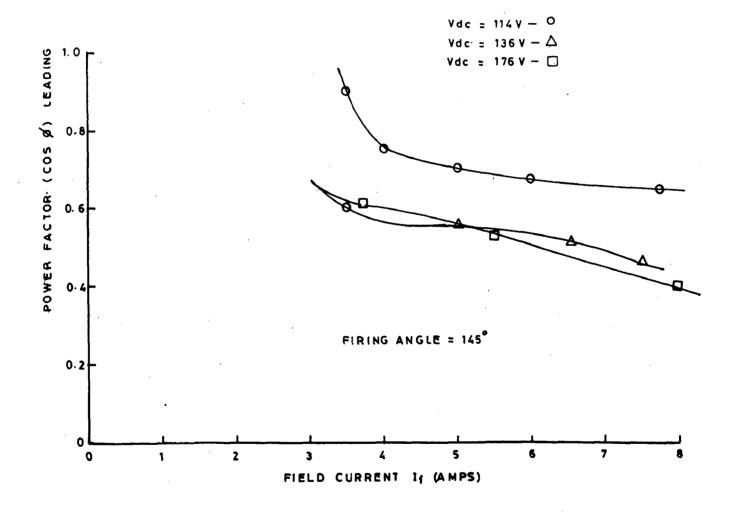

#### 1.7.5 SPEED CONTROL OF CLM:

The speed of this drive can be changed by varying any one of the following parameters:

1. D.C. link voltage, VdC,

- 2. Inverter firing angle,  $\alpha_{i}$

- 3. Synchronous motor field current, If.

Thus, the frequency of the output terminal voltage of the

- 13 -

inverter can be given by

$$f = \frac{K \, Vdc}{I_f \cos \alpha}$$

In the present work control of firing angle  $\alpha$  is obtained with the help of both type of schemes;

1. Analog firing scheme,

2. Microcomputer based firing scheme.

#### STARTING OF COMMUTATORLESS MOTOR:

The major drawback with the CLM is it's inability to start from standstill because the gating signals of inverter SCRs are controlled by the synchronous motor itself, and the commutation voltage necessary for machine commutation of LCI is not available. Hence, some other method of commutation of current from one SCR to another is necessary. Several methods are known for this purpose. Some of these techniques are listed by Perret[38].

The automatic starting of CLM is more simplified when microcomputer control is implemented. This method of starting requires two fully controlled SCR bridges. One operating as a machine commutated inverter and one as a fully controlled rectifier supplying D.C. link voltage, Vdc to LCI. The field current control with the help of a single phase converter is optional.

The automatic starting schemes can be broadly

- 1. Starting with out an auxiliary thyristor accross D.C. Link inductor,

- 2. Starting with an auxiliary SCR accross D.C. link inductor.

### 1.7.7 STARTING WITHOUT AN AUXILIARY SCR:

In this method, commutation is accomplished by forcing the rectifier bridge into inverter mode during a short instant so as to interrupt the D.C. link current and reduce it to zero. Standstill rotor position is sensed by using any one out of the three techniques described earlier. The terminal voltage is sensed and at each interval forced commutation is obtained as follows:

- 1. Inverter triggering pulses are stopped,

- 2. Rectifier (three phase) firing is fixed at  $\alpha = 150^{\circ}$ ,

- 3. D.C. link current is monitored till it becomes zero,

- 4. Rectifier normal operation is then reestablished and the following SCR pair is triggered.

The main advantage of this technique is that no additional commutating component is required. However, during each commutation interval the motor current is reduced to zero, so that instantaneous torque is zero during this period. This torque zero period is c fixed by the machine and converter circuit dynamics, and is undesirable in case of high starting torque requirements.

•

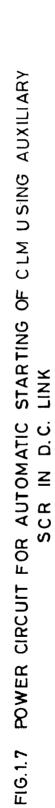

# 1.7.8 <u>STARTING WITH AN AUXILIARY SCR IN PARALLEL WITH D.C. LINK</u> INDUCTOR:

This method of automatic starting also requires two fully controlled three phase bridges and an additional SCR in parallel with D.C. link inductor as shown in Fig.1.7. Forced commutation during each commutation cycle is achieved following steps:

- Firing pulses to the two fully controlled bridges

i.e. rectifier and inverter are inhibited.

- 2. The auxiliary SCR is gated.

- 3. The current through D.C. link is deviated through the auxiliary SCR and thus forced commutation of LCI SCRs is achieved.

This method has been used by Ventatraman[21] with the help of analog control circuitary.

This method overcomes the disadvantage of zero torque during commutation interval obtained in the previous method.

The manual method of starting involves the running of synchronous motor using an auxiliary motor and the gating signals for inverter SCRs are derived from generated e.m.f. of synchronous machine. The auxiliary motor is later cutoff as its current reduces to zero when active power is drawn by the synchronous motor from the LCI.

In the experimental work manual procedure of starting the CLM has been used.

ł

OR MICROCOMPUTER

# 1.8 DESCRIPTION OF CLM - INDUCTION MOTOR SYSTEM:

- 17 -

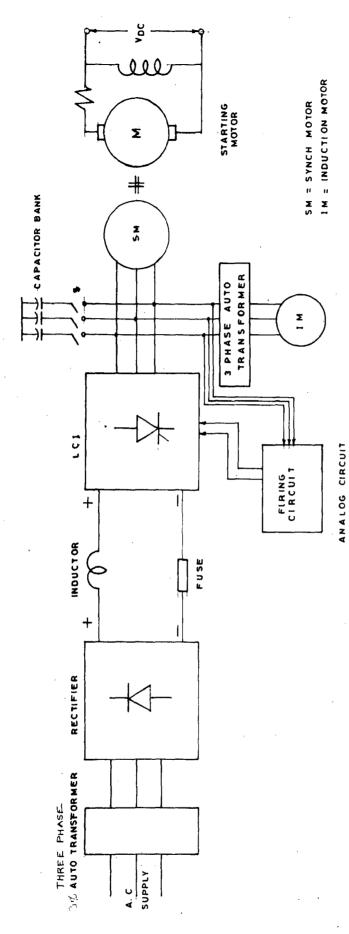

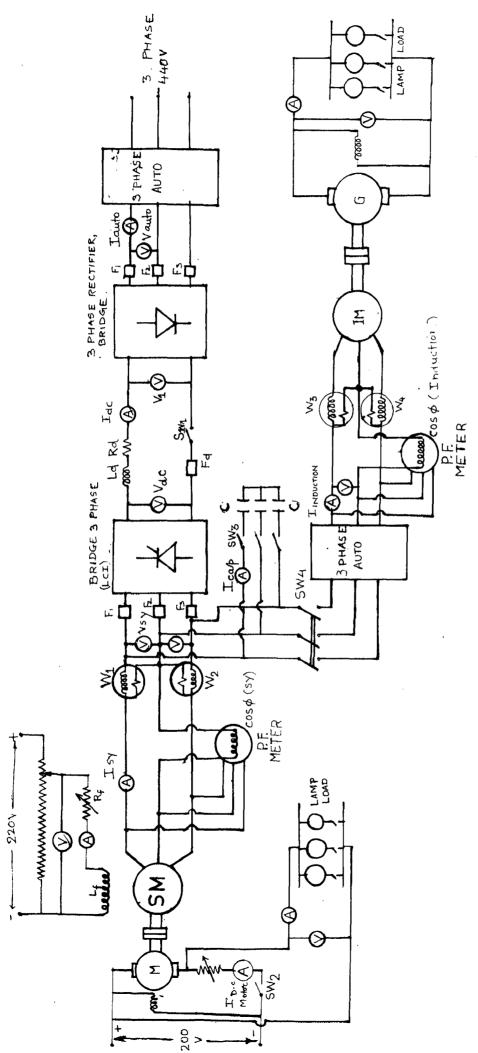

The block diagram of the experimental system that has been designed, fabricated and tested, is as given in Fig.1.6. Two types of firing and control circuitry have been developed. These are:

1. Analog firing circuit,

2. Microcomputer based firing circuit.

As shown in the Fig 1.6 an auto transformer has been used to connect the induction motor to the 3 phase output of line commutated inverter. This transformer helps in improving the stability of the system by enabling reduced voltage starting of the induction motor. A 3 phase star connected capacitor bank can be connected in parallel with the synchronous machine by closing the switch S. The role of this capacitor bank is only to add investigative flexibility in the system. Otherwise the system can work without this capacitor bank as well. The LCI, D.C. link inductor, converter, synchronous machine, etc. forming the CLM have been described earlier.

#### 1.9 <u>CONCLUSION</u>:

The design and description of the analog and microcomputer based firing circuits, the steady state performance of results of the LCI-SM system and LCI-SM-IM system are given in the following chapters.

- 0 -

#### CHAPTER II

#### DESIGN OF ANALOG FIRING AND POWER CIRCUIT

#### 2.1 GENERAL:

This chapter mainly deals with the analog firing circuit design. The design of converter-inverter power circuit also forms an important part of this chapter. The determination of conduction intervals of individual SCRs of the LCI, and the sequence of firing is also discussed.

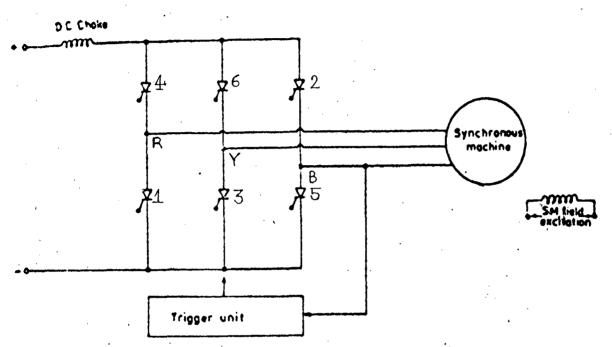

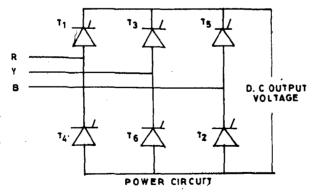

#### 2.2 THREE PHASE SCR BRIDGE (LCI):

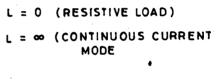

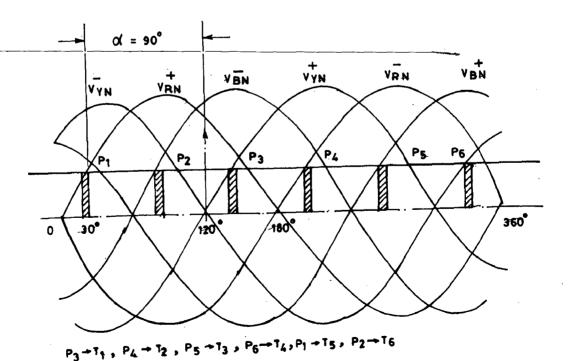

A three phase SCR bridge has been used as a line commutated inverter the commutation of the bridge. SCRs is achieved by the back e.m.f of the synchronous motor connected to the three phase output of the bridge as shown in Fig.2.1. The firing angle of the bridge is adjusted between.  $90^{\circ}$  to  $180^{\circ}$  so as to obtain the inverter mode of operation. In the inverter mode the direction of surrent flow through the bridge remains the same however the D.C. terminal voltage of the bridge reverses polarity.Thus,the LCI is nothing but a three phase fully controlled converter with firing angle between  $90^{\circ}$  to  $180^{\circ}$ . The sequence of firing of SCRs and the conduction intervals can be explained with the help of a detailed demription of 3 phase fully controlled converter.

The power circuit for a three phase fully controlled bridge is same as that of LCI in Fig.2.1. The advantage of the bridge configuration is that it does not place any restriction

Fig 2.1 Three phase SCR bridge (line commutated inverter)

1

| Time in degrees | 0   | 60  | 120 | 180 | 240 | 300 |

|-----------------|-----|-----|-----|-----|-----|-----|

| Firing sequence | 1   | 2   | 3   | 4   | S   | •   |

| Conducting SCRs | 6,1 | 1,2 | 2,3 | 3,4 | 4,5 | 5,6 |

FIG. 2. 2 3 PHASE LINE VOLTAGES

| 5. NO. | wt = 0       | SCR TO BE      | MAX. VALUE   |  |

|--------|--------------|----------------|--------------|--|

|        |              | TRIGGERED      | LINE VOLTAGE |  |

| 1      | t1           | 71             | VRY          |  |

| 2      | t2           | 72             | VRB          |  |

| 3      | t 3          | 13             | VYB          |  |

| 4      | t 4          | 74             | VYR          |  |

| 5      | * <b>*</b> 5 | ۲ <sub>5</sub> | VBR          |  |

| 6      | t 6          | 76             | VBY          |  |

TABLE NO. 2.2

on the connections of the windings of the three phase source (i.e. if it should be star connected or detta connected).

The thyristors  $T_1, T_3$  and  $T_5$  are called positive group SCRs because they conduct when the A.C. supply phase voltage are positive, while the thyrestors  $T_4$ ,  $T_6$ ,  $T_2$  are called negative group SCRs because they conduct when the supply phase voltages are negative.

In one cycle of the : A.C. supply wave there are six conducting intervals each of  $60^{\circ}$  in which a pair of SCR conducts. These intervals are as given in Table No.2.1.

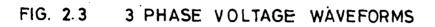

The line to line voltages are as shown in the Fig.2.2. When VRY is at its positive maximum i.e. at wt =  $90^{\circ}$  SCRs T<sub>1</sub> and T<sub>6</sub> are conducting giving

$V_0 = VRY$  at wt =  $\pi/2$

when <sup>V</sup><sub>RY</sub> is at the negative maximum then SCRs  $T_3$  and  $T_4$  are conducting giving  $V_0 = -$  VRY at wt =  $3\pi/2$ . If the other line voltages are also considered then the appropriate pairs of SCRs as given in table 2.1 will be conducting when any one of the six line voltages will be ; having a greater value than the other five voltages.

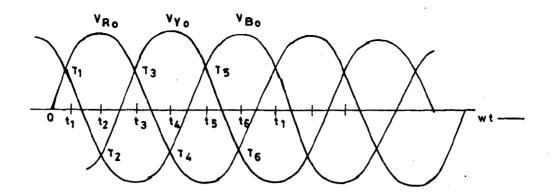

From the Fig 2.3 it is clear that the phase voltage VRN is more positive then any other phase voltage in the range of  $30^{\circ} \leq w_t \leq 150^{\circ}$  i.e. between the two cross over points of  $V_{\rm RN}$  and  $V_{\rm BN}$  and  $V_{\rm RN}$  and  $V_{\rm VN}$ . The SCR in the positive

- 19 -

group and in the red phase arm i.e. the  $T_1$  can conduct in this interval. If the SCR is replaced by a diode then it would start conduction from st =  $30^\circ$ ; hence  $t_1$  point is the reference point for firing angle  $\alpha$  of SCR  $T_1$ . The reference points for other SCRs are also determined in the same manner and are as given in Table no.2.2. The table also lists the line voltage having zero magnitude at each reference point. Thus, the reference point for measuring firing angle can either be taken as cross over points of phase voltages or the zero crossing points of line voltages.

The firing angle of the converter can be varied from  $0^{\circ}$  to  $180^{\circ}$ , however practically it is varied from the minimum value of  $10^{\circ}$  to the maximum value of  $165^{\circ}$ . There are two modes of operation of the fully controlled three phase bridge converting upon value of load inductance.

- 1. Discontinuous current mode,

- 2. Continuous current mode.

#### 2.3 DISCONTINUOUS CURRENT MODE:

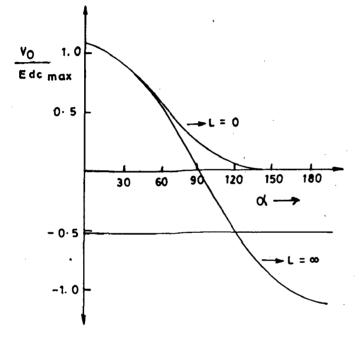

The converter in this mode operates only as a rectifier. The load is generally resistive i.e. with low conductance. The rectifier operation starts from  $\alpha = 0^{\circ}$  upto  $\alpha = 120^{\circ}$ , when the output voltage becomes zero. The voltage Vdc versus firing angle  $\alpha$  plot for resistive load is as shown in Fig.2.4. The D.C. output voltage upto  $\alpha = 60^{\circ}$  is same as in case of continuous conduction mode of operation, this is due to the fact that the upto  $\alpha = 60^{\circ}$  the output voltage of converter even in case of

### FIG. 2.4 OUTPUT VOLTAGE OF THREE PHASE FULLY CONTROLLED BRIDGE AS A FUNCTION OF FIRING ANGLE

FIG1-2:5 Theoretical waveform of voltage across the bridge (a) Firing angle 30 degrees (b) Firing angle 90 degrees (c) Firing angle 160 degrees (d) Conducting SCRs

.

,

continuous conduction, does not become negative hence the D.C. output of both discontinuous conduction and continuous conduction modes are the same. As the load is almost purely resistive with negligeble value of inductance hence when  $\alpha$  becomes greater than  $60^{\circ}$  the bright voltage output is unable to become negative because of low load inductance the load current almost follows the voltage waveform. Hence the converter operates upto  $\alpha = 120^{\circ}$  as rectifier with resistive load. After  $\alpha = 120^{\circ}$  the output voltage of the bridge becomes zero.

#### 2.4 CONTINUOUS CURRENT MODE:

In this mode of operation the load current of the bridge is maintained constant by the large value of load inductance. Thus, in this mode of operation the current will be maintained constant even if the output voltage becomes negative. The relation,

$V_{\rm dc} = \frac{3\sqrt{3}}{\pi} \quad \text{Emph cos } \alpha \qquad \dots \qquad (2.1)$

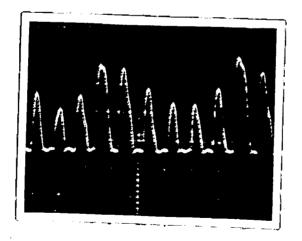

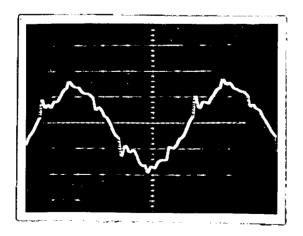

gives the output voltage for a particular value of firing angle, for this mode of operation. The Fig 2.4 gives the output voltage variation with firing angle  $\alpha$ . Fig. 2.5 give, the output voltage wave forms of the converter for  $\alpha = 30^{\circ}$ ,  $\alpha = 160^{\circ}$  and  $\alpha = 90^{\circ}$ , in continuous current mode of operation. It is evident from these waveforms that as firing angle  $\alpha$  reaches  $90^{\circ}$  the output voltage reduces to zero. As the firing angle  $\alpha$  is increased above  $90^{\circ}$  then the output

- 21 -

voltage becomes negative. Thus now the converter starts operating in the inverter mode i.e. if a D.C. source of proper polarity is connected accross its D.C. terminals then power will be delivered from the D.C. source to the three phase side. This mode of operation (i.e. the line commutated inverter mode) is of special interest in the thesis work.

Finally it is clear that for continuous load current there are two modes of operation depending upon value of  $\alpha$  they are,

| (1) | Rectifier | $0 \leq \alpha \leq 90$ ,                       |

|-----|-----------|-------------------------------------------------|

| (2) | inverter  | 90 <u>&lt;</u> α <u>&lt;</u> 180 <sup>0</sup> . |

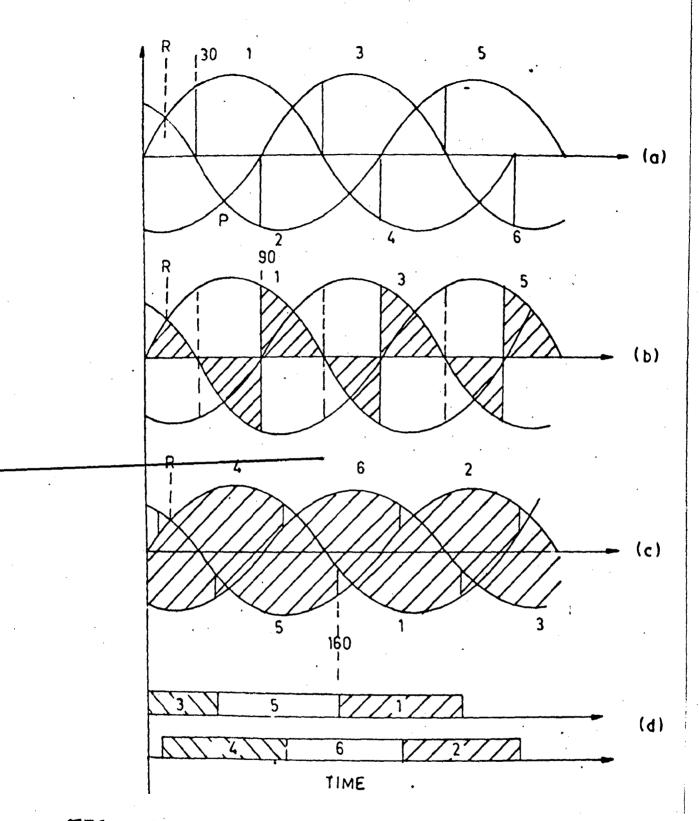

## 2.5 <u>EFFECT OF SOURCE INDUCTANCE ON THREE PHASE BRIDGE</u> CONVERTER(F.C):

The discussion upto now was based on the assumption that the source inductance is absent, however this is rarely true. The source normally has some inductance, this does not allow instantaneous current commutation in SCRs. The commutation of SCR  $T_5$  is explained with the help of Fig.2.6, when an SCR i.e.  $T_5$  is the positive group is undergoing commutation, the incoming SCR i.e.  $T_1$  of positive will also start conducting resulting in conduction of three total SCRs. Two in positive group and one in negative group. The effective result is that a commutation over lap region is obtained. The current in the outgoing SCR  $T_5$  reduces to zero and the current in the incoming SCR i.e.  $T_1$  gradually rises to the full value

FIG. 2.6 VOLTAGE AND CURRENT WAVEFORMS OF A 3 PHASE f.c. BRIDGE WITH COMMUTATION OVERLAP ANGLE

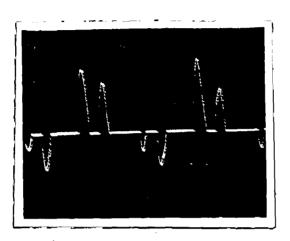

as shown in Fig 2.6. This figure also gives the output voltage waveform including commutation overlap regions. In case of three phase bridge converter there will be six commutation overlap regions in one cycle.

The reduced output voltage due to commutation overlap is given by equation 2.2 [ ]

$$Y_{dc} = \left[\frac{3\sqrt{3}}{\pi} \quad \text{Emph cos } \alpha - \frac{3wL_sI_L}{\pi}\right]$$

The overlap angle is generally represented by the symbol  $\mu$  it depends up,

- 1. Number of phases,

- 2. Load current,

3. Source inductance.

Depending upon the value of commutation overlap angle there are three modes of operation[1] of the fully controlled three phase bridge.

| ļ. | Mode I   | α < 60 <sup>0</sup>           | two and three SCRs conducting  |

|----|----------|-------------------------------|--------------------------------|

| 2. | Mode II  | $\alpha = 60^{\circ}$         | three SCRs conducting          |

| 3. | Mode III | α <u>&gt;</u> 60 <sup>0</sup> | three and four SCRs conducting |

normally the bridge operates in the mode I.

The commutation overlap angle effects the performance of the converter is a number of Ways[3] they are,

(i) The wave shape of the output voltage is altered. The

output voltage during overlap is the mean of voltages of out going and in coming phases,

- (2) The reduction in output voltage is proportional to load current giving a sort of regulation property to the converter, and can be considered as a equivalent resistance in series,

- (3) The input current waveforms are rounded at edges this results into the reduction of harmonic currents. The individual current segments are streched,

- (4) At the input to the converter commutation notches are produced in the line and phase voltages, subjecting the thyristors to excessive dv/dt,

- (5) In the inverter operation the commutation of SCRs depends upon the negative voltage of mains. The overlap reduces the negative voltage interval necessiating the reduction of maximum delay angle i.e.  $\alpha$ .

#### 2.6 <u>DESIGN OF FIRING CIRCUIT FOR LCI</u>:

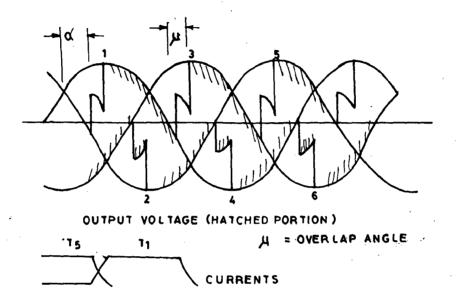

It has been discussed in the preceeding section that the six  $SCRsT_1$  to  $T_6$  are to be fired sequencially at an interval of  $60^\circ$  in one cycle of A.C. wave. Each SCR conducts for an interval of  $120^\circ$  and with two SCRs of opposite group and of the remaining two phases. It has earlier also been explained that the reference points for SCR firing angle  $\alpha$ , can either be obtained from the cross over points of phase voltages or the zero crossing points of the line voltages.

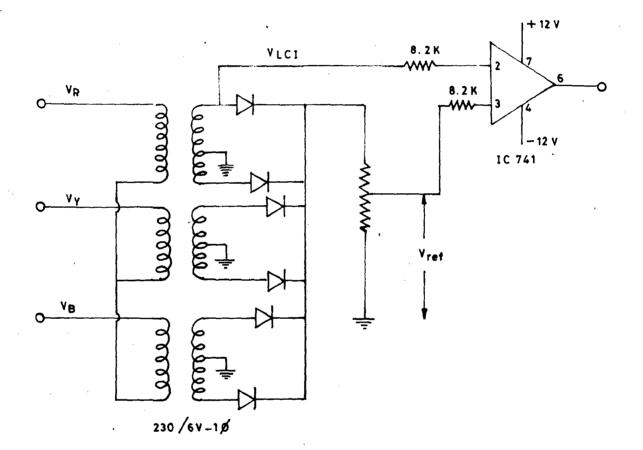

In the analog firing circuit developed the synchronous

## FIG. 2.7 COSINE FIRING SCHEME TO OBTAIN FIRING ANGLE & AT VARIABLE FREQUENCY

motor terminal voltages or the LCI output voltages are stepped down using a three phase<sup>Y</sup> connected, 230 /6V transformer, and then compared with a D.C. reference voltage  $V_{ref}$  for obtaining the firing angle  $\alpha$  as shown in Fig 2.7.

The output voltage and frequency of LCI are not constant and the voltage waveforms have to be sensed to derive the firing pulse for the control of commutator less motor (LCI-SM). Since the frequency and voltage magnitude are changing continuously, it is not possible to obtain the same value of firing angle  $\alpha$  with a constant value of  $V_{\mbox{ref}}.$  Thus in order to maintain  $\alpha$  constant at different operating frequencies, V signal should be derived in such a way, that it's value is frequency independent. This is achieved by deriving the NV ref signal from the variable output of a pot. The voltage input to the pot is the rectified stepped down output of LCI. Thus now as the frequency of LCI output signal changes for a constant excitation of S.M., then the LCI terminal voltage will also change proportionally, changing the value of  $V_{ref}$  in the same ratio. It can be analytically shown that firing angle  $\alpha$  becomes frequency independent when V ref is derived from LCI voltage.

$V_{LCI} = KxfxCos wt \qquad \dots \qquad (2.3)$   $V_{ref} = K_1'xf \qquad \dots \qquad (2.4)$  K and K' are constants  $Cos wt = \frac{K'}{K}$

- 25 -

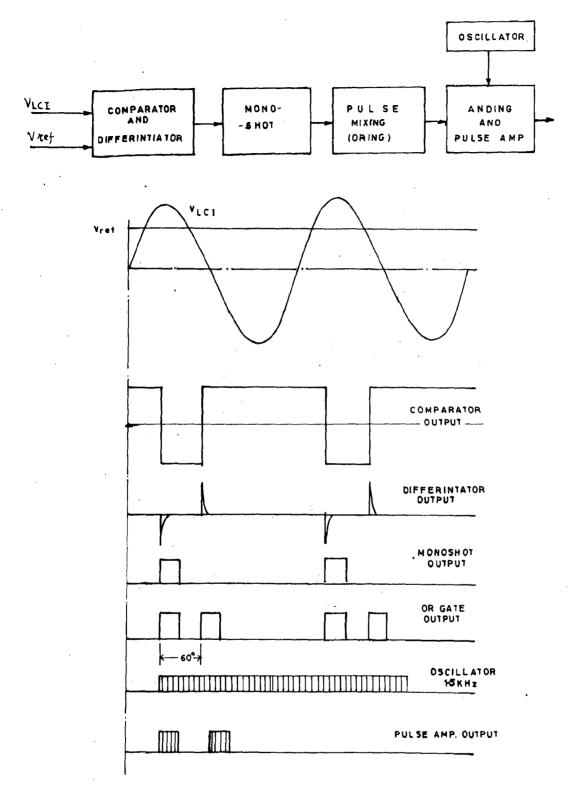

FIG. 2.8 BLOCK DIAGRAM OF ANALOG FIRING CIRCUIT

1

- 26 -

Now wt =  $\alpha$   $\alpha = \cos^{-1}(\frac{K'}{K})$

The block diagram of the firing circuit is shown in Fig.2.8. It consists of following parts:

1. 3 phase signalling, Y/Y connected transformers,

- 2. Comparators,

- 3. Differentiator

- 4. Monoshot,

- 5. OR gates,

- 6. AND gates,

7. Pulse amplifiers,

8. High frequency oscillator.

#### 2.6.1 SIGNAL TRANSFORMERS:

Three single phase, 240/6V transformers with centre tapped secondaries are connected in Star/star configuration. The six phase voltage waveform required for comparison with  $V_{ref}$  are obtained from the centre tapped secondaries.

#### 2.6.2 COMPARATOR:

IC 741 is used as a comparator. It compares the stepped down phase voltage connected to its pdn, number 2 with  $V_{ref}$  applied to its pin No.3. The output waveform of comparator is shown in Fig.2.8.

#### 2.6.3 DIFFERENTIATOR:

The output of the comparator is differentiated with the help of simple R C differentiator the RC components are

# FIG. 2.9 MONO STABLE MULTIVIBRATOR USING IC 555 TIMER

~

designed with suitable values so that it can work satisfactorily in the frequency range of 5 to 100 Hz

R = 10K  $C = 0.01 \mu F$

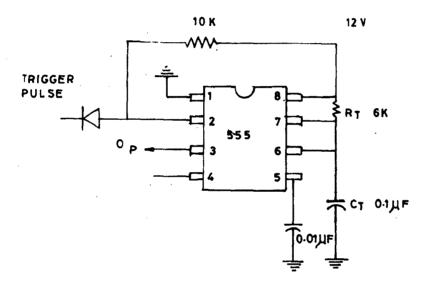

#### 2.6.4 MONOSHOT:

A negative edge tuggered monoshot has been fabricated using IC 555 timer in monostable configuration the value of various components and the circuit are given in Fig 2.9. The value of the timing components  $R_{ex}$  and  $C_{ex}$  is selected on bases of the required pulse width of monoshot output that would be sufficient to trigger the thyristor to ON state

$T_{ON} = 1.1 R_{ex} C_{ex}$

taking  $T_{ON} = 600 \,\mu$  Sec  $C = 0.1 \,\mu$ F  $R_{ex} = 6 \,K \,Ohms$

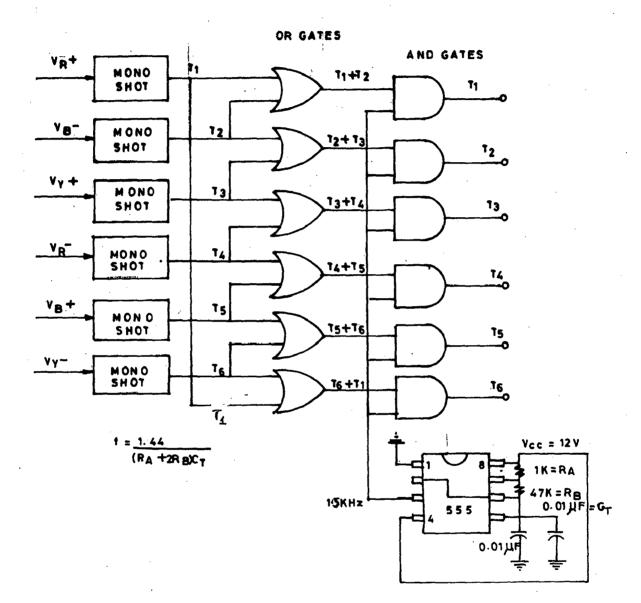

#### 2.6.5 OR GATING:

The six pulses for triggering the individual SCRs can be obtained from the monoshot outputs. However, in a three phase bridge an SCR conducts with two SCRs of opposite group for an interval of  $120^{\circ}$ . The turning on of the conducting SCR is ensured by oring the pulse of the conducting SCR with the pulse of the in coming SCR, coming after an interval of  $60^{\circ}$ . The second pulse is known as the slave pulse and the first pulse is the master pulse. The oring sequence of pulses

$T_1+T_2$ ,  $T_2+T_3$ ,  $T_3+T_4$ ,  $T_5+T_4$ ,  $T_6+T_5$ ,  $T_6+T_1$

in terms of phase voltages the sequence can be given as  $V_R^+ + V_B^-$ ,  $V_B^- + V_Y^+$ ,  $V_Y^+ + R^-$ ,  $R^- + B^+$ ,  $B^+ + Y^-$ ,  $Y^- + R^+$

FIG. 2. 10 PULSE MIXING OF SIX MONOSHOT OUTPUTS

. ·

FIG. 2.12 PHASE ADVANCING TECHNIQUE IN CASE OF Y/Y CONNECTED ANALOG FIRMS SCHEME

.

The pulses derived from the indicated phase voltages are OR gated using IC 7432.

#### 2.6.6 AND GATING:

The master slave output of the six OR gates become the six firing channels as shown in Figure. The Fig 2.10 gives the OR gated signals and with the SCR number to which it is to be given. These OR gate outputs are low frequency outputs hence they are ANDED with a high frequency modulating signal obtained from IC 555 oscillator with a frequency of 1.5 K Hz., this prevents the saturation of pulse transformers in the pulse amplifier circuits.

#### 2.6.7 PULSE AMPLIFIER:

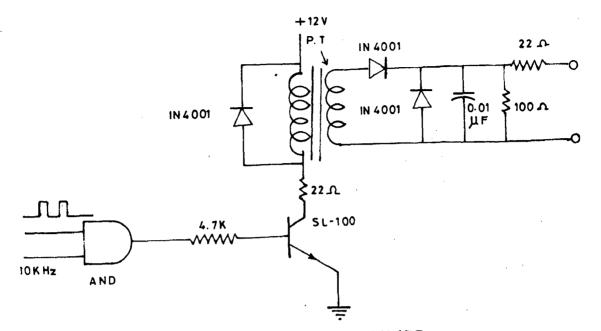

The strength of the AND gate output pulses is amplified using the pulse amplifier circuit shown in Fig 2.12. A pulse transformer is used for isolating the power circuit from the firing circuit. The diode connected accross the primary winding provides the path for free wheeling of stored inductor energy of transformer is off state.

#### 2.7 DESIGN OF POWER CIRCUIT:

The power circuit for the present work consists of the following parts:

1. Three phase fully controlled bridge(LCI),

2. Three phase diode bridge,

3. D.C. link inductor.

A power circuit panel board has been fabricated to house the

converter, inverter bridges. The design ratings of SCRs and diodes for the bridges must be such that they should not be exceeded when maximum power is being delivered by the circuit.

#### 2.7.1 CHOICE OF RATING OF RECTIFIER BRIDE DIODES:

The power circuit has been designed to supply an active load of  $I_{\rm RMS}$  = 25 A at V = 400V input to the three phase bridge. Thus the D.C. link current for this A.C. current can be obtained from the relation,

$$\frac{I_{RMS}}{I_{dc}} = 0.816 \quad (for three phase bridge)$$

$$I_{dc} = 0.816 \times I_{RMS}$$

$$= 30.63 \text{ Amp.}$$

The voltage rating of the diodes of the uncontrolled bridge have to be selected with the consideration of the peak inverse voltage appearing accross the device, this in turn depends upon the maximum three phase input line voltage to the bridge. The maximum line voltage is 400V at 50 Hz. Therefore the PIV accross each diode is

$\frac{V_{\text{PIV}}}{V_{\text{LN}}} = 2.45 \quad (120^{\circ} \text{ conduction, three phase bridge})$   $V_{\text{PIV}} = 2.45 \times \frac{400}{\sqrt{3}}$  = 566 Volts

A safety factor of 2 is kept so that the diodes can easily take reasonable transient over voltage. Thus, diodes having a

- PIV rating of 1200V are selected. The ratings of the diodes selected are listed below.

- 1. Mean forward current = 25 Amps.

2. Type = HR/HN D-25

3. Maximum case to stude 100 C

- $\frac{1}{2}$ . temperature =  $120^{\circ}C$

- 4. Maximum junction temperature =  $150^{\circ}C$

- 5. Repetative peak value of current = 130 Amps

- Thermal resistance junction to case =  $1.3^{\circ}C/W$

- 2.7.2 SELECTION OF **R**ATINGS OF SCR FOR LCI BRIDGE:

The following below given factors have to be considered for selecting the ratings of the SCR

- 1. The power circuit configuration.

- 2. Conduction angle of individual SCR.

- 3. Current waveform.

- 4. Average current.

- 5. Maximum PIV appearing accross the device.

A three phase SCR bridge has been chosen as the line commutated inverter. The maximum value of line voltage accross the SCRs of the bridge is governed by the maximum voltage rating of the synchronous motor which is 400V for the present thesis work.

For a three phase bridge the ratio of peak reverse voltage to line to neutral voltage is given by

= 2.45

$$E_{PIV} = \frac{400}{3} \times 2.45$$

= 566 V

Taking a safety factor of 2, a 1200 V SCR is required. Hence, BTW -39 has been selected. The RMS current rating of the SCR is 25 Amps. The detailed ratings of the SCRs are as given:

1. Manufacturer = Solid state Electronic Pvt. Ltd

- 2.  $PIV_3 = 1200 V$

- 3.  $I_{rms} = 25 Amps$

- 4.  $T_{jm} = 125^{\circ}C$

- 5. V<sub>CT</sub> = 3.0 Volts

- 6.  $I_{GT} = 80 \text{ mA}$

- 7.  $I_{T(av)} = 16$  Amps.

- 8.  $P_{D} = 30 \text{ W}$

- 9.  $dV/dt = 200V/\mu S$  (minimum)

- 10.  $di/dt = 100A/\mu S$  (maximum)

- 11.  $I^2 t = 200 A^2 S_{ec} (t < 10 m S)$

Hence under full load conditions the SCR and diode bridges can deliver a maximum value of  $I_{dC} = 30.6$  Amps.

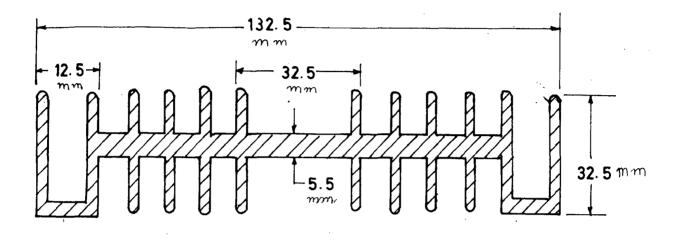

The power circuit diagram for the panel board is as shown in Fig 2.14(b). The power dissipation of the individual thyristors at a conduction angle of  $120^{\circ}$  is 30 Watts. The maximum allowable temperature of the device is  $120^{\circ}$ C. Assuming an average ambient temperature of  $40^{\circ}$ C, the maximum temperature rise allowable will be

$120^{\circ}C - 40^{\circ}C = 80^{\circ}C$

SH - 132

1. HIGH GRADE ALUMINIUM ALLOY

2. ANODISED BLACK

3. THERMAL RESISTANCE

a) NATURALLY COOLED = 1.2°C/WATTS

b) FORCED COOLING (5M/SEC) 0.35°C/WATTS

FIG. 2.13 SECTIONAL PLAN OF HEAT SINK

$R_{CH}$  = Thermal impedance case to heatsink  $R_{HA}$  = Thermal impedance heatsink to ambient.  $R_{CA}$  = Thermal impedance case to ambient

$$R_{CA} = R_{CH} + R_{HA}$$

$$R_{HA} = R_{CA} - R_{CH}$$

$$= 2.66 - 0.3$$

$$R_{HA} < 2.36^{\circ}C/W.$$

Thus the thermal impedance for the heat sink should be less than 2.36 °C/W. Heat sinks with  $R_{H\Lambda} = 1.2^{\circ}C/W$  (natural cooling), have been Belected. The sectional diagram of heat sink and its ratings are as given in Fig 2.13.

#### 2.8 CONCLUSION:

Let,

The range of firing angle  $\alpha$  obtained by adopting the sequence of firing discussed in this chapter. In case of Y/Y connection is from 150 to 160 and from 0 to 60 i.e.  $30^{\circ}$ in inversion range and  $60^{\circ}$  in rectifier range. Hence to obtain  $\alpha$ in the range of  $90^{\circ}$  to 180 a pulse advancing technique is used The pulses and the phase voltages are as given in Fig 2.12. From the Fig 2.12 it is clear that if the pulse derived from Y + phase voltage is used to fire the T<sub>1</sub> SCR (i.e. all the SCRs are given pulses  $120^{\circ}$  behind their original pulses) a full variation of  $\alpha$  from 90 to  $180^{\circ}$  may be obtained for V<sub>ref</sub> changing from 0 to V<sub>ref</sub> max. Even after phase advancing the analog firing scheme using Y/Y connected signal transformers has a number of disadvantages. They are

- Non-sinusoidal voltages due to Y/Y connection., These may lead to shifting of firing pulses leading to commutation failure and instability,

- 2. Non-linear variation of firing angle with the change in reference Voltage  $V_{ref}$ .

Due to these disadvantages the micro computer scheme for control of firing angle was preferred.

FIG. 3.1 BLOCK DIAGRAM OF LCI FIRING ANGLE CONTROL SCHEME

#### CHAPTER III

#### MICROCOMPUTER BASED FIRING SCHEME FOR LCI

#### 3.1 GENERAL:

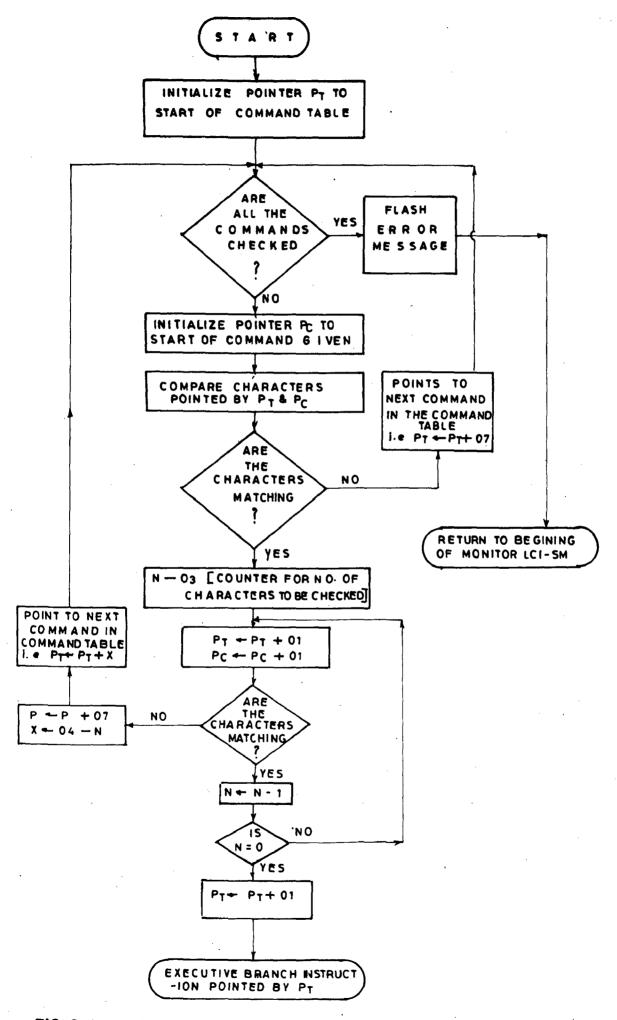

In this chapter the microcomputer based LCI firing angle control scheme philosophy has been explained. Further, the development of software for the scheme is explained with the help of flow charts.

The disadvantages of analog firing scheme used for control of LCI\_SM system are as follows:

- 1. Variation of firing angle  $\alpha$  is limited to 90° by using cosine firing scheme,

- 2. The harmonic content of the voltage waveform of LCI can disturb the firing pulse instants, leading to misfiring of LCI.

- 3. The firing sequence of SCRs is different for rectifier and inverter operations,

- 4. Hard wired logic circuitry fixes the firing scheme philosophy and any change, if necessary, cannot be included without changing the circuit,

These drawbacks of the analog scheme can be overcome using a a microcomputer based firing angle control scheme for LCI.

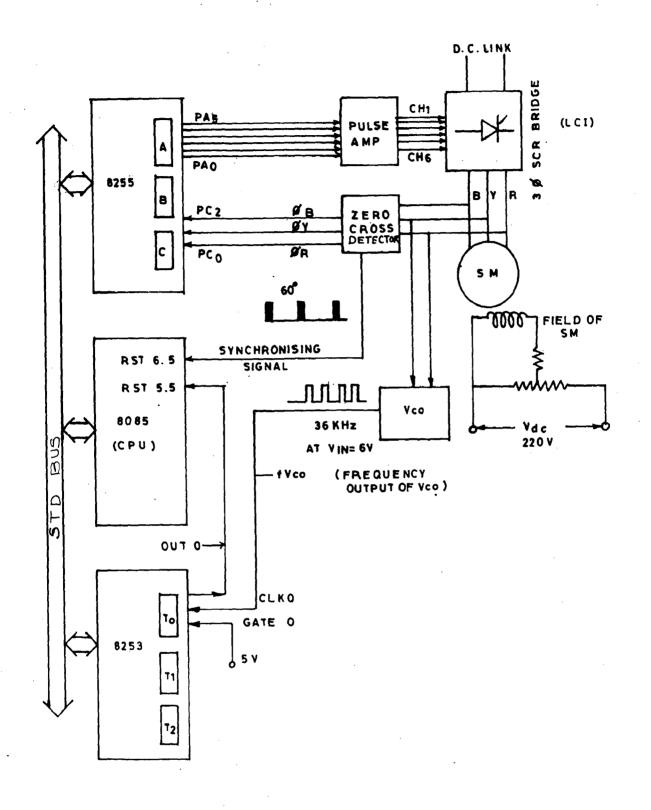

The scheme used for generating the firing pulses is

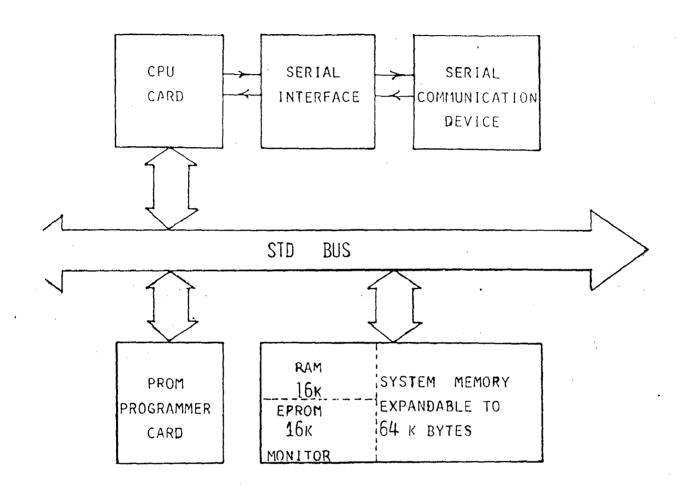

shown in block diagram form in Fig 3.1. It consists of following parts:

- 1. Three signal transformers, single phase 440/6V,  $\Delta/Y$  connected,

- 2. Zero crossing detector circuit,

- 3. Voltage controlled Oscillator,

- 4. Timer Card,

- 5. Pulse amplifier Circuit.

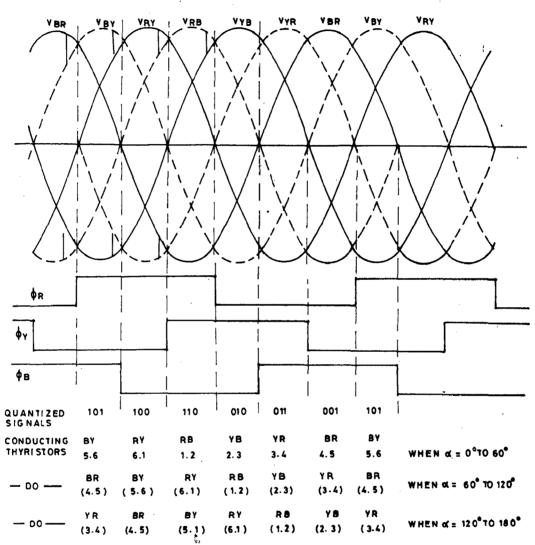

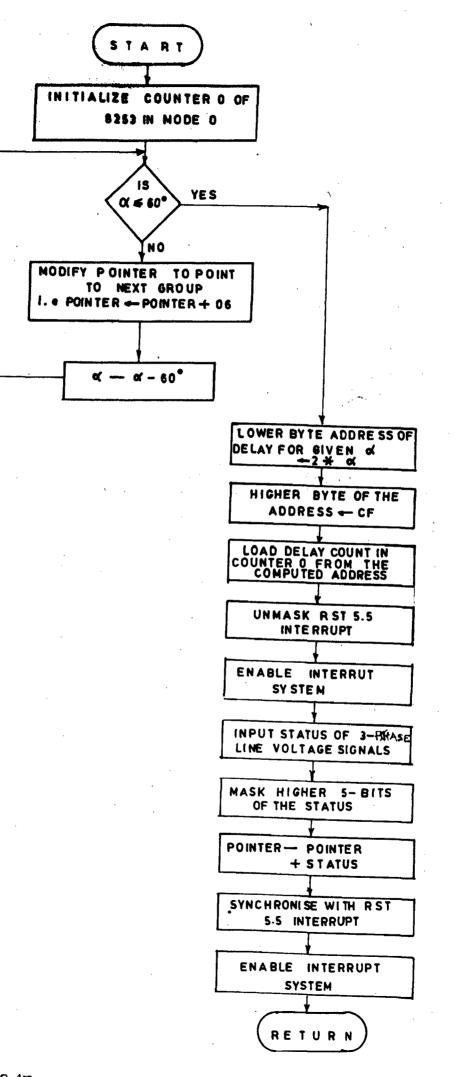

The microcomputer has to execute the following tasks sequentially after every 60° interval:

- 1. Compute the range of the given firing angle value i.e.  $0^{\circ}-60^{\circ}$ ,  $60^{\circ}-120^{\circ}$ ,  $120^{\circ}-180^{\circ}$ ,

- 2. Depending upon the range and value of the given firing angle load the delay word into the 8253 counter 0, to generate a delay proportional to the value of firing angle α,

- 3. Check the status of three digital signals  $\phi_{\rm R}$ ,  $\phi_{\rm y}$ ,  $\phi_{\rm B}$ , these signals are in phase with the line voltages  $V_{\rm RY}$ ,  $V_{\rm vB}$ ,  $V_{\rm BR}$ ,

- 4. Depending upon the firing angle  $\alpha$  and the status of  $\phi_{\rm R}$ ,  $\phi_{\rm Y}$ ,  $\phi_{\rm B}$  a firing command word is selected from the firing command table,

- 5. The two SCRs as selected by high bits of firing command word are fired.

Irrespective of the algorithm used by the micro computer for the

1

(REFER TO FIG. 3.5)

FIG. 3.3 SYNCHRONIZING SIGNALS

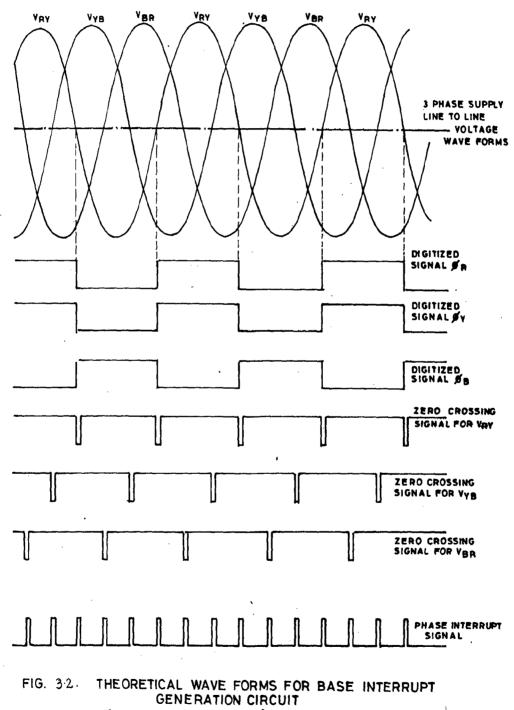

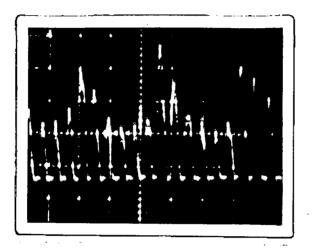

control of  $\alpha$ , the signals that synchronise with the input supply voltages are very necessary. The six pulse bridge circuit will require six such signals in one cycle. These signals are the zero crossing signals of the line voltages. These are used by the microcomputer to programme a delay proportional to a. The zero crossing circuit derives a train of these pulses as shown in Fig 3.2, these signals are displaced by 60° interval. They are used as base interrupt signals to interrupt the microprocessor after every 60° interval. Three digitalised power signals are also obtained from the zero crossing detector circuit. These signals  $\phi_{\rm R}$ ,  $\phi_{\rm Y}$ ,  $\phi_{\rm B}$  are in phase with supply line voltages,  $V_{RY}$ ,  $V_{YB}$ ,  $V_{BR}$ . The status of these signals is inputted by microprocessor in every  $60^{\circ}$ . These signals have 6 distinct values for each 60° interval. The thyristor pair to be treggered in a particular 60° interval depends upon the status of signals  $\phi_{\rm R}$ ,  $\phi_{\rm B}$ ,  $\phi_{\rm Y}$ . Hence firing tables as shown in Fig 3.3 giving the status word of the signals in increasing order and the SCR pair to be fired for the given status word for 3 ranges of values of firing angle i.e.  $\alpha = 0$  to  $60^{\circ}$ ,  $60^{\circ}$  to  $120^{\circ}$ , 120 to  $180^{\circ}$ have been prepared i.e. Table 3.1.

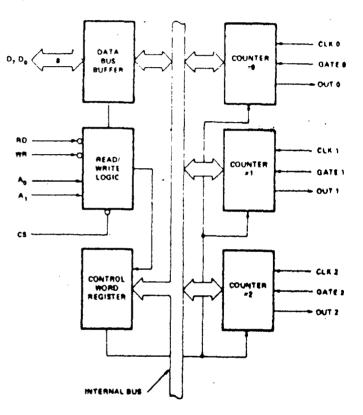

The microcomputer uses a programmable interval timer chip 8253 to produce the delay required for given value of  $\alpha$ . The PIT 8253 consists of 3 counters (16 bit). These counters when loaded start down counting on negative edge of each clock pulse. There are six modes of operation of 8253 counters, in

- 36 -

all these modes of operation the output of the counters changes status on the terminal count. In the thesis work the counter zero has been used in the mode zero. In this mode the counter output becomes low as soon as the count is loaded and goes high on terminal count. The down counting is enabled by the high status of gate. The clock pulses to the Timer To are derived from the voltage controlled oscillator.

The high going output of the counter  $T_0$  interrupts microprocessor via RST 5.5. The firing command is outputted via 8255 port pins PA<sub>0</sub> to PA<sub>5</sub>. The firing pulse duration is programmed to be 180 µS. These firing pulses are amplified using a pulse amplifier circuit which is same as described in the analog firing circuit scheme.

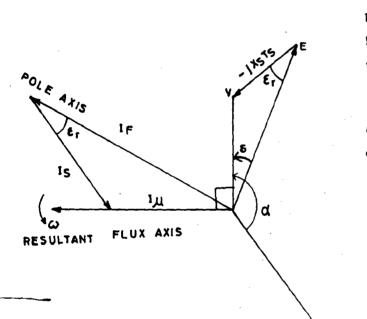

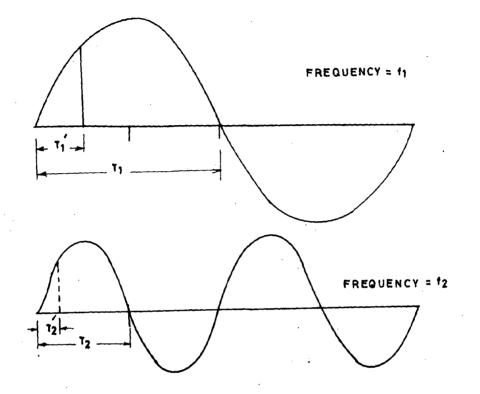

## 3.2 ROLE OF VCO IN VARIABLE FREQUENCY MICROCOMPUTER BASED FIRING SCHEME FOR LCI:

The LCI output voltage and frequency can be changed proportionally by,

- 1. Controlling D.C. link voltage

- 2. Cos  $\alpha$

The field current has been assumed constant in both the above cases. As explained earlier the firing angle  $\alpha$  is **fixed** by the delay word loaded in counter 0 of 8253. A delay word table giving delay words for different firing angle  $\alpha$ , is as given in Table 3.2 is loaded in the memory of the micro-computer from memory address CF00 to CF77. This table is

prepared for a fixed value of operating frequency and voltage and also a fixed value of clock frequency of timer counter  $T_{0}$ .

In case of variable frequency operation of LCI single delay word will not be able to maintain firing angle constant, for a constant frequency of clock.

Thus there are two alternatives possible,

- (1) Change delay word loaded keeping clock input frequency of 8253 constant,

- (2) Change the clock input frequency of 8253 proportionally with the LCI frequency keeping, delay word loaded constant.

The first alternative requires a large no of delay tables, one for each operating frequency of LCI. Thus, this will require a large memory space of microcomputer and also cause a jerky transition from one operating point to other. The disadvantage of excessive memory space required can be overcome by computing the delay word-in each cycle from the operating frequency of LCI. This will again require much CPU time which could be usefully utilized in some other important control action.

In the second method a single delay word table is required. The clock frequency of timer counter is the output frequency of a VCO, which is proportional to the input voltage of VCO. This input voltage if it is derived from the LCI voltage, then LCI voltage changes with LCI frequency which in turn changes the clock input frequency. Thus a constant

FIRING ANGLE O REMAINS CONSTANT FOR 1 AND 12

$$1E \frac{T_{1}}{T_{1}} = \frac{T_{2}}{T_{2}}$$

BUT  $T_1 = 2T_2$

$$\therefore$$

$T_1 = 2T_2$

$\frac{1}{f_1 V_{CO}} = \frac{2 \times 1}{f_2 V_{CO}}$  FOR CONSTANT DELAY WORD = N

# FIG. 3.4 PRINCIPLE OF FIRING ANGLE CONTROL WITH Vco

firing angle will be obtained at variable frequencies with the help of a single delay word as explained in the Fig 3.4. The basic advantages of this method are,

- 1. Only one delay word table is required, designed at a particular operating frequency i.e. 50Hz and V/f ratio i.e. 8. The VCO output frequency is 36 K Hz at these operating conditions which is well within the operating frequency range of 8253,

- 2. The real time of CPU is saved and can be used for other control actions since it is free from the frequency instrumentation problems.

The only disadvantage is that the delay words will have to be modified if the excitation current (i.e. V/f ratio) is changed. This can be easily accomplished through software by sensing the field current and modifying the delay word proportionally. However in the thesis work the synchronous machine is operated in hard saturation region hence change in field current would not cause a considerable error in the set value of  $\alpha$ .

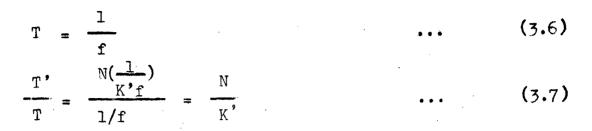

It can be shown analytically that value of firing angle remains constant in this method.

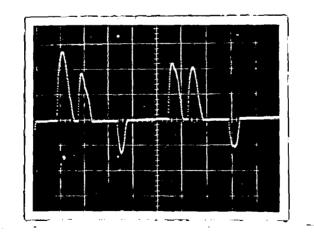

The firing angle  $\alpha$  will remain constant at two frequencies if the ratio of -T' (i.e. the time delay for  $\alpha$ ) and T the time period of the LCI voltage remains constant as shown in Fig 3.4.

- 39 -

- 40 -

i.e.  $\alpha$  is constant if,

$\frac{T}{T}$  = constant ( at  $f_1$  and  $f_2$ )

or T'/T is frequency independent

$f_{VCO}$  = Output frequency of VCO

$V_{\rm TN}$  = input voltage to VCO.

$K_{o}$  = transfer function of VCO

- =  $f_{VCO}/V_{IN}$ .

- $K_1$  = constant of proportionally for  $V_{LCI}$  output voltage, and frequency i.e.  $K_1 = V_{LCI}/f$ .

$$K_2$$

= constant of proportionallity for  $V_{IN}$  to  $V_{CO}$ , and  $V_{LCI}$ .

=  $V_{IN}/V_{LCI}$

N = Delay word for timer 8253

If the field current of synchronous motor is kept constant then

$V_{LCI} = K_1 x f$  ... (3.1)

$V_{IN} = K_2 V_{LCI}$  ... (3.2)

Combining equations (3.1) and (3.2) we get

$$V_{IN} = K_1 \times K_2 \times f$$

... (3.3)

$f_{VCO} = K_{o} V_{IN}$

$$f_{VCO} = K_0 \times K_1 \times K_2 \times f$$

... (3.4)

Let K' =

$$K_1 \times K_0 \times K_2$$

= constant

$$T' = N \times (\frac{1}{f_{VCO}})$$

... (3.5)

## TABLE 3.1

## FIRING COMMAND DATA

Range of firing angle  $\alpha = 0^{\circ}$  to  $60^{\circ}$

| Ø <sub>R</sub>                                               | φ <sub>Y</sub> | ø <sub>B</sub> | I quan-<br>tizer | Address of<br>firing<br>command | ON<br>SCRS | Firing<br>Command                 |

|--------------------------------------------------------------|----------------|----------------|------------------|---------------------------------|------------|-----------------------------------|

| 1                                                            | 2              | 3              | 4                | 5                               | 6          | 7                                 |

| 0                                                            | 0              | 1              | 1                | D000+01                         | 4,5        | 00011000<br>(PA7_PA0)<br>i.e.18H. |

| 0                                                            | 1              | 0              | 2                | D000+02                         | 2,3        | 00000110<br>i.e. 06H              |

| 0                                                            | l              | 1              | 3                | D000+03                         | 3,4        | 00001100<br>i.e. OCH              |

| 1                                                            | 0              | 0              | 4                | D000+04                         | 6,1        | 00100001<br>i.e. 21H              |

| 1                                                            | 0              | 1              | 5                | D000+05                         | 5,6        | 00110000<br>ì.e. 30H              |

| 1                                                            | 1              | 0              | 6                | D000+06                         | 1,2        | 00000011<br>i.e. 03H              |

| Range of firing angle $\alpha = 60^{\circ}$ to $120^{\circ}$ |                |                |                  |                                 |            |                                   |

| 1                                                            | 2              | 3              | 4                | 5                               | 6          | 7                                 |

| 0                                                            | 0              | l              | l                | . D000+07                       | 3,4        | ОС Н                              |

| 0                                                            | 1              | 0              | 2                | D000+08                         | 1,2        | 03 H                              |

| 0                                                            | 1              | 1              | 3                | D000+09                         | 2,3        | 06 H                              |

| 1                                                            | 0              | 0              | 4                | D000+0A                         | 5,6        | 30 H                              |

| l                                                            | 0.             | 1              | 5                | D000+0B                         | 4,5        | 18 H                              |

| 1                                                            | l              | 0              | 6                | D000+0C                         | 6,1        | 21 H -                            |

|        |   |   | * |           |     | والمتناعين والالالا المحب والياد المحبولين والمرابق |

|--------|---|---|---|-----------|-----|-----------------------------------------------------|

| 1      | 2 | 3 | 4 | 5         | 6   | 7                                                   |

| 0      | 0 | l | 1 | D000+0D   | 2,3 | 06 H                                                |

| 0      | 1 | 0 | 2 | D000+0E   | 6,1 | 21 H                                                |

| 0      | 1 | 1 | 3 | DOOO+OF   | 1,2 | 03 H                                                |

| · 1    | 0 | 0 | 4 | D000+10   | 4,5 | 18 H                                                |

| 1      | 0 | 1 | 5 | - D000+11 | 3,4 | OC H                                                |

| ב<br>ב | 1 | 0 | 6 | D000+12   | 5,6 | 30 H                                                |

|        |   |   |   |           |     |                                                     |

Range of firing angle  $\alpha = 120^{\circ}$  to  $180^{\circ}$

1

- 42 -

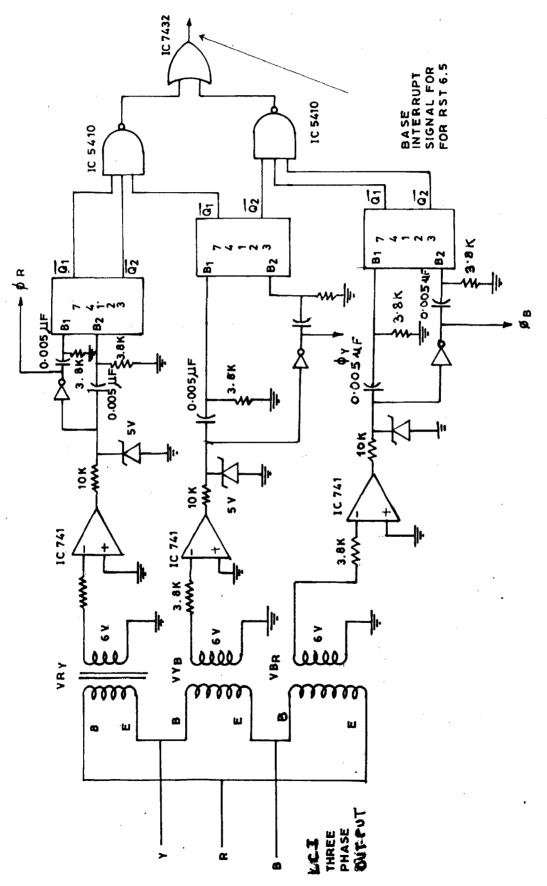

FIG. 3. 5 BLOCK DIAGRAM OF ZERO CROSSING CIRCUIT

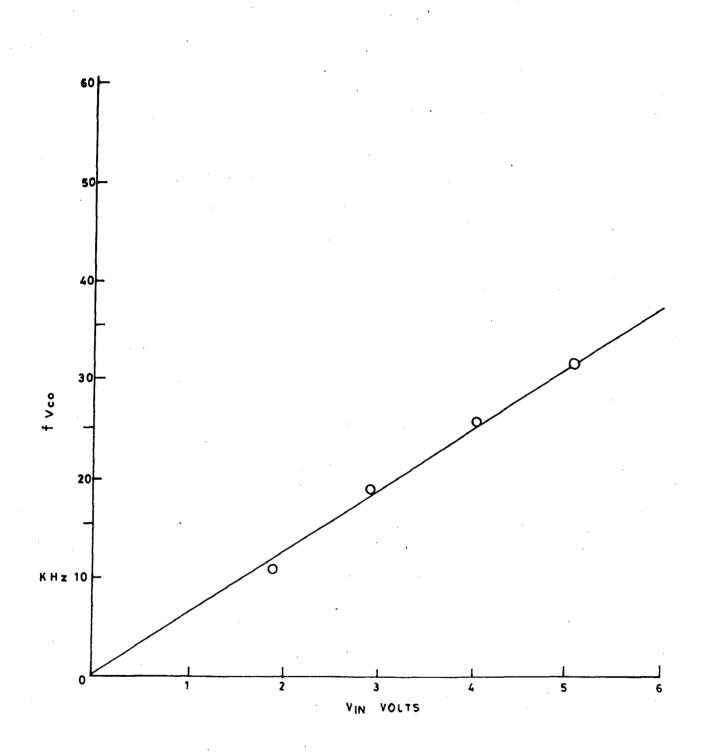

From the equation 3.3, it is clear that ratio of T' and T is only dependent on N i.e. delay word and is totally independent of frequency for constant value of field current of SM. The relation of output frequency versus input voltage of the LM 331. VCO is as given in Fig 3.7. It is clear that a linear relation exists between  $f_{VCO}$  and voltage input to VCO

#### 3.3 DESIGN OF ZERO CROSSING DETECTOR CIRCUIT:

The six synchronising signals required by the microprocessor for controlling the firing angle of a three phase bridge are generated by this circuit. The synchronising signals are nothing but the zero crossing points of the six line voltages. The zero crossing points are detected by the comparator as given in the Fig 3.5.

A monoshot is triggered at each zero crossing point. The output pulse width of monoshot should be have a pulse width of at least 20  $\mu$ rs in order to effectively interrupt the microprocessor via  $R_{ST}$  6.5 interrupt. A pulse **Hrmin** of these synchronising signals displaced at 60° is obtained by logically combining the outputs of all the monoshots.

The block diagram of the zero crossing circuit is as given in Fig 3.5.

The zerocrossing detector consists of the following:

- 44

1. Signal transformers,

2. Comparators,

3. Differentiator,

4. Monoshots,

5. Logic NAND and OR gates.

### 3.3.1 SIGNAL TRANSFORMERS:

The stepped down line voltages of LCI are obtained from these transformers. Three single phase transformers of 440/6V, have been used. The primary windings of these transformers are connected in delta. The advantage of this connection is that the secondary output voltages will be in phase with the LCI line voltages; This enables the derivation of synchronising signals from line voltage zero crossing points.

#### 3.3.2 COMPARATOR:

The IC 741 is used as a comparator to compare the A.C. line voltage signals with  $\P V$ . The output signal of the comparator is a square wave. These signals are in phase with the line voltages. The signals are reduced to digital TTL level with the help of 5V zener diodes. The digital square wave outputs of 3 comparators which are in phase with  $V_{RY}$ ,  $V_{YB}$ ,  $V_{BR}$ , are sensed by microprocessor to determine the pair of SCR to be turned on for the particular  $60^{\circ}$  interval. The selection of SCR pair based on status of  $\phi_{R}$ ,  $\phi_{Y}$ ,  $\phi_{B}$  signals has already been explained.

FUNCTIONAL TABLE

ţ

(Q)

TABLE 3G(a)

| SNO | CLR | A  | В | Q  | Q  |

|-----|-----|----|---|----|----|

| 1   | L   | X  | Х | L  | Н  |

| 2   | ×   | H  | X | L  | H  |

| 3   | ×   | X  |   |    | H  |

| 4   | Н   | 1. | 1 |    | 1- |

| 5   | Н   |    | Н |    |    |

| 6   | 1   |    | Н | Л. | 1  |

FIG. 3 GID CIRCUIT DIAGRAN OF MONIC HOT 1412.5

### 3.3.3 INVERTER:

In order to obtain 6 signals from the 3 digital power signals  $\phi_R$ ,  $\phi_Y$ ,  $\phi_B$ , these signals are inverted using 7404 hex inverter to get  $\phi_R$ ,  $\phi_Y$ ,  $\phi_B$ . The rising edge of these 6 signals are used to trigger 6 monoshots. The rising edges are obtained by differentiating the square wave signals with a RC differentiator with a very small time constant RC = 10  $\mu$ S.

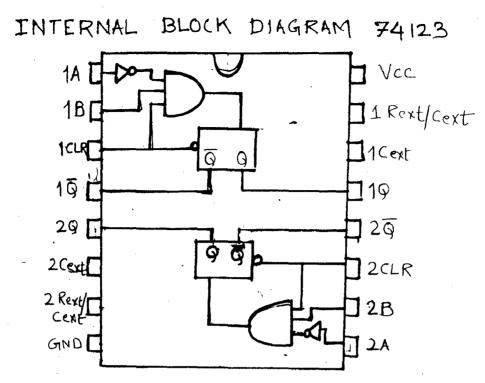

### 3.3.4 MONOSHOT:

The six monoshots have been obtained by using 74123 IC in positive edge triggered mode. The functional table, Internal block diagram of the chip with pin assignment and circuit diagram, all are shown in Fig.3.6. The output pulse width of monoshot is desided by the external timing capacitor and Resistance and is given by,

$t_w = 0.45 R_{ext} C_{ext}$

where

$R_{ext} = in K$   $C_{ext} = in picofarads$  $t_w = in nano seconds$

The designed value of  ${\rm R}_{\rm ext}$  and  ${\rm C}_{\rm ext}$  are

R = 5.64 K,  $C = 0.002 \mu \text{F}$ giving  $t_w = 50.4 \text{ micro seconds}$

A pulse train of all the synchronising signals spaced at  $60^{\circ}$  is obtained as shown in Fig 3.3 by logically combining them with the help of digital logic gates. The pulse train forms

- 45 -

FIG. 3.8 CIRCUIT DIAGRAM OF Vco

FIG. 3.9 RELATION BETWEEN FREQUENCY OUTPUT OF Vco AND INPUT VOLTAGE

the base interrupt signals for RST 6.5 interrupt.

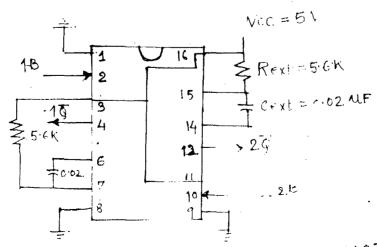

### 3.4 <u>VOLTAGE CONTROLLED OSCILLATOR</u>:

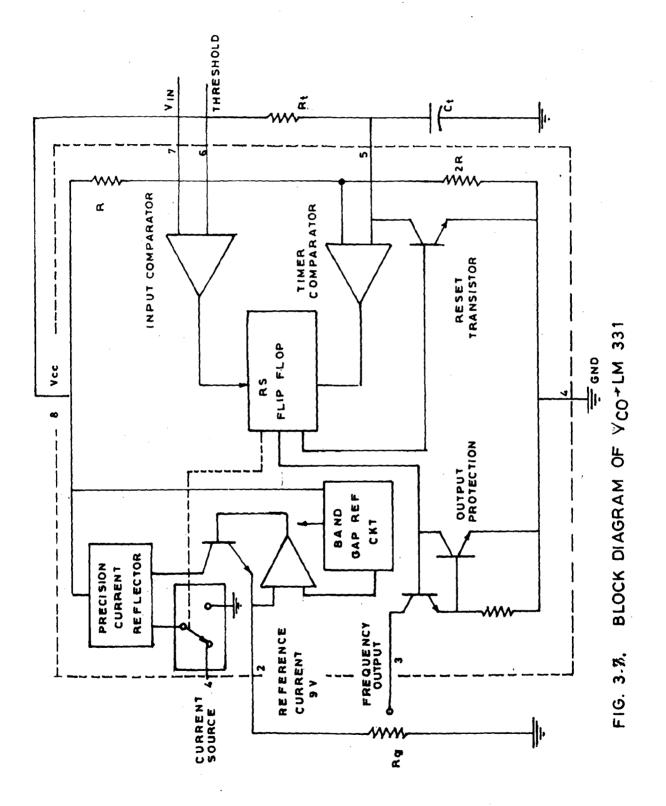

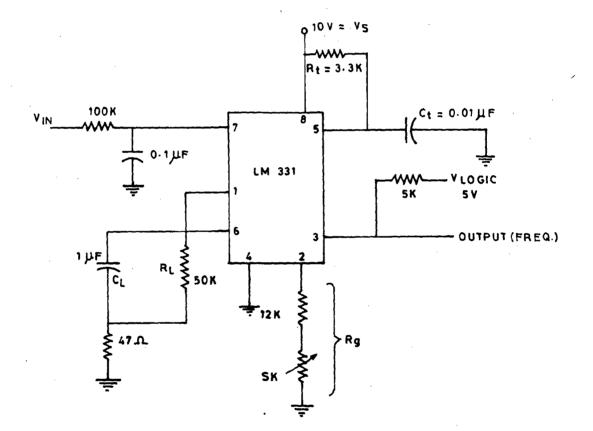

The VCO is designed using IC LM 331 from National Semiconductors. It is a precision voltage to frequency converter. The pin out diagram of this 8 pin DIP IC and it's internal functional block diagram is as shown in Fig 3.7. The circuit diagram of voltage to frequency converter is as given in Fig 3.8.

The frequency output of VCO is given by the relation  $f_{out} = \frac{V_{IN}}{2.00} \times \frac{R_{g}}{(R_{L} \times R_{t}) \cdot C_{t}}$

where  $R_g$ ,  $R_L$ ,  $R_t$ ,  $C_t$  are the symbolic names of the components as given in Fig 3.8. The VCO LM 331 operates from a single 5V power supply. The full scale frequency range of output is 1 KHz to 100 KHz.

It is clear from the block diagram that the VCO consists of a switched current source, input comparator, and a l shot timer. The comparator compares a positive input voltage  $V_{\rm IN}$  at the pin 7 with the voltage  $V_{\rm X}$  accross the capacitor at pin 6. If  $V_{\rm IN}$  is greater then the comparator triggers the one shot timer. The output of the one shot timer will turn on both the frequency output transistor as well as the switched current source for a time period of t =  $1.1R_{\rm t}C_{\rm t}$ i.e. up to the time when the voltage at pin 5 rises to  $2/3 V_{\rm CC}$  then the timer comparator causes the R-S flip flop to reset. This causes the reset transistor to turn on and the current source is switched off.

As the current source is switched off therefore the capacitor  $C_L$  now discharges through  $R_L$  until the voltage  $V_X$  at pin 6 fall below  $V_{\rm IN}$ . Then the comparator will again trigger on the 1 Shot timer and another cycle of operation begins.

The current flowing into  $C_L$  is  $I_{av}=ix(1.1xR_txC_t)xf$ and the current flowing out of  $C_L$  is  $Vx/R_L \sim V_{IN}/R_L$  $I_{av} = V_{IN}/R_L$  thus if the input voltage is doubled then the frequency has to double to maintain the charge balance.

A characteristics feature of this chip is the current pump circuit which forces the voltage at pin 2 to be at 1.9V and causes a current  $i = 1.9/R_g$  to flow out of pin 2. The precision current reflector provides a current equal to i (i.e. it reflects the current at pin 2 into the current source) to the current source. Thus the charging current is controlled by  $R_g$ .

The designed values of various components to obtain a frequency output of 36 KHz for  $V_{\rm IN}$  of 6 Volts are as given

> $R_{t} = 3.3 \text{ K}$   $R_{L} = 50 \text{ K}$   $C_{t} = 0.01 \,\mu\text{F}$   $C_{L} = 1 \,\mu\text{F}$  $R_{g} = 12 \text{ K} + 5 \text{ K}$  (Variable).

- 47 -

### TABLE 3.2

Table fo firing angle  $\alpha$  and delay words for counter  $T_{\mbox{\scriptsize o}}$  of  $\mbox{\scriptsize 8253.}$

$V_{LCI} = 400V$ , f = 50 Hz,  $f_{clock} = f_{VCO} = 36 KHz$ .

| S.NO. | MEMORY<br>ADDRESS | DELAY<br>COUNT | S.<br>NO   | MEMORY<br>ADDRESS | DELAY<br>COUNT | S.<br>NO. | MEMORY<br>ADDRESS | DELAY<br>COUNT |   |

|-------|-------------------|----------------|------------|-------------------|----------------|-----------|-------------------|----------------|---|

| 1     | CFOO              | 00 '           | 35         | CF22              | 22             | 70        | CF45              | 00             |   |

| 2     | CF01              | 00             | <b>3</b> 6 | CF23              | 00             | 71        | CF46              | 46             |   |

| 3     | CF02              | 02             | 37         | CF24              | 24             | 72        | CF47              | 00             |   |

| 4     | CF03              | 00             | 38         | CF25              | 00             | 73        | CF48              | 48             | , |

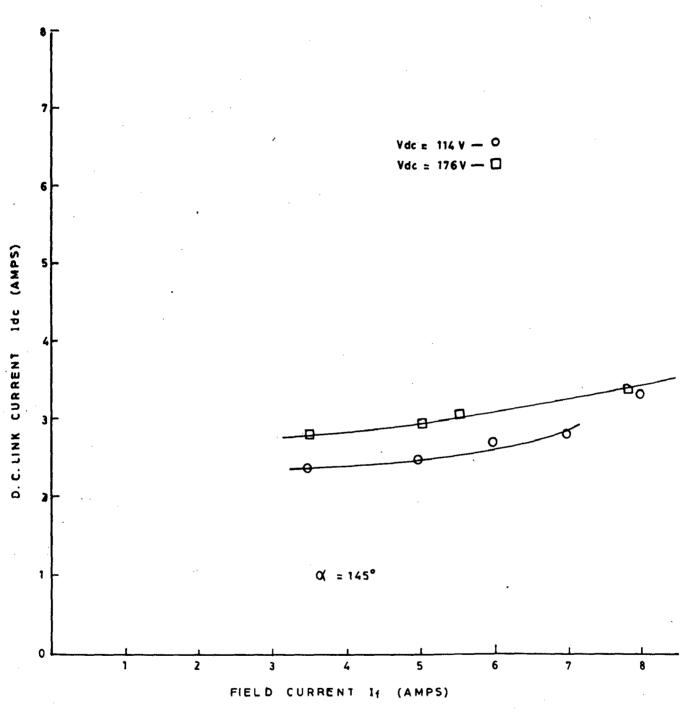

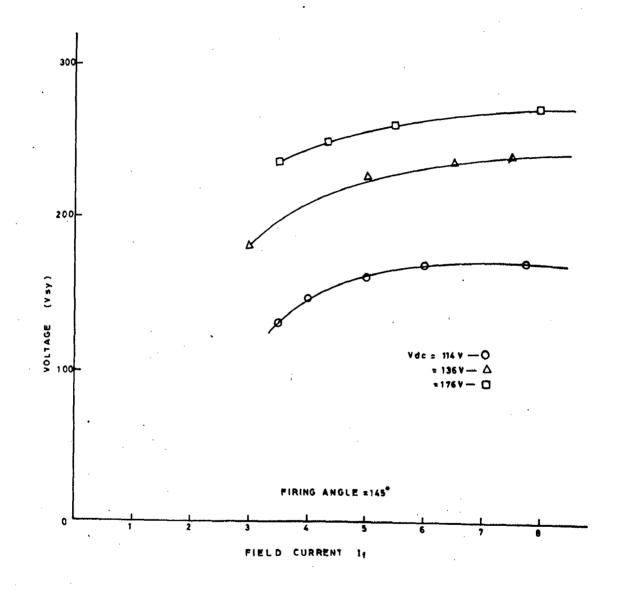

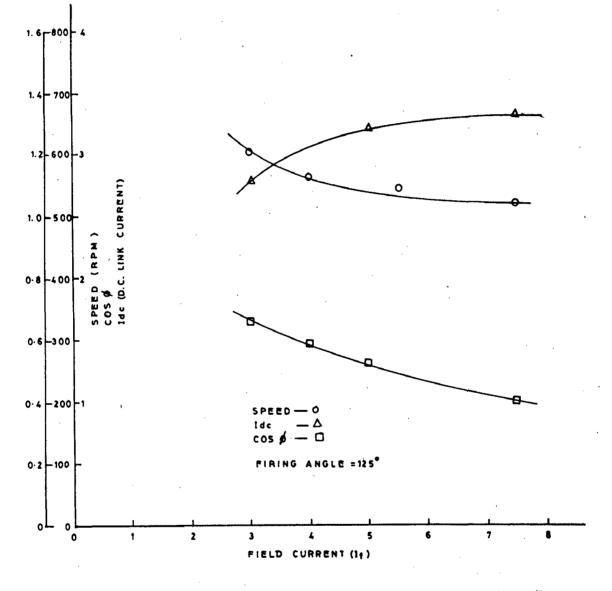

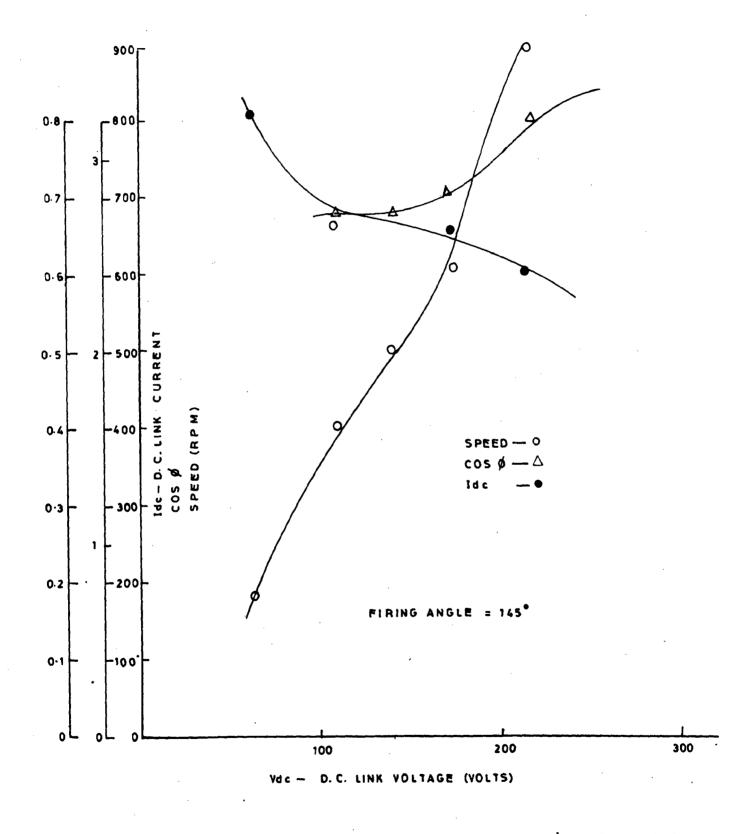

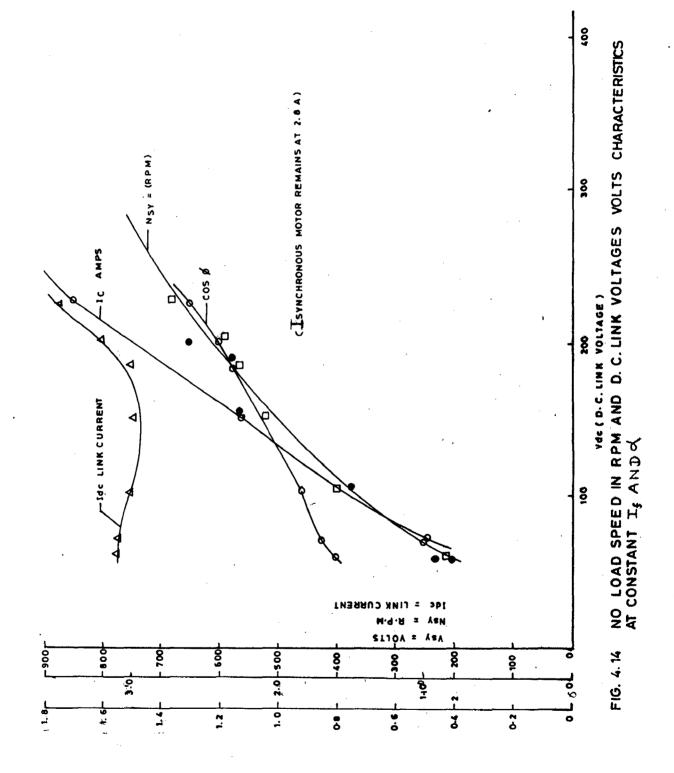

| 5     | CF04              | 04             | <u>3</u> 9 | CF26              | 26             | 74        | CF49              | 00             |   |