# MICROPROCESSOR BASED IC TESTERS

### A DISSERTATION

Submitted in partial fulfilment of the requirements for the award of the degree

of

MASTER OF ENGINEERING (System Engineering & Operations Research)

CKPT

by

### Capt H.C. LOHUMI

DEPARTMENT OF ELECTRICAL ENGINEERING UNIVERSITY OF ROORKEE ROORKEE-247 672 (U-P.) Oct. 1982

#### CERTIFICATE

Certified that the dissertation entitled "MICROPROCESSOR BASED IC TESTERS" which is being submitted by Capt H C LOHUMI in partial fulfilment for the award of the Degree of MASTER OF ENGINEERING in ELECTRICAL ENGINEERING (System Engineering & Operations Research) of the University of Roorkee, Roorkee, is a record of student's own work carried out by him under my supervision and guidance. The matter embodied in this dissertation has not been submitted for the award of any other Degree or Diploma.

This is further to certify that he has worked for a period of about nine months from Jan.82  $\sim$  to Oct.82  $\sim$  for preparing this dissertation at this University.

anan 11 m

(M.K. VASANTHA) Reader Electrical Engg. Department University of Roorkee ROORKEE-247 672 U.P.

Dated : Oct.13,1982

#### ACKNOWLEDGEMENT

I would like to express my gratitude to Mr.M.K.Vasantha, Reader, Department of Electrical Engineering, University of Roorkee, Roorkee for initiating me in the field of microprocessor applications implementation. I am, indeed, indebted to him for his unflagging support and invaluable guidance in solving numerous problems encountered in the practical work.

I am also grateful to Dr. G.K.Tandon, Head, Computer Centre for permitting me the use of ADM-3A terminal for this work.

I am extremely grateful to Mr.M.Pant, Lecturer, Department of Electrical Engineering and Mr. A.K.Raja, Reader, Department of Electrical Engineering for permitting unrestricted access to various facilities at their disposal, freely and for material assistance.

Special thanks are due to Mr. L.K.Gupta for helping me in solving the problems encountered in PCB design and fabrication. Lastly, I would like to thank all the teachers and the staff of the Department for assisting me in various stages of this dissertation.

Capt H C Lohumi

#### ABSTRACT

Microprocessor based systems are being used increasingly in nearly all the walks of life. Their usage is wide spread, from house-hold gadgets to sophisticated missiles. In order to be able to design even simple microprocessor based systems, it is necessary to understand completely the working of the microprocessor chip and allied peripherals. For this, a 'hand on' experience is a must. The aim of this dissertation was to get this experience. Microprocessor based digital IC testers were a natural choice of the practical system selected for design because of the necessity of testing IC chips before actually using them.

The basic unit used was HIL-2961 microprocessor trainer, an INTEL 8085A based system. A brief description of this unit is given in Chapter 1. Chapter 2 deals with the underlying principles of IC testing alongwith an initial test programme for IC 7400.

A CRT terminal is a very useful peripheral device for increasing the user efficiency in communicating with the microcomputer. The IC tester developed in this dissertation operates through ADM-3A, a CRT terminal.

Abstract contd..

Chapter 3 deals with design of the hardware interface between the terminal and the microcomputer. Monitor developed for the IC tester is discussed in Chapter 4.

. .

Test programmes for various ICs are discussed in Chapter 5 and finally the design of a Universal IC Tester is discussed in Chapter 6. Chapter

•.

| 1 | GETTING ACQUAINTED WITH HIL-2961<br>MICROPROCESSOR TRAINER | 1           | 1-1          |

|---|------------------------------------------------------------|-------------|--------------|

|   | 1:1 Introduction                                           |             | 1-1          |

|   | 1:2 Clock Frequency                                        | * d<br>● ●  | 1-3          |

|   | 1.3 Memory Allocation and Decoding Circuitry               | 1           | 1-3          |

|   | 1.4 Input and Output Ports                                 | • •         | 1 <b>-</b> 5 |

|   | 1.5 Keyboard Management                                    | 1           | 1-9          |

|   | 1.6 Bus Protection                                         | <b>4</b> 4  | 1-9          |

|   | 1.7 Utility Programmes                                     | a .<br>● ●  | 1-11         |

| 2 | GENESIS OF IC TESTING AND 7400 TEST PROGRAMME              | ••          | 2-1          |

|   | 2.1 Introduction                                           | ••          | 2–1          |

|   | 2.2 Detection of Logic Malfunction                         | • •         | 2-3          |

|   | 2.3 Implementation of Test Sets                            | •           | 2-5          |

|   | 2.4 Development of IC Tester                               | • •         | 2-7          |

|   | 2.5 Quadruple Two Input Nand Gate IC 7400                  | ••          | 2-8          |

|   | 2.6 Minimal Test Set Development for IC 7400               |             | 2-8          |

|   | 2.7 Key Debouncing                                         | )<br>•      | 2-10         |

|   | 2.8 Programme for IC 7400 Test                             | • •<br>* 4. | 2-13         |

| 3 | INTERFACING HIL-2961 WITH CRT TERMINAL                     |             | 3-1          |

|   | 3.1 Introduction : Need for a CRT Terminal                 | • •         | 3-1          |

|   | 3.2 Interactive Display Terminal ADM-3A                    | • •         | 3-2          |

|   | 3.3 Development of Interface .                             | . •         | 3-4          |

|   | 3.4 Hardware Interface                                     | •           | 3-5          |

|   | 3.5 Power Supply                                           | * •         | 3-6          |

|   | 3.6 Baud Rate Generator                                    | ••          | 3 <b>-</b> 6 |

|   |                                                            |             |              |

|     |      | -:2:-                                             |             |      |

|-----|------|---------------------------------------------------|-------------|------|

|     |      |                                                   |             |      |

|     |      | 3.6.1 Design Calculations                         | •           | 3-8  |

|     |      | 3.6.2 Operating the Baud Rate Generator           |             | 3-9  |

|     | 3•7  | RS-232C and 8251A USART Interface                 | • •         | 3-11 |

|     |      | 3.7.1 INTEL 8251A USART                           | ` &<br>₿ ●  | 3-14 |

| 4   | MONI | FOR FOR THE CRT TERMINAL                          | * •         | 4-1  |

|     | 4•1  | Introduction                                      | ••          | 4-1  |

|     | 4.2  | Sign on Message Programme                         | - 4]<br>∳ ● | 4⇔2  |

|     | 4.3  | Get Command Programme                             | ••          | 4-2  |

|     | 4.4  | Functional Commands                               | ••          | 4-3  |

|     | 4.5  | Try Command                                       | ••          | 4-4  |

|     | 4.6  | List Command                                      | ••          | 4-5  |

|     | 4•7  | Execute (GO) Command                              | • •         | 4-5  |

|     | 4.8  | Subroutines for Programmes                        | • •         | 4-6  |

| · . | 4.9  | Monitor Listing                                   | • •         | 4-6  |

| 5   |      | PROGRAMMES DEVELOPMENT FOR A FEW<br>CTED IC CHIPS | • •         | 5-1  |

|     | 5.1  | Introduction                                      |             | 5-1  |

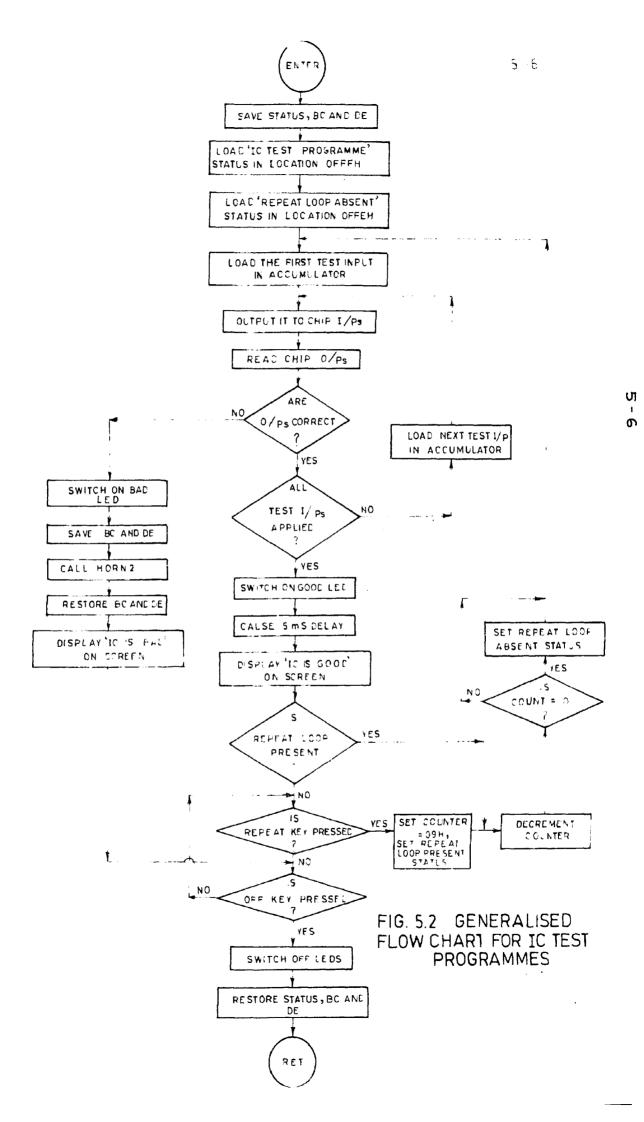

|     | 5.2  | Test Programmes                                   |             | 5-1  |

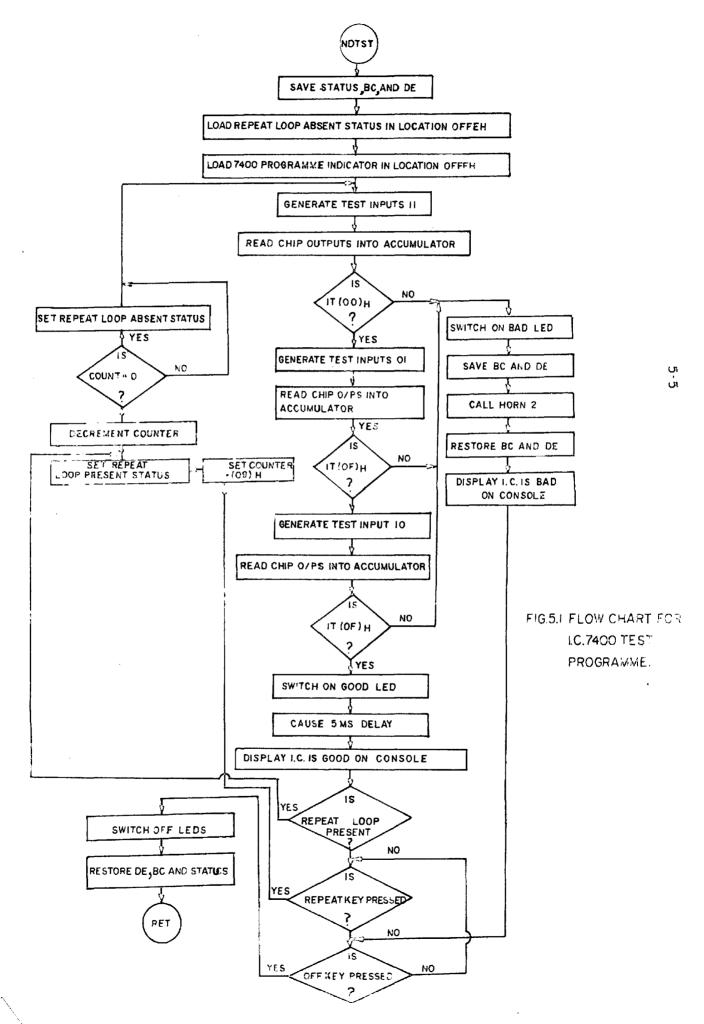

|     | 5.3  |                                                   | ••          | 5-2  |

|     | 5.4  | •                                                 | o 🌢         | 5-4  |

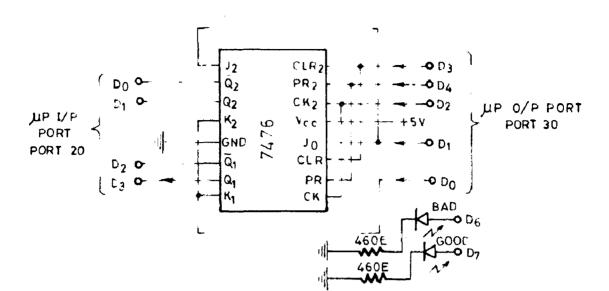

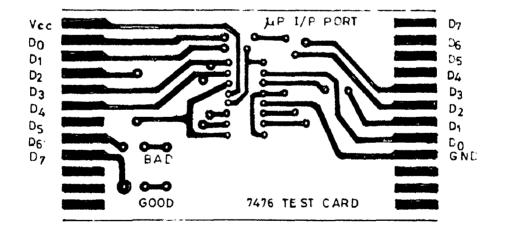

|     | 5.5  | IC 7476 Test Programme                            | • •         | 5-4  |

|     | 5.6  | IC 7490 Test Programme                            | • •         | 5-6  |

|     | 5.7  | IC 7493 Test Programme                            |             | 5-9  |

|     |      |                                                   |             |      |

.

-: 3: -

| 6 | UNIVE       | ERSAL IC TESTER                     | • • | 6-1          |

|---|-------------|-------------------------------------|-----|--------------|

|   | 6.1         | Introduction                        | ••  | 6-1          |

|   | <b>6.</b> 2 | Requirements                        | ••  | 6-1          |

|   | 6.3         | Design of Universal IC Tester       | ••  | 6-2          |

|   | 6.4         | Programming the Universal IC Tester | ••  | 6-4          |

|   | 6.5         | Comments                            | ••  | 6 <b>-</b> 4 |

| 7 | CONCI       | LUSION                              | ••  | 7-1          |

|   | 7.1         | Summary of the Work                 | ••  | 7 <b>-</b> 2 |

|   | 7.2         | Recommended Developments            | ••  | 7-2          |

|   | REFER       | RENCES                              | ••  | R-1          |

### APPENDICES

# Appendix No.

.

| A | INTEL 8085A : Brief Description                                        | • • | A <b>1</b> |

|---|------------------------------------------------------------------------|-----|------------|

| В | 8085A Instruction Set                                                  | ••  | B-1        |

| C | HIL-2961 Utility Programmes : Explanation                              | • • | C-1        |

| D | Interactive Display Terminal ADM-3A                                    | ••  | D-1        |

| E | Details of Components                                                  | ••  | E-1        |

| F | Serial Data Transmission Formats                                       | ••  | F-1        |

| G | INTEL 8251A Universal Synchronous<br>Asynchronous Transmitter Receiver | • • | G-1        |

| Н | Initialization Programme for Universal<br>IC Tester Testing IC 7400    | ¢ 🌢 | H <b>1</b> |

•

• •

### CHAPTER-1

|          | ACQUAINTED |           |

|----------|------------|-----------|

| HIL-2961 | MICROPROCI | SSOR      |

| TRAINER  |            | - manaped |

#### 1.1 INTRODUCTION

HIL-2961 microprocessor trainer (1), marketed by Hindustan Instruments Limited, is a microcomputer based on INTEL's 80854 uP. This system formed the basis of all the work carried out in this dissertation. It is, therefore, necessary to gain an insight into the various functional aspects of this system before proceeding further with the discussion of the dissertation work.

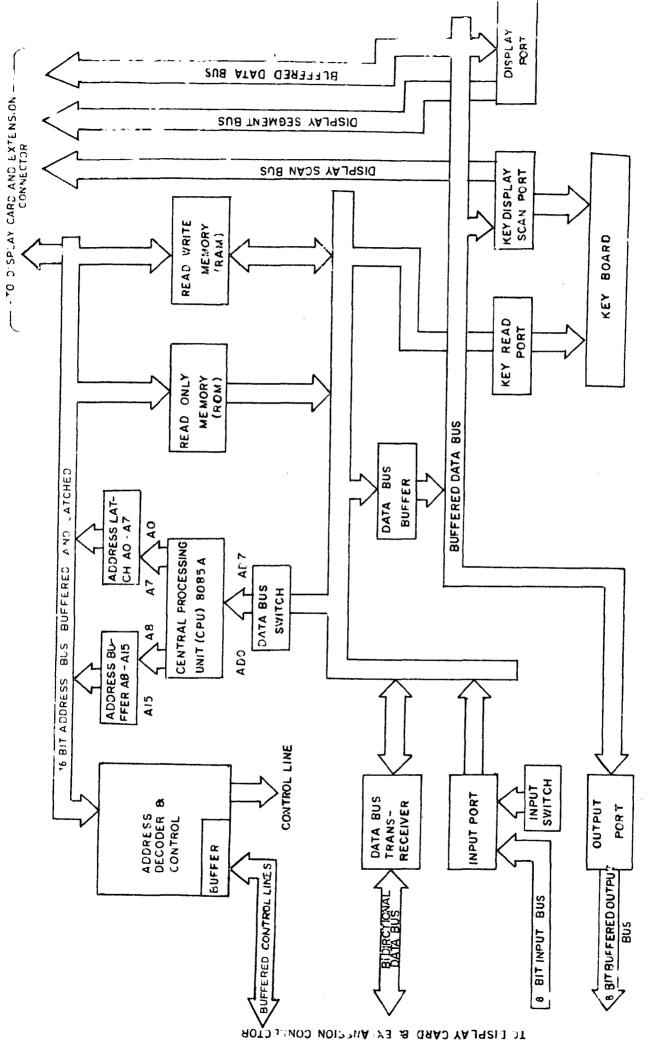

The pin configuration and brief description of the 8085A uP is given at Appendix 'A'. The summary of the instruction set is given at appendix 'B'. Fig.1.1 shows a block diagram representation of HIL-2961's architecture. The user can communicate with the system through a 24 key keyboard. Sixteen of these keys are used for the Hexa decimal code and the remaining eight keys viz., FETCH REG, FETCH ADDR, STORE/INC, DECR, SINGLE STEP, FETCH PC, MC STEP and EXECUTE provide the user the facility of entering and executing his programme as well as faciliate software debugging.

Results of various operations are displayed on a six digit seven segment display provided on the top right hand side of the trainer. The first four digits show the addressed location

FIG 1 HL 2961 ARCHITECTURE.

in hexa-decimal code and the last two display the content of that location. This di**b**play is software managed. Another six digit, seven segment display provided on the top left hand side of the trainer displays the address and its content in a similar manner in machine step operation. This display is hardware managed.

1.2 CLOCK FREQUENCY

The 3085 A CPU can operate at a maximum internal clock frequency of 3.125 MHz. The actual operating frequency is dependent upon the parallel resonant frequency of the quartz crystal placed at its  $X_1$  and  $X_2$  inputs, which must be twice the internal frequency desired. Thus the 8085 A CPU can accomodate a quartz crystal having a parallel resonant frequency of 6.25 MHz or less. In HIL-2961, the external quartz crystal has the parallel resonant frequency of 4.00 MHz, thereby generating an internal clock frequency of 2.00 MHz for the CPU operation. Practically, this frequency was measured using a digital frequency counter and found to be 2.0007 MHz.

### 1.3 MEMORY ALLOCATION AND DECODING CIRCUITRY

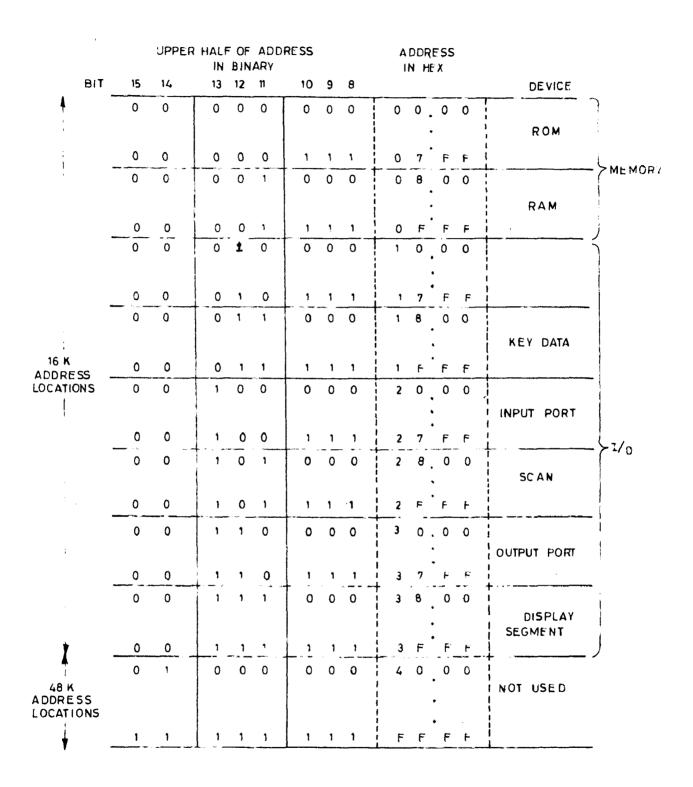

The 8085AµP can address 64K bytes of memory. Of these, only 16 K bytes have been decoded in the HIL 2961. This gives approximately 1.8 K bytes of memory space to theuser. Fig.1.2 shows the system address map for various devices used in the trainer. The memory allocation for the RAM, ROM, one E/P port

|                       |    | UPPE | R HALF<br>IN | ≂ OF<br>BIN |    | RESS |         |          |          |   | DDR<br>N HI | ESS<br>EX |        |                 |                    |

|-----------------------|----|------|--------------|-------------|----|------|---------|----------|----------|---|-------------|-----------|--------|-----------------|--------------------|

| BIT                   | 15 | 14   | 13           | 12          | 11 | 10   | 9       | 8        |          |   |             |           |        | DEVICE          |                    |

| 4                     | 0  | 0    | 0            | 0           | 0  | 0    | 0       | 0        | (        | 0 | 0           | 0         | 0      | 1               |                    |

| 2                     |    |      |              |             |    |      |         |          |          |   | •           | •         |        | ROM             |                    |

|                       | 0  | 0    | 0            | 0           | 0  | 1    | 1       | 1        |          | 0 | 7           | F         | ۴      |                 | <b>.</b>           |

|                       | 0  | 0    | 0            | ٥           | ,  | 0    | 0       | 0        | <b>†</b> | 0 | 8           | 0         | 0      | E               |                    |

|                       |    |      | 1            |             |    |      |         |          | į        |   |             | •         |        | RAM             |                    |

|                       | 0  | 0    | 0            | 0           | 1  | 1    | 1       | ۱        |          | 0 | ۴           | ,<br>F    | F      | ,<br>,          | )                  |

|                       | 0  | 0    | 0            | 1           | 0  | 0    | 0       | 0        | 1        | 1 | 0           | 0         | 0      |                 | $\hat{\mathbf{b}}$ |

|                       |    |      |              |             |    |      |         |          |          |   |             | •         |        | 1               |                    |

|                       | 0  | 0    | 0            | ١           | 0  | 1    | 1       | 1        |          | 1 | 7           | F         | F      |                 |                    |

|                       | 0  | 0    | 0            | 1           | 1  | 0    | 0       | 0        | +        | 1 | 8           | 0         | 0      |                 |                    |

| ì                     |    |      |              |             |    |      |         |          | {        |   |             | •         |        | KEY DATA        |                    |

| 16 K                  | 0  | 0    | 0            | 1           | 1  | 1    | 1       | 1        |          | 1 | F           | F         | F      |                 |                    |

| ADDRESS<br>LOCATIONS  | 0  | 0    | 1            | 0           | 0  | 0    | 0       | 0        | +        | 2 | 0           | 0         | 0      | 1               | -                  |

|                       |    |      | Ì            |             |    |      |         |          |          |   | •           | •         |        | INPUT PORT      |                    |

|                       | 0  | 0    | 1            | 0           | 0  | ,    | 1       | 1        |          | 2 | 7           | F         | F      | 1               |                    |

|                       | 0  | 0    | -†·,         | 0           |    | 0    | 0       | 0        | ·+       | 2 | 8           | 0         | 0      |                 | $\cdot \geq 1/0$   |

| i                     |    |      |              |             |    |      |         |          | į        |   |             | •         |        | SCAN            |                    |

|                       | 0  | 0    | 1            | 0           | 1  | 1    | 1       | 1        |          | 2 | F           | F         | F      | 1               |                    |

| 4                     | 0  | 0    | 1            | 1           | 0  | 0    | 0       | 0        | +        | 3 |             | . 0       | 0      |                 |                    |

|                       |    | -    |              |             | -  |      | •       | •        | i<br>T   |   | ~           | •         | •      | OUTPUT PORT     | 1                  |

|                       | 0  | 0    | 1            | 1           | 0  | 1 1  | 1       | 1        | 1        | 3 | 7           | •<br>F    | F      |                 |                    |

|                       | 0  | 0    |              | 1           | 1  | 0    | 0       | 0        | +        | 3 | <br>8       | 0         | 0      | -+              |                    |

|                       |    |      |              |             |    |      |         |          | 1        |   |             | •         |        | DISPLAY         |                    |

| *                     | 0  | 0    | 1            | 1           | 1  | 1    | 1       | 1        | -        | 4 | F           | •         | F      | SEGMENT         |                    |

| Å.                    |    |      | 0            |             | 0  | t o  | '-<br>0 | ··'<br>0 | +        | * | 0           | _`<br>_0  | °<br>0 |                 | )                  |

| 48 K                  | -  |      |              | Ŭ           | -  |      | U       | v        | 1        | - | J           | • ~       | 5      | NOT USED        |                    |

| A DDRESS<br>LOCATIONS |    |      |              |             |    |      |         |          | i        |   |             | •         |        | 1               |                    |

| Ļ                     | ١  | ı    | ,            | ۱           | 1  | 1    | 1       | 1        |          | F | ۴           | F         | F      |                 |                    |

| Ŧ                     |    |      |              |             |    | .L   |         |          |          |   |             |           |        | - <del>  </del> |                    |

FIG 1.2 SYSTEM ADDRESS MAP FOR 2961 MICROPROCESSOR TRAINER

FIG 1.2 SYSTEM ADDRESS MAP FOR 2961 MICROPROCESSOR TRAINER

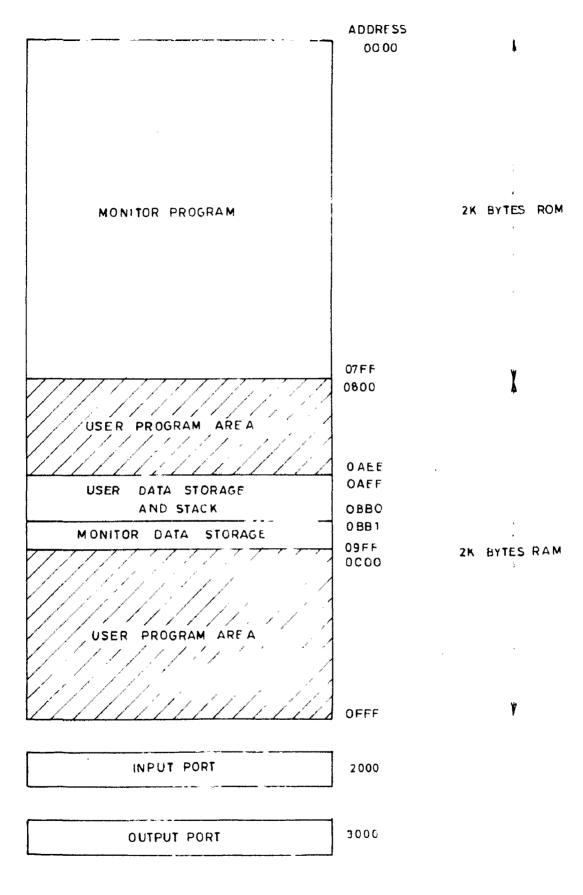

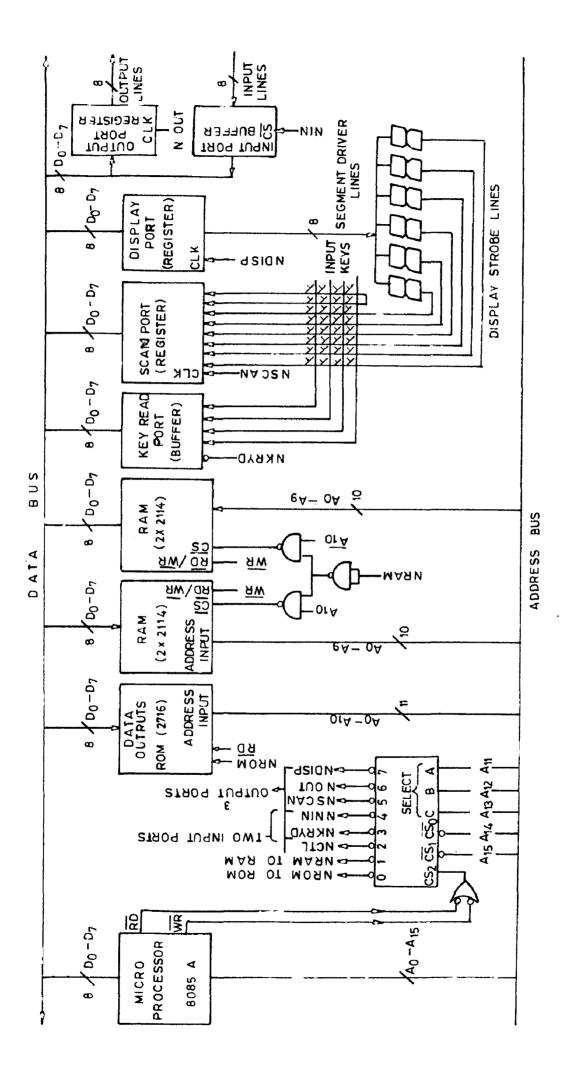

and one O/P port is shown in Fig.1.3. Hemory locations from 2000H to 27FFH serve a dual purpose. This space may either be utilized for addressing the Input port provided on the trainer, or else it may be used for 2K ROM storing the software for audio cassette interface, EPROM programming and some utility programmes. Either of these functions may be selected by the user by suitable positioning of a jumper provided on the trainer PCB. The address decoding circuitry for the 16K memory space is shown in Fig.1.4.

1.4 INPUT AND OUTPUT PORTS

The microprocessor trainer provides an eight bit parallel input port and an eight bit parallel output port. These ports may be addressed either through in-structions based on I/O mapped I/O (i.e. IN Fort or OUT port instructions) or those based on memory mapped I/O (i.e. STA addr or LDA addr and/other memory reference instructions). Since each of these ports is allocated 2K of memory space in the decoding, these ports may be addressed by any of the addresses shown in Table 1.1.

Both the ports are available on the 60-pin extension connector provided on the trainer. Through this connector all the signals of the 8085A CPU as well as some control signals used in the 2961 architecture are made available to the user for any hardware development.

FIG.1.3 MEMORY ALLOCATION IN HIL 2961

BLOCK DIAGRAM OF THE 2961 MICROPROCESSOR TRAINER SHOWING ADDRESS DECODING FIG.1.4

#### TABLE 1.1 : ADDRESSES FOR PORT SELECTION

| S.N | o. Port  | Type of addressing | Memory addresses/Port<br>Nos for selection. |

|-----|----------|--------------------|---------------------------------------------|

| 1   | I/P port | I/O mapped         | Port 20H to 27H                             |

| 2   |          | Memory mapped      | 2000H to 27FFH                              |

| 3   | 0/P port | I/O mapped         | Port 30 to 37H                              |

| 4   | d.0      | Memory mapped      | 3000H to 37FFH                              |

The data on the output port can be read on a set of 8 LEDs labelled OUTPUT on the display pannel. This data is latched through 741S273. This was very suitable for developing the IC tester, since a particular input for the IC under test could be held valid while the output of the IC was being read into the uP through the Input port.

In contrast, the Input port data bus is tristate buffered. Data can be entered into the input port by means of 'INPUT' switches provided on the trainer PCB. In order to load the data on the input port externally, all the switches must be held in 'HI' position, which pulls all the eight bits to logical 1. In addition, the jumper mentioned in Sec. 1.3 must be appropriately placed for enabling communication with the CPU through the input port.

# FIG 1.5 KEYBOARD INTERFACE IN HIL 2961

#### TABLE 1.1 : ADDRESSES FOR PORT SELECTION

| S.No. Port |          | Type of addressing | Memory addresses/Port<br>Nos for selection. |  |  |  |

|------------|----------|--------------------|---------------------------------------------|--|--|--|

| 1          | I/P port | I/O mapped         | Port 20H to 27H                             |  |  |  |

| 5          | -0 D-    | Memory mapped      | 2000H to 27FFH                              |  |  |  |

| 3          | 0/P port | I/O mapped         | Port 30 to 37H                              |  |  |  |

| 4          | -d.o-    | Memory mapped      | 3000H to 37FFH                              |  |  |  |

The data on the output port can be read on a set of 8 LEDs labelled OUTPUT on the display pannel. This data is latched through 74LS273. This was very suitable for developing the IC tester, since a particular input for the IC under test could be held valid while the output of the IC was being read into the µP through the Input port.

In contrast, the Input port data bus is tristate buffered. Data can be entered into the input port by means of 'INPUT' switches provided on the trainer PCB. In order to load the data on the input port externally, all the switches must be held in 'HI' position, which pulls all the eight bits to logical 1. In addition, the jumper mentioned in Sec. 1.3 must be appropriately placed for enabling communication with the CPU through the input port.

#### 1.5 KEYBOARD MANAGEMENT

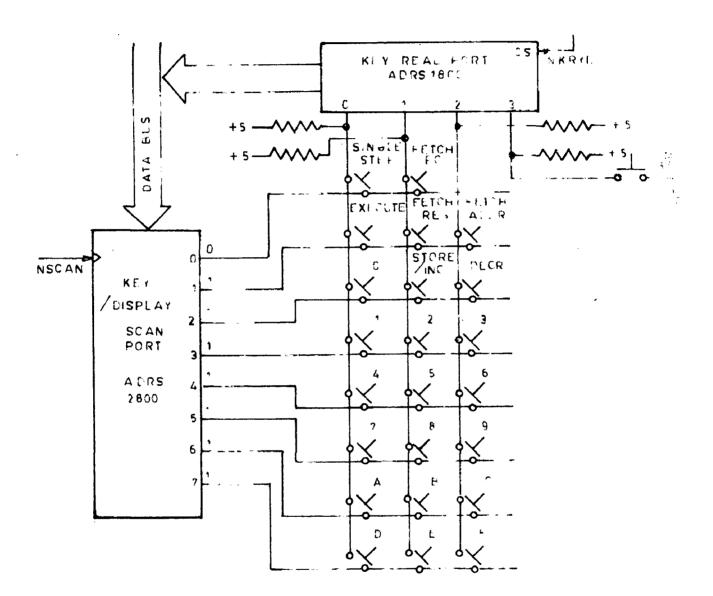

The keyboard consists of 24 keys. In order to differentiate between various keys, the keyboard is arranged into an 8 x 3 matrix. This is shown in Fig.1.5. The key scan port behaves as an output port and the key read port behaves as an input port. Through a monitor subroutine called KIND, different keys are identified uniquely as follows:

- 1. Data 11111110 is sent to the Scan port. Thus a LCM is placed on row zerc. other rows remain HIGH.

- 2. The key read port reads the column information .Since all bits are pulled HIGH, the column information will be XXXX1111 if no key is pressed.

- 3. In case a particular key in row zero is pressed, that particular column will be set LOW. This will be detected while reading the key read port.

- 4. If no key is found pressed, the monitor will arrange to place a zero on row 2,3 & so on and follow the same procedure. When aparticular key is found pressed, the uP branches to appropriate location connected fwith that key.

#### 1,6 BUS PROTECTION

In order to protect the system from any conflict arising due to placement of data continuously by the user erroneously on the data bus, while the CPU is directed to perform other operations requiring the data bus, the trainer data bus,

# FIG 1.5 KEYBOARD INTERFACE IN HIL 2961

.

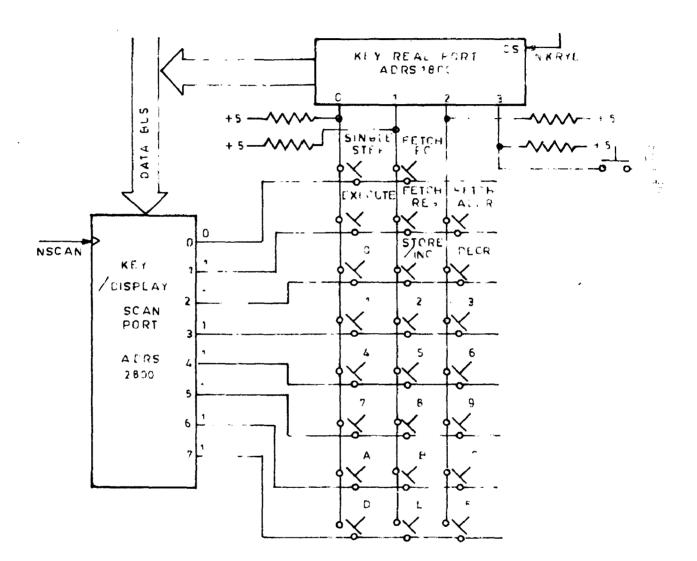

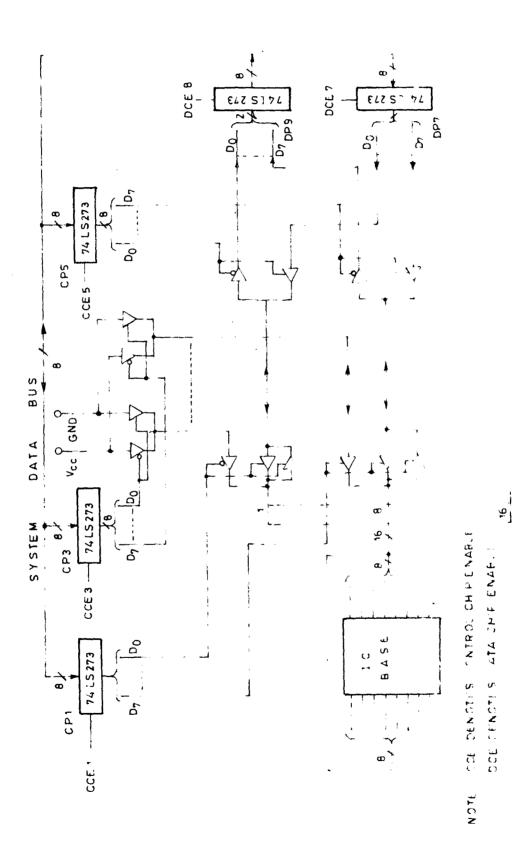

available externally at the expansion connector, has been designed to remain in output mode, normally. The output buffers are permanently enabled by connecting the D CUT terminal to Ground. The input buffers are permanently disabled by connecting D IN terminals to +5V line directly. In case the user wants to expand the system, the data bus must be programmed to be in the desired input or output mode. This is achieved by first disconnecting the permanent connections of D OUT to Ground and of D IN to +5V and then connecting a logic circuit shown in Fig.1.6.

As mentioned in Section 1.3, only 16K bytes of memory space has been decoded inside the trainer. It can be seen in Fig.1.4 that A15 and A14 lines are always logical ZERO while addressing any location inside the trainer. For this address space, the circuit of Fig.4.6 ensures that the data bus is always in output mode irrespective of RD signal. (D OUT is LOW and D IN is HIGH). When any location from 4000H to FWFFH is being addressed, either A15 or A14 or both will always be logical ONE and now the data bus will be in input mode whenever either RD goes LCW or INTA goes LOW. Otherwise, the data bus will remain in output mode.

1.7 UTILITY PROGRAMS

Two of the utility programmes viz., DELB and HORM subroutines have been incorporated in the test programmes developed for IC testing. Assembly language programmes for these subroutines

•

### FIG. 1.6 PROGRAMMING THE HIL 2961 EXTERNAL DATA BUS

.

were written down from the flow charts provided in the users' manual of HIL-2961. These programmes are given at Appendix 'C'.

.

-

.

#### CHAPTER-2

# GENESIS OF IC TESTING AND 7400 TEST PROGRAMME

#### 2.1 INTRODUCTION

Integrated circuit technology and its applications have brought about revolutionary changes in the design of circuits and systems. IC chips enable tremendous reduction in overall system size, increase system reliability and reduce maintenance and repair problems. Put in a well designed circuit, a good IC gives a long and trouble free service. Due to the dependence of correct system behaviour on the correct behaviour of the IC chip, there is an obvious need for testing an IC chip before using it in a circuit. An IC chip has numerous behaviourial aspects. These can be grouped, very generally, into two categories, viz., parametric behaviour and functional behaviour.

Parametric behaviour includes DC characteristics like threshold voltage, maximum voltage, fan-in, fanout; dynamic characteristics like propagation delays,

transient response; and frequency sensitivity, specifying the frequency range over which the IC can perform the desired function. Functional behaviour, on the other hand, describes the output response (logic function) of the IC chip to the specified combinations of input signals.

In order to absolutely minimize the risk of circuit malfunction, all the behavioural characteristics of IC chips, used in the circuit, must be tested. An IC must tester incorporating all the testing provisions, by necessity, be extremely fast and economically viable, if it is to be of any practical use. Besides, the design of such a tester is very complex and is beyond the perview of this dissertation.

A designer of a digital circuit must have detailed knowledge of digital electronics and of the capacities and capabilities of different ICs used in the circuit. A good designer takes care to ensure that, in so far as possible, the IC does not operate in a critical zone and that sufficient safety margin exists. Also, the production process of IC chips incorporates sufficient safeguards to guarantee very high overall reliability (95-98%).

Most irksome and at times, the most frequently encountered hazard is the spurious IC chip. Spurious chips are, therefore, responsible for major share of overall chip malfunctions. Such an IC chip can be easily spotted by functional testing. It can thus be seen that, provided sufficient care has been taken to ensure sufficient margin in parametric capabilities, an IC chip tested for correct functional behaviour, will function correctly in the circuit, in overwhelming majority of cases.

### 2.2 DETECTION OF LOGIC MALFUNCTION

Digital circuits are basically classified into combinational and sequential circuits. In combinational circuits, the circuit outputs depend entirely upon the present set of input vectors. In sequential circuits, the circuit outputs depend not only upon the present set of input vectors but also upon the past history of inputs. In either category,

a logic malfunction may be permanent or time varying. Permanent faults relate to faults caused by a particular line permanently stuck at zero (s-a-0) or stuck at one (s-a-1). Time varying or intermittent faults are caused by very close tolerances in the chip or due to general deterioration of components.

This basic differente leads to different approaches for developing fault detection test sets for combinational and sequential circuits. Without going into further details, it will suffice to say that in combinational circuits a minimal test set may be found by using only those input combinations for which the output function is different for correct and faulty circuit behaviour(2,3,4).

In development of test sets for sequential circuits, the emphasis is more on finding a suitable procedure for ensuring fault detection. Usually, the first step is to identify the current state of the circuit or to bring it to a known state and then apply test inputs in the sequence for which the output sequence is known.

Needless to say, the IC chips implementing combinational and sequential circuits will need accordingly specified testing procedures.

#### 2.3 IMPLEMENTATION OF TEST SETS

Having developed the test set for an IC, the problem is confined to developing means of applying the test inputs and observing the responses. Manual procedures are discarded since the time factor involved would render such a procedure useless for practical application. Microprocessor, with its extremely fast speed of operation, extremely low hardware requirement, flexibility of operation due to software facilities etc. is an automatic choice for most efficient implementation of test sets.

Microprocessor based IC testers may again be of two types, viz., dedicated testers and universal testers. Dedicated testers will require different hardware for different ICs and are, as such, suited for application in places where only few specific types of ICs are being used. In a laboratory already having a microprocessor based system, it will be very easy and inexpensive to design such a tester.

Universal IC tester, as the name suggests, can test different types of IC chips using the same hardware. The problems encountered in such a design are discussed in chapter 6. The hardware cost of such a tester will, definitely, be more than a dedicated IC tester, but with a common hardware, such a tester is very useful for testing a wide variety of ICs, e.g., in a store of ICs from where ICs may be distributed to different sections.

2--5

In both the IC testers, a similar testing procedure may be used. Test programmes for testing different ICs are stored in the non-erasible memory. The IC to be tested is inserted in the test socket. The programme may be executed directly by the user, after finding out the starting location of the test programme; or by pressing different keys provided on the tester in a particular sequence.

Once the test programme begins, the microprocessor continuously sends different test inputs to the chip and reads the chip outputs. These outputs are compared with the desired response through microprocessor software. In case the two do not tally, the IC is faulty. This may be indicated by switching on a RED LED or sounding a horn or displaying a fault message.

In case the two outputs tally, the microprocessor proceeds to impress subsequent test inputs sequentially till all are exhausted or a wrong output is obtained, whichever is earlier. In case all outputs tally, the IC is declared as good. This may be accomplished by switching ON a GREEN LED or by displaying a suitable message.

#### 2.4 DEVELOPMENT OF IC TESTER

In this dissertation, a dedicated IC tester has been developed. This IC tester makes use of the HIL-2961 microprocessor trainer. Initially, various test programmes were executed through HIL-2961 keyboard. The good status of an IC is indicated by a GREEN LED and the faulty status of an IC is indicated by a RED LED accompanied by a horn. Subsequent developments, including interfacing the HIL-2961 with a CRT terminal, are discussed in later chapters.

Implementing the test programme once and obtaining satisfactory results, does not, necessarily, mean absence of intermittent faults which are time varying. For this purpose, a facility has been provided to implement the test programme repeatedly. Generally, the test programme may be repeated 1000 times or so. However, at present, this facility has been restricted to repeatition of the test programme ten times. This number can be modified easily by changing the number loaded in the counter indicating number of repeat loops desired. Working on the same basis, reliability testing, using accelerated, destructive test procedure, can be incorporated. Key 5 on the HIL-2961 keyboard is programmed as the key for executing REPEAT instruction. To exit from the test programme, the user presses STOP key. Key 6 on the HIL-2961 keyboard is programmed to execute STOP instruction.

1.24

The programme for REPEAT and STOP keys was developed on the basis of keyboard management technique used by the HIL-2961 monitor. In addition, the IC tester programme uses DELB and HORN2 subroutines provided in the HIL-2961 monitor.

2.5 QUADRUPLE TWO INPUT NAND GATE IC 7400

7400 chip consists of four 2-input NAND gates. Its pin configuration is given in Appendix 'E'. The truth table for a two input NAND gate (Fig.2.1) is given in Table 2.1 for fault free operation.

FIG.2.1 : TWO INPUT TABLE 2.1 : TRUTH TABLE NAND GATE

2.6 MINIMAL TEST SET DEVELOPMENT FOR IC 7400

The two input NAND gate shown in Fig.2.1 has three lines (two input lines and one output line). Assuming single faults leads to a total of six possible faults of the nature of s-a-1 or s-a-0.

С

1

1

0

In order to arrive at a minimal test set, we shall consider each fault separately and determine the test vector which detects this fault. The minimal combination of all such test vectors will yield the minimal test set.

For a particular fault  $\mathcal{L}$ , vector  $(A,B)_{i}$  is a test vector iff the circuit yields different O/Ps for the circuit for healthy and faulty behaviour.

Therefore, for  $(A,B)_i$  to be a test vector for fault  $\mathcal{L}$ ,

$$C_i \oplus C_i^{\mathscr{L}} = 1$$

where  $\bigoplus$  denotes exclusive - OR,  $C_i$  and  $C_i^{\bigstar}$  are O/P values of healthy and faulty gate respectively, corresponding to input vector (A,B)<sub>i</sub>.

TABLE 2.2 Gives the test sets for individual faults.

| FAULT   | $T \frac{EST}{A}$ | VECTOR | С | c | c⊕ c <sup>≵</sup> |

|---------|-------------------|--------|---|---|-------------------|

| A.s-a-1 | 0                 | 1      | 1 | 0 | 1                 |

| A s-a-O | 1                 | 1      | 0 | 1 | 1                 |

| B s-a-1 | 1                 | 0      | 1 | 0 | 1                 |

| B s-a-0 | 1                 | 1      | 0 | 1 | 1                 |

| C s-a-1 | 1                 | 1      | 0 | 1 | 1                 |

| C s-a-0 | 0                 | 0      | 1 | 0 | 1                 |

| C s-a-0 | 0                 | 1      | 1 | 0 | 1                 |

| C s-a-0 | 1                 | 0      | 1 | 0 | 1                 |

|         |                   |        |   |   |                   |

TABLE 2.2 : TEST SETS FOR TWO INPUT NAND GATE

Complete test set is 01, 11, 10,11,11,00,01,10. The minimal test set, therefore, is 01,10,11.

01 tests faults A s-a-1, C s-a-0

10 tests faults B s-a-1, C s-a-0

11 tests faults A s-a-O, B s-a-O, C s-a-1

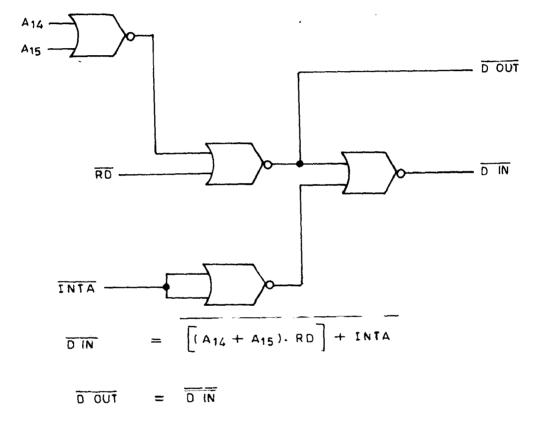

The flow chart implementing this test set in 7400 test programme is given in Fig.2.2.

#### 2.7 KEY DEBOUNCING

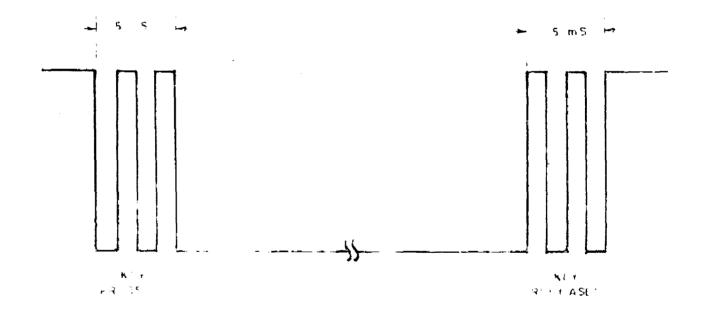

Every mechanical key is associated with a clatter whenever it is pressed or released. This results in intermittent ON and OFF signal generation for about 5 ms whenever a key is pressed or released. Typically, thesignal generated whenever a particular key is pressed or released, may be as shown in Fig.2.3. In order to correctly interpret the signal from a particular key, special attention must be paid to this characteristic. In this dissertation, a software debounce programme has been developed and usedfor key 6 and key 5.

Having executed the test programme once, the microprocessor waits for a REPEAT or STOP instruction. It constantly scans the keyboard. Whenever it receives a signal indicating that key 6 or key 5 has been pressed, it waits for 10 ms to ignore the clatter. It then again scans the keyboard

\*

•

to see if the key is still pressed and waits till the operator lifts his finger from the key. On receiving the indication that the key is released, the programme again waits for 10 ms to ignore the clatter associated with key release.

2.8 PROGRAMME FOR IC 7400 TEST

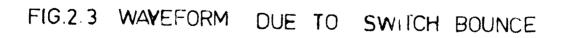

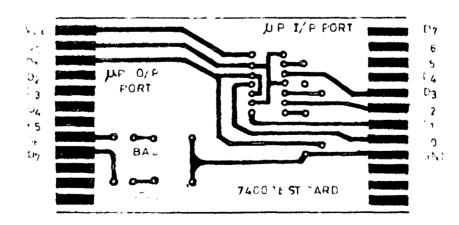

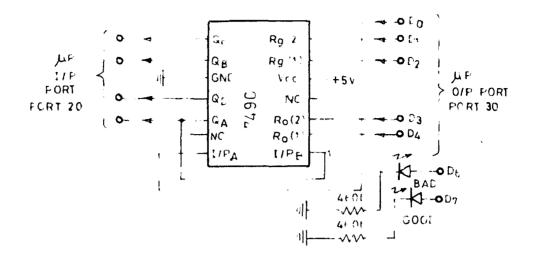

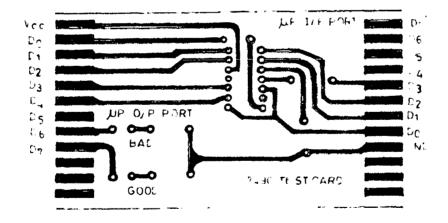

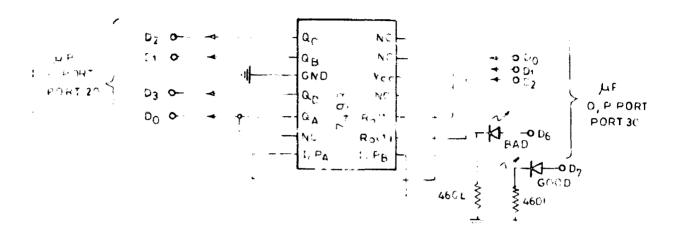

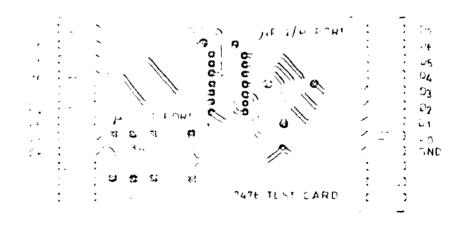

The programme for IC 7400 test through HIL-2961 is labelled as 'T074' and starts from location OCBOH in the ememory. Existing ports provided in HIL-2961 i.e., port 30 ( O/P port) and port 20 (/P port) are used for applying test I/Ps and reading chip O/Ps. Circuit connections for 7400 test card are shown in Fig.2.4 and the PCB layout is given in Fig.2.5. The test programme is given below:

| NAME OF  | SUBROUTINE  | T074 |      |

|----------|-------------|------|------|

| INPUTS   | NONE        |      |      |

| OUTPUTS  | SIGNALS FOR |      | HORN |

| CALLS    | DELB, HORN2 |      |      |

| DESTROYS |             |      |      |

DESCRIPTION TO74 CHECKS UP IC 7400 USING HIL 2961 KEYBOARD

| OCBO<br>OCBO | F5             | Т074 | PUSH       | PSW               | Save status                     |  |

|--------------|----------------|------|------------|-------------------|---------------------------------|--|

| OCB1         | 05             |      | PUSH       | В                 | Save BC                         |  |

| OCB2         | D5             |      | PUSH       | D                 | Save DE                         |  |

| 0СВ3<br>0СВ5 | 3E00<br>32FEOF |      | MVI<br>STA | A, OOH<br>RPTLP ] | Store repeat loop absent status |  |

FIG. 2.4 7400 TEST CARD CIRCUIT DIAGRAM

.

•

| OCB8                 | • • <b>-</b>             | START | 1 ef 7 Tr                |                       |                                                     |

|----------------------|--------------------------|-------|--------------------------|-----------------------|-----------------------------------------------------|

| OCB8<br>OCBA         | 3 EO 7<br>D3 30          |       | MV I<br>OUT              | A,07H<br>30H          | Apply test I/Ps(11)<br>to NAND gates                |

| OCBC                 | DB20                     |       | IN                       | 2011                  | Read chip O/Ps                                      |

| OCBE                 | EGOF                     |       | ANI                      | OFH                   | Mask unwanted bits                                  |

| 0C <b>C</b> 0        | C2270D                   |       | JNZ                      | FLIIND                | If chip O/Ps are not correct, branch                |

| 0CC3<br>0CC5         | 2E06<br>D330             |       | MV I<br>OUT              | A,06H<br>30H          | Apply test I/Ps (10) <sub>2</sub><br>to NAND gate   |

| 0007                 | DB20                     |       | IN                       | 20H                   | Read chip O/Ps                                      |

| 0009                 | E60F                     |       | ANI                      | OFH                   | Mask unwanted bits                                  |

| OCCB<br>OCCD         | FEOF<br>C2270D           |       | CPI<br>JNZ               | OFH<br>FLIND          | If chip O/Ps are not correct, branch                |

| 0CD0<br>0CD2         | 3 EO 5<br>D3 30          |       | MV I<br>OUT              | A,05H<br>30H          | Apply test I/Ps (01) <sub>2</sub> )<br>to NAND gate |

| OCD4                 | DB 20                    |       | IN                       | 20 H                  | Read chip O/Ps                                      |

| OCD6                 | E60F                     |       | ANI                      | OFH                   | Mask unwanted bits                                  |

| OCD8<br>OCDA         | FFOF<br>C2270D           |       | CPI<br>JNZ               | OFH<br>FLIND          | If chip O/Ps are not correct, branch                |

| OCDD<br>CCDF         | 3 E80<br>2:20            |       | MVI<br>OUT               | A, 80 H ]<br>%0 H     | Chip is good. Switch<br>on GOOD LED                 |

| OCE1<br>OCE4         | 010500<br>CD3004         |       | L <sub>X</sub> I<br>CALL | B,0005H<br>DELB       | Cause 5 ms delay                                    |

| OCE7<br>OCEA<br>OCEC | 3AFEOF<br>FE15<br>CA570D |       | LDA<br>CPI<br>JZ         | RPTLP<br>15H<br>RPTND | If repeat loop is present, brandh                   |

| OCEF<br>OCEF<br>OCF1 | A<br>3EEF<br>D328        | LPHA  | MVI<br>OUT               | A, EFH ]<br>28H       | Set scan port to EFH                                |

| OCF3                 | DB18                     |       | IN                       | 18H                   | Read key board I/P                                  |

| OCF5<br>OCF7<br>OCF9 | E607<br>FE05<br>CA390D   |       | ANI<br>CPI<br>JZ         | 07H<br>05H<br>ALPHA3  | If REPEAT key (key5)<br>is pressed, branch          |

•

| CFC<br>CEC<br>CFE | ALPHA1<br>3EEF<br>D328   | MVI<br>TUO               | EFH<br>28H            | Elase, set scan port<br>to EFH                                 |

|-------------------|--------------------------|--------------------------|-----------------------|----------------------------------------------------------------|

| DO 0              | DB18                     | IN                       | 18H                   | Read keyboard I/P                                              |

| D02<br>D04<br>D06 | E607<br>FE03<br>C2EFOC   | ANI<br>CPI<br>JN2        | 07H<br>03H<br>ALPHA   | If STOP key (key6) is<br>not prexsed, try for<br>another input |

| DO9<br>DOC        | 010A00<br>CD3004         | L <sub>X</sub> I<br>CALL | B, OOOAH<br>DELB      | Cause 10 ms delay                                              |

| DOF<br>OF<br>D11  | ALPHA2<br>3 EEF<br>D3 28 | MVI<br>OUT               | <b>A, E</b> FH<br>28H | Set scan port to EFH                                           |

| D13               | DB18                     | IN                       | 18H                   | Read key boand input                                           |

| D15<br>D17<br>D19 | E607<br>FE03<br>CAOFOD   | ANI<br>CPI<br>JZ         | O7H<br>O3H<br>ALPHA2  | If OFF key is pressed,<br>wait.                                |

| D1C               | CD3004                   | CALL                     | DELB                  | Else, wait for 10 ms                                           |

| D1F<br>D21        | 3E00<br>D330             | MVI<br>OUT               | A, OOH<br>30H         | Switch OFF LEDS                                                |

| 723               | D1                       | POP                      | D                     | Restore DE                                                     |

| D24               | C1                       | POP                      | В                     | Restore BC                                                     |

| D25               | F1                       | POP                      | PSW                   | Restore status                                                 |

| D26               | 76                       | HLT                      |                       |                                                                |

| D27<br>D27<br>D29 | FLTND<br>3E40<br>D330    | MVI<br>OUT               | A, 40H<br>30H         | Chip is bad. Switch on<br>'BAD' LED                            |

| 023<br>D2C        | C5<br>D5                 | PUSH<br>PUSH             | B<br>D                | Save BC<br>Save DE                                             |

| OD2D<br>OD2F<br>OD31         | 0620<br>1630<br>CD4704  |        | MVI<br>MVI<br>CALL | D, 20H<br>D, 30H<br>HORN 2 | Sound Horn                                                    |

|------------------------------|-------------------------|--------|--------------------|----------------------------|---------------------------------------------------------------|

| OD34                         | D1                      |        | POP                | D                          | Restore DE                                                    |

| OD35                         | C1                      |        | POP                | В                          | Restore BC                                                    |

| OD36                         | C3FCOC                  |        | JMP                | ALPHA1                     | Go back to programme to get next instruction.                 |

| OD39<br>OD39<br>OD3C         | 010A00<br>CD3004        | ALPHA3 | LXI<br>CALL        | B, OOOAH                   | Debounce beg <b>ins.</b><br>Cause 10 ms delay                 |

| OD3F<br>OD3F<br>OD41<br>OD43 | 3EEF<br>D328<br>DB18    | ALPHA4 | MVI<br>OUT<br>IN   | A, EFH<br>28H<br>18H       | Get an input from<br>keyboard                                 |

| 0D45<br>0D47<br>0D49         | E607<br>FE05<br>CA3FOD  |        | ANI<br>CPI<br>JZ   | 07H<br>05H<br>ALPHA4       | If REPEAT key <b>is</b> still pressed, check again            |

| OD4C                         | CD3004                  |        | CALL               | DELB                       | Key released. Cause<br>10 ms delay.Dobounce ends              |

| OD4F                         | 110A00                  |        | L <sub>X</sub> I   | D,OAH                      | Set up repeat loop counte                                     |

| 0D52<br>0D54                 | 3 <b>E1</b> 5<br>32EFOF |        | MVI<br>STA         | A, 15H<br>RPTLP            | Sct up repeat loop<br>present status                          |

| OD57<br>OD57<br>OD58         | 7B<br>FEOO              | RPTND  | MOV<br>CPI         | A, E<br>OOH                | Is the lower byte of counter exhausted?                       |

| OD5A                         | CA610D                  |        | JZ                 | RPT ND1                    | Yes-Branch                                                    |

| OD5D                         | 1B                      |        | DCX                | D                          | No-Decrement counter                                          |

| OD61<br>OD61<br>OD62         | 7A<br>F <b>e</b> 00     | RPTND1 | MOV<br>CP I        | A, D<br>OOH                | Lower byte of counter<br>is zero. Is upper byte<br>also zero? |

| OD64                 | CA6 BOD                      | JŻ           | RPTND2          | Yes-Branch                                                      |

|----------------------|------------------------------|--------------|-----------------|-----------------------------------------------------------------|

| OD67<br>OD68         | 1 <sup>B</sup><br>C3B80C     | DC X<br>JMP  | D<br>START      | No-Decrement counter<br>Repeat programme                        |

| OD6B<br>OD6B<br>OD6D | RPT ND2<br>3 EOO<br>3 2 FEOF | MV I<br>ST A | a, coh<br>Rptlp | Counter exhausted. Load<br>repeat Loop absent<br>statu <b>s</b> |

| 0 <b>D70</b>         | C3 BSOC                      | JMP          | START           | Repeat programme                                                |

# PROGRAMME TABLE

.

\*

| OFFE | RPTLP | EQU | OFFEH | Location for repeat |

|------|-------|-----|-------|---------------------|

|      |       |     |       | loop status.        |

# CHAPTER-3

## INTERFACING HIL 2961 WITH CRT TERMINAL

INTRODUCTION: NEED FOR A CRT TERMINAL

that has been mentioned in Chapter 1/the visual display in the -2961 is limited to six digit, seven segment LEDs. This )ses a severe handicap on the user efficiency in communiing with the trainer. For example, having entered a gramme, checking for its correctness to ensure that the gramme has been entered correctly, the user has to examine address one by one. Besides being extremely slow and lous, this method is liable to cause repeated mistakes cially when checking up a long programme. Again, while igging a programme, the user may insert break points in programme or execute it instruction by instruction. The so obtained has to be noted down by the user and since Its of various instructions are not available directly, akes very long to spot bugs in the programme.

T terminal is an ideal solution to these problems. Due he semi-permanent display provided on the CRT screen, a e amount of data is available to the user. With a suitable tor, the user can get the entire programme or large blocks t on the screen, contents of various registers can be layed after execution of each instruction and many such rammes can be developed to enhance user efficiency. Interfacing a CRT terminal is, therefore, the first logical step in system development after the first stage of communicating directly with the microprocessor through a key board.

Besides, the process of developing the hardware inteface and software programmes for the monitor permits the user an intimate interaction with the numerous aspects of microprocessor functioning, thereby resulting in better understanding of the microprocessor's software potential and hardware requisites.

In the context of development of IC tester, the CRT terminal can be used effectively to simplify the testing procedure. With various messages printed on the screen in response to programmed keys, any person can use the IC tester without getting involved with unnecessary details.

Obviously, it is not economically viable to produce an IC tester with a CRT terminal. However, on the basis of this work a similar approach can be used to display different messages on a smaller display using 7 segment LEDs.

Nevertheless, the IC tester developed is very useful for use in a laboratory where a CRT terminal may be already available, thereby not requiring additional investment.

3.2 INTERACTIVE DISPLAY TERMINAL ADM-3A (5)

In very general sense, CRT terminal is a device which generates unique ASCII codes in response to different keys being pressed

on its keyboard. This code is then transmitted serially to the interfaced computer. It can also accept data through the connected computer serially, decode it and display the character on the screen. For the purpose of this dissertation, an 'Interactive Display Terminal ADM-3A', marketed by Lear Siegler, Inc., was provided by the Computer Centre.

ADM-3A has a 30 cm rectangular screen which can display 24 lines each having a maximum of 80 characters. It's keyboard layout is identical to that of a standard type-writer and has 59 keys. It can communicate over a large range of battd rates from 75 to 19200, switch selectable. It permits both RS-232C(6.7) and 20 mA current loop interface and has many other features described in Appendix 'D'.

For interfacing ADM-3A with HIL-2961 following features were selected.

- 1. RS-232C interface

- 2. Full Duplex mode

- 3. 300 baud rate

- 4. 7 bit data word length

- 5. Bit 8 forced to zero

- 6. Parity inhibited

- 7. 2 stop bits

- 8. AUTO NL mode

- 9. Upper case alphabetic characters' option.

## 3.3 DEVELOPMENT OF INTERFACE

Development of an interface between the CRT terminal and the microcomputer has the following two main aspects.

- 1. Hardware interface: It must satisfy the following requirements:

- (a) Change TTL level signals from the microcomputer to RS-232Clevel signals for the CRT and vice versa,

- (b) Convert parallel data from the microcomputer into serial form for transmission to the CRT terminal, and similarly convert serial data from the CRT into parallel 8-bit characters for the microcomputer; and

- (c) To attach relevant framing information to each character received from the microcomputer for transmission to the CRT terminal and to remove this information before transmitting a character from CRT terminal to the microcomputer.

It may be noted that the hardware interface may be considerably simplified by using the SID and SOD lines of the 8085A. The microcomputer can then communicate serially with the CRT terminal without necessiating a serial to parallel conversion and vice-versa. In case of HIL 2961, the SOD line is connected permanently to a speaker and, therefore, not available unless this connection is cut. Another factor against the use of the SID and SCD lines is the time wasted by the microcomputer in sending and receiving data serially on these lines. This implies underutilization of the microprocessor efficiency.

2. Software interface: The functions outlined in 1(b) and (c) are fulfilled by the 82514 USART. The 82514 requires a software programme to enable its function in the desired manner. The software interface is also required for programming different keys on the CRT terminal keyboard for executing different commands on the microcomputer through the CRT terminal.

The hardware interface is akin toachandshake between two strangers and the soft-ware interface is like a common language the two must speak for an intelligent information exchange.

3.4 HARDWARE INTERFACE

The hardware interface development consisted of developing following units:

1. +5V, +12V and -10V power supply.

2. Baud Rate Generator

3. RS-232C and 8251A USART interface

Each of these will be discussed in subsequent sections.

## 3.5 POWER SUPPLY

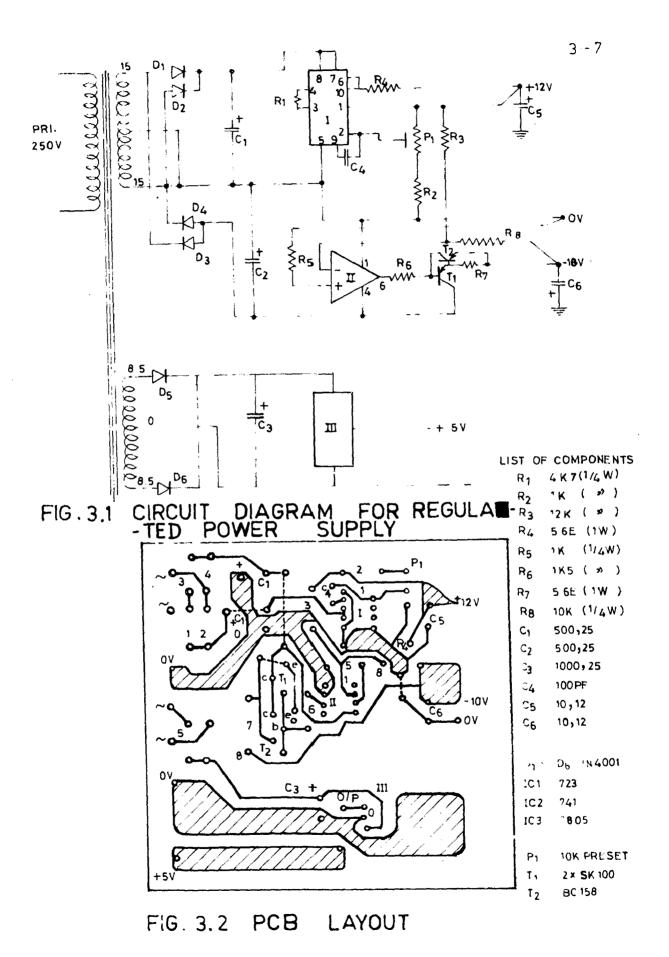

The power supply is used for providing +5V supply to different ICs and +12V and -12V supplies are used for different transisinterface. tors used in the RS-232C/ Since the hardware circuitry is designed to operate correctly at the specified voltages, there is an obvious need for a regulated power supply. Regulated +12V and -10V supplies were obtained using ICs 723 and 741. The +5V regulated supply was obtained using IC 7805. The circuit diagram for the power supply is shown in Fig.3.1 and the PCB layout is shown in Fig.3.2.

## 3.6 BAUD RATE GENERATOR

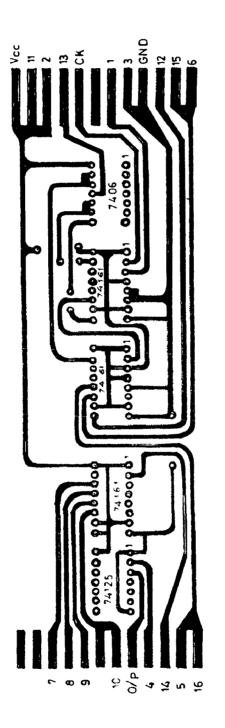

Using the 2MHz clock available at CLK OUT terminal (Pin 37) of the 8085A CPU (available at Pin 28 of the extension connector of HIL 2961), a variable baud rate generator has been developed. This can provide switch selectable baud rates of 19200, 9600, 4800, 2400, 1760 and 1200. When used in conjunction with the 'baud rate factor' facility provided in the it INTEL 8251A USART/can ehable the user to operate the CRT terminal at different baud rates. In addition, using the 1760 baud rate and a band rate factor of 16 in the 8251A, an interface for interfacing the HIL 2961 with a tele-typewriter can also be developed.

IC 74161 is the basic chip used for generating different baud rates. It is a synchronous, presettable, 4 bit binary counter. The synchronous feature is useful for high frequency

operation and the pre-settable feature reduces the external hardware to a bare minimum. Thepin configuration and other details of 74161 are given in Appendix 'E'.

3.6.1 Design Calculations

Original frequency : 2MHz Frequencies desired : 19200, 9600, 4800, 2400, 1760, 1200 Dividing factors : As per table 3.1 <u>TABLE 3.1 : Dividing Factor Calculations</u> Frequencies Dividing required. factors 19200 13,8

| 19200        | 13,8    |

|--------------|---------|

| 9600         | 13,16   |

| 48 <b>00</b> | 13,16,2 |

| 2400         | 13,16,4 |

| 1760         | 14,16,5 |

| 1200         | 13,16,8 |

|              |         |

Three 74161s are used. The first one is used as  $\div$  13 or  $\div$  14 counter (first state), the second one is used as  $\div$  2,  $\div$  4,  $\div$  5 or  $\div$  8 counter (third stage), the third one is used as  $\div$  9 or  $\div$  16 counter (second stage).  $\div$  13,  $\div$  14 and  $\div$  5 counts are obtained by programming the counter. Appropriate inputs are placed at terminals 3,4,5 and 6, and the counter begins counting sequence from states determined by the particular combination of inputs.

### 3.5 POWER SUPPLY

The power supply is used for providing +5V supply to different ICs and +12V and -12V supplies are used for different transisinterface. tors used in the RS-232C/ Since the hardware circuitry is designed to operate correctly at the specified voltages, there is an obvious need for a regulated power supply. Regulated +12V and -10V supplies were obtained using ICs 723 and 741. The +5V regulated supply was obtained using IC 7805. The circuit diagram for the power supply is shown in Fig.3.1 and the PCB layout is shown in Fig.3.2.

### 3.6 BAUD RATE GENERATOR

Using the 2MHz clock available at CLK OUT terminal (Pin 37) of the 8085A CPU (available at Pin 28 of the extension connector of HIL 2961), a variable baud rate generator has been developed. This can provide switch selectable baud rates of 19200, 9600, 4800, 2400, 1760 and 1200. When used in conjunction with the 'baud rate factor' facility provided in the it INTEL 8251A USART/can ehable the user to operate the CRT terminal at different baud rates. In addition, using the 1760 baud rate and a band rate factor of 16 in the 8251A, an interface for interfacing the HIL 2961 with a tele-typewriter can also be developed.

IC 74161 is the basic chip used for generating different baud rates. It is a synchronous, presettable, 4 bit binary counter. The synchronous feature is useful for high frequency

operation and the pre-settable feature reduces the external hardware to a bare minimum. Thepin configuration and other details of 74161 are given in Appendix 'E'.

3.6.1 Design Calculations

Original frequency : 2MHz Frequencies desired : 19200, 9600, 4800, 2400, 1760, 1200 Dividing factors : As per table 3.1 TABLE 3.1 : Dividing Factor Calculations Frequencies Dividing required. factors 19200 13,8 9600 13,16 4800 13.16.2 2400 .13,16,4 1760 14,16,5 1200 13,16,8

Three 74161s are used. The first one is used as  $\div$  13 or  $\div$  14 counter (first state), the second one is used as  $\div$  2,  $\div$  4,  $\div$  5 or  $\div$  8 counter (third stage), the third one is used as  $\div$  9 or  $\div$  16 counter (second stage).  $\div$  13,  $\div$  14 and  $\div$  5 counts are obtained by programming the counter. Appropriate inputs are placed at terminals 3,4,5 and 6, and the counter begins counting sequence from states determined by the particular combination of inputs. The circuit diagram for the baud rate generator PCB is shown in Fig.3.3. In order to provide a buffered output, a 74125 buffer has been used. The PCB layout is shown in Fig.3.4. In order to make the baud rate generator an independent unit, separate power supply has been provided for it. The regulated +5V supply uses a 7805IC.

3.6.2 Operating the Baud Rate Generator

The front panel of the baud rate generator has two select switches. Right hand side selector switch labelled 'MASTER SELECT' selects either 1760 or the group of other baud rates. For individual baud rates, the left select switch labelled 'RATE SELECT' is then used. The recommended operating procedure is as under:

- Before connecting the unit to power supply, ensure that both the select switches are in OFF position and the power on switch is OFF.

- 2. Select appropriate switch positions for the desired baud rate.

- 3. Connect the CLK OUT terminal of 8085A to the terminal marked I/P on the front pannel. Connect the Ground terminal to terminal marked GND.

BAUD RATE GENERATOR CIRCUIT DIAGRAM d/0 - GND - Vc c U U A Þ · 4 . [ , [; , ]]] · · 74 '6' \*; ]; \_\_\_\_\_ 4 · · · + · J CUMITENTS Γ FIG. 3.3 <u>\_</u> Ξ ہم (م) 60 •] 2 2 1 - 3 , 12 - 13 , 14 - C 16 , 4 - 17 - 1 وَي 1 4 73 5 8017 ' 510171 " # 0121 201. 1752 1270 " J 470 15 , J 470 9 9 J.J. F а. 12. т WITE CONNETTS ł 1 5 OR 116 TC 2, 12 TO " , 14 TO 15 1, "2 TOM 9 14 TOM 12: 3 ļ H N 1 \* \* \* 1 • • • • ++ 1 E1 + HO 71 + -هې مړ ~ I **b** - -4 . EAUD RATES 1 2 | | 24.0C 12.0C 00261 1800 . ••• - d/:

3 1'

- 4. Connect 230V supply and switch ON the power ON switch.

- 5. Switch on the trainer to activate the 2MHz clock.

- 6. The desired band rate is available at terminal marked O/P.

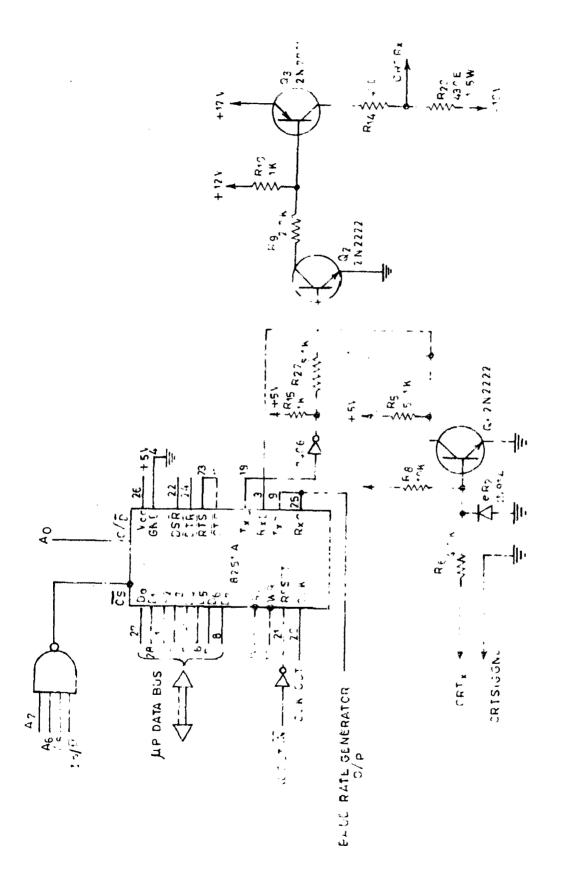

3.7 RS-232C AND 8251A USART INTERFACE (8)

ADM-3A offers two possible interfaces viz., RS-232C and 20 mA current loop. In this dissertation RS-232C option was chosen. RS-232C uses negative true logic for its operation. -15V to -5V is recognised as logic 1 and +5V to +15V is recognised as logic 0 level. TTL levels used by HIL 2961, on the other hand, use positive true logic, recognising 2.4 V to 5.25V as logic 1 and 0 V to .8V as logic 0 (9).

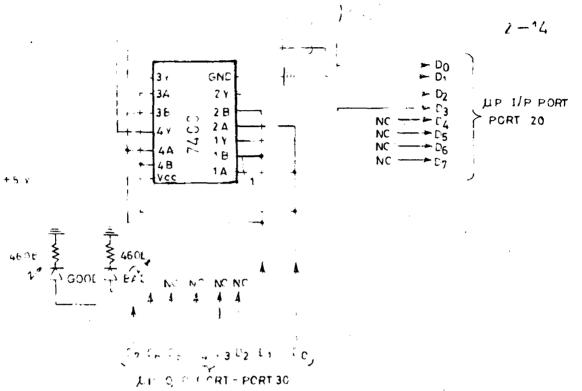

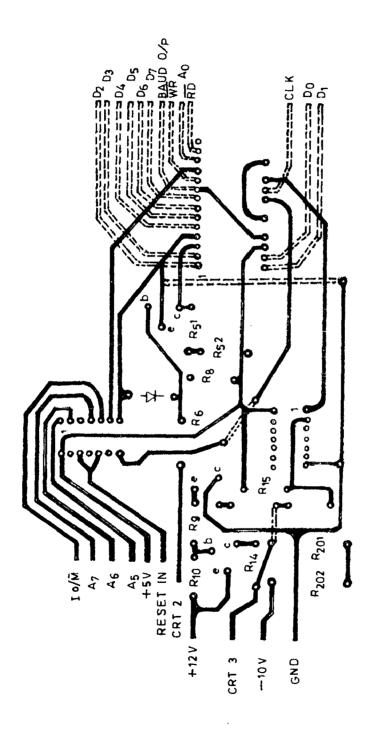

'RS 232C and 8251A USART interface' is the unit which performs the functions of a hardware interface outlined in section 3.3. Power supply and the baud rate generator are used as supporting units to make this unit functional. The circuit diagram of this interface is shown in Fig.3.5 and the PCB layout is given in Fig.3.6.

The ADM-3A terminal operates in asynchronous format, the 8251A can operate both in the synchronous and the asynchronous format. In order to understand the microcomputer to CRT terminal interface, it is necessary to understand the techniques of serial data transmission. Appendix 'F' provides a brief description of communication formats with special emphasis on asynchronous format.

8251 A USART INTERFACE RS 232 C AND FIG. 3.5

3.7.1 INTEL 8251A USART

INTEL'S 8251A 'Universal Synchronous Asynchronous Receiver Transmitter' is an IC chip that facilitates data transfer between a parallel and serial device. The functions of a USART are as follows:

- Receive parallel data from the microprocessor, convert it into serial form and encode it as per the required format.

- 2. Transmit this data to the I/O device.

- 3. Receive serial data from the I/O device, decode it, convert it into parallel data and send it to the microprocessor.

- 4. Generate appropriate control signals to inform the microprocessor that it is ready to receive a word from it or that it already has a word yet to be transmitted to theI/O device, to inform the microprocessor that it has a data word for it from the I/O device. It also checks the data word for correct format and raises appro-

priate signals for correctness/fault. The detailed description of 8251A is given in Appendix 'G'. The operation of the 8251A in the interface developed is as under. Pins  $D_0$ - $D_7$  (Pin Nos 27,28,1,2,5,6,7,8) are connected to the microprocessor data bus. TXD (pin 19) is used for either loading the mode and control instruction, or for reading the Status Register. The RTS (Pin 23) and the CTS (Pin 17) terminals are shorted together to enable data transmission. Other pins of the 8251A are not used.

Once all external connections are made with the interface unit, and the power is switched ON on all supporting units, the interface becames functional. However, before the interface can commence operation, the 8251A must be programmed. This willbe discussed in the software development described in Chapter 4. 3.7.1 INTEL 8251A USART

INTEL'S 8251A 'Universal Synchronous Asynchronous Receiver Transmitter' is an IC chip that facilitates data transfer between a parallel and serial device. The functions of a USART are as follows:

- Receive parallel data from the microprocessor, convert it into serial form and encode it as per the required format.

- 2. Transmit this data to the I/O device.

- 3. Receive serial data from the I/O device, decode it, convert it into parallel data and send it to the microprocessor.

- 4. Generate appropriate control signals to inform the microprocessor that it is ready to receive a word from it or that it already has a word yet to be transmitted to theI/O device, to inform the microprocessor that it has a data word for it from the I/O device. It also checks the data word for correct format and raises appro-

priate signals for correctness/fault. The detailed description of 8251A is given in Appendix 'G'. The operation of the 8251A in the interface developed is as under. Pins  $D_0$ - $D_7$  (Pin Nos 27,28,1,2,5,6,7,8) are connected to the microprocessor data bus. TXD (pin 19) is

connected to 'Receive Data' pin (pin 3) of ADM-3A. RXD (pin 3) is connected to 'Transmit Data' pin (pin 2) of the ADM-3A. Connections from 8251A to ADM-3A carry the necessary circuitry for changing the voltage levels appropriately to TTL level or RS-232C. TXC (Pin 9) and RXC(Pin 25) are shorted and connected to the output of the band rate generator. CLK (Pin 20) is connected to CLK OUT terminal of 8085A which is of 2MHz frequency. RD, WR, Vcc and GND are appropriately connected. RESET (Pin 21) is connected to the RESET IN terminal of 8085A through an inverter. In the present design, the 8251A can be addressed by any port number between EO to FF. Accordingly, the CS (Pin 11) terminal is connected to the output of a four input NAND gate having 8085 signals A7, A6, A5 and IO/M as its inputs. The other select terminal  $C/\overline{D}$  (Pin 12) is connected directly to address line  $A_{\bigcirc}$  of the microprocessor. In this dissertation, the 8251A is addressed either as EO or E1. Addressing it as port EO enables data transfer between USART and the microprocessor, while the E1 address is

used for either loading the mode and control instruction, or for reading the Status Register. The RTS (Pin 23) and the CTS (Pin 17) terminals are shorted together to enable data transmission. Other pins of the 8251A are not used.

Once all external connections are made with the interface unit, and the power is switched ON on all supporting units, the interface becames functional. However, before the interface can commence operation, the 8251A must be programmed. This willbe discussed in the software development described in Chapter 4.

### CHAPTER-4

### MONITOR FOR THE CRT TERMINAL (10)

#### 4.1 INTRODUCTION

As discussed in Section 3.3, a software interface is necessary for integelligent interchange of information between the microprocessor and the CRT terminal. This software performs two distinct functions:

- Programming the 8251A : For proper working, the USART must be programmed correctly before commencing data transfer. This involves loading the appropriate Thode word. and control word into the 8251A control register.

- 2. Programming ADM-3A keys for specific tasks: This involves developing programmes for identifying different keys and executing commands represented by them.

Accordingly, different programmes have been developed. All these programmes together constitute the monitor for the IC tester. Different programmes in the monitor developed in this dissertation shall be discussed in subsequent sections. The complete monitor listing is available at the end of this Chapter.

### 4.2 SIGN ON MESSAGE PROGRAMME

Once the hardware interface has been activated, the execution of this programme results in the initial sign on message, 'IC. TESTER I READY' to be displayed on the ADM-3A screen. The Control word used is' CEH, i.e., (11001110)2. This implies that the data communication is in asynchronous format, Character length is 8 bits, 2STOP bits will be added to each character, parity is not being used and the baud rate factor is 1/16. Since the ADM-3A band rate has been selected as 300, therefore the band rate generator output, connected to TxC & RxC terminals of 8251A, must be selected as 4800 band. The mode word used is (27)<sub>H</sub>. This implies that RTS will be held LOW, Receive and Transmit functions are enabled and the DTR (Data Terminal Ready) signal is enabled. Since RTS is connected directly to CTS, CTS will also be forced LOW and this will enable data transmission. This programme labelled 'SIGNON' resides in memory location O800H to O813H in the monitor.

# 4.3 GET COMMAND PROGRAMME

After displaying the initial sign - on message, the monitor requests the user for a command by displaying a prompt character "." This involves polled data transfer. The status register of the 8251A is repeatedly checked to see if any character has been received by the receiver, i.e., to check if a key has been pressed on the key board. Once a key is pressed on the key board, the programme compares the code generated against the list of valid commands for the monitor. In case the code signifies one of the valid commands, the control is passed to the concerned programme for further execution. Otherwise, an asterik (\*) signifying erroneous command is displayed on the terminal screen and the monitor once again waits for a valid commandfrom the user. This programme is labelled 'GETCMD' and resides in memory locations O816H to O83DH in the monitor.

4.4 FUNCTIONAL COMMANDS

The programmes discussed in Section 4.2 and 4.3 are automatically executed when the control is transferred to the ADM-3A keyboard from the HIL 2961 keyboard by executing the programme from O800H. After the control is transferred to the ADM-3A keyboard, the HIL 2961 can regain the control at any time by pressing the RESET key on HIL-2961 keyboard.

Three functional commands have been provided in the IC tester monitor :

- 1. TRY command

- 2. LIST command

- 3. EXECUTE command

Function of these commands shall be explained individually later in this chapter. The monitor has been so programmed that each command must be terminated by a CARRIAGE RETURN. 177/60

A.C.S. 13. 14.14 14

Any other character used for terminating the command shall make the command invalid. This gives the user the option of abondoning a command at any stage before the RETURN key is pressed.

## 4.5 TRY COMMAND

This command is represented by key T on the ADM-3A key board. On pressing T, the monitor responds by displaying ICNO: . The user should now type the number of the IC. The numbers will be displayed on screen. The monitor recognises four hexadecimal digits as valid number of digits. If less than four digits have been typed, the monitor will wait for the remaining If more than four digits digits and initiate no other action. are typed, the monitor will cause the error character to be displayed and revert to GET CMD programme. The monitor recognises T command as a valid command only for the 74 series of TTL. Typing any other number in the first two digits results in error character display. Every time an error character is displayed the monitor jumps to the GET CMD programme, abondoning whichever command it was receiving. With small changes, T command can be used for other IC series also. Once all the four digits have been typed, the command must In case the IC tester be terminated by the RETURN key. has a software programme for testing the IC mentioned, it sends the following message:

AVAILABLE

LOCATION :

The memory location, at which the programme for testing the IC in question begins, shall be displayed in front of LOCATION:

In case the IC tester does not have a software programme for testing the IC, following message will be displayed:

#### NOT AVAILABLE

In both the cases, after displaying the message, the monitor shall revert to the GET CMD programme. The TRY command programme is labelled as TRY and resides in memory locations O88AH to O89AH in the monitor.

## 4.6 LIST COMMAND

This command is represented by key L on the ADM-3A key. Like other commands, this command also must be terminated by RETURN. The complete command is as follows :

#### L RET

This causes the monitor to list all the ICs for which a diagnostic programme is available. List command is labelled LIST and resides in memory location 0947H to 095DH in the monitor.

# 4.7 EXECUTE (GO) COMMAND

This command is represented by key G on the ADM-3A key board. A valid GO command consists of typing G followed by four valid hexa-decimal digits and terminated by the RETURN key. In case more than four hexa decimal digits are typed, the monitor recognises only the last four digits as the starting address of the programme to be executed. Once a valid command is received, the address typed in bythe user is loaded in the programme counter of the µP and control is transferred to the programme. After execution of the programme, the control is transferred back to the monitor which goes back to the 'GETCMD' programme. The programme for EXECUTE command is labelled as GCMD and it resides in memory location 095EH to 097CH in the monitor.

## 4.8 SUB-ROUTINES FOR PROGRAMMES

Many sub-routines like CI, CO, ERROR, GETHX etc. are frequently called by various programmes listed in previous sections. These programmes can be understood by studying the comment field provided alongwith the programme in the monitor listing.

# 4.9 MONITOR LISTING

Complete monitor listing is given in Table 4.1. First column gives the first memory location in hexa-decimal code for the corresponding instruction, the second one gives the content(s) of memory location (s) for the instruction in hexa-decimal, the third column carries the label accorded to the instruction, if any, fourth column specifies the mnemonic for the instructions. Operands taking part in the instruction are specified in the fifth column and the sixth column represents the comment field. A brief description of the programme is given at the beginning of each programme.

## TABLE 4.1 : MONITOR LISTING

1000

-----

SIGNON PROGRAMME

| NAME              | SIGNON          |               |        |       |   |

|-------------------|-----------------|---------------|--------|-------|---|

| INPUTS<br>OUTPUTS | NONE<br>SIGN ON | MESSAGE 'I.C. | TESTER | READY | ł |

|                   |                 | ON SCREEN     |        |       |   |

## CALLS CO DESTROYS A, B, C, H, L, F/Fs

DESCRIPTION SIGN ON message is displayed on screen. The USART is assumed to come up in RESET position (This will be taken care of by the hardware). Once the USART has been initialisted, subsequent entry for printing the SIGN ON message and for transfer control to ADM-3A from HIL 2%1 keyboard must be made at location 0808H.

| )800         | SIGNON       |            |                 |                                                        |

|--------------|--------------|------------|-----------------|--------------------------------------------------------|

| )800<br>)802 | 3ECE<br>D3E1 | MVI<br>OUT | A, MODE<br>CNTL | Output mode word to<br>USART control port.             |

| 1804<br>1806 | 3E27<br>D3E1 | MVI<br>OUT | A, CMD<br>CNTL  | Output command word to<br>USART Control port.          |

| 808          | SIGN1        |            |                 | Restart point                                          |

| 808          | 21000F       | ΓXΙ        | H,MSG           | Load memory pointer with<br>address of SIGN ON message |

| 80 <b>B</b>  | 0614         | MVI        | B,LMSG          | Load number of character<br>in SIGN ON message in B    |

| CO8          | SIGN05       |            |                 |                                                        |

| 80D          | 4E           | MOV        | С,М             | Get the character in C.                                |

| 80E          | CD6408       | CALL       | CO              | Output character to screen                             |

| 811          | 23           | INX        | Н               | Move memory pointer<br>to next character               |

| 812          | 05           | DCR        | ·B              | Reduce number of characters to be output by 1.         |

| 813          | C20D08       | JNZ        | SIGN05          | Repeat if all characters not displayed.                |

## GET COMMAND PROGRAMME

| NAME<br>INPUTS | GETCMD<br>NONE |                        |    |        |

|----------------|----------------|------------------------|----|--------|

| OUTPUTS        |                | CHARACTER'.' DISPLAYED | ON | SCREEN |

CALLS ECHO, CI, ERROR DESTROYS A, B, C, H, L, F/Fs