# INTEL 8086 MICROPROCESSOR BASED DIGITAL FILTER REALIZATION

# A DISSERTATION

submitted in partial fulfilment of the requirements for the award of the Degree

of

# MASTER OF ENGINEERING

in

ELECTRICAL ENGINEERING (System Engineering & Operational Research)

SAROJ AMBARDAR

by

DEPARTMENT OF ELECTRICAL ENGINEERING UNIVERSITY OF ROORKEE ROORKEE U.P. (INDIA) August, 1982

# CERTIFICATE

Certified that the dissertation entitled "INTEL 8086 MICROPROCESSOR BASED DIGITAL FILTER REALIZATION" which is being submitted by Ms Saroj Ambardar in partial fulfilment for the award of the degree of MASTER OF ENGINEERING in ELECTRICAL ENGINEERING (System Engineering & Operational Research) of the University of Roorkee, Roorkee, is a record of student's own work carried out by her under my supervision and guidance. The matter embodied in this dissertation has not been submitted for the award of any other degree or diploma.

This is further to certify that she has worked for a period of about 7 months from Jan. 1982 to August 1982 for preparing this dissertation at this University.

asan 14ai 1982

(M. K. VASANTA) Reader Electrical Engineering Department University of Roorkee Dated August 16, 1982 Roorkee

(i)

# ACKNOWLEDGEMENTS

I wish to express my indebtedness and grateful thanks to Shri M. K. Vasanta, of the Department of Electrical Engineering for the invaluable guidance provided by him in carrying out the work contained in these pages. His guidance has been a constant source of encouragement and inspiration throughout the course of this study.

I also thank all those who helped me directly or indirectly in preparing this dissertation.

Saroje Ambardar

(ii)

(SAROJ AMBARDAR)

(iii)

### ABSTRACT

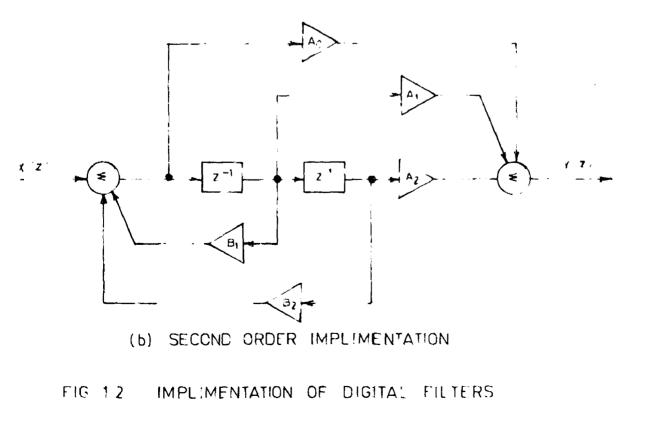

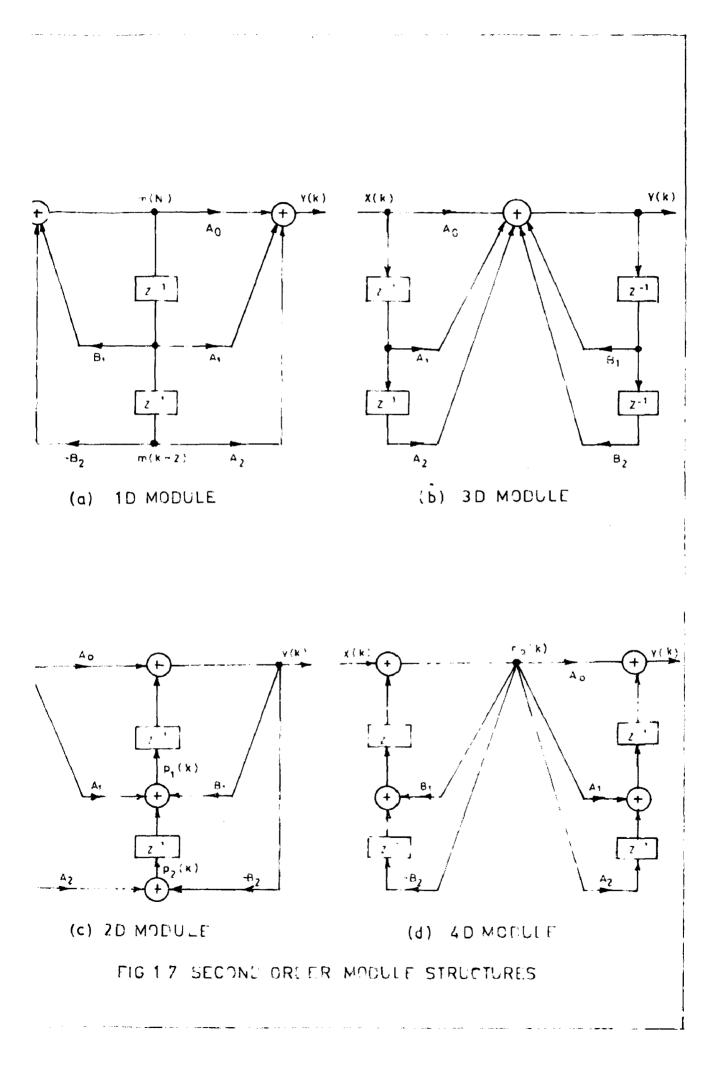

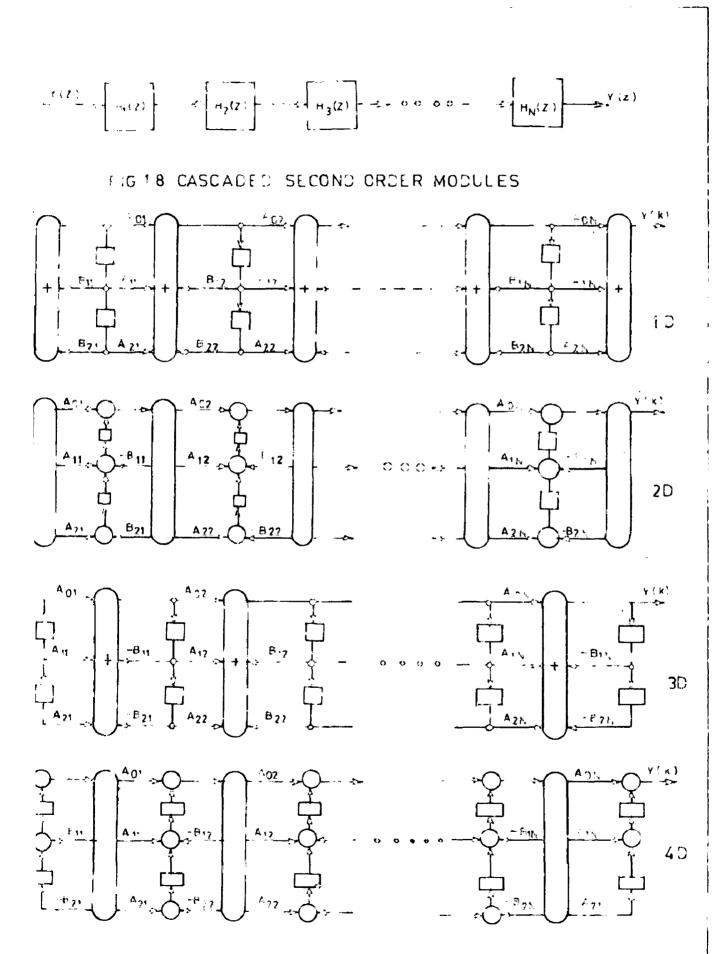

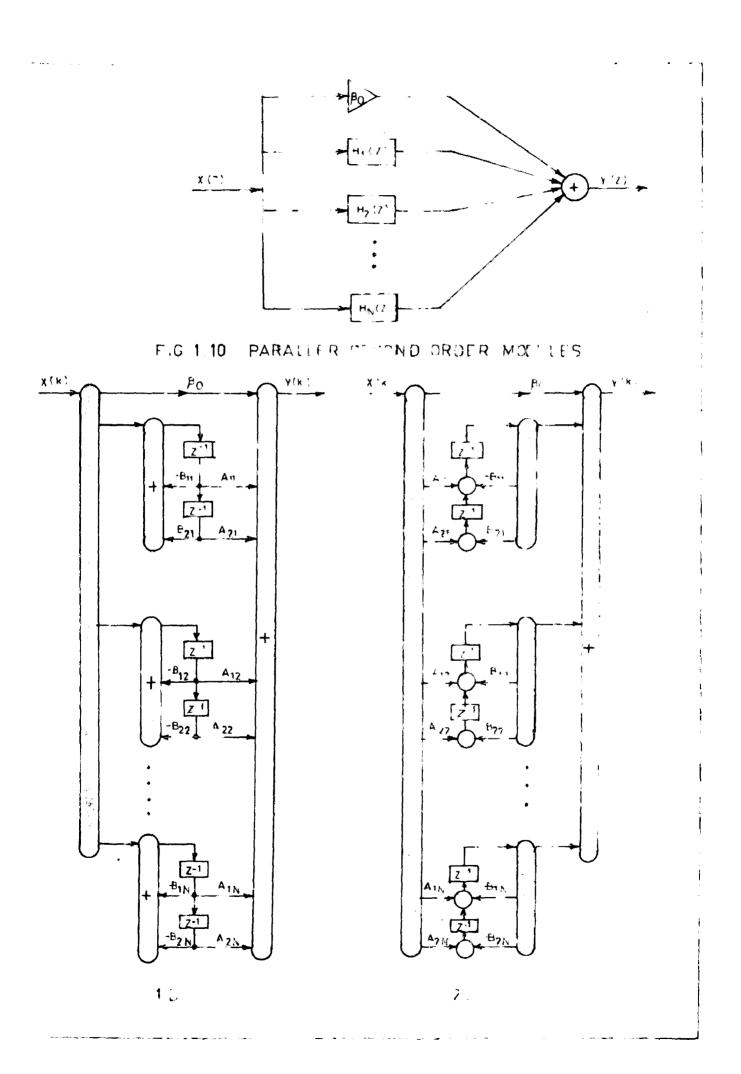

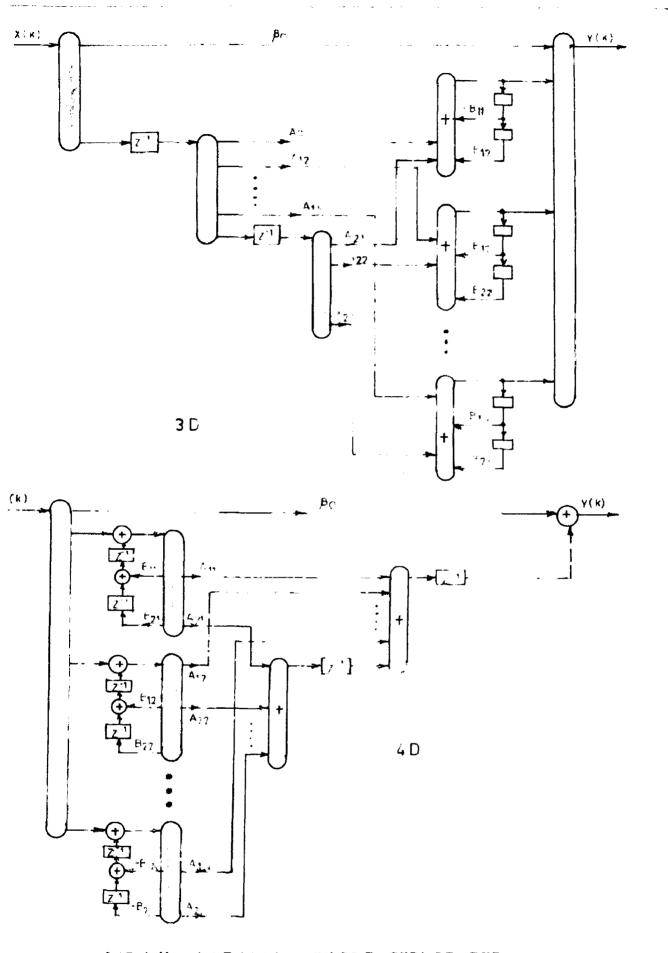

Digital filtering is a major subdivision of Digital signal processing. The practical realizations of a Digital filter have been discussed in this dissertation. To avoid coefficient sensitivity problems, the Z-Transfer function of a Digital filter is implemented as a cascaded or parallel combination of second order modules. Each module in itself can be one of the four Direct structures.

The significant break-through in the area of IC technology have opened up new options for the implementation of Digital filters. The present day research is centred around the microprocessor based design of a Digital filter. Digital filters are now implemented making use of 16-bit word length microprocessors. Intel 8086 has been considered in this dissertation. The Assembly language of 3086 is used to implement all the Digital filter modules. The software programs are given for K'th order Digital filter using N second order modules in cascade. It has also been shown that the same subroutines developed for second order modules can be used for parallel structure implementation.

# CONTENTS

| Chapter |      |                        |       |                                |         |       | Page   | No. |

|---------|------|------------------------|-------|--------------------------------|---------|-------|--------|-----|

| 0       | INTR | ODUCTIC                | N     | • • •                          |         | • • • | 1 –    | 6   |

|         | 0.1  | Histor                 | ical  | Introduction                   |         | • • • | 1      |     |

|         | 0.2  | Outlin                 | e of  | Work                           |         | • • • | 5      |     |

| I .     |      | SFER FU<br>DIGITA      |       | ON AND REALIZ.<br>LTER         | ATIONS  | •••   | 7 -    | 17  |

|         | 1.1  | Introd                 | ucti  | on                             |         | •••   | 7      |     |

|         | 1.2  | Z-Tran                 | sfer  | Function                       |         | • • • | 7      |     |

|         | 1.3  | Filter                 | Rea   | lization Tech                  | niques  | • • • | 10     |     |

|         |      | 1.3-1                  | Dir   | ect form Real:                 | ization | 1     | 10     |     |

|         |      | 1.3-2                  | Cas   | cade form Real                 | lizatio | n     | 14     |     |

|         |      | 1.3-3                  | Par   | allel form Re                  | alizat  | Lon   | 16     |     |

|         | 1.4  | Summar                 | У     |                                |         | • • • | 17     |     |

| ĨĨ      |      | ENT FEA<br>OPROCES     |       | S OF INTEL 80                  | 86      | • • • | 18 -   | 42  |

|         | 2.1  | Introd                 | lucti | on                             |         | • • • | 18     |     |

|         | 2.2  | <b>Salie</b> n<br>8086 | nt Fe | atures of Mic                  | roproc  | essor | · 18   |     |

|         |      | 2.2-1                  | Fun   | ctional Pin D                  | escrip  | tion  | 19     |     |

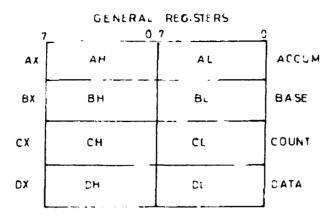

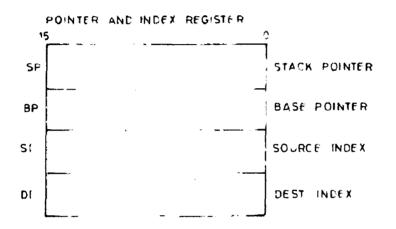

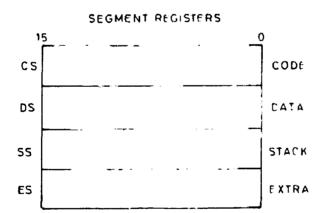

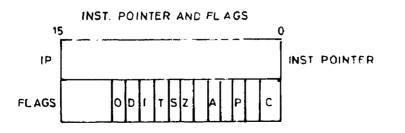

|         |      | 2,2-2                  | Reg   | ister Organiz                  | ation   | • • • | 24     |     |

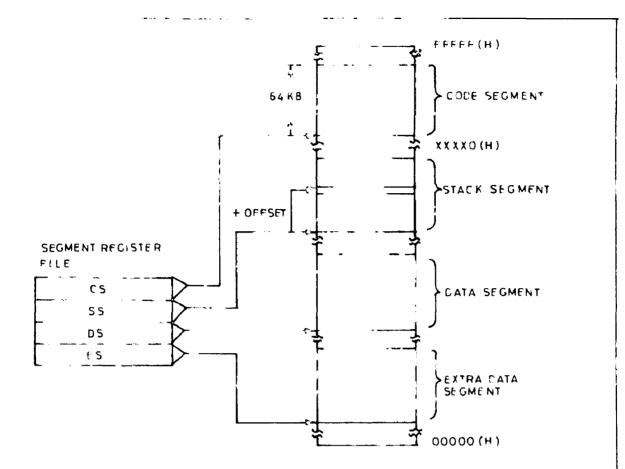

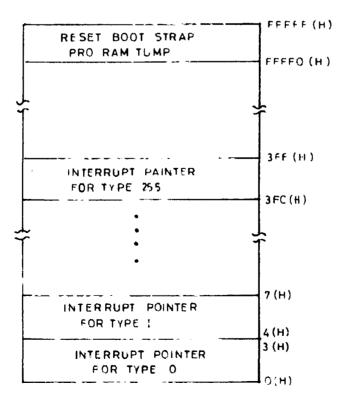

|         |      | 2.2-3                  | Mem   | ory Organizat                  | ion     | • • • | 26     |     |

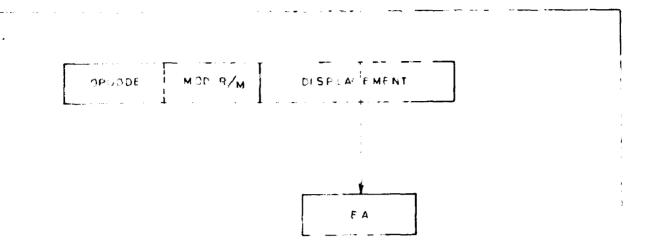

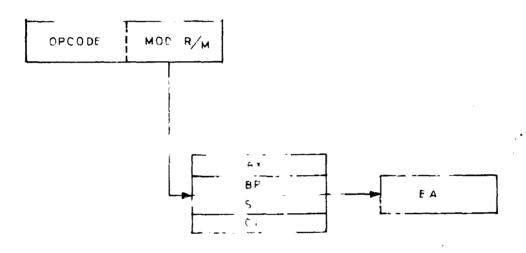

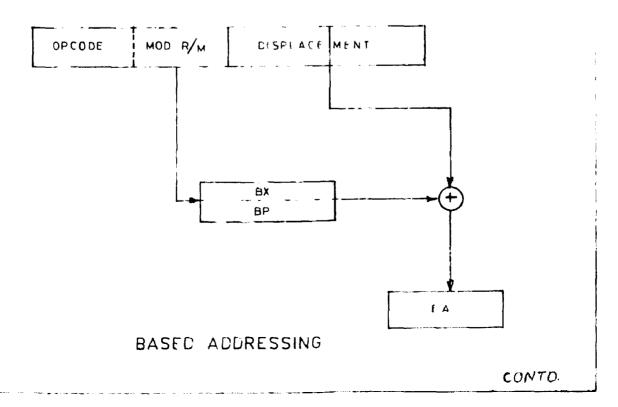

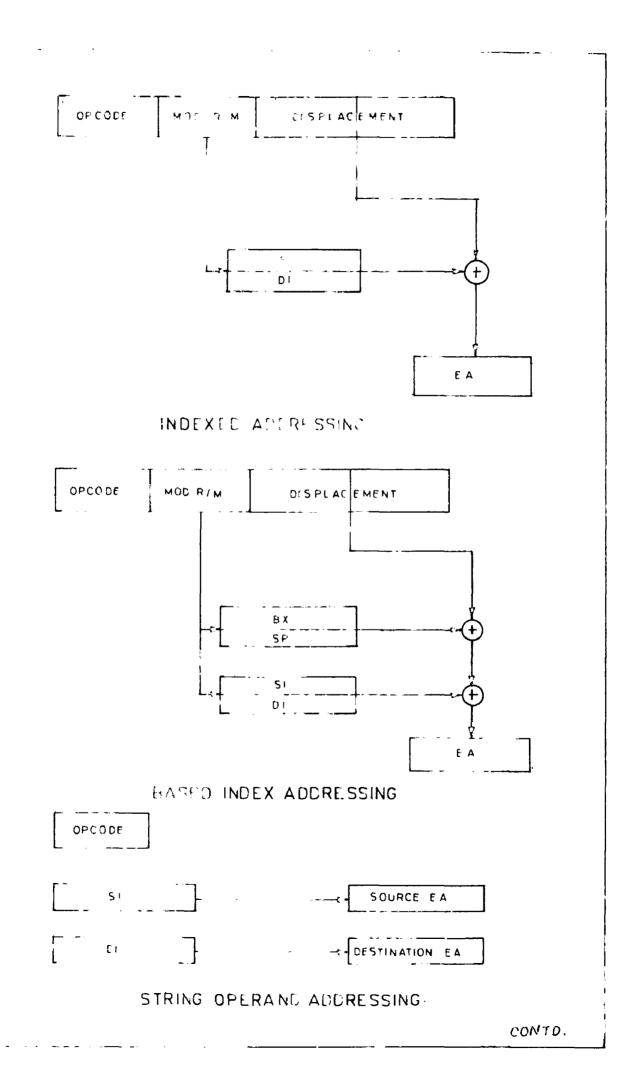

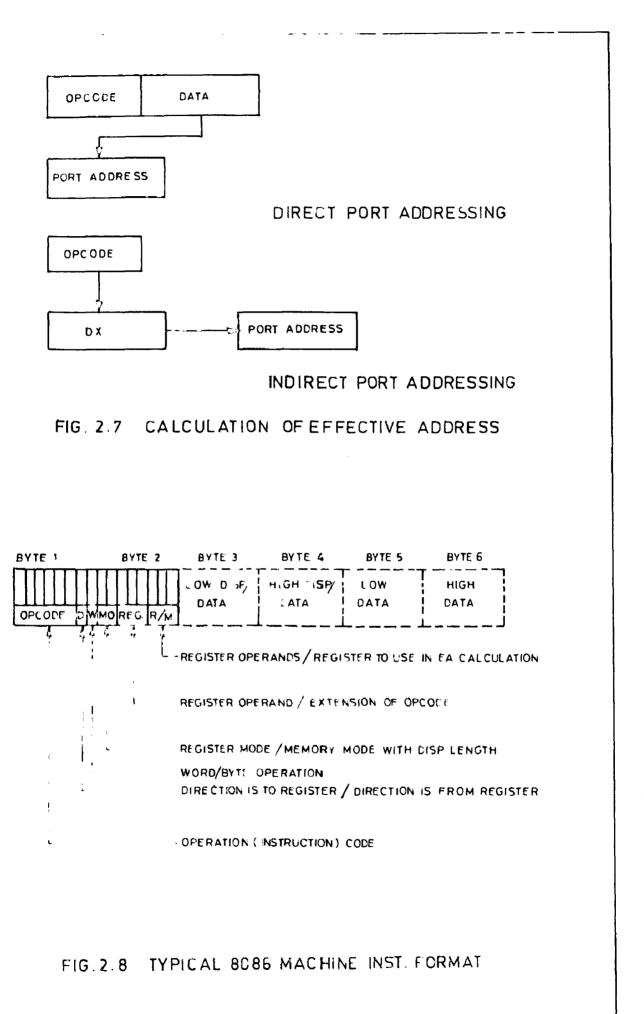

|         |      | 2.2-4                  | Add   | lressing Modes                 |         | •••   | - 29   |     |

|         |      | 2.2-5                  | Ins   | truction set                   |         | • • • | 33     |     |

|         | 2.3  | Summar                 | у     |                                |         | • • • | 42     |     |

| III     |      |                        |       | DIGITAL FILTE<br>URE AS BASICI |         |       | . 43 – | 64  |

|         | 3.1  | Introd                 | lucti | on                             |         | •••   | 43     |     |

|         | 3.2  | Why a                  | Seco  | nd O <b>rde</b> r Moáu         | le      | • • • | 43     |     |

\_\_\_

| 3.3  | Second                                                                               | Order Digital Filter                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

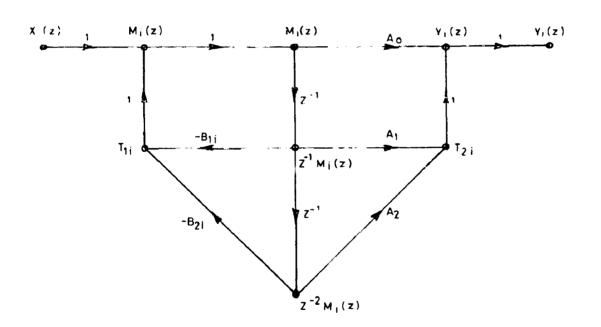

|      | 3.3-1                                                                                | Mathematical Derivation                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | 3.3-2                                                                                | Algorithm for Implementation                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | 3.3-3                                                                                | Software Program using Intel<br>8086 Instruction Set                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.4  |                                                                                      |                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | 3.4-1                                                                                | I'th Module                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

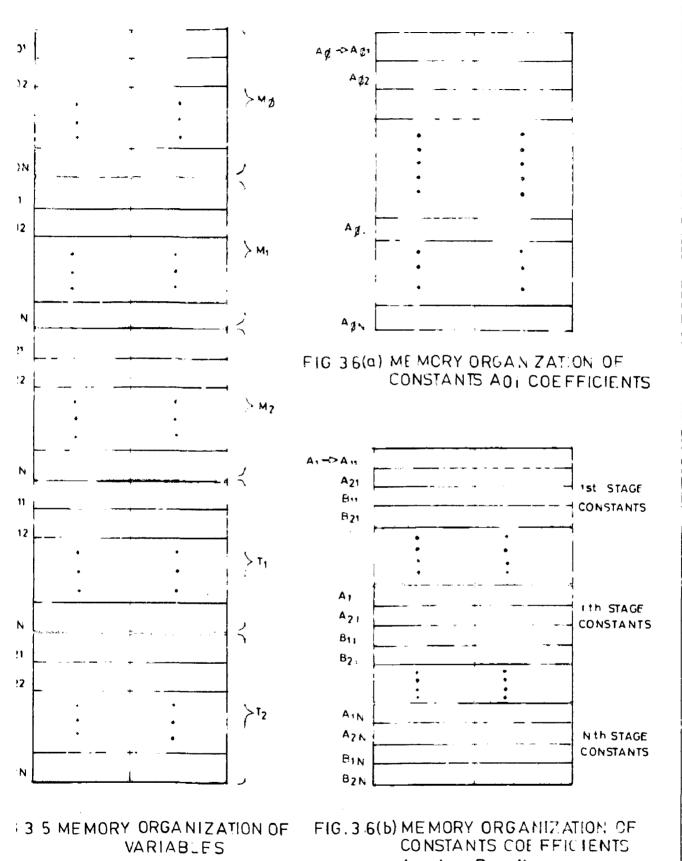

|      | 3.4-2                                                                                | Memory Organization                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | 3.4-3                                                                                | Identification of Subroutine                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

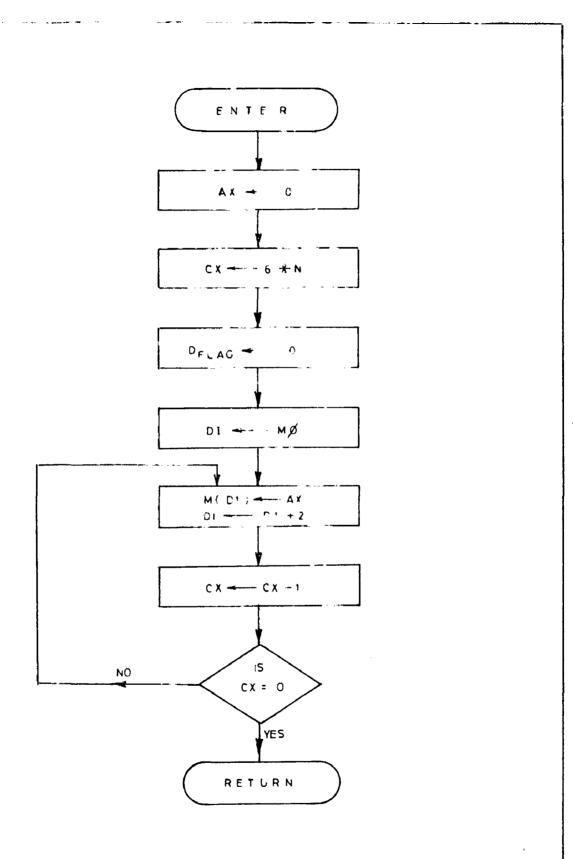

|      | 3.4-4                                                                                | Subroutine Thitilization 1D                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

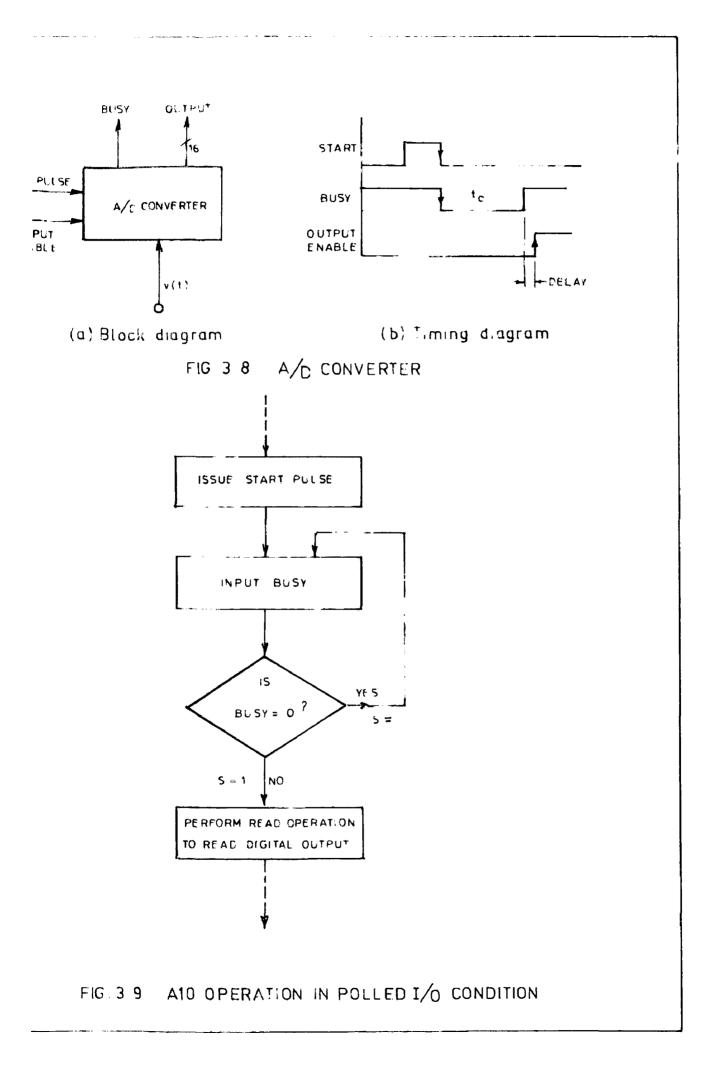

|      | 3.4-5                                                                                | Subrottine Input 1D                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

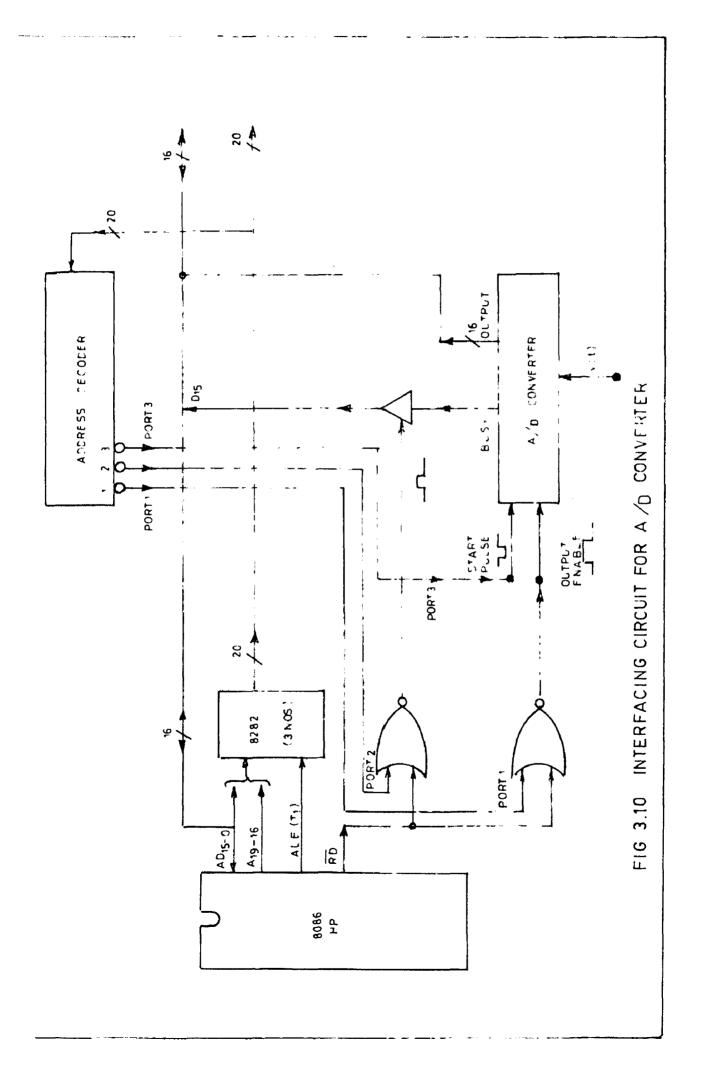

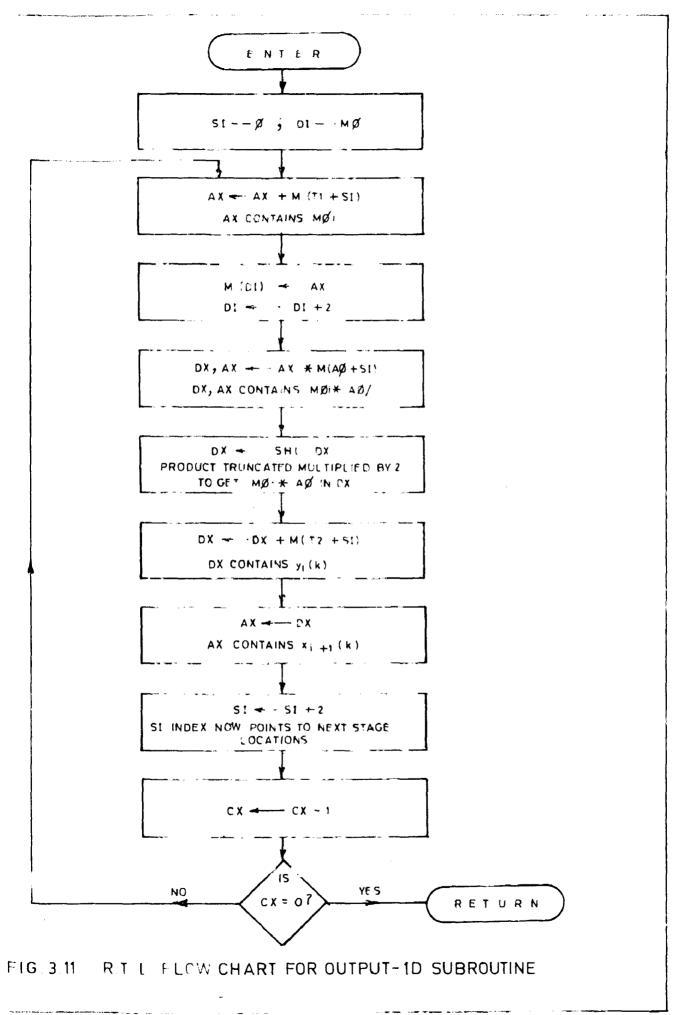

|      | 3.4-6                                                                                | Subroutine Output 1D                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

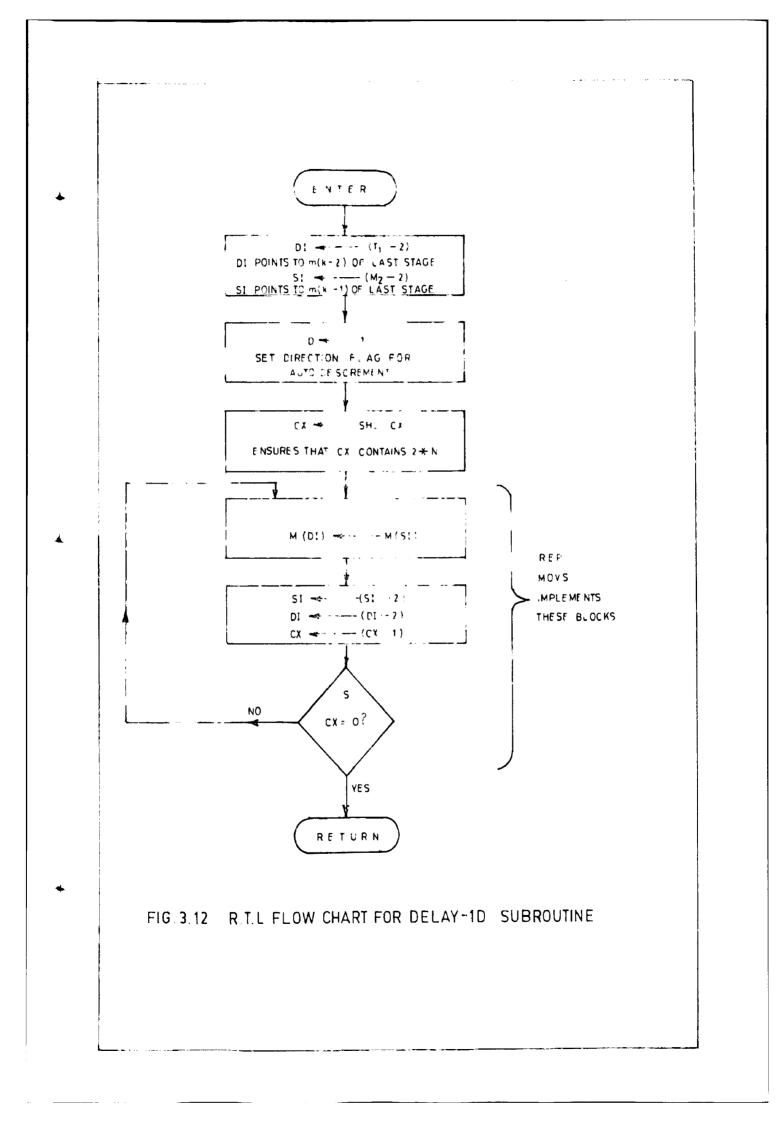

|      | 3.4-7                                                                                | Subroutine Delay 1D                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

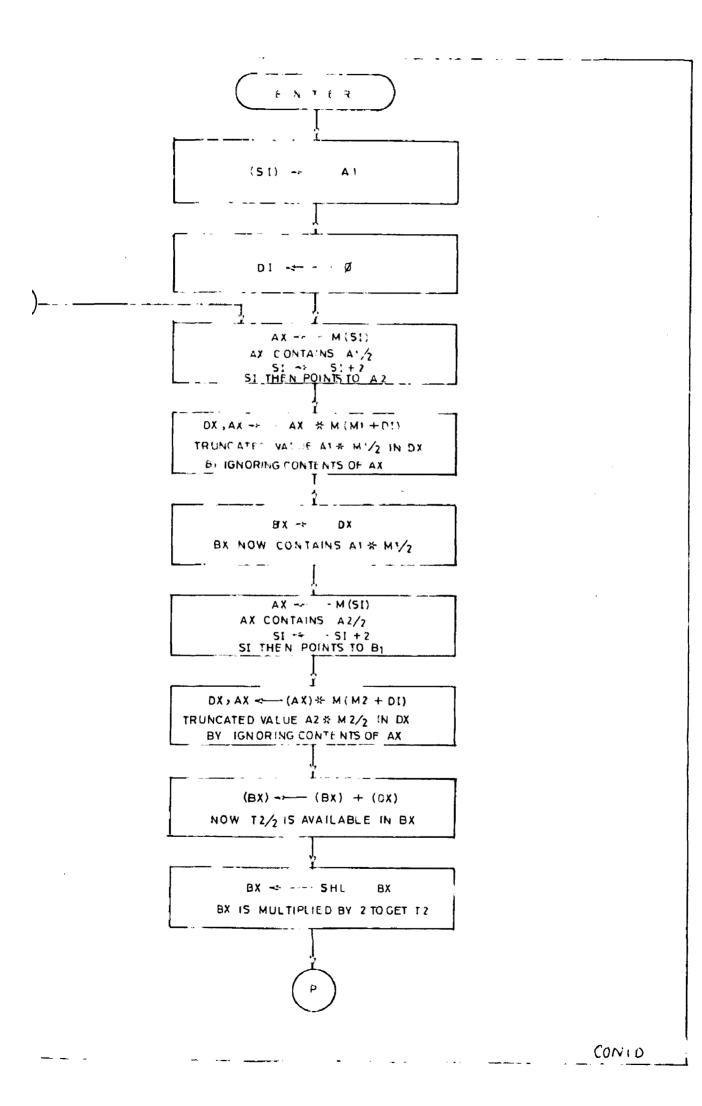

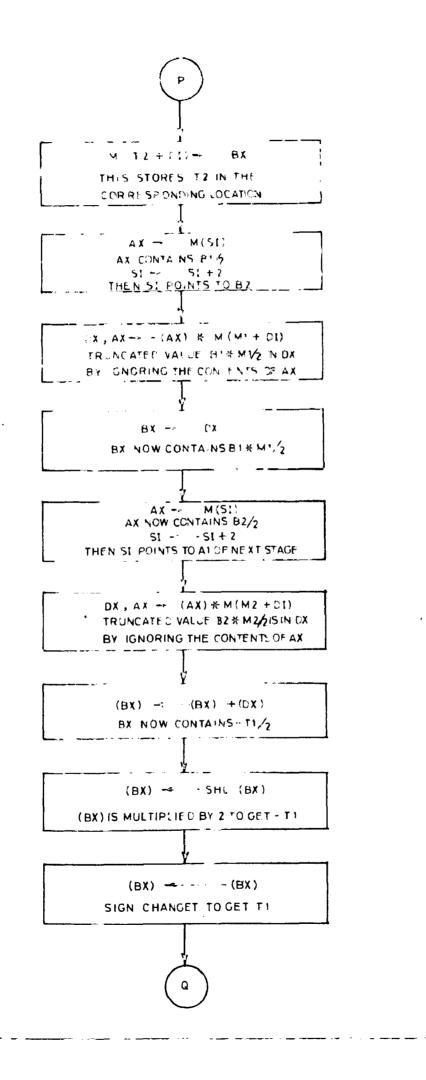

|      | 3.4-8                                                                                | Subroutine Preprocessing 1D                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

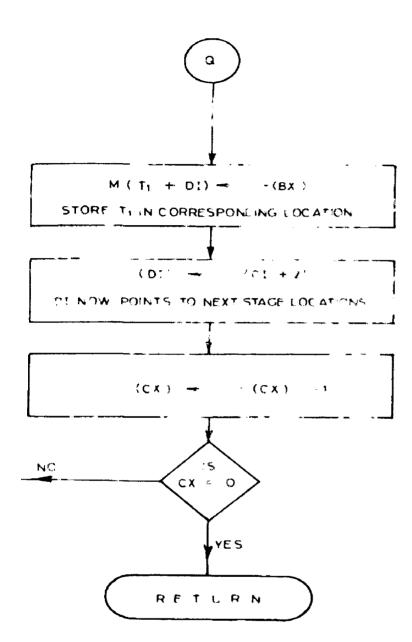

|      | 3.4-9                                                                                | Main Program                                                                                                                                                                                                                                                                                                                               | ٠                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.5  |                                                                                      | -                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.6  | Summar                                                                               | У                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      |                                                                                      |                                                                                                                                                                                                                                                                                                                                            | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | - 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.1  | Introd                                                                               | uction                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4.2  | 2D Str                                                                               | acture                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

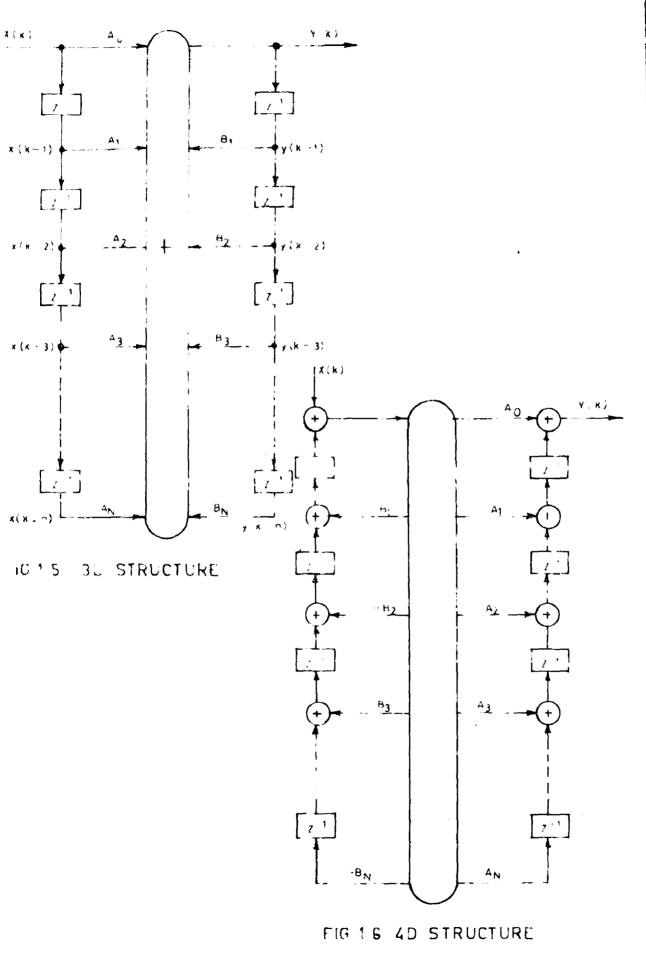

| 4.3  | 3D Str                                                                               | uctura                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4•4  | 4D Str                                                                               | ucture                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4•5  | 1X and                                                                               | 2X Structure                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4.6  | Summar                                                                               | y                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CONC | LUSIONS                                                                              | & SUGGESTIONS FOR FURTHER WORK                                                                                                                                                                                                                                                                                                             | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | - 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| REFE | RENCES                                                                               |                                                                                                                                                                                                                                                                                                                                            | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | - 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| APPE | NDICES                                                                               | (I to V)                                                                                                                                                                                                                                                                                                                                   | 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | - 128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 3.4<br>3.5<br>3.6<br>IMPLI<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>CONC<br>REFE | 3.3-1<br>3.3-2<br>3.3-3<br>3.4 Cascade<br>Second<br>3.4-1<br>3.4-2<br>3.4-3<br>3.4-3<br>3.4-4<br>3.4-5<br>3.4-6<br>3.4-7<br>3.4-6<br>3.4-7<br>3.4-8<br>3.4-9<br>3.5 Parall<br>Order<br>3.6 Summary<br>IMPLEMENTATY<br>DIGITAL FILM<br>4.1 Introdu<br>4.2 2D Structure<br>4.3 3D Structure<br>4.4 4D Structure<br>4.5 1X and<br>4.6 Summary | <ul> <li>SOBE Instruction Set</li> <li>3.4 Cascade Structure of K'th order Filter - N<br/>Second Order 1D Modules in Cascade</li> <li>3.4-1 I'th Module</li> <li>3.4-2 Memory Organization</li> <li>3.4-3 Identification of Subroutine</li> <li>3.4-3 Identification of Subroutine</li> <li>3.4-4 SubroutineTwitilization 1D</li> <li>3.4-5 Subroutine Input 1D</li> <li>3.4-6 Subroutine Output 1D</li> <li>3.4-7 Subroutine Preprocessing 1D</li> <li>3.4-8 Subroutine Preprocessing 1D</li> <li>3.4-9 Main Program</li> </ul> 3.5 Parallel Implementation of K'th<br>Order Digital Filter 3.6 Summary IMPLEMENTATION OF SECOND ORDER<br>DIGITAL FILTER THROUGH OTHER STRUCTURES 4.1 Introduction 4.2 2D Structure 4.3 3D Structure 4.4 4D Structure 4.5 1X and 2X Structure 4.6 Summary CONCLUSIONS & SUGGESTIONS FOR FURTHER WORK | <ul> <li>3.3-1 Nathematical Derivation</li> <li>3.3-1 Nathematical Derivation</li> <li>3.3-2 Algorithm for Implementation</li> <li>3.3-2 Algorithm for Implementation</li> <li>3.3-2 Algorithm for Implementation</li> <li>3.3-2 Algorithm for Implementation</li> <li>3.3-3 Software Program using Intel<br/>8086 Instruction Set</li> <li>3.4 Cascade Structure of K'th order Filter - N<br/>Second Order 1D Modules in Cascade</li> <li>3.4-1 I'th Module</li> <li>3.4-2 Memory Organization</li> <li>3.4-2 Memory Organization</li> <li>3.4-3 Identification of Subroutine</li> <li>3.4-4 SubroutineTMitlization 1D</li> <li>3.4-5 Subroutine Input 1D</li> <li>3.4-6 Subroutine Output 1D</li> <li>3.4-7 Subroytine Dalay 1D</li> <li>3.4-8 Subroutine Prepro cessing 1D</li> <li>3.4-9 Main Program</li> </ul> 3.5 Parallel Implementation of K'th<br>Order Digital Filter 3.6 Summary IMPLEMENTATION OF SECOND ORDER INFIGURAL FILTER THROUGH OTHER STRUCTURES 4.1 Introduction 4.2 2D Structure 4.3 3D Structures 4.5 1X and 2X Structure 4.6 Summary CONCLUSIONS & SUGGESTIONS FOR FURTHER WORK 83 REFERENCES |

IV

V

#### CHAPTER - O

# INTRODUCTION

# 0.1 HISTORICAL INTRODUCTION

As man becomes more certain of his control of physical things, an ever more important part of his work is the manipulation of symbols he uses to describe and control these physical things. The field of waveform manipulation or signal processing as in radio, radar, sonar, seismology etc., is one of the keystones of science and technology. The techniques and applications of this field are as old as Newton and Gauss and as new as digital computer and intograted circuits.

During the decade of 1960-70, it became practical to represent information-bearing waveforms digitally and to do signal processing on the digital representation of the waveform. The availability of high speed digital computers fostered the development of increasingly complex and sophisticated signal processing algorithms. The significant break through in the area of integrated circuit technology promise occonomical implementations of very complex digital signal processing systems.

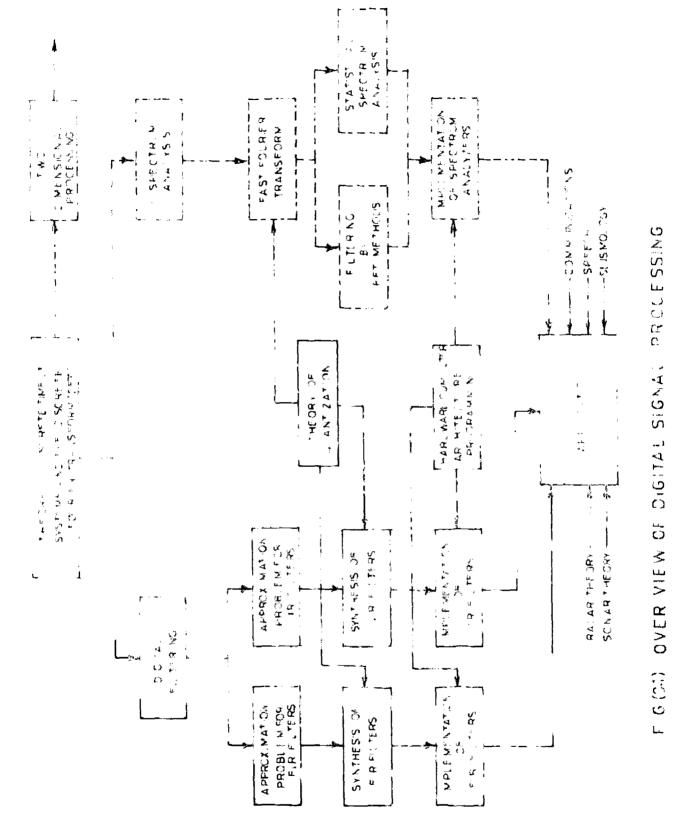

Fig. (0.1) illustrates one view of how the field has emerged and spread out. Digital filtering is one of the major subdivisions of Digital signal processing. Digital filtering processing algorithms have been used primarily in

; ; ;

------

į

| |

ļ

; ;

ţ

computer simulation, sampled data analysis and data reduction computations. With the increasing extensive application of digital processors to many systems, more and more importance is place on the development of mathematical tools for its analysic and dosign. The 'Z-transform' result in considerable simplification and understanding. The work of Kaiser, the first major contribution to the field of Digital signal processing, showed how much of the well. developed theory of the design of filters made of resistors, capacitors and inductors could be translated, with the aid of the Z-transform into straightforward digital filter techniques. At about the same time tremendous impetus was given to this emerging field by the Cooley-Tukey (1965) paper on a fast method of computing the discrete Fourier transform, a method that was subsequently popularized and extended via. many papers in the IEEE Transactions of the Group on Audio and Electroacoustics and other journals. At this time. the development of a formal and quite comprehensive theory of digital filters was well under way.

Perhaps the most interesting aspect of the development of the field of Digital signal processing is the changing relationship between the roles of FIR (finite impulse response) and IIR (infinite impulse response) digital filters. Initially Kaiser analysed FIR filters

using window functions, which indicated that IIR filters were more efficient than FIR filters. However, Stockham's work on the FFT method of performing convolution, or more specifically FIR digital filtering, indicated that implementation of high-order FIR filters could be made extremely computationally efficient; thus comparisons between FIR and IIR filters are no longer strongly biased towards the latter. These results also inspired significant research for efficient design for FIR filters.

The Digital filter implementation till now was confined primarily to computer programs for simulation work or for processing relatively small amounts of data. However, with the rapid development of integrated circuit technology and especially the potential for large-scale-integration (LSI) of digital circuits made many of the Digital filters more attractive from the standpoint of cost, size and  $e \times theme$ reliability.

The design of high space multipliers was of prime concern to many hardware and software implementations of signal processing algorithms. Standard TTL components gave sufficient speed to allow an effective filter to be implemented. Integrated circuits such as the Advanced Micro Devices AM25 LS14 2's complement multiplier was introduced specifically for signal processing applications. Peled and Liu

used semiconductor memories for the purpose of fast multiplication, and resulted in significant saving in the cost and power consumption.

The Digit filter may be regarded as a special purpose computer built from an 'off-the shelf' logic family. The design depends upon the sampling rate and flexibility required. For simple sections a special purpose hardwork filter will be more efficient than a general purpose microprocessor. Instruction sets allow greater flexibility. The suitable microprocessor selected depends upon the particular application. Digital filters for different purposes have been implemented making use of 8 bit, 16 bit microprocessors Much credit here goes to Nagle & Nelson.For most applications 16-bit accuracy is sufficient to avoid qualization problems with filtors of moderate order  $(n \leq 10)$ . It has been seen that with Intel 8086 (and other 16 bit microprocessors presently available) a significant improvement over the sampling rates can be achieved as compared with the previous generation of microprocessors, without significant increase in system cost.

### 0.2 OUTLINE OF THE PRESENT WORK

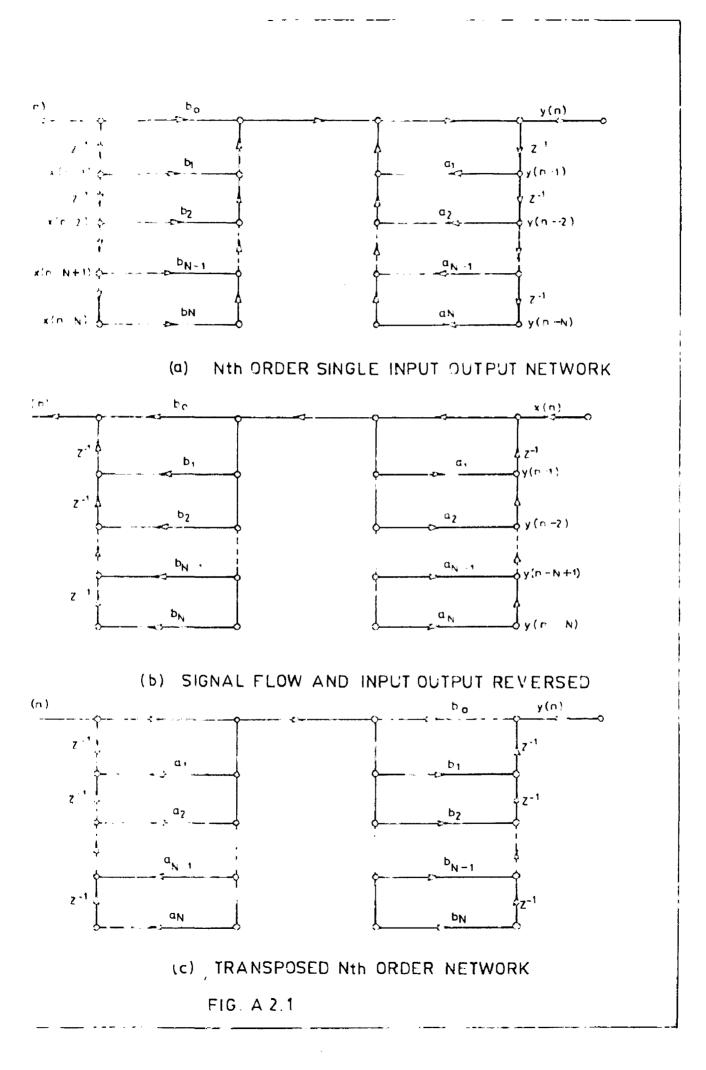

Chapter I discusses the general Transfer function and the various techniques for realizing a Digital filter.

Four Direct structures have been derived and it is in one of these structures that a Digital filter is usually implemented.

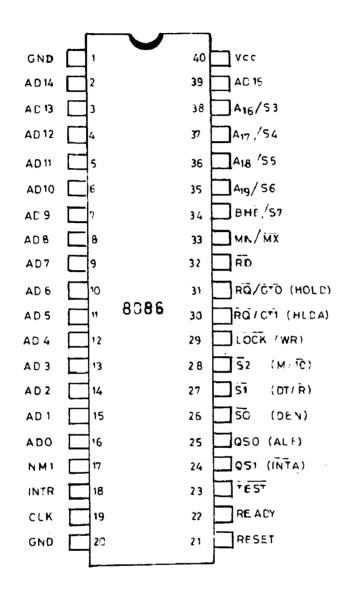

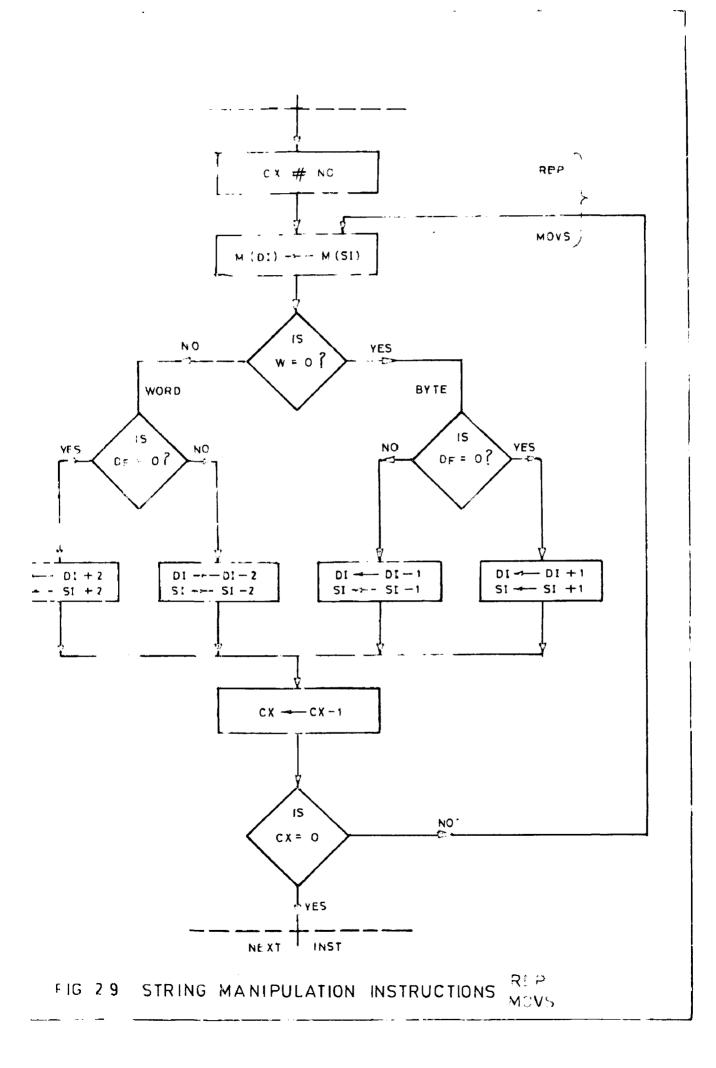

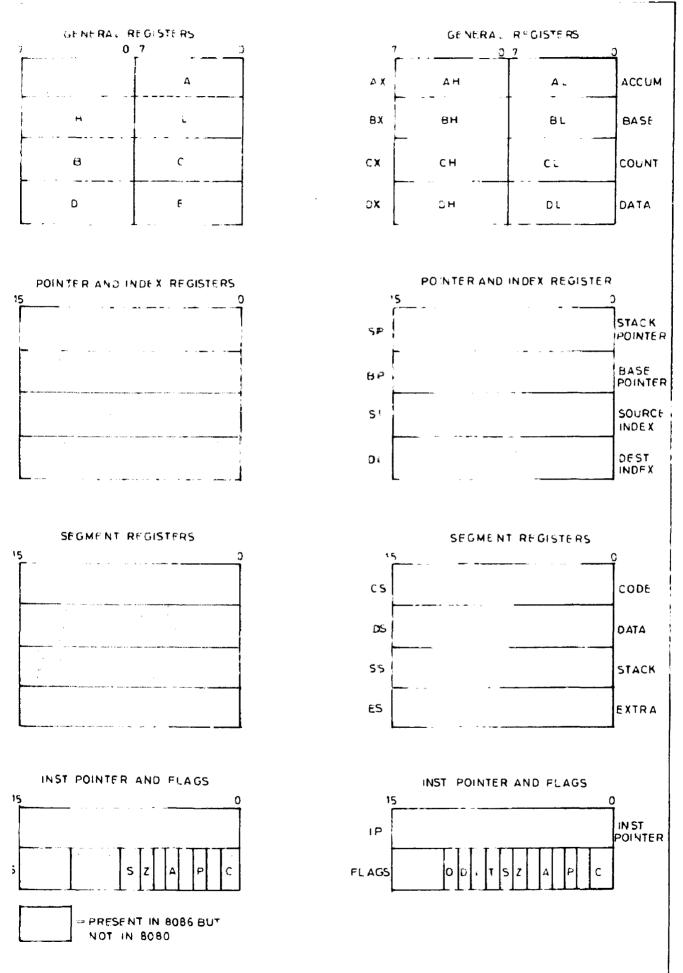

The salient features of Intel 8086 microprocessor which is selected for our purpose has been carried out in considerable detail in Chapter II. 8086 microprocessor is a totally new design, than any microprocessor previous offered by the Intel group and has a powerful set of instructions. Memory to memory string operations, hardwired multiplication and division, and flexible addressing modes are some of the significant operations.

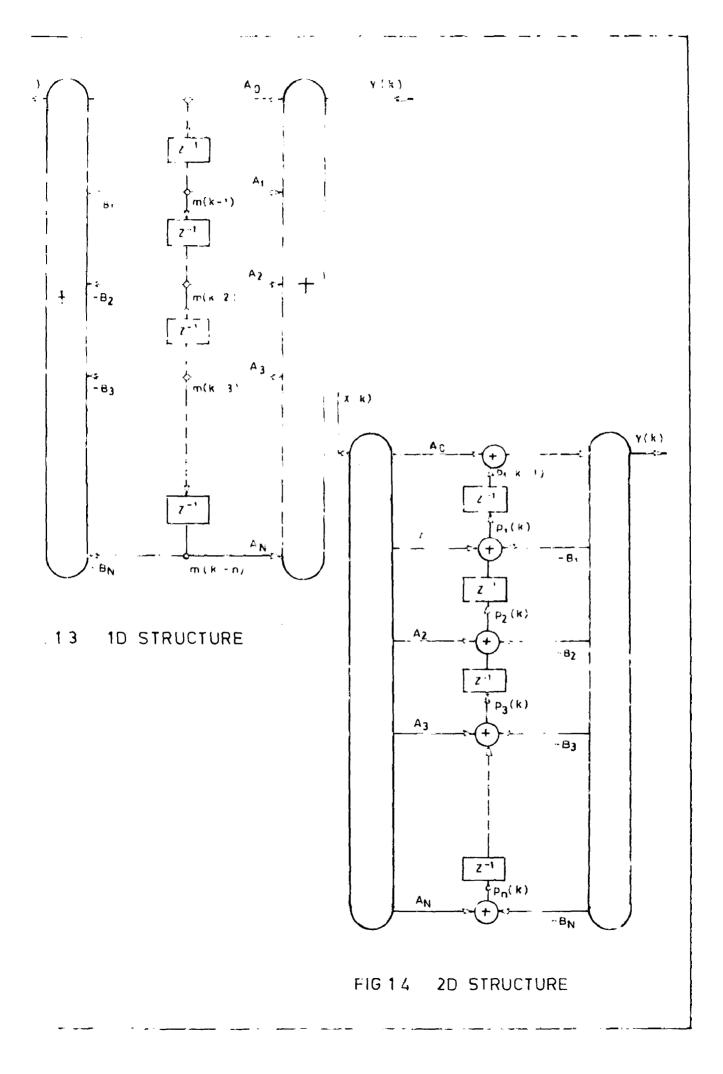

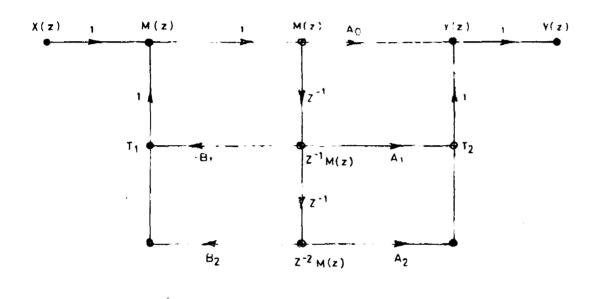

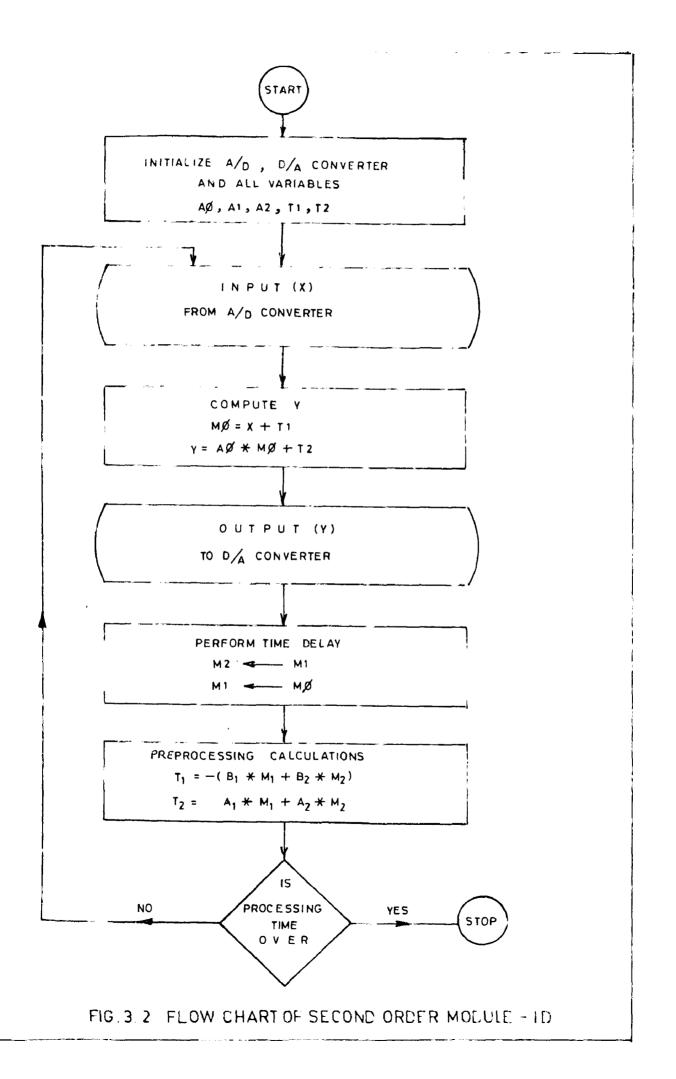

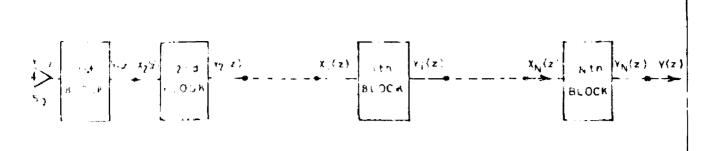

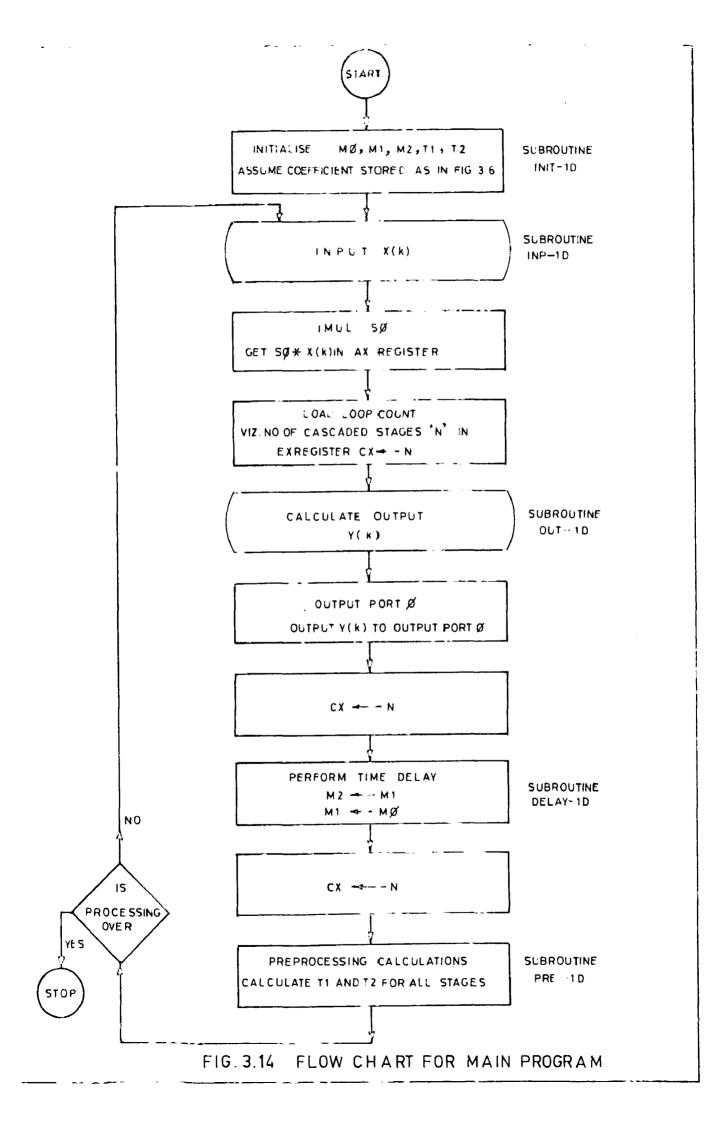

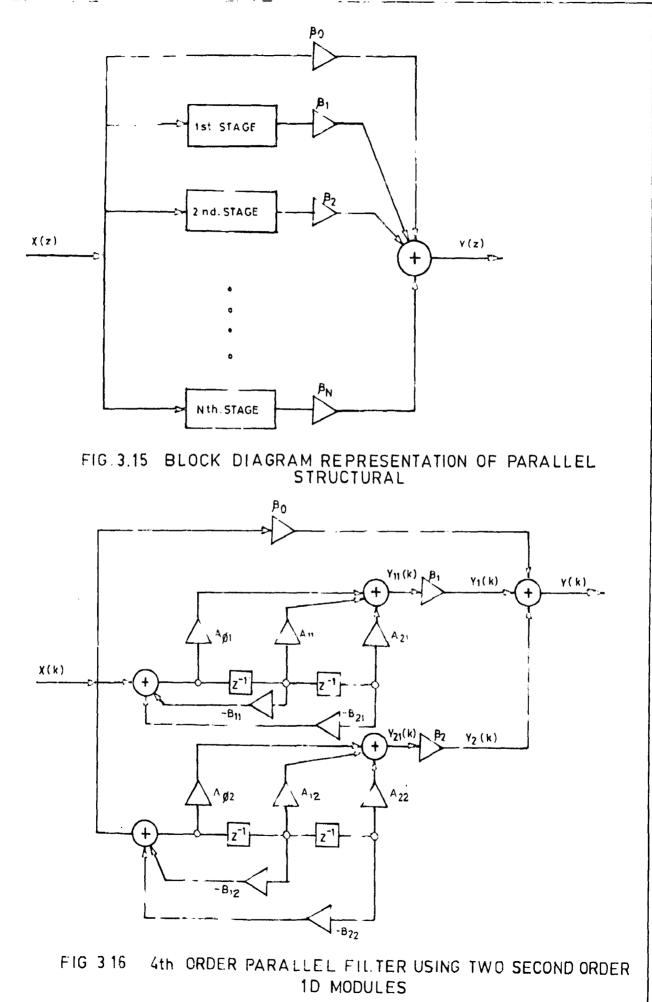

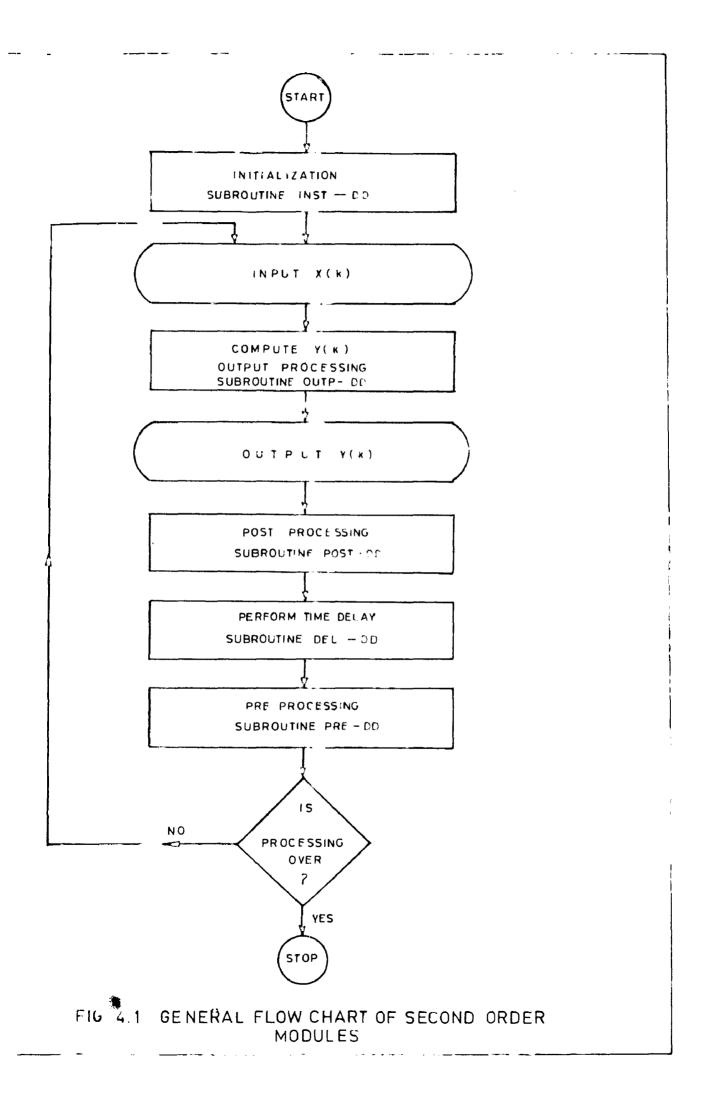

Referring to Kaiser's work a second order structure is best suited for implementing higher order filters. Chapter III presents the implementation of a second order 1D module. A flow chart and a main program in 8086 Assembly language and the various subroutines with explanations is given. A K'th order cascaded filter has been discussed. Also a 4th order parallel filter has been given as an example. Use of 1D second order module subroutine is made in the programs:

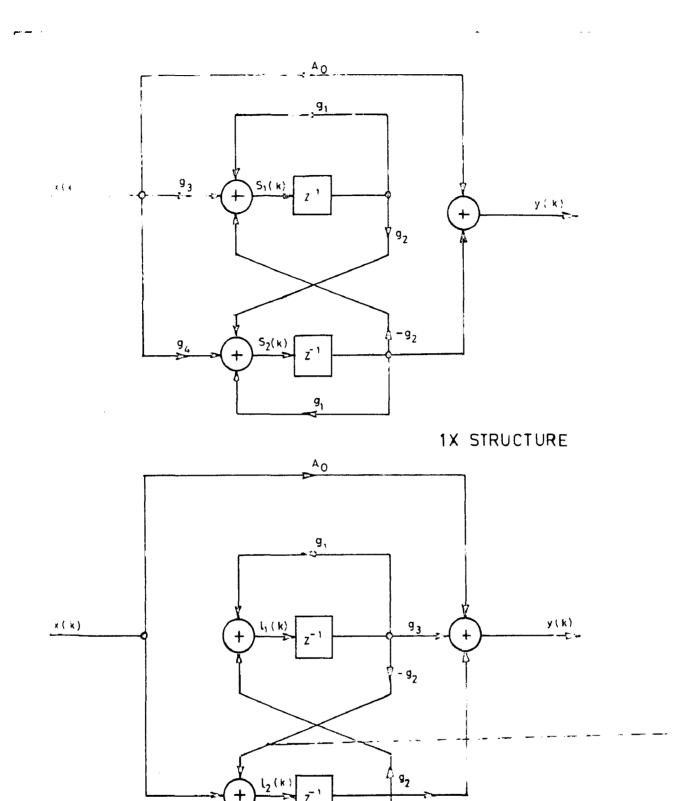

Chapter IV discusses the other types of structures used for realization of Digital filters. The sequence of study here is the derivation of the necessary equations, algorithm and the flow chart programs in 8086 Assembly

language. A second order module is considered in each of the five cases viz. 2D, 3D, 4D, 1X, 2X.

The dissertation concludes with the summary of the work done alongwith suggestions for future study and development.

#### CHAPTER - I

TRANSFER FUNCTION AND REALIZATIONS OF A DIGITAL FILTER

#### 1.1 INTRODUCTION

A major subdivision of Digital Signal Processing is Digital filtering - a computational algorithm performed on a sampled input signal resulting in a transformed output signal. Digital filtering processing algorithms have been used in computer simulation, sampled data analysis and data reduction computations. Kaiser <sup>6</sup> shows that the Z-Transform results in considerable simplification and understanding of problems associated with sampled data system. In this chapter the Transfor function of a Digital filter and its pictorial representations are discussed. Also, the various types of realizations of a Digital filter are studied.

# 1.2 Z-TRANSFER FUNCTION

In Linear continuous (Analog) filter theory, linear differential equation is one of the mathematical tools available to describe the Transfer function. Similarly, in linear Digital (Sampled) filter theory the linear difference equation is available as a mathematical tool for analysis and synthesis.

The linear difference equation <sup>7</sup> defines the sampled output pulse amplitude as a function of the present input pulse and any number of past input and output pulses. A

general form of the difference equation is

$$Y(nT) = \sum_{i=0}^{N} A_i \cdot X(nT - iT) - \sum_{i=1}^{N} B_i \cdot Y(nT - iT) \dots (1.1)$$

where X(nT) represents the present input samples and X(iT) are the past input samples. Similarly, Y(nT) and Y(iT) are present output samples and past output samples respectively. A<sub>i</sub> and B<sub>i</sub> coefficients are constants which determine the response of the filter.

The Z-Transform  $^{1,3,5,7}$  of the above mentioned general difference equation (1.1) is :

$$Y(z) = X(z) \cdot \sum_{i=0}^{N} A_{i} \cdot Z^{-i} - Y(z) \cdot \sum_{i=0}^{M} B_{i} \cdot Z^{-i} \dots (1.2)$$