# MICROPROCESSOR IN POWER SYSTEM INSTRUMENTATION

## A DISSERTATION

Submitted in partial fulfilment of the requirements for the award of the Degree of MASTER OF ENGINEERING

in

## ELECTRICAL ENGINEERING (MEASUREMENT AND INSTRUMENTATION)

By

ATUL NIGAM

GIL BL

DEPARTMENT OF ELECTRICAL ENGINEERING UNIVERSITY OF ROORKEE ROORKEE (INDIA) 1981

## ACKNOWLEDGEMENI

The author humbly expresses his deep sense of gratitude to his guides Dr. V.K. Verma, Professor in Electrical Engineering and Mr. V.K. Bansal, Reader in U.S.I.C. for their keen interest, kind guidance and thoughtful advice rendered by them during the course of dissertation work.

ATUL NIGAM

#### CERTIFICATE

Certified that the dissertation entitled "MICRO-PROCESSOR IN POWER SYSTEM IN STRUMENTATION" which is being submitted by ATUL NIGAM in partial fulfilment for the award of Degree of Master of Engineering in ELECTRICAL ENGINEERING (Measurement & Instrumentation) of the University of Roorkee, Roorkee, is a record of the student's own work carried out by him under my supervision and guidance. The matter embodied in this dissertation has not been submitted for the award of any other degree or diploma.

This is further certified that he has worked for a period of 18 months from January 200 to June 1981 for preparing this dissertation for the Master of Engg. Degree at this University.

(V.K.BANSAL) READER USIC ROORKEE,U.P.

(V.K.VERMA) PROFESSOR ELECTRICAL ENGG.DEPTT. UNIVERSITY OF ROORKEE

## ACKNOWLEDGEMENI

The author humbly expresses his deep sense of gratitude to his guides Dr. V.K. Verma, Professor in Electrical Engineering and Mr. V.K. Bansal, Reader in U.S.I.C. for their keen interest, kind guidance and thoughtful advice rendered by them during the course of dissertation work.

## ATUL NIGAM

| AND A CONTENTS AND | ŧ   |

|--------------------------------------------------------|-----|

| 1. INTRODUCTION                                        | 1   |

|                                                        | 4   |

| 2. PROBLEM FORMULATION                                 | 5   |

| (1) Synchronizer Detail                                | 6   |

| (11) Block Diagram Description<br>(111) Flow Chart     | 7   |

| (TTT) LTOM MUSIC                                       | 10  |

| 3. MICRO PROCESSOR BASIC                               | 10  |

| (1) Introduction                                       |     |

| (11) Architecture of CPU                               | 12  |

| (iii) Instruction set                                  | 13  |

| 4. MICROPROCESSOR BASED SYSTEM DESIGN                  | 35  |

| (1) Hardware Design                                    | 35  |

| (11) System's Operation                                | 47  |

| (111) Soft-ware Design                                 | 49  |

| 5. MATHEMATICAL MODELLING & COMPUTER SIMULATION        | 59  |

| (i) Introduction                                       | 59  |

| (11) Mathematical Model of Synchronous Machine         | 59  |

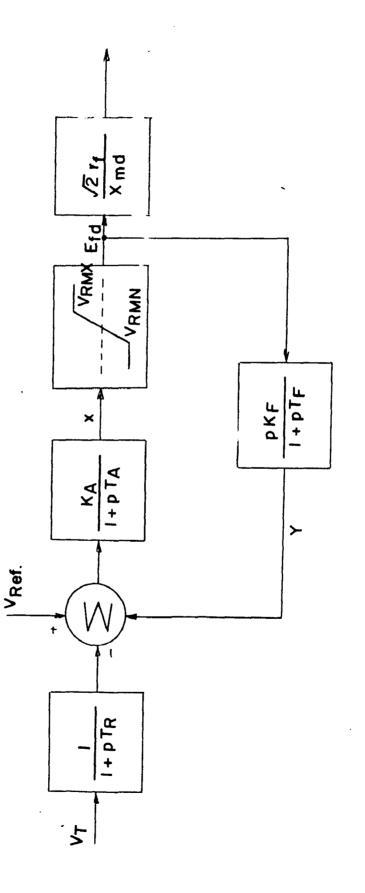

| (111) Computer Representation of Excitation System     | 63  |

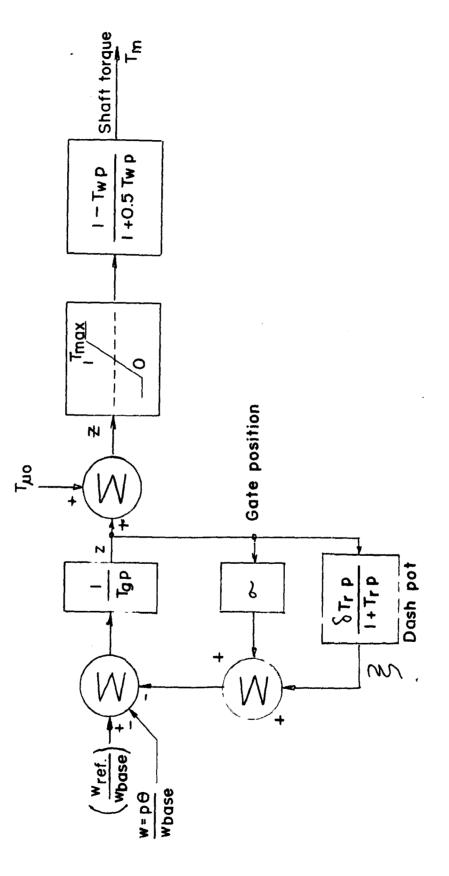

| (1v) Computer Representation of Governor               | 66  |

| (v) Initialization                                     | 67  |

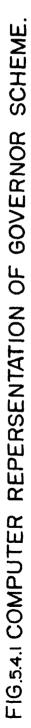

| (vi) Flow Chart                                        | 68  |

| (vii) Discussion                                       | 69  |

| (viii) Appendix                                        | 70. |

| 6. CONCLUSION                                          | 73  |

| REFERENCES                                             | 74  |

•

#### CHAPTER 1

#### INTRODUCTION

In the modern power houses, the protection of equipments has become very important. Invariably the protection of machines is an interdependent phenomenon i.e. the protection of one machine is related to a group of machines. The system requires the monitoring of a large number of parameters and after processing the data the commands have to be issued to various machines for control purposes.

The invention of microprocessor has made possible the design of such equipments for protection and control purposes. It is possible to monitor a very large number of interdependent parameters, process them and then decide the control command for various machines with the help of a small desk top microprocessor based equipment.

Synchronization of generators on to the main bus is an important problem. It requires the continuous monitoring of voltage, frequency and phase angle of generator and the bus. The control commands have to be issued to the generator C.B., field circuit and governors to achieve safe synchronization.

A machine can be switched into the system, only when certain conditions necessary for its synchronization with the system are satisfied. Manual method using Voltmeter to judge the voltage and synchroscope to judge the slip frequency and phase difference is common, but not suitable when synchronizing is to be carried out rapidly and accurately. For example, in peak load stations, generators have to be operated only during peak loads and have

to be shut down during slump load period. Hence there is requirement for a faster synchronization.

2

Solid state components based automatic synchronizers have already been reported (1,2,3, ). Such synchronizers use a very large number of discrete components leading to a complexity of circuitary and lowering of its reliability.

A microprocessor based synchronizer can over come above mentioned a limitations of solid state components based automatic synchronizer. A.K. Ghai, H.K.Verma and P.Mukhopadhaya have developed and laboratory tested a microprocessor based synchronizer which is claimed to have a good prospect for small power houses to assist the operating engineer to carry out perfect and fast synchronization. They used on 8 bit SC/MP microprocessor system as a controller. First of all they measured and compared the voltages outside of microprocessor when it comes within the required band, the frequency of the machine and system was measured and compared in terms of the time periods inside the microprocessor. After the fulfilment of frequency condition, the C.B. is closed at minimum phase difference of the two voltages.

In the proposed synchronizer, the voltages are measured and compared inside the microprocessor itself. For this voltages are sampled and peak value is compared. When voltage and frequency of the incoming machine and system came within the required band, the rate of change of phase angle is calculated in order to send the closing command to circuit breaker to close the circuit at zero phase difference angle.

An 8-bit Intel 8080 A system has been used in the work presented here.

. : · · ·

. • \

•

...

•

#### CHAPTER 2

#### PROBLEM FORMULATION

When an incoming machine has been paralled with busbars, the factors influencing the extent of any disturbances or surges which may arise are- the capacity of the running plant, voltage, frequency, and phase of the machine with respect to those of busbars, and the synchronising torque. Accordingly, the conditions are laid down in the reported work to obtain a perfect and accurate synchronizations ensuring minimum system disturbances.

### 2.01 Conditions for Synchronization :

Following are conditions for synchronization of incoming machine with the system :

(1) Phase sequence of the incoming machine voltages and that of busbars must be same.

(2) The difference between magnitudes of their voltages must be small. In proposed work  $\pm$  5% of system voltage is assumed.but adjustable to any other value.

(3) Difference in frequencies of the two must be small. A maximum slip frequency of  $\pm 0.5$  % of the supply frequency is assumed in proposed work. However to get more precision slip frequency can be adjusted to the desired value.

(4) The difference in time phase between the incoming machine and running voltage must be small and decreasing with time. The proposed system is designed to permit the circuit closure at zero degree phase difference.by

taking into account the effect of rate of change of phase angle and circuit breaker closing time.

#### 2.1 Synchronizer Details :

The proposed synchronizer compares the machine voltage and frequency with those of busbars and gives signals for correcting the generator excitation and its speed. Once the voltage and frequency values are acceptable, the closing signal is sent to the circuit breaker, after taking into consideration the circuit breaker closing time, such that the circuit breaker closes at exact phase coincidence.

In proposed synchronizer; the busbar and incoming machine voltages from the respective transformers (V.Ts.) are fed to rectifiers through auxiliary VTs. The rectified voltages are fed to A/D convertors and then to microprocessor for voltage measurement. The largest value in one cycle of one voltage signal is compared with the largest value in one cycle of other voltage, signal. If the two values are within the acceptable limit, microprocessor starts frequency measurement.

For this, the rectified signals are squared and fed to microprocessor. With the help of clock, the counting is done inside the microprocessor for the time periods of the two wave-forms. The two counts are compared and when the counts difference comes within the acceptable limit, microprocessor starts to calculate the rate of change of phase angle. Otherwise, the frequency high or frequency low signal is sent to governor for correction.

-5

To calculate the rate of change of phase angle, the two signals which were used for frequency (time period) measurement are again used. Number of checking cycles between the two rising edges of waveforms are counted and when it starts decreasing, the rate of change is calculated and thus the instant of zero phase difference is calculated.

2.2 Block Diagram Description :

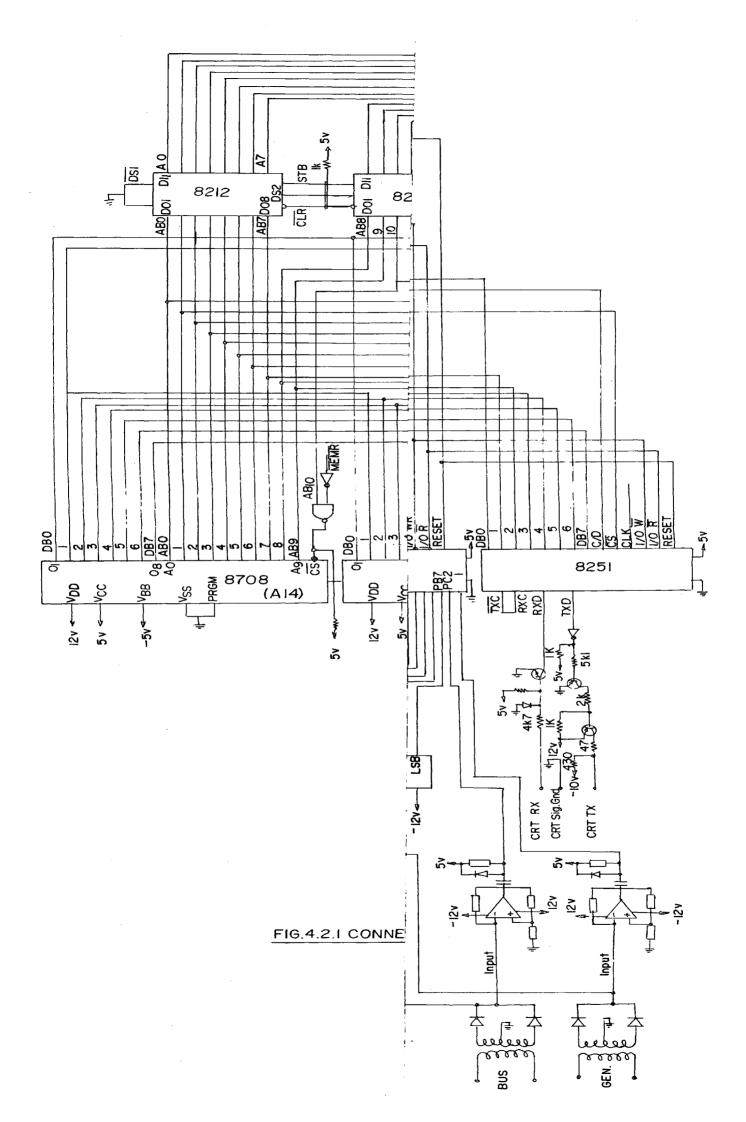

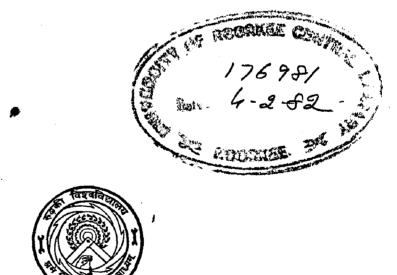

The system solving the autosynchronization problem can be represented in following blocks (Refer fig. 2.2) :

<u>Auxiliary Transformer</u> :- The order of the incoming bus and alternator voltage is 230 Volt. Which is too high to be used with other blocks of the system. Therefore a step down transformer is used.

<u>Rectifier</u>:- Input signals are rectified so that they can be used for voltage and frequency measurement.

<u>Squaring circuit</u> :- Rectified signal is fed to squaring circuit. The output of the squaring circuits are the square waves at the bus and generator frequencies respectively. The CPU carries out the time period measurement of the above waveforms.

<u>Analog to Digital (A/D) convertor</u> :- Signals from the rectifier circuits are fed to A/D convertors. As the name suggests the blocks convert the analog signals into digital signals for the voltage measurements, inside the CPU. Further the CPU also compares the bus and generators voltages and issues a MATCH command when the two are within programmed limits. Otherwise a "GENERATOR VOLTAGE HIGH" or " GENERATOR VOLTAGE LOW" commands are sent to the governors.

<u>Input/Output Ports</u> :- The signals from squaring circuits and Analog to Digital convertors are fed to microprocessor through the input ports. Those input ports which are connected to the signals coming from A/D covertors are used as Output port also for outputting the messages and command such as voltage low, voltage high, frequency low, Frequency High and circuit Breaker closing command. Teletype is also connected with IP/OP Port. <u>Read Only Memory</u> :- This is used to store the Monitor programme and other various programmes for Voltage measurement and comparision, Frequency measurement and comparision, calculation of rate of change of phase angle etc.

<u>Random Access Memory (RAM)</u> :- This is used for storing the intermediate results involved in the execution of program. <u>CPU</u> :- This is heart of microcomputer where the actual execution of instructions takes place.

<u>CRT</u> :- With the help of CRT, the operator can communicate with the equipment. The tolerances for voltage and frequency comparisions can be modified if required. A print out of circuit breaker closing command can also be obtained.

2.3 Flow Chart description :-

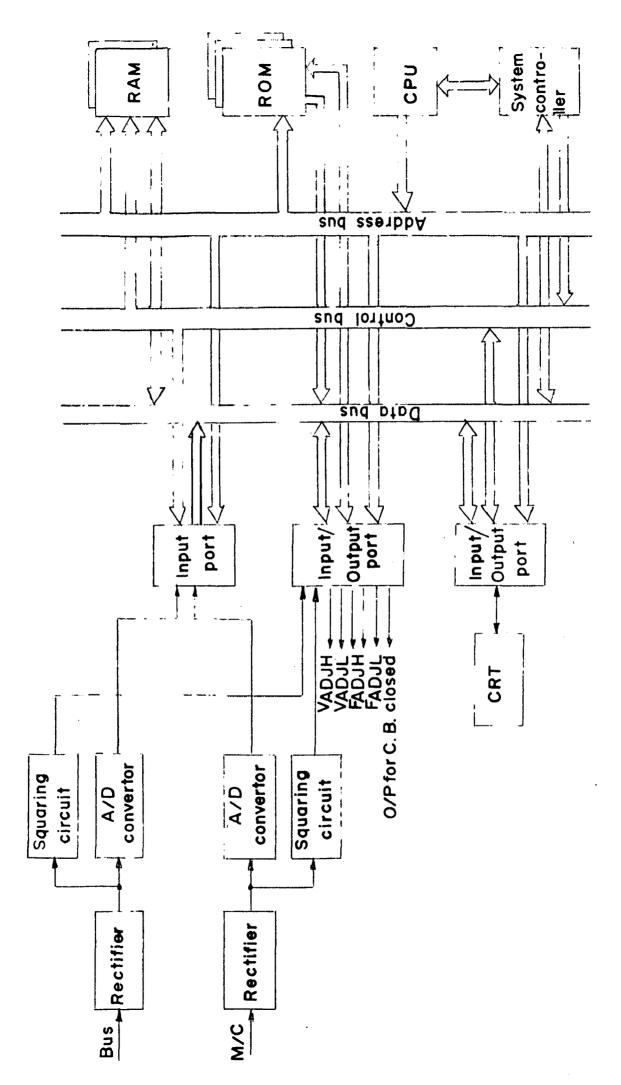

Fig. 2.3.1 shows the basic flow chart for autosynchronizer.

For this, maximum value of bus voltage is achieved on which tolerance of 5% is calculated. The maximum value of generator voltage is calculated and compared with the tolerance band across

bus voltage. If it does not lie in between tolerance band, a signal for adjustment of generator voltage is outputted and after a time delay of 5 seconds, same process is repeated.

When generator voltage comes within tolerance band, the time period corresponding to bus frequency is calculated on which tolerance of 0.5% is calculated. Then generators time period is calculated and compared with the tolerance band across the bus time period. If it does not lie in between tolerance band, a signal for adjustment of generator frequency is outputted and after a  $t_{ime}$  delay of 5 seconds; same process is repeated.

When generator voltage and frequency comes under tolerance band, the phase difference between the bus and generator is calculated. The time for zero phase difference is anticipated. The circuit breaker classing command is sent; taking the circuit breaker closing time in to account.

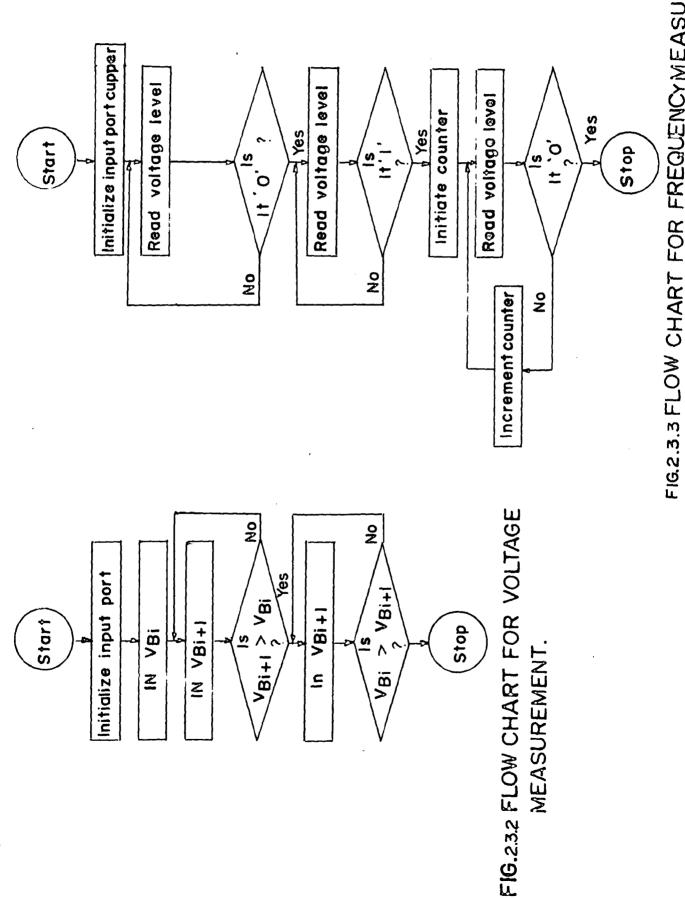

Fig. 2.3.2 shows the flow chart for voltage measurement. The output of Andogy to Digital (A/D) convertor is inputted and stored. This value is compared with the next output of A/D convertor. Both the values are compared and larger value is stored. In this way, largest value of voltage signal is retreived.

Fig. 2.3.3 shows the flow chart for frequency measurement. Frequency is measured in terms of time period. The coutning starts only when the zero to one transition takes place coutning is stopped when one to zero transition takes place thus the available counts are proportional to half value of frequency.

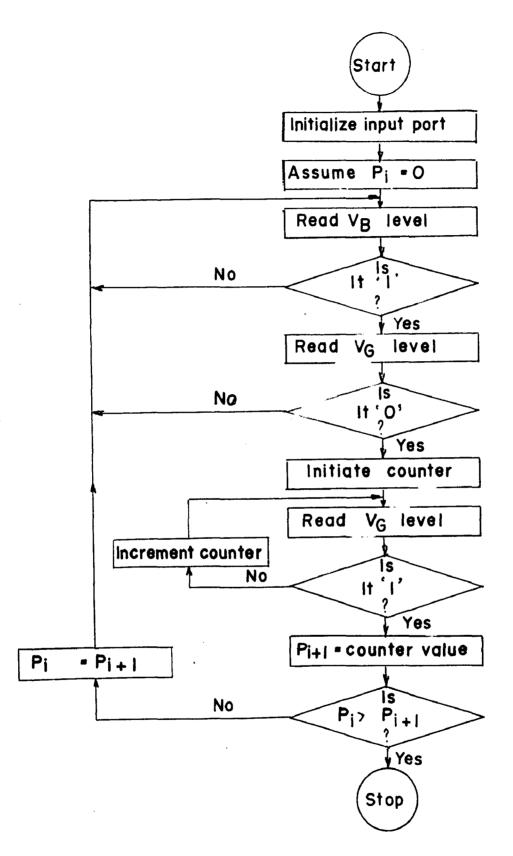

Fig. 2.3.4 shows the flow chart for phase measurement. Phase is measured in terms of counts between the bus signal and generator signal. To avoid mistake in counting, masking is done so that the counting initiates at the right moment.

#### CHAPTER 3

#### MICRO PROCESSOR BASIC

#### 3.01 INTRODUCTION :

The advent of minicomputers enabled the designers to include digital computers as part of various process control systems. Unfortunately the size and cost of mini computers has limited their use in "dedicated applications". The advent of microcomputer has made it possible to have a one card computer (size  $6^n \times 4^n$ ) as an integral part of the Process control equipment Microcomputer provides immense flexibility to the electronics engineering designing systems. By simple reprogramming the microcomputer; it is possible for the system designer to have another system.

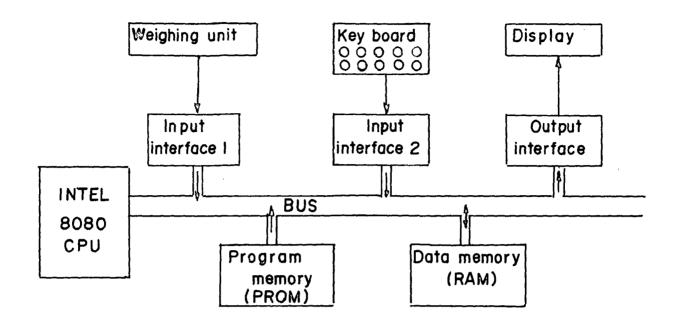

Consider the design of an automatic computing scale for the supermarket. The weighting unit finds out the weight of the commodity, and the price of the commodity is entered to the microcomputer through a keyboard and it is required to work out and display the total price.

The system block diagram is shown in figure 3.1. The weighing machine measures the weight of the object. The weight is converted in binary form and made available to the system through the Input Interface 1. The rate of the commodity is made available through Input interface 2. The central processing unit has multiplied the two numbers and OUTPUTS, the result to displays through output Interface. The steps can be summarised as below : 1. INPUT WEIGHT TO CPU FROM INTERFACE 1

2. INPUT PRICE TO CPU FROM INTERFACE 2

3. MULTIPLY WEIGHT AND PRICE

4. OUTPUT VALUE TO OUTPUT INTERFACE.

These commands are stored in programmable read only memory (PROM) in machine language instruction i.e. in binary form. The CPU FETCHES the instruction from PROM and EXECUTES. Random access memory (RAM), which can be used for both READ and WRITE operation can also be used for storing the programme or any data. The CPU and other devices communicate with each other on a bi directional bus.

Each Central processing unit has a set of instructions associated with it which can be broadly classified into the following three categories :

(a) <u>Transfer instructions</u> : These set of instructions are required to affect transfer of information between the three components of the microprocessor system i.e. CPU memory and Input/Output ports.

(b) <u>Accumulator group instructions</u> : These instructions are required to carry out arithmatic and logic operations like addition, subtraction; AND, EXOR, comparision etc. inside CPU, on the data which has been transferred inside CPU at an earlier stage.

(c) <u>Control instructions</u> : The programme instructions are arranged in the memory in the order of their execution. A program counter, inside CPU is normally

incremented by one to recall the instructions one by one from the memory. The control instructions are required to alter the normal recalling of instructions to the CPU.

## 3.02 ARCHITECTURE OF CENTRAL PROCESSING UNIT :

The heat of the microprocessor based system is the central processing unit. In the following paragraphs is defined the architecture of a typical CPU Intel 8008 which is simpler and easier to understand. The other CPU's essentially follow the same architecture with few changes here and there.

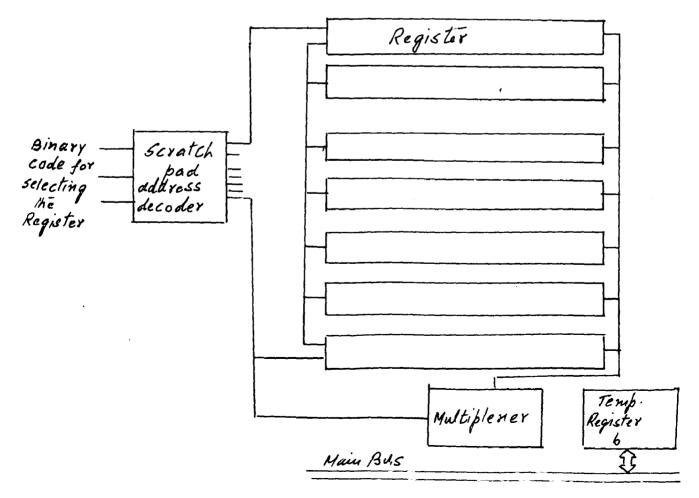

<u>Scratch pad registers</u> : CPU contains 7 nos. of scratch pad registers each of 8 bit length. The registers are labelled as A,B,C,D,E,H and I. Each register is a signed a three bit binary code; which can be used to address any register. The codes as used in Intel 8008 CPU are given below :

| Register            | Binary code | Register | Binary Code |

|---------------------|-------------|----------|-------------|

| A                   | 000         | E        | 100         |

| B. B. S. B. Starter | 001         | H        | 101         |

| Ċ                   | 010         | L        | 110         |

| D                   | 011         | H-LL     | 111         |

A separate code has been provided for addressing H-L pair of registers, which can be used to store data of 16 bit length in the CPU.

#### 3.03 INSTRUCTION SET

As described earlier the complete set of instructions can be divided into the following three categories :

1. Transfer instructions

2. Accummulator group instructions

3. Control instructions

Each instruction is represented in the short form called Mnemonic.

#### 3.03.1 TRANSFER INSTRUCTIONS

(a) Data transfer inside CPU : An instruction to transfer the content of scratch pad register B to register D is shown below :

| MOVD,B   | 1 1 1 · · · · · · | 011          | 001        |

|----------|-------------------|--------------|------------|

| Mnemonic | op code for the   | Code for the | Code for   |

|          | move instruction  | destination  | source     |

|          | · · · · · ·       | register     | register B |

(b) <u>Data transfer from CPU to memory</u>: Whenever the memory has to be addressed it needs a 16 bit address ( 8 bit low order and 6 bit high order and 2 bit control code with the high order address). In order to transfer the data from CPU to memory first the memory address from the CPU has to be sent to the memory. This memory address is stored in H-L pair of registers by a preceeding instruction. An instruction to transfer the data from scratch pad register C to memory is shown below :

| MOVM,C   | 11                          | 010                | 111                           |

|----------|-----------------------------|--------------------|-------------------------------|

| Mnemonic | op code for<br>move instru- | Code for<br>reg. C | Code to recall<br>H-L pair of |

|          | ction                       |                    | register 1.                   |

(c) <u>Data transfer from memory to CPU</u>: In this case also the memory address, where the data is available, is preloaded in H-L pair of registers by a preceeding instruction. A typical instruction is shown below : Mnemonic op code code for 'D' Code for memory M O V D,M 11 011 111 The operation content of memory moved to register D is shown symbolically as  $(D) \leftarrow (M)$ .

(d) <u>Immediate data instructions</u> : The move instruction (CPU memory) described earlier needed preloading of H-L pair of registers with the memory address. The move immediate instructions are 2 byte instructions; designed to eliminate the preloading of H-L pair of registers.

| Mnemonic | op code | destination | op code |

|----------|---------|-------------|---------|

| MVI B    | 0 0     | 001         | 110     |

| Data     | bb      | b b b       | bbb     |

The operation in the symbolic form is shown below :

$(B) \leftarrow (Data)$

Here the data to be transferred from the memory to CPU is stored in the program itself, in a location which is next to the instruction. It can also be seen that there is no source for the more immediate instruction. Hence the last three bite, normally reserved for the source code, have also been used to specify the op code. Move immediate instructions be used to store data directly in memory.

| Mnemonic | op | code | <br>code | for | memory |    | op | code |

|----------|----|------|----------|-----|--------|----|----|------|

| MVIM     | 0  | 0    | <br>     | 1 1 |        | ,  | 1  | 10   |

| DATA     | b  | b    |          | bb  | b      | ۰. | b  | bb   |

In this case the source and destination both are in the memory. The data stored in the program has to be transferred to some other location in the memory whose address has been preloaded in H-L pair of registers.

(e) Increment and decrement instructions for the scratch

pad registers : The formats for the above two

instructions are given below :

I N B 0 0 0 0 1 0 0 0

D C D 0 0 0 1 1 0 0 1

The opertions are as shown below i

$(B) \leftarrow (B) + 1$  $(D) \leftarrow (D) - 1$

#### 3.03.2 ACCUMULATOR GROUP INSTRUCTIONS :

The scratch pad register a serves as the accumulator, Accumulator is also the destination register for accumulator group instructions. Hence the space allotted for destination code becomes part of the op code. The general format of the accumulator group instructions is as given below :

| op | code | Function | Source |

|----|------|----------|--------|

| b  | b    | b b b    | bbb    |

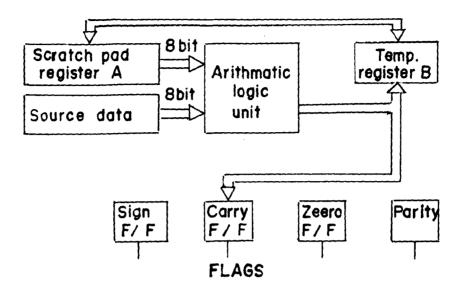

The central processing unit contains an Arithmatic logic unit for carrying out the arithmatic and logic operations.

The arithmatic logic unit in Intel 8008 can do the following operations :

a. Addition

b. Subtraction

c. Logic functions AND,

EXCLUSIVE OR, OR and Compare.

The data in the source register are operated on by the arithmatic logic unit and the result is stored back in the accumulator. The source register could be either a scratch pad register or a register in the memory.

Several types of questions can be asked about the content of accumulator, and the answer to those questions are indicated by FLAGS. The arithmatic logic unit of Intel 8008 permits the following four flags.

<u>SIGN</u>: The most significant bit (MSB) of the 8 bit word indicates the sign. The SIGN flag is TRUE or ON when the MSB of the word stored in accumulator is '1'. The magnitude of the word is given by the remaining 7 bits.

<u>CARRY</u> : Consider the case when two words of 8 bits are added and the result is a 9 bit word or in other words a 'carry' is generated. Similarly consider the case when a larger number is subtracted from a smaller number and a 'Borrow' is generated. In both the conditions 'CARRY' flag is true. ZERO : The zero flag is TRUE when the content of the accumulator is zero.

<u>PARITY</u>: When the word in accumulator contains even number '1'; the parity flag is TRUE.

The accumulator group instructions for Intel 8008 are summarised in Table

| Mnemonic | Format     | Function                                                                                          | Comment                            |

|----------|------------|---------------------------------------------------------------------------------------------------|------------------------------------|

| ADD r    | 10 000 SSS | $(A) \leftarrow (A) + (r)$                                                                        | r is unaffected                    |

|          | 10 000 111 | $(A) \leftarrow (A) + (M)$                                                                        | Memory address is preloaded in H-L |

| ADI      | 00 000 111 | $(A) \leftarrow (A) + (data)$                                                                     | 2 byte instruction                 |

|          |            | a<br>1995 - Alexandria Alexandria<br>1996 - Alexandria Alexandria<br>1997 - Alexandria Alexandria |                                    |

In the above addition operation carry is not taken into account :

| مشينية.<br>م | ADC r    | 10 001 SSS | $(A) \leftarrow (A) + (r) + (c)$    |  |

|--------------|----------|------------|-------------------------------------|--|

|              | ADC M    | 10 001 111 | $(A) \leftarrow (A) + (M) C (c)$    |  |

| e e tra      | ACI data | 00 001 100 | $(A) \leftarrow (A) + (Data) + (c)$ |  |

In the above operations carry bit as indicated by the carry flag is also added.

| ,<br>,<br>, | SUr            | 10 010 SSS                   | $(A) \leftarrow (A) - (x)$                               |

|-------------|----------------|------------------------------|----------------------------------------------------------|

| , .         | SUM            | 10 010 111                   | $(A) \leftarrow (A) - (M)$                               |

| ,,          | SUI            | 00 010 100<br>(B2)           | $(A) \leftarrow (A) = B$                                 |

| -           | SBr            | 10 010 SSS                   | $(A) \leftarrow (A) - (r) - (borrow)$                    |

|             | SBM            | 10 011 111                   | $(A) \leftarrow (A) - (M) - (borrow)$                    |

|             | Mnemoic<br>SBI | Format<br>00 011 100<br>(82) | Function Comments $(A) \leftarrow (A) - (B2) - (borrow)$ |

-- 17

18

| ANDE | 10 100 SSS         | (A) + (A). (r)                      | • . •                                                                                                              |

|------|--------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| ANDM | 10 100 111         | (A) ← (A). (M)                      | AND                                                                                                                |

| ANDI | 00 100 100         | (A) ← (A). (B2)                     | <b>Öperation</b>                                                                                                   |

| XRr  | 10 101 SSS         | (A) = (A) ④ (r)                     | Exclusive                                                                                                          |

| XRM  | 10 101 111         | $(A) \leftarrow (A) \oplus (M)$     | OR                                                                                                                 |

| XRI  | 00 101 100         | $(A) \leftarrow (A) \bigoplus (B2)$ | Operation                                                                                                          |

| ORr  | 10 110 SSS         | $(A) \leftarrow (A) + (r)$          | OR                                                                                                                 |

| ORM  | 10 111 0111        | $(A) \leftarrow (A) + (M)$          | Operation                                                                                                          |

| ORI  | 00 110 100         | $(A) \leftarrow (A) + (B2)$         |                                                                                                                    |

| CPr  | 10 111 555         | (A) - (r)                           | Compare                                                                                                            |

| СРМ  | 10 111 111         | (A) - (M)                           | operation                                                                                                          |

| CPI  | 00 111 100<br>(B2) | (A) - (B2)                          | The result of the<br>substruction operatio<br>is not loaded back<br>in accumulator. HENCE<br>(A) remains unchanged |

In compare operation; the function is indicated against each operation is carriedout and the result is stored in accumulator. It is possible to obtain separate indications for the following three conditions; by testing appropriate flags as indicated against each condition.

| (A) | > | (Source) | Zero | ·     | Carry<br>0 |

|-----|---|----------|------|-------|------------|

| (A) | ۷ | (Source) | 0    | · · · | 1          |

| (A) | = | (Source) | 1    |       | 0          |

### Rotate accumulator instructions :

These instructions can be used to shift the content of the accumulator either alone or within the carry bit; to the right or to the left by one bit.

| RAL, RAR | C       | AD     | A1             | A2                | AЗ   | A4                | AS                  | A6                | A7  |                |     |

|----------|---------|--------|----------------|-------------------|------|-------------------|---------------------|-------------------|-----|----------------|-----|

| Rot      | ate wit | h carr | Y              |                   |      |                   |                     | · .               |     |                |     |

| RLC, RRC | C       | AD     | At             | A                 | 2    | A3                | A4.                 | A5                | A6  | A7             | ]   |

| Rot      | ate wit | hout c | arry           | •                 |      |                   |                     | ۱                 |     |                | -   |

| The      | instru  | ctions | are            | sum               | nari | sed               | belo                | W 87              | . e | · · ·          |     |

| Maemonic | Ē       | ormat  | 199 <b>.</b> - |                   | Fund | tion              |                     | ورية<br>الأرب الم | Com | nents          |     |

| RLC      | 00 0    | 00 010 | • • • •        | (A)<br>(A)<br>(C) | 0) é | (A7<br>(A7        | 9                   |                   | Shi | ft le:         | ft  |

| RRC      | 00 0    | 01 010 |                | (A                | 7) e | AM-<br>(AO<br>) ← |                     | tan tan           | Shi | t ri           | ght |

| RAL      | 00 0    | 10 010 |                | (A)               | 0) 🖛 | ← (<br>(Ca<br>) ← | Am)<br>IIY)<br>(A7) |                   |     | ft le:<br>car: |     |

| RAR      | 00 0    | 11 010 |                | - (A              | 7) & | (Am<br>(Ca        | rry)                |                   |     | t ri<br>1 car  |     |

### 3.03.3 CONTROL INSTRUCTIONS :

As explained earlier the program counter, a 14 bit register; stores the address of the next byte to be brought to the CPU. The program counter is normally incremented by 1, after each byte is fetched. The control instructions can alter the content of the program counter. The following instruction are included in the set of control instructions. a. Unconditional JUMP

b. Conditional JUMP

c. CALL and RETURN instructions

(a) <u>UNCONDITIONAL JUMP</u> : The format and the function is as shown below :

| Mnemonic | Format     | Function            |

|----------|------------|---------------------|

| JMP      | 01 xxx 100 | (PC) (B3) (B2)      |

|          | (82)       | 1,e. B2, B3 entered |

|          | (B3)       | in program counter. |

It is a 3 byte instruction. The next instruction to be brought to the CPU shall be from memory location whose lower order address is (B2) while the higher order address is (B3). In the execution phase of the instruction the content of program counter PC is replaced by (B3)(B2).

(b) <u>CONDITIONAL JUMP</u> : These are also 3 byte instructions. The instructions along with their function are summarised below :

| Mnemonic | Format         | Function                   |

|----------|----------------|----------------------------|

| JTc      | 01 1 C4 C3 000 | Jump to location (B3) (B2) |

|          | (B2)           | if the condition flag is t |

|          | (B3)           |                            |

| JFc      | 01 0 C4 C3 000 | Jump to location B3,B2 if  |

| ·        | (B2)           | condition flag is flase.   |

|          | (B3)           |                            |

In the earlier sections four conditions flags i.e. zero carry, parity and sign were discussed. Each flag is specified by two control bite C4 C3 which are as given in the following Table

| FLAG   | TRUE CONDITION                      | C4 C3 | Mnemonic |

|--------|-------------------------------------|-------|----------|

| ZERO   | When (A) is zero                    | 00    | JTZ      |

| CARRY  | When there is overlow or underflow. | 01    | JTC      |

| PARITY | Even number of 1's in (A)           | 10    | JTP      |

| SIGN   | When A7 or MSB is 1 in (A)          | 11    | JTS      |

(c) <u>CALL INSTRUCTION</u> : Call instruction is different from the jump instructions defined above. Whenever a call instruction comes, the contents of program counter are saved in a special memory inside CPU called the STACK, so that one can return to the main program after executing the Call subroutine. The Call instruction is also a 3 byte instruction. Therefore if first byte of the CALL instruction is located at (PC); then (PC) + 3 may have to be saved in order to come back to the main program after executing the subroutine. The typical CALL and RETURN instructions are shown below :

UNCONDITIONAL CALL INSTRUCTION :

| Mnemonic | Format     | Function         |  |  |

|----------|------------|------------------|--|--|

| CALL.    | 01 xxx 110 | Stack (PC)       |  |  |

|          | (B2)       | (PC) 👝 (B3) (B2) |  |  |

| ·        | (B3)       | •                |  |  |

Let  $(PC) = x_2$  where the first byte of CALL instruction is stored. When the third byte of the CALL instruction is brought to CPU, (PC) = X + 2. At this stage, program counter as usual shall be incremented by 1, i.e. (PC) = X + 3. Now the program counter contents shall be saved in a special memory called STACK, and the program counter shall be loaded with B3; B2 which is the address of the first instruction of the subroutine.

and the second sec

• . · · · · · · ·

### CONDITIONAL CALL INSTRUCTIONS :

| Mnemonic | Format        |

|----------|---------------|

| CTc      | 01 104 03 010 |

|          | B2            |

|          | <b>B3</b>     |

| CFc      | 01 004 03 010 |

|          | B2            |

|          | B3            |

In case of CTc; if the flag c is true i.e. (c) = 1 then, the next two byte of instruction are brought to the CPU, and specified functions will follow. Otherwise the data bytes B2; B3 will not be brought to the CPU, and the instruction stored at (PC) + 3 shall be brought to the CPU for execution. (d) <u>RETURN INSTRUCTIONS</u> : The CALL and RETURN instructions are operated in pair. The RETURN instructions are summarised as below :

| Mnemonic | Format        | Function                   |

|----------|---------------|----------------------------|

| RET      | 00 xxx 111    | (PC) $\rightarrow$ (Stack) |

| RTc      | 00 1 C4C3 011 | If $(C) = 1$ then          |

| х · ·    |               | (PC) ->(Stack) otherwis    |

|          |               | (PC) ->(PC) + 1            |

| RFC      | 000 C4C3 011  | If $(C) = 0$ then          |

|          |               | (PC) ->(Stack) otherwis    |

|          |               | (00) (00) 4                |

In case of conditional return instructions, if conditions are satisfied, the program counter content PUSHED in stack, is POPPED OFF from the stack and stored in program counter, to enable the CPU to return to the main programme. If conditions are not satisfied, the next instruction in the subroutine is executed.

(e) <u>HALT INSTRUCTION</u> : This instruction causes the CPU to go in STOPPED state and remain there until receipt of an INTERRUPT signal.

| Mnemonic | Format     | Function          |  |  |

|----------|------------|-------------------|--|--|

|          | 00 000 00x | (PC) -> (PC) + 1  |  |  |

|          | 11 111 111 | CPU Stopped state |  |  |

The program counter points to the next instruction.

#### 3.03.4 PROGRAM COUNTER :

The memory addresses where the current instruction is available, is stored in a special register called Program counter. The program counter is a 14 bit wide register. The memory addresses is 14 bit wide and consists of a 6 bit Higher order address and a 8 bit lower order address. The memory address is sent to the memory on 8 bit wide bus in two parts. First the 8 bit lower order address and then the 6 bit higher order address is sent. The balance two bits in the high order address are called the control bits. The control bits occupying D6, D7 positions in the data bus decide the control cycle of the CPU.

#### 3.04 <u>CENTRAL PROCESSING UNIT ON A CHIP</u> :

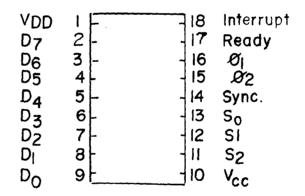

Intel 8008 microprocessor chip is shown in fig. 3.4

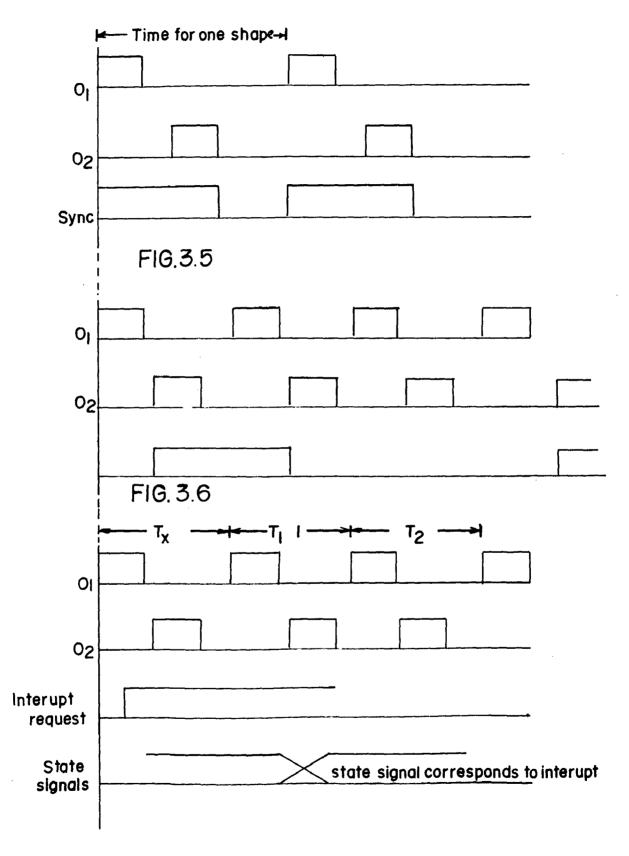

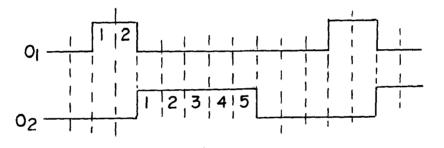

The CPU required two clock  $\phi_1$  and  $\phi_2$  and sync pulses at the SYNC terminal from a clock generator for synchronization of the complete system. The pulses at  $\phi_1$ ,  $\phi_2$  and SYNC. are shown in fig. 3.5.

#### Instruction cycle and machine cycles :

The time required to fetch and execute an instruction is called the Instruction cycle.

Every Instruction cycle consists of a number of machine cycle. A machine cycle is required each time the CPU access the memory or an I/o part.

Each machine cycle consists of a number of states (T1 to T5). The time period of each state is determined by the time period of clock pulses  $\emptyset_1$  and  $\emptyset_2$ . Begining of a new machine cycle is synchronized with the rising edge of  $\emptyset_1$  in state T1, which is also the first state of any machine cycle.

#### Execution of an instruction :

A basic instruction cycle consists of two phases :

1. FETCH Phase

2. EXECUTE Phase.

States T1 and T2 of any machine cycle are associated with the FETCH phase. The state T3 is reserved for actual transfer of data. The states T4 and T5 are reserved for actual execution of the instruction inside the CPU. The 8 bit low order address to the memory is sent during T1, while the 8 bit high order address is sent during T2. The type of machine cycle is indicated by the control bits D6 D7 sent during T2 along with high order address. The function performed in each machine cycle and the control bits assigned to them are shown in the table given below:

| D6 D7 | Cycle code | Function performed               |

|-------|------------|----------------------------------|

| 00    | PCI        | READ Ist byte of instruction     |

| 0 1   | PCR        | READ additional byte of instruct |

| 10    | PCC        | Designate the data as I/O comman |

|       | PCW        | WRITE the data bits in memory    |

ł

The control bits are used by external circuitry to provide MEMORY WRITE And MEMORY READ Command.

Consider - for example the execution of MOVD, M instruction.

|      | Type of<br>machine<br>Cycle | State      | Operation                                         |

|------|-----------------------------|------------|---------------------------------------------------|

| •    |                             | TI         | Low order address of the<br>instruction to memory |

| M1   | PCI                         | T2         | High order address of the                         |

|      |                             |            | instruction to memory                             |

|      |                             | T3         | Instruction MOV D;M brought                       |

| • •  |                             |            | to CPU                                            |

| · ·  |                             | T          | (L) sent to memory                                |

| Ţ    |                             | T2         | (H) sent to memory                                |

| M2   | PCR                         | <b>T</b> 3 | Data read from memory and sent<br>to CPU bus      |

| •• . |                             | <b>T4</b>  | Data latched in temp.reg.b                        |

|      | L                           | T5         | (b) transferred to D                              |

$(M_{A_{1}}) = (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) + (1 + 1) +$

--- 25

As apparent the Instruction cycle consists of two machine cycles (PCI and PCR). PCI cycle consists of only 3 states, while PCR cycle consists of five states. A machine cycle always begins with state Ti.

Beginning of a new state coincides with the rising edge of  $\phi_1$ . The rising edge of SYNC pulse coincides with the rising edge of  $\phi_2$ . SYNC pulse identifies the first state Ti in every machine cycle.

The internal state of the CPU is indicated at 50,51 and 52 terminals. These state signals are also used to synchronise the entire system. The state signals at 50, 51, 52 for various states are shown below :

| 50 | <b>S1</b> | <b>S2</b> | State                  |

|----|-----------|-----------|------------------------|

| 0  | 1         | 0         | Ti Low order address   |

| 0  | 1         | 1         | TII CPU interrupted    |

| 0  | 0         | 1         | T2                     |

| 0  | 0         | 0         | Walt, memory not ready |

| 1  | Ő         | Ö         | ТЗ                     |

| 1  | 1         | 0         | Stopped * Halt* state  |

| 1  | 1.        | 1         | <b>T4</b>              |

| 1  | 0         | 4         | <b>T</b> 5             |

(a) <u>INTERRUPT</u> : Many real world situations like power failure; human decisions etc. require forced entry of instructions in CPU. An interrupt signal (active high) at the Interrupt terminal of CPU interrupts the normal flow of program. After the interrupt needs of the external system have been met, the

normal flow of programme resumes. Since interrupt request comes from the external circuit, it may appear in the middle of an instruction. In such a case the CPU completes the current instruction and then acknowledges the receipt of interrupt request through the state signals (SO,S1,S2). That is once the current execution is over, the machine cycle to follow has its first state designated as TH. The program counter at this stage points to the next instruction in the normal programe.

At this point a special instruction called RESTART instruction is zammed into CPU by the external device requesting the interrupt.

Mnemonic

| RST | 00 AAA 101 | $(Stack) \leftarrow$ | (PC)       |

|-----|------------|----------------------|------------|

|     |            | (PC) <-              | 000 000    |

|     |            |                      | 00 AAA 000 |

The Restart instruction, allows the CPU to obtain the programme to be executed during the Interrupt period from memory location whose address has been loaded in the program counter during the execution of Restart instruction. The last instruction in the interrupt subroutine a is a Return instruction; which allows the normal program flow to resume.

(b) <u>WAIT STATE</u>: When memory is presented with address; it takes some time to output or Input the data. In slower memories; if this time, also known as the access time; is larger than the time of one state, the memory can request a wait state to the CPU, by pulling the READY line low. Since the request is coming from memory, the request can be synchronised with the  $\phi_2$  pulse during T2, that is when addresses have been transmitted and they have been allowed sufficient time to stabilise. The CPU responds by outputting state TW, instead of state T3. In the wait state CPU idles. The CPU comes out of the WAIT state, when the Ready line goes high during a  $\phi_2$  pulse. CPU acknowledges the receipt of signal on Ready line through state signals.

3.1 ARCHITECTURE OF CENTRAL PROCESSING UNIT :

The architecture of Intel 8080 is different from Intel 8008 in the following manner :

(a) Intel 8080 also has the same number of scratch pad registers (A, B, C, D, E, H, L). However the codes for them are different. In 8008 only scratch pad H and L registers could be accassed together, while in 8080 B and C; D and E and H and L registers can be accessed in pairs.

|           | Codees f | or Registers | Codes fo                                                                                                                                                                                                                           | or Register pairs                     |

|-----------|----------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

|           | A        | 111          | B-C                                                                                                                                                                                                                                | 00                                    |

|           | В        | 000          | D-E                                                                                                                                                                                                                                | 01                                    |

|           | c        | 001          | H-L                                                                                                                                                                                                                                | 10                                    |

|           | D        | 010          | SP                                                                                                                                                                                                                                 | 11                                    |

|           | E        | 011          | Ťoh                                                                                                                                                                                                                                | ole 2                                 |

|           | H        | 100          | Idk                                                                                                                                                                                                                                |                                       |

| • · · · · | Ľ        | 101          |                                                                                                                                                                                                                                    | •                                     |

|           | Tabl     | e 1          | a di seconda di second<br>Seconda di seconda di se | i i i i i i i i i i i i i i i i i i i |

(b) The last entry in Table 2 is for a register called stack pointer. Intel 8080 has the sack stack memory located inside An external Random access memory addressed from the stack pointer; a 16 bit register stores the address of the memory location filed last.

(c) Intel 8080 has a seperate 16 bit bus for sending the memory address, besides the 8 bit data bus.

(d) There are five flags in Intel 8080. The additional flag is called auxiliary. Which can be understood with the following example.

Intel 8080 has any instruction called D A A which is defined as below:

| Mnemonic | Code |     |     |  |

|----------|------|-----|-----|--|

| DAA      | 010  | 111 | 111 |  |

The Decimal adjust accumulator operation is defined to adjust the eight bit number in the accumulator to form bit numbers The instruction is useful while working with decimal numbers.

Consider the following example :

| 5,7  | •        | 0 | 1 | 0 | 1   | 0   | 1 | 1 | 1 |  |

|------|----------|---|---|---|-----|-----|---|---|---|--|

| 7.6  |          | 0 | 1 | 1 | 1   | ,0  | 1 | 1 | 0 |  |

| 13.3 | Add 6 to | 1 | 1 | 0 | 0 ' | · 1 | 1 | 0 | 1 |  |

|      | readjust | 0 | 0 | 0 | 0   | 0   | 1 | 1 | 0 |  |

|      |          | 1 | 1 | 0 | 1   | 0   | 0 | ĺ | 1 |  |

When the value of least significant 4 bits is more than 9, as in the above case, the readjustment can be done by

adding 6 to the least significant bits.

The most significant 4 bits are also adjusted in the same manner except that the carry flag is checked instead of the auxiliary carry flag.' The flags and their codes are shown in the following table.

|   | Flag        |   | c <sub>5</sub> | с <sub>4</sub> | с <sub>3</sub> |

|---|-------------|---|----------------|----------------|----------------|

|   | NOT ZERO    | - | Ö              | 0              | 0              |

|   | ZERO        |   | 0              | 0              | 1              |

|   | NO CARRY    |   | 0              | 1              | 0              |

|   | CARRY       |   | 0              | 1              | 1              |

| 4 | PARITY ODD  |   | 1              | 0              | 0              |

|   | PARITY EVEN |   | 1              | 0              | 1              |

|   | PLUS        |   | 1              | 1              | 0              |

|   | MINUS       |   | 1              | 1              | 1              |

the following:

The auxiliary carry flag cannot be specified. The most significant bit indicates the sign of the number. <u>Intel 8080 CPU CHIP</u> is a 40 pin device which is used for

| Designation             | Number of pins | Remark                  |

|-------------------------|----------------|-------------------------|

| Ao to A15               | 16             | Address bus             |

| $D_0$ to $D_7$<br>+ 12V | 8              | Data bus                |

| + 5V<br>- 5V            | 4              | Power supply and ground |

| and                     |                |                         |

| READY                   |                |                         |

| er<br>Anti-             |                |                         |

ч. .,

| Total      | al ten. '                             | 40 pins | н              |

|------------|---------------------------------------|---------|----------------|

| HALDA      | s.<br>Anno a chuirte Albhana an Airte | 1<br>4  |                |

| WAIT       |                                       | •<br>•  | 1 - 2 - 4<br>  |

| SYNC       |                                       |         |                |

|            |                                       | 6       | Control output |

| DBIN<br>WR |                                       |         |                |

| INTE       |                                       |         |                |

| HOLD       |                                       |         | · · ·          |

| RESET      |                                       |         |                |

| CLOCKS     |                                       | 6       | Control inputs |

| INT        |                                       |         |                |

Intel 8080 has a seperate 16 bit address bus which is loaded by the memory address. The addresses remain stable until the Ist pulse after  $T_3$ .

## TYPES OF MACHINE CYCLE AND STATUS WORD

The following types of machines cycles may occur within an instructions in Intel 8080.

| (1)  | FETCH INSTRUCTION | •<br>                 | Same as PCI of 8008                                                                                                                                    |

|------|-------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| (2)  | MEMORY READ       | *                     | Same as PCR of 8008                                                                                                                                    |

| (3)  | MEMORY WRITE      |                       | Same as PCW of 8008                                                                                                                                    |

| (4)  | STACK WRITE       |                       |                                                                                                                                                        |

| (5)  | STACK READ        | . *                   |                                                                                                                                                        |

| (6)  | INPUT             |                       | ,                                                                                                                                                      |

| (7)  | OUTPUT            | ° <b>₿</b> °<br>• N N | Same as PCC of 8008                                                                                                                                    |

| (8)  | INTERRUPT         | . <b></b>             |                                                                                                                                                        |

| (9)  | HALT              |                       |                                                                                                                                                        |

| (10) | HALT.INTERRUPT    |                       | a da anti-arresta a constructiones.<br>A constructiones a constructiones de la construction de la construction de la construction de la construction d |

The cycles at 4,5,8,9 and 10 are additional. Since 8080 has a seperate address bus, data bus is free during  $T_1$  and  $T_2$ .

<u>Status Signal</u>: The data bus  $D_0$  to  $D_7$  is also used to transmit status information which indicates the external circuitary the type of machine cycle currently running at any time in the CPU.

The status information is available on the bus during first state i.e.,  $T_1$  of every machine cycle and during the SYNC internal. The data bus is available free during  $T_1$  and  $T_2$  for such an operation. Each data bit is assugned a specific function which are detailed below:

| Bit            | Symbol | Definition                                                                                                                                        |

|----------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Do             | INTA   | Acknowledge signal for interrupt request. The<br>signal is used to latch a RESTART instruction<br>when DBIN is active.                            |

| D <sub>1</sub> | WO     | Indicates a WRITE memory or OUTPUT function,<br>otherwise a READ MEMORY or INPUT Operation<br>will be executed.                                   |

| <sup>D</sup> 2 | STACK  | Indicates that the address bus holds the pushdown stack address from the stack pointer.                                                           |

| D3             | HLTA   | Acknowledge signal for HALT instruction                                                                                                           |

| D <sub>4</sub> | OUT    | Indicates that the address bus contains the address of an output device.                                                                          |

| D <sub>5</sub> | MI     | CPU is in the fetch cycle for the first byte<br>of an instruction.                                                                                |

| D <sub>6</sub> | INP    | Indicates that the address bus contains the<br>address of an input device and input data<br>can be placed on the data bus when DBIN is<br>active. |

| D7             | MEMR   | The data bus will be used for memory read data.                                                                                                   |

.

<u>Control inputs and Outputs and SYNC</u>: A set of non-overlapping pulses  $(\phi_1, \phi_2)$  are used to synchronise all the operations. The rising edge of  $\phi_1$  is the beginning of new state. The SYNC pulse output from the CPU identifies the beginning of a new machine cycle. SYNC pulse is triggered by the rising edge of  $\phi_2$  and ends with the rising edge of  $\phi_2$  in the next state.

<u>Ready and Wait</u>: When READY to CPU is made low, the CPU goes in the WAIT state. As long as the ready input is low the processor remains in the wait state TW. Ready input is used essentially by slow memories which take more time to output. However, the request must be received during state  $T_2$  to enable the CPU to acknowledge the request by outprinting WAIT signal. The WAIT signal will get reset during state  $T_2$ .

<u>INT and INTE</u>: Interrupt request is asymphronous and may originate at any time. The request is however acknowledged if it persists till INTE signal appears; in the last state of a cycle. Once this happens an interrupt m-achine cycle follows which is a normal machine cycle with five states. As usual the status word is transmitted on data bys; which however accompanied k an INTA status bit. This signal can be used by the external device to jam a RESTART instruction during  $T_3$  which tells the processor the location of the programme.

<u>DBIN</u>: DBIN signal from microprocessor is used by external devices to enable the transfer of the data to CPU. The signal is available in the following machine cycles.

1. FETCH

2. MEMORY READ

# 3. STACK READ

4. INTERRUPT : for reading the Restart instruction from the external device.

DBIN is initiated by the rising edge of  $\phi_2$  during state T<sub>2</sub> and terminated by the corresponding edge of  $\phi_2$  during T<sub>3</sub>. Any TW state, between T<sub>2</sub> and T<sub>3</sub> will therefore extend DBIN by one or more clock periods.

WR : Similar to DBIN, CPU generates a WR signal which can be used by the external devices to enable transfer of data from CPU during  $T_3$ . The signal is available in the following machine cycles. The leading edge of WR signal is synchronized by the leading edge of  $\phi_1$  in a state following  $T_2$  and the trailing edge of WR signal with the leading edge of  $\phi_1$  in a state following  $T_3$ .

#### CHAPTER 4

#### MICROPROCESSOR BASED SYSTEM DESIGN

4.1 HARDWARE DESIGN

#### 4.1.1 MICROPROCESSOR SYSTEM

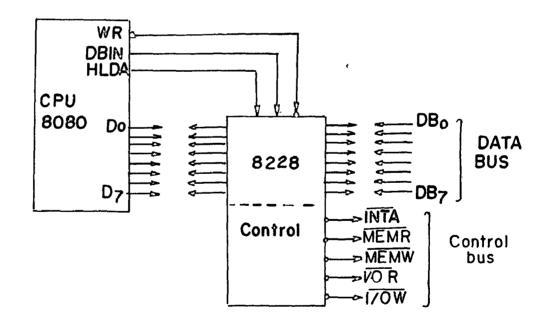

A micro-computer system using INTEL 8080 would consist of the following components.

- <u>Central Processing Unit chip 8080</u> ; Which is heart of the system.

- 2. <u>Clock generator 8224</u> : Which provides nonoverlapping clock pulses  $\phi_1$ ,  $\phi_2$  to the C.P.U.

- 3. <u>System Controller 8228</u> : Which buffers the data bus and also provides control signal (control bus 6 bit wide) using status word form data bus and DBIN,WR, HLDA from C.P.U.

- 4. <u>Address bus buffers (optional) 8212</u> : The address bus can not provide sufficient current and hence the address bus has to be buffered. Intel 8212 load the address bus by 0.25 mA and provide a maximum loading of 75 mA at its output terminals.

- 5. Programmable Read only memories PROMS.

- 6. Random access memories RAMS

- 7. Input/Output interface devices

- (a) 8251 for interfacing with teletype CRT, terminal etc.

(b) 8255 for interfacing with a A/D converter.

- 8. <u>Programmable Interrupt controller</u> (8259, 8214): To manage the interruption of C.P.U. by a number of devices and to latch RESTART instruction.

9. <u>Programmable DMA controller (8257)</u> : To manage DMA service for a number of periplreal devices.

Description of Individual block :

1. <u>Central Processing Unit</u> :

CPU 8080 has been described earlier.

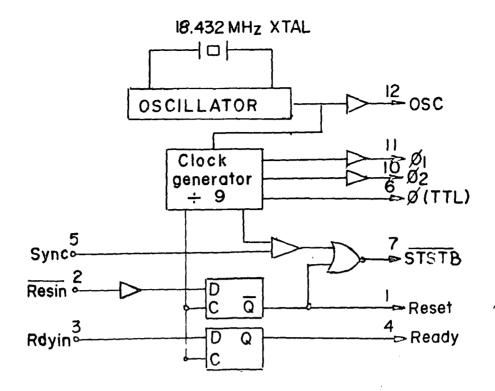

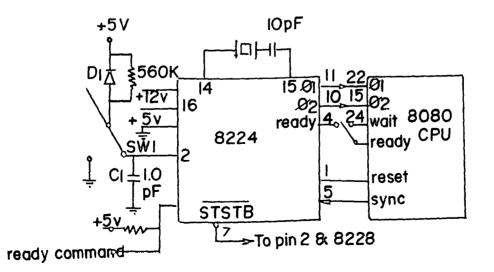

2. <u>Clock Generator (8224)</u> : (?Ref. fig. 4.1.2)

Oscilator frequency is 9 times the speed at which the microprocessor has to be run. The clock period (tcy ) is specified for the microprocessor. Consider, for example, 8080 A CPU chip for which tcy can be from 0.48 H Sec to 2.0 M Sec.

Considering the fastest speed, i.e.  $t_{0} = 0.48$  micro-second.

Crystal frequency =  $\frac{1}{0.48}$  x 9 MHz = 18.8 MHz

Standard crystal of 18.432 MHz is available which gives a tcz = 0.49 micro second.

Clock generator consists of a devide by 9 counter whose four outputs  $Q_A$  to  $Q_B$  are combined in logic gates to obtain  $p_1$  and  $p_2$  clock pulses for CPU which are shown in fig. 4.1.3.

$\emptyset_2$  TTL available at pin 6 which is similar to  $\emptyset_2$  except for a small delay, can be used for external timing purposes. It is especially useful in DMA dependent activities.

$\phi_2$  (TTL) can be used to gate the requesting device on the bus once CPU issues HOLD ACKNOWLEDGE (HLDA) signal.

12

The clock generator also generates STSTB (status strobe) signal which is used to latch the status word on the control bus peger Fig. 4.1.4. The control bus is connected to the data bus through the SYSTEM CONTROLLER (8228). The states signal is available on the data bus during the SYNC pulse.

Automatic system reset feature on power on can be incorporated by adding components  $R_1$ ,  $C_1$  and  $D_1$  in the circuit. The  $\overline{\text{RESIN}}$  input to the Reset flip is through a Schmidt trigger which converts the slow transition into a clean fast edge for triggering the D flip flop.

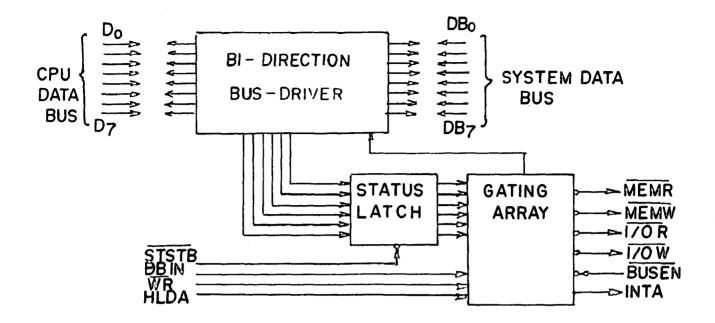

3. System Controller (8228) : (Ref. Fig. 4:1.5 and 4.1.6)

System controller generates all control signals required to directly interface RAM, ROM, and I/O components.

An eight-bit, bidirectional bus driver buffers the data bus from memory and Input/Output devices. Data bus which has an input requirement of 3.3 volts (min.) and can drive (sink) a maximum current of 1.9 mA is assured by data bus driver to fulfil these input requirement even in enhance moise immunity. Due to the availability of adequate driving current (10 mA typ.) on the system side of the driver, a large number of memory and I/O devices can be directly connected to the bus.

When STSTB input goes low, the status information that is issued by CPU to its data bus at the beginning of each machine cycle gets stored in the status Latch.

The Gating Array generates control signals (MEMR, MEN W, I/OR, I/OW and INTA) by gating the outputs of the status Latch with signals from the 8080 CPU (DBIN; WR and HLDA).

The BUSEN (Bus Enable) input to the Gating Array is an asychronous input that forces the data bus output buffers and control signal buffers into their high-impedance state if it is a 'one'. If BUSEN is a 'zero' normal operation of the data buffer and control signals take place.

# Programmable Communication Interface (8251) :

It is used as a peripheral device and is programmed by CPU to operate using virtually any serial data transmission technique. Its functional configuration is programmed by the system's software for maximum flexibility.

In the problem, a CRT is used which communicate with CPU through this interface.

### Programmable peripheral interface (PPI 8255) :

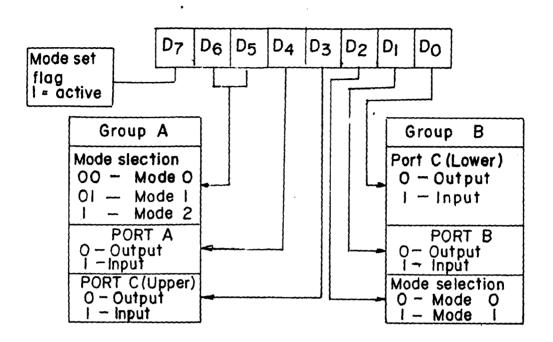

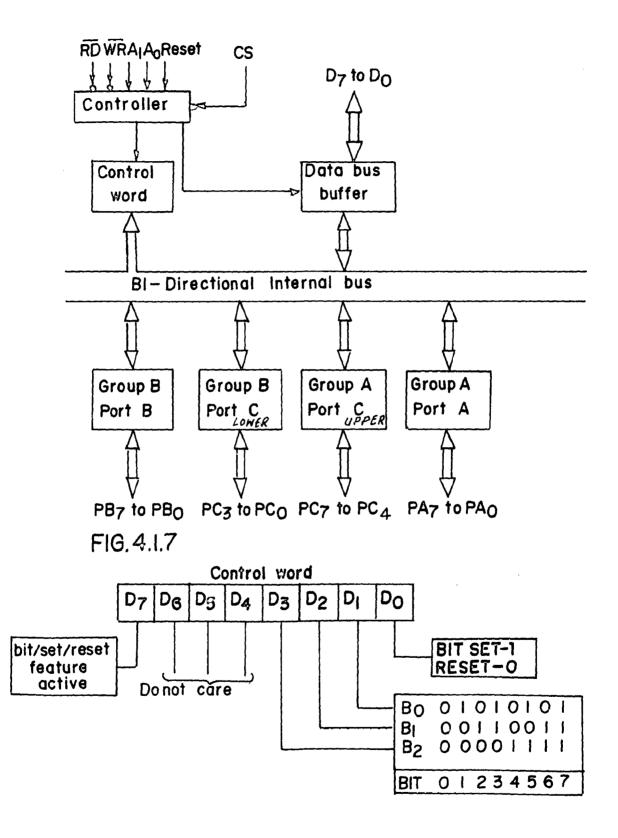

A block diagram of the device is shown in figure 4.1.7. The device is connected to the data bus through a 3 state data bus buffer. The cutput terminals of the device have been arranged in 4 ports (A, supper  $C_j$  lower C, B). These ports have been arranged in two groups. Group A consists of Port A and Upper C while group B consists of lower C and port B.

The device has a register to store the control word, which decides the manner in which the ports will behave. Besides this the device has a number of control inputs ( $\overline{RD}$ ,  $\overline{WR}$ , Ao, AL, Reset and  $\overline{CS}$ ).

The data is received or transmitted upon execution of IN port or OUT port instructions by the CPU, which are described as below :

IN port

(A) (data)

|     |      | ÷ •      |       |

|-----|------|----------|-------|

| 11  | 011  | 011      | · · · |

| n n | port | <u>4</u> |       |

The data placed by the specified port on the data bus is moved to Accummulator.

Similarly in OUT port instruction, data from the accumulator is put on the data bus for transmission to a specified port.

In both the cases the port is specified by the 2nd byte of the instruction becomes the lower order part of the address (A7 to A0), upon execution of the instruction.

| Ao | AL | · · · ·    |                  |

|----|----|------------|------------------|

| 0  | ٥  | Port A 🚑   | Data bus         |

| 0  | 1  | Port B 🔿   | Data bus         |

| 1  | 0  | Port C 🚔   | Data bus         |

| 1  | 1  | Data bus 🔿 | Control register |

The control word sent from CFU through an OUT port instruction decides the mode in which various ports of 8255 operate.

There are three basic modes of operation in which the ports can operate. (Refer fig. 4.1.8).

| Mode | 0 |   | Basic Input/Output       |

|------|---|---|--------------------------|

| Mode | 1 | - | Strobed Input/Output     |

| Mode | 2 | - | <b>Bidirectional bus</b> |

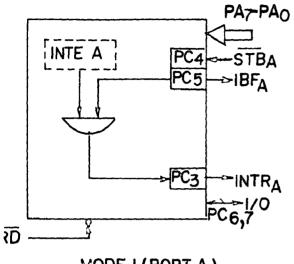

It is also possible to set/reset any of the eight bits of port C by using a single OUT port instruction (Refer Fig.4.1.)

When Reset input goes high all ports will be set to the Input mode (in the high impedance set). After the RESET is removed 8255 can remain in the Input mode with no additional initialization required.

#### APPLICATIONS

MODE 0 OPERATION : When operated in Mode 0 the basic features are given below :-

1. Two 8 bit port and two 4 bit ports.

2. Any port can be input or output.

3. Outputs on the ports are latched.

4. Inputs on the ports are not latched.

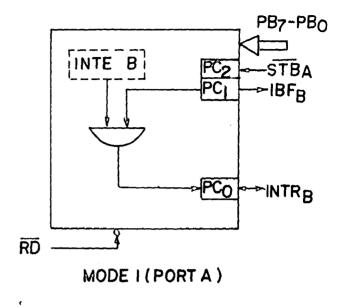

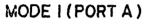

Mode 0 is ideally suited to communicate simple switch closings to the CPU. Depending upon the control word number of configurations of the ports are possible (Refer Annexure 1 for details). <u>Mode 1 Operations</u> :- In mode 1 the basic features are as given below :(Refer Fig.4.1.10).

1. Ports operate in groups only (Group A and Group B).

2. In group A, Port A operates as 8 bit data port while upper C acts as control/data port. Consider for example, the case when port A operates as an input port. A low on PC4 loads data into the input latch. A high on PC5 indicates that the data is loaded in the input latch although it has yet to be off loaded by CPU. When CPU of loads the data by accessing port A, PC5 goes low again. It is also possible to generate an Interrupt request for the CPU by the peripheral device connected on Port A, 8255 contains an INTE A flip flop which can set/reset by PC4, when CPU sends the following control word.

> 0 x x x 1 0 0 1 for setting the INTE flip flop 0 x x x 1 0 0 0 for resetting the flip flop.

As a first step the peripheral device on port A latches RST instruction on the port. As a result IBFA goes high.If INTE flip flop has been SET by CPU earlier, an INTERRUPTS the CPU. During T3 of the interrupt cycle RST instruction is off loaded. RD pulse also resets INTEA flip flop.

PC6, 7 the balance terminals of upper C port can be programmed as either input or output port as the case may be.

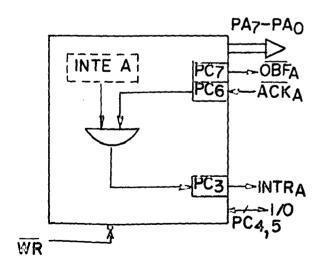

In a similar manner port B, and lower C port can be used to generate an Interrupt request.

In mode 1, port A or port B can be operated as output, ports.

The OBF output goes low to indicate that CPU has written data in the port. A low on ACK input informs 8255 that the data has been accepted by the peripheral device. It is also possible to generate an Interrupt request by the peripheral device connected on the specified port.

Once the peripheral device has accepted the data both OBF and ACK are high. At this stage if INTE flip flop is SET by sending an oppropriate control word, Interrupt request shall be generated. In this case RST instruction shall be loaded by some other peripheral device connected on an Input port, Refer Table 3 in Annexure 1 for more details.

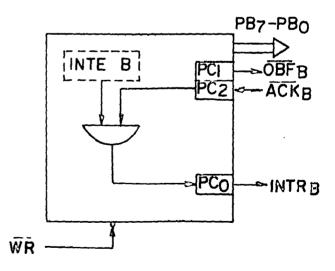

#### MODE-2 Operation

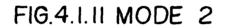

The basic features of Mode 2 operation are as given below : (Ref. Fig. 4.1.11).

1. Mode 2 is used in group A only (Port A and 5 bit upper C) for control.

2. In mode 2 both inputs and outputs are latched. In mode 2 port A operates as a bidirectional bus.

The terminals OBF, ACK, STB, IBF have their usual meaning. The interrupt request is generated at PC3. Reading Port C status :

When the 2255 is programmed to function modes 1 or 2 Port C generates or accepts handshaking signals with the peripheral devices. Reading the status of Port C allows the programmer to verify the status of each peripheral device by sending a simple IN port C instruction. The word can be finally interpreted.

Example :

Consider the case when 12 bit D/A converter has to be connected as an output device while an 8 bit A/D converter as an Input device. The software for initialisation of the ports is as shown in fig. 4.1.12.

| MVI, A           | 8E | This makes port A OUt, Upper C |

|------------------|----|--------------------------------|

| 82               | 82 | Out, lower C-out, Port B-Inp   |

| OUT              | D3 | in Mode 0.                     |

| Control register | 17 |                                |

| ,                | ۰. |                                |

When CPU wants to request A/D converter for a data it sends a strobe pulse to A/D converter on PC3. The conversion takes place and the digital word is stored in the A/D converter. After some time CPU sends sample enable pulse at PC2 and data is communicated to CPU on the data bus.

| A IVM  |   | 3E  | Bit PC3 of port C is set and   |

|--------|---|-----|--------------------------------|

| 07     | • | 07  | then reset to produce a sharp  |

| OUT    | ¥ | D 3 | pulse at PC3, which is the     |

| PORT C |   | 16  | strobe pulse to A/D converter. |

| DCR A  |   | 3 D |                                |

| OUT    |   | D 3 |                                |

| PORT C | , | 16  |                                |

|     | As    | a | next | step  | CPU  | would | sent | a | pulse | at | PC2 | to | enable |  |

|-----|-------|---|------|-------|------|-------|------|---|-------|----|-----|----|--------|--|

| the | sampl | e | on t | he da | ta b | us of | CPU+ |   |       |    |     |    | -      |  |

|   | المربية والمارية المراجعة والمحصر بالمحصر والمتحدث والمتحدث والمتحدث والمتحدث والمحاد |     |

|---|---------------------------------------------------------------------------------------|-----|

|   | MVI A                                                                                 | 3 2 |

|   | 05                                                                                    | 0 5 |

| ÷ | OUT                                                                                   | D 3 |

| · | Port C                                                                                | 1 6 |

|   | DCR A                                                                                 | 3 D |

|   | OUT                                                                                   | D 3 |

|   | Port C                                                                                | 16  |

|   |                                                                                       |     |

In a similar manner software programmes can be written to OUT put data through 12 bit D/A converter.

ANNEXURE - 1

FOR SDK - 80 KIT ONLY

TABLE - 1

| B | YT | E | 2 |    | <b>n nin</b> | - | Častain ( Qajar, 14 | BYTE (HEX) | SELECTION                 |

|---|----|---|---|----|--------------|---|---------------------|------------|---------------------------|

| X | ×  | × | 1 | 10 | x            | X |                     | 18         | 8251                      |

| X | ×  | X | 1 | 0  | ŧ            | 0 | 0                   | 14         | Port A/8255 (1)           |

| x | X  | x | 1 | 0  | 1            | 0 | •                   | 15         | Port B/8255 (1)           |

| X | x  | X | 1 | 0  | 1            | 1 | 0                   | 16         | Port C/8255 (1)           |

| X | x  | x | 1 | 0  | ŧ            | 1 | 1                   | 17         | Control register/8255 (1) |

| X | x  | X | 0 | \$ | 1            | 0 | 0                   | 00         | Port A/8255 (2)           |

| X | x  | x | Ō | 1  | \$           | 0 | 1                   | OD .       | Port 8/8255 (2)           |

| x | x  | x | 0 | 1  | 1            | 1 | 0                   | OE         | Port C/8255 (2)           |

| X | x  | X | 0 | 1  | 1            | 1 | 1                   | OF         | Control register/8255 (2) |

By sending OUT Port or IN port instruction any port (A,B,C) or the control register can be accessed. In case of control register only OUT port instruction is valid, because the data stored in Control register cannot be read.

MODE-O Operation

Table-2

| CONTROL<br>BINARY | WORD | HEX | STA<br>GROUP A<br>A | TUS OF<br>PORTS<br>UPPER C |     | ATUS OF<br>B PORTS<br>LOWER C |

|-------------------|------|-----|---------------------|----------------------------|-----|-------------------------------|

| 1000              | 0000 | 80  | OUT                 | CUT                        | OUT | out                           |

| 1000              | 0001 | 8 1 | OUT                 | OUT                        | out | INP                           |

| 1000              | 0010 | 82  | OUT                 | OUT                        | INL | OUT                           |

| 1000              | 0011 | 83  | OUT                 | OUT                        | INP | INP                           |

| 1000              | 1000 | 88  | OUT                 | INP                        | OUT | out                           |

| 1 0 0 0           | 1001 | 8.9 | OUT                 | INP                        | out | INP                           |

| 1000              | 1010 | 8 A | OUT                 | INP                        | INP | out                           |

| 1000              | 1011 | 8 B | OUT                 | INP                        | INP | INP                           |

| 1001              | 0000 | 90  | INP                 | OUT                        | OUT | OUT                           |

| 1001              | 0001 | 91  | INP                 | OUT                        | OUT | INP                           |

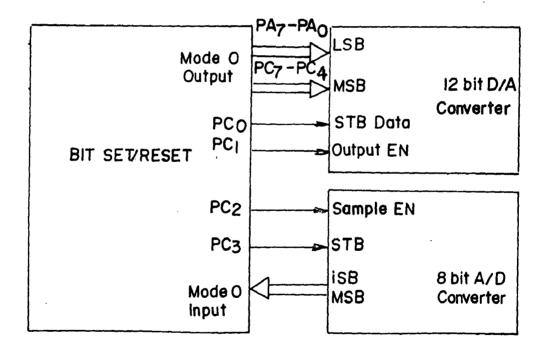

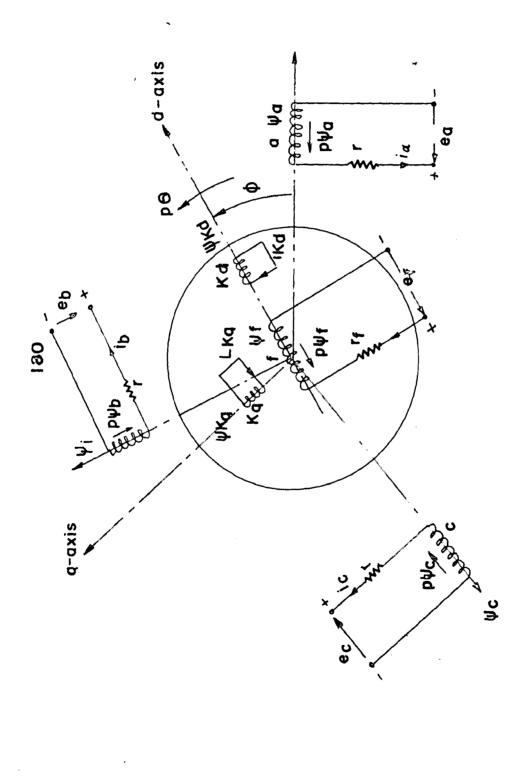

| 1001              | 0010 | 92  | INP                 | OUT                        | INP | OUT                           |