# OPTIMAL DESIGN OF NON-LINEAR ELECTRONIC CIRCUITS

# A DISSERTATION

submitted in partial fulfilment of the requirements for the award of the degree

of MASTER OF ENGINEERING

in

ELECTRICAL ENGINEERING (System Engineering & Operation Research)

by

# DEPARTMENT OF ELECTRICAL ENGINEERING UNIVERSITY OF ROORKEE ROORKEE-247672 (INDIA)

# <u>CERTIFICATE</u>

Certified that the M.E.dissertation entitled, "OPTIMAL DESIGN OF NON LINEAR ELECTRONIC CIRCUTS" which is being submitted by Sri P.K.Gupta in partial fulfilment for the award of the Degree of ME in Electrical Engineering (Sysetm Engg.& Operation Research) of the University of Roorkee, Roorkee is record of students own work carried out by him under our supervision and guidance. The matter embodied in this dissertation has not been submitted for the award of any other degree or diploma.

This is further certified that he has worked for a period of 18 months from Feb.1980 to Aug.1981for preparing this dissertation for the Master of Engg.Degree at M/s Indian Telephone Industries Ltd; Naini.

(Dr.H.D.GUPTA) Reader Elect.Engg.Deptt. University of Roorkee Roorkee

abvaywa Si.

(A.K.VANWASI) Senior Engineer Reșezach & Development Divison I.T.I. Ltd.Naini,ALLD.

(1)

ACKNOWLEDGEMENTS

The author takes this opportunity to express his profound gratitude, appreciation and sincere thanks to Mr. A.K.Vanwasi, Senior Engineer, M/s. Indian Telephone Industries Ltd., Naini and Dr. H.O.Gupta, Reader, Department of Electrical Engineering, University of Roorkee, Roorkee for their valuable and inspiring guidance, and enlightening suggestions. The abundant enthusiasm shown, the zeal with which Mr. Vanwasi solved the author's difficulties whenever approached will be remembered with gratitude of no parallel.

The author thanks Mr. B.L.K.Rao, Dy. General Manager and Mr.S.P.Singh, Manager Production, M/s. I.T.I.Ltd., Naini for providing excellent facilities and most favourable working condition for preparation of this dissertation.

PRADEEP KUMAR GUPTA

(ii)

## ABSTRACT

Switching mode converters are basically nonlinear time varying discrete time systems. For analysing such systems either nonlinear discrete time or small scale linearization techniques are used. This work is concerned with modelling and analysis of the audiosusceptibility performance of a switching mode converter using DIDF technique.

A general method for modelling power stages of any switching mode d.c. to d.c. converter has been developed through the State-Space approach. The fundamental step is in replacement of the state space description of the two switched network by their average over the single switching period T, which results in a single continuous state space description. From state space description a canonical circuit model is developed which gives various performance characteristics of different switching converters directly.

Using this technique, a small signal average model of switching mode regulator is derived to investigate the complex interaction among input filter, output filter and control loop. Performance indices of a switching regulator have been formulated, and a comparison has been made for a series switching regulator using different input filter configurations. Basic constraints for optimal two stage input filter configuration have been discussed.

dity

# LIST OF SYMBOLS USED

| T, <b>T</b>        | : Time period                                      |

|--------------------|----------------------------------------------------|

| Ton                | : Time when switch is ON                           |

| TOFF               | : Time when switch is OFF                          |

| d                  | : Duty cycle                                       |

| zs                 | : Output Impedence of Input filter                 |

| z <sub>i</sub>     | : Input Impedence of switching regulator           |

| H <sub>s</sub>     | : Forward transfer function of Input filter        |

| μ                  | : Transformation ratio of d.c. to d.c. transformer |

| Ws                 | : Filter cut-off frequency                         |

| F                  | : Switching frequency                              |

| Fc                 | : Duty cycle power stage gain                      |

| Fp                 | : Power stage transfer function                    |

| Ē                  | : Transfer function of Error Processor             |

| F <sub>M</sub>     | : Transfer function of PWM                         |

| G <sub>T</sub> (s) | : Open loop gain of switching regulator            |

| $G_{A}(s)$         | : Audiosusceptibility                              |

| ×                  | : Attenuation of Input filter                      |

| <sup>B</sup> F     | : Resonant peaking of H s                          |

| BR                 | : Resonant peaking of $z_s$                        |

.

úv)

.

.

CONTENTS

| CHAPTER | PARTICULARS                                                   |       | PAGE NO. |

|---------|---------------------------------------------------------------|-------|----------|

|         | CERTIFICATE                                                   | • • • | I        |

|         | ACKNOWLEDGEMENTS                                              | •••   | 11       |

|         | ABSTRACT                                                      | • • • | lii      |

|         | LIST OF SYMBOLS USED                                          | • • • | iv       |

| I       | INTRODUCTION                                                  |       | 1        |

| II      | MODELLING OF SWITCHING MODE<br>CONVERTERS                     | •••   | 15       |

| III     | DESIGN & ANALYSIS OF SWITCHING<br>CONVERTERS                  | •••   | 50       |

| IV      | PERFORMANCE COMPUTATION OF A<br>SWITCHING MODE BUCK CONVERTER | •••   | 77       |

| V       | DISCUSSION AND CONCLUSION                                     | •••   | 83       |

|         | REFERENCES                                                    | •••   |          |

|         | APPENDIX A                                                    | • • • |          |

|         | APPENDIX B                                                    | • • • |          |

|         | APPENDIX C                                                    | • • • |          |

\*\*\*\*

# CHAPTER I

# INTRODUCTION

- 1.1. Introduction

- 1.1.1 Introduction of Non-Linear Systems.

- 1.1.2 Common methods of non linear system study

- 1.2 Linear Power Supplies & Switching Mode Regulator 1.2.1 Linear Power Supply and its types

- 1.2.2 Switched Mode Power Supply

- 1.2.3 Advantages & disadvantages of Switched mode Regulators

- 1.3 General Circuits for Power Supply Regulators

1.3.1 Buck Regulator

1.3.2 Boost Regulator

1.3.3 Buck-Boost Regulator

- 1.4 Performance Indices of Switching Regulator

- 1.5 Organisation of the Thesis

#### 1.1 INTRODUCTION

Most of the practical systems are non-linear in nature. For a nonlinear system superposition principle is no longer valid. In such systems there is no possibility of generalized form of response, as the response of such systems depends upon the magnitude and type of the input. In other words a non-linear system behaves completely differently for different type of inputs. This constitutes a fundamental and important difficulty in studying nonlinear systems.

In spite of the analytic difficulties, we have no choice but to attempt to deal in some way with nonlinear systems, because of the importance of such systems. No single method can be used for all types of nonlinear systems. The existing methods for analysing nonlinear systems are described in (9), these can be classified as under:

1. prototype test :

The most certain means of studying a system is to build one and test it. The greatest advantage of this is that it avoids the necessity of choosing a mathematical model. The disadvantages are the time required to construct a series of trial systems, the cost involved etc.

2. Closed Form Solution :

There are a number of nonlinear differential equations,

### 1.1 INTRODUCTION

Most of the practical systems are non-linear in nature. For a nonlinear system superposition principle is no longer valid. In such systems there is no possibility of generalized form of response, as the response of such systems depends upon the magnitude and type of the input. In other words a non-linear system behaves completely differently for different type of inputs. This constitutes a fundamental and important difficulty in studying nonlinear systems.

In spite of the analytic difficulties, we have no choice but to attempt to deal in some way with nonlinear systems, because of the importance of such systems. No single method can be used for all types of nonlinear systems. The existing methods for analysing nonlinear systems are described in [9], these can be classified as under:

1. prototype test :

The most certain means of studying a system is to build one and test it. The greatest advantage of this is that it avoids the necessity of choosing a mathematical model. The disadvantages are the time required to construct a series of trial systems, the cost involved etc.

2. Closed Form Solution :

There are a number of nonlinear differential equations,

mostly of second order, for which exact solutions have been found or for which certain properties of the solutions have been tabulated. But this is applicable only for certain special cases.

### 3. Phase plane Solution :

The dynamic properties of a system can be described in terms of the differential equations of state, and an attempt made to solve for the trajectories of the system in the state space.

#### 4. Lyapunov's Direct Method :

One of the most important properties of a system, stability, can in principle, be evaluated without calculating the detailed responses of the system.

### 5. Series Expansion Solution :

A whole family of techniques exists which develop the solutions of nonlinear differential equations or express the dynamic properties of non-linear systems in expansion of various forms.

## 6. Linearization :

The problem of studying a nonlinear system can be avoided altogether by simply replacing each nonlinear operation by an approximating linear operation and studying the resulting linear system.

#### 7. Computer Simulation :

In the cases where manual analysis of nonlinear characteristic becomes impractical, modern computer is the only alternative. Small signal operation of semiconductor devices can be represented by linear circuit model which may be analysed through the use of well documented computational techniques.

For design and analysis of a system with multiple nonlinearities, it is separated into functional blocks, with each block containing one nonlinearity. The block is then linearized, and all linear blocks are then used jointly to arrive at an initial system design and analysis.

A switching regulator contains two major nonlinearities. The first resides in the power stage, and is due to the on-off operation of the power switch and the different circuit topologies attendant to the respective time intervals. The second exists in the digital signal processor accomplishing the analog to discrete time duty cycle conversion. But before going in detail of modelling and analysis of switching mode converters and the problem arises therein we will briefly discuss in the next section the conventional power supplies and the advantages of switching mode converters over contentional linear power supplies.

#### 1.2 Linear Power Supply & Switching Mode Converters :

A power supply equipment is defined as :

"An item of equipment that accepts power from batteries or from the mains, and converts or modifies it for use in a particular part of equipment."

When a load requires precision control of both voltages and current and when an outside ac or dc source of energy is used, a system must incorporate a power supply using a regulator. Basically there are two types of regulators dissipative and non-dissipative.

The dissipative regulator absorbs the difference between input voltage at the source and the regulated voltage at the load. A non-dissipative regulator stores excess power in an LC filter and delivers the power to the load in measured intervals. Non-dissipative regulators use switching devices to control output power. During the time switch is ON, power is stored in an energy storage network (the LC filter) and is delivered to the load as required. Ideally, the switching approach exhibits non power dissipation. The block diagram of linear power supply is shown in fig. 1.1.

# Switched mode power supply :

The term 'Switched Mode Power Supply" convers a number of modern techniques and circuits for the conversion of a given dc voltage and current, to one or more other dc voltages and/or currents. In other words, switched mode

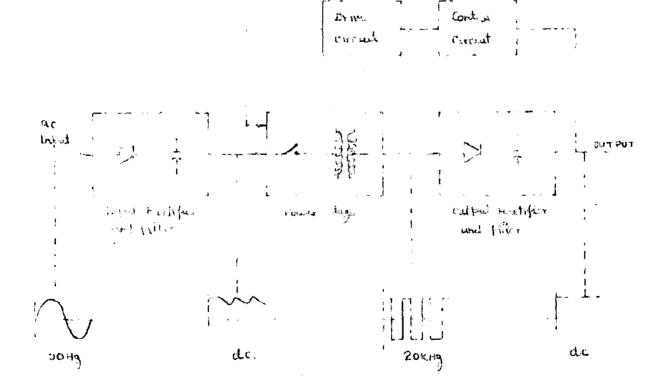

FIG 1 / BLOCK DIAGRAM OF AN A C'IMPUT SWITCHED MODE

FIG 1.1 BIOCK TRAGRAM OF LINEAR POWER SUPPLY.

power supplies are all d.c. to d.c. converters. The qualification "switched mode" indicates that the input voltage to the power supply is switched on and off, normally at a rate above the audible range. Thus switched moder power supply is a modern solid state version of the electromechanical vibrator.

The schematic diagram of switched mode power supply is shown in fig. 1.2. Main a.c. input of 50 Hz is rectified and smoothed by input rectifier and filter, the output of which is unregulated d.c. voltage. This d.c. voltage is chopped at high frequency by a transistor and output is fed to a transformer. The output of power stage gives high frequency pulses of 20 KHz. These are rectified and filtered by output rectifier and filter to give required d.c. output. Output is sensed by the control circuit and a correction signal is produced which is used to vary the ON/OFF ratio usually called 'Duty-Cycle' which results regulated d.c. voltage at output.

Non-dissipative components are the basis for switch mode regulation. The inductor and capacitor of switched mode regulator exhibits little d.c. resistance, hence dissipate little d.c. power. The switch, a transtor, either fully off or saturated, dissipates much less power.

Ā

## Advantages of Switching Mode Regulators :

(i) Power Dissipation :

Linear dissipative series or shunt regulator dissipates large amount of power at high load currents, especially when input-output difference is large.

Since the power transistor switch is always either cut. off or saturated (except for a very brief transition between these two states) and load current flows through low resistance elements, the switch, the inductor, capacitor and the 'ON' diode, the d.c. dissipation is therefore less.

(ii) Size and Weight :

The size and weight of a power supply rated for any given output power are determined chiefly by the switching frequency, the internal power dissipation and the size of the heat exchanges. Other factors are the magnetic components transformers, inductors and capacitors. The size of the magnetics included in the power supply is inversely proportional to the switching frequency of the regulator. For example, a typical 50 Hz transformer that can handle one kilowatt of power has volume of 160 cubic inches and weight about 10 Kg. A 20 KHz transformer, on the other hand would be about 40 cubic inches and weight just one Kg. Thus with high switching frequency there is a considerable reduction in

transformer size and weight and some reduction in the size of the smoothing components.

(iii) Efficiency :

Since power dissipation in switching regulator is less, it maintains high efficiency over wide range in load current. Moreover, with the reduction of size, the power loss to maintain the same temperature rise in the regulator box is also reduced, as cooling is proportional to surface area. This again results increase in efficiency. In general switching regulators are twice as efficient as linear supplies. The typical efficiency figures for linear power supplies are 30% to 40%, whereas, for switching mode regulator it is 60% to 90%.

Since efficiency of switching regulator is twice that of linear power supplies, therefore, input current amplitude will be half as high in case of switching regulator, which in turn, reduces the amplitude of the input current spectrum.

In addition to saving in weight, volume, power and cost, the switching power supplies offer further advantages because of its versatility. It is simple matter of changing one connection to enable a supply to operate with either 110 volt or 220 volts a.c.

Furthermore, in case of a.c. input, since smoothing is

done at 250V instead of at the low voltage, it allows further saving in capacitor size and cost. Because energy stored is proportional to  $cv^2$ , while the capacitor volume is proportion to cv.

# Disadvantages :

The primary power source delivers current to the switching regulator in pulses which for efficiency reasons, have short rise and fall times. In these applications where a significant series impedance appears between the supply and regulator, the rapid changes in current can generate considerable noise. This problem can be reduced by reducing the series impedance, increasing the switching time, or by filtering the input to the regulator.

<u>Response time to rapid changes in load current</u>. The switching regulator will reach a new equilibrium only when the average inductor current reaches it

new steady state value. In order to make this time short, it is advantageous to use low inductor values.

#### 1.3 General Circuits for Power Supply Regulators :

There are several designs for power supply circuitory. The common names for the six most widely used circuits are -

- 1. Buck regulator

- 2. Boost regulator

- 3. Buck\_Boest regulator

- 4. Full bridge regulator converter

- 5. Half bridge regulator converter

- 6. Push-Pull regulator converter.

Here we will discuss only the first three circuits which are most common.

# Buck Regulator

The circuit for this bype of regulator is shown in fig. fig. 1.3(a). The control circuit causes transistor switch  $Q_1$  to switch ON and OFF at a predetermined frequency f. During the time that  $Q_1$  is ON,  $T_{on}$ , the input voltage,  $E_{in}$  is applied to the input of LC filter, causing current  $i_1$  to increase. When  $Q_1$  is OFF, the energy stored in the inductor L maintains current flow to the load, circulating through "catch" diode  $D_1$ . The input of the LC filter is now at zero volts.  $i_1$  decreases to its original value and the cycle repeats.

The output voltage  $E_0$ , will equal the time average of the voltage at the input of the LC filter :

$$E_{o} = E_{in} T_{ON}/T$$

The control ckt. senses and regulates Eo by controlling the duty-cycle ,  $d = T_{on}/\tau$  . If E increases, the control circuit will cause a corresponding reduction in the duty cycle as to maintain a constant E

The output voltage is controllable from zero volts to E<sub>in</sub>. The voltage stress on the series switching transtor is equal to E<sub>in</sub> plus the forward drop of the communicating diode. Average current through the transistor switch is equal to the load current. Current limiting is achieved by cort rolling the switch duty cycle. The Buck Regulator is very efficient for simple stepdown regulation.

#### Boost Regulator :

It is similar to Buck regulator except that the circuit is designed to provide an output voltage that is higher than the input voltage. This circuit is shown in fig. 1.3(b).

The Boost regulator has drawbacks in some applications. It has no inherent capability to limit current and the output voltage cannot be reduced to zero. It has a minimum value equal to the input voltage.

#### Buck-Boost Regulator :

The circuit for Buck-Boost regulator is shown in fig. 1.3(c) It provides both regulation and isolation, if we use transformer for L. Multiple dutputs are possible with just the single device. Output voltage can be either higher or lower than the input voltage.

This circuit has two characteristics. First, the use of a transformer in the circuit creates a problem of leakage inductance. Secondly, this type of regulator generates high output dynamic impedance and may generate high output ripple. A series regulator at the output may be used to reduce impedance and ripple. This approach, of course, somewhat complicated and sacrifices some efficiency.

#### 1.4 Performance Indices Switching Regulators :

#### Input Reflected Ripple :

A dc/dc converter term which describes the voltage spike resulting from switching generated transient currents as measured at the d.c. input source.

#### Line Regulation :

Change in DC output voltage due to variation of input voltage with all other factors held constant, expressed as a % of the nominal d.c. output voltage. Also called source voltage effect.

#### Load Regulation :

Change in d.c. output voltage, due to variation of external load current with all other factors held constant : expressed as a % of the nominal d.c. output voltage. Usually the external current is varied from zero to rated maximum, also called load effect.

#### Overall Regulation :

The percent of output voltage change resulting from a specified change of input voltage, output load, temperature or time. The resulting specifications are line regulation, load regulation, temperature coefficient and stability. Ripple :

The periodic AC noise component present at the power source d.c. output. Unless specified separately this specification may include random voltage noise. It is usually expressed as peak, peak to peak or RMS.

# Ripple and Noise (PARD) :

AC components present in the power source d.c. output that are measured within a 10 Hz to 20 MHz bandwith. Expressed as peak, peak-to-peak, or RMS, the specification is also termed Periodic And Random Deviations.

# 1.5 Organization of the Thesis :

In chapter II, apart from state space modelling and averaging technique, a third method for modelling switchingconverter power stages is discussed, whose starting point is the unified state space representation of the switched networks and whose end result is a **fom**plete state space description and its equivalent small signal low frequency linear circuit model.

A canonical circuit model is discussed whose fixed topology contains all the essential input-output and control properties of any d.c. to dc switching converter by which different converters can be charactorized in the form of a table conveniently stored in a computer data bank to provide a useful tool for computer aided design and optimization.

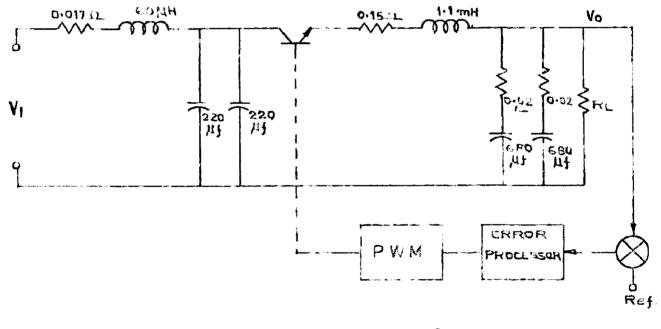

Chapter III deals with the necessity of input filter for switching regulators, its advantages-disadvantages, and effect on performance of switching regulator are discussed. The interaction between the input filter and the control loop of switching regulators often results in loop instability, transient response and audio-signal-rejection rate etc. A small signal average model is derived to investigate these effects. Design constraints of an input filter and switching regulators system are formulated.

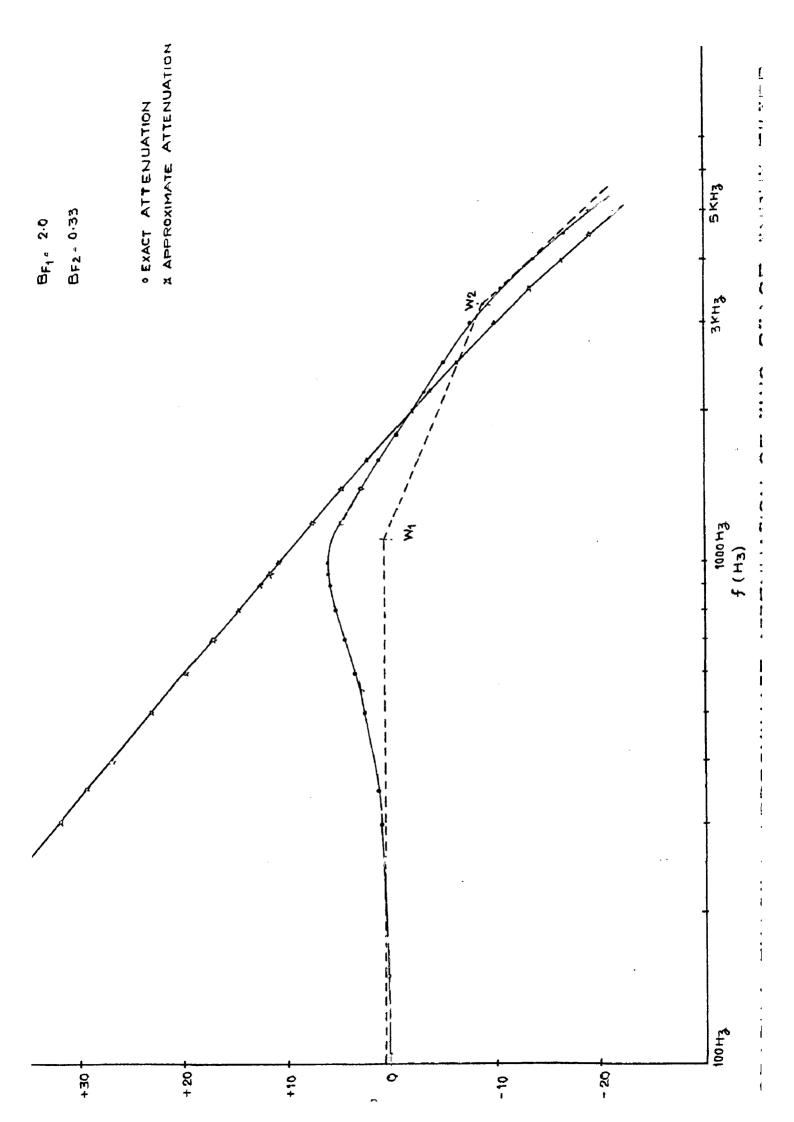

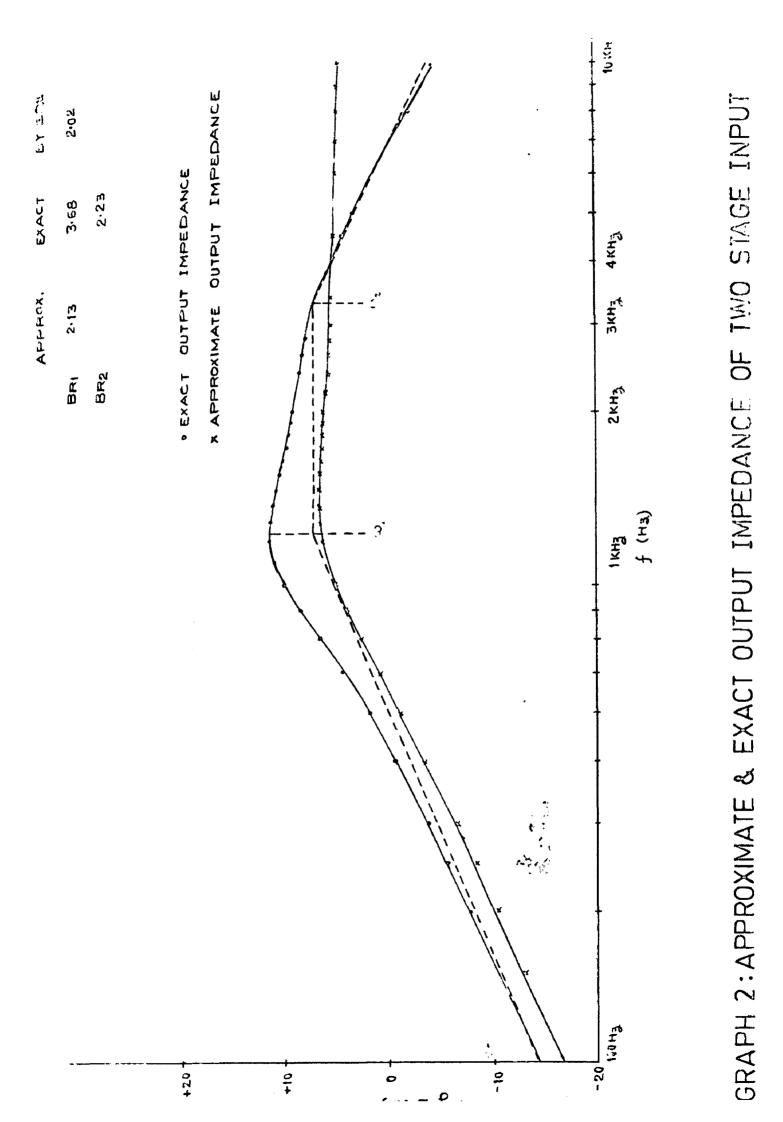

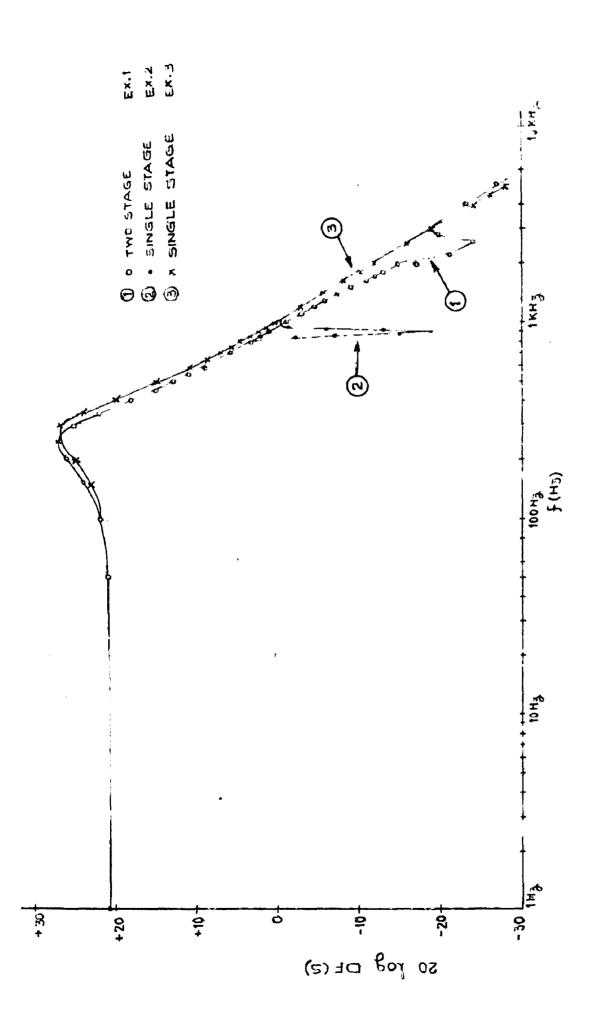

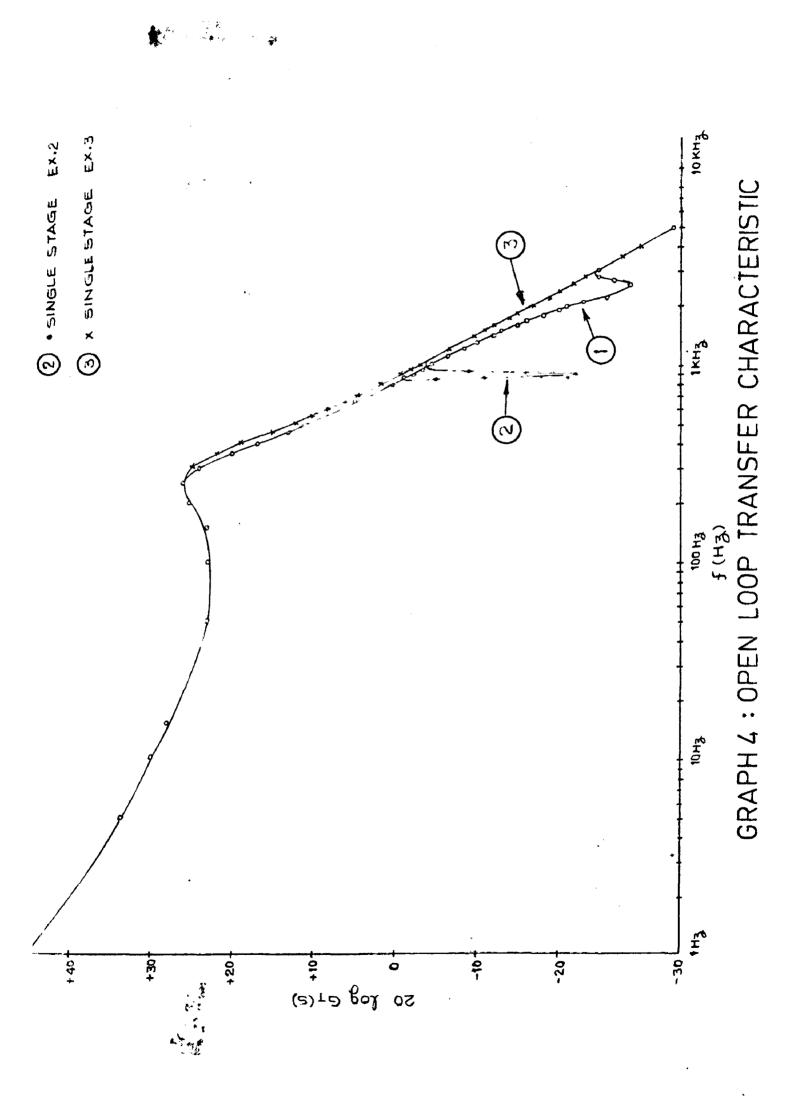

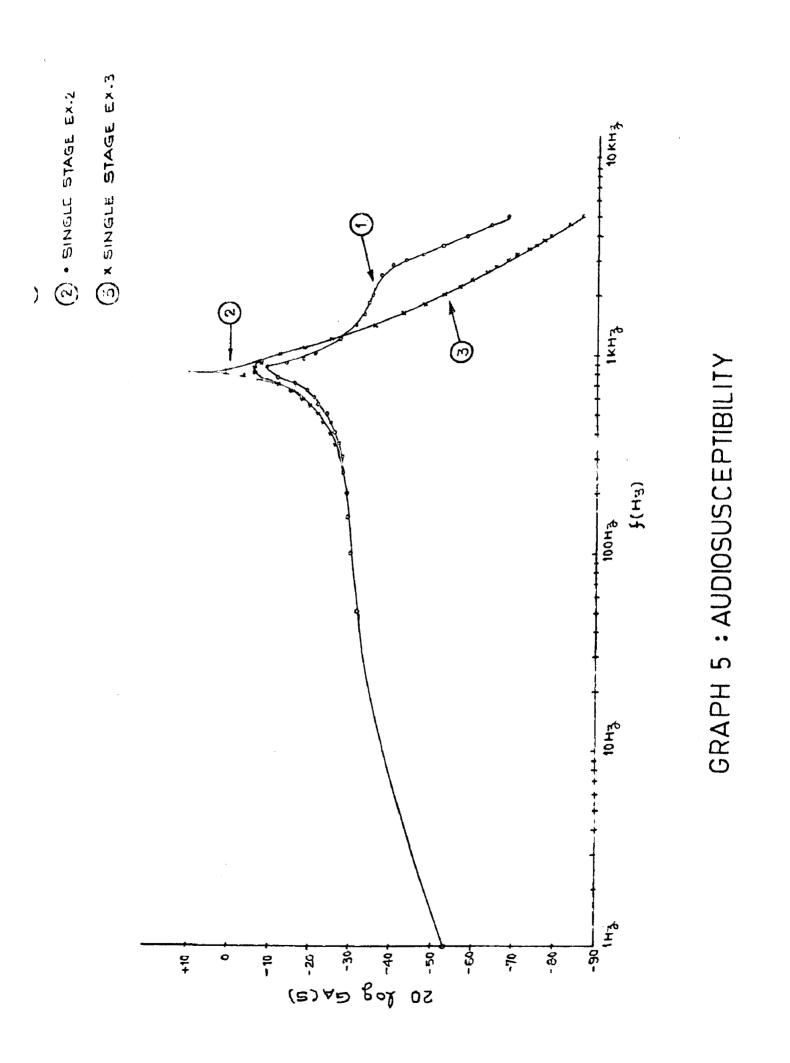

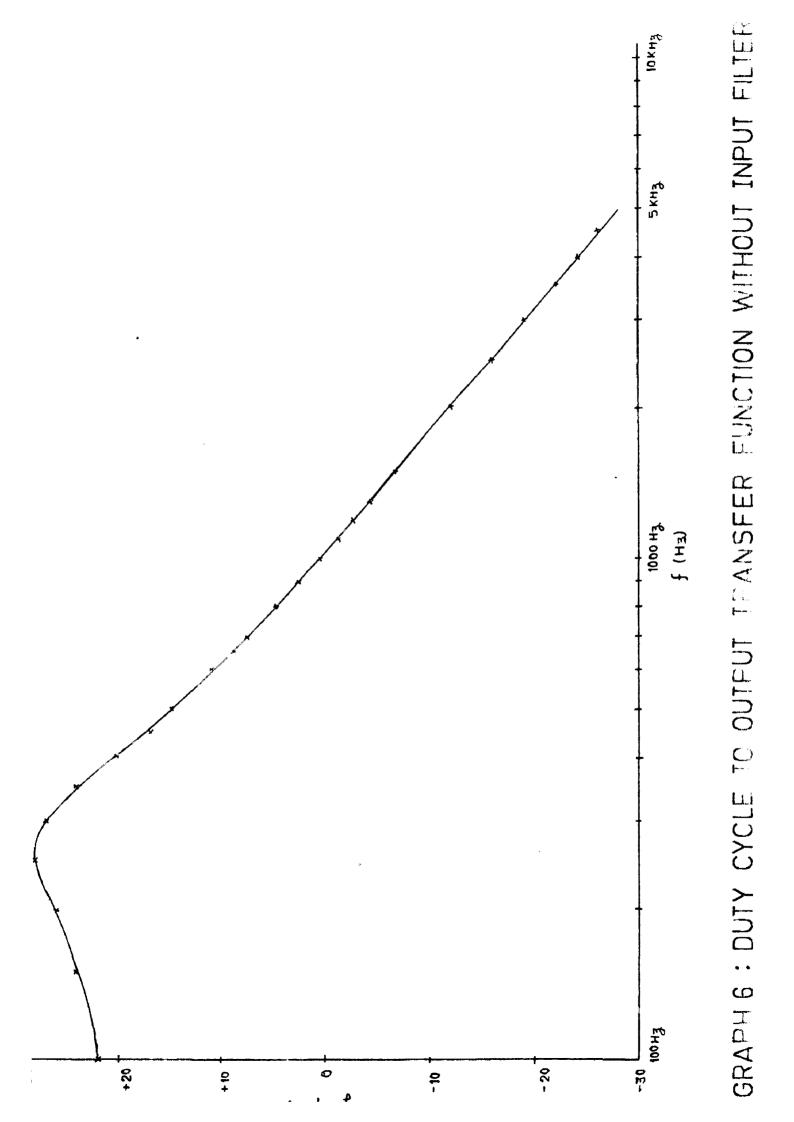

In chapter IV, a computer program in FORTRAN is developed to analyse the switching mode converter and the effect of input filter on its performance. Different types of input filter were taken to find out the optimum design. Their comparative performance is plotted on graphs.

In last chapter, the conclusion of this work is made and scope for further work is suggested. The state space matrices for Buck type switching regulator are given in Appendix A. Appendix B gives the fundamental approximation in the state space averaging approach. In Appendix C, Dither method is discussed to obtain pulsewidth modulator signal and its describing function.

# <u>CHAPTER - II</u>

# MODELLING OF SWITCHING MODE CONVERTER

- 2.1(a) Introduction

- 2.1.1 Small Scale Linearization method : State Space, Averaging, State Space averaging techniques, Assumptions and Limitations.

- 2.1.2 Nonlinear discrete time model.

- 2.1(b) State Space Representation

- 2.2 Averaging Technique

- 2.3 State Space Averaging

- 2.3.1 Basic State Space model

- 2.3.2 Linearization and Final State Space Averaged Model.

- 2.3.3 Circuit Realization

- 2.3.4 Canonical Circuit Model.

- 2.4 Modelling of Modulator

#### 2.1 INTRODUCTION :

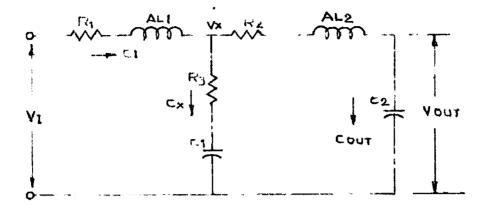

The switched mode dc-dc converter can be characterized by the three basic functional blocks : power stage, analog signal processor and digital signal pressor or duty-cycle controller, as shown in fig. 2.1.1.

The power stage process the power from input to output. The analog signal processor togetherwith the digital signal processor regulates the power flow from input to output. The output of the power stage is processed by the analog signal proces sor for error amplification and compensation. The output from the analog signal processor is converted into a discrete time\_interval by a digital signal processor, which provides the duty cycle control of the power switch in the power stage. Such converters can be characterized as nonlinear time varying system and have presented considerable difficulties in modelling and analysis. We call these systems as time varying since duty cycle 'd' is a function of time and varies considerably in case of large scale or transient performance. Thus during turn on interval the duty cycle increases gradually as shown in fig. 2.1.2. Similarly during the transient period duty cycle d( the ratio of  $T_{ON}/T_{OFF}$ ) varies with time before it reaches to its steady state value in about 1 sec. This is necessary (i) to avoid undesired over shoot

in output response (ii) to avoid saturation of magnetic components (iii) to prevent over-voltage tripping. Partially due to the nonlinear discrete nature of such system and partially due to the rapidly evolving new circuit technology, modelling and analysis of power processing systems has been constantly lagging behind the circuit development.

The different modelling techniques can be broadly classified into two Categories : (1) small-scale linearization technique [1], [2] and (2) non-linear discrete time model [3][4].

#### Small -scale Linearization Method :

In this technique the model of the converter is linearized about its operating point with the following assumptions :

(a) Duty cycle d is constant and only small perturbations are allowed.

(b) Inductor current is in continuous conduction mode.

(c) There are only small changes in input voltage or load.

(d) The performance is evaluated over single repetition period 'T' by averaging over two switched intervals T<sub>d</sub> and T(1-d).

The techniques in this category are averaging technique, state space modelling and state space averaging technique.

#### (1) State Space Modelling :

This approach remains strictly in the domain of equation manipulations and hence relies heavily on numerical methods and computerized implementations. Its primary advantage is in the unified description of all power stages regardless of the type (Buck, Boost, Buck-Boost or any other variation) through utilization of the exact state space equations of the two switched models.

### (2) Averaging Technique :

This technique is based on equivalent circuit manipulations, resulting in a single equivalent linear circuit model of the power stage. This has the distinct advantage of providing the circuit designer with physical insight into the behaviour of the original switched circuit.

# (3) State Space Averaging Technique :

This method bridges the gap between the state space technique and the averaging technique of modelling power stages. This model offers the advantages of both the previous methods, the general unified treatment of the state space approach, as well as an equivalent linear circuit model as its final result.

As per the assumptions, the above techniques are valid only when the inductor current is in a continuous conduction mode (explained in the next paragraph) and can not be applied for discontinuous conduction mode. In each cycle of the converter operation, two power stage topologies can be defined. One is for the ON time interval when the power switch is "ON" and the commutating diode is "DFF" and the other is for the off time interval when the power switch is OFF and the diode is ON. These two power stage circuit topologies for Buck type dc\_dc switched converter are shown in fig. 2.1.3 (a) & (b) respectively.

As we know if L is equal to or greater than the critical inductance, the current through the inductor L is always greater than zero as shown in fig. 2.1.3(c). From this figure it is clear that in this case the period of each switching cycle can be clearly divided into two time intervals.  $T_{ON}$  (switch is ON and diode is OFF) and  $T_{OFF}$ (switch is OFF and diode is ON). This mode is called continuous conduction mode and the state space averaging technique is limited to this mode only.

But if L is less than the critical inductance, a third state exists when inductor current becomes zero. During this time interval, both the power switch and the diode are in the "OFF" state. The circuit topology for this time interval consists of only the filter capacitor and the load as shown in fig. 2.1.4(a).

d".

n a sta

÷

The inductor current for this case is shown in Fig. 2.1.4(b). In this case the current through the inductor reduces to zero and resides at zero for a time interval  $T_{off2}$ . This is called non-continuous conduction mode. To analyse such systems we have to go for non-linear discrete time model.

The linearized models as explained above are limited only to analyzing the small signal steady state operation when the duty cycle signal can be regarded as a constant. However in most applications, the converter is frequently subjected to lan signal step line/load transients, subsequently varying the duty cycle ratio to maintain input-output regulation. Due to the time varying and switching nature of the system, it is impossible to deduce the large signal performances from the above small signal linear models. Therefore to study such systems we have to go for non-linear discrete time model.

### Non-linear discrete time model :

The limitations of small scale linearization method can be overcome by this nonlinear discrete time model. This method is suitable for :

- (a) Generalized Converters

- (b) Large\_scale performance

- (c) Transient response

- (d) Small-scale linearization can also be done.

- (e) Non-continuous conduction mode.

- (f) Stability can also be predicted.

- (g) Large frequency range.

- (h) Audio-susceptibility can be predicted.

This method is discussed in (3) & (4) in detail. In this technique, system is characterized by three piece-wise linear state space equations. The third equation represents the behaviour of the system when inductor current is zero. A nonlinear recurrent time domain equation is derived that characterizes the converter behaviour exactly. The approach discussed in (4) is generalized to include all types of power stages, all types of duty cycle, controllers with single or multiple feedback loops and both containuous and discontinuous inductor current operations. Here we will discuss small-scale linearization methods in detail.

#### State Space Representation :

Voltage across the capacitor and current through the inductor are selected as the state variables X of the system. But state variables can be choosen differently depending upon individual problem. In general X is an n x 1 column vector. The system representation for continuous conduction mode is

$$x = A_1 x + b_1 u \quad durfing T \qquad (2.1.1)$$

$$x = A_2 x + b_2 u \quad during T_{OFF}$$

(2.1.2)

The column vector V is an (m  $\times$  1) input vector, Containing the input voltage  $E_{in}$ , the reference  $E_{ref}$ , the

saturation voltage drop across the power transistor and the forward voltage drop across the diode etc. The n x n matrices  $A_1$  and  $A_2$  and the n x m matrices  $b_1 \& b_2$  are constant matrices represented by the various circuit parameters. These matrices for Buck type stage are shown in the Appendix A.

The converts, which are basically nonlinear switching circuiare accurately described by the different equations represented by (24.1) & (24.2). The solution of the linear differential equations can be expressed by the following state transition equation

$x(t+T) - \phi_{i}(T)x(t) + D_{i}(T)u$ ... (2.1.3) where  $\Phi_{i}(T) = e^{A_{i}T}$ ; i = 1, 2

$$Di(T) = e^{A_{i}T} \left[ \int_{O}^{T} e^{-A_{i}S} dS \right] bi ; i=1,2$$

...(2.1.4)

¢i(T) and Di(T) for any given T can be computed either analyticall or numerically. If they are computed numerically, the following Taylor series expansion is used :

$e^{A_{i}T} = I + A_{i}T + \frac{(A_{i}T)^{2}}{2I} + \frac{(A_{i}T)^{3}}{2I} + \dots; i=1,2\dots(2.1.5)$ 2.2. AVERAGING TECHNIQUE

This technique is based on Equivalent Circuit manipulation and is discussed in (1). Here non-linear circuits are converted into single equivalent linear circuit by averaging the forcing functions. Here we will develop these equivalent linear circuits for the three basic power stages, Buck, Boost and Buck-Boost.

First we will take Boost power stage circuit. The general circuit and equivalent circuit of this power stage are shown in Fig.2.2.1(a) and (b) respectively. Duty cycle d(t) is defined as :

$$d(t) = \begin{cases} 1 \text{ Switch closed} \\ 0 \text{ Switch open} \end{cases} \dots (2, 2.1)$$

Since thn state variable response times are always much greater than the nominal switching period T, therefore the forcing functions (sources) may be averaged over a time interval T in the following manner :

$$\langle d \rangle (t) = \frac{1}{T} \int_{t-T}^{t} d(x) dx \qquad \dots (2.22)$$

With this approximation, the time averaged model of the Boost power stage is drawn in Fig. 2.2.1(c). In these circuits circles are used to denote independent sources, whereas squares are used for dependent generators. Similarly averaged models of Buck power stage and Buck Boost power stage are developed in Fig. (2.2.2) and Fig. (2.2.3) respectively. Since generator gains of Buck power stage averaged model are unity, this was further simplified to a linear circuit shown in Fig. 2.2.2(c).

#### Analysis of Response to Source Variations :

Now we will assume that the average duty ratio is constant and we take D as numerically equal to the dc average of d(t) i.e.

$$\langle d \rangle$$

(t) = D ... (2.23)

When we substitute this assumption in average model of Buck power stage of Fig. 2.2.2(c) we get equivalent linear circuit shown in Fig. 2.2.4(a). This relates unspecified source variations to the corresponding output variations for the Buck power stage. Similarly for Boost and Buck-Boost power stages we define a complementary duty ratio D' as

$$D' \equiv 1 - D$$

... (2.2.4)

The Averaged Boost and Buck-Boost Power Stage models after substitution of Eq. (2.2.4) are shown in Fig. 2.2.5(a) and 2.2.6(a) respectively. To eliminate dependent generators, constant generator gains must be unity. For this we divide voltage sources and impedance values by D', so that the current <i> will remain unchanged. Similarly to maintain <v> unchanged, we divide current generator gain by D' and multiply impedances by D'. The circuits, after normalizing the constant generator gains to unity, of Boost and Buck-Boost models are shown in Fig. 2.2.5(b) and Fig. 2.2.6(b). These circuits are further simplified to Fig. 2.2.5(c) and Fig. 2.2.6(c). The averaged circuits in Fig. 2.2.4(a), 2.2.5(c) and 2.2.6(c) are equivalent linear circuits for Buck, Boost and Buck-Boost power stages respectively for source variations and constant control. These circuits are useful for analysis of either transient or frequency responses caused by variations in the source voltage.

#### Analysis of Response to Control Variations:

We will now consider the situation when the averaged source voltage is constant

i.e.

$$\langle v_{S} \rangle$$

(t) =  $V_{S}$  ...(2.2.5)

and the averaged duty ratio  $\langle d \rangle$  is fluctuating with time. Using this substitution in Average model of Buck power stage of

Fig. 2.2.2(c), we get equivalent linear circuit shown in Fig. 2.2.4(b). But when this substitution of Eq. (2.2.5) is applied in Averaged models of Boost Fig. 2.2.1(c) and Buck-Boost Fig. 2.2.3(c), these models are nonlinear for variations of the duty ratio and therefore a different approach is required.

For this approach we consider the control perturbation

i.e.  $\langle d \rangle$  (t) = D +  $\hat{d}$ (t) ...(2.2.6)

where  $\hat{d}$  is a time varying perturbation of the duty ratio D.

<1-d> (t) = 1 - [D +

$$\hat{d}(t)$$

]

= 1 - D -  $\hat{d}(t)$

= D'- $\hat{d}(t)$  ...(2.2.7)

The effect on state variables due to control perturbation may be expressed as :

$$\langle v \rangle$$

(t) = V +  $\hat{v}$ (t) ...(2.2.8)

(i) (t) = I +  $\hat{i}$ (t) ...(2.2.9)

When the above perturbations are substituted in Fig. 2.2.1(c), the equivalent circuit of the averaged boost power stage becomes as shown in Fig. 2.2.7(a). To find  $\hat{v}$ in terms of  $\hat{d}$  we split this circuit Fig. 2.2.7(a) into unperturbed values (steady state equivalent circuit) Fig.2.2.' and perturbed values as in Fig. 2.2.7(c). This circuit can be linearized by neglecting second order terms  $\hat{dv}$  and  $\hat{di}$  as in Fig. 2.2.8(a). After separating dependent and independent generators, this circuit becomes as in Fig. 2.2.8(b). This circuit can further be simplified by normalizing the gains to unity as in Fig. 2.2.8(c). Fig. 2.2.8(d) shows the final equivalent circuit for variation for Boost power stage model when the averaged source voltage is constant.

The steady state equivalent circuit of Fig. 2.2.7(b) is simplified in Fig. 2.2.9. The relationship between  $\hat{d}$  and  $\hat{v}$ can not be obtained from Fig. 2.2.8(c) directly, due to the presence of two generators. But since this circuit is linear, Laplace transforms can be manipulated using Thevenin and Nortons equivalents to combine the generators into the single source as shown in Fig. 2.2.10.

Fig. 2.2.9(b) and Fig. 2.2.10 show the equivalent circuits of the averaged boost power stage model for small control variations and constant source for steady state and linearized for variations respectively.

Some procedure is applied for Buck-Boost power stage. When the perturbation from Eqn. (2.2.6) to (2.2.9) are substituted in Fig. 2.2.3(c), the Buck-Boost power stage model becomes as shown in Fig. 2.2.11. This circuit may be simplified as in the case of Boost power stage. The steady state equivalent circuit and its reduction is shown in Fig. 2.2.12. Similarly circuit for variations is shown in Fig. 2.2.13. Fig. 2.2.13(d) represents the equivalent linear circuit for variations for Buck-Boost power stage. As in the case of Boost power stage, since the circuit is linear, Laplace Transform can

be obtained using Thevenin and Norton equivalents to combine the generators into the single source and final linear circuit is shown in Fig. 2.2.14.

Since there is no Capacitor current or Inductor voltage in the steady state, the static source to output gain of each power stage configuration can easily be derived from the averaged power stage models with static conditions :

$$\langle v_s \rangle$$

(t) =  $V_s$

$\langle d \rangle (t) = D$

From Averaged Buck Power stage model of Fig. 2.2.2(c), with above conditions

$$\frac{V}{DV_{s}} = \frac{R}{R+R_{1}}$$

$$\frac{V}{V_{s}} = \frac{DR}{R+R_{1}}$$

...(2.2.10)

For steady state Boost Power stage model of Fig. 2.2.9

$$\frac{V}{\frac{1}{D}V_{s}} = \frac{D^{t}R}{D^{t}R + \frac{R_{1}}{D^{t}}}$$

0

or

or

$$\frac{D^{*}V}{V_{s}} = \frac{(D^{*})^{2}R}{(D^{*})^{2}R+R_{1}}$$

or  $\frac{V}{V_{s}} = \frac{D^{*}R}{(D^{*})^{2}R+R_{1}}$  ...(2.2.11)

For steady state Buck-Boost power stage model of Fig. 2.2.12(c)

17; Bould Prover Step Collection

and and a second se

and the second second

.

the second construction of the second second

CAR A CONTRACT STREET

And the second second

•

(19) AVENIATION NO.

Charles March 1997 - Anna 1

.

.

**`**

. .

> . .

. 4

×

. .

¥

$D'R_c$ , ,

$$\frac{V}{\frac{D}{D^{\prime}} V_{s}} = \frac{D^{\prime}R}{D^{\prime}R + \frac{R_{1}}{D^{\prime}}}$$

or

$$\frac{V}{V_{s}} = \frac{DD'R}{(D')^{2}R + R_{1}} \qquad \dots \ (2.2.12)$$

Thus the Averaging technique characterizes the low frequency response of switched power stage. The above analysis reveals one interesting thing that when we consider averaged control duty cycle <d> fluctuating with time, the averaged Buck power stage circuits becomes linear whereas averaged Boost and Buck-Boost models are nonlinear for which perturbations were considered.

### 2.3. STATE SPACE AVERAGING

The previous techniques, state space modelling (6) and Averaging technique (1) have little correlation between each other. The first approach is in the domain of equation manipulation whereas Averaging technique is based on equivalent circuit manipulation.

In this section the state-space averaging method is developed first in general for any dc- to - dc switching converter, and then demonstrated in detail for the particular case of the boost power stage in which parasitic effects (esr of the capacitor and series resistance of the inductor) are included General equations for both steady state (dc) and dynamic performance (ac) are obtained, from which important transfer functions are derived and also applied to the special case of the boost

power stage.

Basic State-Space Averaged Model :

The basic dc- to - dc level conversion function of switching converters is achieved by repetitive switching between two linear networks. We assume that the circuit operates in the Continuous conduction mode, therefore, there are only two different 'states' of the circuit. If we take a boost power stage circuit shown in fig. 2.3.1(a), for analysis, the two linear circuit models, when switch is ON and when switch is OFF can be represented as in Fig. 2.3.1(b) & (c) respectively.

These two states may be represented by the corresponding set of state-space equations :

(i) Interval Td  $x = A_1x + b_1v_g$   $y_1 = C_1^T x$ (ii) Interval Td  $x = A_2x + b_2v_g$   $y_2 = C_2^T x$ (iii) Interval Td  $y_2 = C_2^T x$ (iii) Interval Td

where Td : interval when the switch is ON

$T(1-d) = Td^{1}$ : interval when the switch is OFF, as shown in fig. 2.3.2.

The objective now is to replace these two state space descriptions of the two successive phases of the switching cycle T by a single state space description which represents approximately the behaviour of the circuit across the whole period T. For this we take the average of both dynamic and static equations for the two switched intervals (2.3.1), in the following manner :

Ň

. .

$$\dot{\mathbf{x}} = \mathbf{d} (\mathbf{A}_{1}\mathbf{x} + \mathbf{b}_{1}\mathbf{v}_{g}) + \mathbf{d}^{*} (\mathbf{A}_{2}\mathbf{x} + \mathbf{b}_{2}\mathbf{v}_{g})$$

$$\mathbf{y} = \mathbf{d}_{1}\mathbf{y}_{1} + \mathbf{d}^{*} \cdot \mathbf{y}_{2} \qquad \dots (2.3.2)$$

$$= (\mathbf{d}\mathbf{c}_{1}^{T} + \mathbf{d}^{*}\mathbf{c}_{2}^{T})\mathbf{x}$$

After rearranging (2.3.2) we obtain the basic averaged state space description over a single period T:

$$\dot{\mathbf{x}} = (d\mathbf{A}_1 + d^{\dagger}\mathbf{A}_2) \mathbf{x} + (d\mathbf{b}_1 + d^{\dagger}\mathbf{b}_2) \mathbf{v}_g \qquad \dots (2.3.3).$$

$$\mathbf{y} = (d\mathbf{C}_1^{\mathrm{T}} + d^{\dagger}\mathbf{C}_2^{\mathrm{T}}) \mathbf{x}$$

In essence, comparison between (2.3.3) and (2.3.1) shows that the system matrix of the averaged model is obtained by taking the average of two switched model matrices  $A_1$  and  $A_2$ , its control is the average of two control vectors  $b_1$  and  $b_2$ , and its output is the average of two outputs  $y_1$  and  $y_2$  over a period T.

The justification and the nature of the approximation in substitution for the two switched models of (2.3.1) by averaged model (2.3.3) is indicated in Appendix B.

If we now assume that the duty ratio d is constant from cycle to cycle, namely, d = D (steady state dc duty ratio) we get :

$$\dot{\mathbf{x}} = \mathbf{A}\mathbf{x} + \mathbf{b}\mathbf{v}_{g}$$

$$\mathbf{y} = \mathbf{C}^{T}\mathbf{x}$$

where  $\mathbf{A} = \mathbf{D}\mathbf{A}_{1} + \mathbf{D}^{T}\mathbf{A}_{2}$

$\mathbf{b} = \mathbf{D}\mathbf{b}_{1} + \mathbf{D}^{T}\mathbf{b}_{2}$

$\mathbf{C}^{T} = \mathbf{D}\mathbf{C}_{1}^{T} + \mathbf{D}^{T}\mathbf{C}_{2}^{T}$

...(2.3.4)

...(2.3.4)

...(2.3.5)

Since (2.3.4) is a linear system, superposition holds and it can be perturbed as in Averaging technique by introduction o line voltage variations  $\hat{v}_g$  as  $v_g = V_{g} + \hat{v}_g$ , where  $V_g$  is the dc line input voltage, causing a corresponding perturbation in the state vector  $x = \mathbf{X} + \hat{x}$ , where X is the dc value of the state vector and  $\hat{x}$  is the superimpdsed ac perturbation. Similarly,  $y = \mathbf{Y} + \hat{\mathbf{y}}$ . Putting these value in (2.3.4) :

$$\dot{\hat{x}} = A(X + \hat{x}) + b(V_g + \hat{v}_g)$$

$$\Psi + \hat{y} = C^T (X + \hat{x})$$

or

$$\dot{\hat{x}} = AX + bV_g + A\hat{x} + b\hat{v}_g$$

...(2.3.6)

$$Y + \hat{Y} = C^{T} X + C^{T} \hat{X}$$

Separating steady state (dc) part from the dynamic (ac) part, we get :

Steady state (dc) model :

$AX + bV_{g} = 0$ ;  $Y = C^{T}X$

or

$$X = -A^{-1}bV_g$$

;  $Y = -C^TA^{-1}bV_g$  ...(2.3.7)

dynamic (ac) model :

$$\hat{\mathbf{x}} = \mathbf{A}\hat{\mathbf{x}} + \mathbf{b}\hat{\mathbf{v}}_{g}$$

$\hat{\mathbf{y}} = \mathbf{C}^{T}\hat{\mathbf{x}}$  ...(2.3.8)

From the ac model, the line voltage to state vector transfer functions can be easily derived as :

$$s\hat{x}(s) = A\hat{x}(s) + b\hat{v}_{g}(s) \qquad \dots (2.3.9)$$

$$\hat{y}(s) = C^{T}\hat{x}is$$

or

$$\frac{\hat{x}(s)}{\hat{v}_{g}(s)} = (sI - A)^{-1}b \qquad \dots (2.3.10)$$

$$\frac{\hat{y}(s)}{\hat{v}_{g}(s)} = C^{T}(sI - A)^{-1}b$$

We now will include the duty ratio modulation effect into the basic averaged model (2.3.3).

# Perturbation :

Now suppose the duty ratio changes from cycle to cycle, that is,

$$d(t) = D + d$$

where  $\hat{d}$  is a superimposed (ac) variation. Put these values in (2.3.3) :

$$\begin{aligned} \dot{\mathbf{x}} &= \left\{ (\mathbf{D}+\hat{\mathbf{d}})\mathbf{A}_{1} + (\mathbf{1}-\mathbf{D}-\hat{\mathbf{d}})\mathbf{A}_{2} \right\} (\mathbf{X}+\hat{\mathbf{x}}) + \left[ (\mathbf{D}+\hat{\mathbf{d}})\mathbf{b}_{1} + (\mathbf{1}-\mathbf{D}-\hat{\mathbf{d}})\mathbf{b}_{2} \right] (\mathbf{V}_{g}+\hat{\mathbf{v}}_{g}) \\ \mathbf{y}+\hat{\mathbf{y}} &= \left\{ (\mathbf{D}+\hat{\mathbf{d}})\mathbf{C}_{1}^{\mathrm{T}} + (\mathbf{1}-\mathbf{D}-\hat{\mathbf{d}})\mathbf{C}_{2}^{\mathrm{T}} \right\} (\mathbf{X}+\hat{\mathbf{x}}) \\ \text{or} \quad \dot{\hat{\mathbf{x}}} &= (\mathbf{D}\mathbf{A}_{1}+\mathbf{D}\mathbf{A}_{2})\mathbf{x} + (\mathbf{D}\mathbf{A}_{1}+\mathbf{D}^{*}\mathbf{A}_{2})\hat{\mathbf{x}} + (\mathbf{A}_{1}-\mathbf{A}_{2})\hat{\mathbf{d}}\mathbf{x} + (\mathbf{A}_{1}-\mathbf{A}_{2})\hat{\mathbf{d}}\hat{\mathbf{x}} \\ &+ (\mathbf{D}\mathbf{b}_{1}+\mathbf{D}^{*}\mathbf{b}_{2})\mathbf{v}_{g} + (\mathbf{D}\mathbf{b}_{1} + \mathbf{D}^{*}\mathbf{b}_{2})\hat{\mathbf{v}}_{g} + (\mathbf{b}_{1}-\mathbf{b}_{2})\hat{\mathbf{d}}\mathbf{v}_{g} + (\mathbf{b}_{1}-\mathbf{b}_{2})\hat{\mathbf{d}}\hat{\mathbf{v}}_{g} \\ &\mathbf{Y}+\hat{\mathbf{y}} &= (\mathbf{D}\mathbf{C}_{1}^{\mathrm{T}} + \mathbf{D}^{*}\mathbf{C}_{2}^{\mathrm{T}}) (\mathbf{X}+\hat{\mathbf{x}}) + (\mathbf{C}_{1}^{\mathrm{T}} - \mathbf{C}_{2}^{\mathrm{T}})\hat{\mathbf{d}}(\mathbf{X}+\hat{\mathbf{x}}) \\ \text{or} \quad \dot{\hat{\mathbf{x}}}=\mathbf{A}\mathbf{X}+\mathbf{b}\mathbf{v}_{g} + \mathbf{A}\hat{\mathbf{x}}+\mathbf{b}\hat{\mathbf{v}}_{g} + \left[ (\mathbf{A}_{1}-\mathbf{A}_{2})\mathbf{X} + (\mathbf{b}_{1}-\mathbf{b}_{2})\mathbf{v}_{g} \right] \hat{\mathbf{d}} + \left[ (\mathbf{A}_{1}-\mathbf{A}_{2})\hat{\mathbf{x}} + (\mathbf{b}_{1}-\mathbf{b}_{2})\hat{\mathbf{v}}_{g} \right] \end{aligned}$$

dc.term line va- duty ratio nonlinear second riation variation order term

$$Y + \hat{Y} = C^{T}X + C^{T}\hat{X} + (C^{T}_{1} - C^{T}_{2}) \times \hat{d} + (C^{T}_{1} - C^{T}_{2})\hat{X} \hat{d} \dots (2.3.11)$$

d.c. a.c. a.c. term nonlinear term

term term

The above perturbed state space eugations are nonlinear owing to the presence of the product of the two time dependent quantities  $\hat{\mathbf{x}}$  and  $\hat{\mathbf{d}}$ .

## Linearization and Final State Space Averaged Model :

Small Signal Approximation : Variations in the steady state values are negligible compared to the steady state values them - selves, i.e.

$$\frac{v_g}{v_g} <<1 ; \frac{\hat{d}}{D} <<1 ; \frac{\hat{x}}{x} <<1.$$

...(2.3.12)

Using above approximation we can neglect second order terms and we get

$$\dot{\hat{x}} = A X + b V_g + A \hat{x} + b \hat{v}_g + [(A_1 - A_2) X + (b_1 - b_2) V_g] \hat{d}$$

$$Y + \hat{y} = C^T X + C^T \hat{x} + (C_1^T - C_2^T) X \hat{d}$$

which is a linear system.

Separating steady state (d.c.) and dynamic (a.c.) part we steady state (d.c.) model :

$$X = -A^{-1}bV_{g}$$

;  $Y = C^{T}X$  ...(2.3.13)

=  $C^{T}A^{-1}bV_{g}$

Dynamic (ac) model :

$$\dot{\hat{x}} = A\hat{x} + b\hat{v}_{g} + [(A_{1} - A_{2})X + (b_{1} - b_{2})V_{g}]\hat{d} \dots (2.3.14)$$

$$\hat{y} = C^{T}\hat{x} + (C_{1}^{T} - C_{2}^{T})X\hat{d}$$

Equations (2.3.13) and (2.3.14) represent the small signal low frequency model of any dc to dc switching converter working in the continuous conduction mode.

Boost Power Stage with Parasitics : We will now illustrate an example of Boost Power stage. With assumption of ideal switches, the two switched models of Fig. (2.3.1)(a) are shown in fig. 2.3.1(b) & (c). We take inductor current i and capacitor voltage v as state variables, i.e.

$$x = \begin{bmatrix} i \\ v \end{bmatrix}$$

Intermal Td : Fig. 2.3.1(b)

$v_{g} = R_{1}i + L \cdot \frac{di}{dt} \qquad y_{1} = R \cdot \frac{v}{R+R_{c}} \qquad v = -\frac{1}{C} \int \frac{v}{R+R_{c}} dt$ or  $\frac{di}{dt} = -\frac{R_{1}}{L}i + \frac{v_{g}}{L} \qquad \qquad or \frac{dv}{dt} = -\frac{1}{C} \cdot \frac{v}{R+R_{c}}$  $\therefore \begin{bmatrix} i \\ * \end{bmatrix} = \begin{bmatrix} -\frac{R_{1}}{L} & 0 \\ 0 & -\frac{1}{C(R+R_{c})} \end{bmatrix} \begin{bmatrix} i \\ v \end{bmatrix} + \begin{bmatrix} \frac{1}{L} \\ 0 \end{bmatrix} v_{g}$

$$\mathbf{x} = \mathbf{A}_{1}\mathbf{x} + \mathbf{b}_{1}\mathbf{v}_{g}$$

$$\mathbf{y}_{1} = \mathbf{C}_{1}^{T}\mathbf{x}$$

$$\mathbf{A}_{1} = \begin{bmatrix} -\frac{\mathbf{R}_{1}}{\mathbf{L}} & \mathbf{0} \\ \mathbf{0} & -\frac{1}{(\mathbf{R}+\mathbf{R}_{c})\mathbf{c}} \end{bmatrix} \quad \mathbf{b}_{1} = \begin{bmatrix} \frac{1}{\mathbf{L}} \\ \mathbf{0} \end{bmatrix} \quad \mathbf{C}_{1}^{T} = \begin{bmatrix} \mathbf{0} & \frac{\mathbf{R}}{\mathbf{R}+\mathbf{R}_{c}} \end{bmatrix}$$

$$\dots (2, 3, 15)$$

Interval Td' Fig. 2.3.1(c)

$$i_1 = \frac{y_2 - v}{R_c}$$

$$Y_2 = R(i-i_1) = R(i - \frac{Y_2 - V}{R_c})$$

= Ri -  $\frac{R}{R_c} Y_2 + \frac{R}{R_c} V$

or  $y_2 = \frac{RR_c}{R + R_c}i + \frac{R}{R + R_c}v = (R \parallel R_c)i + \frac{R}{R + R_c}v$

$$v_{g} = R_{1}i + L \cdot \frac{di}{dt} + Y_{2}$$

$$= R_{1}i + L \cdot \frac{di}{dt} + (R \cap R_{c})i + \frac{R}{R + R_{c}}v$$

or  $\frac{di}{dt} = -\frac{\frac{R}{l} + R \prod R_{c}}{L}$   $i - \frac{R}{L(R+R_{c})} v + \frac{1}{L} v_{g}$

$v = -\frac{1}{2} \int -i_1 dt$

$$=\frac{1}{C}\int \frac{(R \parallel R_{c}) i + \frac{R}{R+R_{c}} v - v}{R_{c}} dt$$

or  $\frac{dv}{dt} = \frac{1}{C} \frac{R \parallel R_C}{R_C} i - \frac{1}{C (R+R_C)} v$

*,* .

$$\begin{array}{c} \cdot \begin{bmatrix} \mathbf{I} \\ \mathbf{\dot{v}} \end{bmatrix} = \begin{bmatrix} -\frac{R_{1} + R \mathbb{I} R_{c}}{L} & -\frac{R}{L(R+R_{c})} \\ \frac{R}{(R+R_{c})C} & -\frac{1}{(R+R_{c})C} \end{bmatrix} \begin{bmatrix} \mathbf{\dot{i}} \\ \mathbf{\dot{v}} \end{bmatrix} + \begin{bmatrix} \frac{1}{L} \\ \mathbf{\dot{o}} \end{bmatrix} \mathbf{v}_{g} \\ \\ \cdot \mathbf{A}_{2} = \begin{bmatrix} -\frac{R_{1} + R \mathbb{I} R_{c}}{L} & -\frac{R}{L(R+R_{c})} \\ \frac{R}{C(R+R_{c})} & -\frac{1}{C(R+R_{c})} \end{bmatrix} \begin{bmatrix} \mathbf{\dot{i}} \\ \mathbf{\dot{v}} \end{bmatrix} + \begin{bmatrix} \frac{1}{L} \\ \mathbf{\dot{v}} \end{bmatrix} + \begin{bmatrix} \frac{1}{L} \\ \mathbf{\dot{v}} \end{bmatrix} \mathbf{v}_{g}$$

$$C_{2}^{T} = \left[ \frac{RR_{c}}{R+R_{c}} \qquad \frac{R}{R+R_{c}} \right] \qquad \dots (2.3.16)$$

Substitute these values in (2.3.5) we get

$$\begin{aligned} A &= DA_{1} + (1-D) A_{2} \\ &= D(A_{1}-A_{2}) + A_{2} \\ A &= D \begin{bmatrix} \frac{R_{C} u R}{L} & -\frac{R}{L(R+R_{C})} \\ -\frac{R}{(R+R_{C})C} & 0 \end{bmatrix} + \begin{bmatrix} -\frac{R_{1}+R_{C} u R}{L} & -\frac{R}{L(R+R_{C})} \\ -\frac{R}{(R+R_{C})C} & -(\frac{1}{(R+R_{C})C}) \\ -\frac{R}{(R+R_{C})C} & (1-D) \end{bmatrix} \\ &= \begin{bmatrix} -\frac{R_{1}}{L} - (1-D) & \frac{R_{C} u R}{L} \\ -\frac{R}{(R+R_{C})C} & (1-D) \\ -\frac{R}{(R+R_{C})C} & (1-D) \end{bmatrix} \\ &= -\frac{1}{(R+R_{C})C} \end{bmatrix} \end{aligned}$$

$$c^{T} = Dc_{1}^{T} + (1-D) c_{2}^{T} \\ &= D[c_{1}^{T} - c_{2}^{T}] + c_{2}^{T} \\ &= D[c_{1}^{T} - c_{2}^{T}] + c_{2}^{T} \\ &= D[-\frac{RR_{C}}{R+R_{C}} & 0] + \left[ \frac{RR_{C}}{R+R_{C}} - \frac{R}{R+R_{C}} \right] = \left[ \frac{RR_{C}(1-D)}{R+R_{C}} - \frac{R}{R+R_{C}} \right] \\ b = b_{1} = b_{2} = \begin{bmatrix} \frac{1}{L} \\ 0 \end{bmatrix}$$

Steady State (d.c.) model : From eq. (2.3.13)  $X = -A^{-1}b V_g$

$$|A| = \frac{R_{1} + (1-D)R_{c} ||R|}{LC(R+R_{c})} + \frac{R^{2}(1-D)^{2}}{LC(R+R_{c})^{2}} = \frac{(R+R_{c})R_{1} + (1-D)R_{c} ||R| + R^{2}(1-D)}{LC(R+R_{c})^{2}}$$

$$A^{-1}b = \frac{LC (R+R_{c})}{R_{1}+(1-D)R_{c}^{11}R+\frac{R^{2}(1-D)^{2}}{R+R_{c}}} \begin{bmatrix} -\frac{1}{C(R+R_{c})} & \frac{R(1-D)}{L(R+R_{c})} \\ -\frac{R(1-D)}{C(R+R_{c})} & \frac{R_{1}+(1-D)R_{c}^{11}R}{L} \end{bmatrix} \begin{bmatrix} 1\\ 1\\ 0 \end{bmatrix}$$

$$= \frac{LC (R+R_{c})}{R_{1}+(1-D)^{2}R + D(1-D)R_{c} \parallel R} \begin{bmatrix} -\frac{1}{LC(R+R_{c})} \\ -\frac{R(1-D)}{LC(R+R_{c})} \end{bmatrix}$$

$$X = \begin{bmatrix} I \\ V \end{bmatrix} = -A^{-1}bV_{g} = \frac{V_{g}}{R'} \begin{bmatrix} 1 \\ R(1-D) \end{bmatrix}$$

where  $R' = R_1 + (1-D)^2 R + D(1-D) R_C || R$

$$Y = -C^{T}A^{-1}bV_{g} = \frac{V_{g}}{R!} \begin{bmatrix} \frac{RR_{c}(1-D)}{R+R_{c}} & \frac{R}{R+R_{c}} \end{bmatrix} \begin{bmatrix} 1\\ R(1-D) \end{bmatrix}$$

or =

$$\frac{V_g}{R^*} \left[ \frac{RR_c(1-D)}{R+R_c} + \frac{R^2(1-D)}{R+R_c} \right]$$

$$= \frac{V_{g}}{R!} R (1-D) \qquad \dots (2.3.17)$$

where I is the dc inductor current, V is the dc capacitor voltage, and  $\mathbf{y}$  is the dc output voltage.

Dynamic (ac small signal model) :

From eq. (2.3.1.4)

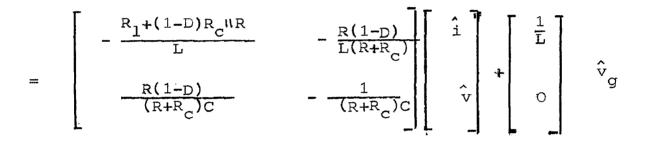

$$\dot{\hat{x}} = \frac{d}{dt} \begin{bmatrix} \hat{i} \\ \hat{v} \end{bmatrix} = \begin{bmatrix} -\frac{R_1 + (1-D)R_C \parallel R}{L} & -\frac{R(1-D)}{L(R+R_C)} \\ \frac{R(1-D)}{(R+R_C)C} & -\frac{1}{(R+R_C)C} \end{bmatrix} \begin{pmatrix} \hat{i} \\ \hat{v} \end{bmatrix} + \begin{bmatrix} \frac{1}{L} \\ 0 \\ 0 \end{bmatrix} \hat{v}$$

$$+ \frac{V_{g}\hat{d}}{R^{\dagger}} \begin{bmatrix} \frac{R_{c}^{\parallel}R}{L} & R \\ - \frac{R}{(R+R_{c})C} & 0 \end{bmatrix} \begin{bmatrix} 1 \\ 1 \\ (1-D)R \end{bmatrix}$$

$$\left[ \begin{array}{c} \frac{R}{L} & \frac{D'R + R_{c}}{R+R_{c}} \\ - \frac{R}{(R+R_{c})c} \end{array} \right]$$

$$\hat{\mathbf{Y}} = \begin{bmatrix} (1-D)(\mathbf{R}_{C} \mathbf{i} \mathbf{R}) & \frac{\mathbf{R}}{\mathbf{R} + \mathbf{R}_{C}} \end{bmatrix} \begin{bmatrix} \hat{\mathbf{i}} \\ \hat{\mathbf{v}} \end{bmatrix} + \begin{bmatrix} -\mathbf{R} \mathbf{i} \mathbf{R}_{C} \\ \mathbf{R} \end{bmatrix} \begin{bmatrix} 1 \\ \mathbf{R} (1-D) \end{bmatrix} \begin{bmatrix} \mathbf{V}_{g} \\ \mathbf{R} \mathbf{i} \end{bmatrix} \hat{\mathbf{R}} \hat{\mathbf{d}}$$

$$= \begin{bmatrix} (1-D)\mathbf{R}_{C} \mathbf{i} \mathbf{R} \\ \mathbf{R} + \mathbf{R}_{C} \end{bmatrix} \begin{bmatrix} \hat{\mathbf{i}} \\ \hat{\mathbf{v}} \end{bmatrix} - \mathbf{V}_{g} \frac{\mathbf{R} \mathbf{i} \mathbf{R}_{C}}{\mathbf{R}^{T}} \hat{\mathbf{d}} \qquad \dots (2.3.18)$$

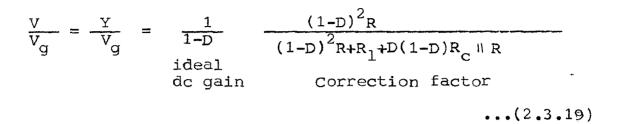

If we consider dc voltage transformation ratio from  $\epsilon_{\rm c}^{2.3.1}$  we get

If all parasitics are zero i.e.  $R_1=0$ ;  $R_c=0$ then dc voltage gain =  $\frac{1}{1-D}$  or  $\frac{1}{D}$

And in presence of parasitics, this gain is slightly reduced since correction factor is less than 1.

From the dynamic model (2.3.18) we can find the duty ratio to output and line voltage to output transfer functions.

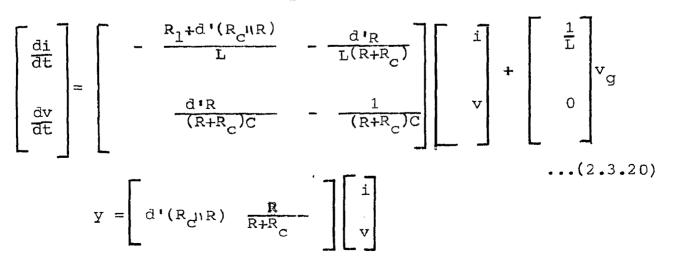

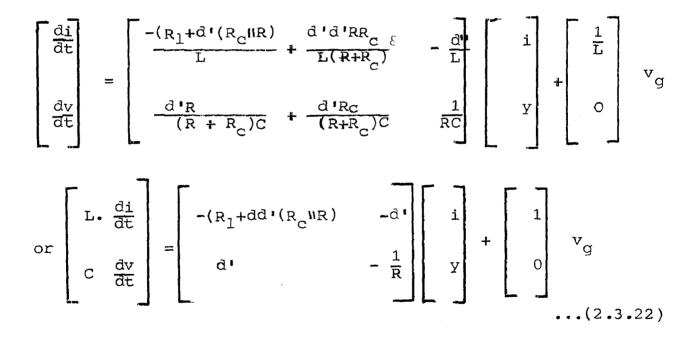

### circuit Realization :

By the basic overaged model given by eq. (2.3.3) we can find a useful circuit realization for any specific converter. Here we will demonstrate this circuit realization for the same boost power stage example:

Put the values of  $A_1$ ,  $A_2$ ,  $C_1 \& C_2$  in eqn. (2.3.3) we get

or  $y = d \cdot \frac{RR_c}{R+R_c} i + \frac{R}{R+R_c} v$

Capacitor voltage

$$v = \frac{R+R_{c}}{R} y - (1-d)R_{c}i$$

or

$$\begin{bmatrix} i \\ v \end{bmatrix} = \begin{bmatrix} 1 & 0 \\ -d'R_{c} & \frac{R+R_{c}}{R} \end{bmatrix} \begin{bmatrix} i \\ y \end{bmatrix} \dots (2.3.21)$$

Substitute eqn. (2.3.21) is eq. (2.3.20) we get

From the eqn. (2.3.22) we can reconstruct the circuit as in Fig. 2.3.3(a).

In this circuit realization we have taken non-perturbed values and therefore this model is valid for d.c. regime only.

. .

r

The two dependent generators can be treated as an ideal d':1 transformer as shown in Fig. 2.3.3(b).

The circuit model of Fig. 2.3.3(b) reduces to switched models in fig. 2.3.1(b) and 2.3.1(c) for d=1 & d=0 respectively. If d is constant i.e. d = D, the dc regime can be found easily by considering L to be short and C to be open. Hence the dc voltage gain (2.3.19) can be directly seen from fig. (2.3.3(b).

In the ideal d':1 transformer, turn ratio changes when the duty ratio is a function of time, d(t). It is through this ideal transformer that the actual controlling function is achieved when the feedback loop is closed.

#### The Canonical Circuit Model :

We know that the general final state space averaged model defined in eq. (2.3.13) & (2.3.14) gives complete description of the system behaviour. But in usual practice we need a circuit model which describes the input-output and control properties of the system. The Block diagram of such model is shown in Fig. 2.3.41.e. from State space averaged mode: we will derive a circuit model which directly gives the input output and control properties and is called as 'Canonical Circuit Model'.

Although in deriving this Canonical Model from State space averaged model, some information about the internal behaviour of some of the states will certainly be last, but there are many advantages of this Canonical model, specially in computerization. Since Canonical Circuit Model contains .

all the essential input-output and control properties of any dc - to - dc switching converter, regardless of its detailed configuration, therefore by this model different converters can be characterized in the form of a table and which can be conveniently stored in a computer data bank, which is very useful for Computer aided design and optimization.

A new Canonical Circuit Model is shown in Fig. 2.3.5. Any switching convert input-output model, regardless of its detailed configuration could be represented in this form.

Different converts are represented simply by an appropriate set of formulas for the four elements e(s), j(s),  $\mu$ , He(s) in the general equivalent circuit.

## Derivation of the Canonical Model through State Space :

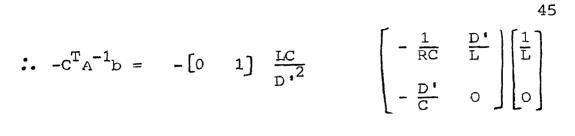

We will reproduce general state space averaged model (2.3.13) & (2.3.14) here :

$$X = -A^{-1}b V_{g} ; \qquad Y = c^{T}X$$

$$= -c^{T}A^{-1}bV_{g}$$

$$\dot{x} = A\hat{x} + b\hat{v}_{g} + [(A_{1}-A_{2})X + (b_{1}-b_{2})V_{g}] d\hat{x}$$

$$\dot{y} = c^{T}\hat{x} + (c_{1}^{T} - c_{2}^{T}) X d\hat{x}$$

Taking Laplace Transform we will get :

$$\hat{\mathbf{x}}(s) = (\mathbf{s}\mathbf{I} - \mathbf{A})^{-1} b \hat{\mathbf{v}}_{g}(s) + (\mathbf{s}\mathbf{I} - \mathbf{A})^{-1} \left[ (\mathbf{A}_{1} - \mathbf{A}_{2})\mathbf{x} + (\mathbf{b}_{1} - \mathbf{b}_{2})\mathbf{v}_{g} \right] \hat{\mathbf{d}}(s)$$

$$\hat{\mathbf{y}}(s) = \mathbf{C}^{T} \hat{\mathbf{x}}(s) + (\mathbf{C}_{1}^{T} - \mathbf{C}_{2}^{T})\mathbf{x} \hat{\mathbf{d}}(s) \qquad \dots (2 \cdot 3 \cdot 23)$$

Now, converter input-output relationship is defined as

$$\hat{y}(s) = G_{yg} \hat{v}_{g}(s) + G_{yd} \hat{d}(s)$$

$\hat{i}(s) = G_{ig} \hat{v}_{g}(s) + G_{id} \hat{d}(s)$  ...(2.3.24)

In which G's are known from (2.3.23). The subscripts of G's designate the corresponding transfer functions. For example  $G_{yg}$  is the source voltage  $\hat{v}_g$  to output voltage  $\hat{y}$  transfer function.

For the proposed canonical circuit model in fig. 2.3.5, we directly get :

$$\hat{Y}(s) = (\hat{v}_{g} + e(s)\hat{d}) \frac{1}{u} H_{e}(s)$$

$$\hat{1}(s) = j(s)\hat{d} + (e(s)\hat{d} + \hat{v}_{g}) \frac{1}{\mu^{2}Z_{ei}(s)} \dots (2.3.25)$$

$$\hat{Y}(s) = \frac{1}{\mu} H_{e}(s)\hat{v}_{g}(s) + e(s) \frac{1}{\mu}H_{e}(s)\hat{d}(s)$$

or

$$\hat{i}(s) = \frac{1}{\mu^2 Z_{ei}(s)} \hat{v}_g(s) + j + \frac{e(s)}{\mu^2 Z_{ei}(s)} \hat{d}(s)$$

...(2.3.26)

Compare (2.3.24) & (2.3.26)

$$G_{yg}(s) = \frac{1}{u} H_e(s) \qquad G_{yd} = e(s) \frac{1}{u} H_e(s)$$

$$= e(s) \cdot G_{yg}$$

$$G_{ig}(s) = \frac{1}{\mu^2 Z_{ei}(s)}$$

$$G_{id} = j(s) + \frac{e(s)}{\mu^2 Z_{ei}(s)}$$

$$= j(s) + e(s)G_{ig}(s)$$

$$: e(s) = \frac{G_{yd}(s)}{G_{yg}(s)} \qquad j(s) = G_{id}(s) - e(s) G_{ig}(s) \qquad \dots (2.3.27)$$

$$H_e(s) = \mu G_{yg}(s)$$

$\boldsymbol{\mu}$  could be calculated from :

$$\frac{Y}{V_g} = -C^T A^{-1} b = \frac{1}{\mu} \text{ correction factor.} \qquad \dots (2.3.28)$$

e(s) and j(s) can be defined as

e(s) = E

$$f_1(s)$$

j(s) = J  $f_2(s)$

where  $f_1(0) = f_2(0) = 1$ , and E&J are the dc gains of the frequency dependent functions e(s) & J(s) respectively.

## Example : Ideal Boost Power State -

From (2.3.18) with  $R_1=0 \& R_c=0$ , the final state space averaged model for Boost Power Stage becomes :

$$\begin{bmatrix} \frac{d\hat{1}}{dt} \\ \frac{d\hat{v}}{dt} \\ \frac{d\hat{v}}{dt} \\ \end{bmatrix} \begin{bmatrix} 0 & -\frac{D'}{L} \\ \frac{D'}{C} & -\frac{1}{RC} \\ A \end{bmatrix} \begin{bmatrix} \hat{1} \\ \hat{v} \\ \hat{v} \\ \frac{D'}{r} \end{bmatrix} + \begin{bmatrix} 1 \\ 1 \\ 0 \\ 0 \\ \frac{1}{r} \\ 0 \end{bmatrix} \hat{v}_{g} + \begin{bmatrix} \frac{RD'}{L} \\ -\frac{1}{C} \\ \frac{1}{C} \\ \frac{D'^{2}R}{D'^{2}R} \hat{d} \\ \dots (2.3.29) \\ \dots (2.3.29) \\ \hat{y} = \begin{bmatrix} 0 & 1 \\ 0 \\ C^{T} \end{bmatrix} \begin{bmatrix} 1 \\ \hat{v} \\ \hat{v} \end{bmatrix}$$

$$=\frac{1}{D}$$

Put in eq. (2.3.28)

$$\mathcal{L} = 1 - D$$

$$\frac{d\hat{i}}{dt} = -\frac{D'}{L}\hat{v} + \frac{1}{L}\hat{v}_{g} + \frac{V_{g}}{LD'}\hat{d}$$

$$\frac{d\hat{v}}{dt} = \frac{D'}{C}\hat{i} - \frac{1}{RC}\hat{v} - \frac{1}{C}\frac{V_{g}}{D'^{2}R}\hat{d}$$

Taking Laplace Transform, we get

.

or

Solving eqn. (2.3.30) for i(s) we get

$$i(s) = \frac{1 + sRC}{sL(1+sRC)+D'^{2}R} \hat{v}_{g}(s) + \frac{2 + sRC}{D' sL(1+sRC)+D'^{2}R} V_{g}d$$

Compare with (2:3.24)

$G_{ig}(s) = \frac{1 + sRC}{sL(1+sRC) + D^2R} \qquad G_{id}(s) = \frac{2 + sRC}{sL(1+sRC) + D^{\prime 2}R} V$

$$: j(s) = \frac{2 + sRC}{sL(1+sRC)+D^{2}R} - \frac{D^{2}R - sL}{D^{2}R} \cdot V$$

$$\frac{(1 + \text{sRC})}{\text{sL}(1+\text{sRC}) + D^{2}R}$$

After solving we get

$$j(s) = \frac{V}{D^{1/2}R} \qquad \therefore \qquad J = \frac{V}{D^{1/2}R} \qquad f_2(s) = 1$$

Expressions for the elements in the canonical equivalent circuit can be found in a similar way for any converter configuration. Results for the three common converts, the buck, boost, and buck-boost power stages are summarized in table 1.

| Table 1        |                 |                  |                            |                       |                    |                         |                           |

|----------------|-----------------|------------------|----------------------------|-----------------------|--------------------|-------------------------|---------------------------|

|                | μ(D)            | E                | f <sub>1</sub> (s)         | J                     | f <sub>2</sub> (s) | Le                      | Re                        |

| Buck           | 1<br>D          | $\frac{V}{D^2}$  | 1                          | V<br>R                | 1                  | L                       | Rl                        |

| Boost          | 1-D             | V                | $1-s\frac{L_e}{R}$         | $\frac{V}{(1-D)^2 R}$ | 1                  | $\frac{L}{(1-D)^2}$     | $\frac{R_{1}}{(1-D)^{2}}$ |

| Buck-<br>Boost | <u>1-D</u><br>D | $-\frac{V}{D^2}$ | $1-D \frac{R_e + sL_e}{R}$ | $-\frac{V}{(1-D)^2R}$ | 1                  | L<br>(1-D) <sup>2</sup> | $\frac{R_1}{(1-D)^2}$     |

The negative sign E & J in case of Buck-Boost power stage indicates the inverting polarity of the ideal transformer. Therefore for positive input dc voltage  $V_g$ , the input dc voltage V is negative.

## 2.4. Modelling of Modulator :

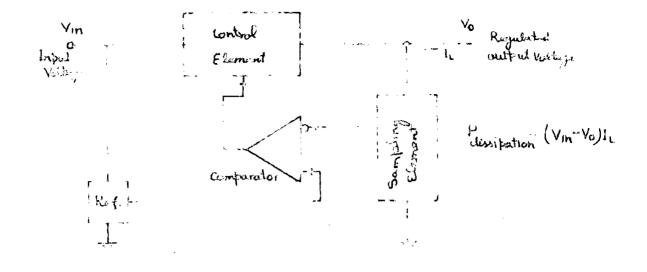

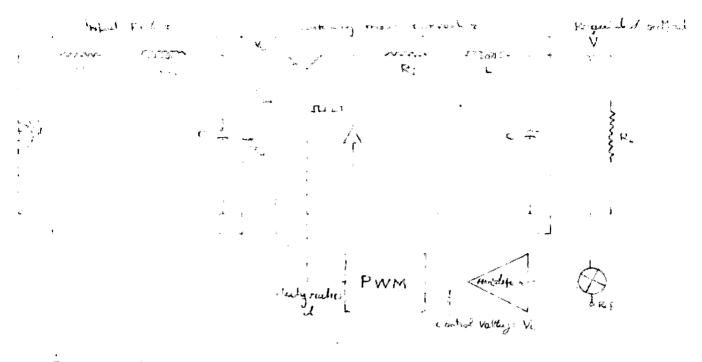

We have discussed about the switching mode converter in the previous sections. Now a general representation of a switchin mode regulator in which switching mode converter is represented by a buck-boost power stage, is shown in fig. 2.4.1.

We have already overcome the main difficulty in analysing the switching mode regulator viz. the modelling of its nonlinear part, the switching mode convert by obtaining the small signal low-frequency circuit model in the canonical circuit form.

Now in the next step we will develop a model for the modulator. This is easily done by writing an expression for the essential function of the modulator, which is to convert an (analog) control voltage  $V_c$  to theswitching duty ratio D. This expression can be written as

$$D = \frac{V_{C}}{V_{m}}$$

where  $V_m \equiv Range$  of control signal required to sweep the duty ratio over its full range from 0 to 1.

A small variation  $\hat{v}_c$  superimposed upon  $V_c$  therefore produces a corresponding variation  $\hat{d} = \frac{\hat{v}_c}{V_m}$  in D, which can be

INPUT FILTER & CONSTOL CARCUIT

FIG 242 FOUNDERT CHILDE OF COMPLETE CLOSED LOOP PERCULATOR

generalized to account for a nonuniform frequency response as :

$$\hat{\mathbf{d}} = \frac{\mathbf{f}_{m}(s)}{V_{m}} \hat{\mathbf{v}}_{c} \qquad \qquad \mathbf{f}_{m}(o) = 1$$

Thus, the control voltage to duty ratio small signal transmission characteristic of the modulator can be represented in general by the two parameters  $V_m$  and  $f_m(s)$ , regardless of the detailed mechanism by which the modulation is achieved.

Now if we substitute  $\hat{d}$  from the above equation in the two generators in canonical circuit model of the switching converter, the resulting model will be expressed in terms of the ac control voltage  $\hat{v}_c$ . Thus the resulting model will be a linear ac equivalent circuit that represents the small-signal transfer properties of the nonlinear processes in the modulator and converter

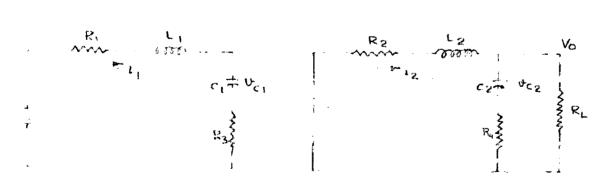

Now if we add the linear amplifier and the input and output filters, we obtain the ac equivalent circuit of the complete closed loop regulator as shown in Fig. 2.4.2.

In the circuit the modulator transfer function has been incorporated in the generator designation and therefore in the closed loop regulator, the generators no longer are independent but are dependent on another signal in the same system.

The current generator in fig. 2.4.2 is responsible for the interaction between the switching mode regulator-converter and the input filter, thus causing performance degradation and/or stability problems when an arbitrary input filter is added. The design of the input filter will be discussed in next section.

Thus as shown in fig. 2.4.2, we have succeeded in obtainin

the linear circuit model of the complete switching moderegulator. Hence the well known body of linear feedback theory can be used for both analysis and design of this type of regulator.

Now let us summarize the modelling aspect of switching mode regulator. A general method for modelling power stages of any switching dc- to - dc converter has been developed through state-space averaging approach. The fundamental step is in replacement of the state space descriptions of the two switched networks (2.3.1) by their average over the single switching period T, which results in a single continuous state-space equation description (2.3.3) designated the basic averaged state space model.

After some perturbation and linearization steps, a final state space averaged model is given by (2.3.13) & (2.3.14). From these equations a Canonical circuit model of fig. 2.3.5 was developed. Different converters are represented simply by an appropriate set of formulas (2.3.27) & (2.3.28) for four element in this general equivalent circuit. Besides its unified description, one of the advantages of the canonical circuit model is that various performance characteristics can be compared in a quick and easy manner.

## CHAPTER - III

DESIGN AND ANALYSIS OF SWITCHING CONVERTERS

- 3.1(a) Introduction

- 3.1(b) Input Filter Considerations in Design and Application of Switching Mode Regulators

3.1.1 Necessity of Input Filter 3.1.2 Ways of designing an Input Filter 3.1.3 Oscillation problem 3.1.4 Small Signal Average Model

- . 3.2 Input Filter Design

- 3.2.1 Single Stage Input Filter Configurations 3.2.2 Input Filter Interactions Loop Stability & Transient Response and Audiosusceptibility.

- 3.2.3 Optimal Input Filter Configuration & Design Constraints

- 3.3 Analysis of Switching Mode Converters with Input Filter.

#### 3.1 INTROLUCTION

We have discussed the modelling of switching mode converter and developed a canonical circuit model which describes the input-output and control properties of the system. Now in this section we will analyse some switching mjode converters with input filters. The effect of input filter on system performance will be discussed and a comparative study will be made for switching mode converters with single stage and two stage input filter. Design constraints for optimal input filter configuration are also obtained.

In case of two stage filter, the constraints of optimal design becomes very complicated and difficult to solve. Some approximations are made to simplify these equations and the effects of these approximations on input filter and system performance are also discussed.

# Input Filter Considerations in Design and Application of Switching Mode Regulator

As we have discussed, at power levels above a few hundred watts, switching mode regulators are more useful because of the significantly higher efficiency than can be obtained with linear dissipative regulators. But when we use switching regulators, the regulator input current has a substantial ripple component at the switching frequency. When more than one power supplies are connected to a common main as

> 176978 CENTRAL LIDERARY DEIVERSITY OF ROOMING

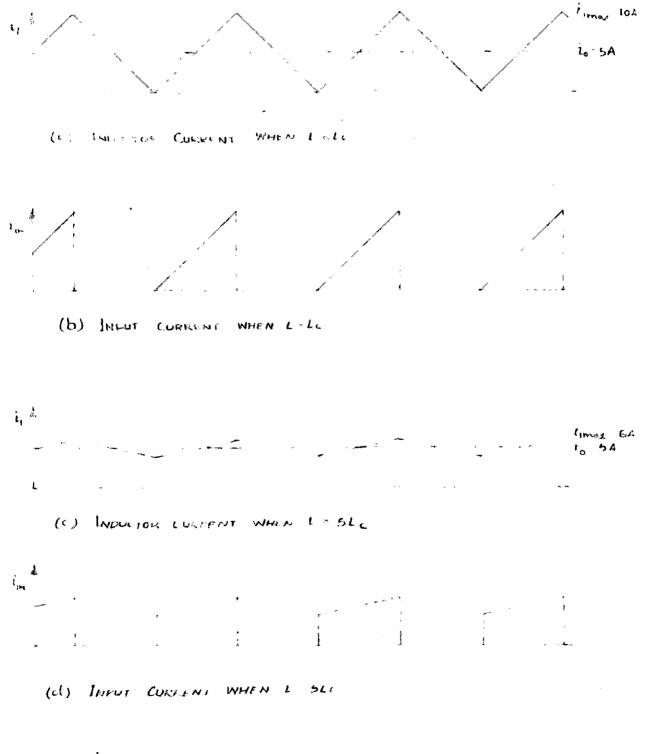

is shown in Fig. 3.1.1, the reflected ripple current of one of the power supplies may affect the performance of other power supplies, e.g. if we consider Buck type switching mode regulators of Fig. 1.3(a) its inductor current and input current is shown in Fig. 3.1.2. Fig. 3.1.2(a) & (b) show inductor inductor and input current respectively when L is equal to the critical inductance  $L_c$ . Fig. 3.1.2(c) & (d) show these currents when  $L = 5L_c$ . For battery driven systems, to meet this peak current requirement, capacity of the battery has to be increased very much. Moreover, it affects battery e.m.f. and therefore other power supplies connected to the **same** battery will also got affected.

Similarly, as shown in Fig. 3.1.1 when an apparatus such as a d.c. motor, a line printer etc. is connected to one of the power supplies, the noise generated in this apparatus and noise of one power supply is transmitted to the other power supplies which again affect the performance of other power supplies.

Therefore, to smooth the current drawn from the unregulated bine supply, use of an input filter is a necessity. One function of the input filter is to present a low pass transfer characteristic to current variations in the opposite direction. A switching mode regulator may demand an input current that has a large component at the switching frequency and input filter prevents this component from

FIG. 311 POWER SWATCHES COMMERCED TO COMMON MAINS

.

1 ... 7 1: INTAL OUT PUT CUTIPENT FOR BUCK TYPE SWITCHING

MODS. RECULTION

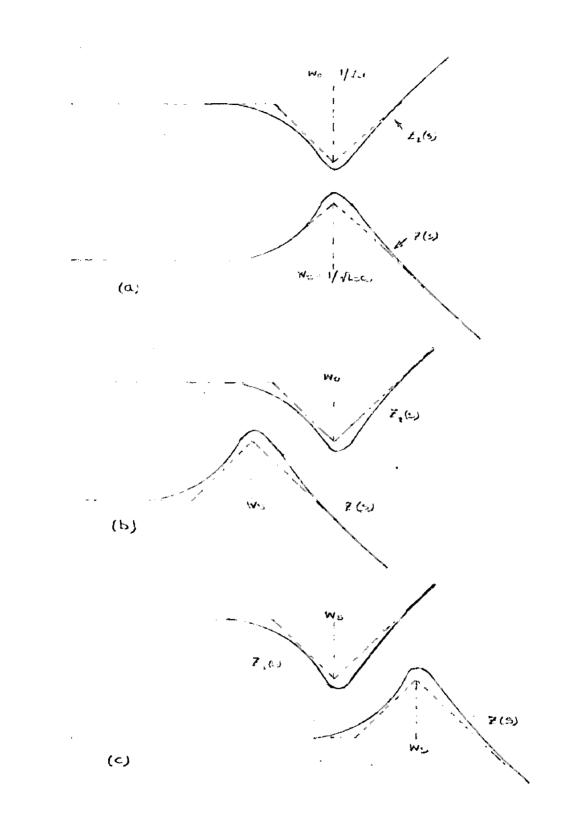

flowing in the line source. Another function of the input filter is to present a low pass transfer characteristic to the unregulated line voltage  $V_s$  in Fig. 2.4.1 so that higher frequency disturbances  $v_s$  are suitably attenuated at the regulator. These functions "forward voltage transfer function", and "reverse current transfer function" are defined by H( $\overline{s}$ ) as shown in Fig. 3.1.3 and called <u>Forward Transfer Characteristic</u> of input filter. This function H(s) is defined for the "unloaded filter, that is, without the regulator attached; this makes H(s) a property of the filter only, unaffected by the complex nature of the regulator input impedance.

This input filter serves to :

- prevent the regulator switching current from being reflected back into the source;

- 2) to isolate source voltage transients so as not to degrade the performance of the switching regulator down\_stream.

Consequently, the filter is required to provide not only high attenuation at the switching frequency but also sufficient damping against any line disturbance so that output peaking is properly controlled.

There may be two ways of designing an input filter for switching mode regulator :

(1) <u>Design Regulator and Input Filter Simultaneously</u>:

The preferred approach is to design the regulator

and input filter together so that the inequality condition for stability shown by equation (3.1.2) and other conditions may be satisfied.

## (2) Post Facto Design :

If the regulator is a 'black box' for which no information on its internal structure is available, we have to design the input filter on the basis of direct experimental measurements of input impedance  $z_i$  of the regulator and thus maintaining the inequality condition  $z_s < z_i$ . But such an input filter design procedure ensures only system stability, and does not guarantee that the regulator performance will remain essentially unaffected. Another drawback of this design is that the system may oscillate because of this inadequate input filter.

## Nature of the Oscillation Problem :

To understand this problem we will consider a Buck type switching regulator as shown in Fig. 2.4.1.

The switching mode converter acts as a dc transformer having some voltage conversion ratio  $\mu = V_S/V$  to the extent that the conversion is 100 percent efficient, the current conversion ratio is  $I_S/I = 1/\mu$  and the converter input power P =  $V_SI_S$  equals the output power VI. For a given load resistance  $R_L$ , the feedback action of the regulator adjusts the conversion ratio  $\mu$  to maintain constant output voltage and hence constant output power, even if the input voltage  $V_s$  varies. It follows that if  $V_s$  increases,  $I_s$  must decrease since the input power also remains constant. Consequently the regulator exhibits a negative incremental input resistance  $R_i$  given by -

$$R_{i} = \frac{dV_{s}}{dI_{s}} = \frac{d}{dI_{s}} \frac{P}{I_{s}} = \frac{P}{I_{s}^{2}} = -\frac{V_{s}}{I_{s}} = -\mu^{2} \frac{V}{I} = -\mu^{2}R_{L} (3.1.1)$$

This is the low frequency value of the regulator input impedance  $z_i$  indicated in fig. 2.4.1. For the basic Buck converter configuration shown, the conversion ratio is  $\mu = 1/D$  where D is the dc duty ratio of the power switch, so that  $R_i = -R_L/D^2$ .

The regulator negative input resistance  $R_i$  in combination with the input filter can under certain conditions constitutes a negative resistance oscillator, and is the origin of the system potential instability. The input filter output impedance  $z_s$  is a low (positive) resistance at dc and low frequencies, but in the neighbourhood of the filter cut-off frequency its output impedance rises to a resonant maximum  $|Z_s|_{max}$  which in a high Q filter may be many times the associated ohmic resistances, and if  $|Z_s|$  rises sufficiently that the net vircuit resistance becomes negative, oscillation will occur.

To explain further, let us consider the circuit of Fig. 3.1.4.

Equivalent impedance =

$$\frac{-|R_i| |Z_s|}{|Z_s| - |R_i|}$$

Therefore if  $|R_i| < |z_s|$ , the net resistance becomes negative and

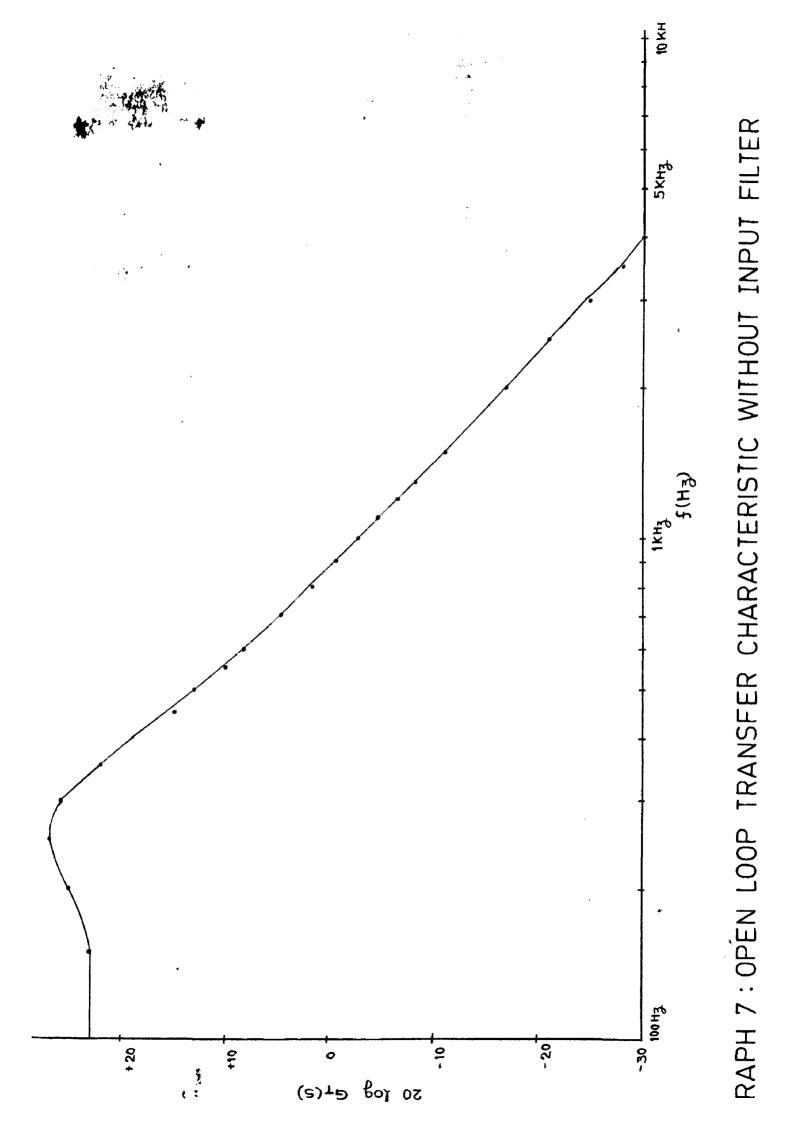

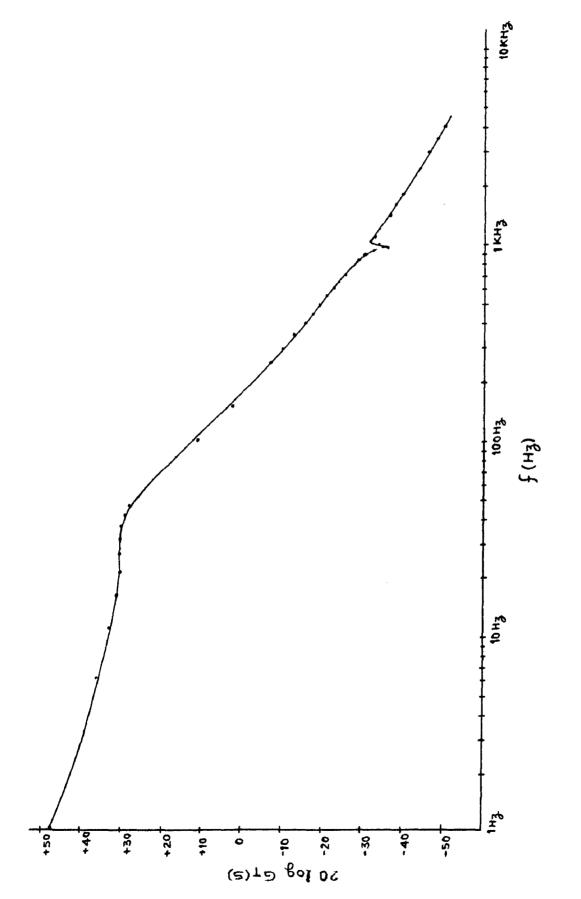

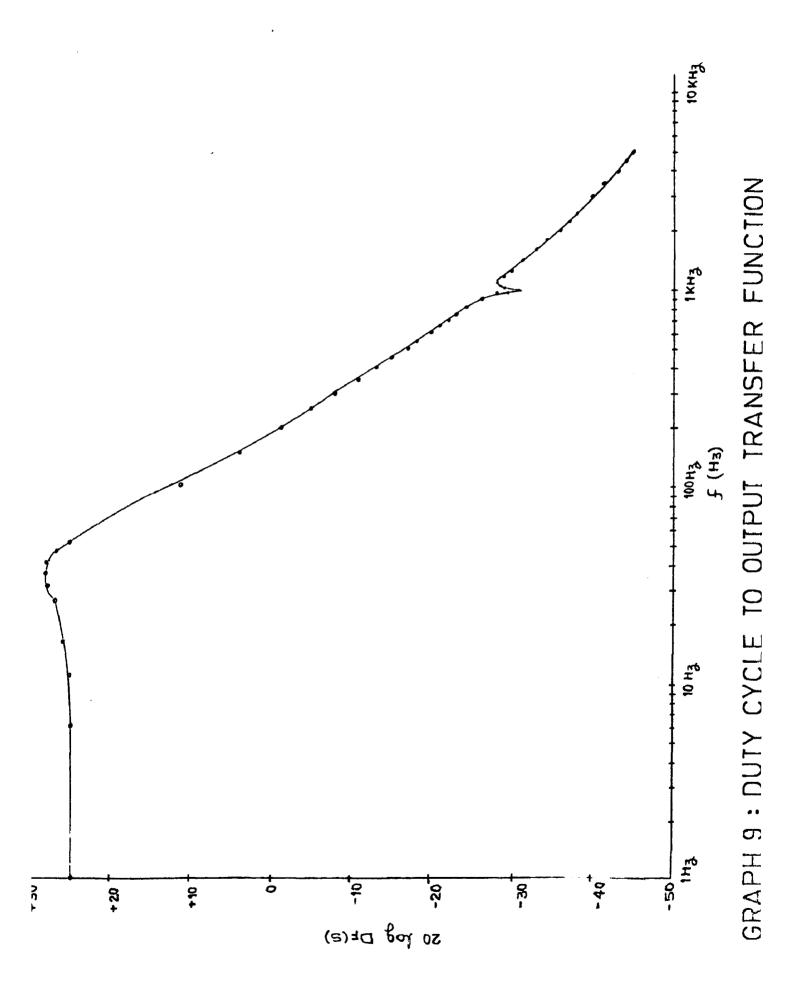

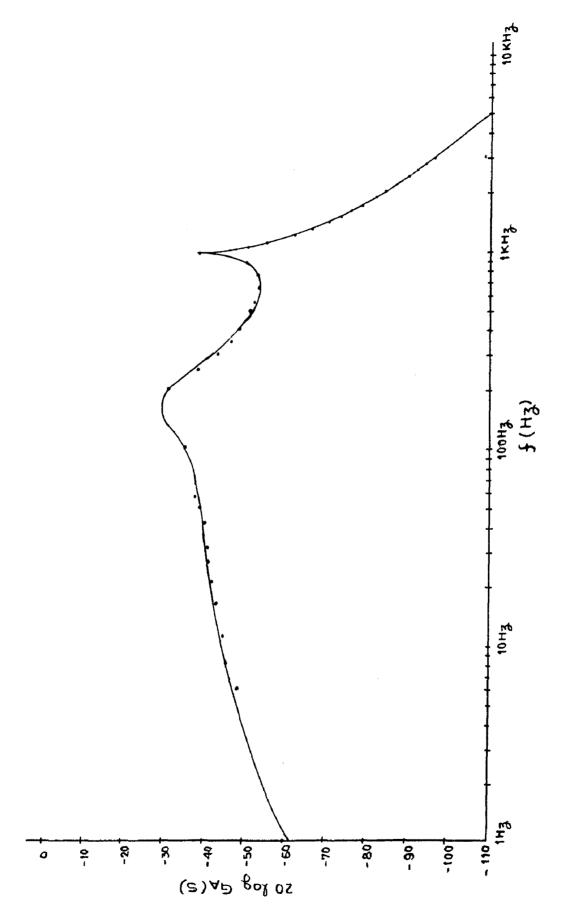

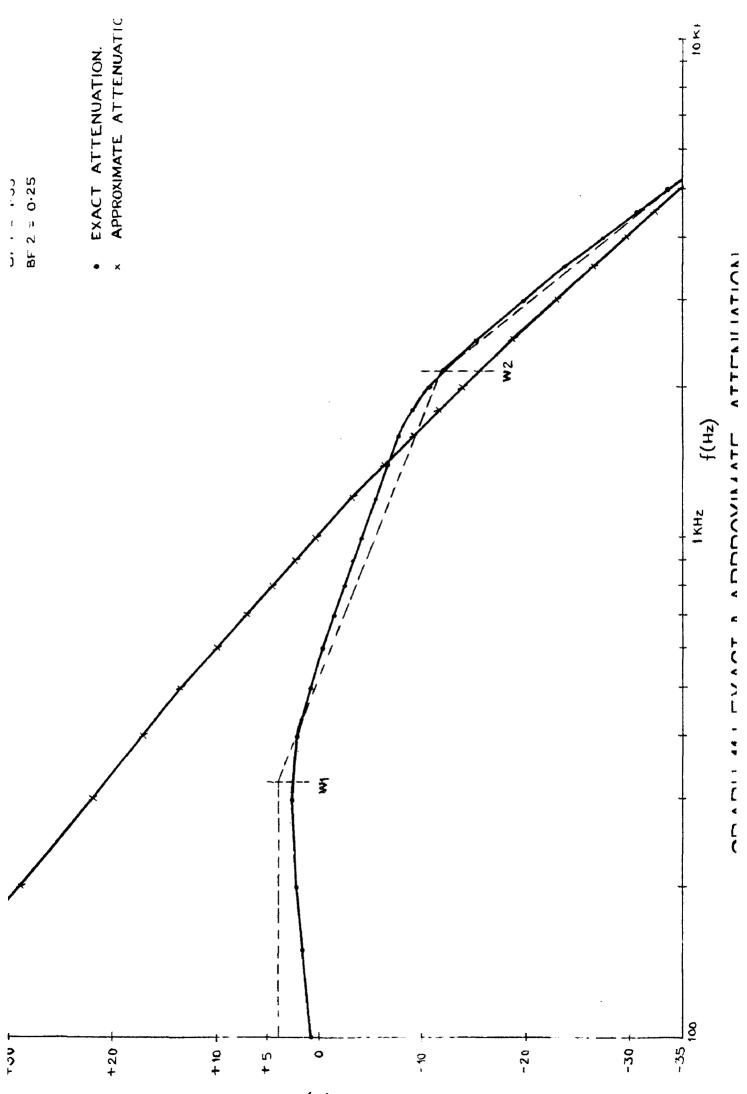

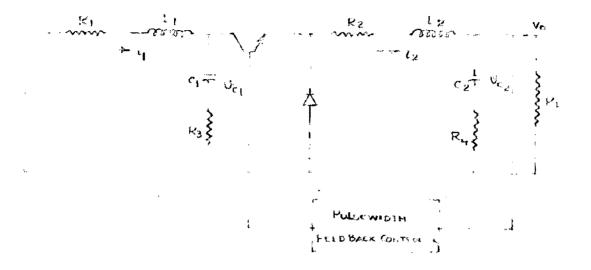

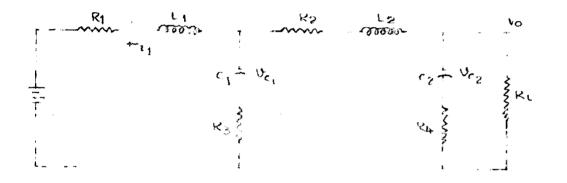

oscillation will occur.