# A SOLID STATE INVERTER FED INDUCTION MOTOR DRIVE

#### A DISSERTATION

Submitted in partial fulfilment of the requirements for the award of the degree

of

# MASTER OF ENGINEERING in

### ELECTRICAL ENGINEERING (Power Apparatus & Electric Drives)

by YASH PAL SINGH

(n. 8**3**

### DEPARTMENT OF ELECTRICAL ENGINEERING UNIVERSITY OF ROORKEE ROORKEE (INDIA)

1980

# <u>C E R T I F I C A T E</u>

Certified that the dissertation entitled"A Solid State Inverter Fed Induction Motor Drive" which is being submitted by Sri Yash Pal Singh in partial fulfilment for the award of the Degree of Master of Engineering in Power Apparatus and Electric Drives of the University of Roorkee is a record of students own work carried out by him under my supervision and guidance. The matter embodied in this dissertation has not been submitted for the award of any other Degree or Diploma.

This is further to certify that he has worked for a period\_ of 11 months from Feb. 1979 to Dec. 1979 for preparing dissertation for Master of Engineering Degree at this university.

Dalle

(DEV RAJ KOHLI) Professor Deptt. of Elect. Engg. University of Roorkee Roorkee.

Place : Roorkee. Dated : Jan, 1980.

# ACKNONLEDGEMENTS

The Authour wishes to express his profound gratitude to his guide Prof: D.R. Kohli, Electrical Engineering Department, University of Roorkes for the expert guidence, valuable and constructive discussion, protival ideas and constant encouragement throughout dissertation period.

The author also wishes to express his gratitude to Sri V.K. Bensel and Sri Bharat Gupta for their valuable practical discussions, suggestions and encouragement from time to time, during the period. of dissertation.

The author also thanks to Sri Tula Ram & S.K. Banerjee for their kind co-operation & assistance in provinding all possible laboratory facilities.

The authour feels highly indebted for all help and facilities provided by Dr. P. Mukhopadhyay, Professor in Electrical Engineering Dr. L.M. Ray, Professor & Head; Department of Electrical Engineering University of Roorkee, Roorkee.

Jozna

# CONTENTS

.

| CHAPTER |                                                                                        | PAGE   |

|---------|----------------------------------------------------------------------------------------|--------|

| Ţ       | INTRODUCTION                                                                           | 1 - 14 |

|         | 1.1 Importance of Statically Controlled                                                |        |

|         | Induction Motor Drives.                                                                | 1      |

|         | 1.2 Variable Frequency Inverter Fed                                                    |        |

|         | Induction Motor Drives.                                                                | 2      |

|         | 1.2.1 Constant Flux Operation.                                                         | 4      |

|         | 1.2.2 Constant Current Operation.                                                      | 4      |

| · .     | 1.2.3.Constant Torque Operation.<br>(Below & upto one per unit speed)                  | 5      |

|         | 1.2.4 Constant Horse Power Operation.<br>(Above and upto per unit speed).              | 6      |

| N.      | 1.2.5 Constant Horse Power Operation.<br>(At low speeds in Sub- synchronous<br>region) | 6      |

|         | 1.3 Types of inverters used for variable                                               |        |

|         | frequency induction motor drives.                                                      | 6      |

|         | 1.3.1 Adjustable voltage Input Inverter.                                               | 8      |

|         | 1.3.2 Pulse Width Modulated Inverter.                                                  | 9      |

|         | 1.3.3 Current Source Inverter.                                                         | 10     |

|         | 1.4 Special Features of a Three Phase                                                  |        |

|         | Solid State P.W.M. Inverter using                                                      |        |

|         | Power Transistors.                                                                     | 11     |

|         | 1.5 Brief description of the work presented                                            |        |

|         | in this thesis.                                                                        | 14     |

# PAGE

| II | REVIEW | OF PULSE WIDTH MODULATION TECHNIQUES & SOLID  |         |

|----|--------|-----------------------------------------------|---------|

|    | STATE  | INVERTER FED INDUCTION MOTOR DRIVES           | 15 - 31 |

|    | 2.0    | Review of Fulse Width Modulation Techniques   | 15      |

|    | 2.1    | Single Pulse Modulation or Quasi Square       |         |

|    |        | Modulation                                    | 15      |

|    | 2.2    | Multiple Pulse Hodulation                     | 16      |

|    | 2.2.1  | Two Pulse Unidirectional Wave Modulation      | 16      |

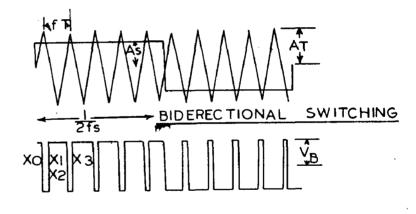

|    | 2.2.2  | Two Pulse Bi-directional Wave Modulation      | 17      |

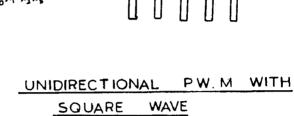

|    | 2.2.3  | Unidirectional P.W.M. with Square Wave        | 19      |

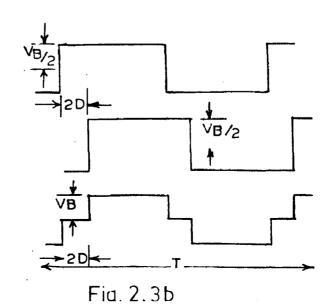

|    | 2.2.4  | Bi-directional P.W.M With Square Wave         | 20      |

|    | 2.3    | Sinusoidsl Pulse Width Modulstion             | 21      |

|    | 2.3.1  | Two-level or Bi-directional Sinusoidal P.W.M. | 22      |

|    | 2.3.2  | Three-Level or Unidirectional Simusoidal      |         |

| ·  |        | P.W.M.                                        | 23      |

|    | 2.4    | Review of Some Control Schemes for Solid      | ,       |

|    |        | State (P.W.M.) Inverter Yed Induction Motor   |         |

|    |        | Drives                                        | 25      |

|    | 2.4.1  | A Six-step P.W.M. Inverter Fed Induction      |         |

|    |        | Motor Drive                                   | 25      |

|    | 2.4.2  | Out put Current Regulation With P.W.M.        |         |

|    |        | Inverter in Inverter - Motor Drive.           | 27      |

|    | 2.4.3  | Direct Flux & Torque Regulation in a P.W.M.   |         |

|    |        | Inverter Fed Induction Motor Drive.           | 28      |

CHAFTER

| 2.4.4 | A Precision Speed Control of Induction Motor |    |  |

|-------|----------------------------------------------|----|--|

|       | Using Phase Locked Loop.                     | 29 |  |

| 2.4.5 | A Completely Automatic Speed Regulating      |    |  |

|       | System.                                      | 30 |  |

III A SOLID STATE THREE - PHASE P.W.M. INVERTER -- CONTROL UNIT

- 3.0 Description of the Control Scheme

- 3.1 Generation of Three Phase Reference Sine Waves and Triangular Carrier Wave.

- 3.1.1 Design of Voltage to Frequency Converter

- 3.1.2 Design of Three step Counter.

- 3.1.3 Design of Square Pulse to Square Wave Converter.

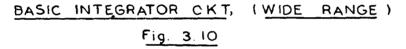

- 3.1.4 Design of Square Wave to Triangular Wave Converter.

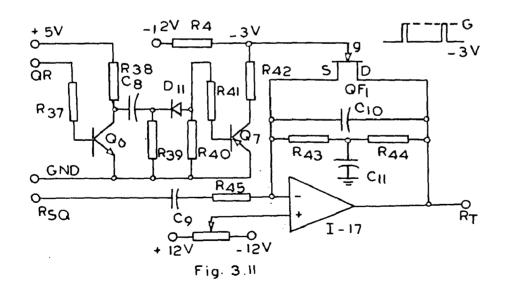

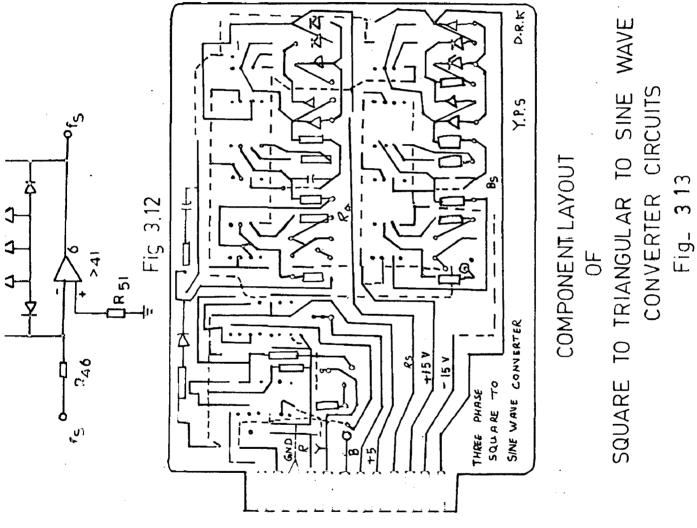

- 3.1.5 Design of Triangular to Sine Wave Converter.

- 3.2 Amplitude Control of 3 Phase Reference Sine Wave with a d.c. Control Signal

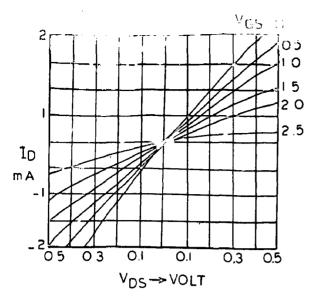

- 3.2.1 Amplitude Control of Sine Wave Employing F.E.T ass Variable Resistor.

- 3.2.2 Analog Multipliers for Amplitude Control of Three Phase Reference Sine Waves.

- 3.3 Pulse Width Modulation of Sine Waves With a Triangular Wave.

3. 3.1 P.W.M. Schemes based upon Modulation Ratio

3.3.2 Design of Triangle Wave Generator.

3.3.3 Basic Pulse Width Modulation Circuit

**3.4.0** Circuit Isolation.

#### CHAPTER

#### 3.4.1 Design of Pulse Transformer.

- IV A THREE PHAST SOLID STATE P.W.M. INVERTER POWER UNIT

- 4.1 Description of Power Unit for Three Phase Solid State P.W.M. Inverter.

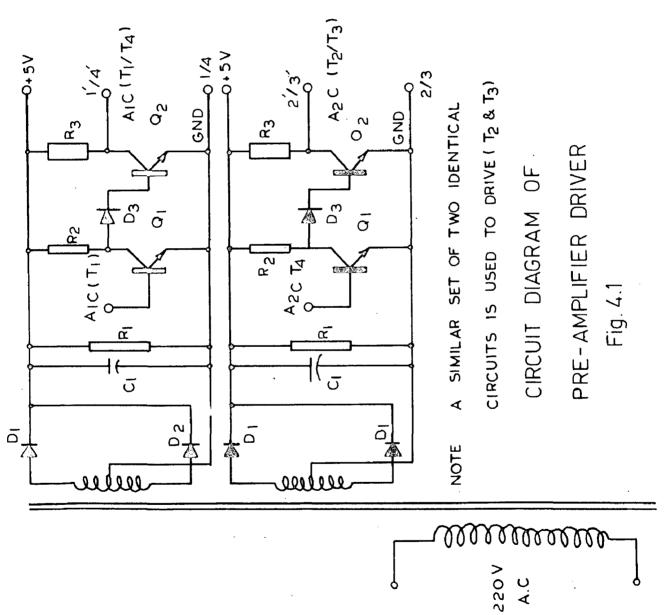

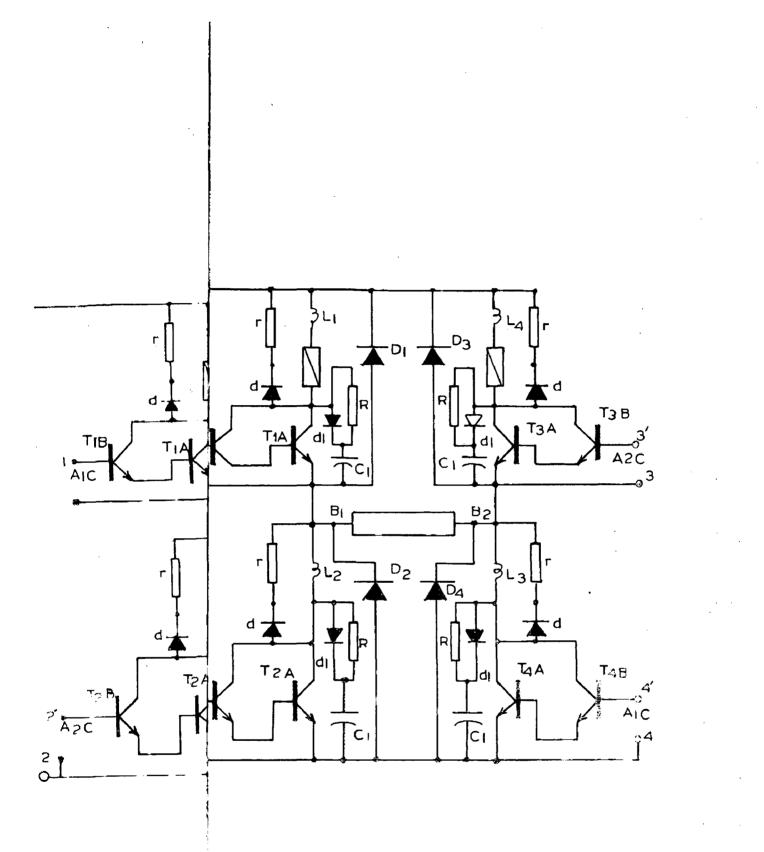

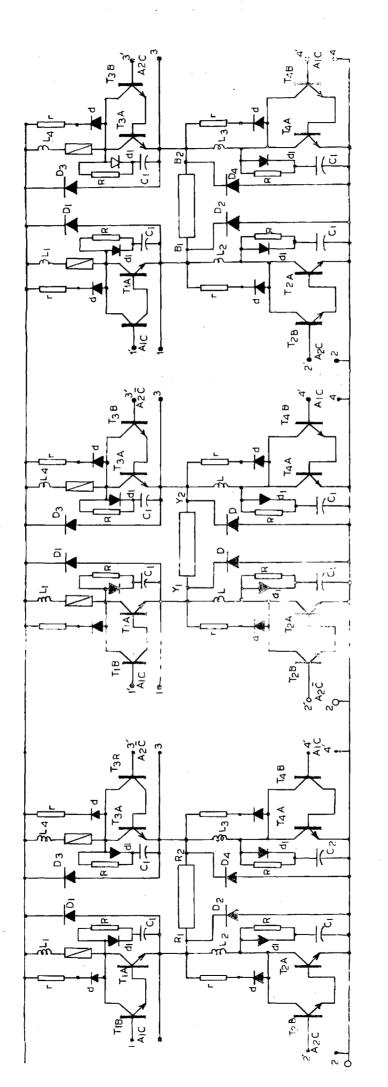

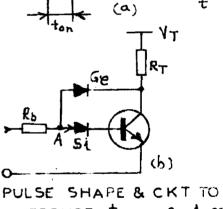

- 4.1.1 Description of Pre-emplifier/Driver Stage

- 4.1.2 Description of Power Control Unit

- 4.2 Design of Pre-emplifier/Driver.

- 4.3 Design of Power Control Unit.

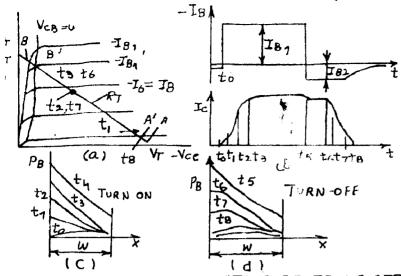

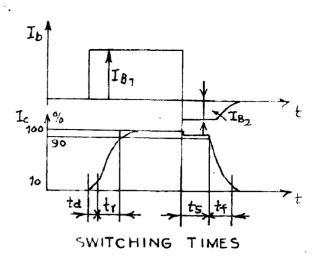

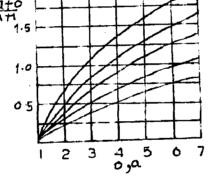

- 4.3.1 Basic Operation & Switching Time Constants of Power Transistor Switch.

- 4.3.2 Design Trade off & Practical Considerations for using Power Transistor as a switching device.

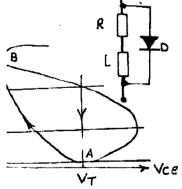

- 4.3.3 Criterion and Justification for the selection of Proper Power Transistor.

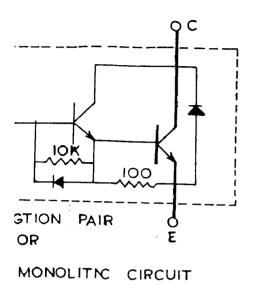

- 4.3.4 Power Monolithic circuit/Darlington Pair/ High Gain Triple Darlington Configuration of Power Transistors.

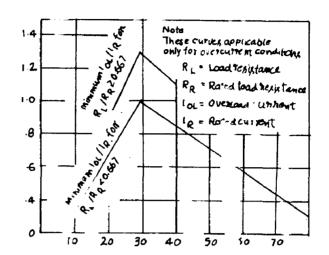

- 4.4 Design & selection of Protection circuits & Components.

- 4.4.1 Selection of Proper Rating for Free Wheeling Diode.

- 4.4.2 Design of air core inductor.

- 4.4.3 Design of circuit for protection against voltage Transients.

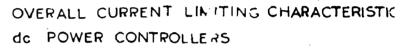

- 4.4.4 Over Current Protection and Overall -ourrent Limiting Characteristics of Static Power Controllers.

CHAPTER

4.5 Filtering of Hermonics At The Input of A P.W.M. Inverter.

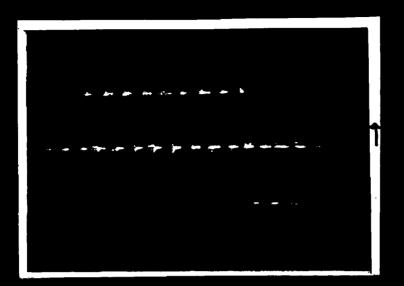

Y PRACTICAL OBSERVATIONS & TEST RESULTS

- 5.1 Waveforms Observed at Various Points in Control Unit.

- 5.2 Waveforms & Test Results of Power Unit/P.W.M. Inverter.

- VI CONCLUSIONS AND SUGGESTIONS

BIBLIOGRAPHY

#### CHAPTER I INTRODUCTION

#### 1.1 Importance of Statically Controlled Induction Motor Drives

The field of static control and conversion of electric power has been revolutionized with the development of solid state semiconductor devices (such as silicon controlled rectifiers, power diodes and power transistors etc.). Also the fast developments in Power Electronics have opened up new vistas in the field of static control of electric drives that are gaining more and more popularly. An electric drive basically consists of an electric machine associated with a control equipment (that may include a frequency converter, rectifier etc.) to convert electrical energy into a mechanical energy and thereby to provide a versatile control of speed, torque etc. of the electric machine.

Normally, among the statically controlled electric drives, a d.c. motor operated as a variable speed drive by a static power controller is a popular choice. But the main draw backs of a d.c. motor are :-

(1) Increase in cost and decrease in power/weight ratio because elaborate mechanical commutator.

(11) Accentuated sparking at high currents and speeds.

- (111) A limited armature voltage rating inherent in d.c. machines.

- (iv) A limited armature current, because of commutation problem.

Because of the above drawbacks of a d.c. motor, a suggested alternative is to use a cage rotor induction motor, or a synchronous motor or a reluctance motor ; operating at variable frequency and supplied from a static frequency converter. The use of a cage rotor-induction motor has the advantage that 1-

- (1) The cost of induction motor is only about one sixth for the d.c. motor of the same speed and power rating.

- (ii) The lower/weight ratio of the squirrel cage I.M. is twice that of a d.c. machine.

In general, a solid state inverter fed induction motor drive, is an efficient, and robust, drive system, having an application in fields where an extremely precise speed control or speed matching is required. Thus, the static frequency converters provide a wide range variable speed drive with control accuracies upto .001 %, since the solid state frequency converters/inverters provide output frequencies that are precise and stable. The initial capital cost of such drives is very high and discourages the application of such drives for general purpose application. However the fast decline in the cost of solid state devices and electronic components, and an added advantages obtainable in such drives these are bound to replace  $\frac{Zerre}{Zerre}$

1.2 Variable Frequency Inverter Fed Induction Motor Drives

A cage-rotor induction motor fed with a variable frequency supply provides a versatile and wide range speed

controlled drive. The variable frequency supply that alters the synchronous speed of the induction motor. can be obtained through a static frequency converter. For optimum motor performance and effective utilization of core material, the air gap flux of the induction motor should be maintained constant. The air gap flux can be maintained approximately constant by keeping a constant volts/Hz ratio i.e. varying the supply voltage proportionately as the frequency is varied. However with constant v/f operation, the performance of the motor deteriorates at low frequencies because at low frequencies the influence of stator resistance is increased and consequently the air gap flux reduces to some extent. Hence, in order to improve the low frequency characteristic, the terminal voltage should be increased more than the proportionate value. The required boost actually depends upon the design and size of the machine. A constant volts/Hz operation gives the following characteristic features to a variable frequency drive:-

- (1) The starting current, power factor and also the starting torque are improved.

- (ii) The pull-out torque remains approximately constant.

- (111) Sufficiently high torque can be achieved through-out the entire range of speed control.

There are two mode of operation of a variable frequency induction motor drives, such as I-Constant Flux operation ; (II-Constant Current operation.

-3-

1.2.1 <u>Constant Flux Operation</u>:- In order to maintain a high torque throughout the entire speed range, it is essential to maintain the flux constant. This can be achieved if the air-gap e.m.f.  $B_1$ , instead of terminal voltage is varied linearly with the frequency and a proper boost in  $E_1$  is given at low frequencies in order to compensate for the increased effect of stator winding resistance. Further it can be shown that [1] the electromagnetic torque is proportional to square of  $E_1/f_1$  or air gap flux, at a given rotor frequency  $f_2$ . Consequently if  $E_1/f_1$  or air gap flux is maintained constant, the torque is solely determined by the absolute rotor frequency " $f_2$  and is independent of supply frequency,  $f_1$ ".

Thus a control scheme in which the rotor-slip frequency is directly controlled while maintaining the constant air gap flux or  $E_1/f_1$ , the drive can exhibit a precise control and adjustment of torque at any speed.

1.2.2 <u>Constant Current Operation</u> :- Practically, high torque under constant flux operation can be obtained only at the cost of increased stator current. Again it has been shown<sup>[1]</sup>, that the stator current  $I_{i}$ , is independent of the supply frequency,  $f_{i}$ , when the air-gap flux is constant, but depends upon the rotor slip frequency,  $f_{2}$ . Thus the air gap flux of the motor can be indirectly determined by the stator current and rotor slip frequency  $f_{2}$ . Further, the torque can be expressed in terms of stator current and rotor frequency<sup>[1]</sup>. Therefore in second mode of operation the stator current  $I_1$ , as well as rotor frequency  $f_2$  are controlled in order to maintain the air gap flux constant and consequently the high torque throughout the entire range of speed control. The basic advantage of constant-current operation is that there is no necessity of large overcurrent capacity of the inverter since there are no current surges and thus the inverter design is economical.

Normally variable frequency drives are closed loop drives and the simplest scheme is the controlled, Slip drive, in which the slip frequency is contineously controlled so as to ensure that operation is always at small slip. This owes a high developed torque at high power factor with low losses. The overall characteristics of the drive can be adjusted so. as to suit the particular application and two basic types of characteristics i.e. as 'constant torque' and 'constant horse power' characteristics can be achieved in the following way?-

1.2.3 <u>Constant Torque Operation</u> :- (Below and upto one per unit sped). It can be obtained by increasing the terminal voltage linearly with the supply frequency and to provide a suitable boost in terminal voltage at low frequencies in order to maintain a constant air gap flux. This gives a high torque through-out the speed range. However the speed range can be increased above the i p.u. speed by keeping the terminal voltage constant and increasing the fundamental frequency above the normal rated supply frequency. But in this case the torque goes on reducing as speed is increased above one per unit because of decrease in air gap flux.

-5-

1.2.4 <u>Constant Horse Power Operation</u> :- (Above and upto per unit speed) If the frequency  $f_2$  is increased linearly with  $f_1$  for a constant stator voltage then it can be shown that torque is inversly proportional to the supply frequency. Since  $T = K^{**}\phi^2 f_2$  or  $\approx K^{**}(V_1/f_1)^2 \propto f_2$ .

This means that the torque varies inversly with the speed i.e. a constant horse power characteristic is obtained.

## 1.2.5 Constant Horse Power Operation :- (At low speeds in subsynchronous region).

For a fixed value of 'f2', A It can be obtained by varying  $(V_1)^2$  proportional to  $f_1$ , In this case torque varies inversiv proportional to  $f_1$ and a constant hourse power output is obtained, since  $T = K^{11} \phi^2 f_2 a \phi^2 a(V_1^2/f_1^2).$

Constant horse power operation over a wide speed range is required for Traction purpose and for that methods describe above under section 1.2.4 and 1.2.5 can be conveniently used.

# 1.3 Types of Inverters Used for Variable Frequency Induction Motor Drives

The variable frequency operation of an induction motor is obtained by the use of Frequency Converter. A frequency converter is a machine or equipment that can generate or convert the input supply to a supply of variable frequency and amplitude. The rotating type of frequency converters have been used in past but now a days are out-dated and are replaced by the selid state frequency converters. State frequency conversion hase the following advantages:-

- (1) Entroly high accuracy and stability are obtained.

- (11) High officiency and absence of moving parts, reduces the operating cost.

- (111) Ecquiro smallor space, lessor maintennee, so machino alignment and have lover installation cost.

- (17) Past roopense and control can be achieved casily.

The static frequency convertors are divided into two entegeriess- [A] D.C. Link Convertors ; [D] Cycleconvertors. A d.e. link convertor is a two stage conversion device in which proof from the a.e. notwork is first rectified to d.e. and then inverted to obtain a.e. voltage at variable frequency. This type of invertor can operate over a large frequency range and is suitable for vide-range speed control drives. However this type of invertor employing thyristors, require additional commutation circuits and therefore complicated control circuitry. Also for regeneration capability it requires additional circuits and hence the cost and complexity is increased.

A cyclo-convertor is a device to convert directly the supply frequency to a lower subput frequency and does not require intermediate restification. The subput frequency range and is limited to about one third of the supply frequency and therefore the drives employing cyclo-convertors are suitable only for operation at low-frequency or speed range. However the basis advantage of a cyclo-convertor is its inherent capability of superstive operation and a close approximation of the output voltage to a sine wave, particularly at low frequencies, since the output wave is fabricated from the segments of the input supply waveforms.

In general for wide range speed control and where regeneration braking is not essential a d.c. link converter fed induction motor is the best choice. In actual practice for drive applications, a d.c. link converter is required to provide an output of variable frequency as well as variable voltage. Based upon the above requirements, the rectifierinverters (frequency converters) are divided into the following two groups:-

(A) A.V.I. (Adjustable Voltage Input) inverter.

(B) P.W.M. (Pulse Width Modulated) inverter.

(C) Current Source Inverter.

1.3.1 <u>Adjustable Voltage Input Invertor</u> :- The A.V.I. inverter<sup>[2]</sup>, basically consists of three major circuits: a phase controlled bridge or a chopper controller for voltage control, an inverter for frequency control and a fixed d.c. bus to provide constant commutating capability.

In phase controlled bridge rectifiers, a 'phase control' technique (in which delayed firing of thyristors normally connected in three phase bridge configuration) is employed in order to control the d.c. voltage input to the static-inverter. Basically, in phase controlled rectifiers, the displacement power factor varies linearly with the output voltage and at low output voltage, the power factor is low which is a disadvantage. Also, send "benting" notor currents are caused by the difference of invertor output and rectified line frequency and in order to minimize them a smoothing L.C. filter is required. Further because of discontinuous conduction at low voltages, the filter capacitor required would be larger than that for a P.L.M. invertor where continuous conduction takes place. Again because of large filter time constant response is slow.

...V.I. investor with choppor controlled input has the advantage of good power factor at the a.c. input and possible factor voltago response due to smaller time constant on account of L.C. filter used on the output of a high-frequency chopper. 1.3.2 Pulse Uldth Modulated Invertor 1- The P.U.H. invertor [2], can be considered as a refined version of the chopper-input A.V.I., since in this case voltage and frequency control are accoupliched with only one power controller and some special control logic elecultry. The P.U.N. invertor basically generates an cutnut voltage of constant applitude and variable width blocks; which when supplied to an inductive load (or motor), produces a smoothed version of the voltage waveford i.e. of fundamental frequency. Pulso width wodulated blocks are generated by the comparison of a reference sinusoidal signal (of fundamental frequency) with a carrier wave (that may be a triangular. rectangular, square or trapisoidal). Formally the ratio of the carrier wave to reference elacave to kept high in order to reduce the lover order harmonice.

-9-

The pulse width modulated inverters have the following advantages:-

- i. When the pulse width is sinusoidally modulated with high frequency triangular wave, the output voltage and current have small harmonic contents. This reduces the undesirable torque pulsation which are usually associated with low frequency static a.c. drives

- 2. A high pulsing frequency reduces the lower order harmonics content and eases the filter requirements.

- 3. Mains interference and distortion are also minimized because of an uncontrolled rectifier and high pulse repetition frequency in the inverter.

- 4. The P.W.M. system requires a minimum of auxiliary equipment, since the only apparatus required, in addition to inverter, is an inexpensive bridge rectifier.

- 5. Good power factor to a.c. line and excellent dynamic response.

6. Full load speed range of 20:1 is obtainable.

1.3.3 <u>Current Source Inverter</u>:- Most of the solid state inverters used in variable frequency a.c. drives are of variable voltage and frequency type. Recently, current source unverters<sup>[3]</sup> have been developed in which the magnitude of current at any point is always controlled by the regulated current source. The current source inverters are becoming more popular and ideally suited for a.c. drives requiring a constant torque output. In a current source inverter fed induction motor drive, the average d.c. voltage at the input terminals of the inverter varies with the power demand of the motor. For example, if the motor is unloaded, the d.c. voltage will be near zero, while it will be at some maximum positive value when supplying rated H.P. If the motor load is overhauling, the d.c. voltage reverses in polarity and the power will be returned to a.c. through the controlled rectifiers i.e. regeneration takes place. However the circuit and induction motor parameters effect the performance of current source inverter<sup>[3]</sup>. The current source inverters have the following specific advantages over the voltage fed inverters:-

- Simple configuration and non-inverter grade thyristors can be used.

- 2. Commulation capability is load current dependent.

- 3. Ability to ride through commulation failure and also to recover from momentary short circuit failure. Hence thyristors require minimal protection and full current handling capacity can be utilized.

- 4. Regeneration capability, makes these ideally suited for drives requiring frequent acceleration and decceleration.

5. Low cost.

# 1.4 Special Features of a Three Phase Solid State P.W.M. Inverter Using Power Transistors

Normally, P.W.M. inverters employ thyristors, having fast turn off time of the order of 20 micro-sec. but the commutation difficulties and commutation circuit time constant limit the switching frequency. In a sinusoidal P.W.M. with triangular wave a Modulation Ratio (Ratio of triangular carrier frequency to the frequency of reference sine wave) upto 20 can be achieved and may give an inverter motor drive with substantially a good performance for normal application of speed control. But for some specialized applications; such synthetic fiber manufacturing, paper manufacturing and other continuous processing plants, a very precise, wide range, stable and coordinated speed control of multimotor drives system is the specific requirement and K.V.A. ratings are in the range of upto 20 K.V.A. For such applications, a solid state P.M.M. inverter (employing Power Transistors as a switching element) Fed Swuirrel Cage Induction Motor Drive is the best choice because of the following reasons:-

- (a) A Power Transistor exployed as a solid state switching element requires only one signal to switch it ON and *x* turns OFF automatically, when the switching ON signal is absent. Hence the P.W.M. Inverter employing Power Transistors, do not require any commutation circuitry and the problems associated with commutation in the Thyristors are over. Further the control circuitry is much simplified.

- (b) Power Transistor being a fast switching device, having a turn ON and turn OFF times of the order of 1 micresecond ar issue, the inverter can be operated at high switching frequencies and thus high modulation ratios, (even upto 100) can be achieved. Therefore an output wave of low harmonic content can be generated, with all

-12-

the harmonics that effect the motor performance, being reduced to minimum.

The ready availability and fast reduction in the cost of high rating switching power transistors (e.g. 800V, 30 Amp) have resulted in a possible alternative to use power transistors in place of thyristors. With this view a Three Phase Solid State Inverter is designed and fabricated ; the practical feasibility of this alternative have, tried and the results are reported in this thesis. The P.W.M. inverter designed and fabricated have the following specifications:-

(a) Output K.V.A. Rating =- 0.5 KVA\* (50V, 10 Amp, 3 Phase).

- (b) Operating Frequency Range :- 5 Hz to 100 Hz.

- (c) Faculty to control the voltage and frequency of the output with seperate control signals, in order to provide constant V/F operation.

- (d) Modulation Ratio :- Two modes of operation are possible:-

(1) Fixed Modulation Ratio (M.R. = 6, 12 or 24).

(11) Variable Hodulation Ratio (M.R. Varying 20 to 100 with the variation of fundamental frequency from 50 to 5 Hz)

("The rating of the developed inverter is limited to 0.5 KVA because the only power transistors available were 2N3055 (60V, 15 Amp). The inverter rating can be extended upto 10 KVA by using the power transistors of rating 800V, 30A; with the same control and power unit).

### 1.5 Brief Description of the Work Presented in This Thesis

In chapter 2, the review of various pulse width modulation techniques is presented and some P.W.M. inverter fed induction motor drives are discussed. The third chapter describes the control scheme for the Three Phase P.W.M. Inverter, designed and fabricated as a part of this dissertation. Design considerations that are of vital importance in design are fully discussed and design of various blocks is given. The design of Power Unit is also presented in the same fashion in fourth chapter. In the last chapter (Chapter V) the praotical observations of P.W.M. inverter and conclusions are presented.

PULSE MODULATION

PULSE UNIDIRECTION WAVE

Fig- 2.2

Fig. 2.4

P.W. M WITH SQUARE WAVE

Fig.2.5

ULSE BIDIRECTIONAL WAVE

ODULATION

Fig 2.3a

#### CHAPTER - II

# REVIEW OF PULSE WIDTH MODULATION TECHNIQUES AND SOLID STATE INVERTER FED INDUCTION MOTOR DRIVES

#### 2.0 Review of Pulse Width Modulation Techniques

It is evident from the discussion of section 1.3.2. that a P.W.M. inverter can inherently perform a dual function of varying the frequency as well as the magnitude of the output voltage. The voltage control is basically achieved by Pulse Width Modulation which may be defined as the control of average level of a quantity (Voltage, current, flux etc.) by applying or driving that quantity in discrete intervals or pulses. The most commonly used techniques of pulse width modulation are :-

- 1. Single Pulse Width Modulation or Quasi Square Modulation.

- 2. Multiple Pulse Width Modulation.

- 3. Sinusoidal Pulse Width Modulation.

- 4. P.W.M. in Sir-Step Wave.

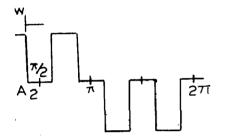

#### 2.1 Single Pulse Modulation or Quasi Square Modulation

This type of modulation is characterized as one whose polarity reverses twice per cycle. This is the most simple type of modulation technique employed to control the amplitude of fundamental component of the wave by varying the work to space ratio as shown in Fig.2.1. The analysis of such a wave form gives the r.m.s. value of the n<sup>th</sup> coefficient as

$$\frac{V_{\rm F}}{V_{\rm B}} = \left[\frac{2\sqrt{2}}{\pi} \cos n D\right] \times 100$$

(2.1)

and the total r.m.s voltage of the waveform, including all the harmonics. is given by

$$\frac{X r \cdot r \cdot s (r)}{v_{R}} = \left[1 - \frac{2D}{r}\right]^{1/2} \times 100$$

(2.2)

Equations (2.1) and (2.2) are derived in and numerical results are given in Ref.[4], table 9.1. The greatest disadvantage of the quasi-square or single pulse modulation is that the normal voltage control range is limited only 30 to 90 % because allow voltage various harmonics have amplitude almost equal to that of fundamental.

#### 2.2 Multiple Pulse Modulation

In this type of modulation polarity reverses more than twice per cycle and harmonic content at lower output voltages can be significantly reduced by using several pulses in each half cycle. This type of modulation can be further sub-devided into following groups:-

I-(a) Two Pulse Uni-directional Wave Modulation.

I-(b) Two Pulse Bi-directional Wave Modulation.

II-(a) Uni-directional P.W.M. with Swuare Wave.

II-(b) Bi-directional P.W.M. with Square Wave.

2.2.1 Two Pulse Uni-directional Wave Modulation: - In two pulse unidirectional wave modulation, two pulses of either polarity + or - are generated in each half of the cycle as shown in Fig.2.2. The word unidirectional means that all the pulses in a given half cycle, have either a positive magnitude posybywe OF a negative magnitude with respect to ground or zero level and the wave may assume zero level for some time. As shown in Fig.2.2, if  $B = \frac{A_1 + A_2}{2}$  and  $w = \frac{A_2 - A_1}{2}$ , then the nth fourier coefficient is given by

$$b_n = \frac{8V_B}{\pi n} \sin nB \cdot \sin nW$$

(2.3)

Here by proper selection of 'B' as shown in Fig.2.2, the PM' harmonic can be eliminated, if the following condition is satisfied i.e. Sin PB = 0 or B =  $\pi/P$ . Also by maintaining this value of 'B' and varying the width 'w', the effective voltage can be varied while the Pth harmonic still remains absent. From equation (2.3) the r.m.s values of the n<sup>th</sup> harmonics and the total harmonic content is given by % r.m.s(n)

$$\frac{V_{e}r_{e}\pi_{e}g(n)}{V_{B}} = \left[\frac{4\sqrt{2}}{\pi} \sin \frac{n}{p} \cdot \sin n v\right] \ge 100 \quad (2.4)$$

and

$$\frac{V_{F,m,s}(T)}{V_{B}} = 100 \left[\frac{2}{\pi}(A_{2} - A_{1})\right]^{1/2} = 200 \sqrt{N/\pi} \qquad (2.5)$$

Since the harmonics of the order P is absent from the output, this technique is also called "Selected harmonic elimination" technique. It can be observed in this case that even though lower harmonics are eliminated, the total harmonic content is large and the most serious disadvantage is that the fundamental (max), obtainable is 75.1 %, 62.2 % or 33.3 %, of the d.c. according to whether 3rd. 5th or 7th harmonic is eliminated.

2.2.2 <u>Two Pulse Bi-directional Wave Modulation</u>:- In two pulse bidirectional modulation the output voltage have dual polarity pulses, having a symmetry over a cycle, as shown in Fig.2.3(a). Here, again B and W can be selected to eliminate a particular harmonic and to vary the fundamental voltage and are given by  $B = (A_1 + A_2)/2$  and  $W = (A_1 - A_2)/2$ . The voltage components in this case are given by

$$\frac{\sqrt{r_{eB}} s(n)}{V_{B}} = \frac{2\sqrt{2}}{n\pi} [1-4 \sin nB \sin nw]$$

(2.6)

Now it is possible to combine, two phase shifted bi-directional waveforms of Fig.3.2(a). This combination results in a quasisquare wave. For example, if two phase shifted bi-directional square waves are combined together, then they produce a quaisquare waveform as shown in Fig.3.2(b).

The combination of two phase-shifted, two pulse bidirectional waveform would give a modified r.m.s. value of n<sup>th</sup> harmonic as 1-

$$\frac{4 r.m.s(n)}{8} = \frac{2\sqrt{2}}{\pi} [1-4 \sin nB \sin nW] \cos nD$$

(2.7)

and total harmonic content as

$$\frac{\chi_{r.m.p(T)}}{V_{\rm B}} = 100 \sqrt{1-2D/\pi}$$

(2.8)

where 2D is the phase shift between the two waveforms.

Now, there are three control variables w,B, and D, out of that w and B can be used to eliminate any two harmonics, while D controls the magnitude of fundamental voltage. Therefore a selected harmonic elimination for any two harmonics (say P<sub>1</sub> and P<sub>2</sub>) can be achieved, if the following condition is satisfied i.e. 1-4 sin (P<sub>1</sub>B).sin (P<sub>1</sub>W) = 0 and 1-4 sin (P<sub>2</sub>B).

$$\sin(P_2 W) = 0 \tag{2.9}$$

From an analysis of these results it can be observed [4] that -

- (a) Fundamental output (max) voltage is more than that obtainable from unidirectional wave particularly when higher harmonics are eliminated.

- (b) Total harmonic content is less than that obtained with uni-directional wave.

- (c) The amplitude of harmonic increases with the harmonic number e.g. 9th is the largest when 3rd and 5th are eliminated, where as when 3rd and 7th are eliminated 11th predominates, while others also exist but with lesser amplitude.

- (d) Only two chosen harmonics are eliminated while in the case of uni-directional wave, an odd multiple of the harmonic being eliminated are also absent from the output.

- (e) Normally harmonic elimination causes the remaining harmonics to be of objectionably larger amplitudes.

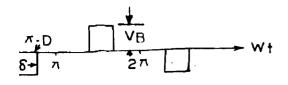

- 2.2.3 <u>Uni-directional P.W.M.</u> With Square Wavet- In this type of modulation several equally spaced unidirectional pulses every half cycle, are generated, by feeding a high frequency carrier triangular wave and a low frequency reference square wave into a comparator. The resulting output waveform is shown in Fig.2.<sup>4</sup>, and swings between  $V_B$  and zero and the width of the pulses are determined by the ratio  $A_{sq}/A_T$  and the number of pulses per cycle, by the ratio of  $f_T/f_q$ . The harmonic voltages are given by:-

$$\frac{\frac{1}{2} r_{*}m_{*}s(n)}{V_{B}} = \sum_{n=0,24}^{\infty} \frac{2\sqrt{2}}{n} \left[ \cos nx(M) - \cos nx(M+1) \right] \quad (2.10)$$

and

$$\frac{\chi_{T,R}(T)}{B} = 100 \left[ \frac{f_T}{2\pi f_q} \{ x(0) - x(1) \} \right]^{1/2}$$

(2.11)

where M = Modulation Ratio =  $A_{so}/A_T$ The analysis of equations (2.10) and (2.11) for various values of f. /f. indicate that =-

- (a) Lower harmonics are considerably reduced, although total harmonic content increases with pulse number.

- (b) The third harmonic at high pulse number varies almost linearly with the fundamental.

- (c) The maximum fundamental r.m.s voltages is 90 % of d.c.

- (d) All even harmonics are absent from the output.

- 2.2.4 Bi-directional P.W.M. with Square Wave :- Several equispaced bidirectional pulses can be generated as shown in Fig.2.5 by mixing a triangular and square wave through a comparator. This output waveform with this type of modulation contains odd and even harmonics. The nth harmonic component is given by [4]

$$\frac{\chi_{F,\overline{n},s(n)}}{V_{B}} = \frac{\sqrt{2}}{n\pi} \times 100[1-\cos n \times (0)+\Sigma[\cos n \times (2M+1)-\cos n \times (2M+2)]]$$

=  $\Sigma[\cos n \times (2M)-\cos n \times (2M+1)]]$  (2.12)

(2.12)

where M is the Modulation Ratio =  $A_{go}/A_T$  and  $x_0, x_1, x_2, x_3$  are the points of intersection of triangular and squarewaye. This type of modulation gives the following characteristics:-

(a) Even harmonics except those of the order  $(f_T/f_S)$  and  $3(f_T/f_S)$  are absent e.g. for  $f_T/f_S = 4$  only 4th and 12th even harmonics are present.

-20-

- (b) The harmonic with number equal to  $f_T/f_S$  has the largest amplitude.

- (c) The content of lower order harmonics is less than that obtained with unidirectional switching.

- (d) The odd harmonic content generally increases as the operating frequency is increased, while reverse is true in the case of unidirectional switching.

#### 2.3 Sinusoidal Pulse Width Modulation

Simisoidal pulse width modulation is obtained by modulating the reference sine wave with triangular wave. This type of modulation is also termed as subharmonic method of control, and offers the advantage of reducing the harmonics to a tolerable limit in the voltage and current and consequently in torque (in P.W.M. inverter fed drives). In speed control of induction motors using P.W.M. inverters (employing sinusoidal pulse width modulation), there is a production of sinusoidal mean voltage from a square alternating voltage with different positive and negative voltage-time areas. Also the flux varies according to the mean voltage of this alternating square voltage.

Basically, a voltage with sinusoidal mean value contains two types of harmonics e.g.

- (1) Three-phase harmonics that forms a rotating field.

- (ii) The harmonics that are in-phase and drive a current in the neutral. Practically, the in phase harmonics can be easily eliminated by omitting the neutral.

0

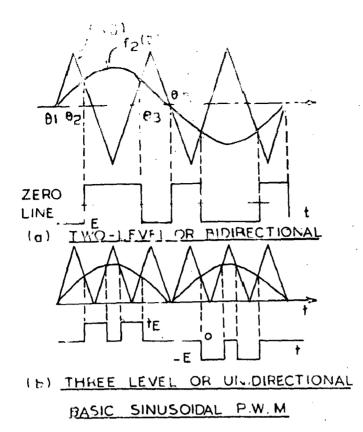

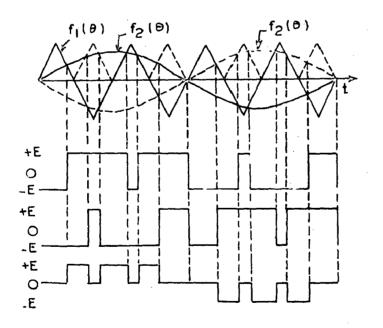

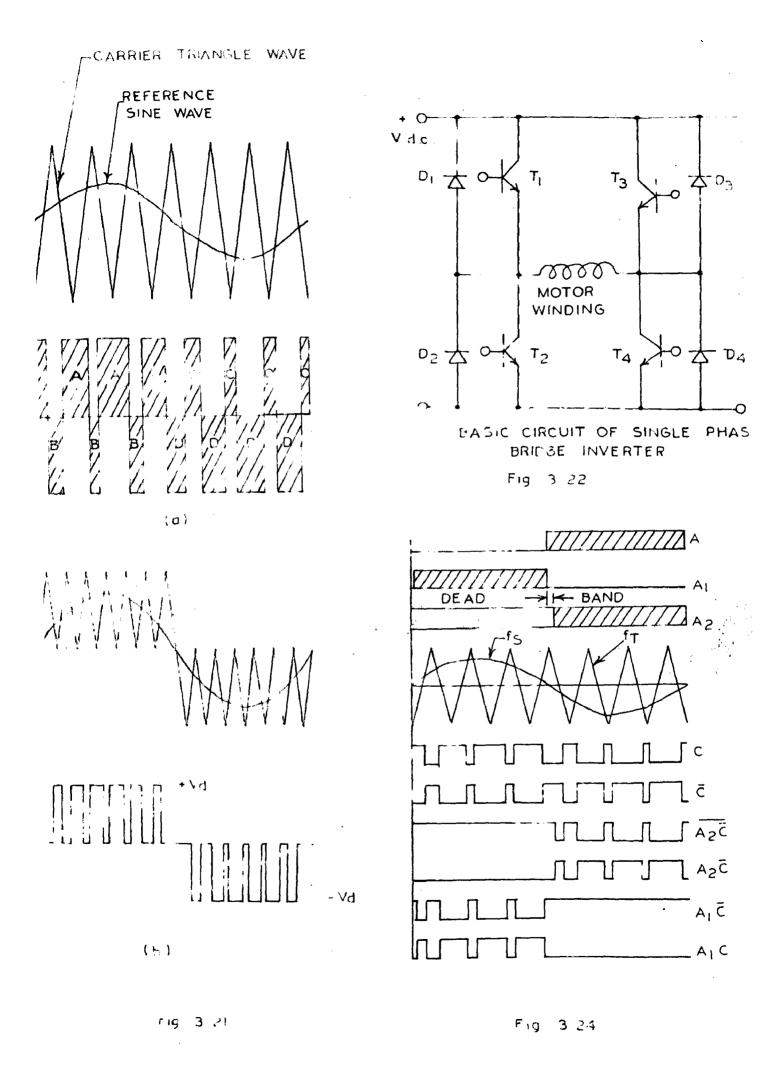

SYNTHESIS OF THREE-LEVEL PWM. WAVEFORM BY TWO DIFFERENT TWO LEVEL P.W.M. WAVES Fig 2.7 There are two types of Sinusoidal Pulse Width Modulation<sup>[5]</sup> schemes: (1) Two Level or Bidirectional P.W.H. and (2) Three Level of unidirectional P.W.H.

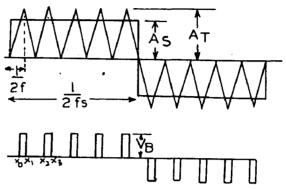

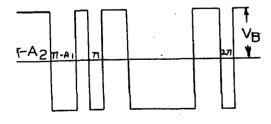

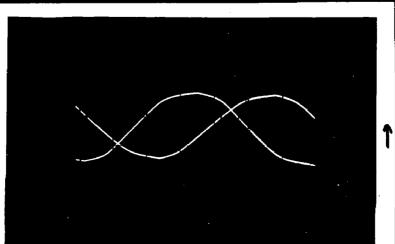

2.3.1 Two Level or Bi-directional Sinusoidal P.W.M :- A two level or bidirection pulse modulation is shown in Fig.2.6, where  $Q_1, Q_2$ ,  $Q_3, \ldots, \theta_m$  are the points of intersection of triangular carrier wave  $f_1(\Theta)$  and the modulating wave  $f_2(\Theta)$ .where

$$f_{q}(\theta) = (\theta - j \frac{\pi}{N}) \frac{(-1)j}{\pi/2N}$$

(2.13)

where  $j = 0$ ;  $0 \le \theta \le \pi/2N$

$j = 1$ ;  $\pi/2N \le \theta \le 3\pi/2N$

$j = 2$ ;  $3\pi/2N \le \theta \le 5\pi/2N$

$j = N$ ;  $(2N - 1) \pi/N \le \theta \le (2N + 1)\pi/N$

and  $f_2(\theta) = Y \sin \theta$ ; here N = Frequency Ratio =  $f_T/f_S$  and Y = Modulation Index (Ratio of amplitude of sine wave to that of triangular wave. From Fig.2.6(a) we get m = (N + 1),  $\theta_1 = 0$  and  $\theta_m = \pi$  and also  $|Y| \leq 1$ .

The R.M.S. value of the n<sup>th</sup> harmonic -Voltage of two level or Bi-directional P.W.M. waveform from unit D.C. link voltage is given by<sup>[5]</sup>

$$2^{V_{n}} = \frac{\sqrt{2}}{n\pi} \left[ -\cos n(\theta_{1}) + 2\left(\cos n \theta_{2} - \cos n \theta_{3} + \dots + (-1)^{N} \cos n \theta_{N}\right) - (-1)^{m} \cos n \theta_{m} \right] \qquad (2.14)$$

The solution of the equation (2.14) for four values of  $N = f_T/f_S$ are given in Tables 9-20 to 9.23<sup>[4]</sup>. It is seen from these tables that the harmonics with largest amplitude is that which occurs at the member given by  $\Gamma_{\rm T}/\Gamma_{\rm S}$  .

For example when operating at  $f_T/f_S = 6$ , the sixth harmonic; at  $f_T/f_S = 10$ , the 10th harmonics and at  $f_T/f_S = 20$ the 20th harmonics, have the largest amplitude. For zero modulation index the output is a square wave at the frequency N.f<sub>S</sub> and the fundamental is zero. Also the amplitude of the N.f<sub>S</sub> harmonics has a value 90 % of the d.c. supply. As the Hodulation Index increases the fundamental also increases in value and the N.f<sub>S</sub> harmonic reduces, where as adjacent even harmonics increase in value.

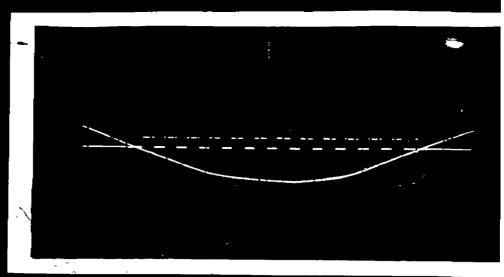

### 2.3.2 Three Level or Unidirectional Sinusoidal P.W.M. :-

A three level P.W.H. wave form as shown in Fig.2.6(b) can be synthesized by subtracting a two-level P.W.H. waveform with a Modulation Index of (+Y) from a similar two-level P.W.H. waveform with a Modulation Index of (-Y) as shown in Fig.2.7.

Let N'be the frequency ratio of three-level unidirectional P.W.M. waveform. The Fig.2.7 shows that N'= 2N, hence the r.m.s. value of the n<sup>th</sup> harmonic voltage of a three level P.W.M. with a frequency ratio of N'is given by<sup>[5]</sup>

$3v_n = \frac{1}{2} [2v_n(+x, n) - 2v_n(-x, n)]$

where  $2V_{n}$  (+Y,N) represents the r.m.s value of the n<sup>th</sup> harmonic voltage of a two level P.W.M. waveform with a modulation (+Y) and frequency N. This concept of synthesizing a three-level P.W.M. waveform simplifies computation of harmonic components, since the same algorithm can be used for computation, in both the cases. The Newton-Rahpson method can be used to compute the intersection points  $\theta_{1}, \ldots, \theta_{m}$  to an accuracy of 10<sup>-5</sup> radians.

The maximum value of the modulation index  $(A_S/A_T)$  is limited to 0.98 rather than unity to prevent adjacent pulses from merging into each other.

In this type of modulation it can be noticed that -

- (i) The harmonic number having the largest amplitude occurs at  $f_T/f_S \pm 1$ : For example with  $f_T/f_S = 10$ ; the harmonics are largest at the 9th and 11th. This is logical also since the 10th ha rmonic is the carrier wave itself and no attempt is made to eliminate it.

- (11) The higher the ratio of  $f_T/f_S$  the more effective this system becomes.

- (iii) Because of symmetrical output wave all the even harmonics are eliminated.

However, there are following disadvantages in the schemes of sinusoidal P.W.M. :-

- (a) The higher inverter frequency required to give effective lower-harmonic reduction leads to lower efficiencies.

- (b) The maximum fundamental output is approx. 70 % of d.c. in case of two level or bidirectional and 78 % of d.c. for three-level or unifectional P.W.M. for maximum

value of Modulation Ratio  $(f_T/f_S = 20)$  and Modulation Index  $(A_g/A_T = 0.98)$ . This max. value of fundamental output is well below that of a square wave modulation that is about 90 % of d.c.

(c) There is a characteristic increase in the total harmonics contents with higher operating frequencies. However this is not a serious drawback since the higher harmonics can be more easily filtered out than lower order harmonics.

# 2.4 Some Control Schemes For Solidstate for (P.W.M.) Inverter Fed Induction Motor Drives:

Ravieword

In this section some selected schemes for Induction Motor drives, employing P. W. M. Inverters are discussed. Their control schemes and special features are also reviewed and discussed in brief, so as to give a different control actions, type of protections and mode of operations possible with a P.W.M. Inverter-Motor Drive. These scheme are:-

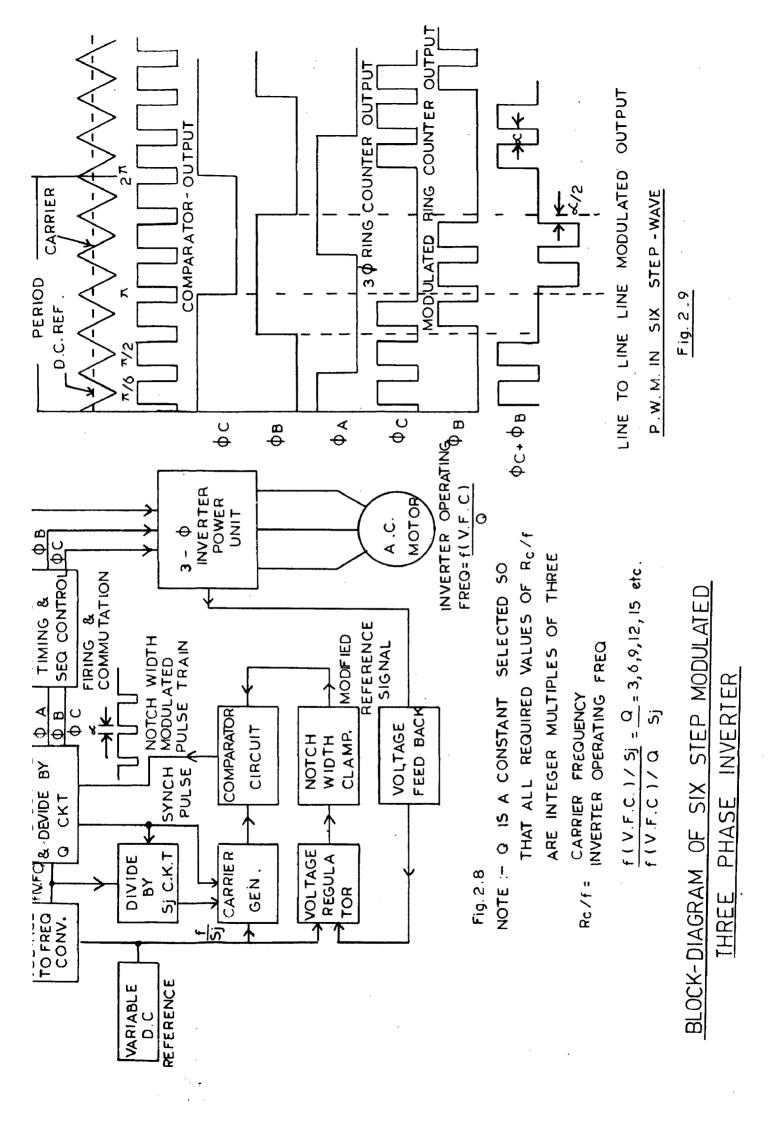

""" A Six-Step P.W.M. Inverter Fed I.M. Drive:- R.D.Adams and R.S. Fox<sup>[6]</sup>, have discussed a basic pulse width modulated six-step inverter fed induction motor drive, where the following three modulation schemes are adopted:- (i) Fixed Ratio Modulation (11) Variable Ratio Modulation (111) Adaptive Ratio Modulation.

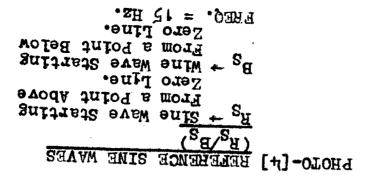

The basic 'Notch Width' or pulse width modulated. Sixstep system is shown in Fig.2.8. In this system a variable d.c. reference signal is used for (1) a voltage to frequency converter (V.F.C), which in turn controls the inverter output frequency and also the carrier frequency.(2) Carrier frequency generator.(3) Output voltage level control through a voltage regulator. It can be observed in this scheme that the modified version of this reference voltage is compared with carrier wave through a comparator, the output of which is a "Notch width" modulated pulse Train. These pulses are used to modulate a 3-phase output of ring counter, through a modulation circuit and the three phase modulated ring counter output is obtained as shown in Fig.(2.9). This output is used to drive a Thyristor Firing Sequence Controller, that produces sequential pulses to turn-ON or turn OFF (through Commutation Circuit) the thyristors in a particular sequence, in order to produce a three-phase pulse width modulated wave at the output of Power Bridge and thus to control the speed of the induction motor.

Basically, in the fixed ratio system the ratio of carrier to fundamental frequency (denoted by  $R_0/f$ ) remains constant over the operating range of the inverter. Where as in the variable ratio scheme the ratio  $R_0/f$  is varied along with the fundamental frequency in sequential steps, so as to produce only higher order harmonics in the output wave, that all easily filtered out. However, there is a limit in the increase of modulation ratio  $R_0/f$  or " the notch width" because of the switching capability of the power thyristors. The minimum value of 'Notch Width'(a) as well as minimum value of pulse width are limited by the combination of thyristor switching and recovery times. It can be observed that a typical 300 µ-sec operating time produces the following results:-

(a) The maximum voltage that can be obtained for a given  $R_c/f$  varies inversly with operating frequency.

-26-

CURRENT REGULATED P.W.M. INVERTER MOTOR DRIVE O PHASE V a V W نت م D'C. GEN ¥ (C.C.I. CURREN REGULATOR) (SYSTEM BLOCK - DIAGRAM ) IPK LIMIT PHASE CURRENTS HOLD х Ч wqV b LIMIT E E RESET Vpwl γ ≥ х Б . 9 FREQUENCY REF. Javl (max) VOLTAGE SUPERVISED AVERAGE CURRENT CONTROLLER FREQ. LIMIT CURRENT LIMIT REGULATOR C C I CONTROL ≥ ∧ d Д AVERAGE CURRENT LIMIT ļ ON/OFF -> 000E+ F W D/REW BUS 2-F REQ. U D

Fig. 2.10

(b) A minimum output voltage must be maintained for a particular  $R_0/f$  and operating frequency. This minimum output voltage increases with the inverter output frequency.

The basic problem with Fixed/Variable ratio modulation is that a provision is to be made for a 'Notch Width Clamp' that operates on d.c. reference level, which will not permit notch width (a) to become less than 300 micro-sec. In the adaptive ratio technique the carrier ratio  $R_c/f$  is automatically adjusted to take care of all possible limiting combinations of the pulse width, notch width and the carrier frequency and maintains constantly a high carrier frequency through out the entire operating range. Thus the adaptive ratio technique optimizes the operating charactéristic of the modulated six-step inverter.

## 2.4.2 Output Current Regulation With P.W.M. Inverter in Inverter Motor Drive:

Basically current regulation plays an important role in the protection of solid state drives, operating from stiff voltage source<sup>[7]</sup>. The P.W.M. inverters, however are not suitable for peak or average current regulation with motor loading. For stable, average and peak current regulation, the control system must limit the rate of inverter output reduction. A variable frequency, non-regenerative reversible drive, with average current and overload protection is shown in Fig.2.10. Here the control provides a dual policy peak current limit and a frequency control loop is used to recover the rotor from pull-out i.e. the rotor frequency is not allowed to increase (or speed to decrease) more than rotor break down frequency at which break down torque occurs. The dual policy substantially extends the range of induction motor over loads, that do not exceeds the inverter commutation capability. Thus the transient performance of the drive for rapidly applied motor overloads is substantially improved and practically a load step change of 3-p.u. and max. peak load current of 1-p.u. are easily achieved.

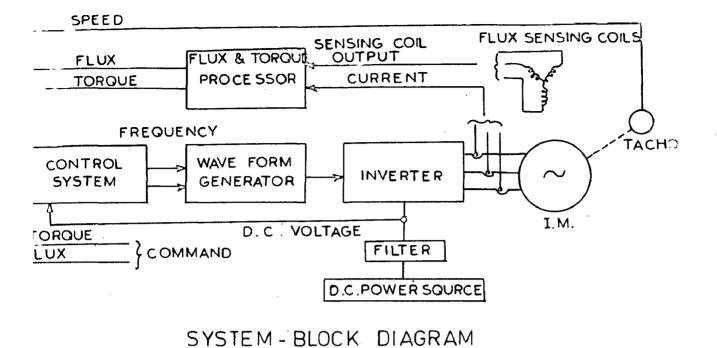

## 2.4.3 Direct-Flux and Torque Regulation in a P.W.M. Inverter-Induction Notor Drive:-

Almost all the methods of induction motors torque regulation assumed that the motor flux level is proportional to the applied voltage divided by the frequency and the torque is then proportional to the real component of stator current. In this technique inaccuracy in torque regulation occurs due to source voltage changes, load changes, and cable and motor internal voltage drops. An alternative method of torque regulation is sensing the slip frequency and real component of stator current to allow regulation of both flux and torque, if the rotor resistance is constant and known.

The method of torque and flux regulation described by<sup>[8]</sup> allows direct regulation of flux without depending upon the invariance of the motor parameters and also provides automatically and electrically isolated feedback signal. A simple calculation of motor torque that is not effected by time harmonics of stator voltage and current can be made using the flux signals and a measurement of stator current. A system is described in which inverter is sinusoidally pulse width modulated

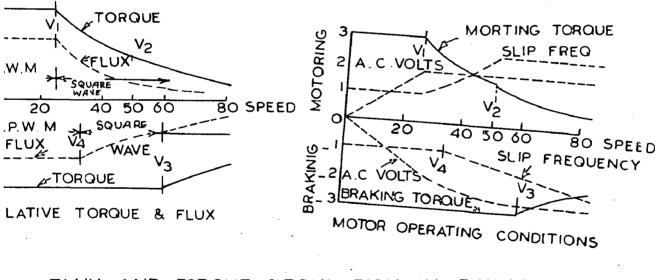

FLUX AND TORQUE REGULATION IN P.W.M. INVERTER- INDUCTION MOTOR DRIVE. Fig. 2.11 at low frequencies so as to shape the a.c. voltage waveform. At higher speed square wave operation is used for maximum efficiency. An intermediate transition mode of P.W.M that is not sinusoidal is used for smooth transition for P.W.M. mode to squarewave mode. The system in block diagram and desired motor operating conditions are shown in Fig.2.11. The flux and torque measurement is done by sensing the flux through flux sensing coils placed in the motor winding in which the voltage generated represents the flux. The level of the flux in the motor is always chosen to be regulated at the maximum in order to minimize the time for which the inverter is P.W.M. and maintaining the operation of the inverter at the minimum possible frequency. However, it should be noticed that this scheme does not require the use of tachometer.

## 2.4.4 <u>A Precision Speed Control of Induction Motor Using Phase</u> Locked Loop -

The particular application of an electric drive, basically determines the degree of speed control required. In some applications a simple open loop speed control of A.C. motor operating with solid state variable frequency inverter may be sufficient, while in some cases feedback control is essential in order to achieve better performance. In close-loop systems, conventionally an analog-servo feedback system is used in which any change in speed is sensed by a tachometer and is compared with a fixed reference voltage and gives a corrective signal. However in some applications, where an excellent speed regulation and fast

-29-

(\* ٢ dynamic response are required, even analog-servo systems are not satisfactory. These feature can be achieved by using digital phase locked loop control system<sup>[9]</sup>.

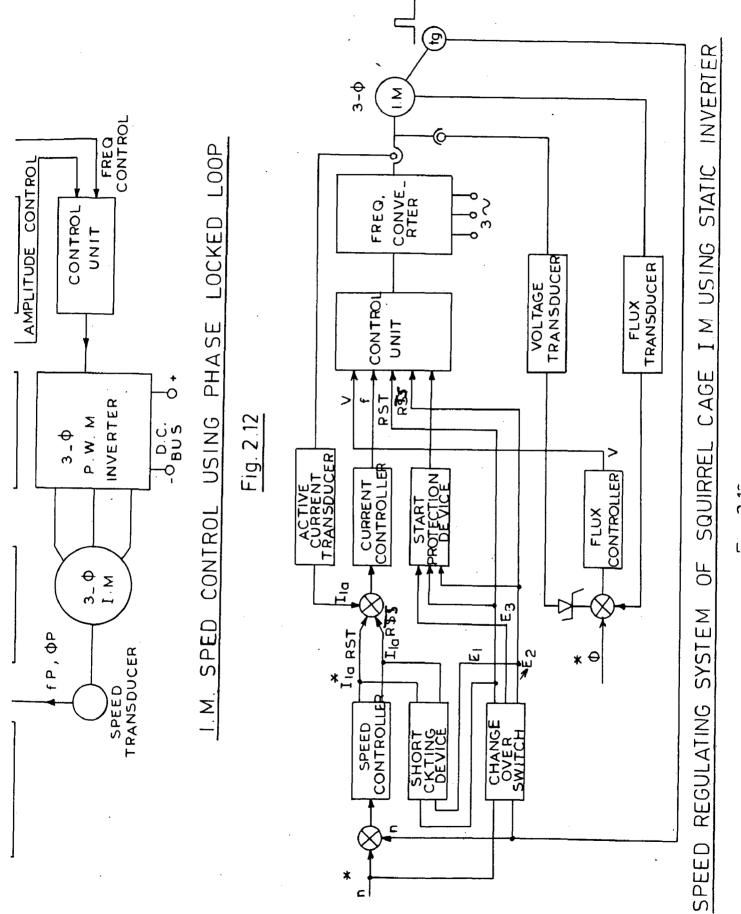

In a phase locked loop method; motor speed is converted to a digital pulse train which is synchronized with a reference digital pulse train. In this way by locking into the reference frequency, precise speed control of motor speed is achieved. The block diagram of an induction motor drive with phase-locked loop in the feedback network is shown in Fig.2.12, where a speed control accuracy upto 0.002 % can be achieved.

The phase locked loop control system is desired where motors must be synchronized to each other such as paper mill; textile mill drive or drives used for manufacturing of synthetic fiber.

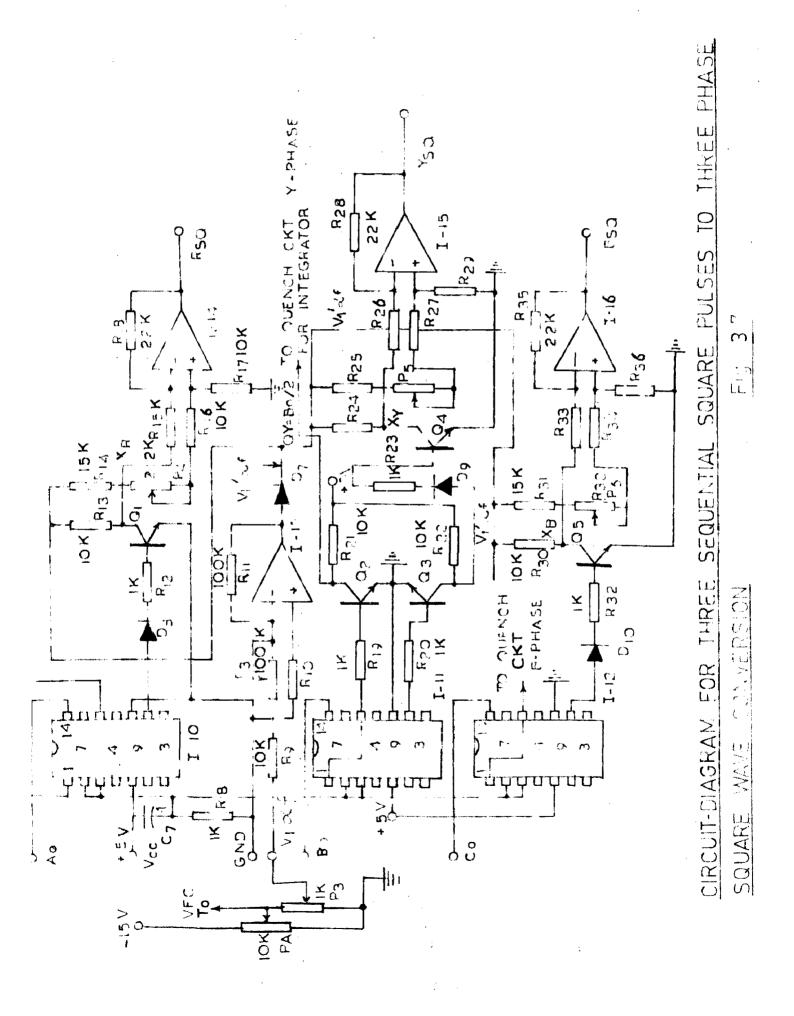

2.4.5 <u>A Completely Automatic Speed Regulating System</u>:- I.D. LANDAU<sup>[10]</sup> has described a completely automatic control system for wide range speed control of three phase squirrel cage induction motor using static converter. The block diagram of the control system is shown in Fig.2.13. The speed and the active current of the motor (that is proportional to torque for a given value of flux) are controlled in a cascaded manner. This system also ensures an independent control of sir gap flux by maintaining constant V/f operation in subsynchronous region and operation at constant rated voltage with in the frequency range above synchronous. The change over of from one control to other is accomplished by a gate circuit. The active current during overloads or transient process is limited by the current control loop. Actually the limiting value of the active current is determined by the maximum value of the speed controller output voltage. A logical change over switch, which processes logically the preset speed and the measured speed value, provides a reverse operation. The logical change over switch actuates the control device of converter, a short circuiting device and the start and protection device. The short circuiting device always short circuits one of the speed controller output  $I_{1a}R_{ST}$  or  $I_{1a}R_{TS}$  (either in phase or antiphase with respect to input) according to the motor direction of rotation so that sign  $I_{1a}^* = Sign(|\tilde{n}| + |n|)$ . The astrick (\*) indicate the preset parameters and without astrick (\*) as the measured one. ELECTRONIC CONTROL SCHEME FOR

IN VERTER WIDTH MODULATED PUL SE PHASE THREE

### CHAPTER - III

### A SOLID STATE THREE-PHASE P.W.N. INVERTER - CONTROL UNIT

### 3.0 Description of the Control Scheme

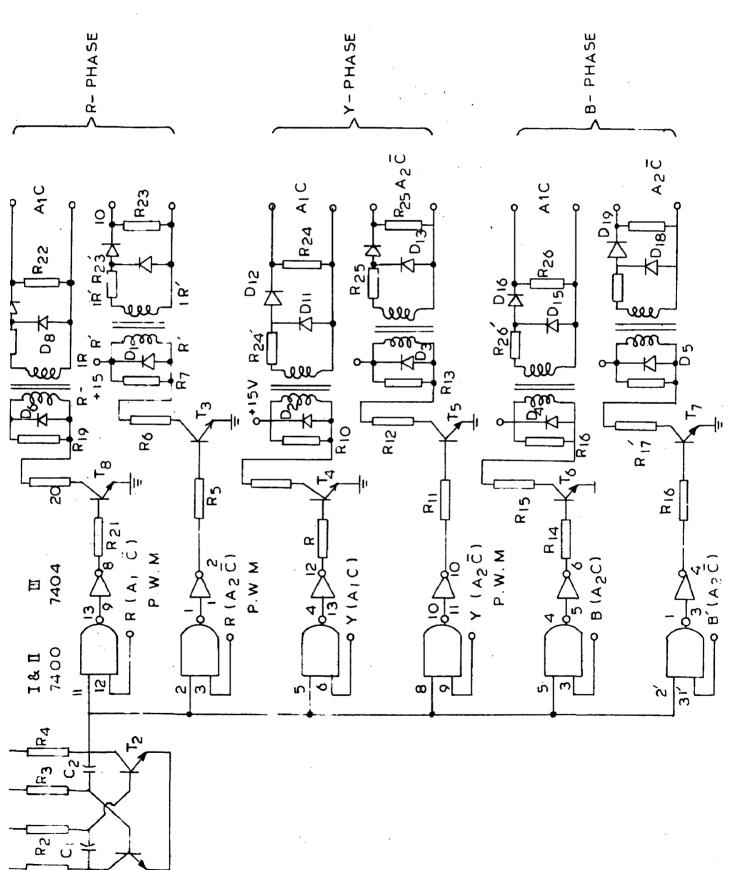

A solid state three phase P.W.M. inverter, used for speed control of induction motor basically performs the following two functions:-

- (a) It delivers a Three Phase Sinusoidal Pulse Width Modulated output voltage of variable amplitude.

- (b) It controls the frequency of sinusoidal three phase output.

Based upto the above two basic requirements, and the specific features of A Solid State Three Phase P.W.M. Inverter employing Power Transistor as a switching element(ds discussed funder section 1.4), which is designed and fabricated in this thesis. For simplicity the design and fabrication of P.W.M. Inverter is devided into two parts:-

- I The design and fabrication of Control Unit, the design of which is presented in this chapter.

- II The design and fabrication of Power Unit, the design of which is presented the next chapter i.e. chapter IV.

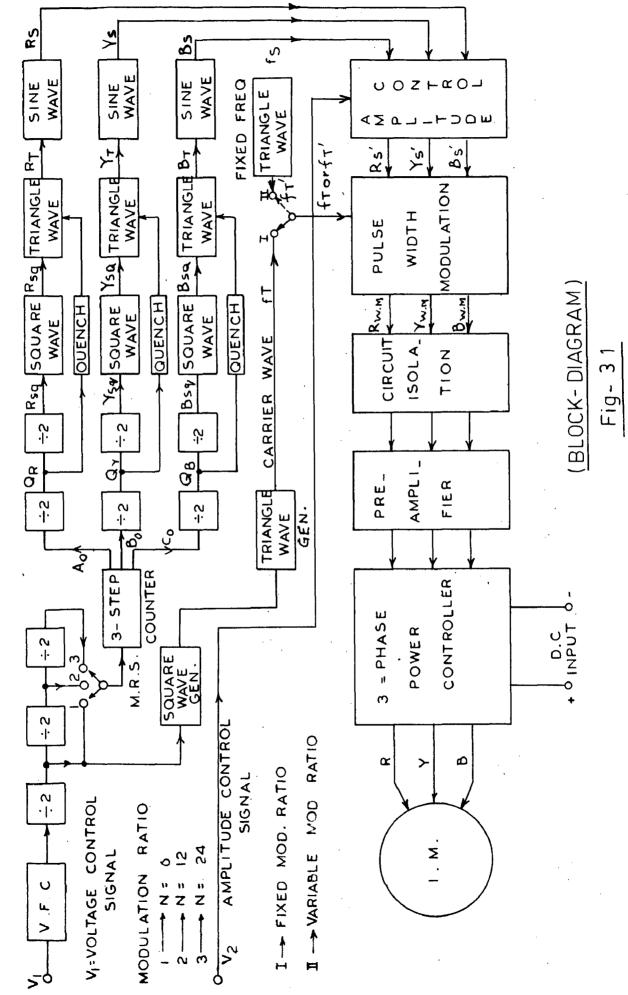

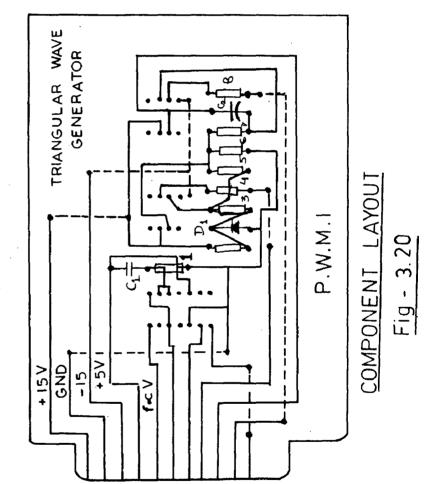

The basic control scheme used for control unit is depicted in the form of block diagram in Fig.3.1. The design considerations and the basic design of each individual block is presented in the subsequent part of this chapter (i.e. from sections 3.1 to 3.4).

•

As shown in block-diagram (Fig.3.1), the control scheme employ two control signals  $V_1$  and  $V_2$ . The d.c. signal  $V_1$ controls the fundamental frequency of the output sinusoidal P.W.N. wave, while the signal  $V_2$  controls the amplitude of this P.W.N. output wave. Further as shown in block-diagram (Fig.3.1) the signal  $V_1$  is fed to a voltage to frequency converter (V.F.C.) that generates the pulses directly proportional to this signal. The pulses from V.F.C. are divided through a binary counter in order to maintain a fixed frequency ratio of the sinusoidal reference wave to the triangular carrier wave (that is required to be generated). A proper Modulation Ratio, denoted as  $N = f_T/f_s$  where  $f_T =$  frequency of triangular wave and  $f_s =$  frequency of reference sine wave can be selected through a Modulation Ratio Selector Switch (M.R.S.); such as N = 6,12or 24.

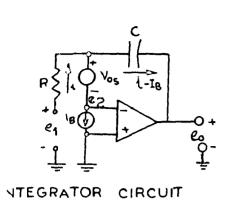

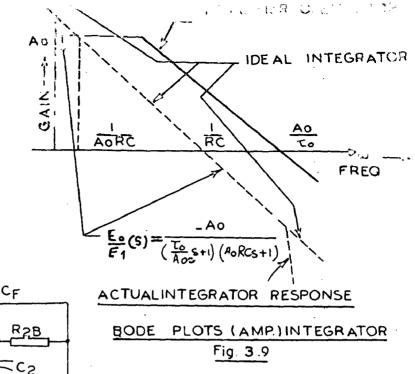

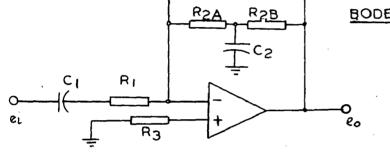

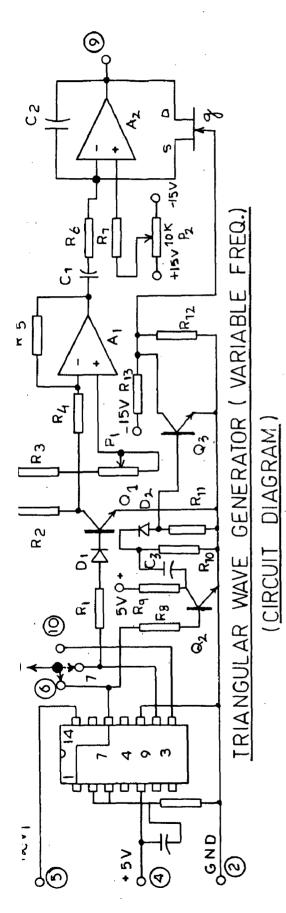

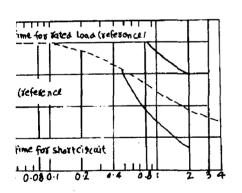

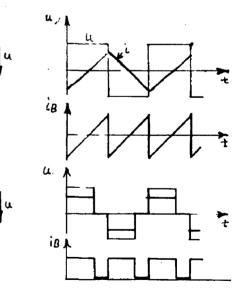

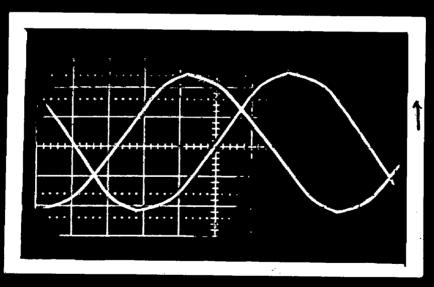

In the next stage a three-step ring counter to which the pulses are fed after a proper M.R. section; generate three seperate sequential square pulses,  $A_0$ ,  $B_0$ ,  $C_0$ , as shown in Fig.(3.1). These pulses on further division by a factor of four (actually divided by a factor of two in 2-stages) and with proper inversion generate three square pulses that are at 120 degree phase displacement (i.e.  $R_{sq}$ ,  $Y_{sq}$ , and  $B_{sq}$ ). These square pulses are unidirectional pulses and are converted to bi-directional square waves  $R_{sQ}$ ,  $Y_{sQ}$  and  $B_{sQ}$  through unidirectional square pulse to Bi-directional square pulse converters. These equare waves are then converted to triangular waves ( $R_{TP}$ ,  $X_{T}$  and  $D_{T}$ ) through square wave to triangular wave convertors or analog integrators.

In an analog-integrator any d.c. off not (althor in the invat square waves or besauce of operational emplifier used in integrator), causes a problem of saturation at the out put. Hense inorder to evereane this problem. Quenching or Resot alrealto are also added to the basic integrators, so as to provide the Report of Quench pulses to the integrators and are discussed in detail later under section (3.1.4). Further in order to maintain the amplitude of the triangular vaves constant with pospest to the variation of the reference frequency (through  $\nabla_{o} P_{o} C_{o}$ ), a d.e. signal  $\nabla_{q}$  ' proportional to  $\nabla_{q}$  is fed to square vavo convortors that vary the amplitudes of the square vaves as the frequency is varied through V. . Now the triangular vaves are converted to sine waves of constant applitude through the unvoltaping or triangular to sine-wave convertors. Theo a sot of three phase (120 degree phase displaced) constant amplitudo reference sine wave (1.e. R<sub>S</sub>, Y<sub>a</sub> and B<sub>S</sub>) is generated.

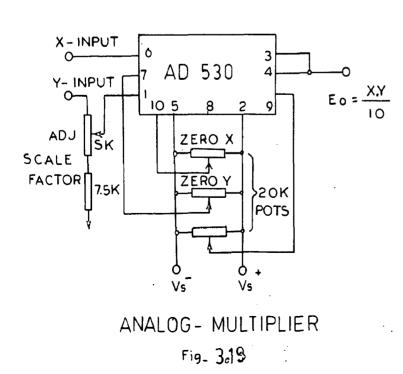

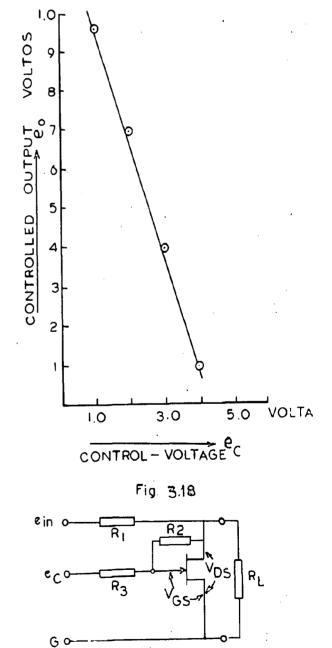

In order to maintain a constant V/Hs ratio<sup>o</sup> the amplitudes of  $R_{gp}$   $X_{gp}$  and  $B_{g}$  are controlled through analog multipliere or some other amplitude control circuits with the help of a seperate d.c. signal  $V_{p}$ (i.e. Amplitude Control Signal).

The amplitude controlled reference sine waves are Pulse Width Modulated through P.U.M. circuits where the

Sinusoidal Pulse Width Modulation is achieved through the comparator circuits. A P.W.M. circuit receives at its input, the amplitude controlled reference sine wave  $(R_S^* \text{ or } Y_S^* \text{ or } B_S^*)$  and a triangular carrier wave  $f_T$  or  $f_T^*$ , and generates a tranm of width-modulated pulses that are generated at the cross-over points of reference sine wave and the triangular carrier waves. Basically, there are two schemes of Pulse Width Modula-tion:-

- (I) <u>Fixed Modulation Ratio</u> 1- Here the ratio of trangular wave to sinusoidal wave is kept constant and is achieved by proper division of pulses after V.F.C. as shown in Fig.3.1.

- (II) <u>Variable Mountation Ratio</u> :- Here the ratio of triangular wave to simusoidal waves  $(f_T/f_S)$  varies inversely as the frequency of the reference sine waves is varied i.e. the M.R.  $(f_T/f_S)$  increases as the frequency of sine waves is reduced, and the value of M.R. is maximum when the frequency of sine wave is minimum.

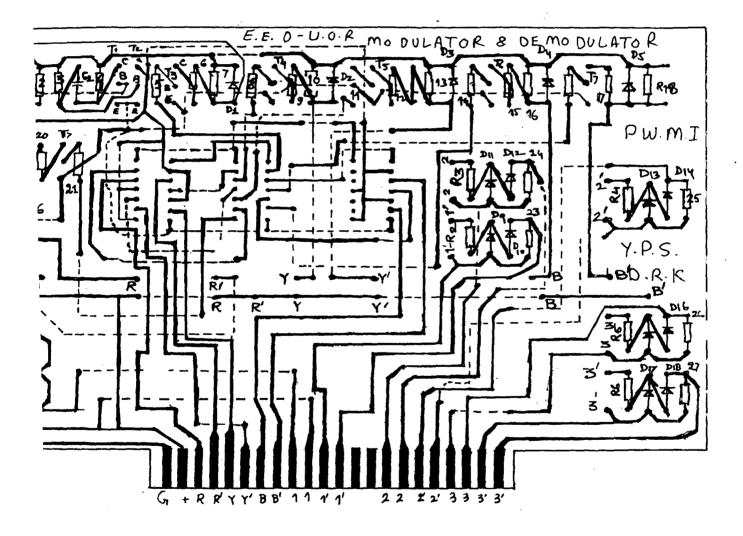

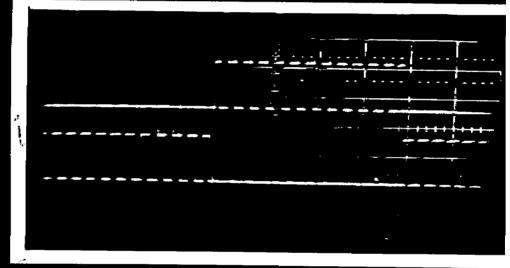

The Pulse Width Modulated Waves  $(R_{idi}, Y_{idi})$  and  $B_{idi}$ ) are now required to be transferred to the Power Control Unit, ensuring proper circuit isolation and retaining the pulse widths. The circuit isolation is normally achieved through optical isolators that employ Light Emitting Diodes and Photo-transistors. But there are two main problems in employing optical isolators i- (i) The output signal of Photo-transistor is very weak in strength and requires, large amplification. (11) Some spurious pulsesmay be generated because of ground noise or supply transients. In the scheme presented in this dissertation a new technique has been used for circuit isolation in which the width modulated pulses are first modulated with a high frequency (say 25 KHz or more). The high frequency modulated pulses are fed to the primary of pulse transformers. The pulse transformers transfer, The H.F. modulated pulse at their secondaries with proper circuit isolation. The high frequency superimposed width modulated pulses transformers at the secondaries of pulse transformers, are demodulated and produces at exact replica of pulse width modulated pulses i.e.  $R_{\rm LM}$  and  $B_{\rm LM}$ .

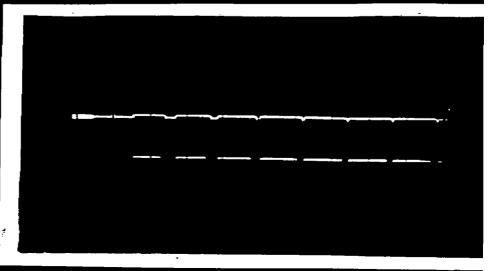

The width modulated pulses (after demodulation) are amplified in current strength through Preamplifier/Driver and then fed to Power Control Unit. The pulses after driver stage are sufficient in current strength to drive the Power Transistors in Power Control Unit at full rating. The three phase power control unit delivers at its output a three phase P. W. M. supply to control the speed of induction motor. With proper coordination of two control signals  $V_1$  and  $V_2$ , it is possible to operate the inverted fed induction motor drive in constant Volt/Hz mode.

The design and development of the control scheme as described above is devided into the following groups :--

(1) Generation of Three Phase Variable Frequency,

(constant amplitude) reference sine waves and Triangular carrier waves.

- (11) Amplitude Control of Three Phase Reference sine waves with a control signal V2.

- (111) Pulse Width Modulation of amplitude controlled sine waves with the triangular wave.

- (iv) Circuit Isolation.

# 3.1 Generation of Three Phase Reference Sine Waves and Triangular Carrier Waves

As described in section 3.1; the Three Phase sine wave is generated by converting the control signal to pulses of proportional frequency through VFC and then these pulses to three-sequential pulses through a 3-step Ring Counter. These pulses are then converted to three phase square, triangular and finally to sine waves through square wave, triangular wave and sine wave converters. Similarly triangular waves are generated either by suitable division and integration or by a seperate circuit. Hence the actual design can be further subdevided into following sub-groups:-

- (1) Design of voltage to frequency converter.

- (2) Design of Three-Step Ring Counter.

- (3) Design of Square-Pulse to Square Wave Converter.

- (4) Design of Square Wave to Triangular Wave Converter.

- (5) Design of Triangular Wave to Sine Wave Converter.

### 3.1.1 Design of Voltage to Frequency Converter:-

(a) Criterion for Selection of Proper Voltage to Freq. Converter:

A voltage to frequency converter produces, Butput frequencies that are proportional to an input. The selection

of a particular type of V.F.C depends upon the following factors:-

- (a) Input requirements:-

- (1) Input signal for full scale'f'out (Voltage and Current Limits).

- (ii) Whether input signal is single ended or differential.

- (111) Nominal input impedence of V.F.C.

- (iv) Circuit input off set voltage and off set current.

- (v) Input supply and power.

- (b) Output available :-

- (1) Output frequency range for full range of input signal.

- (11) Non-linearity in voltage to frequency conversion.

- (111) Output pulse width (Min/Max).

- (iv) Full Scale-temp coefficient ( $\pm p p m/0^{\circ}C max$ ).

- (v) Conversion time.

Out of the above factors, the accuracy and conversion time are the most important factors, that must be given due circuit considerations for the selection of a particular V.F.C currents or Integrated circuit.

Presently, very precise (highly accurate and linear) and high frequency range, voltage to frequency converters are available in integrated circuit chip form. We may have V.F.C with frequency range from 10 KHz to 5 MHz and linearity ranging from 1 % to .005%. But these V.F.C chips are very costly.

The precison V.F.C chips are not readily available in India. The only readily available chip is 566, that has frequency range of 10 KHz and linearity of only 1 %.

For our purpose where 10 KHz frequency is sufficient and 1 % linearity is tolerable, the 566 chip seems to be a good selection and we could have used it no doubt but in some more precise variable speed drives we may require a better linearity. In view of this fact we have selected a voltage to Frequency Converter circuit<sup>[11]</sup>, that employ only two general purpose operational amplifiers and some discrete components. This circuit has low cost and a good linearity of the order of .05 %.

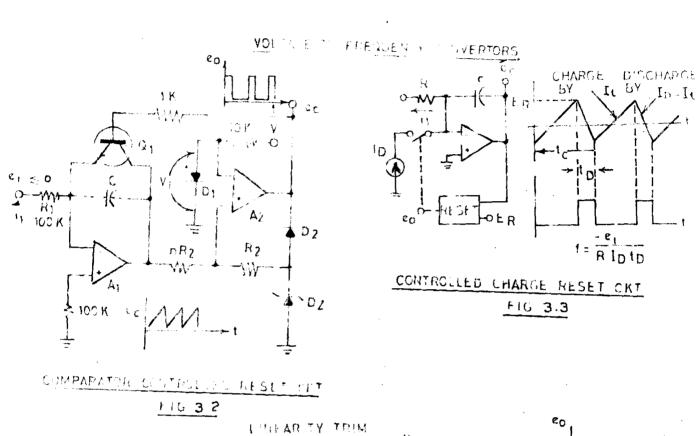

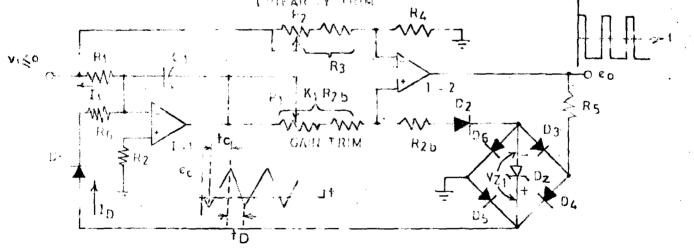

### Basic Design of Voltage to Frequency Converter :-

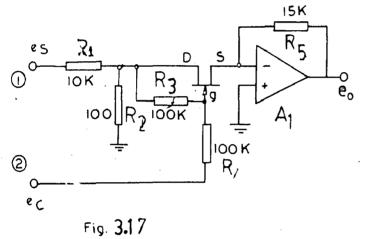

The basic circuit of a V.F.C is shown in Fig.3.2 and consists of an integrator and a comparator. When an input signal of constant amplitude is applied to the integrator, it charges the capacitor  $C_1$  at the rate defined by the time constant set by  $R_1$   $C_1$  combination and causes the output of the integrator to increase linearly with time. The comparator employs a sener diode to control the high threshold and has hysteresis to provide low threshold. In this circuit a negative input voltage causes the output of the integrator

......

increase to  $o_c = n \ \forall z \ (n \ 1) \ \forall_f$ . At this point the constor output suings to positive and turns on the reset suitch The reset suitch discharges the capacitor C and it contisuntill  $o_c$  reaches the low threshold of the comparator. low threshold equals the forward voltage drop across the lo  $b_{10}$  or the voltage level at the inverting (-) input of comparator. It can be observed that  $R_2$  supplies no positive iback so long as the output is positive, because of diede

The diode  $D_q$ , always heaps the lower threshold about zero. ) is necessary since  $Q_q$  can not discharge the capacitor C but the transistor saturation voltage. The change in capacitor tage during each cycle between two comparator switching point  $n(V_B \diamond V_f)$  as shown in Fig.3.2. The operating frequency of convertor is determined by time required for this change in lefter voltage (i.e.  $\Delta \circ_{\mathbf{G}}$ ). If we assume that if the input rent  $\mathbf{i}_4$  remains constant during the charging cycle, then charging time is given by  $\Delta \mathbf{t} = C_*\Delta \circ_{\mathbf{G}}/\mathbf{i}_4$  and the frequency  $f = 1/\Delta \mathbf{t} = -\mathbf{e}_4/\operatorname{nCR}(V_E \diamond V_F)$

performance of this V.F.C. depends upon the off set, carity and gain. The error produced in output frequency auso of offset produced by the operational amplifier  $A_q$ , given by

$$= (\nabla_{\alpha\beta} \diamond \mathbb{I}_{\alpha\beta} \cdot \mathbb{R}_{\beta}) / [n \mathbb{CR}_{\beta} (\nabla_{\beta} \diamond \nabla_{\beta})]$$

(3.9)

ro  $V_{OS}$  is the off-set voltages and  $I_{OS}$  is the off-set rent of the operational amplifier  $A_{i}$ .

The Non-Linearity error is introduced by the discharge time  $t_D$ and the limited gain of  $A_1$  and is given by

$$\Delta f N = f.[f.t_{D} + \frac{n(v_{g} + v_{f})}{A_{0} o_{i}}]$$

(3.2)

= Non-linearity.

The slow rate of the op-amp or the maximum current of  $h_{ave}$ the discharge switch  $Q_{i}$ , which ever is more limiting effect determines the reset time  $t_{D}$ . Normally the gain error is governed by the tolerance variation of  $R_{i}$ ,  $C_{i}$ ,  $R_{2}$ ,  $nR_{2}$ ,  $D_{i}$  and  $D_{i}$ .

A technique to achieve better linearity with higher frequency :-

The operating frequency limits of a V.F.C. are governed by two factors:-

(a) The conversion time, that places a limit on the minimum operating frequency and for practical conversion times not exceeding 1-sec., the minimum usable converted frequency is 1 Hz.

(b) The resulting time of the integrator capacitor limits high

frequency operation.

Also the non-linearity error is introduced by the reset time and to reduce this error to .01 %, the reset time must be no more than .01 % of the minimum signal period i.e. 10-n-sec for 10 KHs range. Practically it is very difficult to achieve such short reset intervals and even if achieved they produce sharp pulses of such a small pulse width that they are absorbed by the line capacitance itself. Hence a technique is employed to supply to the integrating capacitor, a controlled amount of resetting charge, rather than a fixed reset voltage in order to extend dynamic range for improved precision.

The principle of operation of a V.F.C. employing controlled charge reset circuit is depicted in Fig.3.3. In this circuit the reset charge is supplied each time, the input signal charges the integrating capacitor to a reference level  $E_R$ , at a rate determined by the current  $i_1$  from an input signal. At the reference level the discharge current  $I_D$ , discharges the capacitor for a period  $t_D$ . As the process repeats the charging and discharging voltages are equal and opposite since  $Q_c = i_1 t_c = -Q_D = I_D t_D$ .

where  $I_D = Discharge current$ ;  $t_D$  is the discharge time;

i is the input charging current and  $t_c$  is the charging time. Also  $Q_c$  and  $Q_D$  are the amount of charges that provide charging and discharging respectively.

The frequency of oscillation is given by  $f = 1/t_c = 1/i_0 \cdot t_0 \cdot i_i$ =  $-e_i/R \cdot I_0 \cdot t_0$ .

If I and t are constant we can clearly observe that f  $\alpha \, \mathbf{e}_i$  .

## A Precision Voltage to Frequency Converter :-

The circuit of a precision VFC employing controlled reset charged reset technique is shown in Fig.3.4. Similar to comparator controlled reset circuit as shown in Fig.3.2, this circuit also contains an integrator and a comparator. But the

comparator in this precision circuit provides a controlled discharged current  $I_D$  and a fixed discharge time and thus ensures a constant reset charge of  $Q_D = -I_D \cdot t_D \cdot A$  fixed voltage across the zener diode feeds a controlled discharge current through a summing resistor  $R_6$ . The input signal is coupled to the comparator in order to produce a fixed discharge time, rather than a fixed voltage.

If we apply a negative signal  $V_i \leq 0$ , then the output of the comparator is positive. This positive output conducts a current through  $D_4$ ,  $D_2$  and  $D_6$ . Now a voltage of  $V_2 + V_{16} - V_{11}$ is established across the resistor Rg and creates a discharge current of  $I_D = V_g/R_g$  since  $V_{ff} = V_{ff}$ . Also the current  $I_D > I_1$  and causes a negative going ramp at the output of the integrator I-1. This ramp continues to the 1st trip point of the comparator. The first trip point of the comparator is set only by e, because the diode D, disconnects the positive feedback for positive values of the comparator and is given by  $e_c = V_1/K_2$  where  $K_2 = R_1/(R_2 + R_1)$ . When the negative going ramp voltage at the non-inverting pin of I-2 comparator reaches this trip point, the output of the comparator swings from positive to negative voltage. This negative voltage applies reverse bias at the diode D, and stops discharging. The current  $I_4$  now starts charging the capacitor till the second trip point of the comparator is reached.

The second trip point of the comparator is decided by  $e_4$  and the positive feedback of the comparator, since the diode

$D_2$  now conducts and completes the positive feedback path. The diede byidge in this case inverts the voltage presented by the sener. Thus the same gener diede  $D_3$  establishes a second trip point as well as the discharge current (as indicated carlier). The sener diede thus play an important role in the operation of this VFC. The sener creates a voltage of  $-V_3 = V_{f5} + V_{f2}$  on the comparator feedback resistor  $R_2^{-1}$ . The second trip point is  $Q_3 = K_9(V_3 + V_9/K_2) + V_9/K_2$ , as  $V_{f5} = V_{f2}$ .

The total change in  $q_c$  is given by the difference of these two trip points i.e.  $\Delta q_c \approx K_q (V_g \approx V_q/K_2)$  we can note here that  $\Delta q_c$  is a function of  $V_q$  and hence while discharge time  $t_D$  a constant. The discharge time  $t_D \approx \Delta q_c \cdot C/(I_D - I_q)$  $\simeq \Delta q_c \cdot C/(V_g/K_s \approx V_q/K_q)$  or  $t_D \approx \frac{K_q (V_g \approx V_q/K_2)C}{(V_g/K_s \approx V_q/K_q)} \approx K_q \cdot R_s \cdot C$ since  $R_q \approx R_s$ . With  $t_D$  a constant, the convertor response relates linearly to

$$o_{i} \circ a_{i} \circ o_{i} / (R_{i} \square_{i} \nabla_{i})$$

(3.3)

As discussed already the linearity-error depends upon the reset or the discharge time, and therefore once the discharge time is made constant, the circuit becomes highly linear and error is minimized by reducing  $t_0$  to a minimum by supplying a maximum possible controlled reset charge that greatly depend upon  $V_B$ . The performance of this circuit basically depends upon the component selection, the off set in operational amplifiers and the linearity error.

# Calculation and Selection of Values of the Components for Voltage to Frequency Converter:-

It is evident from the block diagram that the max.ratio between the frequency of voltage to frequency converter and the frequency of three phase reference sine waves  $(f(V.F.C.)/f_g)$ is 96. Hence when the reference sine waves have a maximum frequency of 100 Hz, the V.F.C. output would have a maximum frequency of 9.6 KHz at a max. controlsignal of -10V. V.F.C. employ the operational amplifiers 741 for I<sub>1</sub> and I<sub>2</sub> as shown in Fig.3.4 and because of its gain band width limitation it can not give a good linearity above 5 KHz. It is therefore recommended to operate V.F.C. in two ranges (i) 5Hz to 50 Hz and (ii) 50 Hz to 100 Hz; if the modulation ratio is to be selected as 24. For a modulation ratio of 12 or 6 the range (i) itself can be used for frequency range of 5Hz to 100 Hz, since V.F.C. would operate at a max. freq. of 5 KHz in these of cases.

As shown in equation (3.3), the output frequency of the V.F.C. is given by  $f = e_1/(R_1 CK_1 V_2)$ . Now selecting  $R_1 = 100$  K;  $K_1 = 1$  (such that  $K_1 \cdot R_2 b = 2 \cdot 2$  K-ohm + 1 K-ohm preset and  $R_2 b = 3 \cdot 3$ K-ohms);  $V_2 = 9 \cdot 1$  Volts and operating frequency = 5 KHz for  $e_1 = -10V_2$ , we get the value of capacitor as

$$C = \frac{e_2}{f \cdot R_1 \cdot K_1 \cdot V_z} = \frac{1}{5 \times 10^3 \times 10 \times 10^3 \times 1 \times 9.1}$$

1.e.

$$C = \frac{1}{45.5} \times 10^{-6} = 0.022 \ \mu F.$$

The value of  $R_5$  is selected to be 500 ohm, so that it gives a sufficient regulating current to sener  $D_x$  when  $e_0$  is

positivo. The discharge current  $I_D$  is fixed by  $\nabla_{BV}$  and  $W_{A}$ and for a scaer value of 9.1V, the value of  $W_{B} = 10$  is justified since it shall field a discharge current  $I_D = 9$  mA (approx.) that is much larger (about 100 times) than the masscum injust current which is .09 mA, that is the basis sequirescus.  $C_2$  is conveniently selected as 100 while  $N_2 = 10$  and  $P_2 \approx C_3 = 2.20 \approx 10$  can serve as an accurate linearity trim. The discise  $Q_1$  to  $Q_2$  should be of high speed type in order to have a good performance at high frequency upto 10 MMs.

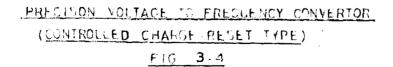

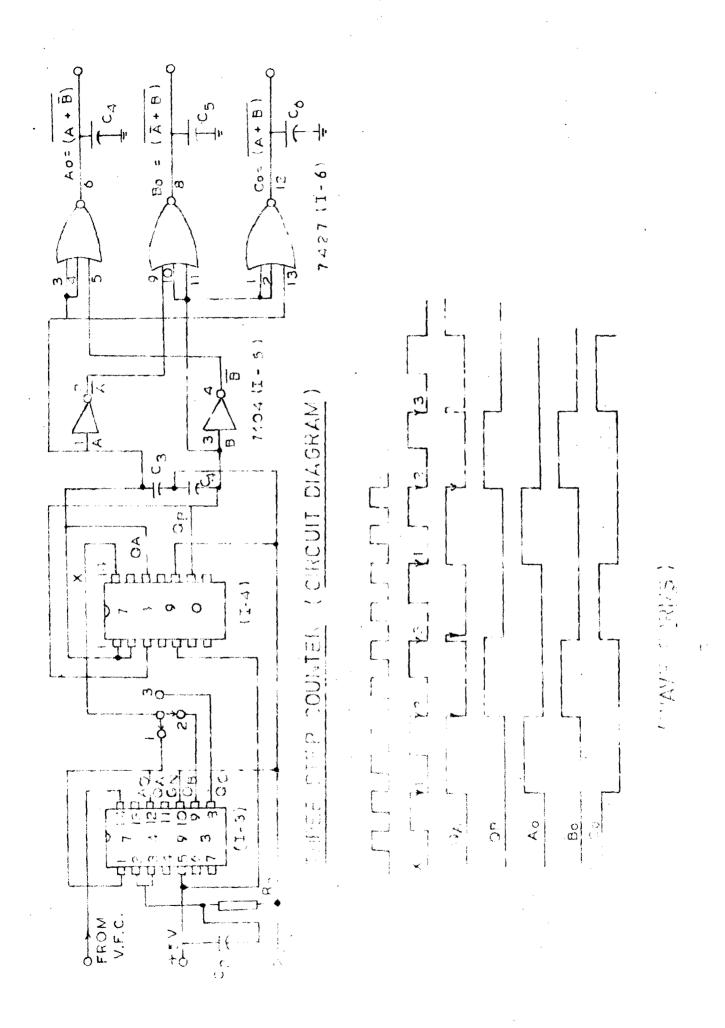

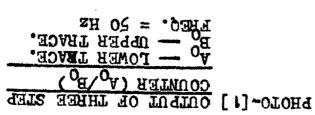

.1.2 Design of Three Step Counter :- The output from voltage to frequency converter is in the form of pulses. This is converted to square wave with the help of a binary counter 7493 by dividing by two. The square wave is further divided by the same factor in next two steps. As shown in Fig.3.5, this division can be obtained at the outputs  $Q_A$ ,  $Q_B$  and  $Q_C$  of IC 7493 (I-3). These outputs are connected to a Modulation Ratio Selector Switch which can select any number 'N' = Frequency of Triangular Carrier/frequency of sine wave. The pole of the selector switch is connected to the 3-step ring counter.

The 3-step ring counter gives a pulse at each step of counting through a digital counter IC-7490 (I-4). The truth table for a counting sequence of 1 to 3 is given below:-

| Counting Sequence | Outputs |                |                |                |

|-------------------|---------|----------------|----------------|----------------|

|                   | QD      | Q <sub>C</sub> | Q <sub>B</sub> | Q <sub>A</sub> |

| 0                 | 0       | 0              | 0              | 0              |

| 1                 | 0       | 0              | 0              | 1              |

| 2                 | 0       | 0              | 1              | 0              |

| 3                 | C       | 0              | 1/0            | 1/0            |

The output  $Q_A$ ,  $Q_B$ ,  $Q_C$  or  $Q_D$  are at low level (= 0.8VI) for state 0 and at high level (= 3.5V) for state 1. Now if the output  $Q_A$  and  $Q_B$  are connected to 'Reset to Zero', inputs ( $R_{01}$  and  $R_{02}$ ) of the 7490, then the counter will reset at every third pulse. In order to obtain a separate pulse at each step ;