# MICROPROCESSOR BASED DIGITAL CONTROL OF

# **NON-DISPERSIVE INFRARED SPECTROPHOTOMETER**

(A SYSTEM DESIGN APPROACH)

### **A** DISSERTATION

Submitted in partial fulfilment of the requirements for the award of the Degree of

# MASTER OF ENGINEERING

in ELECTRICAL ENGINEERING (System Engineering & Operational Research)

> By ATAM P. DHAWAN

DEPARTMENT OF ELECTRICAL ENGINEERING UNIVERSITY OF ROORKEE ROORKEE, (INDIA) MAY, 1979

#### CERTIFICATE

Certified that the thesis entitled 'Microprocessor Based Digital Control of Non-Dispersive Infrared Spectrophotometer' which is being submitted by Mr. Atam P. Dhawan in the partial fulfilment of the requirements for the award of the Degree of Master of Engineering in Electrical Engineering, in System Engineering and Operational Research Group, of the University of Roorkee, Roorkee, India, is a record of student's own work carried out by him under my supervision and guidance. The matter embodied in this thesis, has not been submitted for the award of any other degree.

This is further to certify that he has worked for a period of about four and a half months (from January 1979 to May 1979) at this University for preparing this thesis.

Roorkee  $\frac{1}{24-5-75}$

( M.K. Vasantha ) Reader, Electrical Engg. Department, University of Roorkee, Roorkee ( India )

## A C K N O W L E D G E M E N T

Author wishes to express his profound gratitude and sincere thanks to his guide Sri M.K. Vasantha, Reader in Electrical Engineering Deptt., University of Roorkee, Roorkee for his erudite guidance, wise suggestions and encouragement, the author received from him.

A warm expression of gratitude is due towards all who took interest in completion of this dissertation work.

Atam P. Thawan

( ATAM P. DHAWAN )

# CONTENTS CONTENTS

CERTIFICATE

۲

## ACKNOWLEDGEMENT

| 1. | INTRODUCTION                                                  | l  |

|----|---------------------------------------------------------------|----|

|    | Absorption Spectrometer                                       | 2  |

| 2. | INFRARED SPECTROSCOPY                                         | 7  |

|    | Mechanics of Measurement                                      | 9  |

|    | Application of Infrared Spectroscopy                          | 10 |

| 3. | INFRARED ABSORPTION SPECTROPHOTOMETER                         | 13 |

|    | Non Dispersive Analyzers                                      | 13 |

|    | Description of the P.E.180 Model used                         | 16 |

| 4. | A VIEW OF MICROPROCESSORS                                     | 20 |

| 5. | DIGITAL DATA PROCESSING                                       | 29 |

|    | Computer Spectrometer System                                  | 32 |

|    | Digital Control                                               | 34 |

| 6. | INFRARED DATA HANDLING AND REDUCTION                          | 36 |

|    | Detailed Description of <sup>M</sup> ain Program<br>Functions | 37 |

| 7. | MICROPROCESSOR SELECTION                                      | 50 |

| 8. | GENERALIZED SOFTWARE USING CP1600                             | 56 |

|    | Programming of a Ratio Routine                                | 56 |

|    | Generalized Main Program Applied to CP1600                    | 58 |

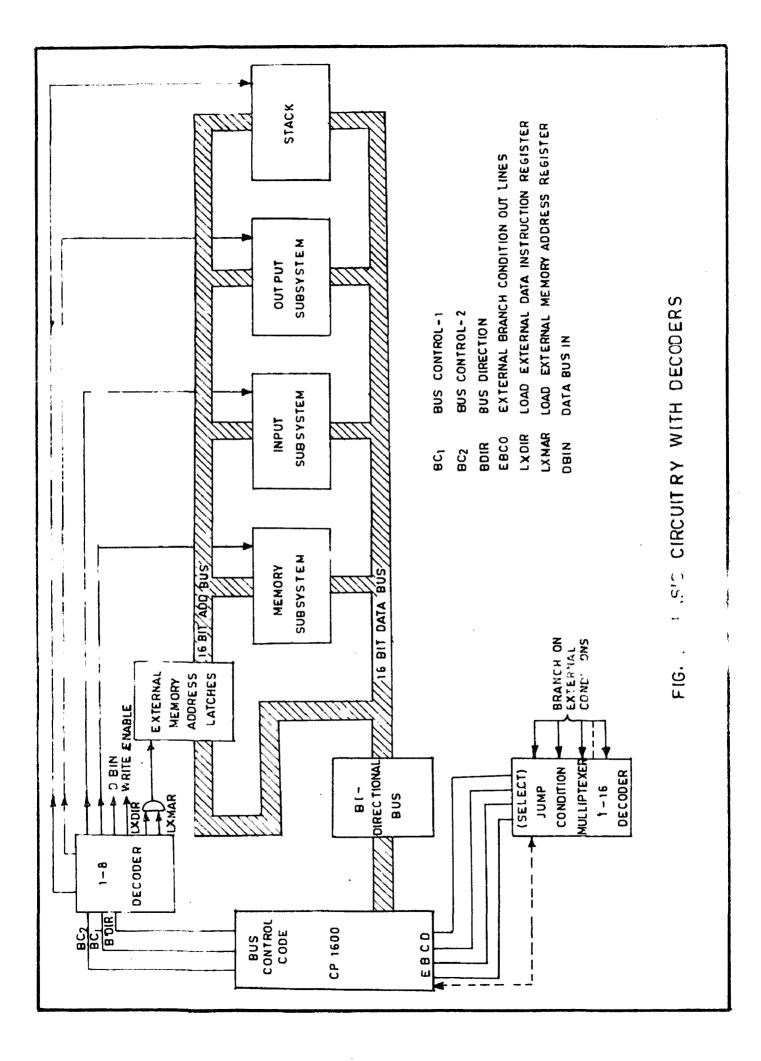

| 9. | HARDWARE SUPPORT                                              | 63 |

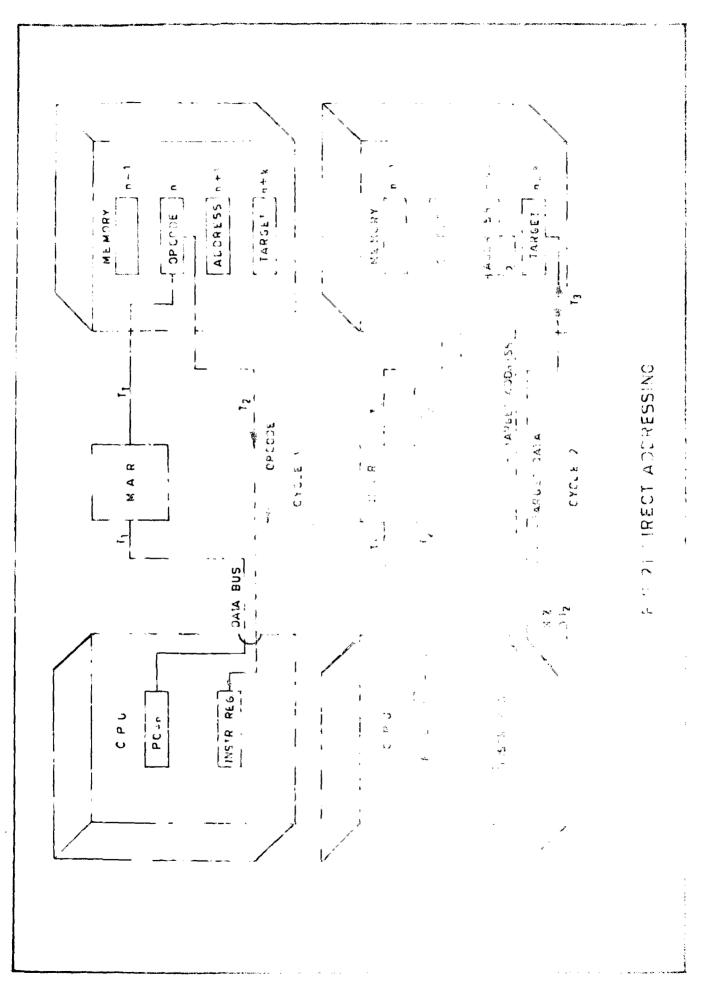

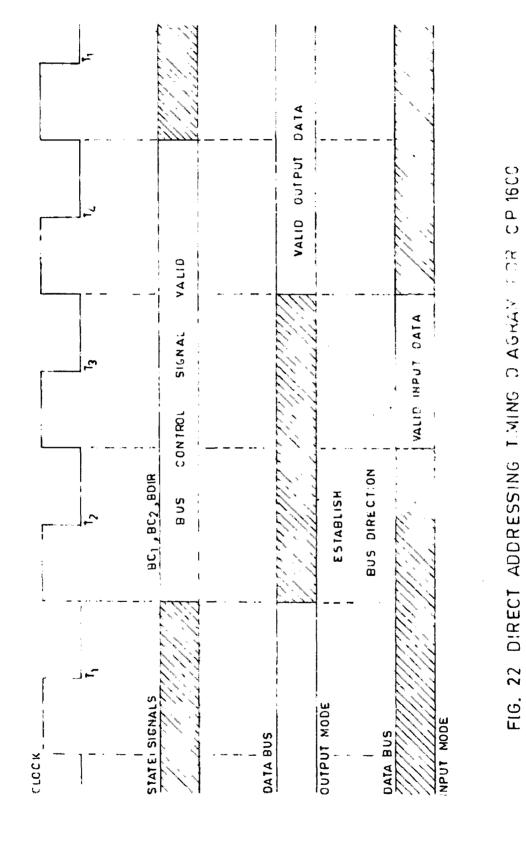

|    | Direct Addressing                                             | 67 |

|     | Test External Conditions                                    | 70 |

|-----|-------------------------------------------------------------|----|

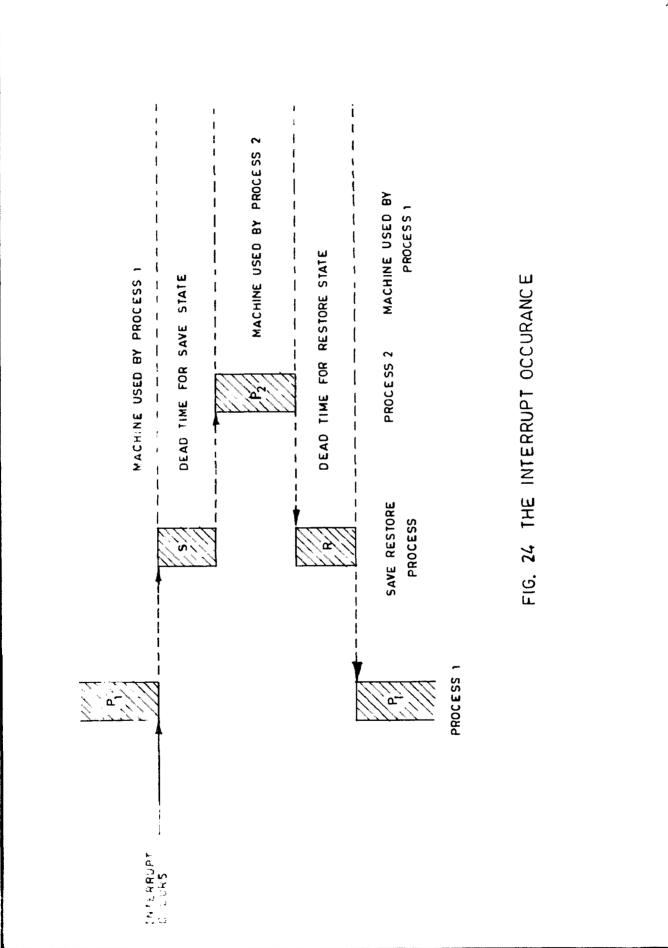

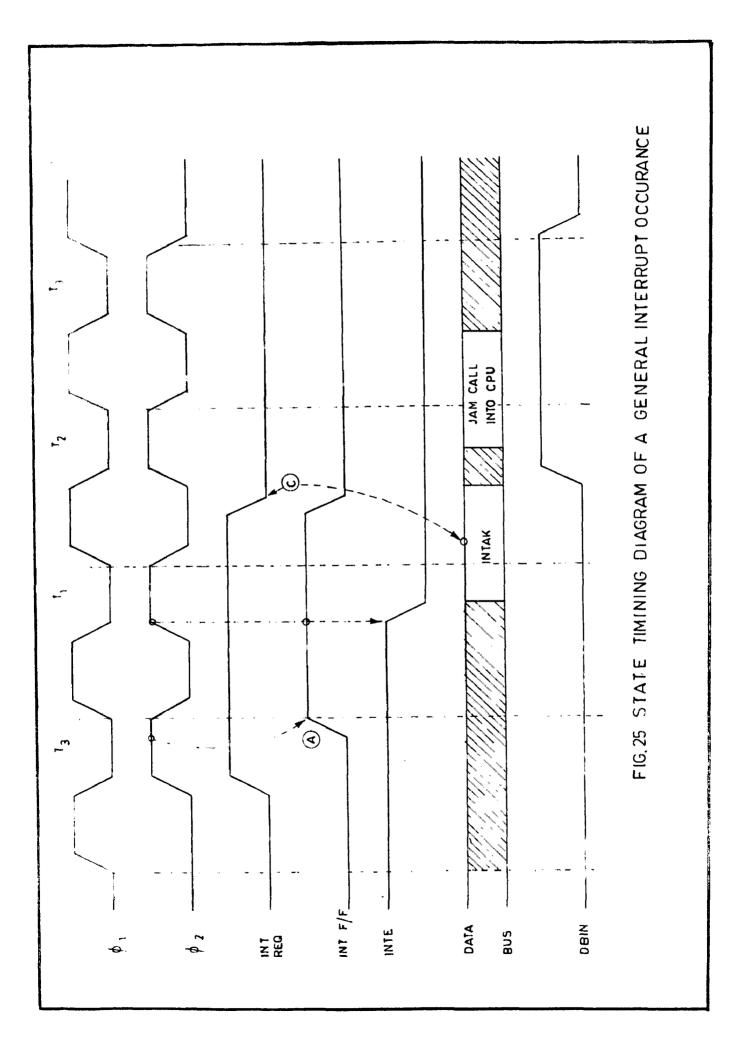

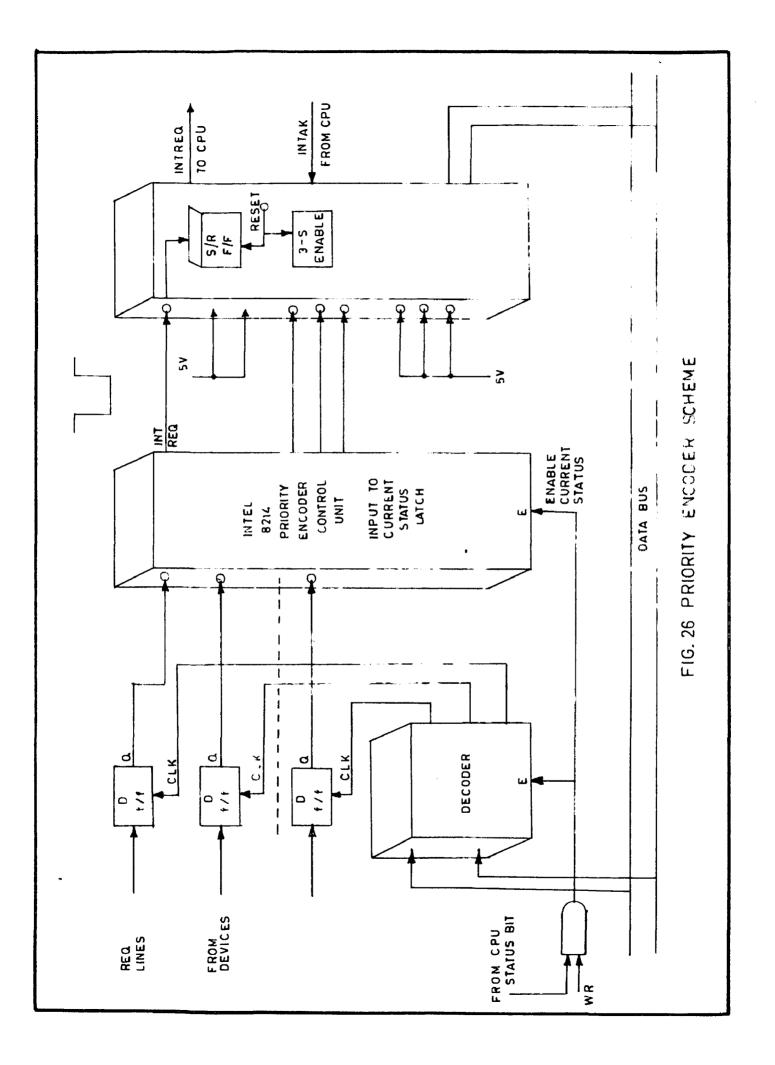

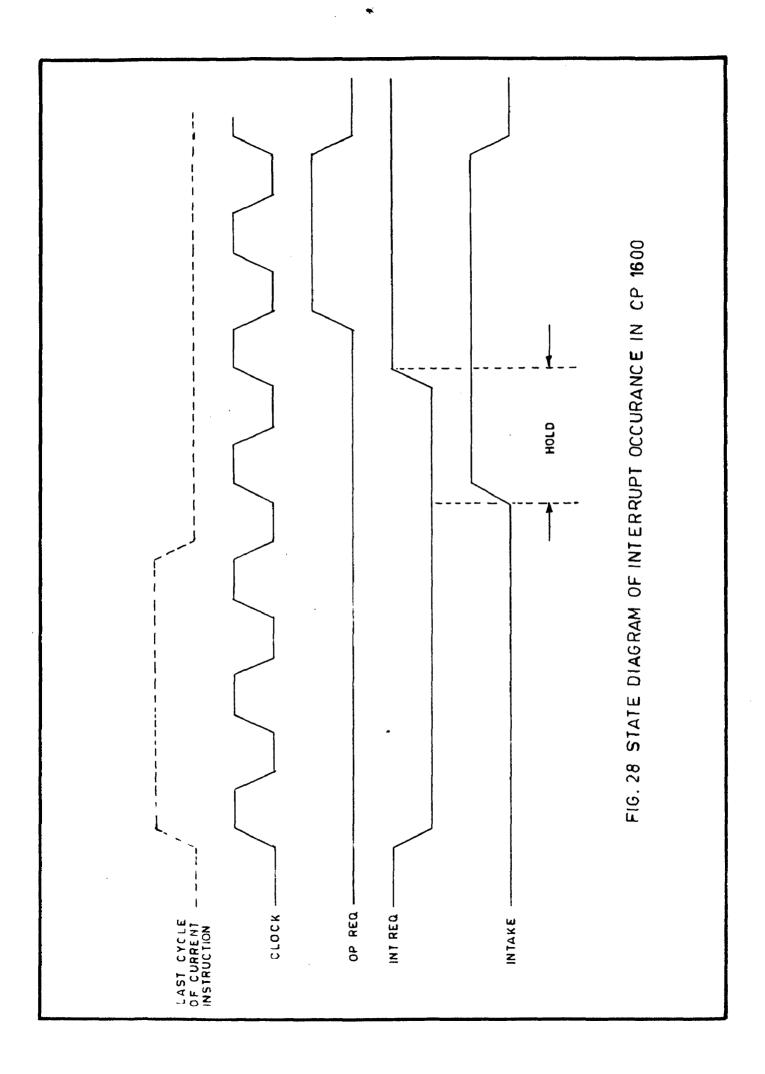

|     | Inturrept Structure                                         | 71 |

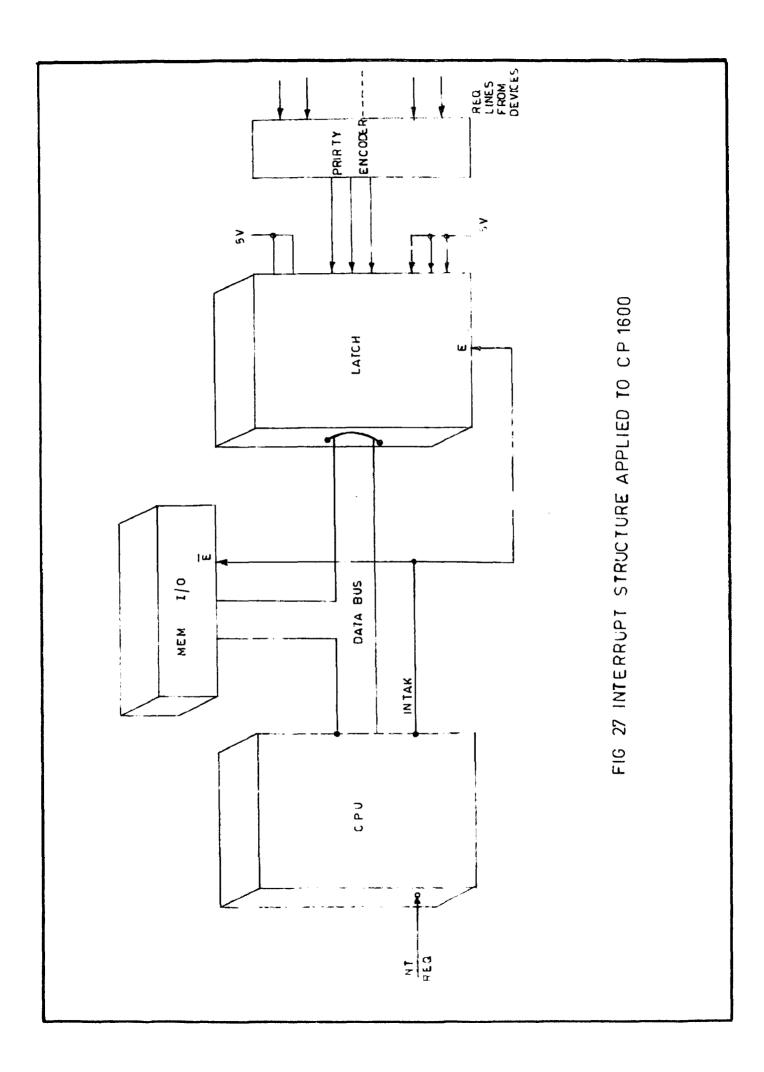

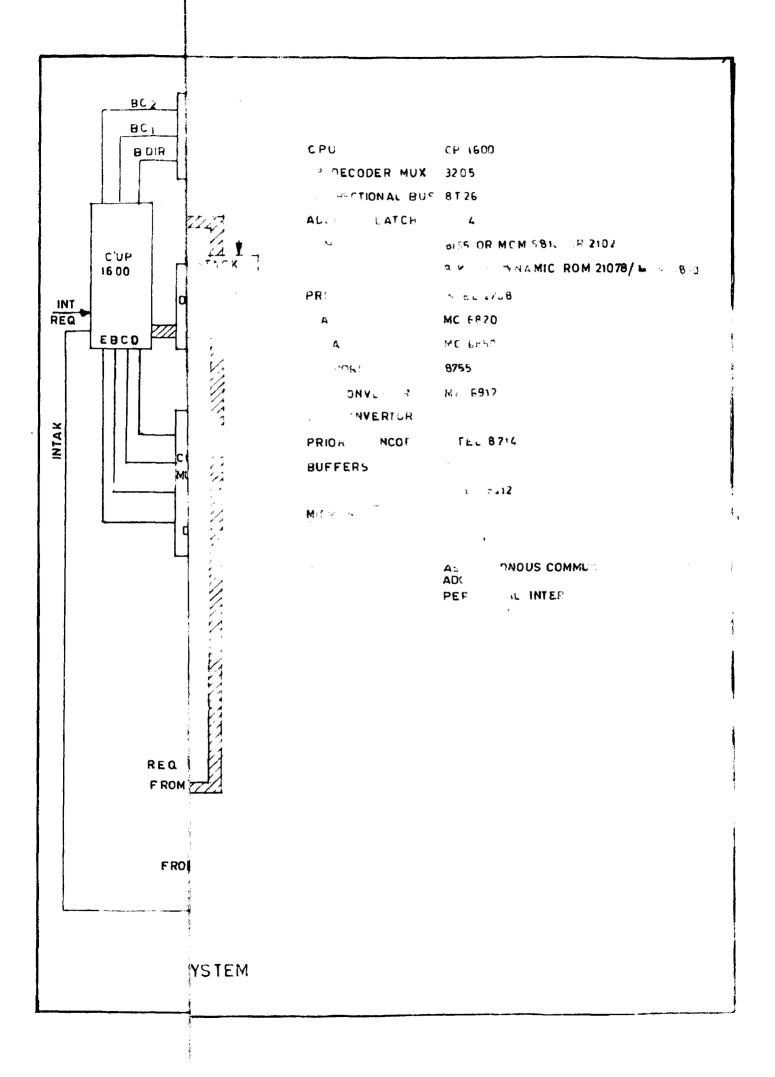

|     | Interrupt Structure Applied to CP1600                       | 74 |

| 10. | ADVANTAGES OF A MICROPROCESSOR BASED<br>NDIR CONTROL SYSTEM | 78 |

| 11. | CONCLUSION                                                  | 81 |

|     | REFERENCES                                                  | 83 |

|     | APPENDIX A - PARTIAL LIST FOR INSTRUCTIONS<br>FOR CP1600    | 87 |

|     | APPENDIX B - SUBROUTINE PROGRAMS                            | 92 |

|     | APPENDIX C - NDIR MAIN PROGRAM                              | 99 |

|     |                                                             |    |

.

: .

#### CHAPTER -I

#### INTRODUCTION

In the past decade computer technology and design (both analog and digital) and the development of low cost linear and digital 'integrated circuitry' have advanced at an almost unbelievable rate. Thus computers and quantitative electronic circuitry are now readily available to chemists, physicists, and other scientific groups interested in instrument design.

"The computer and integrated circuitry are revolutionizing measurement and instrumentation in science".

In general, chemist, physicists and others have just begun to realize and understand the potential of computer applications to their respective research and quantitative measurement. The basic applications are in the areas of data acquisition and reduction, simulation and instrumentation (on-line data processing and experimental control and/or optimization in real time).

For years, while much of the spectroscopic instrumentation market was ignoring the inroads being made into the laboratory by minicomputers and now by microprocessors, individual researchers were deeply involved in the making of laboratory 'workhorse' instruments and powerful laboratory computers. Infrared opectrophotometry has long had . the reputation of being only semiquantitative at best. For

this reason, some of the attention being lavished on the recently developed Fourier transform infrared instrumentation is derived from long-held misconceptions regarding conventional dispersive instrumentation. The dispersive instrument manufactures are moving slowly in the world of today, an era of sophisticated, computer based data acquisition and reduction. As they begin redesigning their 10-yearold dispersive/non-dispersive instrumentation with modern, high speed detectors and associate them with low cost, small computers and now by microprocessors based systems, the field will enjoy a second childhood. The huge advantage of microprocessor aided instrument is that these procedures can be absolutely standardized and are then not subject to error or variation from operator to operation. Another advantage is the uniformity of reporting format, usually taking the form of an alphanumeric printout under control of the microprocessor.

This scheme shows that an infrared absorption spectrometer, such as non-dispersive infrared (NDIR) spectrometer widely applied in the chemical industries and in air pollution control can be successfully married to a microprocessor revealing a lot of advantages being NDIR digital control system.

#### ABSORPTION SPECTROMETER

Radiation passed through semitransparent substances

-2-

in characteristically absorbed selectively, the amount of energy transmitted being a function of the wavelength as well as the depth of the optical path through the sample and the concentration of the absorbing material (Beer's Law). Infrared spectra are generally unique and characteristic of particular organic and inorganic compounds as a result of the interaction of the infrared radiation with the molecular structure, exciting vibration and bending modes of motion and accounting for the energy absorption.

Absorption spectrometers fall into two categories dispensive and non-dispensive. The former type spreads out radiation from a source in space, using a prism or grating and selects a narrow wavelength by passing the dispersed radiation through a slit (this assembly being termed a monochrometer). The resulting beam is passed through a cell containing (the sample and the transmitted radiation is measured by a photoelectric detector. As the monochrometer setting is swept through a range of wavelengths, the spectrum can be plotted on a recorder. In the non-dispersive type, all the radiation, not just a small pass-band is passed through the sample cell. The transmitted energy is detected and then the same amount of source radiation is passed through a reference cell (usually containing a

-3-

non-absorbing gas such as nitrogen) ; the two signals are then compared.

Since the NDIR type utilizes all the energy from the source which covers a broad band of wavelengths, it consequently generates a largest signal and is more sensitive.

The addition of digital data acquisition and reduction hardware to an inherently irreproducible instrument may seen like a foolish preposition at first. However, some of the simplest applications of digital data handling can significantly improve the quality of information from even the least expensive infrared instrumentation. The capability to spectrum-average is a valuable technique for improving the signal noise (S/N) ratio in regions of low transmittance. Averaging n spectra together to form one spectrum, provided that the response time of the detector is taken into account, produces an improvement in S/N equal to the square root of n.' This technique has been employed to great advantage in Fourier transform infrared spectroscopy, where averages of 100 scans are often employed in order to inverse the S/N on a high resolution spectrum. Additional advantages are available to the spectroscopist with some kind of computing capability, such as slit function deconvolution mathematical smoothing, and separation of overlapping peaks.

-4-

It is always possible that some infrared spectrscopists will contend that the inherent properties of complex infrared spectra and some samples will make the acquisition of digital data a waste of time. Strongly absorbing samples, which require reference beam matching or severe attenuation to produce a satisfactory spectrum, suffer from the inability of many instruments to yield identical results from one-day or even hour, to the next. The drawing of base-lines is a difficult task for even the most experienced spectroscopist, when overlapping bands must be used in a quantitative determination. Few infrared spectroscopists will trust the drawing of baselines to their computer, even though the computer's baseline efforts are much more predictable than most of a group of spectroscopists. Complex spectra, such as those of synthetic polymers, do not lend themselves to quantitative analysis of such things as plasticizers, filters etc., except where the substrate spectrum has no interfering absorption bands. With such complex spectra, though, it is often possible to obtain a reference sample which does not contain the analyte . The spectrum of the reference material can then be stored as a baseline to be subtracted from spectra of samples containing the analyte. Using a computer, some fraction of this baseline can be subtracted from the spectrum of a subsequent sample. In this manner,

-5-

the complex baseline is completely removed from consideration, and the spectroscopist can then focus on the difference spectrum for this analysis.

The aim of this work is to present a suitable and adequate hardware for the interface of non dispensive infrared spectrometer to a microprocessor based digital control system and required software to overcome all the difficulties of spectroscopy analysis.

#### CHAPTER - II

#### INFRARED SPECTROSCOPY

The ordinary infrared region extends from 2.5 to 15  $\mu$  (4000 to 667 cm<sup>-1</sup>); the region from 0.8 to 2.5  $\mu$ (12,500 to 4000 cm<sup>-1</sup>) is called the near-infrared and the region from 15 to 200  $\mu$ (667 to 50 cm<sup>-1</sup>) is called infrared. The wave number is directly proportional to the absorbed energy ( K = E/hc), whereas the wavelength is inversely proportional to the absorbed energy (  $\lambda = hc/E$ ;  $\lambda = 1/K$ ).

A molecule is not a rigid assemblage of atoms. A molecule can be said to resemble a system of balls of varying masses, corresponding to the chemical bonds of a There are two kinds fundamental vibrations for molecule. molecules ; stretching in which the distance between two atoms increases or decreases, but the atom remains in the same bond axis, and bending ( or deformation), in which the position of the atom changes relative to the original bond axis. The various stretching and bending of a bond occur at certain quantized frequencies. When infrared light of the same frequency is incident on the molecule, energy is absorbed and the amplitude of that vibration is increased. When the molecule reverts from the excited state to the original ground-state, the absorbed energy is released as heat.

A non-linear molecule that contains n atoms has

(3n-6) possible fundamental vibrational modes that can be responsible for the absorption of infrared light. In order for a particular vibration to result in the absorption of infrared energy, that vibration must cause a change in the dipole moment of the molecule. Thus molecule that contain certain symmetry elements will display somewhat simplified spectra. The C=C stretching vibration of ethylene and the symmetrical C-H stretching of the four C-H bonds of methane do not result in an absorption band in the infrared region. The predicted number of peaks will not be Observed also, if the vibrations result in absorption that are so close that they can not be resolved, or if the absorption is of very weak intensity.

Additional (non-fundamental) absorption bands may occur because of the presence of overtones (or harmonics) that occur with greatly reduced intensity, at  $(\frac{1}{2}, \frac{1}{3}, \cdots)$ of the wavelength (twice, three times...the wave number), combination bands (the sum of two or more different wave nos.) and difference bands (the difference of two or more different wave nos.).

An approximate value for the stretching frequency  $(\nu \text{ in cm}^{-1})$  of a bond is related to the masses of two atoms (M<sub>x</sub> and M<sub>y</sub> in grams) the velocity of light (C), and the force constant of the bond (K, in dynes/cm)

-8-

$$v = \frac{1}{2\pi C} \int \frac{K}{M_x M_y / (M_x + M_y)}$$

Single, double, and triple bonds have force constants that are approximately 5, 10 and  $15 \times 10^5$  dynes/cm respectively.

-9-

The magnitude of the molar extinction coefficient in infrared-spectroscopy varies from near zero to around 2000. The value is proportional to the square of the change in the dipole moment of the molecule that the particular vibration causes. Absorption peaks caused by stretching vibrations are usually the most intense peaks in the spectrum.

#### MECHANICS OF MEASUREMENT

Infrared absorption spectra are usually obtained by placing the sample in one beam of double-beam infrared spectrophotometer and measuring the relative intensity of transmitted (and therefore absorbed) light energy versus wavelength (or wave number). A common light source for infrared radiation is the Nernst glower, a molded rod containing a mixture of zirconium oxide, yttrium oxide and erbium oxide that is heated to around 1500° by electrical means. Either optical prisms or gratings are used to obtain approximately monochromatic light; grating spectrophotometers give higher resolution. Glass and quartz absorb strongly throughout most of the infrared regicn, so they can not be used as cell containers or as optical prisms. Metal halides (e.g. sodium chloride) are commonly

used for these purposes. Recording spectrophotometers are available such that a complete spectrum  $(2.5 - 25\mu 4000 - 400 \text{ cm}^{-1})$  may be obtained in a matter of minutes.

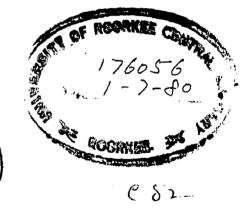

When the spectrum is determined, a caliberation line is usually recorded on the paper. This is necessary because the recorder paper is fitted on a drum of the ordinary spectrophotometer, and it is not possible to place the paper in exactly the same position every time. One of several absorption peaks of polystyrene (Fig. 1 ) is commonly used for this purpose  $3.509 \ \mu$  (2850 cm<sup>-1</sup>),  $6.238 \ \mu$ (1603 cm<sup>-1</sup>) or  $11.035 \ \mu$ (906 cm<sup>-1</sup>).

The spectrum may be determined if the sample is a gas, a solid, a liquid or in solution. The sample should be dry, because water absorbs strongly near 2.7  $\mu$ ( 3710 em<sup>-1</sup>) and near 6.15  $\mu$ ( 1630 cm<sup>-1</sup>). These absorptions may obscure absorptions of substance being analyzed or may, more frequently, lead to erroneous assignments. The most commonly used cells are constructed by using sodium chloride windoes. Cell for the determination of the spectra of gaseous samples are available with path lengths up to several meters.

#### APPLICATION OF INFRARED SPECTROSCOPY

With an adequate number of examples of secure precedence, the chemist will usually know very closely what absorption position to expect from a certain functional

-10-

obtained, there are a number of questions that can be answered fairly rapidly about what it contains ? and what is the substitutional type? . Answers to questions such as these will give many clues for chemical work that can lead to the conclusive identification of the compound. Thus infrared-spectroscopy has been proved of great importance in chemical process industries and air pollution control engineering.

-12-

group in a given environment. In the absence of steric or electrical effects that would affect the vibrational frequency of a given group, that group will absorb infrared energy of very nearly the same wavelength in all molecules. However, the infrared spectrum cannot commonly distinguish a pure sample from an impure sample. In general, however, the spectrum of a pure sample will have fairly sharp and well resolved absorption bands. The spectrum of a crude preparation that contains many different kinds of molecules will display broad and poorly resolved absorption bands because of the many absorptions that are present.

The examination of the infrared spectrum can aid a chemical investigation in many ways. The progress of most organic reactions can be followed readily by examining spectra of aliquots withdraws.

Perhaps the most powerful function of infrared spectroscopy is establishing conclusively the identity of two samples that have identical spectra when determined in the same medium. In order to define a functional group, the spectrum must be examined in detail for other diagnostic absorption bands and used in conjunction with classical chemical reactions and solubility determinations. If the spectrum does not contain an absorption typical of a certain functional group, the molecules does not contain that functional group. When the spectrum of an unknown material is

-11-

#### CHAPTER - III

#### INFRARED ABSORPTION SPECTROPHOTOMETER

We have discussed that when infrared radiation passed through a material, certain wavelengths are absorbed in proportion to the concentrations of the various compon ents in the material. Thus, evaluation of the type and the amount of energy absorbed provides a measure of the concentration of a component in a chemical mixture.

The process-stream analyzers fall into two categories. One type employs the dispersion of light into its component wavelengths, a prism generally being used to disperse the light. These instruments are known as 'dispersive' type.

The second approach does not employ the dispersion of light and is hence called 'non-dispersive'. The non dispersive instruments are generally more suited to liquid systems than are the non-dispersive instruments though the latter can be used efficiently in some cases. The nondispersive instruments, however, make use of an integrated total of the energy absorbed by a material from an infrared beam. This makes possible more signal for driving a recorder than is available when absorption at a single wavelength is used. The non-dispersive analyzer thus generally has a greater sensitivity.

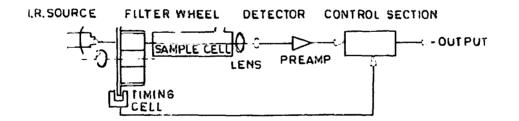

#### NON-DISPERSIVE ANALYZERS

This type of instrument does not operate at any one

specific wavelength but makes use of an integrated total of the energy absorbed by a sample from an infrared beam, to make possible more signal power to drive the recorder. Thus, the non-dispersive type of analyzer has a great increase in sensitivity and stability over the dispersive type of spectrophotometers, which is an important factor in plant-instrumentation. It is more suitable for gases and vapours.

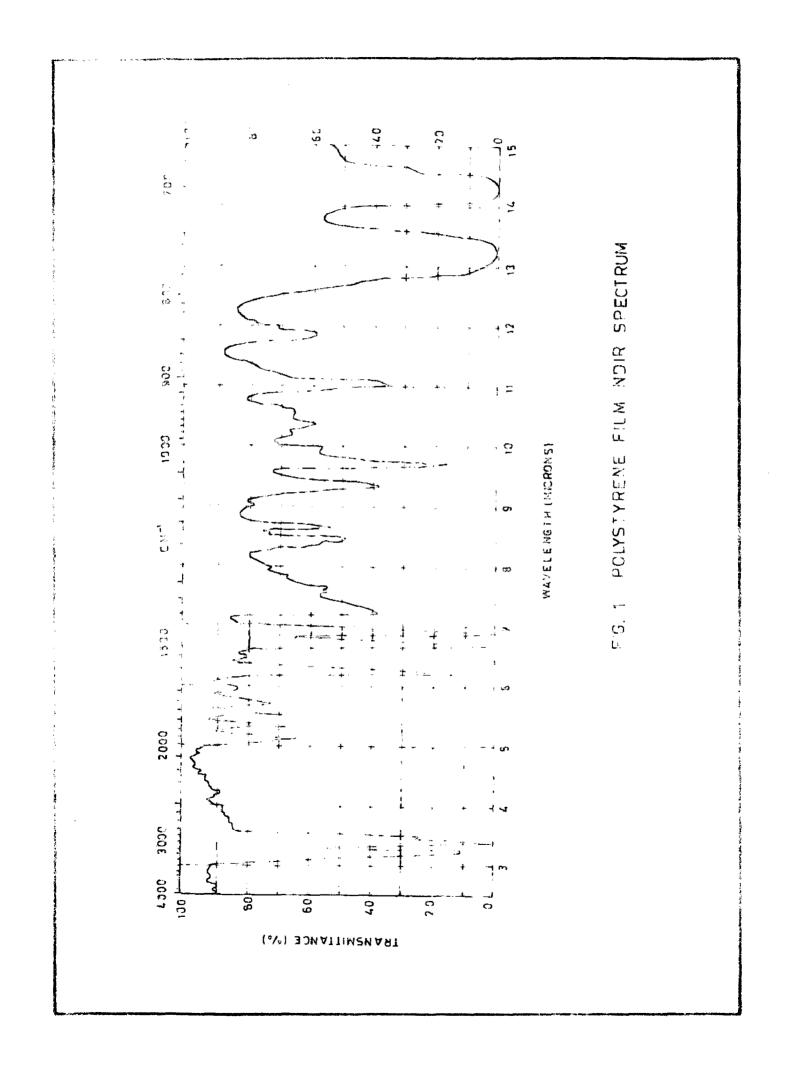

Quantitative isolation of the desired component is obtained by sensitizing the analyzer to changes in the concentration of the desired component and greatly reducing or removing its responsiveness to changes in concentration of all other infrared absorbers present in the sample stream. Although limitations may arise because of interference problems, combinations of stream components which would cause interference can often be predicted and thus can often be compensated for prior to installation. The source is a hot-wire filament or Globar element; the radiation is alternately passed through the sample or reference cell by means of a motor-driven optical shutter (chopper). The detector is a pneumatic cell filled with a pure sample of the gas to be detected - the sample component of interest (COI) - and equipped with a diaphragm electrically connected as a condenser microphone. If the sample cell in fact contains some of the COI, the radiant energy falling on the detector will fluctuate in synchronism

-14-

with the chopper rotation, since some of the energy is absorbed passing through the sample cell but not through the reference cell. This fluctuation is converted by the microphone to an electrical signal. Since the detector (filled with COI) responds only to the radiation absorbed by the COI, it is relatively sensitive only to that compound, ensuring selectivity. The fluctuating signal varies in amplitude with the amount of COI present in the sample tube.

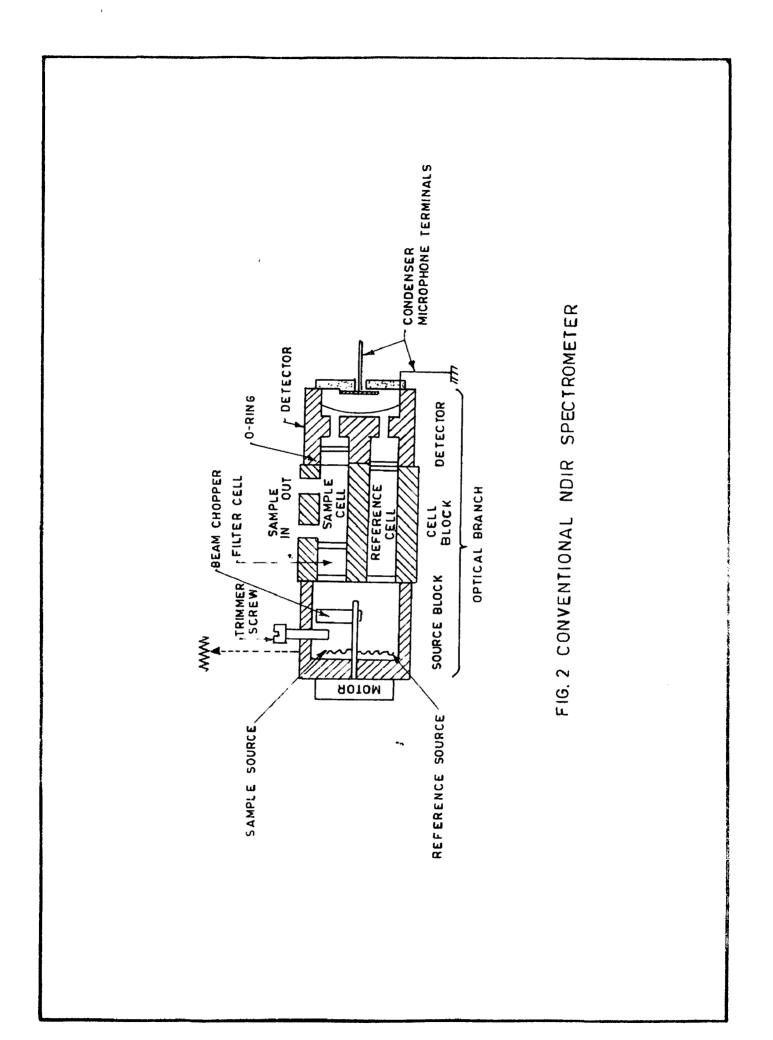

Although such a device is sensitive and selective, being capable of detecting many gases in the range of parts per million, it suffers from a number of shortcomings ; the one that concerns us here is that only a single COI can be detected per instrument. In many industrial and technological situations, it is desired to monitor several components of the gas stream simultaneously and more or less continuously. To overcome these defects and expand the sensitivity of the NDIR instrument a variation of the concept is employed. Instead of preumatic detector, a more sensitive and broad band solid-state detector is used. The rotating chopper and gas filled filter are combined; the filter wheel consists of pairs of these filters alternately interposed in the optical path of the infrared source, sample cell and detector. One is filled with COI and the other with nitrogen. When the COI filter is in

-15-

FIG, 3 FILTER WHEEL NDIR

1

.

optical path the amount of COI present in the sample cell affects the detector output very little, because the radiant energy characteristic of that compound has already been largely absorbed by the concentrated COI in the filter cell, hence this filter is called the 'reference cell'. When its place is taken by a nitrogen cell, called the sensitive cell the amount of energy absorbed is proportional to the COI in the sample cell. Hence the detector output is an a.c. signal proportional to the COI in the sample cell and at the frequency of the filter wheel rotative or chopper. Since the selectivity of this instrument is obtained by means of the reference cell filter (plus optical filters to reduce interference) but without the highly specific detector, in Fig.2.3 the device can be multiplexed by employing several pairs of gas cells in the filter-wheel. This type of detector has been thought as the modification to the conventional NDIR Spectrometer.

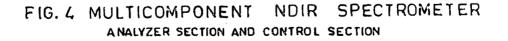

#### Description of the Perkin-Elmer Model-180

The Perkin-Elmer Model-180 infrared spectrophotometer is basically a multigrating, dual beam, ratiorecording instrument. The key abscissa element, the grating carousel is driven by stepping motor pulses to a large frequency cam. As the frequency cam rotates an electromechanical encoder mounted on the cam-shift sends

-16-

signals (via-contact-closures) to the wave-number readout-display and chart drive motor. At appropriate intervals, microswitches initiate grating changes at 2000, 1000, 500 and 250 cm<sup>-1</sup>, and a filter cam triggers the positioning of filters in the recombined beam. A front panel switch enables the operator to step the monochrometer in 0.1 cm<sup>-1</sup> or 0.01 cm<sup>-1</sup> intervals. The fastest scanning speed of the 180 is  $32 \text{ cm}^{-1}$ /sec from 4000 to 2000 cm<sup>-1</sup>, 16 cm<sup>-1</sup>/sec from 2000 to 1000 etc. The thermopile detector has a fairly slow response time, however, and the fastest practical scanning speed for digital data acquisition is 5 digital data per second.

The biggest problem with the model 180 is the electromechanical encoder on the frequency cam. It consists of a spring wire 'Feelers' that rotates on a series of gold-plated annular rings on a small (4 in.) etched circuit board. These wire contacts may have a tendency to bounce when they hit a dust particle, scratch, or other impediment. Thus erroneous abscissa and ordinate data may spew randomly from the standard interface, requiring the user to carefully edit the incoming data with a software routine.

Fig. 5 illustrates the optical lay-out of P.E. 180. Some of its common features are as follows. There is an extra focal point in the source compartment,

-17-

which can be used if a separate source is desired. The sample and reference beams come to a focus (nominally about 11 mm wide) is the sample compartments, which means that many accessories do not work optimally in the 180 unless they are designed to take advantage of this focal point. The second chopper in the monochromator housing, is used to discriminate against self-emission. Shown in Fig. 5 is a polarizer mount between M-15 and the entrance slits, which holds a circular wire grid polarizer, a necessity for serious infrared work. The grating carousel has space for seven gratings. Only four of which are required for the normal range of 4000-180 cm<sup>-1</sup>. The other three plus the mirror M-21 and the far-IR detector and source, shown in dashed lines, are used to extend the range of the 180 into the farinfrared, to 32 cm<sup>-1</sup>.

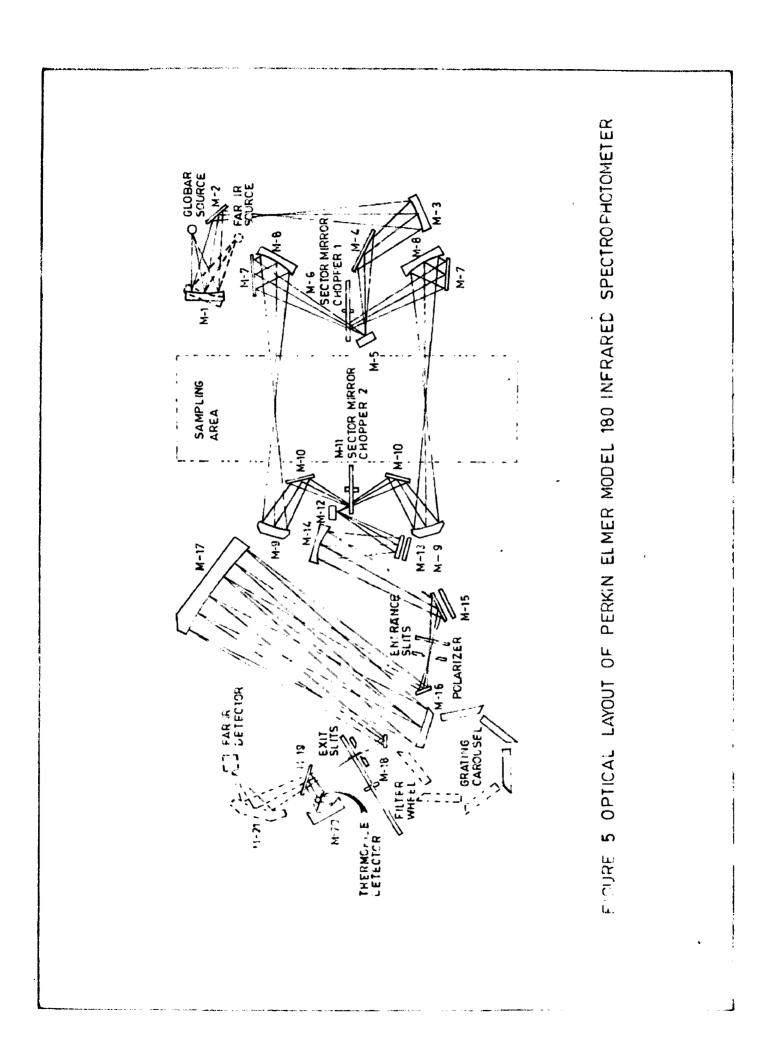

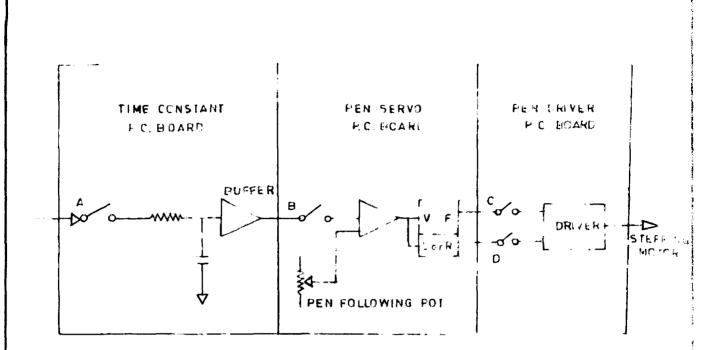

Fig: illustrates the model 180 electrical, mechanical and optical layout to its stand alone configuration. A DPDT switch installed in the recorder circuitry enables the operator to disable the front panel recorder controls : TIME CONSTANT LINA/LINT, 100 % T ADJ, 0 % T ADJ, RATIO MODE (CI/Io), (Io/I) etc.), ORDINATE EXPANSION, ABSCISSA EXPANSION, VARIABLE EXPANSION and SCALE POSITION. In the 'COMPUTER' position, this DPDT turns over the control of the 180's recorder to NOVA and the associated software. In the 'SPECTROMETER' position, the operation can still acquire digital data with the NOVA, while allowing the spectrophotometer to produce an X-Y plot in its normal stand alone mode. Thus offering the operator a chance to monitor such things as the noise level, quality of the dry-air purge, level of transmittance etc., while storing the spectrum in digital form.

Nova is the particular name given to the interface adaptor, by manufacturers, which is provided with the model P.E. 180 spectrometer.

ELECTRONICS OF MODEL 180 WITH STANDARD BLOCK DIAGRAM OF ENTERFACE ADDED. FIG. 6

\$

#### CHAPTER - IV

#### A VIEW OF MICROPROCESSORS

Microprocessors are the most versatile and powerful tools electronics engineers have ever had. Right from the beginning, these large-scale-integrated circuit promised to spread into many diverse and complicated application, being both programmable and in terms of what they can do for the money-very low cost. They are rapidly fulfilling their promise. So many successful applications of microprocessors have proved now that they can be used as strongest tools in digital control system design. Microprocessor technology is developing towards the point where it will be economically feasible to design 'intelligence' into the environment at any desirable point. Microprocessors represent scale changes of several orders of magnitude in size, cost and power consumption.

A microprocessor is an LSI chip or collection of chips which performs the arithmatic and logic and the control logic that instructs and sequences the ALU. The same microprocessor can be a part of a host machine or instrument and become its controller, or it can be a unit of a general purpose microcomputer, The essential features of a processor can be specified by five operations :

- 1. READ the input symbol x

- 2. COMPARE x with z, the internal state of the processors.

3. WRITE the appropriate output symbol y.

4. CHANGE the internal state z to the new state z<sup>\*</sup>

5. REPEAT the above sequence with a new input symbol x.

In approaching the design of microprocessor systems, the first requirement is to get acquainted with the specialized jargon. Some of the basic terms are defined below,

CENTRAL PROCESSING UNIT : a group of registers and logic that form the arithmatic/logic unit plus another group of registers with associated decoding logic that form the control unit. Most metal-oxide-semiconductor (MOS) devices are single-chip CPUs. In that registers hold as many bits as the word length of the unit (Intel 8080 and Motorola 6800, for example, are 8 bit devices and thus the basic registeres are eight bit wide). With bit-slice devices, however, central processing units of any bit width can be assembleed essentially by connecting the bit-slice parts in parallel. Externally, a bit-slice device will appear to be a coherent single CPU capable of handling words of the desired bit length.

REGISTER : logic elements (gates, flipflops, shift

-21-

registeres), that, taken together, store 4,8, or 16bit numbers. They are essentially for temporary storage, in that the contents usually change from one instruction cycle to the next. In fact, much of the microprocessor's operation can be learned by studing the registers, which take part in nearly all operations.

ACCUMULATOR : a register that adds an incoming binary number to its own contents and then substitutes the results for contents.

PROGRAM COUNTER : a register whose contents correspond to the memory address of the next instruction to be carried out. The count usually increases by one as each instruction is carried out, since instructions generally are stored in sequential locations.

INSTRUCTION REGISTER : storage for the binary code for the operation to be performed. Usually this instruction represents the contents of the address just designated by the program counter. However, the contents of the instruction register or the program counter may be changed by the computations. This, of course, represents one of the key ideas of a stored-program computer instructions, as well as data, can be operated upon and subsequent operations will be determined by the results.

INDEX REGISTER : some memories are organized by index. number (the contents of the index register). The address

-22-

of the next instruction may be found by summing the contents of the program counter and the index register. Increasing the index register by one will cause the processor to go to a new section of memory.

STACK POINTER : a register which comes into use when the microprocessor must service an interrupt - a high priority call from an external device for the central processing unit to suspend temporarily its current operations and divert its attention to the interrupting task. A CPU must store the contents of its registers before it can move on to the interrupt operation. It does this in a stack, so named because information is added to its top, with the information already these being pushed further down. The stack, thus is a last-in-first-out type of memory. The stack pointer register contains the address of the next unused location in the stack.

FLAG : usually a flip-flop storing one bit that indicates some aspect of the status of the central processing unit. For example, a carry flag is set to one when an arithmatic operation produces a carry. A zero flag is set when the result is zero. These flags aid in interpreting the results of certain calculations. Others are sometimes provided to permit access by interupt request lines for example, if a CPU is engaged in the highest priority of calculation, it may set all status flags to zero which, loosely translated, means 'don't bother me now'.

-23-

If only some of these flags are set, then only certain interupt lines will be able to get through according to their priority.

DIRECT MEMORY ACCESS : a technique that permits a pheripheral device to enter or extract blocks of data from the microcomputer memory without involving the central processing unit. In some cases, a CPU can perform other functions while the transfer occurs.

ACCESS TIME : time between the instant that an address is sent to a memory and the instant that data returns. Since the access time to different locations (addresses) of the memory may be different, the access time specified in a memory device is the path that takes the longest time.

ADDRESS : a number used by the CPU to specify a location in memory.

BAUD : a communications measure of serial data transmission rate ; loosely bits per second but includes character framing START and STOP bits.

BENCHMARK PROGRAM : a sample program used to evaluate and compare computers.

BOOTSTRAP : technique or device for loading first instructions (usually only a few words) of a routine into memory; then using these instructions to bring in the rest of the routine.

The bootstrap loader is usually entered manually

- 24-

or by pressing s special console key.

BRANCH INSTRUCTION : a decision-making instruction that, on appropriate condition, forces a new address into the program counter. The conditions may be zero-result, overflow on add, an external flag raised etc. One of two alternate program segments in the memory are chosen, depending on the results obtained.

BUS : a group of wires that allow memory, CPU and I/O devices to exchange words.

BREAK POINT : a location specified by the user at which program execution (real or simulated) is to terminate. Used to aid in locating program errors.

DEBUG : to eliminate programming mistakes, including omissions, from a program.

DEBUG PROGRAM : help the programmer to find errors in his programs while they are running on the computer, and allow him to replace or patch instructions into (or out of) his program.

INSTRUCTION : a set of bits that defines a computer operation, and is a basic command understood by the CPU. It may move data, do arithmatic and logic functions, control I/O devices or make decisions as to which instruction to execute next.

REQUEST-INTERRUPT : a signal the computer that temporarily suspends the normal sequence of a routine and transfers control to a special routine. Operation can be resumed from this point later. Ability to handle interrupts is very useful in communication applications where it allows the microprocessor to service many channels.

MEMORY : the part that holds data and instructions. Each instruction or datum is assigned a unique address that is used by the CPU when fetching or storing the information.

MEMORY ADDRESS REGISTER : the CPU register that holds the address of the memory location being accessed. ROM (Read Only Memory) : Read-Only Memory (Fixed Memory) is any type of memory that can not be readily rewritten. ROM requires a masking operation during production to permanently record or data patterns in it. The information is stored on a permanent basis and used repetitively. Such storage is useful for programs or tables of data that remain fixed and is usually randomly accessible.

RAM (Random Access Memory) : any type of memory that has both read and write capability. It is randomly accessible in the sense that the time required to read from or to write into the memory, is independent of the location of the memory where data was most recently read from or written into. In contrast, in a Serial Access Memory, this time is variable.

-26-

SERIAL ACCESS MEMORY : any type of memory in which the time required to read from or write into the memory is dependent on the location in the memory. This type of memory has to wait while undesired memory locations are accessed. Examples are paper tape, disc, magnetic tape etc. In a Randam Access Memory, access time is constant.

SCRATCH-PAD MEMORY : RAM or register that are used to store temporary intermediate results (data), or memory addressed (pointers).

PAGE: a natural grouping of memory locations by higher order address bits. In an 8-bit microprocessor  $2^8 = 256$  consecutive bytes often may constitute a page. Then words on the same page only differ in the lowerorder 8 bit address bits.

PLA (Programmable Logic Array) : a PLA is an array of logic elements that can be programmed to perform a specific logic function. In this sense, the array of logic elements can be as simple as a gate or as complex as a ROM. The array can be programmed (normally mask programmable) so that a given input combination produces a known output function.

PROM (Programmable Read-Only Memory) : an integrated circuit memory array that is manufactured with a pattern of either all logical zeros or ones and has a specific pattern writtn into it by the user by a

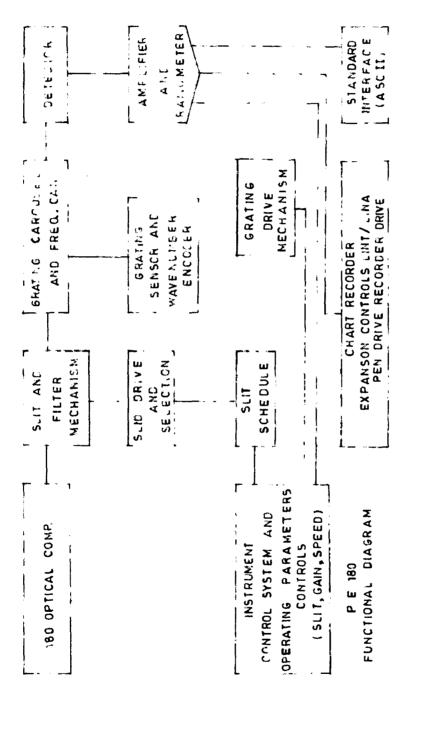

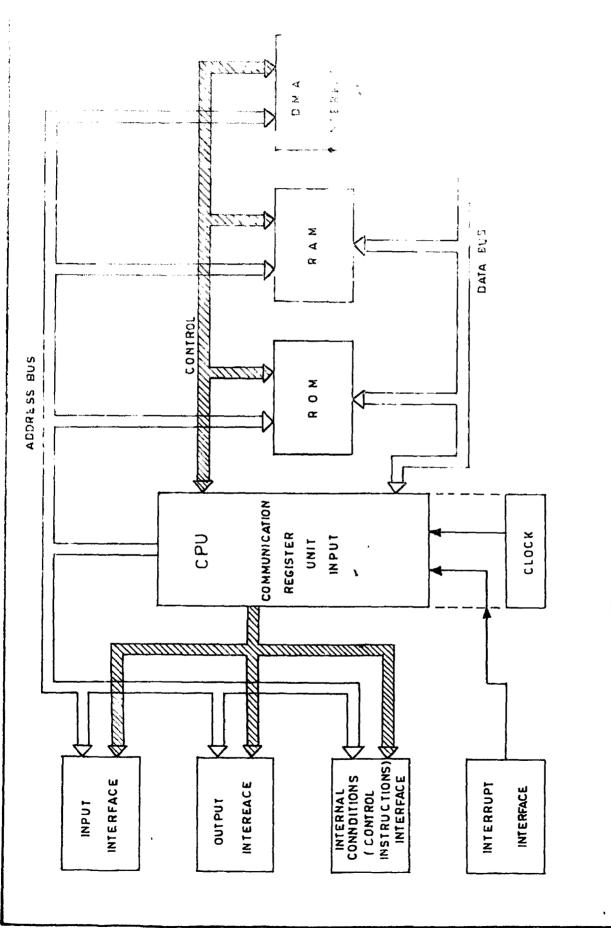

**TE MPORARY** ME MORY FIG. 7 MICROPROCESSOR CONTROLLER ORGANIZATION MICROPROCE SSOR INPUT / JUT PUT DEVICES 11NING PROGRAM MEMORY

special hardware programmer. Some PROMs called EAROMs, Electrically Alterable Read-Only Memory, can be erased and reprogrammed.

HARDWARE : a relatively permanent physical embodiment of an algorithmic process.

SOFTWARE : a relatively impermanent, informational embodiment of an algorithm.

The first microprocessor, the Intel 4004, was introduced in 1971 by Intel Corporation. This device, developed primarily for calculator-oriented applications, is a monolithic integrated circuit (IC) employing large-scale-integration (LSI) in metal-oxide-semiconductor (MOS) technology. The 4004 was soon followed by a variety of microprocessors, with most of the major semiconductor manufacturers producing one or more types. Most microprocessors use LSI technology employing either P-channel MOS, n-channel MOS, silicon-on-sapphire MOS, complementary MOS, or bipolar processes.

Microprocessors are having an impact on the design of virtually all digital systems. They are finding application in many systems which formerly used random logic. In complex systems, a microcomputer is often cheaper and convenient to use than random logic. One can expect, as time and technology progress, that the processor cost will continue to diminish in a manner reminiscent of that of operational amplifier IC.

-28-

### CHAPTER - V

### DIGITAL DATA PROCESSING

It is quite obvious to learn that the most precise spectrometers are those that incorporate a double-beam feature; that is, one optical path from the source to the detector passes through the sample, and the other travels directly or via a neutral or nonabsorbing filter. The absorption of the sample is measured as a ratio of the direct and indirect paths. Thus any variations in strength of the source or of the detector sensitivity, together with the effects of film or dirt obscuring the main optical path, are canceled out by the rationing process. In an NDIR spectrometer, a similar advantage is gained from the alternate presentation of the two filter cells used for each COI, hence it is desired to take the ratio of the signals obtained from each pair.

The filter wheel NDIR spectrometer has been called a 'double beam in time'. If the detector delivers and electrical signal voltage proportional to the transmission or absorption of radiation along each optical path, it desired to obtain an instrument output E<sub>0</sub> equal to

$$E_{o} = A(e_{b} - \frac{e_{r}}{e_{s}}) \qquad (1)$$

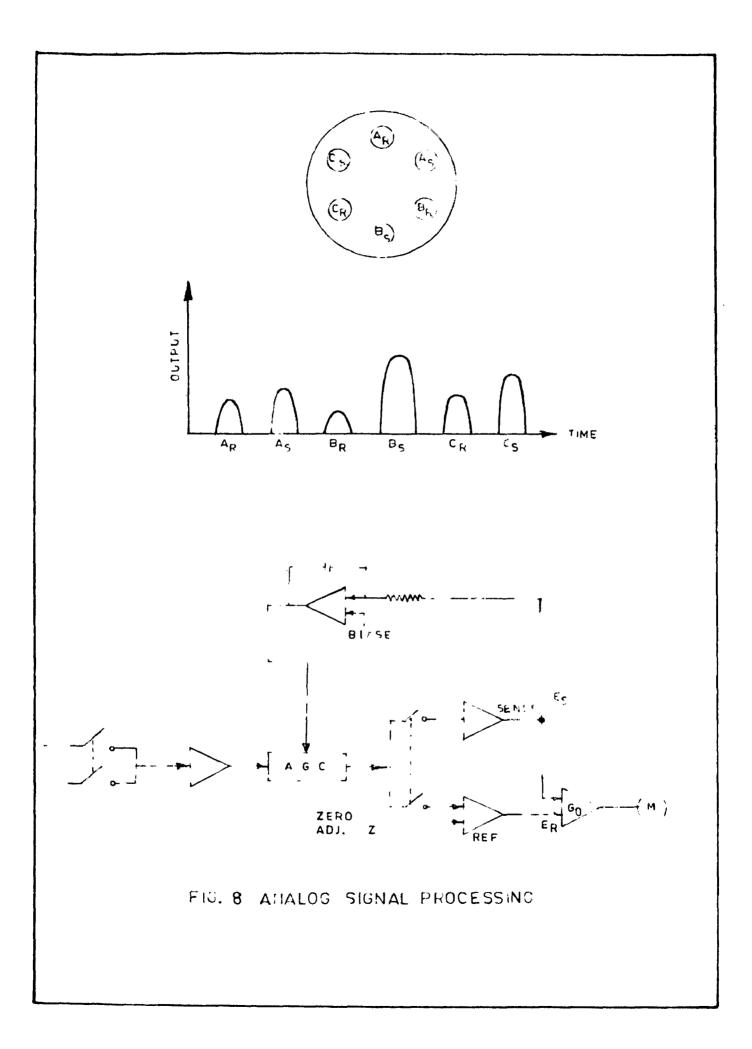

where  $e_r$  and  $e_s$  are the reference and sensitive path voltages and  $e_b$  is a bias voltage added to the computed signal to give a zero reading when the concentration of COI is zero in the sample cell. The division  $e_r/e_s$  in one version of the instrument is accomplished with analog circuitry using a voltage controlled amplifier or automatic-gain-control (AGC), as shown in Fig.

The ganged switches represent gates synchronized by the chopper filter wheel, alternatively emergizing the sense and reference channels. When the sense (COI filter) channel is active, the AGC circuit acts through the feedback integrating amplifier to make the sense output  $E_s$  equal to the fixed bias voltage. Thus the gain of the AGC circuit is proportional to  $1/e_s$ . When the switches alternately gate through the reference signal, the AGC gain remains at  $1/e_s$ , owing to a long time constant, and

$$E_{R} = e_{r} \left( \frac{E_{s}}{e_{s}} + Z \right)$$

(2)

where Z is the zero-adjustment for the reference channel.

The complete expression for the output is obtained from the difference between  $E_k$  and  $E_s$ , since the differential amplifier  $G_o$  also has a long time constant compared with the pulse rates. Consequently

$$E_{o} = G_{o} \left[ E_{s} - E_{s} \left( \frac{e_{r}}{e_{s}} \right) - Z \right]$$

$$= A \left[ e_{b} - \frac{e_{r}}{e_{s}} \right]$$

(3)

which is of the same form as (1). A being equal to  $G_0 E_s$ and  $e_h = (1 - \frac{Z}{2})$  (4)

$$e_{b} = (1 - \frac{Z}{E_{s}})$$

(4)

## Digital Data Processing

Although the analog circuitry developed for this device performs its task very well, there are several important advantages which may accrue from all-digital circuitry, specifically a microprocessor. First, the analog circuitry described, although time shared between sense and reference channels, must be duplicated for every component; that is, a three-component analyzer requires three AGCs and associated amplifiers and gates.

Second, a great deal of gating is required so that a certain portion of the circuitry is digital in any event.

Third, time constants are long in order to 'hold' voltages for subtraction and division - with time constants up to 12 sec a digital memory may save space and component dollers.

Finally, an analyzer of this type is necessarily customized to the extent of being adjustable for different COIs, requiring changes in a few components.

With a microprocessor, programs substitute for custom hardware, and the large dynamic range possible often eliminates the need entirely. Also the microprocessor allows signal processing techniques (such as filtering) to be added or altered with no new hardware, and digital processing generally adds to long term stability, particularly with respect to temperature changes.

For these reasons let us consider what may be involved in applying a microprocessor.to an instrument of this type. To make the problem more realistic, we assume a three-component instrument in which the filter wheel is driven by a pulse stepping motor rather than continuously. The microprocessor has the additional task of synchronizing the filter positions and the signal processing task for the three COIs (or more COIs). As still another complication, let the analog signal from the detector preamplifier be integrated for a precise fixed period before digital conversion and further processing in order to increase the signal strength.

#### Computer Spectrometer System

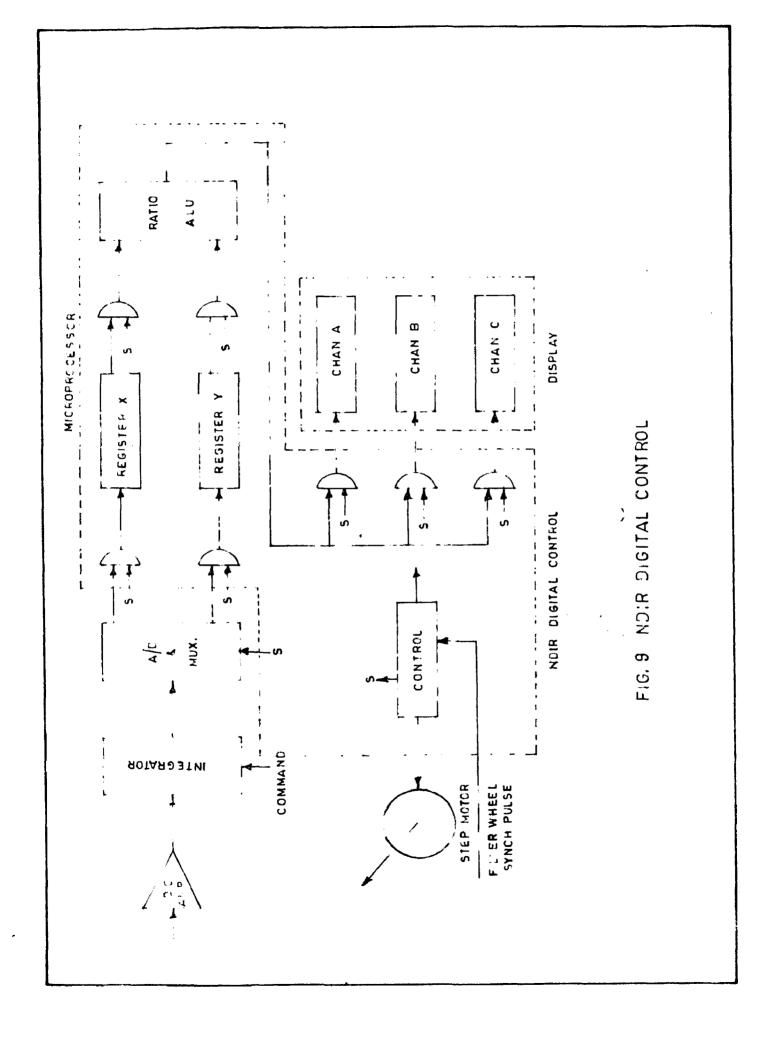

Fig. 9 shows a block diagram of the complete computer-spectrometer system. The basic block diagram for computer assisted system was developed at University of Miami.

We will use this basic block diagram as the base of the microprocessor based digital control system for NDIR spectrophotometer.

-32-

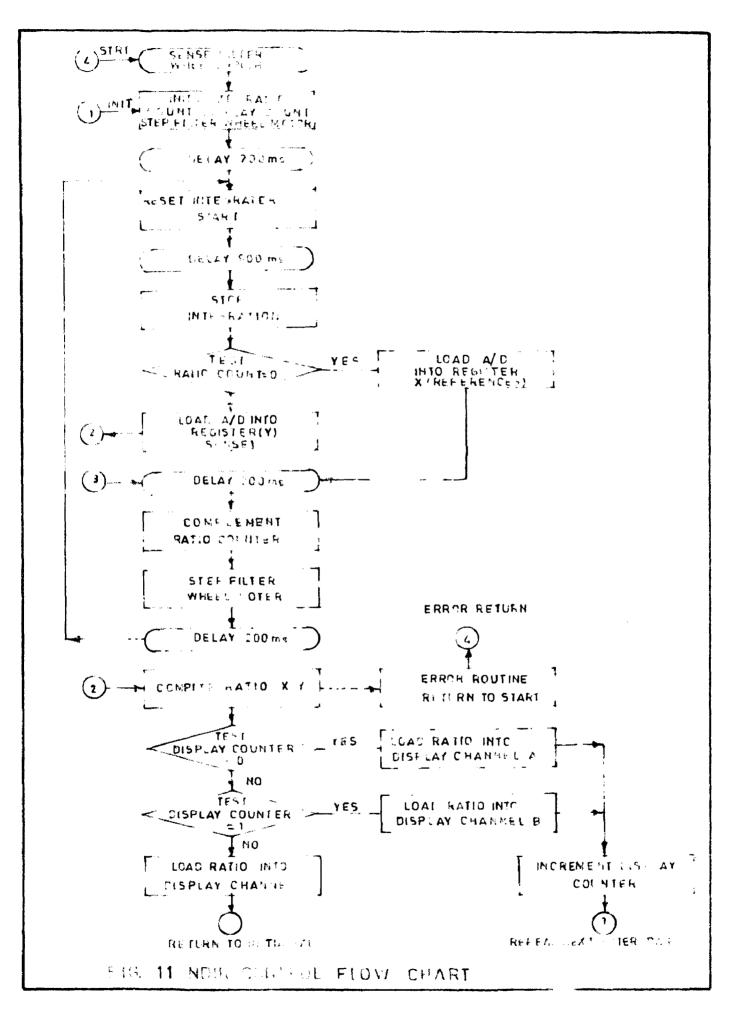

Having received the external signal, the program initiates the following actions. Two counters (registers) termed the ratio counter and the display counter, used for switching logic are set to zero, and a signal is sent to the stepping motor to rotate the first filter, which is the reference filter of the first COI.

The program then delays for 200 msec while the first filter settles into place. At the end of this time, a signal is sent to the analog integrator to reset and begin integrating the pre-amplifier output. The integration continues until the program has measured a 600 msec delay, at which time the integrator stops. The A/D convertor then holds the current output of the integrator in digital form.

The ratio bit counter is then tested. If it holds a '0', the A/D contents will be loaded into a register we shall call X. After a further 200 msec delay, the ratio counter bit is complemented - if it was '1' it becomes '0' and if '0' it becomes '1'. The filter wheel is stepped (to the sense filter of the first COI), another 200 msec delay occurs, and the integrator again zeroed and restarted. At the end of the integration, the ratio-counter shows '1', so the A/D controls are loaded into register Y instead. The program Men computes the ratio X/Y which is the  $e_r/e_s$  required for (3).

-33-

.

To anticipate, the division routine normally used by the microprocessor requires that the divident be smaller than the divisor. In the physical configuration, the reference signal is always smaller than the sense signal. Since the formal results from the absorption of pure COI. Hence, if this inequality condition does not hold, there is an error, such as a failure of the filter wheel to step. If this condition is sensed, an error routine is to be entered which continues to step the wheel and test for the synchronizing position.

If there is no error, the value of the ratio is sent to the correct display channel, utilizing the display counter. If the display counter holds '0' the results of the ratio calculation is sent to channel A. The display counter is then incremented. If the counter holds a '1', the ratio is sent to channel B and the counter incremented again. If the counter holds any other value (more than '1'), the ratio is loaded into channel C and the program is returned to the initializing step.

## DIGITAL CONTROL

For a moment, neglecting the problem of linearization, zero setting, span adjustment (system gain) and display, and consider the end product of the signal processing task is the ratio of the reference and sense

-34-

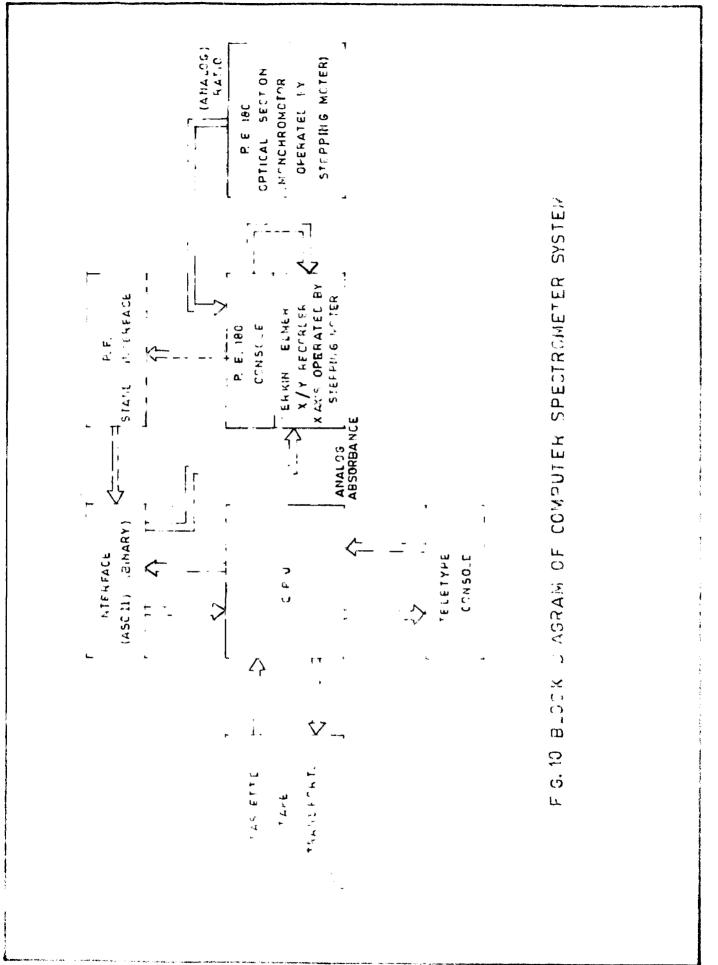

channel voltages and variables. A block diagram of the control processing task (given in Fig. 10) shows the micro-processor tasks under consideration.

The time available for control and signal processing is more than adequate, considering typical micro-processors computing speeds. Table 1 indicates a typical time sequence for these operations, assuming each COI measurement is updated every 6 sec. The corresponding control flow chart is given in Fig. 11

| Milliseconds   | Action Required                                                    |

|----------------|--------------------------------------------------------------------|

| 0              | Reset Sequences (from filter wheel synch.<br>pulse).               |

| 0              | Step filter wheel (motor)                                          |

| 200            | Reset integrator and turn on                                       |

| 800            | Integrator off. Store A/D output in register X                     |

| 1000           | Step filter wheel                                                  |

| 1 200          | Reset integrator and turn on                                       |

| 1800           | Integrator off. Store A/D output in register Y                     |

| 1900           | Compute register X/register Y ratio and gate result into channel A |

| 2000           | Step filter wheel                                                  |

| 2200           | Reset integrator and turn on                                       |

| 2800           | Integrator. Store A/D output in register X                         |

| 3000           | Step filter wheel                                                  |

| 3200           | Reset integrator and turn on                                       |

| 3800           | Integrator off. Store A/D output in register Y                     |

| 3900           | Compute register X/register Y ratio and gate result into channel B |

| 4000           | Step filter wheel                                                  |

| 4200           | Reset integrator and turn on                                       |

| 4800           | Integrator off. Store A/D output in register X                     |

| 5000           | Step filter wheel                                                  |

| 5200           | Reset integrator and turn on                                       |

| 5800           | Integrator off. Store A/D output in register Y                     |

| 5900           | Compute register X/register Y ratio and gate result into channel C |

| 6000-0         | Reset sequence - step filter wheel.                                |

| <u>Table 1</u> | Signal Processor Sequence Table                                    |

#### CHAPTER - VI

### INFRARED DATA HANDLING AND REDUCTION

The main program, in all, carries out seven principal functions, selected by the operator in response to the query FUNCTION Using 4 to represent a carriage return, the seven allowed responses are described below-.P 4 enables operator to reset the zero and 100 % T counters from their default values of 100 and 10,000 or from previously set values.

C \* Reads floating point absorbance data from a file on a cassette tape, after echoing the ASCII title line making up the first record of the file.

W \* Write a data file and an operator written title line onto a cassette tape.

S: Input to ASCII data point from the spectrophotometer to be stored in memory as a string of floating point ordinate values. The operator can choose to average any number of spectra under this mode of operation, combining them all into one spectrum.

T \* Type the ordinate values from the spectrum stored in core onto the teletype.

R \* Ratio two spectra stored as cassette tape files by subtracting absorbances (scale factor for subtrahend included)

M • A response which indicate the operator's wish to

either plot or smooth up to 4096 points stored in memory. An M 4 response is followed thy he query 'SMOOTH OR PLOT'? requestion an operator's response of S<sup>4</sup> or P<sub>4</sub>. S<sup>4</sup> results in the application of a 21 point quartic smooth to the stored spectrum. P<sup>4</sup> causes the stored spectrum to be plotted on the spectrometer's X-Y recorder.

-37-

### Detailed Description of Main Program Functions.

1. P+ Adjusting Live Zero and 100 % T Counters.

The model 180 uses an electronic counter, which counts from zero to as high as 12,000, to represent the ratio of the saample beam intensity to the reference beam intensity  $(I/I_0)$ . When the sample beam shutter is closed, a minimum count, usually between 50 and 200 counts, is produced. The minimum counts provides for a Live zero. , so that very low transmittance (I = 0% T) can be recorded with about 1 % accuracy. The zero count can be manually adjusted via a trimpot on the analog filter p.c. board. The full count trimpot on the same p.c. board can be used to adjust 100 % T count close to 10,000, provided that the sample and reference beams have been properly phased. As a rule, neither the live zero count nor the full scale count match their nominal values of 100 and 10,000, respectively. For this reason, it is necessary to have this routine in order to adjust software counters to represent the actual

signal output of the spectrometer. This is the only way in which one can be certain of matching results over long period of time, over which time the source may be changed, p.c. boards may be replaced or adjusted, external temperature may change, and so on.

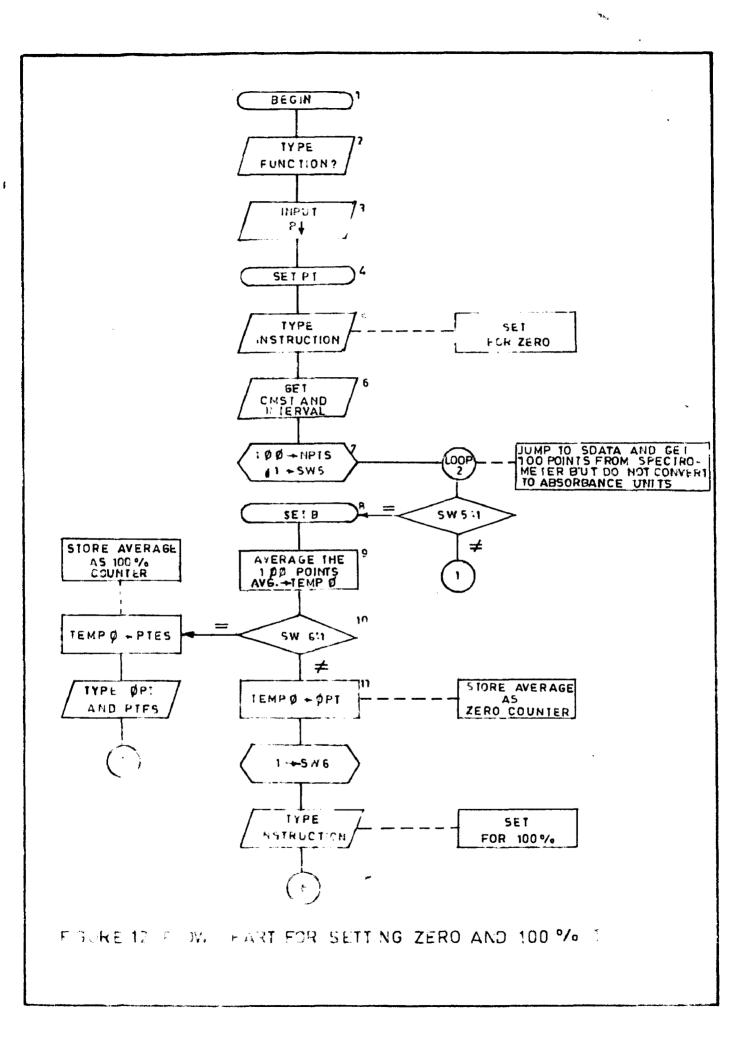

Fig.12 illustrates the straightforward logic flow employed to average 100 points with the sample shutter closed, then 100 points with both beams empty, to get representative values for the zero and 100 % T counters. This routine sets a switch (SW5) which enables it to use the spectrometer data acquisition routine (SDATA), but without modifying the  $I/I_0$  counts in any way.

2. S: Spectrometer Data Acquisition

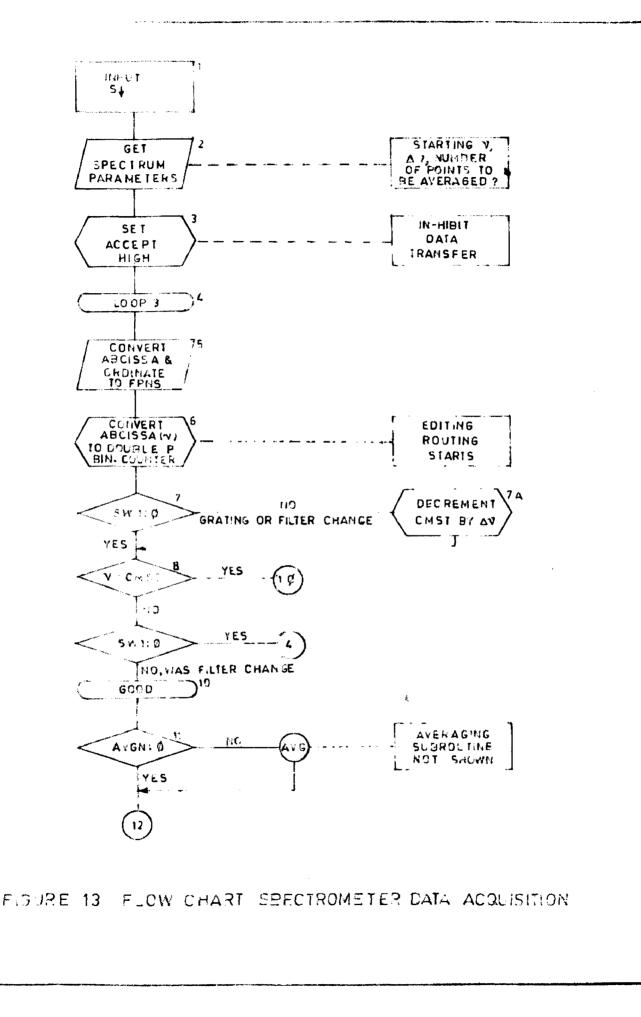

A response of S + to the query 'FUNCTION'? generates requests for the starting wave number (CMST), the data interval (INCRE), the number of points to be acquired (NPTS), whether or not averaging is desired, and if so, the number of spectra to be averaged (AVGN). After computer types 'BEGIN', the operator may start the spectrophotometer scan after all of the instrument setting have been made.

According to Savitzky and Hannah [ ], a model 180 will not accurately respond faster than about five data intervals per second. In addition, our smoothing routine requires about a 21-point half width (FWHM) to

avoid distorting the top of a peak. The two restrictions serve to guide to operator in setting the adjustable parameters of the spectrometer. For the narrow absorption bands of, say, a no.2 fuel oil ,data interval of 0.2 or 0.5 cm<sup>-1</sup> may be necessary, alongwith a midest scanning speed ( 1 to 2.5 cm<sup>-1</sup>/sec), and a narrow slit width. For broader absorption bands, say those of large proteins, a data interval of 1 or 2 cm<sup>-1</sup> is sufficient, larger slit widths can be employed, as well as higher scanning speeds. Naturally the S/N is improved at larger slit openings. thus reducing the need to average spectra to those instances. There does not appear to be any point in scanning at slower speeds since no improvement in S/N should result. The S/N is determined by the absolute attenuation of the sample and reference beams, and the gain and slit settings of the spectrometer. When S/N is low, enhancement can be obtained through spectrum averaging and/or smoothing. The operator of the computer-spectrometer should be familiar enough with the available tradeoffs, both in the spectrometer and in the data handling, to be able to take full advantage of the capabilities of the system.

The flow chart for the acquisition of abscissa and ordinate data from the spectrometer is given. Using the floating point interpreter (F PI), the ASCII character strings are converted to floating point numbers. The

-39-

r

٩

FIGURE 13 FLOW CHART SPECTRMETER DATA ACQUISITION

+

FPI requires that a get character routine be pointed to by an address in page zero location GETC. The get character subrouting used for the data acquisition from the 180 can be as follows (assembly language has been used).

| GCHAR | : | DOB   | ø, ø5       | : Set accept low                              |

|-------|---|-------|-------------|-----------------------------------------------|

|       |   | SKPON | Ø5          | : Skip next instruction when<br>'done' is set |

|       |   | JMP   | 1           | · · · · ·                                     |

|       |   | DIAP  | ø, ø5       | : Take character, set accept high             |

|       |   | LDA   | 2,MSK       |                                               |

|       |   | AND   | 2 <b>,Ø</b> | : Right adjust                                |

|       |   | NIOC  | Ø5          | : Clear 'done'                                |

|       |   | JMP   | ø,3         | : Return                                      |

| MSK   |   | 177   |             |                                               |

The above subroutine will clarify the actions of the commands 'DOB' and 'DIAP' (the latter is a combination of 'DIA' followed by the special I/O pulses), if we have in mind some of the formerly written lines that the software sequence follows

°,

- 1. RESET ACCEPT FF LOW

- 2. WAIT UNTIL READY IS HIGH

- 3. TAKE DATA AND SET ACCEPT FF HIGH

The appearance of  $\emptyset 5$  in the I/O commands ( since here, we have taken five data interval per second) merely indicates the device code for the particular interface

received,  $\nu$ , using double precision binary subtraction rather than floating point arithmatic to eliminate round off errors. A precise agreement causes the exit at step 10 to 600D. Any difference between CMST and V goes into TEMØ, where its absolute value is tested against EPSI INCRE/IØ) is reached to see if it is greater than ( = CMST, and if so, the data are rejected and a new set of data requested. If not, it is tested to see if v is only one data internal ( +10%) less than CMST. If so, a grating change has just been passed and the data are accepted, setting SWI in addition. The 180 does not transmit regular data at a grating change, but skips one data interval, thus SWI is set in order to store the subsequent datum twice. A precaution to the user is to avoid, setting up a scan so that a grating change is the last point in the scan. If this is done, the spectrometer must be allowed to pass through the grating change past the next data interval in order to acquire the final point. The editing routine is an absolute necessity to ensure proper registry when plotting, ratioing or averaging spectras.

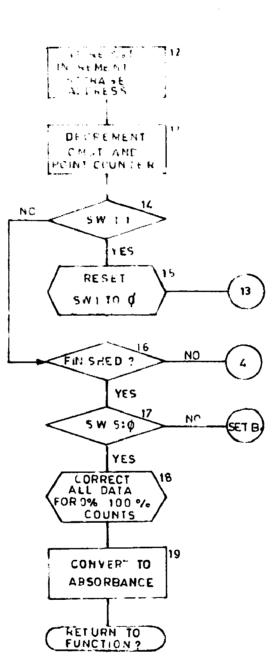

The remainder of the flow chart is straightforward. Once the abscissa is determined to be good, the routine decrements CMST by an data interval and tests AVGN to see if averaging was requested. If averaging is to take place the subroutine AVG (not shown in flow chart)

-42-

takes the floating point ordinate, devides it by AVGN (the number of spectra being averaged), and adds the results to the previous by stored value for the same  $\vee$ . As the data are entered, they are stored in T counts (between zero and 12,000 counts) in floating point notation. This enables the control to take data at very high speeds, much faster, in fact, than the commercial model 180 can scan. At the end of the spectrum (or spectra, if averaging) the entire spectrum is corrected for the live zero, than converted to absolute absorbances (ranging from about +0.05 to about 2 absorbance units).

# 3. M + Plotting or Smoothing Spectrum in Memory

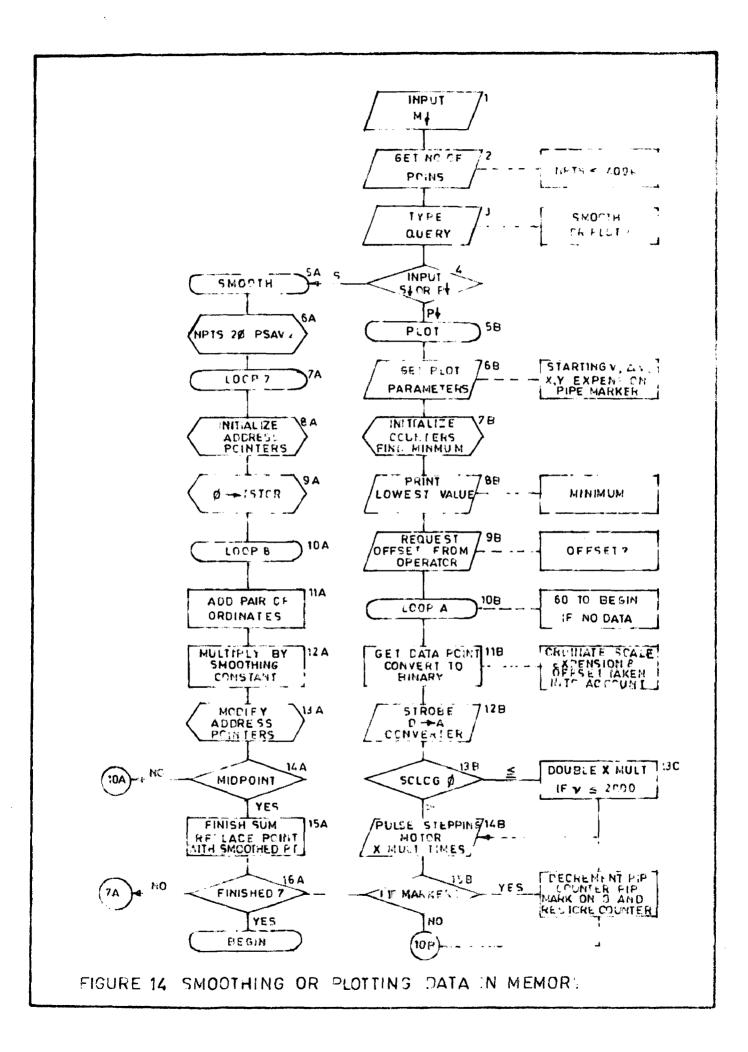

The digital control system replies to a response of M<sup>4</sup> by requesting the number of points (NPTS), and then asking 'SMOOTH OR PLOT'? Flow change (given in Fig. 14 ) illustrates the logic flow followed in response to an S<sup>4</sup> or a P<sup>4</sup> response. The smoothing routine is based on 21-point smooth (as given in reference - J. Steiner, Y.J. Termonia and J. Deltour, Comments on smoothing and differentiation of data by simplified Least square procedure, Anal. Chem. 44:1906 (1972) ). This requires that certain precautions be followed when recording the spectrum. First, the half width (FWHM) of the narrowest peak of interest should not be less than 21 data intervals, otherwise noticable degradation in the peak height will

-43-

occur upon smoothing.

Second, adjacent peaks which are to remain separated after the smooth must have their peak maxima located at least 21 data intervals apart.

When these two conditions can not be met, the alternative available to the operator is to average four spectra together, with an attendant improvement of S/N of  $2(=\sqrt{AVGN})$ . In setting up the  $\vee$  limits, one must remember that, in the 21-point smoothing operation, the first and last 10 points of the spectrum are not modified in any way.

The course of action takes after a P + response is shown in flow chart (Fig. 14). The computer control system requests sufficient information to set up the plot, including the starting wave number, the data interval, abscissa and ordinate expansion factors (the abscissa expansion factor must multiples of 1/2 and the ordinate expansion factor may be any positive number from zero to  $10^{64}$ ), whether or not a pip marker is desired, if so, the interval (in points) between pip marks . Next, the program searches the stored spectrum, finds the minimum absorbance value, prints it, and is prepared to plot the spectrum with the minimum absorbance adjusted to appear as zero on the plotted spectrum. Before plotting, however, the operator is allowed to enter an OFFSET either to displace the spectrum so that the plot will display

-44-

absolute absorbance values, or to vertically offset the spectrum any amount desired. Negative values for OFFSET should be avoided, since the combination of two's-component logic in the computer, the single polarity of the  $D \rightarrow A$ converter, and the 0 to 2.37 V range of the recorder all combines to make small negative absorbance values look like large positive values. (Data are taken from the P.E. 180 spectrophotometer system). The computer subtracts 2000 cm<sup>-1</sup> from the starting frequency in order to set up a binary counter, SCLCG, which will automatically double the number of stepping motor pulses per abscissa when 2000 cm<sup>-1</sup> is reached on the plot (plotted from high wave number to low). Each ordinate, varying between about 0 and 2 absorbance units, is first adjusted for the minimum and offset; i.e., ORDINATE' = ORDINATE - MINIMUM + OFFSET . Since a 10-bit  $D \rightarrow A$  counter is employed, and the unexpanded ordinate scale of the 180 is from 0 to 1.5 absorbance units, each ordinate is multiplied by a scale factor of 682.67 before it is converted into truncated binary integer, and the most significant 10 bits are strobbed into the buffer of DAC. The pip marks are produced by simply adding ten percent of full scale to the contents of DAC buffer, without moving along the X-axis (See Fig. 15B).

Fig.15B illustrates the possible inputs to the chart and pen drive circuitry of the 180. Point A allows

-45-

POINT A: 0-395V FULL SCALE PDINT B: 0-2.37V FULL SCALE POINT C: 0-0.5V \_\_\_\_\_ [ ] ] ] \_\_\_ (0 400 pps Pluse RATE) POINT D: MOTOR DIRECTION CONTROL SV=RIGHT DV=LFET

# FIG.15 B-POSSIBLE INPUTS TO MODEL 180 X/Y RECORDER C.RC JITRY

the operator to retain the function of the spectrometer's RC pen damping control. Our system uses point B for the input to ordinate values from the DAC. Two trim pots connected external to the DAC (not shown) adjust to full scale gain and zero offset for the ordinate. The motor pulse output from the interface goes directly to point C on the pen driver board where it drives the stepping motor (abscissa control) at a rate determined by a counter in the software.

-46-

Setting the spectrometer up for a plot requires throwing the DPDT switch to 'COMPUTER', putting the pen to the right starting point, setting the monochromaton to CONSTANT CM(-1), turning the X-Y recorder ON, and pushing the SCAN button to lower the pen. During the plot, there must be some energy reaching the spectrophotometer detector, or the pen will automatically lift from the paper due to low energy.

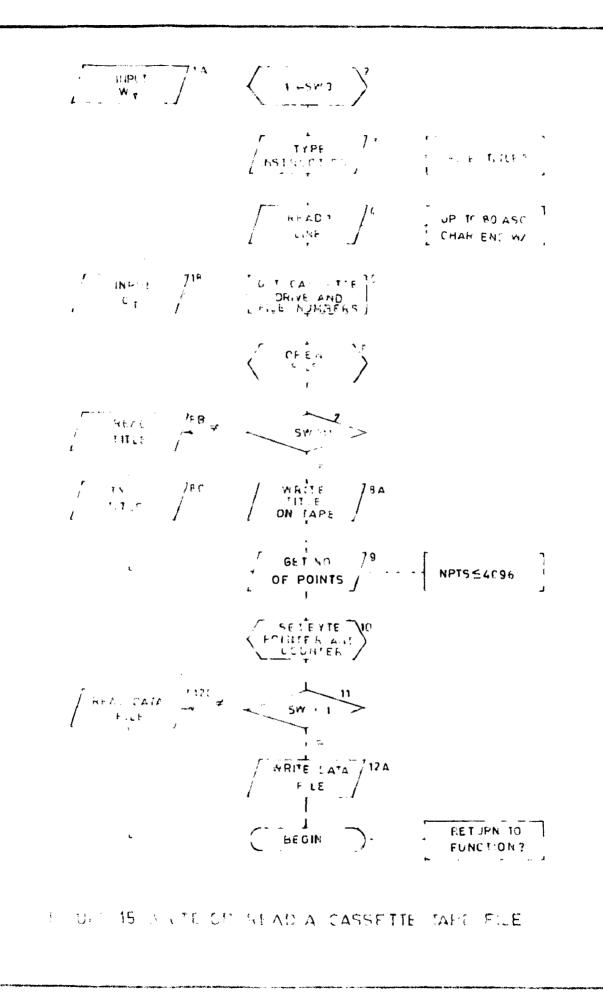

W + and C + Write or Read a Cassette File

Data General's SOS (Stand-alone Operating System) provides the user with simple I/O calls to standard peripheral devices. Call such as

- RDL for read a line

- .WRL for write a line

- .RDS for read sequential

- and .WRS for write sequential.

These calls make it easy to move data between cassette files and core memory. Flow chart (shown in Fig.15 illustrates both read and write flow diagrams. Each read or write command requires a byte counter and a byte pointer which are passed to SOS in one hardwave accumulators  $\underline{AC\emptyset}$ and  $\underline{ACI}$ .

Each data file produced by the main program begins with an ASCII title line , which is typed in by the operator before the data are transferred to the tape. The title line can contain up to 80 characters (132 are allowed in DGC's default mode as allowed in 180 model) terminated by a carriage return. Pressing 'rubout' types a +, and deletes the last character typed. Pressing 'Shift-L' causes the entire line to be ignored and a new line requested. The title line should contain such information as the starting wave number, data interval, number of points, and some kind of sample identification. This makes it easy for multiple users to keep track of their data files over long periods of time.

When a file is to be input following a C<sup>4</sup> response, the title is typed on the teletype before the computer control requests additional information from the operator. Data are transferred, both in read and write modes, a single block of 4-NPTS bytes. Ordinate values are stored sequentially as floating point numbers, each occupying

-47-

two words. ASCII strings are stored one character to a byte, two bytes to a word.

5. R , Ratio Two Spectra by Subtracting Absorbances

The spectrum which is minuend is placed on cassette drive (no.2) and the baseline spectrum goes on cassette drive (no.1). The computer control requests the file numbers for the two sets of data, then reads in the entire spectrum for the drive no.2. A scale factor is then requested from the operator, to be used in a scaled subtraction. Baseline ordinate values are then read in one at a time, multiplied by the scale factor, then subtracted from the minuend already stored. The difference between them replace the spectrum in memory, one point at a time.

Since SOS uses a software buffer to transfer bytes in blocks from a cassette tape, the operation of reading four bytes at a time does not cause jerky tape motion. The above routine does not conserve space, though, by not requiring storage for both spectra.

6. T: Type n points on Teletype.

This is a simple function, could be used to produce paper of spectra, but they are not convenient to handle. May be other sort of displays can be used instead of typing on teletype.

7. CH! There is one more task for the microprocessor,

-48-

can be applied here and that is to synchronize the channel of COI, as described in previous chapters. That, for example, if a filter wheel has arrangement for three channels, after one spectrum analysis is over, a certain delay must be offered to synchronize the second channel by rotating a step-motion and after then similarly third channel should be used for analysis. This will be included in Generalized Main Program.

## CHAPTER - VII

## MICROPROCESSOR SELECTION

The selection of a suitable microprocessor depends primarily on the particular application. Since the characteristics of the various processors are quite different, a number of factors must be considered in making a good choice. From the standpoint of the designer, the selection process involves investigating the software, hardware, and system design of a processor. Software design investigation requires examination of many features, including architecture (e.g., word length and speed) and programming flexibility. Hardware design investigation includes examining completeness (amount of support hardware necessary), and system design considers available design aids (both hardware and software).

Word length is the first feature usually considered. The determining requirement include analog resolution, computational accuracy, character length and width of parallel inputs or outputs. Also, when specifying word size, one should remember that ease of programming, not the efficiency with which the application is performed, is affected.

Other important architectural features include

the number of CPU registers, type of return stock, interrupt capability, interface structures, and memory types. The number of registeres in the processor is obviously an important feature of its architecture. The registerers can reduce reference to main storage which may conserve both external memory and time.

The speed of the microprocessor has been ganged using numerous measures. Some include cycle time, state time, minimum instruction time, register-to-register addition time, and interrupt response time. But these measures should not be the only criteria used in timing estimation since they do not measure the power of the instruction set.

The degree of programming flexibility can be accessed by an examination of the processor instruction set. Multiple addressing modes conserve memory, simplify programming, and increase speed by using one-word memory reference instructions. Other important capabilities include arithmatic instructions (e.g. binary and BCD arithmatic, multiply and divide, double precision arithmatic ) and logical and I/O control instructions.

The number of additional IC packages required for

-51-

a microprocessor based control system is an indication of the completeness of the system. The feature of interest is how many number of additional hardware support is needed like clock generators, timing, memory, I/O control, data address buffers, multiplexer inputs, interrupt control, and power supply units.

In this case, dynamic range and precision are important considerations, since signal changes of only a few thousands of a percent can be measured. From this consideration, a 16 bit processor such as the CP,1600 (manufactured by General Instruments) or PACE (manufactured by National Semiconductors) can be a good choice. But CP1600 is having further advantages of the presence of eight program addressable registers which permit the programmer a great deal of flexibility. Also, as shown in figure, there are the four status flags for sign (0 = +), zero, overflow and carry ( S,Z,OV,C ), which are controlled from the results of the ALU operations. Alongwith these, 10 bits instruction word facility, instruction execution from register to register in just 2 usec facility, with the power requirements of 5V and ±12 Volts are available. This is a 40 pin slice based on NMOS technology with the number of available softwares like cross-assembler, PL (Program library), Simulator and others. Also register holds 16 bits upto 64K words for the representation of memory or I/O locations.

T

-52-

The relatively high performance of the CP1600 makes the processor particularly suitable for high-speed real time applications, such as process control systems.

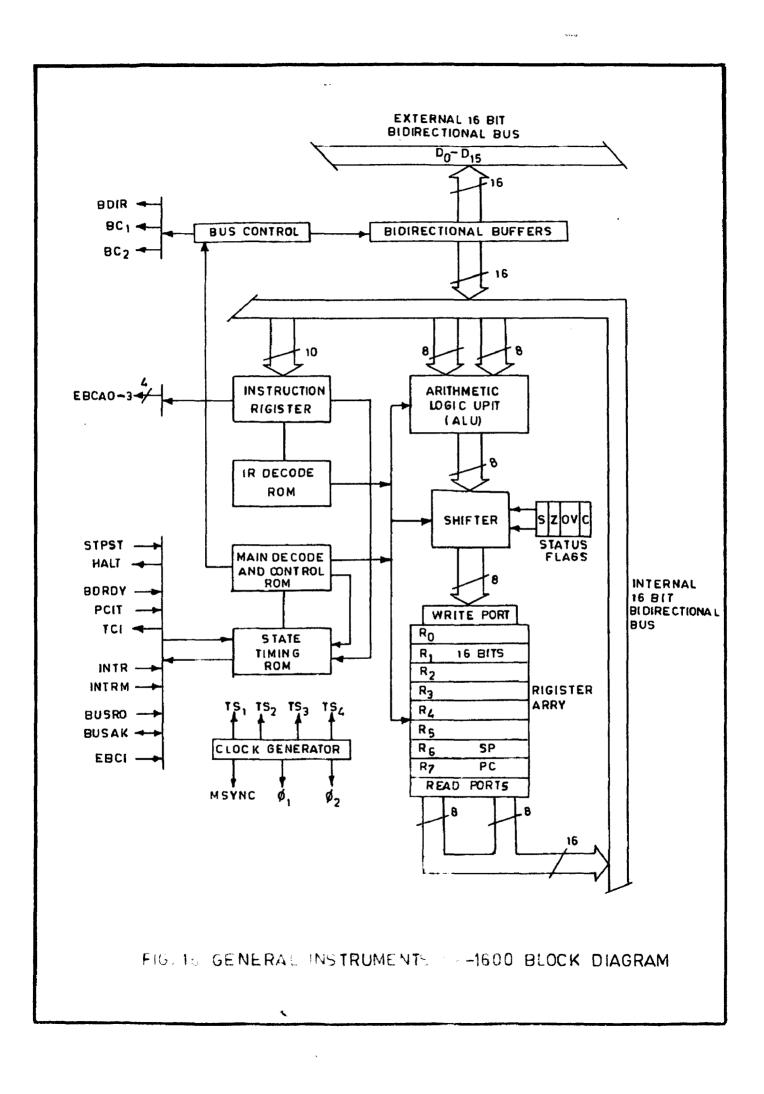

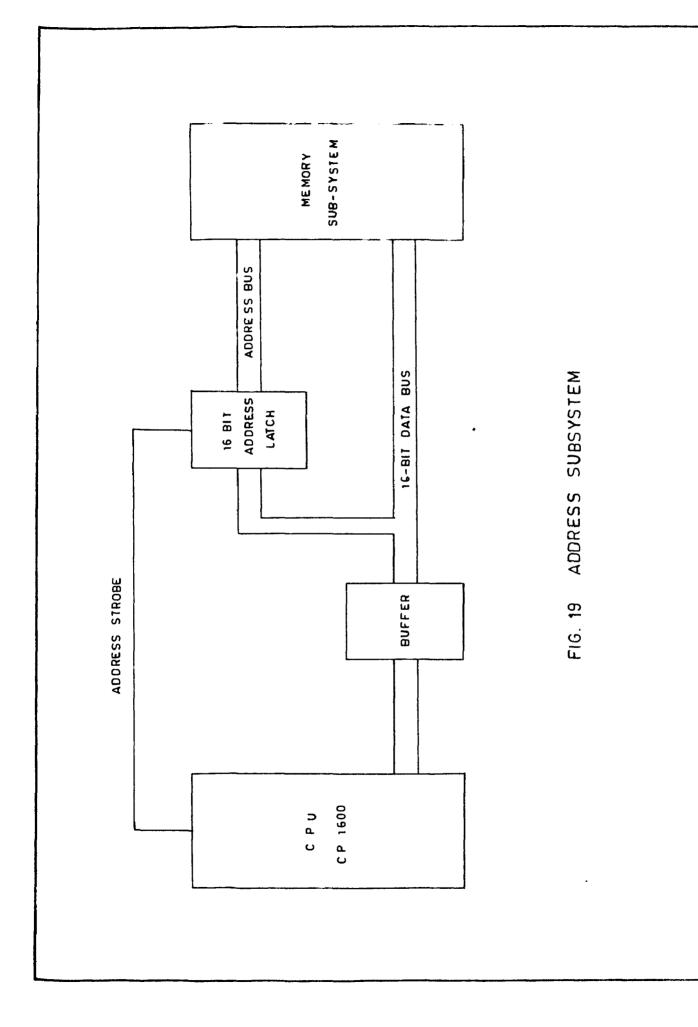

This CPL600 is organized around a 16-bit bidire- ' ctional data bus. Connected to the bus are the following active elements

a bidirectional I/O buffer

instruction register

ALU

eight general-purpose registers (16 bit)

The instruction register is connected to an IR Decode ROM, (Internal Read Only Memory), which decodes the bit sequence of the instructions in the instruction register to provide the appropriate control signals to the ALU, shifter and general purpose registers.

The ALU of the CP1600 operates on 8-bit words. It processes two 8 bit words from the 16 bit bidirectional data bus and produces an 8-bit resultant, which is forwarded to the shifter. The shifter may shift the resultant one bit right or left or may perform no operation at all. The shifter also affects the status flags, depending on the resultant. From the shifter, the data enters the Write Port in which it may be transferred to any one of eightgeneral-purpose registers. The Read Port associated with the registers can then transfer 16 bits in the form of two

8 bit words from registers to 16 bit bidirectional data bus.

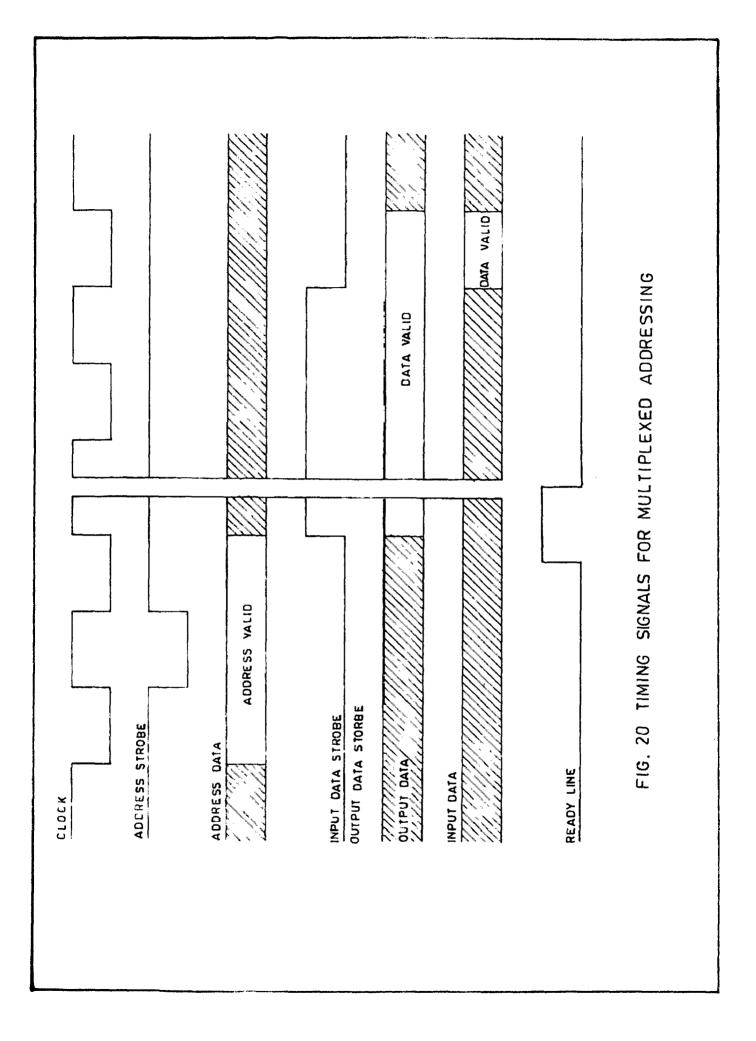

CP1600 is driven by a two phase clock at 5 megahertz, thus producing a cycle time of 400 nanosecond. A state timing ROM decodes the state signals from external signals and transfers such information to the Main Decode and Control ROM.

In the CP1600 all operations to be performed are specified by 10 bit instruction words carried on the lower 10 bits of the 16 bit data bus. The structure of these codes is

Op code RS RD

4 bits 3 bits 3 bits

Where RS and RD represent three-bit codes specifying the <u>source</u> and <u>destination registers</u> respectively. The four op-code bits are decoded by the decoding and control (micro) ROM into 16 basic operations, 8 of which refer to external operations extending through the external data bus into the address space, to memory and peripherals (treated alike). The other eight are internal register to register instructions. The source and destination registers specified in the last two three-bit fields of the instruction refer to any of the eight addressable registers. Under certain conditions the last six bits are operation code modifiers instead of registers.

All external addresses are reached by registeraddressing; that is, the register specified in the instructions contains a pointer to the location within the address space that actual holds or receives the data. Since the register holds 16 bits, up to 64 K words can be reached directly, representing memory or I/O locations.

-55-

The 16 basic instructions and their op-codes, for a generalized main program (as given earlier) are shown in table (Fig. ). The total number of useful instructions that can be generated from one or more of these basic instructions, is well over 100.

Of the more than 100 instructions available in this language, only those necessary to understand this program, together with a listing of their appropriate mnemonics and meaning, is also given here. (Table ).

### CHAPTER - VIII

# GENERALIZED SOFTWARE USING CP1600

We have discussed till now the requirements of the digital control system desired for NDIR spectrometer and what functions, the main program or software of the system should perform. These functions and the corresponding software developed have been made to take care of all available features of Perkin-Elmer-180 Infrared Spectrophotometer model. . But the software program required to channelize the spectrophotometer for various components of interest have not been taken into account yet.

Now let us consider a general spectrophotometer for the digital control desired and develop a generalized main program which can take care of only essential features of control, those are, to channelize spectrophotometer by moving a step-motor that drives the solid-state detector, calculations for ratio routines, storing the required data and the proper display corresponding to the proper channel of the component of interest. In this chapter, the generalized main program has been developed and it has been applied to the CP1600 microprocessor chip to work with.

Before going the entire generalized program, let us put a segment that performs the key operation of division in order to obtain the required signal ratio  $e_r/e_s$ . Since the divident is always smaller than the division, a simpler routine can be used which work only for this condition and will report an error if  $e_r$  is greater than  $e_s$ . As a further simplification of both signals must be positive, although this is not necessarily a software limitation. This particular subroutine is shown in Table. Appendic B.

The first step is to zero the register  $R_3$ , which is accomplished by the instruction CLR  $R_3$ . Next we wish to ensure that A is less than B, or that A-B is positive. This is accomplished by the second instruction CMP R5, R2 which temporarily subtracts R5 from R2 without changing either. In detail, this is a compound instruction. It requires I's complementing B, adding 1 to make the negative of 2's complement, and adding the result (-B) to A. If  $A \ge B$ , there is a carry bit, C = 1. If A < B, C = 0.

The next instruction BOC ERR (or BOHE ERR) requires a jump to the symbolic location ERR (not shown in Table. ) if C = 1. This would put the system into an error routine.

If there is no branch, the program continues with MVI<sup>\*</sup> 4,R6. This instruction moves the number 4, the number of places in the calculations, to the counter R6 where it will be used for control.

The instruction CRC clears the carry, after which the dividend is rotated left with the carry bit, R2-R5 is again examined with the CMP instruction and, if there is no carry (R5 is larger), there is a jump of DV2 on the BNC command. Since there is a carry in this case, the next operation, subtracting R5 from R2, is possible and

~57-

SUB R5, R2 takes place.

The next instruction shifts the carry bit into the LSB of R3 (the quotient) with SRLC S1, R3. R6 is then reduced by 1 (DECR R6), and if it is not get zero, the program jumps back to DV1 on BNZ DV1. Thus more iteration can be required in this case.

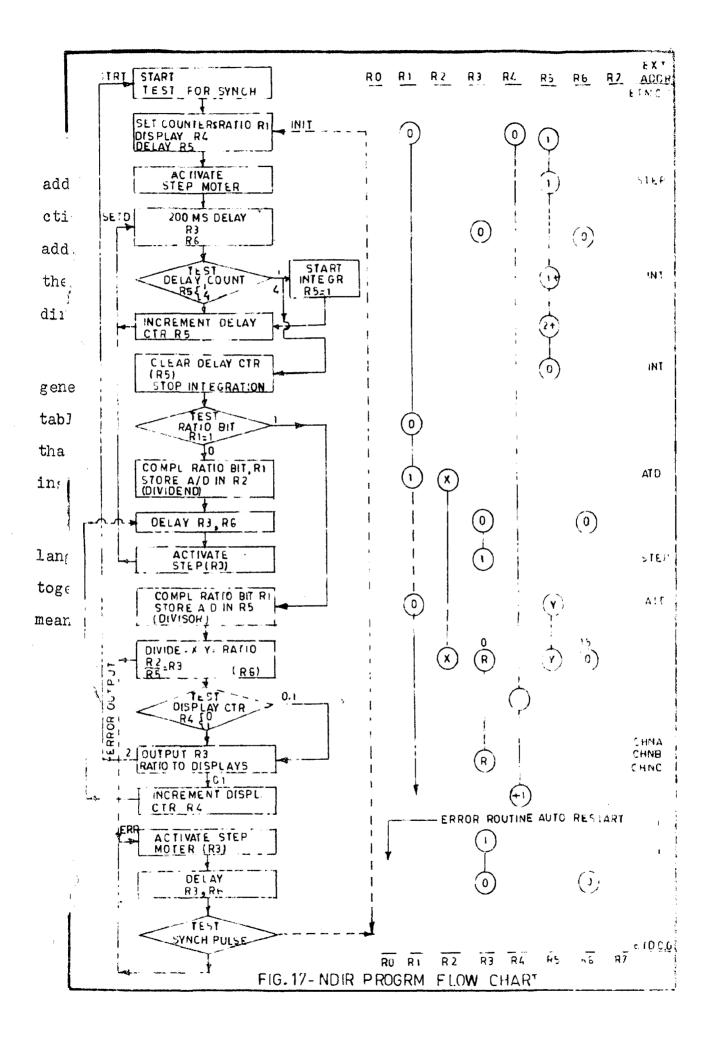

# General Main Program Applied to CP1600

The main program is facilitated by preparing a more detailed flosheet (shown in Fig.17) specifying the microprocessor CP1600 activities. In the CP1600 it is worthful to include a listing if the registers in use at each step in the program. The main program shown in Table Appendix c is written in an assembly language.

Column 1, in program (shown in Table ) shows descriptive amcomment and does not result in coding. The first three lines of coding define the assembly language and the memory location (relative). They symbols in the location field (column 1 to 4) are lebels which represents the memory location. EQU, a psuedo-operation which assigns a specific location to the label. For example STEP EQU 1437 assigns STEP to external word 1437. STEP is used as the address of the stepping motor drive flip flops (external peripheral).

Similarly, the address for the start-stop driver of the analog integrator (INT), the analog to digital (ATD),

-58-

and the digital display channel gates CHNA, CHNB and CHNC, are defined.

The STRT routing senses the presence of the signal satisfying that the no.6 filter is in place and the analyzer is ready to begin the first cycle. The BOS (Branch on sense) instruction refers to an addressable external multiplexer (MUX) in an experiment version of the microprocessor. The instruction BSNS can also be used and the sense signal be located with EQU.

If the signal is sensed, the program jumps to the ERR location with an unconditional branch (BUNC). This routine has the effect of rotating the filter wheels until the no.6 position is found.