# **ELECTRONIC TESTING OF INTEGRATING METERS**

# A DISSERTATION

# Submitted in partial fulfilment of the requirements for the award of the Degree of MASTER OF ENGINEERING

in

# ELECTRICAL ENGINEERING (MEASUREMENT AND INSTRUMENTATION)

By

# AJAY KUMAR SAXENA

DEPARTMENT OF ELECTRICAL ENGINEERING UNIVERSITY OF ROORKEE ROORKEE, (INDIA) MARCH 1979

# <u>CERTIFICATE</u>

Certified that the dissertation entitled, 'ELECTRONIC TESTING OF INTEGRATING METERS', which is being submitted by Ajay Kumar Saxena in partial fulfilment for the award of the degree of Master of Engineering in Electrical Engineering (Measurement and Instrumentation) of the University of Roorkee, Roorkee, is a record of bonafide work carried out by him under my supervision and guidance. The matter embodied in this dissertation has not been submitted for the award of any other Degree or Diploma.

This is further certified that he has worked for 14 months from In., 78 to March, 79 for preparing this dissertation at this University.

(H. K. VERMA) Reader in Electrical Engg., Department of Electrical Engg., University of Roorkee, Roorkee.

Dated March 22, 1979.

# ACKNOWLEDGEMENT

The author humbly expresses his deep sense of gratitude to his guide Dr. H. K. Verma, Reader in Electrical Engineering, for his keen interest, continuous encouragement, kind guidance<sup>3</sup> and thoughtful advise rendered by him during the course of this dissertation work.

Sincere thanks are expressed to Dr. P.Mukhepadhyay, Prefessor and Head of the Electrical Engineering Department for very kindly providing necessary facilities required for the work.

Thanks are also due to Mr. A. K. Ghai, Research Scholar in Electrical Engineering for the help in using the SC/MP microprocessor and to his colleagues who constantly helped and encouraged from time to time.

Last but not the least timely cooperation of the laboratory staff is deeply acknowledged.

AJAY K. SAXENA

# \_A\_B\_S\_T\_R\_A\_C\_T\_

Electronics is fast appearing every field of engineering, and in fact of the human life. Testing of integrating meters (energy meters) has also not been left untouched by electronics. Considerable work has been done by researchers in electronic testing of integrating meters, and to some extent the same has been adopted by the manufacturers. The work done so far has been reviewed here critically. To bring out clearly the advantages and limitations of electronic testing methods as also computer testing, an account of the conventional methods has also been included.

A testing scheme using digital electronic circuits and another one based on the use of a microprocessor has been developed by the author and successfully used for testing induction type energy meters. Principles of these schemes, as also the details of the hardware and software (for the latter scheme only) are presented here. Conclusions on the work done have been drawn and some suggestions for future work have been given at the end.

|                |                                                                         | ł                                |

|----------------|-------------------------------------------------------------------------|----------------------------------|

|                | <u>CONTENTS</u>                                                         |                                  |

|                | FICATE                                                                  |                                  |

| ACKNO<br>ABSTR | WLEDGEMENT<br>ACT                                                       |                                  |

|                | DUCTION                                                                 | *** 1                            |

| 1.1            | Integrating Meter Testing                                               | ••• 1                            |

| 1.2            | Overview of the Dissertation                                            | ••• 4                            |

| 2. CONVE       | NTIONAL TESTING                                                         | • • • 5                          |

| 2.1            | Scope of Meter Testing                                                  | 5                                |

| 2.2            | Range of Tests                                                          | *** 5                            |

| 2.3            | Method of Testing                                                       | ··· 6                            |

| :              | 2.3.1 Long Period Dial Test                                             | ••• 7                            |

|                | 2.3.2 Short Time Test Against Rotating<br>Substandard                   | *** 8                            |

|                | 2.3.3 Test by Substandard Indicating<br>Instruments and Time Masurement | ••• 10                           |

| 2.4            | Stroboscopic Testing                                                    | ••• 12                           |

| 2.5            | Creep-Test                                                              | +++ 13                           |

| 2.6            | Low Power Factor Tests                                                  | ••• 14                           |

| 2.7            | Verification of Substanderds                                            | *** 14                           |

| ·              | 2.7.1 Verification of Indicating Sub-<br>standards                      | ••• 14                           |

|                | 2.7.2 Verification of Time Substandards                                 |                                  |

|                | 2.7.3 Verification of Substandard<br>Integrating Meters                 | • • • 16                         |

| 2,8            | Tosting 3-Phase Maters                                                  | -                                |

| 2.9            |                                                                         | • • • 17                         |

| 2.10           |                                                                         | *** 19                           |

| 2.11           |                                                                         | *** <u>2</u> 1<br>*** <u>2</u> 2 |

|                | RONIC AND COMPUTER TESTING                                              | ••• 26                           |

| 3.1            | Rectronic Testing                                                       | *** 26                           |

|                | 3.1.1 Stroboscopic and Counter Method                                   | ••• 26                           |

|                | 3.1.2 Calibration and Repair Bench                                      | • • • 27                         |

|                | 3.1.3 Automatic Load Holding Facility                                   | •                                |

|                | 3.1.4 Pover Time Method for Precission<br>Meters                        | ••• 27                           |

| 3.2            | Computer Desting                                                        | • •• 28                          |

| ••**<br>•<br>• |                                                                         |                                  |

|     |       | Equipment Controlled by Electronic<br>Computer                         | ••• 28      |

|-----|-------|------------------------------------------------------------------------|-------------|

|     |       | 3.2.2 Computer Controlled Automatic Testin                             | g 30        |

|     |       | 3.2.3 Automatic Test Equipment                                         | ••• 31      |

|     |       | 3.2.4 Fully Automatic later Testing System                             | ••• 33      |

|     | 3•3   | Commonts on Stroboscopic Testing                                       | *** 34      |

| 40  | HEW   | SCHEMES FOR AUTOMATIC TESTING                                          | ••• 36      |

|     | 4.1   | Menual Start and Stop                                                  | ••• 36      |

|     | 4.2   | Manual Start and Auto Stop                                             | ••• 37      |

|     | 4.3   | Analog Error Computation                                               | ••• 37      |

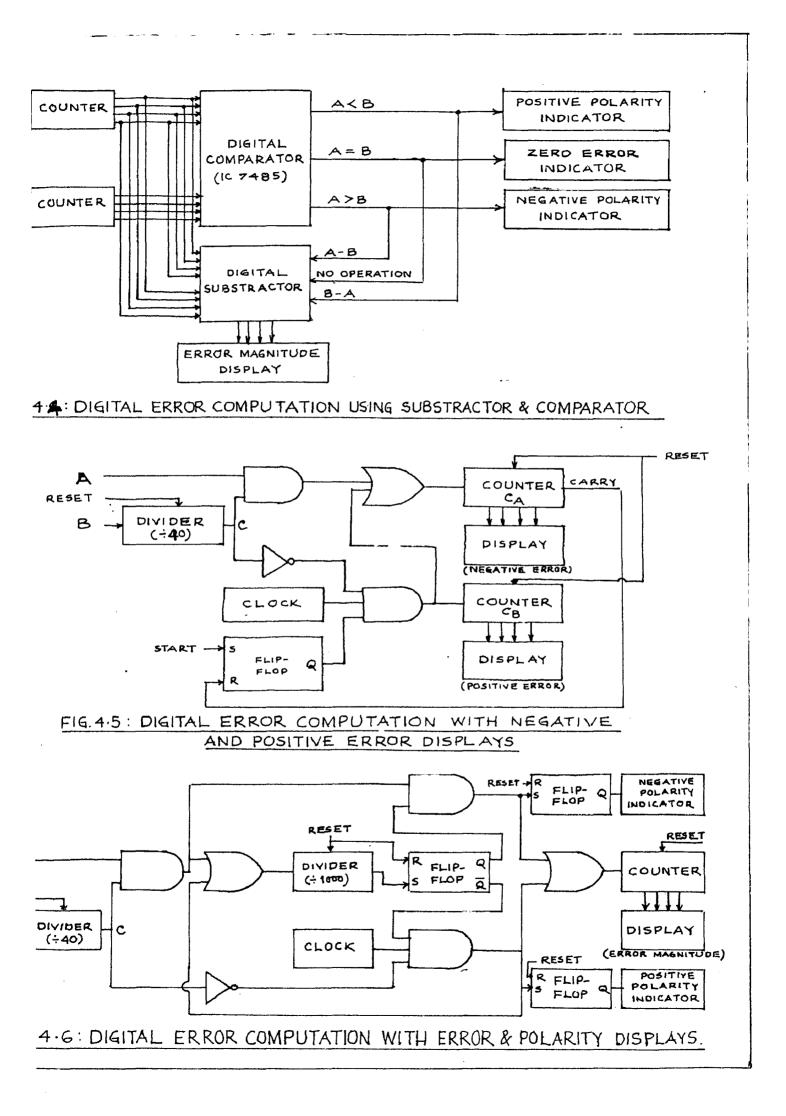

|     | 1. L. | Digital Error Computation Using Substractor<br>and Comparator          | r<br>••• 38 |

| 1   | 4.5   | Digital Error Computation with Negative<br>and Positive Error Displays | ••• 38      |

| ı   | 4,6   | Digital Error Computation with Error and<br>Polarity Displays          | *** 39      |

|     | 4.7   | Meroprocessor based tosting                                            | 40          |

| 5.  | A DIC | NITAL SCHEME DEVELOPED FOR AUTOMATIC TESTING                           | *** 41      |

|     | 5.1   | Principle of Testing                                                   | ••• 41      |

| ,   | 5.2   | Elements of Testing Scheme                                             | ••• 42      |

|     |       | 5.2.1 Primary Stimulus                                                 | ••• 42      |

|     |       | 5.2.2 Transducer Assembly                                              | ••• 42      |

|     |       | 5.2.3 Signal Conditioners                                              | ••• 42      |

|     |       | (a) Amplifier                                                          | ••• 43      |

|     |       | (b) Zero-Crossing Detector                                             | • • • 43    |

|     | 5.3   | Lorking of Testing Scheme                                              | ••• 43      |

|     | 5.4   | Dosign Considerations                                                  | *** 45      |

| 5   |       | 5.4.1 Clock                                                            | ••• 45      |

|     |       | 5.4.2 Monostable (Dalay) Circuit                                       | • •• 45     |

|     |       | 5.4.3 +5 V Regulated Power Supply                                      | ••• 48      |

| . * |       | 5.4.4 ± 12 V Regulated Power Supply                                    | ••• 49      |

|     | 5.5   | Tost Sst-up                                                            | ••• 59      |

|     |       |                                                                        |             |

**,**

| 6. | A MI  | CROPROCESSOR BASED TESTING SCHEME                                                 | ¥•• 51           |  |  |

|----|-------|-----------------------------------------------------------------------------------|------------------|--|--|

|    | 6.1   | Principle of Testing                                                              |                  |  |  |

|    | 6.2   |                                                                                   | ••• 51<br>••• 52 |  |  |

|    | -     | Software                                                                          | ••• 52           |  |  |

| ·  | 6.4   | P rogram                                                                          | *** 53           |  |  |

| 7. | CONCI | CONCLUSIONS AND SUGGESTIONS FOR FURTHER LORK                                      |                  |  |  |

|    | 7.1   | Conclusion                                                                        | •*• 54<br>••• 54 |  |  |

|    | 7.2   | Suggestions for Further Work                                                      | ••• 57           |  |  |

|    |       |                                                                                   | l                |  |  |

|    |       | APPENDIX A : An example of error limits<br>APPENDIX B: Listing of the Program for | <b>* * *</b>     |  |  |

|    |       | APPENDIX B: Listing of the Program for<br>Microprocessor Based Testing            | •<br>**          |  |  |

|    |       | REFERENCES                                                                        | ÷.               |  |  |

|    | *     |                                                                                   | š < .            |  |  |

| •  |       |                                                                                   | •                |  |  |

|    |       |                                                                                   | ، و بر<br>م      |  |  |

|    |       | <b>♥ ♥ ♥ ● ●</b> :                                                                | • • •            |  |  |

|    |       |                                                                                   | 1.5              |  |  |

|    |       |                                                                                   | t an a           |  |  |

|    |       | 4 ;                                                                               | · ,              |  |  |

|    |       |                                                                                   | • • •            |  |  |

|    |       |                                                                                   |                  |  |  |

|    |       |                                                                                   |                  |  |  |

|    |       | · · · ·                                                                           |                  |  |  |

|    |       |                                                                                   | :                |  |  |

|    |       |                                                                                   |                  |  |  |

|    |       |                                                                                   |                  |  |  |

|    |       |                                                                                   |                  |  |  |

|    |       |                                                                                   |                  |  |  |

|    |       |                                                                                   |                  |  |  |

•

### CHAPTER - 1

#### IN TRODUCTION

## 1.1 Integrating Meter Testing

Integrating meters are the meters which measure and register, either the total quantity of electricity in ampere-hours, or the total amount of energy, in kilowatthours, supplied to a circuit over a given period of time. Whereas the former is a d.c. instrument, the latter is of a.c. or d.c. type. Out of these meters, the a.c. energy meter is the most widely used one<sup>1</sup>. As its single largest application it is used for determining the energy consumed by electricity consumers. As such the dissertation is aimed at the testing of a.c. type integrating meters (energy meters) only.

Because of the variation of voltage, frequency, friction and temperature the meters are profieto become eroneous<sup>2</sup>. Integrating meter testing involves not only finding the actual errors but also includes the adjustments to bring the meter within permissible limits of error. The adjustments in the electromechanical (induction type) energy meters<sup>3</sup> are done by

- (1) a light-load compensator either in the form of a non-magnetic, conducting plate in the main air gap or in the form of a seperate shading coil on each outer limb of the voltage magnet.

- (11) a shading device employed for the power factor or quadrature adjustment.

(iii) a braking system by moving either the brake magnet itself or a shading coil on it.

These three adjustments are carried out in a definite order chosen so that each new setting has but little effect on those preceding it.

Limits of error for various integrating meters have been laid down in Indian Standard Specification no. 722. The scopes of various parts of this standard are as follows -

- (i) IS: 722 (Part II) 1962 Single-phase 2-wire whole-current watthour meter.

- (11) IS: 722 (Part III) 1966 : Three-phase wholeourrent and transformer-operated meters, and singlephase two-wire transformer-operated meters.

- (111) IS: 722 (Part IV) 1961 Three-phase kilowatt hour meters with maximum demand indicator.

- (iv) IS: 722 (Part V) 1965 Volt Ampere Hour meters

for restricted power factor range.

- (v) IS: 722 (Part VI) 1968 Reactive volt Ampere Hour meters.

As an example of the limits of error laid down in these Standards, those for single-phase 2-wire whole-current watthour meter are reproduced in Appendix A.

Three basic methods of error determination (discussed at length in the following Chapters) are -

- (i) Use of dials on the meter for checking against a precission dial testing instrument.

- (ii) Comparison of the speed of the rotor of the meter under test with that of a precission rotating substandard meter.

- (iii) Time check of the speed of the rotor of the meter using suitable indicating instruments and a stop watch.

Out of these, the comparision method is most commonly used as it eliminates the need for holding the loads on the two meters constant.

Interest and attention of test engineers has shifted to electronic testing in the past ten decades. Electronic testing, incorporating counting computation and display using electronic components, has higher potential of accuracy because of reduced share of human operator. Such testing may be done by a number of methods. Most of the techniques used consist of an application of analog principles and this results in low resolution and noise contamination unless filtering is used.

More elaborate design consists of hybrid digitalanalog systems, which involve rectification of pulses produced by magnetic or optical transducer giving a train of pulses with a freq. proportional to the angular velocity. Filtering is still necessary.

Digital designs requiring only digital processing have followed the previous ones. These designs involve the measurement of angular distance over a given time by counting the number of uniformly spaced signals produced from rotation of the meter disc. The count, being equivalent to integration over a given time, gives angular velocity. Filtering is not required but the designs are limited by the angular resolution of the disc and slow sampling time.

1.2 Overview of the Dissertation

Chapter 2 of the dissertation deals with conventional testing of a.c. type integrating meters to have an idea of the prevailing methods of testing. Testing of 3-phase meters, reactive meters, kilowatt demand indicators, KVAh and KVA demand indicators is briefly discussed. Chapter 3 reviews electronic and computer methods of testing. In Chapter 4 some new schemes incorporating varied amounts of automation have been proposed. Chapter 5 is devoted to an electronic test set-up which has been successfully designed and developed by the author. Chapter 6 presents a novel method of testing meters using a microprocessor. In the last chapter conclusions on the present work and suggestions for future work are given.

#### CHAPTER - 2

#### CONVENTIONAL TESTING

Before going into details of electronic testing it is essential to have an understanding of the conventional methods of integrating meters! testing. Keeping this in view prevailing methods of testing integrating meters have been discussed in this Chapter. Advantages and disadvantages of those methods have also been discussed in detail.

2.1. Scope of Meter Testing

The purpose of meter testing is the determination of errors of supply meters under approved conditions and by approved methods with a view to submitting these meters for certification. This includes not only the actual testing of the meters, but also the verification of the substandards used in connection therewith. The work of a testing station is not, however, confined within these limits. Most supply undertakings have in operation the systems of charging that necessitate the measurement of electrical quantities other than kwh, and the instruments used for these measurements demand indicators, KVArh and KVA meters - must be checked for accuracy.

2.2. Range of Tests

A typical scheme of tests for a.c. energy meters would consist of tests -

- (a) at the lowest current at which the accuracy is guaranteed (usually 5 percent of marked current);

- (b) at one intermediate current;

- (c) at the highest current at which the accuracy is guaranteed;

- (d) at marked current, 0.5 power factor lagging,

- (e) at the starting current (usually 0.5 percent of marked current), to ensure that the meter will run continuously at this current;

- (f) at zero current, with 10 percent excess voltage

applied to the voltage circuit, to ensure that the

meter does not creep under these conditions.

All the tests except (f) are carried out at normal voltage. Test (a), (b), (c) and (e) performed at unity power factor.

2.3 Methods of Testing

The three methods of test specified from which a choice can be made are as given below.

Method A

Long-period dial tests, using substandard rotating meters.

Method B

(a) Short time tests using substandard rotating meters.

(b) one long period dial test.

Method C

- (a) Tests by substandard indicating instruments

- and time measurement

- (b) One long-period dial test

# 2.3.1 Long-Period Dial Tests

It is the most important test as whichever of the three methods of testing is chosen, it cannot be dispensed In this method the actual advance of the register of with. the meter is observed for the passage of a measured amount of energy through it. Each of the four tests (a) - (d), described in Section 2.2, is carried out as a comparision between the movement of the dials of the test meter and the recorded rotations of the disc of the rotating substandard. The two meters are started simultaneously on the required load and, after a suitable time interval, stopped simultaneously. The regulation of the duration of the test load to an exact number of f seconds is obtained by means of a flexible cord in the voltage circuit of the meter. A flashing device actuated by a standard clock is better for this purpose than a stopwatch. The duration of the test must correspond to not less than ten revolutions of the pointer of the last (or lowest reading) dial.

Advantages -

(a) Complete elimination of errors due to starting or stopping of the substandards or stop watches.

- (b) No need of any necessity for holding the load absolutely constant.

- (c) Complete verification of the accuracy of the meter as an integrating instrument because the verification of substandard meter is done by measuring energy in terms of power and time.

- (d) Errors due to self heating can be determined by this test. For this purpose, after the end of such a test, short time test at full load is performed.

Disadvantages

- (a) Large period of time required for a single test and thus for the complete set of tests.

- (b) Not a suitable method if adjustments to the meters have to be made during testing.

2.3.2 Short-time Test against Rotating Substandard

In this method energy corresponding to a stipulated integral number of revolutions of the rotor of the test meter is measured by means of a substandard meter which registers revolutions and fractions of a revolution of its moving element.

Number of revolutions of the rotor of the test meter is stipulated, and when the substandard meter registers in rotor revolutions and fractions thereof, the advance of the substandard corresponding to the stipulated revolutions of the test meter is calculated.

r = counted revolutions of the meter under test

R = counted revolutions of the substandard meter

k<sub>h</sub> = watthour constant of the meter under test

K<sub>h</sub> = watthour constant of the substandard meter

R<sub>o</sub> = revolutions of the substandard meter, if the

test meter was hundred percent accurate.

$$= \frac{\mathbf{r} \mathbf{k}_{h}}{\mathbf{K}_{h}} \quad (\text{since then } \mathbf{R}_{o} \mathbf{K}_{h} = \mathbf{r} \mathbf{k}_{h})$$

Percentage error is thus

Let

# <u>Calculated revolutions - observed revolutions</u> x 100 Observed revolutions

The test is normally, carried out for between 5 and 100 complete revolutions of the disc of the test meter. As the disc may make some hundreds of revolutions for one revolution of even the last dial of the meter, the time for this test is of the order of two minutes, as compared with something of the order of an hour for a long-period dial test.

Advantages -

- (a) The adjustments to the test meter and repetition of the test are possible without an excessive waste of time.

- (b) Avoidance of load holding.

- (c) Elimination of errors due to starting and stopping.

- (d) Constancy of test load is not essential and hence only one observer is required.

Main disadvantage of the test is that the short period of the test at each load prevents the meter from reaching a steady temperature at that load.

2.3.3. Test by substandard indicating Instruments and Time Measurement

In this method the actual ratio of speed to watts is compared with that for which the gearing constant is suited. The value of power in the test circuit, actual, or nominal at a declared pressure, is measured by substandard indicating instruments, and the accuracy of the performance of the meter is assessed by the measurement of time interval required for a stipulated number of revolutions of the rotor of the meter. In the practical application of this method the time actually required for the execution of a definite exact integral number of revolutions of the meter rotor with a stipulated load is compared with the nominal time which corresponds to the gearing constant.

If watthour constant of the meter =  $k_{h}$ , then correct time required in any condition is given as

seconds =  $\frac{K_h \times \text{revolutions} \times 3600}{\text{volts} \times \text{emperes}}$

29

From this the time required for three different loads (at a stipulated voltage) may be calculated. If the three observed timings agree with their corresponding calculated (correct) values the meter is correct.

If the correct time is  $T_1$  and the observed time  $T_1$ for N revolutions, the actual rotor speed is N/T and the correct speed is N/T<sub>1</sub>. The difference in these speeds expressed as a fraction of the correct speed is

$$\frac{N(\frac{1}{T} - \frac{1}{T_1})}{N/T_1} = \frac{\frac{T_1 - T}{T}}{T}$$

The percentage error would then be

$$\frac{T_1 - T}{T} \times 100,$$

the meter being fast if  $T < T_1$

If the errors are the same at the three test loads these errors are merely of calibration, and either the inherent speed/load characteristic of the meter may be altered to suit the gearing constant or the gearing constant may be altered to suit the actual characteristic.

Notable advantage of this method is the superior accuracy of standard wattmeters in comparision with rotating standards.

## Disadvantages

- (a) Ceaseless vigilance is required to maintain the load constant at its stipulated value during the test.

- (b) Careful regulation of the load throughout the test period by an observer additional to the one who actually measures the time interval.

#### 2.4 Stroboscopic Testing

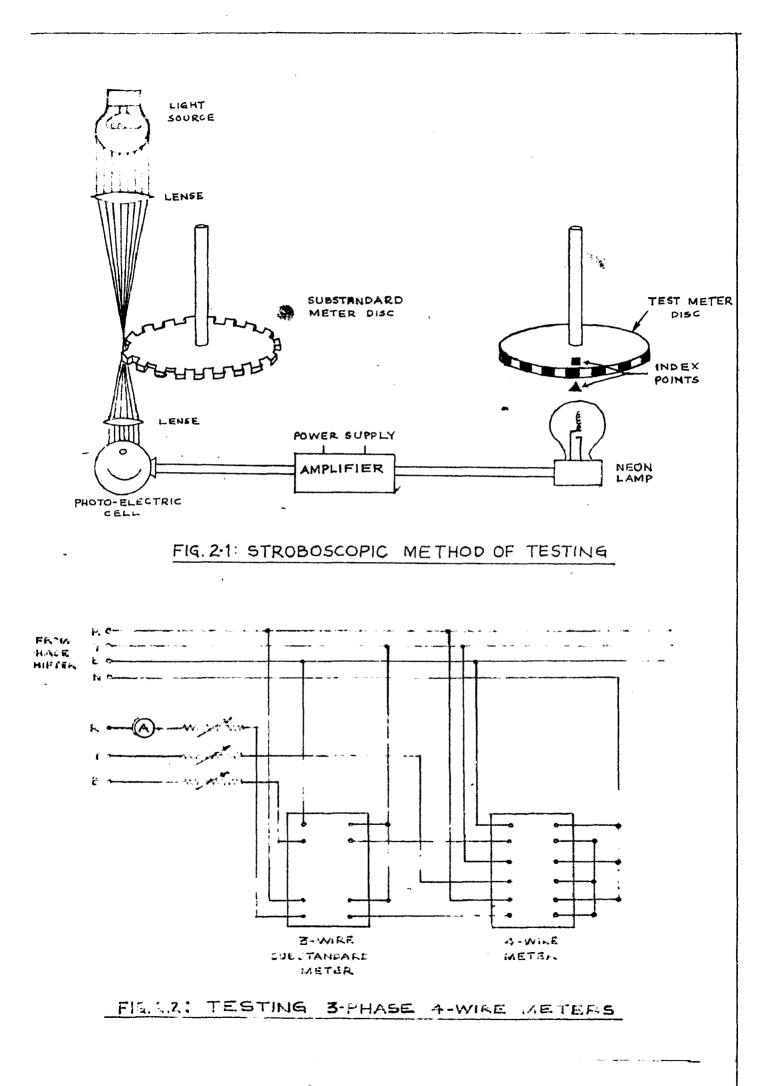

The stroboscopic method of testing is most useful when large batches of metres of similar rating are to be handled and adjusted rapidly. A beam of light is directed perpendicularly at the edge of the disc of the substandard meter (Fig. 2.1). This edge has teeth which alternately intercept and pass the beam. When the beam, is passing through a space between teeth, it activates the photoelectric cell whose output is amplified to flash a neon lamp placed near the disc of the test meter. This disc is marked with regularly spaced black spots. These spots appear to standstill if the meter speeds are the same, as should be the case if both are accurate or have the same error and both have the same watthour constant. If the meter speed is too high, the apparent motion of the disc will be forward at a rate corresponding to the meter error relative to the substandard, and vice-versa.

The adjustment of the test meter consists in setting the position of the brake magnets so that the disc appears to be stationary. This method has been refined for the determination of actual meter errors by direct indication. The substandard is provided with a specially calibrated brake magnet adjusting device, geared to a dial indicating deviations from correct speed in percentages fast and slow. The speed of the substandard is adjusted to exact correspondence with that of the test meter, and the error of this meter is read off directly on the special dial.

## Advantages

- (a) Error is indicated at once.

- (b) The method affords a means of adjusting the meter during the run and thus substantially shortens the time required for testing.

- (c) It also eliminates many opportunities for mistakesin calibration and in recording the sign of the error.

- (d) Measurements of the time intervals and personal error incident thereto are avoided.

- (e) The method is accurate as the setting of the brake magnet is made with certainty.

One of the important limitations of the test is that it is inherently suitable for test loads not less than half the rated full load of the meter. At the lower and loads the disc speeds are so small that this method becomes unreliable or fails entirely to give its characteristic phantom differential speed effect. Some manufacturers have adapted the method to low load testing by temporarily substituting, for the ordinary brake magnets of the substandard and test meters, special low flux magnets which increase the meter speeds tenfold.

# 2.5 Creep Test

Energy meters are tested for creep with its current circuit open and with 110 percent of the rated voltage applied to its voltage circuit under these conditions the disc of the meter should not make more than one revolution.

## 2.6 Low Power Factor Tests

There may be difference between the errors of an a.c. meter at full rated VA at 0.5 power factor and at the same watt load at unity power factor. To check this a.c. meters are tested at full rated VA and 0.5 power factor lagging. A tolerance of 10 percent is allowed in the power factor for this test.

2.7 Verification of Substandards

Meter testing regulations require that all the meters submitted for certification shall be determined by substandard instruments which are themselves periodically tested, either directly or indirectly. The approved apparatus for any testing station is listed below:-

Standard Apparatus : D.C. potentiometer, standard cells, voltage dividers and resistance standards for current measurements.

Ship's chronometer or pendulum clock.

Substandard Apparatus : Indicating wattmeters, ammeters,

voltmeters, rotating meters,

stopwatches or other timing devices.

Current, voltage and phase control apparatus.

Verification of substandards is briefly discussed below -

2.7.1. Verification of Indicating Substandards -

The verification of a substandard indicating meter consists essentially in comparing the true with the indicated values of the quantity purpoted to the measured by the instrument approximately at stipulated points of the scale. There are two ways in which this comparision may be made. First, the quantity to be measured may be adjusted to such a value that the pointer of the instrument deflects exactly to a position on the scale representing the value of the quantity measured, its true value then being measured by the standard potentiometer. Otherwise the value of the quantity measured may be adjusted to be exactly equal to the nominal value required by means of the potentiometer, and the actual instrument reading in this condition observed.

## 2.7.2. Verification of Time Substandards

Substandard stopwatches can be verified for accuracy very easily by a standard instrument with a seconds dial. A comparision of the stopwatch reading with the advance of the standard chronometer or clock over a period of 5 minutes reveals any error of the order of the maximum of 0.15 per cent, permissible with certainty. In practice any stopwatch exhibiting an error of more than 0.1 per cent, that is, an actual error of 0.3 seconds in 5 minutes, is subjected for examination and regulation. The indicated error of a stopwatch is inclusive of the error of starting and stopping, and this will vary with the observer.

If the standard clock is not fitted with a seconds hand, stop watches must be tested by the counting of pendulum swings. To make this tedious process convenient and less

liable to error the standard clock is fitted with an optical device. In this a shutter attached to the pendulum bob allows a light flash to pass from a lamp, through the operature in the shutter, every time it reaches one extreme limit of its swing. By means of a suitable mirror the indicating flash is made visible at a test bench. The position of the lamp is required to be accurately adjusted by trial, so that the flash is given at the extreme point of the travel. Any error in this position will result either in no flash being obtained or in the flash being double. After making the adjustment once, the integrity of the flash is a very good indication of correctness of swing of the standard clock.

2.7.3. Verifying Substandard Integrating Meters

As in two of the three approved methods of testing the meters are tested by comparision with substandard integrating meters, these must itself be verified by indicating substandards. Testing of substandard D.C.meters is similar to that of ordinary supply meters using indicating instruments and stopwatches.

A special technique, in addition to the testing by indicating substandards is used for the testing of A.C. substandard meters. In this the time during which a load of measured power passes the meter is regulated automatically by a standard clock. The automatic time control is obtained either by special contacts fitted to the 'scape' wheel shaft

of the clock or by light flashes received by a photo-electric cell and transmitted electrically to an impulse relay. The voltage circuit of the meter is closed and opened by a contactor relay controlled indirectly by the clock, so that the voltage circuit current of the meter flows during a time interval which is exactly equal to a prescribed number of seconds. The advance of the register in revolutions and fractions of a revolution of the moving element is compared with the energy corresponding to the measured constant test power flowing for the time period controlled by the standard clock.

This method of testing avoids two sources of error: first, the inherent error of a stopwatch, and secondly, the observers error in either starting and stopping the meter in a dial advance test.

#### 2.8 Testing 3-Phase Meters

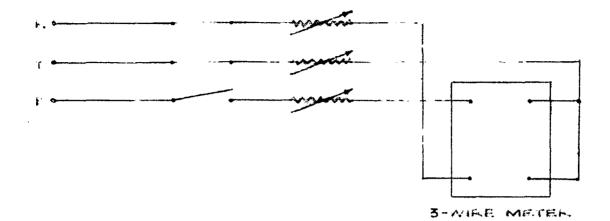

Every 3-phase meter must be tested in 3-phase circuit. Three-phase 4-wire meters may be tested in 3-wire circuits which supply the testing currents, in which case the total power in the phantom test load can be measured either by two wattmeters or by a 2-element polyphase wattmeter; alternatively, tests can be made by substandard 2-element meters. With this method of testing 4-wire meters the common terminal of the three voltage circuits is connected to the neutral of the voltage supply. The sedimentary connections for testing a 4-wire supply meter by a 3-wire substandard are shown in Fig. 2.2.

The technique of testing 3-phase meters by substandard integrating meters, by either short or long-period method, differs in no way from that of the testing of single phase meters other than that of setting the test loads to the required magnitude and to the balanced condition. When 3. however, 3-phase meters are tested by means of indicating substandards, the maintenance of a steady load during testing is not so straight forward. If the power in the phantom 3-phase test load is measured by a single polyphase substandard wattmeter, small adjustments can be made to one of the three variable loading resistances to maintain the required indication of the wattmeter, as these small adjustments do not cause sensible departure from the balanced condition of the load. If, however, the total power in the phantom load is measured by two substandard wattmeters it is by no means easy to maintain an absolutely constant value of this total power by adjustment of a loading resistance, if the supply voltage is not quite steady, because with a star connected load, such adjustment will alter the power indicated by each wattmeter. It is practically impossible to maintain a 3-phase test load, supplied by a varying voltage, at an absolutely constant value by adjustment if the total power is indicated by two Wattmeters, because one observer cannot keep the indications of wattmeters under continual observation.

In addition to the usual tests with a balanced load, every polyphase meter must be tested for balance of elements. In such a test both voltage circuits are tested in the normal way and full load current is passed through each element in turn. These tests are carried out at power factors of unity and 0.5 lagging, the later power factor being subject to a tolerance of 10 per cent. It is to be noted that, in the balance test, unity and 0.5 power factors refer to the singlephase load actually producing torque in the meter when a star connected test load is used, the balance test is conveniently carried out with one line supply to the load interrupted, as shown in Fig. 2.3.

### 2.9 Testing Reactive Meters

As the only meters requiring certification are those which register kwh, there is no officially approved procedure for testing the accuracy of a meter which either registers KVArh or which is a component of a meter registering KVAh. If substandard instruments indicating 3-phase VAr were available, the testing of reactive meters would be similar to the testing of 3-phase energy meters. A polyphase substandard wattmeter or Wh meter can be made to indicate 3-phase VAr by supplying its voltage circuits from a bank of two voltage transformers arranged in open delta<sup>4</sup>.

The normal tests of a reactive meter are carried out at zero power factor when the VAr equal to the VA. In addition, the behaviour of the meter with rated VA unity power

# FIG. 2.3 BALANCE TEST FOR 3-PHASE METER.

FIGL. 4: TEUTING KVAL METERS

a.

factor and zero VAr is observed and a test is made with an intermediate lagging power factor. The test for balance of the elements of a polyphase reactive meter is made with normal voltage excitation and with current in each element singly.

If there are no means available for the measurement of VAr or VArh directly by substandard instruments, indirect methods are used. A straightforward indirect method of obtaining 3-phase VAr is to obtain the watts by actual measurement and VAr from ammeter and voltmeter readings. This method is combersome and undesirable as it involves simultaneous readings of three ammeters, three voltmeters and one or two wattmeters, together with an awkward calculation. Moreover, this method is only fundamentally accurate with a balanced load, but the error with small unbalance is practically negligible.

Another indirect method of obtaining the VAr measure of a balanced 3-phase test load is from the readings of two single-phase wattmeters used to measure the power. /3 times the difference of these readings will give the 3phase VAr if both currents and voltages are accurately balanced. The disadvantage of this method is that the accuracy of the VAr measure so obtained depends so much upon the balance of the currents and voltages.

Third method involves the use of a phase - shifting transformer. The VAr value is obtained indirectly from the reading of a substandard wattmeter. The reactive meter to be

tested is connected in an ordinary 3-phase double circuit, which the voltage supply is derived from the secondary circuit of a phase-shifting transformer. A polyphase substandard meter is included in the circuit.

Neither of these three indirect methods can be considered as anything more than a makeshift. The only satisfactory way to test a reactive meter is by reactive substandards, and the most satisfactory available substandards for this purpose are ordinary substandard wattmeters or integrating meters used with substandard voltage compensators. The accuracy of such substandards will, of course, depend upon exactness of balance of the supply voltages, and if unbalance errors of the substandards are similar in magnitude and phase to those caused by voltage unbalance in the reactive meter, the test will indicate the accuracy of the meter in balanced voltage conditions. No test of a reactive meter can be considered conclusive till single-phase internally compensated reactive substandards are available of an accuracy at standard frequency, comparable with that of a substandard wattmeter.

#### 2.10 Testing Kilowatt Demand Indicators

The accuracy of the Merz demand indicator, provided the associated meter is free from error, will depend upon the accuracy of the gearing ratio controlling the advancement of the pointer and the accuracy of the averaging periods. When the averaging periods are controlled by an external time switch, this switch can be checked for accuracy seperately, and the accuracy of the demand indicator gearing can be tested by a procedure similar to a long-period dial test. The corresponding advances of the sub-standard meter will give the true values of the average power corresponding. The tests should be conducted at full load and about one-quarter of full load. When the averaging periods are controlled by a self-contained clock, the substandard meter reading must be observed at the commencement of each averaging period and the time durations of these periods simultaneously measured. The true average KW in this case will be obtained from the substandard advances and the observed times.

2.11 Testing KVAR Meter and KVA Demand Indicators

These instruments are of four classes : KWh and KVArh combinations with a seperate KVAh mechanism, phasecompensated KWh meters, current-operated instruments with voltage compensation and KWh meters with fixed phase compensation which are accurate at one power factor only.

The first steps in testing an instrument of the first class are to test the KWh and KVArh components seperately by the methods which have already been described. The KVAR register and KVA demand indicator should then be tested by methods corresponding to a long-period dial test and to an ordinary KW demand indicator test at KVA loads of various power factors. The method of testing will, provided the KVA load be known, follow the standard procedure, but it is

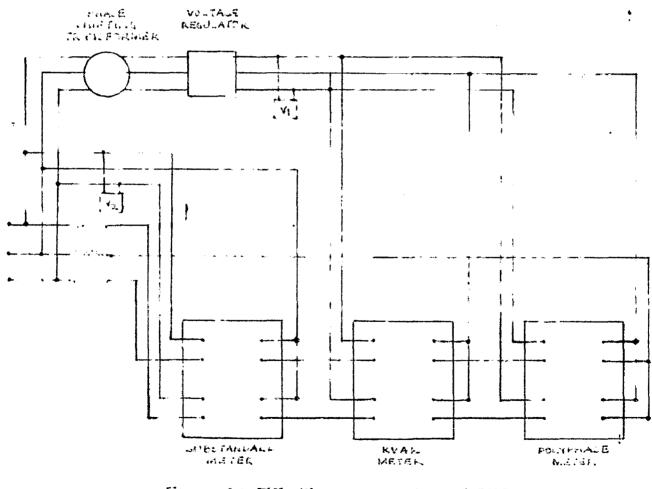

difficult to measure the KVA value of a 3-phase test load over a range of power factors, one method of doing this is illustrated by the schematic diagram (Fig. 2.4). The KVA instrument is tested without its current transformers, as a 5-Ampere instrument. This meter, together with a substandard 3-phase watthour meter and a substandard polyphase wattmeter, carries the current of a non-inductive test load. The substandard watthour meter voltage circuits are in parallel with this load, those of the KVAh meter and the polyphase wattmeter are energised from the secondary of a phaseshifting transformer. The magnitude of the voltages applied to the KVAh meter is adjusted by the voltage regulator to be exactly equal to those applied to the substandard watthour meter, this equality being indicated by the voltmeters  $V_1$  and V2. In this circuit the phantom volt-amperes in the KVAh instrument and in the polyphase wattmeter are the same as the actual volt-amperes in the substandard watthour meter, and, as the load of the circuit containing this latter meter is non-inductive, the rate of advance of the substandard meter will correspond to the KVA in the phantom load for all values of the power factor of this load. Thus, setting the rotor of the phase-shifting transformer to give the desired values of power factor of the phantom load in the KVAh meter, the advance of the KVAh register or of the KVA indicator should correspond to the advance of the substandard watthour meter. The polyphase substandard wattmeter is used to obtain the

position of the phase-shifter rotor corresponding to zero power factor, indicated by zero reading of the wattmeter. Thereafter the movable pointer of the phase-shifting transformer is set to 38 degrees in the usual way. The power factor of the phantom load in the KVAR meter will thereafter he directly indicated on the power factor scale of the transformer KVAh meters should be tested at zero and unity power factors and two or three intermediate power factors which should not, preferably, correspond to phase angles which are an exact submultiple of 90 degrees.

The foregoing method of testing is defective, in that it does not follow the standard and most desirable practice of testing supply meters and associated current transformers as a single measuring unit. But this is overweighed by the convenience of obtaining a direct measure of the KVAh, as compared to the indirect methods, in the phantom test load by means of 3-phase substandard meter. The only adjustment to be made during tests of the KVAh register and KVA indicator is that of maintaining voltages  $V_1$  and  $V_2$  exactly equal.

The above mentioned method of testing is immediately applicable to KVAh meters with automatic phase compensation, the meter first being tested as a standard 3-phase energy meter in the usual way without its auxiliary relay and voltage dividing resistances, and at its normal voltage.

KVA demand indicators, which consist of a watthour meter with fixed phase compensation, can also be tested by the method just described at the nominal p.f. at which they

arē correct. This p.f. can be set by the PST, and it can be checked by comparing it with the ratio of the wattmeter reading to the maximum reading which can be obtained by phase adjustment of the voltage. The meter should then be tested with the phase of the voltage shifted 10 degrees on each side of the position corresponding to the average p.f. to verify that, in each of these positions, a slow error of about 5 percent is obtained.

Three phase KVA demand indicators containing three current operated electromagnetic elements should be tested for balance at two or three loads, the voltage-compensating circuits being excited, and current, of a phase corresponding to balanced load conditions, being passed through each element in turn. The speed of the rotor should be the same for the same current in each element, but there is no definite relation between speed and current. Thereafter the meter will be tested as a 3-phase KVA demand indicator at selected points of the scale at constant 3-phase loads corresponding. The test at rated full load may be carried out at three or four values of p.f. and at unity p.f. with values of the applied voltage 10 percent above and below the rated value to check the accuracy of the voltage compensation.

## CHAPTER-3

#### ELECTRONIC AND COMPUTER TESTING

# 3.1. ELECTRONIC TESTING

In the field of meter testing electronics has been introduced for carrying out objective measurements. There are, for example, crystal clocks, photoelectric scanning equipment, which has come into general use, and electronic counters for counting the revolutions of meter discs or the pulses of calibrating meters.

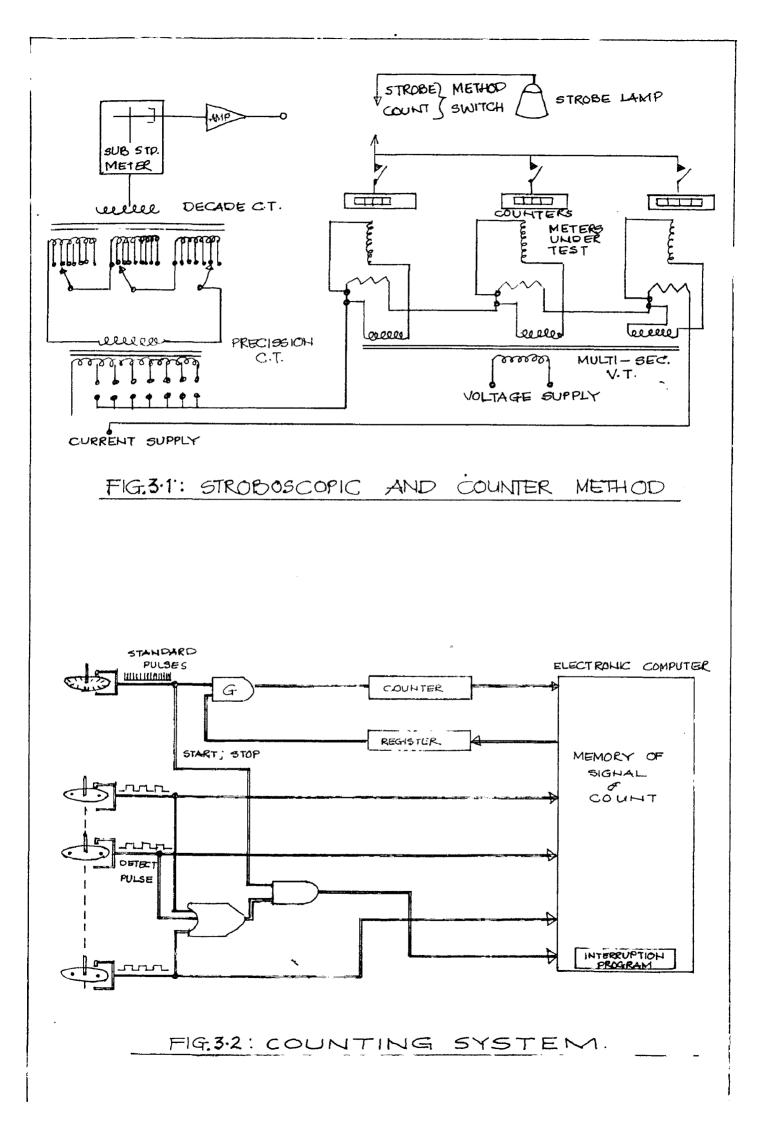

# 3.1.1. Stroboscopic and Counter Method

This method has been discussed by M.L. Done<sup>5</sup> and A.J. Bagott<sup>6</sup>. In this method, shown diagramatically in Fig.3.1, a rotating substandard is fitted with a pick-off device, either of photoelectric or inductive pattern arranged to give either 200 or 400 impulses per revolution of the disc. The output is amplified and switched to either a strobe lamp fitted with a flash tube or else, through dividing circuits to a series of counters, one for each meter.

The rotor of the meter under test is impressed with markings which are arithmetically identical to the subdivisions on the disc of the rotary substandard and under the action of the stroboscope an indication of the performance of the test meter is given, On low loads stroboscopic method can not be used and here, and also, for obtaining actual figures on higher

loads, the counters are used as timbrs. The speed of the PSS meter and the division factors are so arranged that the counters record 1000 for an integral number of revolutions of the test meter, enabling the error to be read directly to the nearest 0.1%. The counters normally started and stopped manually could be operated automatically.

#### 3.1.2. Calibration and Repair Bench

M.L. Done<sup>5</sup> has discussed a testing, repair and calibration bench which can accept two batches of meters, fifteen each, with calibration facilities capable of being transferred from one batch to the other. In operation, one batch is being repaired while the other is being calibrated, the calibration facilities are then transferred to the first batch while the other is moved on for dial test and a new batch put up and repaired.

# 3.1.3. Automatic Load Holding Facility

Another device given by M.L. Done<sup>5</sup> is an extension to a conventional test set whereby the total load on the meters under test is controlled to a predetermined. level on an integrated energy basis. Stop watches may then be used to time meters in the normal way.

## 3.1.4. POWER TIME METHOD FOR PRECISION METERS

A system particularly suitable for the calibration and testing of precision watt hour meters as well as precision standard watt meters, single and three phase, has been described

by J. Pawlat<sup>7</sup>. It functions by the power-time method. With the use of self-balancing comparators for the power measurement and an electronic controller of original design, an accuracy and stability of the power control of better than  $\pm 0.05\%$ is obtained. The development described in this paper aims firstly at eliminating the necessity for the potentioneter and manual regulation of the d.c. control and, secondly, automatically to control the a.c. (power). One of the main advantage claimed by eliminating the potentioneter with its manual control is the reduction of the response time from about 4 seconds to 200 milliseconds.

### 3.2. AUTOMATIC METER TESTING

The automation of meter testing is a subject which has aroused considerable interest in recent years and a number of papers has appeared in literature on installations which involved automation in various degrees.

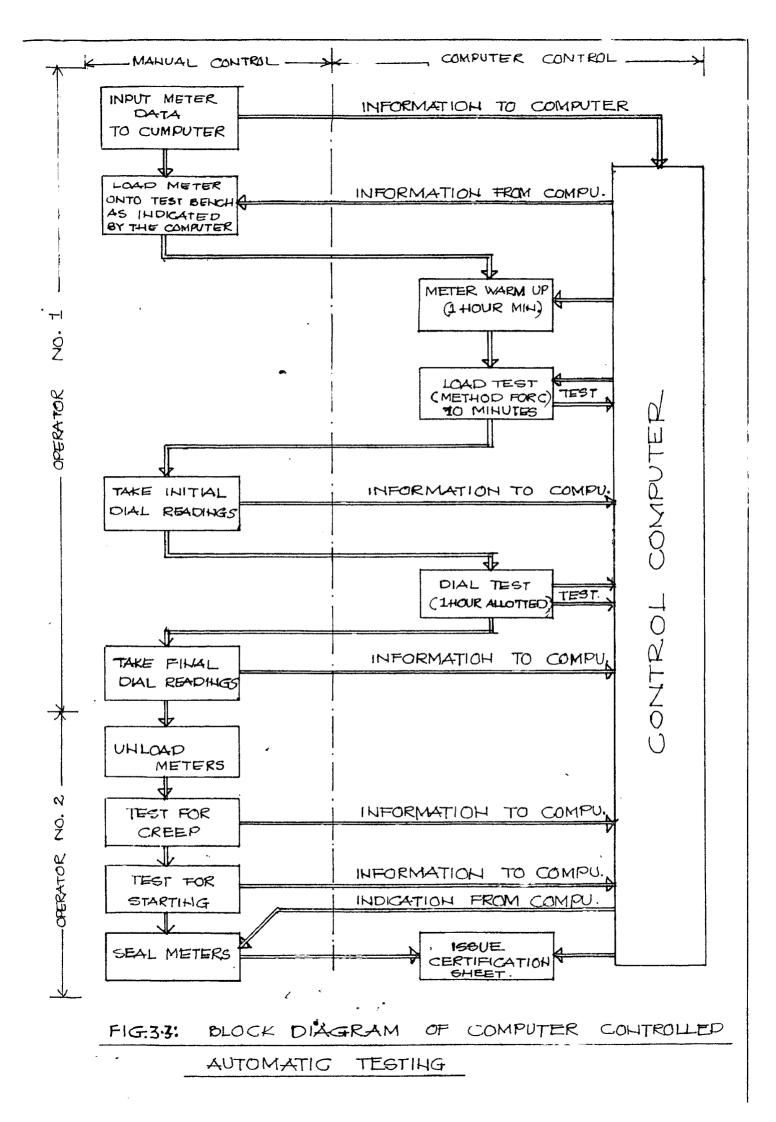

# 3.2.1. Automatic watthour Meter Test Equipment Controlled by Electronic Computer

This test equipment was developed by Japan Electric Meters Inspection Corporation<sup>8</sup>. It can test 60 meters per hour with an accuracy within  $\pm$  0.2%. The equipment consists of meter desks, electronic computer, a controller, power supplies and a control panel. The errors of the meters are measured by comparing the speed of their discs with that of a precision rotating standard, and then calculated and printed automatically according to the computer program. The comparison of speed is carriedout by counting the standard pulses from the precision rotating standard by means of a counting system shown in Fig.3.2. On receiving the 'start 'signal, gate G is opened and counter starts. Whenever, one or more signals of the meter come to the 'OR' circuit, its output signal is synchronised with the front edge of the standard pulse through the 'AND ' circuit and sent to the computer as the 'Interruption 'signal. The computer calculates the error and registers it. A definite count is preset so that the last bit (14th bit) of the counter means the 'stop ' signal. The count preset is determined keeping certain consideration in view.

(11) Comments : The measuring accuracy of the equipment is determined by the following :

- (a) Counting accuracy,

- (b) The accuracy due to the fluctuation in one revolution of the standard,

- (c) Variation in the power supplies and ambient conditions.

Efficiency is determined by the time taken for self heating which is more than 30 minutes.

Advantages : The advantages which make the equipment economical, reliable and easy to maintain are :

- (a) Saving of detectors and their change- over switches

by using the horizontal driven detecting device.

- (b) Saving of counters by using computer counting system.

# 3.2.2. Computer Controlled Automatic Testing

D.F. Ashton<sup>9</sup> proposed that automatic meter testing can be employed which will assist the testing staff. This may be controlled through a testing cycle based on either method B or C (described in section 2.3.) by a digital computer which will also handle stores records and meter documentation, including production of the certification sheet entry. Figure 3.3. shows how the test operators work in conjunction with the computer controlled test bench. This system based on a work study, shows that two operators could handle 86,000 meter per annum and that in testing time of 10 minutes ( statutory time for methods B or C ) each operator could perform the manual tasks for eight meters. A layout for an automatic test bench which will realise this productivity has also been suggested by the author. Batches of four meters only are loaded alternatively onto two moving belts which carry the meters through the stages of meter warm up, automatic load testing and computer supervised. The control console would have a purpose built keyboard arranged to assist the operator in correctly inputting the computer data in shortest possible time. The programming of the computer would be arranged to indicate to the operators what their next function should be i.e. load meter to indicated position, take dial reading, etc., etc. The operators would remain in overall control by failing to perform the next indicated step. At this point. testing would continue on those meters at present on the test cycle but the bench would not advance to the next operation and

would revert to a standby condition of meter warm-up until the missing operation hadbeen completed.

.

After all testing has been completed, the computer indicates whether the meter is satisfactory or not. Meters successfully passing all the tests will then be sealed and will be returned to stores. Meters failing test will not be sealed and will be returned to the calibration section alongwith a print out of the full test results.

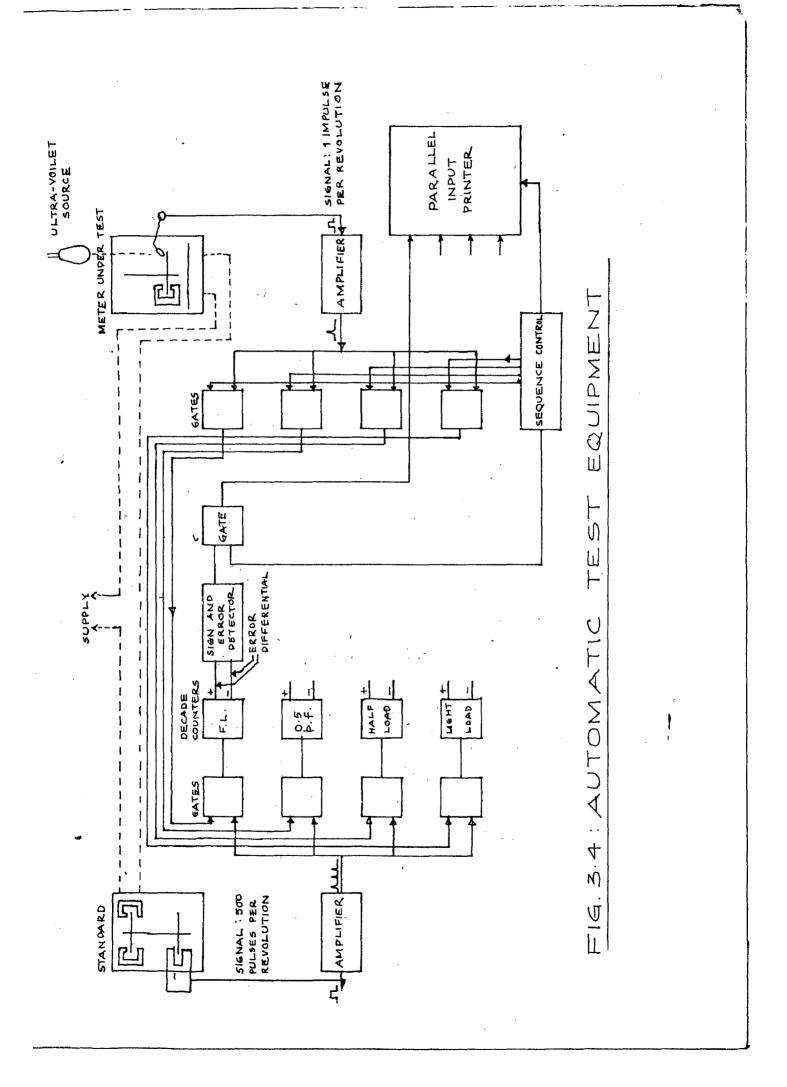

#### 3.2.3. Automatic Test Equipment

An installation at Bexleyheath<sup>60</sup> comprises two duplicate test equipments, or precalibrators which can be operated independently to feed four dial test benches each carrying 60 meters in single rows (Fig.3.4). The precalibrators contain normal power units, control and monitoring instruments appropriate for testing a single meter. Before the test cycle can commence a quick set adjustable probe is adjusted to the disc of the meter under test to obtain information and control the test programme.

The supplies to both meters are provided conventionally except that four separate outputs, solenoid controlled, permit the pre-set loads to be applied to both meters in series according to the selected programme. The rotating standard meter is fed via variable ratio current and voltage transformers adjusted so that its speed is equal to the theoretical speed of the test meter.

The test cycle is programmed by the meter under test, controlling the load changes and error determination. An output

signal for each revolution is taken from the meter disc, each signal representing a definite stage in the testing programme either starting or stopping the registering counters or advancing the programmes so allowing comparison at each of the four loads.

The standard meter, with whose speed the speed of the testmeter is compared, is fitted with a photo-electric transducer and provides for a count of 1000 impulses if the meter under test is error-free. Deviations from this count represent errors in units of 0.1%. The count is displayed separately for each load and percentage error for each is printed out.

The signal output from the standard meter, after amplification, is fed to four separate decade counters giving a four figure display for each load. A parallel entry printer is used to record the meter errors and its prints out the difference between the signal count and 1000.

The printer takes its information from the counter systems via a sign and error detector. Print out is at the end of the programme cycle when the four load counts are displayed.

The equipment has built in facilities for reducing the number of loads taken so that if a detailed investigation at one load is needed repetitive checking at this load can take place. For stability and other investigations this is a useful way to obtain vital information.

3.2.4. Fully Automatic Meter Testing System

E.F. Haerdle<sup>10</sup> has described a fully automatic meter testing system which -

- 1) can test upto 40 meters simultaneously and fully automatically,

- 2) works with test records in the form of punched cards,

- 3) and produces the meter records necessary for administration, so that manual punching is no longer necessary and the meter records are kept automatically.

The test arrangement consists of the meter installation as such, the electronic control equipment, the recording and processing apparatus for the measured data, the punched tape output. The meter test installation is conventional in principle. The electronic control assembly consists mainly of the American Packard Bell 250 computer instructions to be followed and the operands necessary for the computing are stored in a single store. The store consists of a number of magnetostrictive comductors, in which the information is propogated in the form of a pulse train of torsions of the wire. At the two ends of each wire there is a write out coil and a reading coil to transform electric pulses into torsion pulses and to perform reverse transformation respectively.

A special electronic device records the measuring data coming from the test equipment in the form of pulses and processes them in such a way that they can be taken over by the stores in the computer. The method of measurement used is an energy comparison method. If the meter is correct, the number of pulses counted in an electronic counter are equal to the rated value.

While the first group comprising 20 meters is tested, the 20 meters of the second group are preheated in their suspension frames. This is followed by no-load and half-load tests.Meanwhile the photoelectric scanning heads- one for each meter are adjusted to the sensitivity needed for reading the marks on the meter head. When the maximum sensitivity of these heads has been adjusted the computer starts the precision test to interrogate continuously the calibrating meter aswell as the meters under test.

# 3.3. COMMENTS ON STROBOSCOPIC TESTING

Stroboscopic methods have the advantage of giving an instantaneous indication of the disc speed and may be used with an unmodified meter since the normal disc markings suffice.

These methods can easily be used for calibration purpose. The use of these methods for the calibration of high loads reduces calibration time while providing the requisite accuracy at these loads. It is, however, unsuitable for low load calibration. To cope with the diverse range of meters encountered in Area Board Test Rooms, precision current and voltage transformers and pulse test division techniques will extend the range of the method.

However, there are complaints that stroboscopic testing causes eye strain and operator fatigue, and to avoid these complaints a cathode ray tube display has been developed. Pulses derived from markings on the disc of the rotating substandard are filtered to produce a sinusoidal wave. This is used to produce a circular trace on a C.R.T. Pulses from the disc of the test mater intensity modulate the trace giving a dashed pattern on the circle. If the test meter disc is rotating at the same speed as the rotating substandard disc then the pattern is stationary. This method is favoured by one particular manufacturer where the test meter pulses are obtained from an optical detector working on the serrated disc edge. In this scheme the C.R.T. has now been replaced with a ring of light emitting diodes for greater reliability.

#### CHAPTER-4

#### NEW SCHEMES FOR AUTOMATIC TESTING

In this Chapter author has proposed a few schemes for meter testing incorporating automation in various degrees. The advantages and limitations of each scheme have also been dealt with.

Generation of pulses from the meters is achieved by placing uniformly spaced marks on the meter discs and using photo devices. This aspect has been discussed at length in the next chapter.

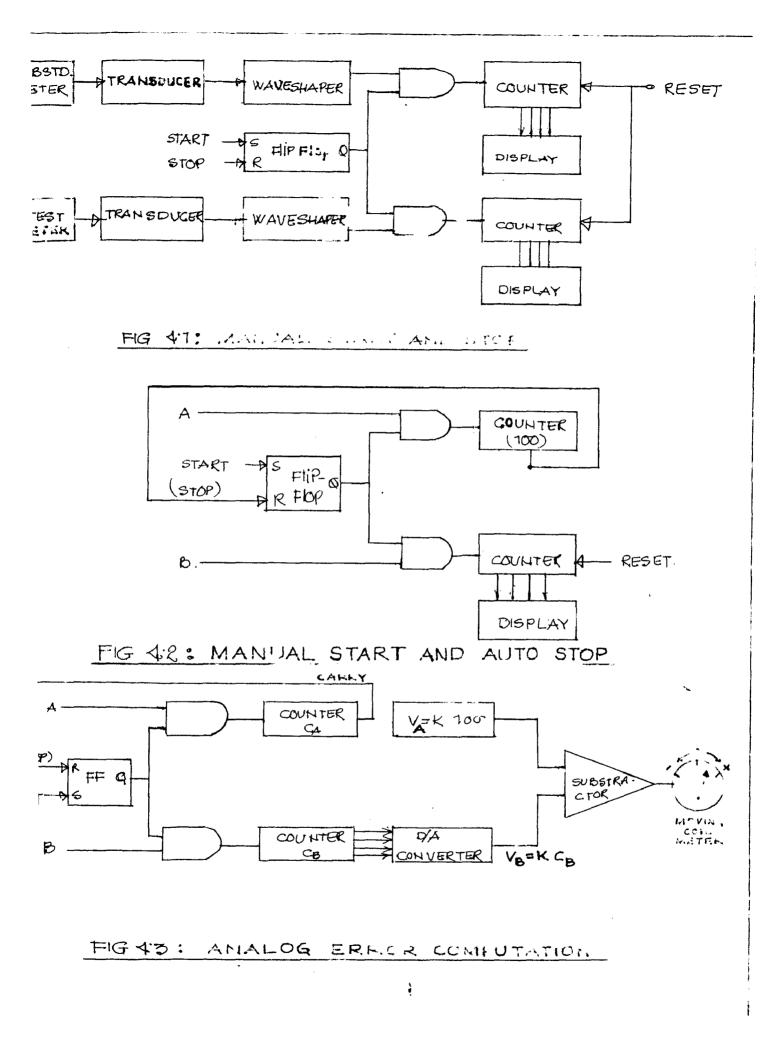

## 4.1. MANUAL START AND STOP (Fig. 4.1)

The pulses obtained from the substandard and test meters are counted by electronic counters over a fixed period of time. Computation of error from the two counts is done manually. The meters which are started manually, are also stopped in the same manner after the predetermined time has elapsed.

This scheme, as also the following schemes, involving electronic counting eliminate the error in reading and recording of number of revolutions by the human operator(s). As the number of revolutions of the meters for a fixed period of time may at many times not be an integral number, human operator is unlikely to read it accurately. Also different operators may read the same amount as different ones.

#### 4.2. MANUAL START AND AUTO STOP

In this scheme pulses from test meter are counted corresponding to a prefixed (say 100) number of pulses from the substandard meter. The two meters are started manually and at the same time flip-flop is 'set 'externally (Fig.4.2). Setting the flip-flop enables two 'AND' gates and the pulses from two meters start accumulating in the counters  $C_A$  and  $C_B$ . As soon as the counter  $C_A$  registers 100 pulses not only the counter  $C_A$  but also the flip-flop gets 'reset '. Resetting of flip-flop in turn disables the 'AND' gates to prevent further entry of pulses to the counters. Error in magnitude and sign is then computed manually. Whereas the resetting of counter  $C_A$ by the last pulse makes it ready for the next cycle, counter  $C_B$  should be manually 'reset ' to zero before commencing the next cycle.

This scheme has the advantage of automatic extinction of counting of pulses.

#### 4.3. ANALOG ERROR COMPUTATION

The basic philosphy of this scheme is similar to that of the last one but it incorporates one more degree of automation. Here the error is computed by analog circuits. The complete costing scheme is shown schematically in Fig.4.3. The digital count  $C_B$  is converted to a proportional analog voltage by using D/A converter. A voltage equivalent to 100 pulses of the substandard meter is generated. The two voltages are fed to an analog substractor and the difference (error) is displayed on a moving coil meter. As the error may be of either polarity, the meter required is a centre-zero meter. Obviously, for the next cycle counter  $C_B$  will have to be reset to zero.

This scheme reduces the involvement of human operator by one more degree as the error is now computed by analog circuits. Accuracy of the system depends on the accuracy of the D/A converter and the accuracy with which the voltage proportional to 100 pulses of the substandard meter is generated.

# 4.4. DIGITAL ERROR COMPUTATION USING SUBSTRACTOR AND COMPARATOR

The pulses obtained from the substandard meter A and test meter B are counted. These counts are then compared in a digital comparator. Three distinct outputs for the three possible conditions are available from the comparator. These outputs are used to drive polarity indicators as well as to give command to a digital substractor to perform substraction if the two counts are unequal, and to carry no operation in case the two counts are same (Fig. 4.4)

# 4.5. DIGITAL ERROR COMPUTATION WITH NEGATIVE AND POSITIVE ERROR DISPLAYS

Unlike the other schemes discussed so far in this Chapter the markings on the two meters are not identical. The substandard meter is marked to give pulses ( A in Fig.4.2.) 1000 in number or its multiple for a fixed number of revolutions

of its disc. The test meter pulses (B) are divided using dividers to give one pulse, C, for the same number of revolutions. AND-1 gate remains enabled during the high state of pulse C and allows the pulses from the substandard meter to be counted and digitally displayed. If the test meter speed is smaller than that of the substandard, the reading of counter is the error ( negative). In case the speed of the test meter is meater than the speed of the substandard meter the count will have to be substracted from 1000 to give error. To perform this function additional pulses from a clock are added to the counter  $C_A$  to make the count 1000. These clock pulses, also allowed to be accumulated in counter CB, are digitally displayed to give the positive error. The addition of pulses is performed during the subsequent low time of the pulse train C. As soon as the count in counter  $C_A$  becomes 1000 negative error display gives zero reading and the carry resets a flipflop to disable AND-2 gate to stop: the feeding of any more pulse to the two counters automatically.'Not' gate keeps the AND-2 gate disabled during high times of pulse C. For the next cycle the counters are required to be 'reset ' to zero and the flip-flop need be set.

This scheme eliminates the error in reading analog meter by the human operator.

## 4.6. DIGITAL ERROR COMPUTATION WITH ERROR AND POLAPITY DISPLAYS

This scheme has been practically realized by the author and is shown in block schematic form in Fig.4.6. Details of the

scheme are discussed in the next chapter.

This scheme has a common display for the magnitude of error ( for positive and negative errors ) and separate indication for polarity of the error.

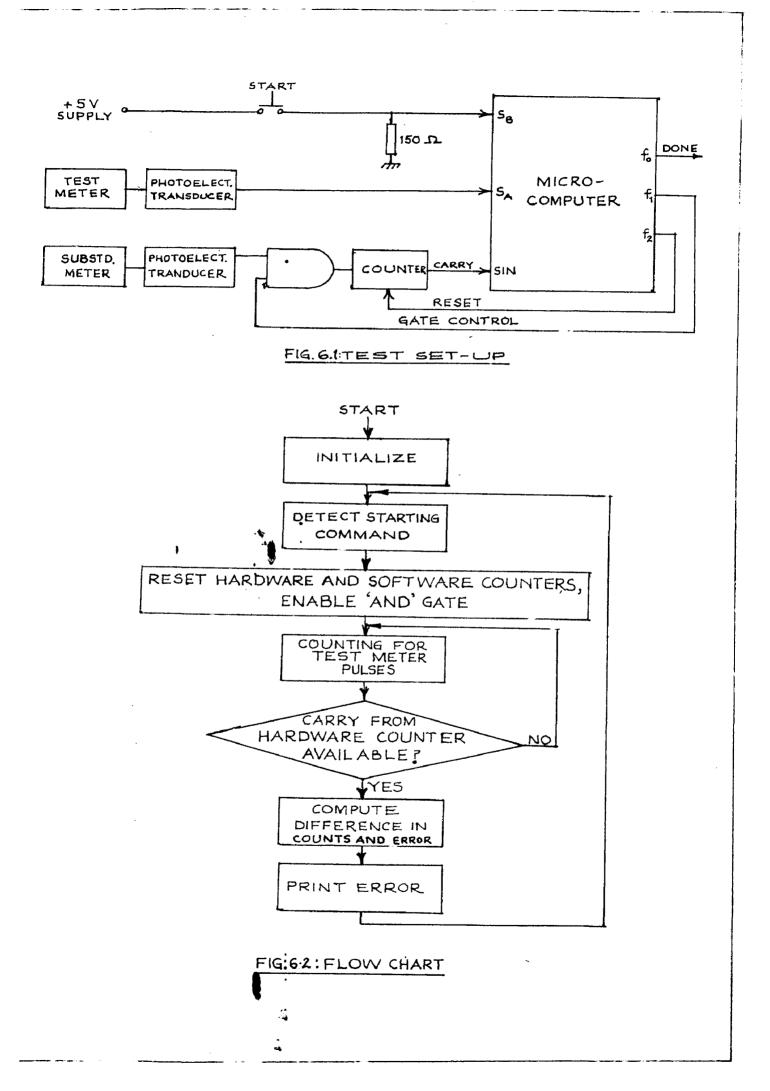

# 4.7. MICROPROCESSOR BASED TESTING

In this scheme author proposes the use of microprocessor for the testing. While a fixed number of pulses from the substandard meter are counted by a hardware counter, the actual corresponding number of pulses from test meter are counted in the microprocessor. The error in magnitude and sign both, is then computed by the software of the microprocessor. This scheme has been discussed at length in Chapter-6.

## CHAPTER-5

#### A DIGITAL SCHEME DEVELOPED FOR AUTOMATIC TESTING

From the various schemes discussed in the preceding chapter, the author has chosen the one described in section 4.5 for practical implementation. The scheme adopted is fully automatic one with inevitable manual start and anautomatic stop. Digital circuits have been chosen for the computation and display of error. Compared to the analog circuits, the digital circuits have greater resolution, better accuracy, lower susceptibility to noise, and avoid parallex and other errors in reading.

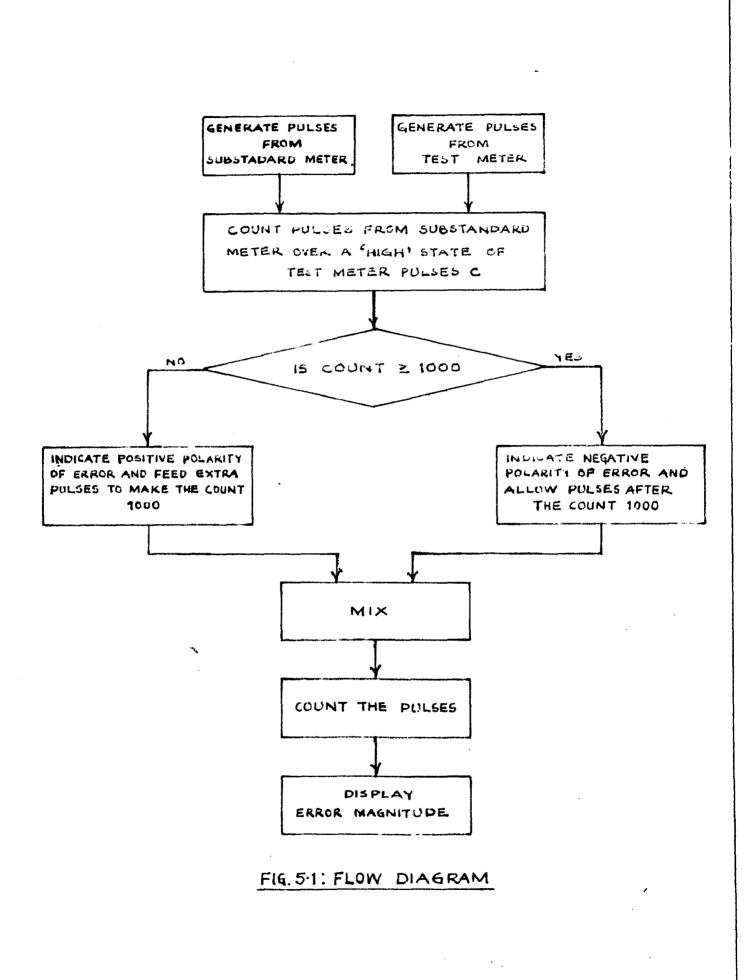

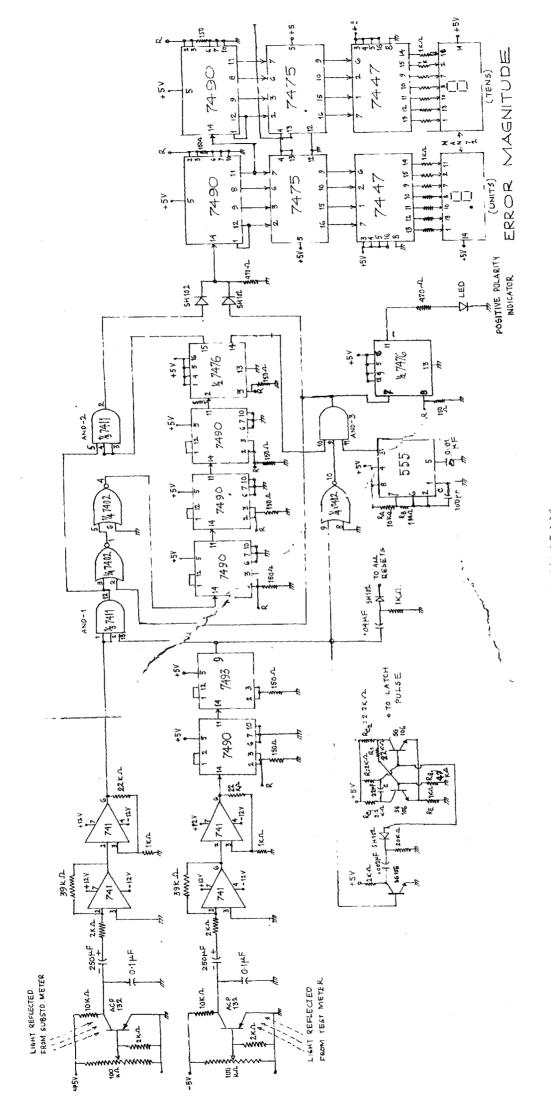

### 5.1. PRINCIPLE OF TESTING

The basic principle of the testing scheme is shown in 'flow-diagram' form in Fig.5.1. Pulses from the substandard meter (A) are counted during 'high' state of the test meter pulses (C). If the substandard meter pulse count is equal to 1000, the test meter does not have any error, relative to the substandard meter. The difference of actual pulse count from 1000 represents the magnitude of the error in the units of 0.1%. In case the pulse count is greater than 1000, pulses after 1000th pulse are counted and displayed and at the same time negative polarity of the error is also indicated. However, if the pulses are less than 1000 in count, extra pulses from an external clock are fed to make the count 1000. These extra pulses which represent the magnitude of the error in this case are counted and displayed.

Provision for positive polarity indication of the error has also been incorporated.

#### 5.2. ELEMENTS OF TESTING SCHEME

The design of an accurate measurement circuit requires a systematic appraisal of the complete system consisting of primary stimulus ( the physical quantity to be measured), the transducer (used to convert the primary stimulus into an electrical signal) and the signal conditioner ( used to make the transducer output appropriate for the following stage)<sup>11</sup>.

#### 5.2.1. Primary Stimulus

As the speeds of the two induction discs are to be compared, the primary stimulus here is angular speed.

### 5.2.2. Transducer Assembly

The transducer consists of light source and phototransistor (ACP 132). Light from two sources is focussed on the edges of the two discs which are marked in a specific manner. The substandard meter circumference is divided into hundred equal parts and of these alternate ones are pointed by black water-based paint. The substandard meter disc edge is painted black except for one part ( equal to that of the test meter). The reflected light from the discs is focussed using double convex lenses on two phototransistors. Whenever there is painted portion in line of incident light, there will be no reflection of light from the disc on to the phototransistor and hence it remains 'off '. Unpainted or bare portion of the disc reflects light to cause an increase in the collector current. Thus mechanical rotation of the discs is transduced into electrical pulses 50 per revolution of the substandard meter disc and 1 per revolution of the test meter disc.

## 5.2.3. Signal Conditioners

## (a) Amplifier:

As the pulses obtained from the phototransistor are of very low magnitude, they have to be amplified (Fig.5.2). This has been performed by using an operational amplifier- IC 741. The connections<sup>12</sup> are shown in Fig.5.4<sup>(1)</sup>. Because the phototransistor is located at some distance from the succeeding stage (amplifier), induced pick-up in long leads and unavoidable ground loops give rise to signals which are many times greater than the transducer output signal. In an attempt to minimize the unwanted signals, shielded wires and proper earthing have been used to correct the transducer to the amplifier.

# (b) Zero-crossing Detector<sup>12</sup>

Because of the switching time the phototransistor gives a slowly varying output voltage. To convert this slowly varying voltage into an output having an abrupt waveform, occuring at a precise voltage ( zerohere), a zero crossing detector is used (Fig.5.2)^.

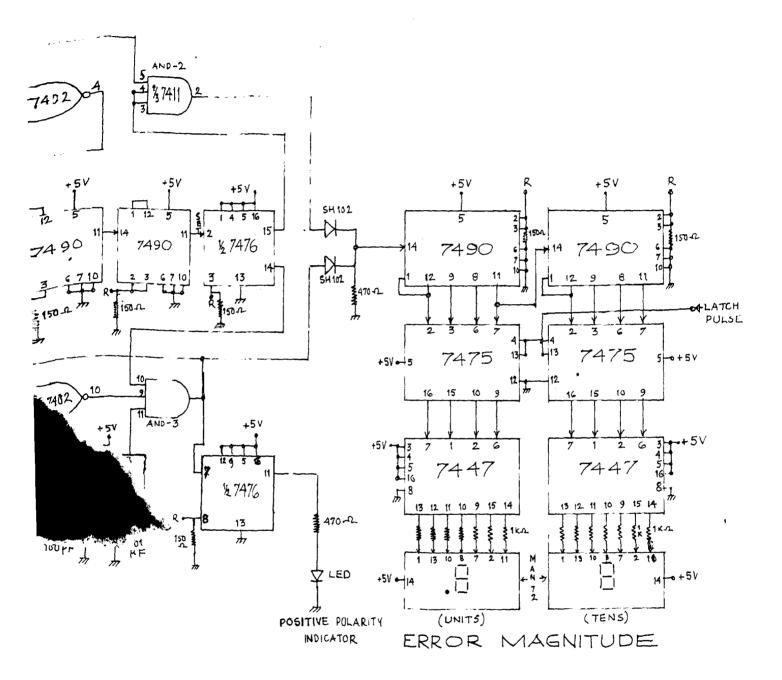

## 5.3. WORKING OF TESTING SCHEME

The testing has been performed for 20 revolutions of the test meter. As shown in fig.5.2 pulses from the test meter (B) are divided by 40-using IC 7490 followed by IC 7493 in divide by

10 and divide by 4 mode respectively - to give one pulse for 20 revolutions of the test meter. During a ' high ' time of the pulse train C. AND-1 gate remains enabled and allows the pulses from the substandard meter to pass through it. If the substandard meter pulses are more than 1000, 1000th pulse sets flip-flop-1, which in turn enables AND-2 gate and disables AND-3 gate. Output pulses of AND-1 gate one now counted with the help of two cascaded decade counters<sup>13</sup> (as the error is generally in the units of few percents). Pulse count is decoded using IC 7447 and the count (error) is displayed on 7-segment LED,. To avoid the flickering display, latches ( IC 7475 ) are used as temporary storage between the counters and decoders/drivers. Information present at its input is transferred to its output when the clock is ' high ' and the output follows the data input as long as the clock remains 'high '. When the clock goes ' low ', the information ( that was present at the input at the time of transition) is retained at its output until the clock is permitted to go high. The first pulse after 1000th sets flip-flop-2 to drive a LED to give negative polarity indication.

In case the pulses in the specified period - high time of pulse train C - are less than 1000, flip-flop 1 remains reset ( all the counters and flip-flops are reset at the instants; of 'low' to ' high ' transition of pulse C and input to AND-3 gate from flip-flop -3 remains in ' high ' state. For the' low' state of the pulses C, AND-3 gate is enabled and clock pulses start accumulating in the counter and divider (  $\frac{4}{1000}$  ). As soon as enough pulses from the clock have accumulated in the

divider to make its count 1000, flip-flor-1 gets ' set' and stops further accumulation of pulses in the counter and divider. The clock pulses, representing error, are finally displayed. The display represents the error in the units of 0.1%. First clock pulse out of AND-3 gate is used for positive polarity indication in the similar manner as used for negative polarity indication. Timing diagram shown in fig.5.3 helps in better understanding of the sequence of operations.

### 5.4. DESIGN CONSIDERATIONS

The only elements requiring elaboration of design are clock, monostable (delay) circuit, and power supplies. Other components being in directly usable digital integrated circuits no require/discussions here.

### 5.4.1. Clock

IC 555 connected in free-running mode serves the purpose of a clock<sup>14</sup>. Its connections are shown in Fig.5.5. The external capacitor C charges through  $R_A \& R_B$  and discharges through  $R_B$ only. The charge time ( output high ) is given by

$t_1 = 0.693 (R_A + R_B) c$

and the discharge time (output low ) by

$t_2 = 0.693 (R_B) C$

Thus the total period is given by

$T = t_1 + t_2 = 0.693 (R_A + 2R_B) C$

FILSTA TIMING LA. FA

The frequency of oscillation is then

$$f = \frac{1}{T} = \frac{1.44}{(R_A + 2 R_B) C}$$

The clock is needed here to feed extra pulses during a time period equivalent to 20 revolutions. As the maximum speed of the integrating meters at full load can be 100 r.p.m. the time for 20 revolutions is 12 seconds. The provision is required to be made for feeding at the most 100 pulses ( as the error can never exceed 10%) during 12 seconds. Thus sets the lower limit of clock frequency approximately equal to 8.5 Hz. Taken

$$R_{\rm A} = 10 \, {\rm Km}_{1}$$

$R_{\rm B} = 1 \, {\rm Mm}_{1}$

$C = 100 \, {\rm pF}_{1}$

These parameters result in clock frequency of 7 K-Hz. Such as high frequency is chosen to make the error computation and display time after the time of 20 revolutions minimum.

# 5.4.2. Monostable (Delay) Circuit

Latches are used between counters and decoders/ drivers to permit the transfer of counter output to decoder/driver and display after the/addition of requisite number of clock pulses have been added to make the count 1000. This is achieved by enabling the latch after a delay of 100 times the time period of clock pulses after the instant of ' high' to ' low ' transition of pulse train C. Design of the delay circuit<sup>15</sup> (Fig.5.5) is as given below:

Supply voltage, V = + 5 volts transistor used are SG 106(NPN) Taken  $I_{e}(sat.) = 2 m A$ When transistor To is conducting  $R_{c_2} + R_E = \frac{V_{cc}}{I_{c}(sat_{c})} = \frac{5.0}{2 \times 10^{-5}} = 2.5 \text{ Km}$ Taken  $R_E = 1 K \Omega_{-}$ ,  $R_{02} = 2.2 K \Omega_{-}$ Similarly when T<sub>1</sub> is conducting  $R_{c1} + R_{E} = \frac{5.0}{2 \times 10^{-3}} = 2.5 \text{ K}$ Taken  $R_{e1} = 2.2 K_{-}$ Now  $I_{B2} = \frac{I_{c2}}{h_{c2}} = \frac{2 \times 10^{-3}}{20} = 0.1 \text{ mA}$  $R_1 + R_{c2} = \frac{5.0}{0.1 \times 10^{-3}} = 50 \text{ K}$ Taken  $R_1 = 47 K \Omega$ R<sub>B</sub> = 22 K\_A Delay required =  $100 \times T = 0.69 RC$  $0r \quad 0.69 \ RC = \frac{100}{7 \ x \ 10^3}$  $RC = \frac{100}{7 \times 0.69 \times 10^3} = 0.2 \text{ sec.}$ Taken  $R = 2 K \Omega$ C = 22 prF

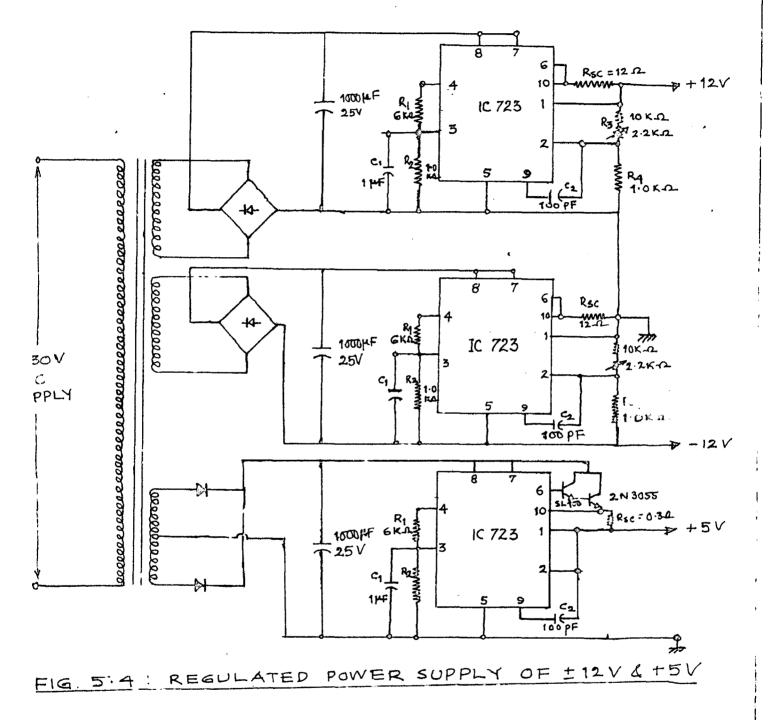

# 5.4.3. + 5 Volts Regulated Power Supply (Fig.5.4)

A 5-volt, 2 amp. regulated power supply is required for the TTL ckts. Mains voltage (230V a.c.) stepped down to 12-0-12 volts with the help of a 1150 (30 SWG)/120 (20 SWG) transformer with secondary centre tapped. This voltage is then rectified using a full wave rectifier to 9 volts. The unregulated voltage is regulated using IC 723. Design of regulator circuit<sup>14</sup> is given below:

Reference voltage for A 723 = 7.0 V (specified) Required output voltage,  $V_{out} = 5.0 V$

•• Vout = Vref

$$\frac{R_2}{R_1 + R_2}$$

5 = 7.0 x  $\frac{R_2}{R_1 + R_2}$

or,  $R_2 = 2R_1$  (1)

To avoid poor regulation at low  $V_{IN}$  and high dissipation at high  $V_{IN}$  the current drain from  $V_{REF}$  should not exceed 2 m<sup>A</sup>.

•

$$R_1 + R_2 = \frac{7.0 V}{2 mA} = 3.5 K_{\Omega}$$

(2)

Taken  $R_1 = 1.5 \text{ K} \Omega$ ,  $R_2 = 3.3 \text{ K} \Omega$

To extend the load current range upto 2 amp. two  $\beta$ - cascaded transistors (SL 100 and 2N 3055) are connected at pin 6 of the regulator.

- - --- ---

**.**...

.

Resistence for short circuit protection is given by

$R_{SC} = \frac{V_{BE(off)}}{I_{logd}} = \frac{0.6 V}{2 A} = 0.3 \Omega$ Taken  $C_1 = 0.1 \ \mu F$ ,  $C_2 = 100 \ p^F$

# 5.4.4. \* 12 volts power supply (Fig.5.4)

A stabilized supply of + 12 V required for supplying the operational amplifiers was also designed and fabricated. Two additional windings of 140 turns each are placed on the same transformer as used for the + 5 V supply. Voltages detained from these windings are rectified and filtered then and fed to two identical regulators. Design of each regulator circuit using IC 723 is as given below :

Vref. = 7.0 volts ( specified ) Vout = 12 volts short circuit current, I load = 50 mA Voltage at pin 3,  $V_3 = V_{ref} + \frac{R_2}{R_1 + R_2}$

$V_3 = 1.0^{V}$ Taken

1.0 = 7.0

$$\frac{R_2}{R_1 + R_2}$$

Taken  $R_1 = 6.0$  Knand  $R_2 = 1.0 \text{kn}$  $(R_{sc} \text{ short circuit resistance }) =$