# SPEED CONTROL AND SYNCHRONIZING OF ALTERNATORS USING PHASE LOCKED LOOPS

## **A DISSERTATION**

Submitted in partial fulfilment of the requirements for the award of the degree of

MASTER OF ENGINEERING in

ELECTRICAL ENGINEERING (System Engineering & Operation Research)

> By PRAVIN PRADHAN

DEPARTMENT OF ELECTRICAL ENGINEERING UNIVERSITY OF ROORKEE ROORKEE (INDIA) November 1978

## <u>CONTENTS</u>

| 1          |                                                                                                                 |     |

|------------|-----------------------------------------------------------------------------------------------------------------|-----|

|            | CERTIFICATE                                                                                                     | 1   |

|            | ACKNOWLEDGEMENT                                                                                                 | 2   |

|            | ABSTRACT                                                                                                        | 4   |

|            | INTRODUCTION                                                                                                    | 5   |

| Chapter 1: | Evolution and Survey of Recent<br>Developments (Locked Loop Drive<br>Systems and Automated Synchroni-<br>zers). | 8   |

| Chapter 2: | The Developed Systems-Description<br>and Fundamental Considerations.                                            | 20  |

| Chapter 3: | The Developed Systems-Design<br>Considerations and Experimental<br>results.                                     | 37  |

| Chapter 4: | Conclusions                                                                                                     | 46  |

| Appendix-A | Linearized Model for Phase<br>frequency Detector (PFD).                                                         | 4१  |

| Appendix-B | Stability of the Phase<br>Locked Loop System (PLS).                                                             | 54- |

| References |                                                                                                                 | 57  |

/

Page

-

## <u>DEDICATION</u>

This work is dedicated to the memory of Khutu Mian who spent more than fifty years of his active life as a Synchronizing operator in the "Salawa" Power station of Meerut District. Khutu personofied in himself the genius of Indias technological skill - a mind innovative and uncontaminated with borrowed and half -bakede ideas, a hand gifted with creative craftsmanship and applied disinterestedly with consummate passion, and an attitude fiercely independent, dominating and primordially, blunt in action. From Khutu more then from any one else has the authors imbibed and inherited some of the finest tradition of the 'Indian Technological Spirit' and he is indeed grateful to him.

#### CERTIFICATE

CERTIFIED THAT the Dissertation entitled "SPEED CONTROL AND SYNCHRONISING OF ALTERNATORS USING PHASE LOCKED LOOPS" which is being submitted by PRAVIN PRADHAN in partial fulfilment for the award of the Degree of Master of Engineering in Systems Engineering add Operations Research - Elect**mic**al Engineering of the University of Roorkee, Roorkee is a record of the student's own work carried out by him under my supervision and guidance. The matter embodied in this dissertation has not been submitted for the award of any other degree or diploma.

This is to further certify that he has worked for a period of  $\underline{9}$  months from  $\underline{FEB}$ , 1978 to <u>OCTOBER</u>1978 for preparing this dissertation at this University.

(M.K./VASANTHA) Reader, Department of Electrical Engg., University of Roorkee, ROORKEE(U.P.)INDIA

ROORKEE November 10,1978. L

## <u>ACKNOWLEDGEMENT</u>

The author expresses his sincerest gratefulness to Shri M.K. Vasantha, Reader, Department of Electrical Engineering, University of Rocrkee, Roorkee and his guide iand Supervisor for the present work, for all the help and guidance that he has received so spontaneously from him throughout the period of this work. It was indeed a privilege to have worked under him.

The author would be **siggulerly**ungrateful if he does not record his indebtedness for the help rendered by M/S Amber, P.K. Srivastava, Ashish Saxena, R.S. "Dneer all presently students of the University. To M/S Kishan Lal, Tiwari, Chaman Lal, C.P. Ganguli, Shoogan Giri, Phool Singh, Rishi Pal all members of that vital force the technician Cadre brigade- without which no technological project worth the salt can be implemented in real flesh and blood, the author cannot but be grateful.

To that symbol of dynamic dangerous living "The UST9803" "the author offers his salutations for the many tasks it has

accomplished with speed and 'efffciency.

RODRKEE

homi Prote

.

. . .

· .

Dated: November 10,1978.

(PRAVIN PRADHAN)

.

#### A\_B\_S\_T\_R\_A\_C\_T\_

In the present work, an integrated and fully automatic speed control scheme, has been conceived and implemented, based on the concepts of both frequency and phase locking. Perhaps for the first time, an attempt has been made to develop, a fully automated Synchronizer for power station applications utilizing the techniques of both frequency and phase locking. In the area of implementation new types of hib precision frequency difference and phase difference detectors have been developed and fully tested. The incorporation of dual locked loops in the control scheme is primarily dictated, from considerations of improving significantly the system stability. Endowed with orders of accurrcy within .002 percent and considerably improved levels of repeatability and stability, the developed control scheme promises to be extremely versatile with applications ranging from high precision regulation of large capacity motors to automated Synchronizing of multi motor systems in addition to that of fully automated alternator Synchronizers. A unit feature of the dissertation is the development of an experimental version of the PLDS for research investigations and educational purposes.

INTRODUCTION

1

The impetus for the present work has come from the realization that the real potential of the Phase Locked Loop and its associated techniques still remain to be exploited in the fascinating and versatile area of precision electrical machine control system. And this becomes evident, even from a cursory survey of the literature pertaining to this area. For how else is it explainable that as yet, the phase Locked Loop and its associated techniques has not been applied to the problem of fully automated Synchronizing of power station alternators. The other major shortcomings which becomes strikingly evident from a survey of the Existing literature of Phase-Locked Loop Drive Systems (P.L.D.S.) are:-

1. This technique has still to make in roads into the commercially important area of 'precision Industrial Electric Drives' involving the use of large DC and AC motors.

2. The problem of instability of PLDS's particularly in the lower speed range has still to be over come even in the case of sub-fractional horsepower servo systems. Ĵ

It was primarily to fill up these important Lacunas in the application of Locked Loop Control Techniques in general and of the Phase Locked Loop in particular the present work was initiated.

With these ends in view the first chapter of the present work deals esecntially with the evolution pattern which has taken place or is exp ected to take place in the allied areas of Locked Loop Drive System and fully, automated Synchronizers. It also presents, the salient details of the significant literature available in this area of development, Chapter 2 deals with the fundamentals and detailed description of the developed schemes and Systems. In particular a detailed description is given of the integrated and fully automated Synchronizers for power stations based on the application of the Locked Loop Techniques. Details circuit action are also spelt out in respect of the phase difference and frequency difference detectors, developed specifically for this scheme . In the third chapter the Emphasis is on design considerations and performance features based on actual experimental investigations and test results.

The concluding chapter summarizes the important conclusions of the present work discusses critically the scope and potential for further work and spells out the specific areas in which such precision drives can find applications. In particular , it predicts radically new areas of application of such systems which are rejevent for the "region" development programmes of the developing countries. ?

#### CHAPTER-I

#### EVOLUTION AND SURVEY OF RECENT DEVELOPMENTS (LOCKED LOOP DRIVE SYSTEMS AND AUTOMATED SYNCHRONIZERS)

#### 1.1 Perspective And The Evolution Pattern

The evolution and development pattern of solid state "Locked Loop Contrd Systems" and in particular of the "Phase Locked-Loop Drive Systems" (P.L.D.S.) has followed the familiar trend of technological advancements that have taken place in recent years, in the area of precision and automated Electrical machine controls in general and of Drive Systems in particular. The initiating impetus for the advancement originates essentally either from major break-throughs achieved in material and component hardware developments or from heavy reductions in the per unit cost of components developsd primarily for applications in conventional areas. This is closely followed by application and adaptation of already existing techniques in the allied areas of signal processing and logc implementation. This in turn leads to new developments in the above techniques with the property aim, of eleminating those new peformance shortcomings that are invariably associated with the advanced systems undergoing development. With performance optimized by an order of

magnitude now-where approachable by the existing conventional systems the emphasis is next placed on achieving a high level of "in built " system reliability. Side by side new testing procedures are evolved and standardized for effecting critical performance evolution of developed systems. The next major step in the evolution pattern stems from the new levels of performance and geometry that are attained with the advanced systems. These levels of performance and geometry ultimately lead to the opening up of radically new areas of applications not in the least possible by the conventional systems. This inturn, brings forth developments oriented towards specific applications in specialized areas.

On the basis of the technical survey carried out in the broader area of precision and automated electrical machine control systems and of Locked Loop control systems in particular, the following salient points emerge in respect of the evolution pattern of automated Locked Loop control systems. This study includes in addition to the conventional research literature scruting acritical survey of both the manufacturers and the users literature in respect of hardware advancements testing techniques and technical specifications of specified application areas really inneed of automated

and high precisi n facilities:-

(1) The initiating impetus for the development of Locked Loop electrical machine control systems came from the availability of in expensive phase Locked Loop in monolithic IC form for the first time in 1971.

(2) The reported developments are confined to the area of "Phase Locked-Loop Drive Systems " using monolithic PLL IC's.

(3) The P.L.D.'S's developed fill yet are essentially servo systems with the associated motors being by and large DC sub-fractional hor sepower motors.

(4) The development pro achieve till yet is still confined to the second stage-nemcly, the development of PLDS's with only the already existing techniques of signal processing and logic implementation.

(5) The Locked Loop Control Systems have as yet, not made in roads into the field of Automated Synchronizers for power stations which goes without saying is an area that is not only of the greatest practically . importance but is also at the same time an application in which the need for total reliable automation is a very genuine one.

e.

(6) The existing state of the art of automated Synchronizers is still at the experimental stage and that too **is** confined to the application of conventional techniques like those of Electomagnetic slip frequency measrment and frequency come face difference comperators using conventional analog methods.

(7) The development trend of Automated Synchronizers reported till yet is towards all "Solid State Equipment".

#### 1.2 <u>Survey-Recent Developments</u>

The first recorded reference in which mention is made regarding the possibility of using phase Locked Loop<sup>3</sup> for electric machine control applications is on article by R.A. Miller (2). This paper established for the first time the unique potential of PLLS's as comparators in digital control schemes for shaft speed and position parameters. However the major emphasizes in this work is towards bringing out the distinct superiority of digital control schemes for rotating electrical machines. In 1970 Volpe(3) established the view points for the first time, that a hysteresis Synchronous motor operates similar to a phase-locked loop as encountered till then in communication applications. From this view point a model adequately describing the motorsmetion

with respect to Synchronism and specifically the well known hunting characteristic phenomenon is presented, analysed and interpreted. It is also mentioned that a fair degree of experimental success was achieved in stabilizing a hysteresis synchronous motor using the PLL typeof control system. However, no details of this are spell out in the above work.

As already emphasized earlier it was not till the advent of in expensive digital PLL'S in monolithic I.C. form that real interest was aroused in the application of PLL's for electrical machine control. To Moore(4) goes the credit of having taken a pioneering step of suggesting a practical PLL control Scheme for a reel to reel tape drive using a MC4044 phase frequency detector IC for controlling a permanent magnet DC Motor. His other significant contributions in this work were as follows:-

(1) His estimated prediction to the effect that P.L.D.S.'s through the experience of locking on to a reference frequency can achieve speed accuracies of the order of .002% representing almost a hundred fold improvement over earlier methods of speed regulation.

(2) His prediction that Motors of any size can be controlled with this technique .

(3) His specific estimation that the digital PLL approach would be more economical as compared to conventional servo systems and particularly for high precession drive systems.

(4) His identification of specific and specialized PLDS application areas such as conveyor systems for materials handling, a computer peripheral drive or in general application where motors have to be Synchronized to each other or to an existing clocking signal.

(5) His performance comparison and evaluation of different types of digital phase detectors with particular reference to their important performance parameters.

(6) His suggestion of a specific practical schemwhich includes component details.

However Moores work does not contain any experimental details of the suggested scheme. His work was followed by Smithgalls' paper (5) in which an attempt was made to fill up the lacuna in Moores' work. The significant aspects of these work are as under :- (1) It describes a practical circuit of a PLDS implemented with an RCA CD4046 AD phase frequency detector . capable of effecting a 40:1 speed range.

(2) It presents a non linear model developed to describe the dynamic response of the control loop.

(3) It compares the response characteristics of the developed model with the measured response of the implemented system and reports the findings that the two "agree quite well".

(4) The developed and tested PLDS has a speed range from 120 RPM to 2520 RPM and speed regulation of less than.l percent at the lower end of the range and less than .02 percent over the majority **efost** range.

(is next important development in this area was reported by Sinha ad Baily (6) and the emphasis herein too was on the implementation side. The major points to emerge from this work **are** as under:

(1) It **is** reported that Moores'(4) suggested circuit using an MC4004 digital phase detector could not be made to operate with the speed encoder or in fact with any pulse train. (2) On the basis of the above findings a modified

scheme was tested using an analog phase detector a NE(SE)

565 PLL deep on a 1/50 H.P. DC Servo-motor.

(3) On the basis of the test results it is reported that the regulation accuracy is within .075% at a base speed of 2500 RPM. It is further predicted that accuracies of the order of about .002% would be achievable particularly at higher speeds.

(4) The performance of the loop has been further

evaluated. On the basis of two performance paramitters

namely fl and f<sub>c</sub> for kik both modes of motor catrol

i.e. both Armature andfield control modes.

(5) It is predicted that still higher orders of accuracy are attainable with a digital PLL using a more sophisticated design.

(6) It is further recommended that improved performance can be obtained by increasing the accuracy of the speed encoder and by eliminating the gitter in its output wave form.

Kenley and Boses' work reported in 1976(8) is perhaps the first and only attempt till yet in the application of phase Locked-Loop Techniques for effecting autatic speed regulation of relatively large sized

motors other unique features of this work are in respect of application of triacs as the controlæd rectifier elements and of ecentral of three phase Induction Motors same of the salient details reported in this work are as follows:-

(1) Experimental results of a 5 h.p., phase Locked Loop Induction motor drive system have been reported. The drive is based on the stator voltage control method using triac as the controlled rectifier elements.

The next significant work • which appeared in 1977(20) is perhaps the first theoretical work on the problem of PLDS instability at low speeds. The paper describes the operation of phase locked servo systems with the aid of a linear discrete model developed specifically for this purpose. Also discussed are the design problems speed variations and the extension of lock range, by Lag-lead net-works. In the area of stability analysis the condition under which the system remains stable has been quantitatively established. (For details please refer appendix B) on this basis an analytic expression has been derived for the lower speed limit. Also discussed are the design requirements and the main problems encountered in the design. These includes the system bandwidth, the lock range and the speed variation of the motor.

A year later (1978) (9) Bose and Jentzen have reported a digital speed ontrol method of a rectifier fed seperately excited dc motor incorporating phase locked loop technique. The salient features of this significant experimental work are as follows:-

1. A digital speed control method based on the phase-Locked Loop technique has been described which provides the advantages of freedom from drift and offset errors, immunity of the control circuit from transients and distorsion of supply voltage andpermits integration of the control circuit.

2. The essentially digital control action is effected by comparing the reference and the feed back frequencies in the phase frequency Detector and generating therefrom an analog error signal proportional to the phase difference of the input waves at the output of the loop filter.

3. The convertor uses cosine wave crossing method, the digital version of which is generated by programming a set of Read-only Memories (ROM).

4. A complete speedcontrol system employing a DC seperately excited 3/4 hp Motor has been designed and tested

in the lab and the system gives satisfactory performance.

The principle can be extended to three phase system with higher horse-power drives or to other phase controlled convertor circuits.

#### OF AUTOMATED SYNCHRONIZERS

The impetus for the development of automatic synchronising equipment came from the development of static Relays. Adamson and Moslands' Work (22). was perhaps the first work in the development of Synchronizing equipment using solid state devices. However his work along with those of Humpage & Co. (23), Malik & Co. (24) and Raj Kumar and Associates (25) suffer from the fullowing shortcomings.

1. They are all at best, only automatic check equipments for ensuring closure of circuit breaker by sensing the instant at which synchronizing is achieved within preset limits. These equipment are essentially used in conjuction with already existing manual or somiautomatic Synchronizing equipment.

2. Testing only under Laboratory conditions.

3. The comparator elements are all conventional and implemented by back dated components and techniques.

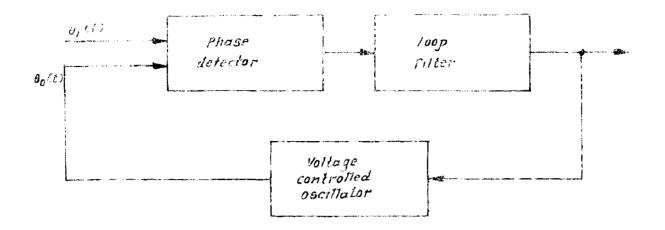

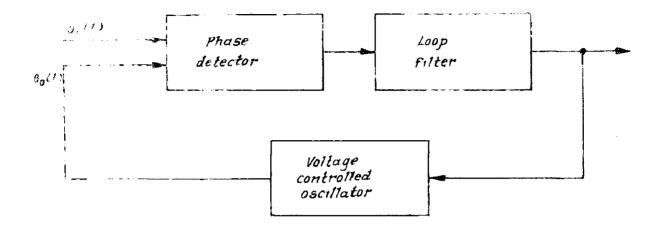

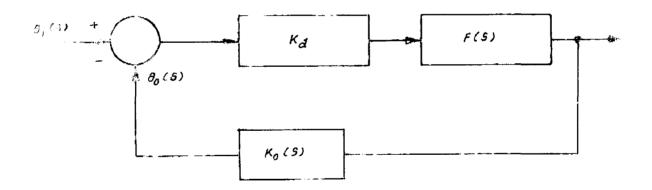

Fig. 3 Schematic diagram of the basic phase-locked loop.

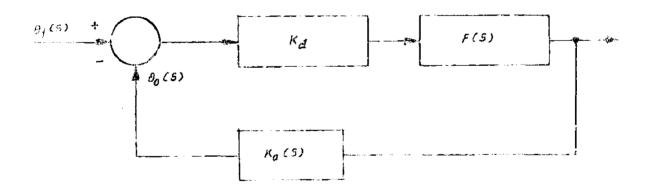

Tig. 4 Block diagram of the phase-locked loop.

#### CHAPTER-II

## THE DEVELOPED SYSTEMS-FUNDAMENTAL CONSIDERATIONS AND DESCRIPTIONS

#### 2.1 Introduction

PLL's havebeen used quite successfully in FM receivers, calour television, missile tracking loops space telemetry and AM demodelution. Gardner has described much of the history and potential applications of PLL's. Some of these application date back to 1930's when the systems were designed with descrete components. These were thereforelimited to such cases where better performance would justify cost of Sophisticated Electroni circuitary for the PLL. The situation has changed considerably since then and currently PLL's are available in the form of a single IC chip at a very low cost. This has led Engineers to find areas of applications of PLL's other than in communications.

#### 2.2 Theory of P.L.L.

Consider the schematic diagram shown in Fig.(3) The phase detector measures the phase difference between an input voltage  $v_i(t)$  and an output voltage  $v_o(t)$  to give an output.

$$V_{d}(t) = kd \left(Q_{i} - Q_{0}\right)$$

(1)

Fig. 3 Schematic diagram of the basic phase-locked loop.

.

ing 4 Block diagram of the phase-locked loop.

Where  $O_0(t)$  is the instantaneous phase of  $V_i(t)$ and  $\Theta_0(t)$  is the instantenous phase of  $V_0(t)$ .

This Error voltage is passed through a low pass filter to reduce Noise and Extraneous high frequency. components. The filtered voltage  $V_f(t)$  drives a voltage controlled oscillator (VCO) and alters its frequency in such a direction as will minimize the phase error. Thechange in the frequency of the VCO output may be related to the input  $V_f(t)$  through the linear equation  $\Delta W_0(t) = K_V V_f(t)$ ..(2)

Since f is the derivative of phase equation (2) may be integrated to obtain  $\Theta_{0}(t) = \Theta_{0}(0) + \int_{0}^{t} K_{0} V_{f}(t) dt$ .

The Loop is said to be locked when the error voltage remains steady and the frequency of  $V_c(t)$  is exactly equal to that of  $V_i(t)$ . The block diagram of the basic loop is shown in Fig.(4). It may be pointed out that the PLL is basically a non-linear feed back control system. But by assuming that thephase detector is linear and that the loop is locked, the response of the loop can be analyzed using laplace transforms and linear system theory. These assumptions are both justified and qualified by gardner(1). The block diagram of motor speed control is shown in Fig.(2) where for the sake of simplicity the motor is assumed to have a first order transfer function. It may be noted that the VCO

. 22

has been replaced by ashaft encoder the output of which is the integral of the speed and therefore analogous to the phase. The reference input may be a periodic wave form with frequency proportional to the desired speed.

The T.F. of theloop is given by

$$\frac{W_{m}(s)}{Q_{i}(s)} = \frac{sKF(s)}{s(1+sT_{m}) + KK_{0}F(s)}$$

Where K: Kd KA KM = gain of forward path.

It is evident the performance of the Loop will depend considerably on the transfer function of the filter F(s). One may therefore use various methods of control system design like root locus, Bode plots, Nichols chart or other linear control system techniques to ensure that the loop will be stable as well as sensitive.

## 2.2 The Locked Loop Alternator Synchronizing System:

Thesystem conceived and developed in the present work has the following salient features in respect of its control action:-

I. Two independent and distinct comparators are incorporated in the developed scheme- namely the Phase difference detector and the frequency error detector for the specific purpose of achieving fully automated high precision and rapid synchronizing and having an order

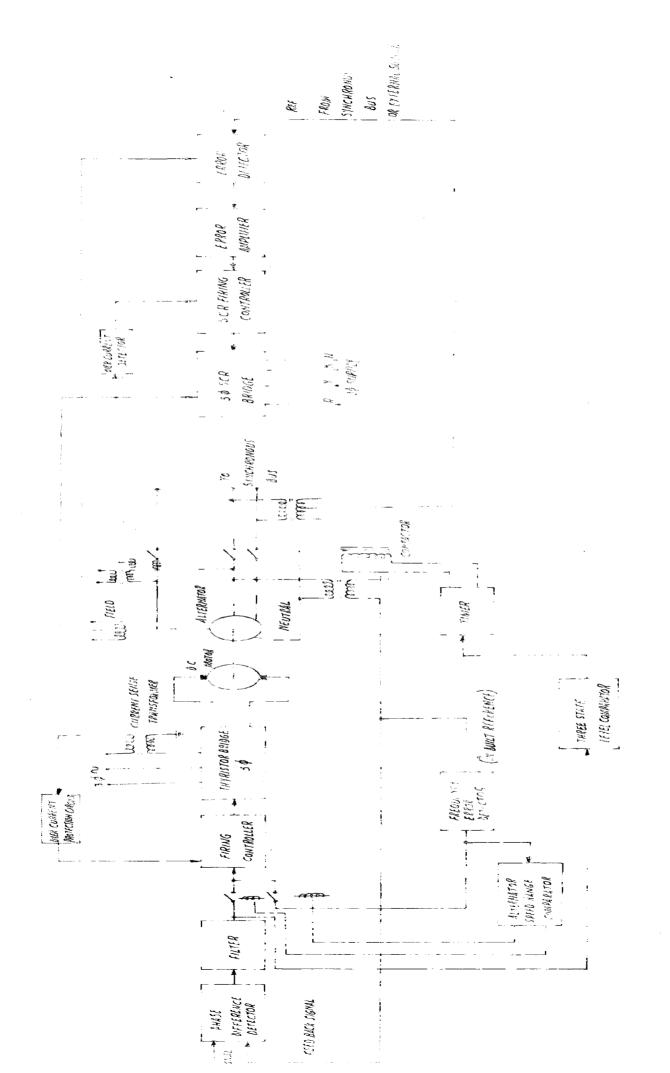

16.5 THE PHASE LOCKED ALTFRANTIOR SYNCHRONISING SYSTEM - BLOCK DIAGRAM OF DEVELOPED SCHEME .

of stability considerably better than that achieved by the conventional types of phasecomparators which have been used in earlier schemes.

2. As is clear from Fig.5, these two comparators are part of two distinct loops kbe of which could be appropriately termed as the phase Locked Loop (PLL) and the other as the frequency Locked Loop (FLL).

3. This performation being implemented in the present work on a 5 kw alternator set driven by a DC Motor but is applicable with the same order of precision topower station generators driven by all types of prime-movers by suitable modification in their existing speed control schemes.

4. In the present scheme as detailed in Fig.(5) the basic control action is initiated and implemented as follows:-

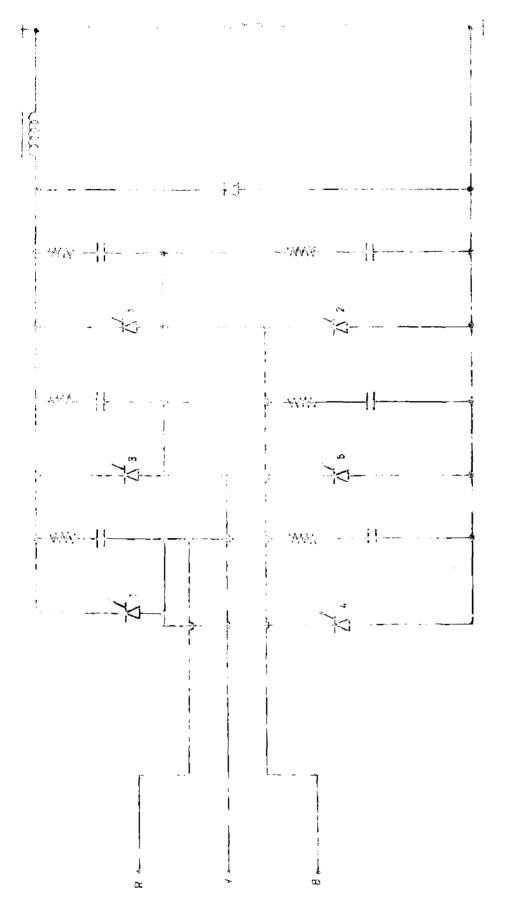

4.1 The DC Motor Alternator set is brought up to near about its synchronous speed by the action of the frequency Locked Loop which includes in addition to the frequency error detector, the firing controller and the three phase SCR bridge type conventor. The alternator output at reduced voltage level is used directly as the output frequency feed back signal.

4.2 With the 3 phase SCR convertor energized and firing controller supply switched on the in built' soft starting arrangement of the firing controller supersures controlled acceleration of the DC Motor through a limiting action.

4.3 The alternator set is brought up to a speed near about the synchronous speed under the exclusive influence of the frequency locked control loop.

4.4 At a preset value of speed (which is adjustable) near about the Synchronous speed (within  $\pm$  3 to 5%) which is a speed by the speed range comparator the frequency error detector is disconnected the frequency locked loop (FLL) goes out of action and is replaced automatically

by the PLL whose comperator is a phase difference detactor. The need for incorporation of the PLL, is justified on the following grounds.

4.3.1 It ensures perfect frequency control with an order of accuracy not at all possible by any other method or through the exclusive use of the FLL.

4.3.2 In additon it ensures perfect phase synchronizing as the PLL in herently compares the instantaneous phases and produces a proportional error signal .

4.4 The reference signal of the PLL is derived directly from the 50 Hz supply and the feed back signal is obtained from the alternator output.

5. The DC Motor controlled convertor has a built in over current protection arrangement.

6. A unique feature of the developed scheme is in pespect of the arrangement provided for automatic closure of the circuit breaker conteacts connecting the incoming machine to the station bus bars. The arrangement comprises a state level comparator acting in conjunction with a timer. This arangements operates on the premise that the contacts are closed only after it is ensured that the phase difference is within the set limits and that it is free of oscillations. The is e achieved by an automatic check arrangement which brings about the above check for a period of 4 to 5 seconds and only there after produces the energizing signal for the contractor.

7. The envisaged scheme also incorporates a closed loop static excitation system using a three phase SCR Bridge convertor and associated control circuits. The reference for this automatic voltage regulator is derived from the station bus and exercised the control is exercised by the error signal varying the SCR firing angle.

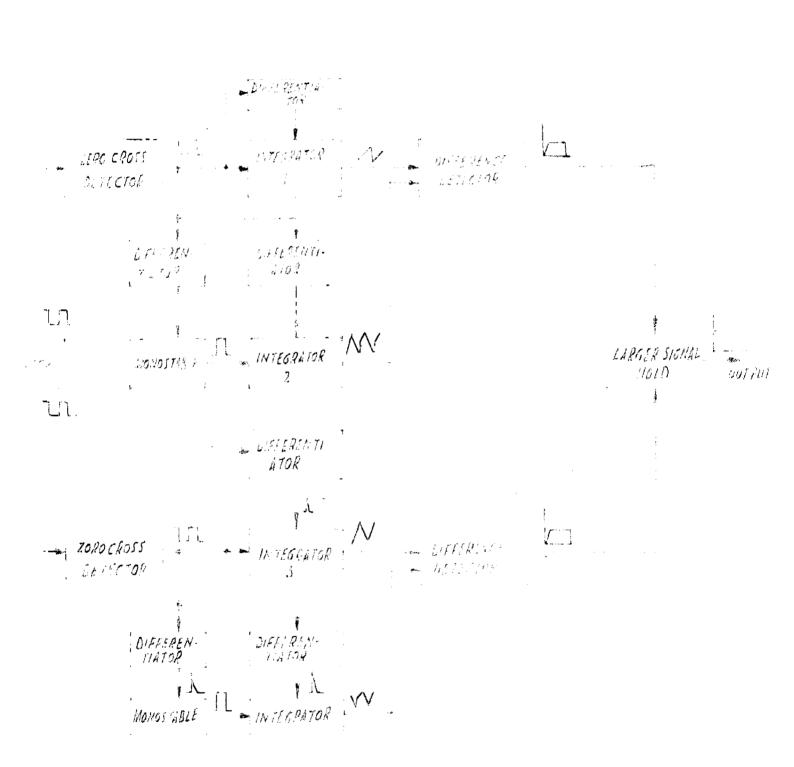

TG. 6 BLOCK SCHEMATIC OF THE DEVELOPED FAST FREQUENCY ERROR DETECTOR.

2.2.1 The Fast Frequency Error Detector:

This constitutes the main functional block of the frequency Locked Loop of the developed scheme. Its block representation is as given in Fig.(6). It generates a DC output voltage whose magnitude is a function of the instantaneous frequency difference, of the sinput signals. The complete scheme could be symmetrically split into two identical portions with each part consisting of a zero-cross detector, a pair of integrators a monostable and a difference detector. The action of this complete circuit is on the following basis:-

I. The feed back signal whose frequency is to be controlled is applid at the terminal marked "Signal input in Fig.(6).

2. The instantaneous frequency difference is measured by comparing instantaneously the half cycle period of the input feed back signal and the pulse duration of the monostable output signal which acts also as the reference timeperiod and therefore as the reference frequency signal.

3. The upper half of the circuitoperates for the positive half cycle of the input signal and is responsible for generating the DC cutput level which is a function of the instantaneous time difference of the two

signals for one half of the input cycle. The lower half of the the circuit operates during the negative half cycle of the Input Signal.

4. The difference detectors used are essentially differential amplifmer.

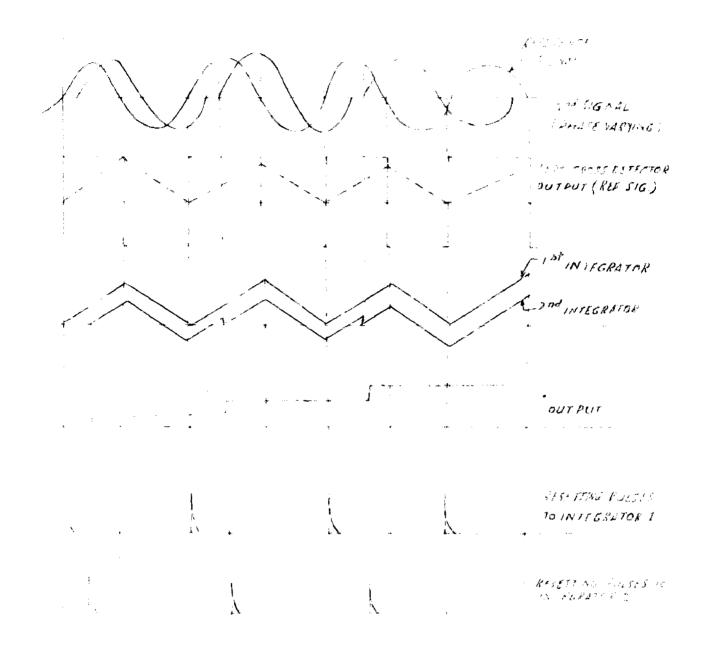

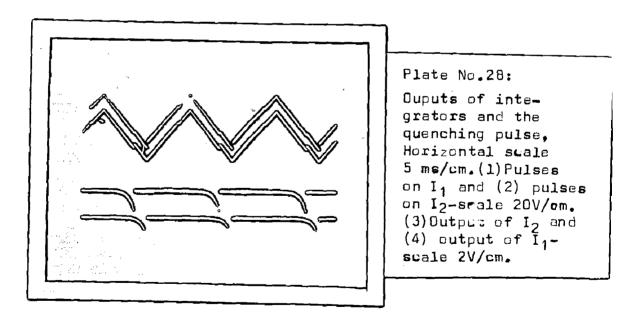

5. Each half of the input signal is converted into a squarewave (refer B & G Fig.7), by the Zero Cross detector which in turn is linearly integrated (refer E and J of Fig.7) by integrator 1. At the instant of commencement of integration by Integrator 1, the monostable is triggered by pulses (refer D and I of

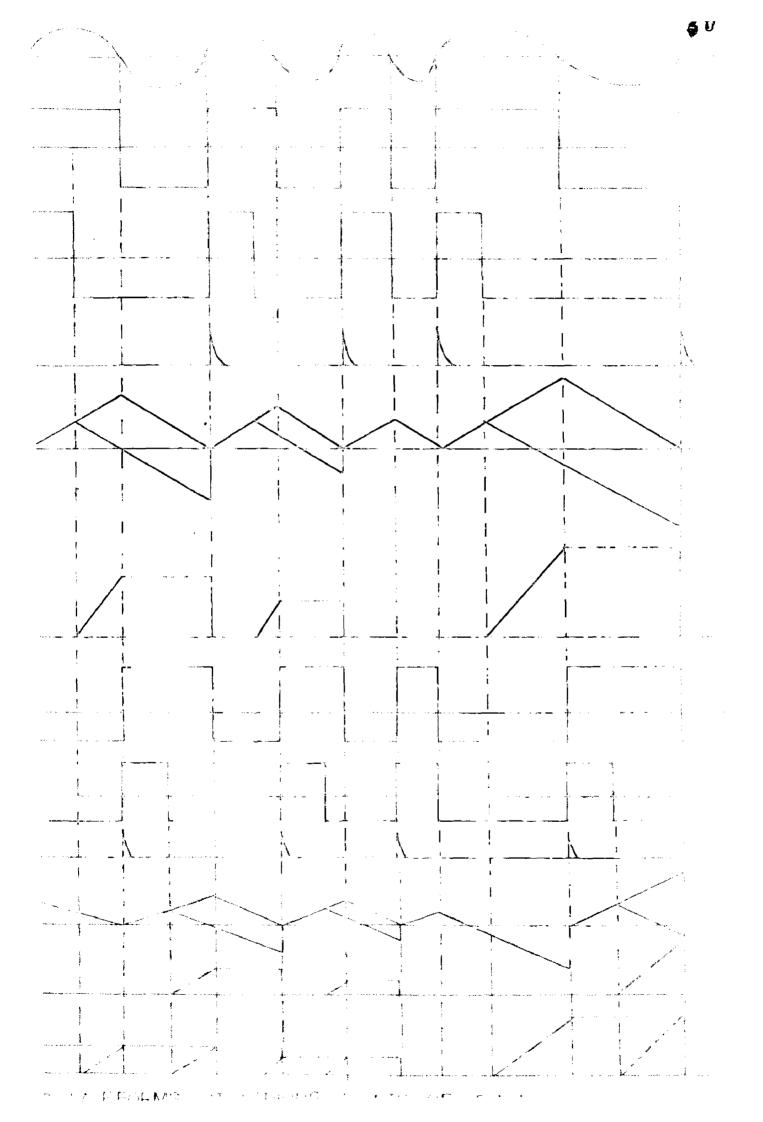

Fig.7) and its output is as shown in C and H of Fig.(7). The monostable output inturn is integrated by Integrat 2. The outputs of each of the two integrators are fed simultaneously to the difference detector(ref. E and J of Fig.7). The output of the difference detector is a DC Voltage which is proportional function of the instantaneou difference of the two frequencies of(refer F & K of Fig.7).

5. The outputs of the two difference detectors are simultaneously fed to the larger signal hold block. At every instant the larger of the two inputs to the hold circuit appears at its output terminal(refer L of Fig.7).

NAME ORMS AT VARIOUS POINTS OF THE PHASE COMPARATOR.

2.2.2 The Fast Phase Error Detector:

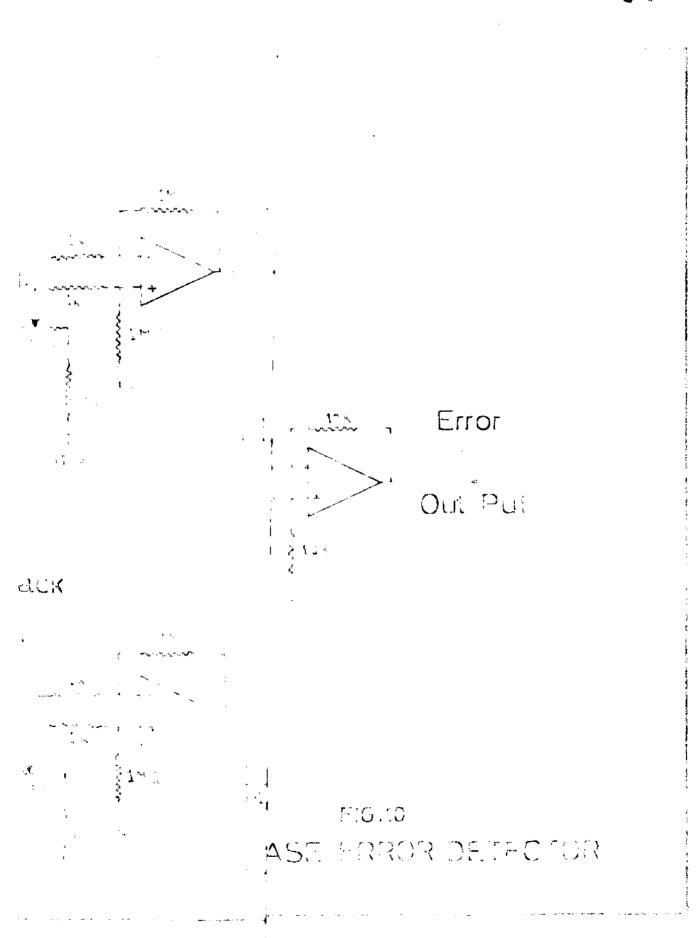

Representing the main functional block of the PLL in the developed scheme the fast phase error detector has been specifically developed to generate a linear DC output voltage Fig. represents the wavetform dragram of diagram of the developed detector and Fig.10 the complete circuit diagram. With reference to Fig.

The reference signal and the feedback signal are given to OP AMP<sub>s</sub>  $Z_1$  and  $Z_2$ , respectively, which act as zero crossing detectors producing square-wave outputs. Later these are converted to sharp pulses and applied at the gates of the field effect transistors. The integrators  $I_1$ and  $I_2$  are quenched by these respective pulses. The integrator  $I_2$  will be quenched depending upon the relative phase position of the feed back signal (Fig.9). The net difference of the two integrated outputs are available at the output as a de voltage (Fig.9). Since integrator  $I_1$  will always be quenched by its own pulse, the output voltage is proportional to the phase difference.

#### Salient Features:

The phase error detector, generates a dc output voltage directly proportional to the phase difference.

2. Since the use of a filter becomes unnecessary the response time of the PLL using this type of phase detector in a PLDS will be much less than the existing PLDS's.

36

, . 1

1 1 1

> , , ,

| n na hanna an an an an an an an an an ann an |

|----------------------------------------------|

|                                              |

|                                              |

|                                              |

|                                              |

|                                              |

|                                              |

|                                              |

|                                              |

|                                              |

|                                              |

|                                              |

|                                              |

|                                              |

|                                              |

|                                              |

|                                              |

· · · ·

# CHAPTER-III

# THE DEVELOPED SYSTEMS DESIGN CONSIDERATIONS AND EXPERIMENTAL RESULTS

# 3.1 Design Considerations:

The major design considerations which have been taken into account in the design of the various functional blocks of the developed integrated scheme are as under.

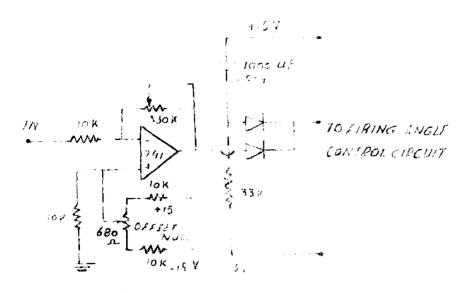

3.1.2 Of The Fast Frequency Error Dectector:

The circuit diagram of this developed detector is given in Fig.ll. The frequency error detector has been designed to meet the following specifications:-

- The response time should be the minimum possible from stability considerations.

- 2. The input frequency range should be of the order of 0 to 50 Hz.

- 3. The output voltage should be a pure DC signal whose magnitude must be a function of the instantaneous frequency difference of the input signals.

The developed frequency difference detector has been primarily evolved with a view to achieve the minimum possible response time so as to improve the overall stability of the control system. With this end in view the developed scheme samples over a half cycle period of the input frequency and is thereby an inherently more superior technique than the conventional detectors of the counter types in which response times are limited from accuracy considerations.

## SALIENT DESIGN FEATURES

- 1. The integrators designed have been provided with "in built" Synchronized resetting facilities to ensure good repeatability.

- 2. The monostables have been designed using IC 555 timer with a view to impart to them higher stability. Higher accuracy is ensured by the use of tantalum (Low Leakage) capacitors in their timima circuits.

3.1.3 Of The Fast Phase Error Detector:

The present phase error detector was primerily designed to eliminate the basic drawbacks of large response times arising from the necessity of providing low pass filters with other types of phase detectors including all types of PLL's available in Monolithic IC form.

FIG. 13 CIRCUIT D'AGRAM, OVER CURRENT PROTECTION.

In all phase detector being used till yet the necessisty for usinglow pass filtrs basically arose from the fact that the output signals wave form was of the pulse type. The technique of phase detection developed in the present work was so altered as to ensure an output signal which was essentially a pure DC signal whose magnitude was proportional to the instantaneous phase difference, of input signal. Some • of the major design considerajonof this improved type of phase detectors are as follows:-

- 1. The phase detection was conceived such that the instantaneous phase difference was converted into

- the level difference of the integrators in contrast to the other types of existing comparators based on gating techniques.

- 2. The resetting switch for the integrators are designed with FETS from considerations of improving the switching characteristics and simultaneously maintaining the linearity of integration.

- 3. The integrator timing capacitors are of the tantalum (Low Leakage) types in order to improve the linearity of integration. This is not possible withelectrolytic typeof capacitors.

. 40

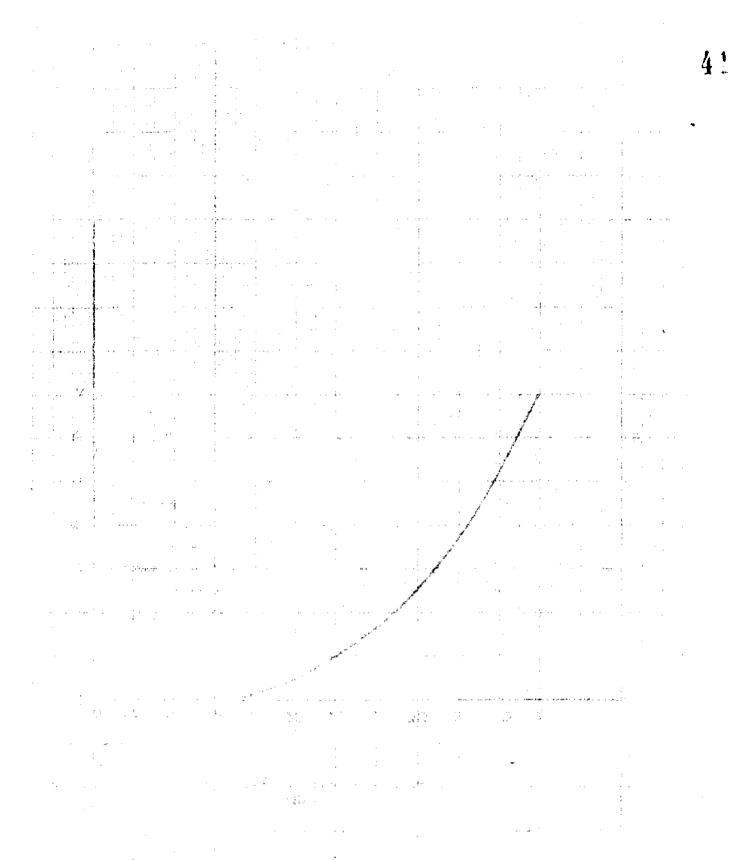

# LE IZ QUITITUT VOLTAGE VERSUE WERE PRESSUENCY

. . . ....

# 3.2 Experimental Results:

# Frequency Error Detector

The developed frequency detector has been fully tested under Laboratory conditions. The salient aspects of the test results are as under.

- The output response curve is as shown in Fig.17 for reference time of 10 m/seconds. This was tested by applying both Sinusoidal and square wave signals.

- 2. <u>Performance Parameters Details</u>:

imput impedance one M Ohm .

Output impedance 75 Ohm.

Frequency range 5 Hz to 45 Hz

Output voltage range 7 to 0 volts.

Supply voltage ± 15 Volts.

# Phase Error Detector

The circuit was tested by using 2 sinusoidal signals. The relative phase difference was varied upto 180°. A good linear relationship was observed between the output DC voltage and the phase difference (refer Fig.18). Even when the signal contained random noises the  $\cdot$  · circuit was found to be stable in operation.

. 43

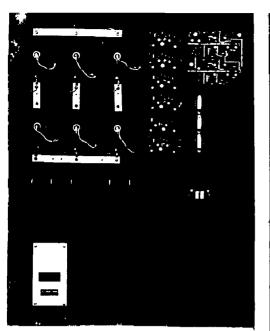

Plate 31: A view of the front panel of the "Experimental Generalized Locked Loop Drive System cum Automated Synchronizer developed at Roorkee.

Plate 32: SCR heat sinks used with the three phase fully controlled convertor of the developed ELLDS.

Plate: The author at work on the control panel of the ELLDS.

panel

Close up view of fest trenuency ebror detector.

Close up Volw of s.c.r. firing circuit

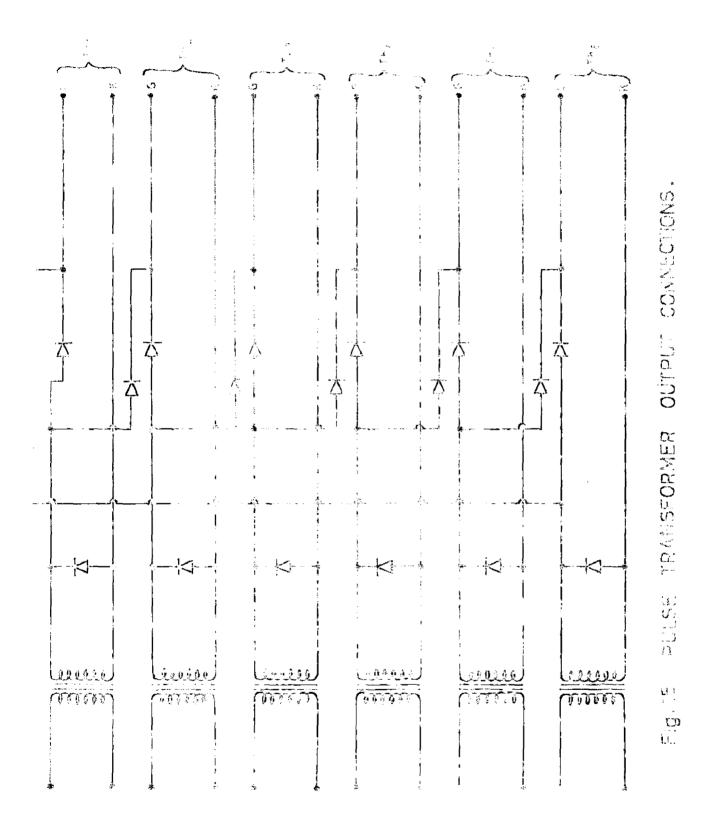

Plate 33: A close up view u of the miniature pulse transformer developed for firing 40 A SCR'S OF ELLDS.

### 2. Performance Parameter Details:

Input impedance 1 M- Ohm. Dutput impedance 65 Ohms. Supply voitage <u>+</u> 15 volts. Phase difference 0 to 180<sup>0</sup>. Dutput voltage 0 to 3 volts.

#### 3. Wave Fform Results:

The wave forms of the various circuits and systems tested under laboratory conditions are as shown in plate close Nos.19 to 30. These are in/ agreement with the theoretically predicted wave forms as detailed in Chapter II.

# 3.3 <u>Details Of "Experimental Generalized Locked Loop</u> <u>Drive Systems Cum Automated Synchronizer</u>"

The development of the above unit was taken up in the present work with a view to create facilities for advanced experimentation in the field of precision locked loop drive systems and fully automated Synchronizers. Some of its  $\sum_{i=1}^{nique}$  are as follows:

> 1. Sufficient flexibility has been"in built" into the unit so as to facilitate detailed experimental investigations on the ffect of comparators on the stability of locked loop drive systems".

> > .

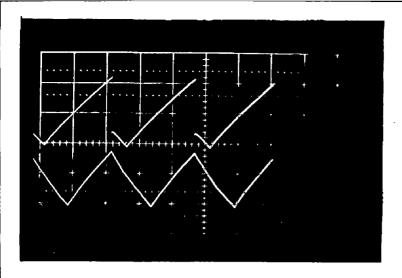

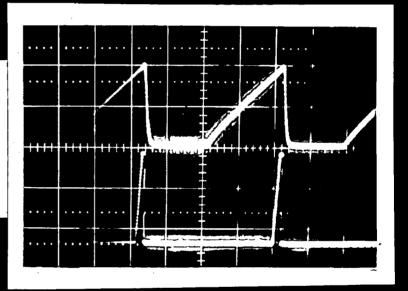

Plate 19.:Dutput of fast frequency error detector,imtegrators (upper trace of Integrator 2 & Lower of integrator 1 Horizontal scale: 10 m sec/cm vertical Scale:2V/rm per both,

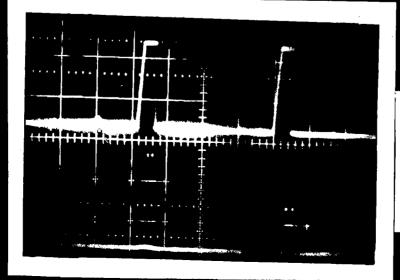

Plate 20: Output of difference detector of fast frequency error detector. Horizontal scale:20 m sec/cm vertical scale 2V/cm.

Plate 21: Final output waveform of the fast frequency error detector. Horizontal scels:20 m sec/cm vertical scale 50 mV/Cm.

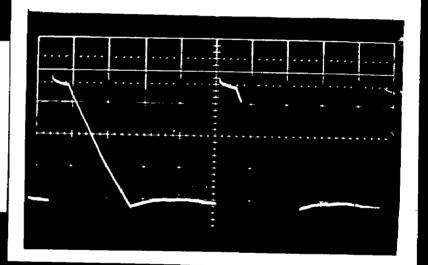

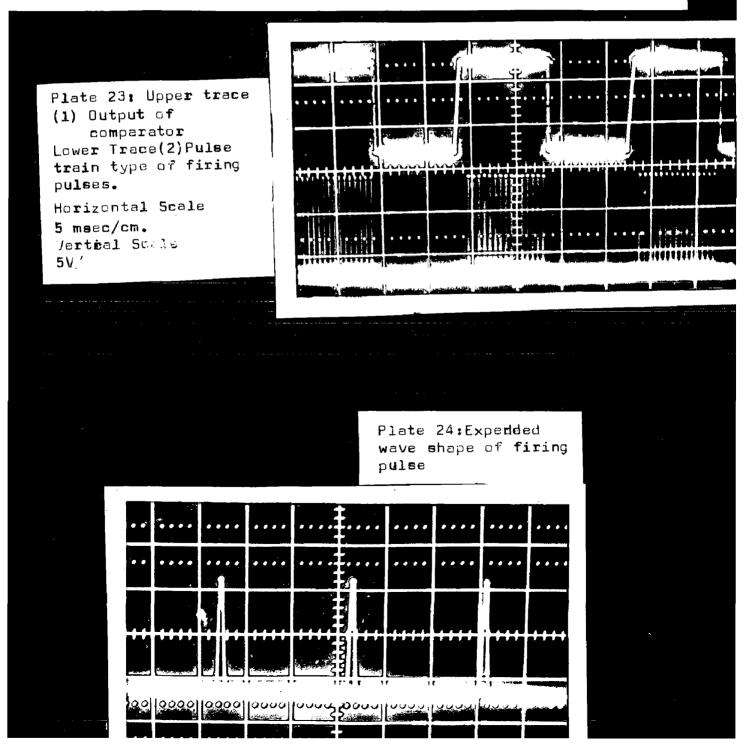

Plate 25:Upper Trace (1)Output of Comparator Lower Trace: (2)Final firing pulses at delay angle = 90° Horizontal scale 5 m sec/cm. vertical scale (1.. & .2) 5V/Cm.

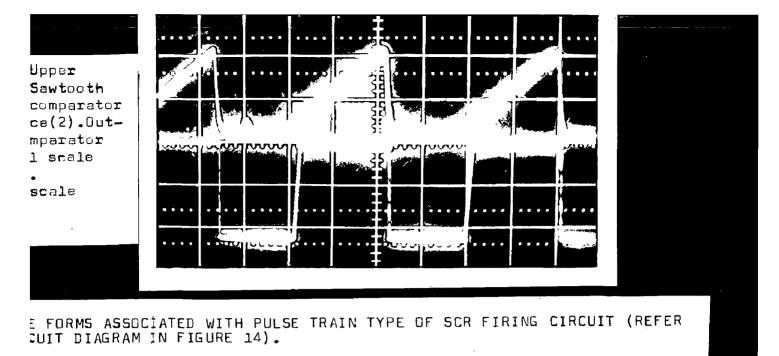

WAVE FORMS FOR VARYING FIRING DELAY ANGLES OF THE PULSE TRAIN TYPE OF FIRING CIRCUIT

Plate 26: Upper trace (1) Sawtooth input to comparator Lower trace (2):Final firing pulses at delay angle equal to 176<sup>Q</sup> (Approx.) Horizontal Scale 5msec/cm. vertical scale(1)2V/cm (2) 5V/Cm.

Plate 27: Up er trace (1) output of comparator Lower trace (2) final firing pulses at delay angle = 45° Horizontal scale :5 msec/cm. Vertical scale 5V/Cm.

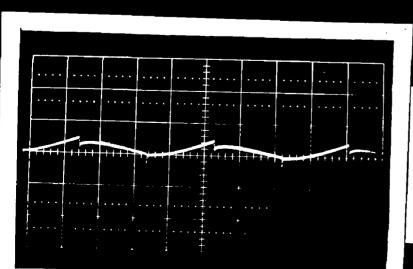

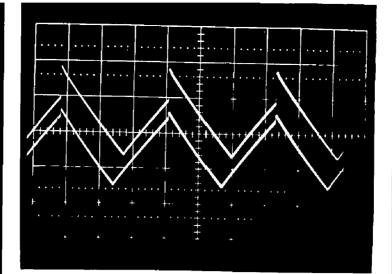

Plate 29: Output waveforms-horizontal scale 5 ms/cm.(1) output of phase detector with zero reference shown belowscale 5 V/rm.(2) Square wave inputs to I1 and I2- scale 10v/cm.(3)Output of I2 and (4) output of I1 - scale 2 V/cm.

Output wave shapes of the two ingegrators of the fast frequency error detector at 60Hz

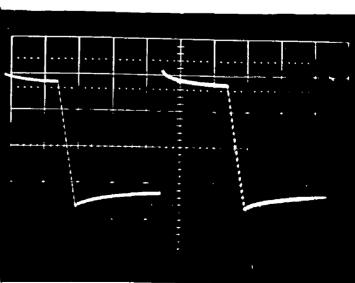

Dutput of Difference Detector, of Fast Frequency Error Detector. At 40Hz.

FAST FREQUENCY ERROR DETCTOR PRINTED CIRCUIT BOARD.

- It would permit experimental performance studies of different types of closed loop solid state drives.

- 3. It would open up the challenging area of detailed experimentation and development of fully automated synchronizers for power station.epplications.

~,

# CHAPTER-IV

# <u>CONCLUSIONS</u>

# 4.1 <u>Major Assetts Of the Fully Automated Dual Locked-Loop</u> <u>Type of Alternators Synchronizer:</u>

With the incorporation of two independent and distinct Locked - Loops the fully automated synchronizer in herits the following significant merits:-

1. Theelimination of PLL and its replacement by the FLL at speeds other than near about the synchronous speeds eleminates the problem of harmonic locking.

2. It improves the systems stability by minimizing the transient circulating currents.

3. It would bring out heavy reduction of the turbine foundation transient stress levels. It is of interest to note that the basic cause of these high stresses is attributable to the draw backs inherent in manual and semi-automatic synchronizing methods which are in use currently.

4. It would bring about considerable reduction of the transient during the synchronizing operation these in turn would ensure the following improvements and advantages. 4.1 It would eleminate considerably the possibility of grid failures arising from imperfected synchronizing operation. 47

4.2 It would lead to a **dsfinite** increase of the power capacity of the existing power systems by increasing the transient stability limit.

4.3 By in-corporating such Synchronizers there would considerable economy in the design of the trans-

# 4.2 Specific Recommended Application:

With overall system stability considerably improved the high precision Locked Loop Drive Systems are admirably suited for the following applications:-

As fully automated Synchronizers in Power stations.

2. For all drive applications demanding extremely high precision specifications-.2% to less than .002% regulation.

3. For all drive applications requiring automatic Synchronizing of Large Number of Mctcrswith respect to each other.

4. For all drive applications requiring atomatic Synchronizing of a motor to an existing clocking pulse train.

# 4.3 Some Specific Application Areas:

Computer peripheral drive such as a disc unit.

2. As a conveyore drive for materials handling

3. A reel to reel tape drive.

In fully automated high precession and shigh pressure misting systems for controlled enviornment ecological systems.

# <u>APPENDIX A</u>

### LINEARIZED MODEL FOR PFD

The objective of this section is to derive a linearized model for the PFD under locked condition and constant reference frequency.

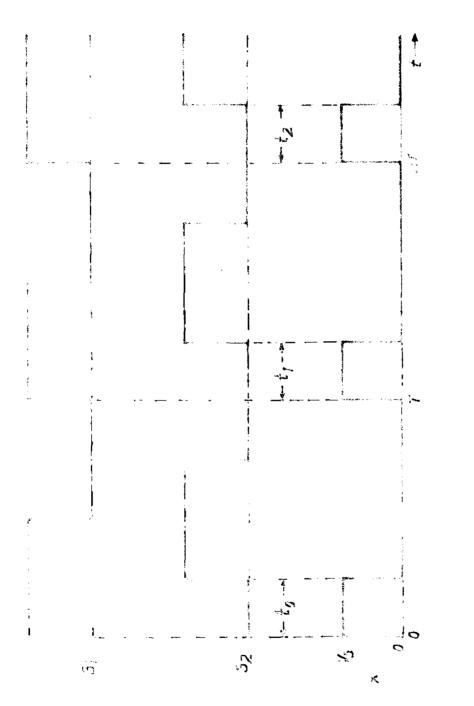

Assume, with no loss of generality, that the reference signal,  $S_1$ , leads the feedback,  $S_2$ . The output x of the PFD will b  $V_s$  during the time interval between the leading edges of  $S_1$  and  $S_2$  as illustrated in Fig.Al.

The phases  $Q_1$  and  $Q_2$  of  $S_1$  and  $S_2$ , respectivly, are:

$$\Theta_1 (kT) = 2 II k$$

(A1)

$$\Theta_{2} (kT + t_{k}) 2 II k \qquad (A2)$$

Denote

$$\Theta = \Theta_1 - \Theta_2 \tag{A3}$$

The PFD output is

| GENTRAL | 17539500<br>LIBAN & U.C. TSKA<br>BOURK 38 | 175325<br>Of ACOMMEN |

|---------|-------------------------------------------|----------------------|

|         |                                           |                      |

. 50

$$X = \begin{cases} V_{s} & KT < t < kT + t_{k} \\ 0 & elsewhere \end{cases}$$

(A4)

Now suppose that the system operates around a nominal value of 0 + 0 + 5 0 (A5) Since the reference frquency is constant, (A5) can occur only if a change occurred in  $\mathbb{F}_2$ :

This will result in a change in the dustion of the output pulses,

$$t_k \rightarrow t_k + \delta t_k$$

(A7)

and a change in the output,

$$\times \rightarrow \times + = \times + = \times$$

(AB)

The method to be used here is to determine the relationship between ox and 50. The relationship constitutes the linearized model of the system. Note that the new pulsedurations are such that (A2) musthold. Thus,

$$\Theta_2(kT+t_k + \delta t_k) - \delta \Theta(kT + t_k + \delta t_k) = 2IIk$$

(A9)

Since  $\delta \Theta$  and  $\delta t$  are very small, we can expand (A9) by

Taylor series and retain the first order terms.

$$\Theta_2(kT_+t_k) + \frac{d\Theta_2}{dt} (kT_+t_k) \delta t_k - \delta \Theta(kT_+t_k) = 2II k \quad (A10)$$

Simplify according to (A2), and note that

$$\frac{d\Theta_2}{dt} = w$$

(All)

Equation (A10) becomes

$$w(kT+t_k)\delta t_k - \delta \Theta(kT + t_k) = 0 \qquad (A12)$$

οr

$$\delta t_{k} = \frac{\delta \Theta (kT + t_{k})}{w(kT + t_{k})}$$

(A13)

Since the frequency is nearly constant, we can write

$$\delta t_{k} = \frac{1}{W} \quad \tilde{\delta} P(kT_{+}t_{k}) \tag{A14}$$

Then the resulting change in x is a pulse of duration  $\delta t_k \boldsymbol{\cdot}$

$$\delta_{x} = \begin{cases} V_{s} & kT + t_{k} < t \leq kT + t_{k} + \delta t_{k} \\ 0 & elsewhere \end{cases}$$

(A15)

Since  $\delta t_k$  is very small, we can approximate the series of pulses of (A15) by a series of impulses of the same area. Note that the area, A, of each pulse ic:

$$A = V_{s} \delta t_{k} = \frac{V_{s}}{w} \delta \Theta (kT + t_{k})$$

(A16)

$$\delta_{X=} \frac{V_{s}}{w} \sum_{k=0}^{\infty} \delta_{\theta}(kT + t_{k}) \delta(t - kT - t_{k}) \quad (A17)$$

Note that if the frequency is constant,  $t_k$  is constant, and we an can shift t to eliminate  $t_k$  in (A17). Also mote that w = 2I /T. Therefore,

$$\delta_{X} = \frac{V_{s}^{T}}{2 \Pi} \sum_{k=0}^{\infty} \delta_{\theta}(kT) \delta(t-kT)$$

(A18)

Thus, the linearized model of the PFD is the sampling of  $\Theta$  by a train of impulses of weight  $V_{\rm s}T/2II$ .

# <u>APPENDIX-B</u>

# STABILITY OF THE PLS

Given the characteristic equation (13).

$$z^{2} + z (-1 B - BC + C) + B = 0$$

(B1)

In order to determine the stablity, use the transformation.

$$z = \frac{\lambda + 1}{\lambda - 1}$$

(B2)

This transforms. the inside of the unit circle, 2 < 1,  $C(1 - B) \times^2 + 2 (1-B) \times + 2(2 + 2B + BC - C) = 0$  (B3) In order for the roots of (B3) to be in the LMP, all the coefficients in (B3) must have the same sign. Furthermore, as (1 - B) is always positive, we require the last term to be positive, too.

$$2 + 2B + BC - C > 0$$

(B4)

This can be written as

$$C(1-B) \ll 2(1 + B)$$

(B5)

or

r

$$C \quad \sqrt{\frac{2(1+B)}{1-B}} \tag{B6}$$

$\mathbf{55}$

# REFERENCES

- F.M. Gardner, Phase lock Techniques, New York,

John Wiley and Sons, Inc, 1966.

- R.A. Miller "Digital Control of Shaft Speed and Position " I.E.E.E. Spectrum Jan. 1968.

- G. Volpe, "A phase locked loof Control System for a Synchronous machine," I.E.E.E. Trans. Automatic Control Vol. AC-15, pp.88-97, 1970.

- 4. A.W. Moore, "Phase-locked loops for motor speed control" I.E.E.E. Spectrum Vol.10, pp.61-67, April 1973.

- 5. D.H. Smithgall, "A phase-locked loop motor control system" I.E.E.E. Trans. Ind. Electronics and Control Instrumentation Vol.IECI-22 pp.487-490, Nov.1975.

- 6. N.K. Sinha and N.H. Bailey, "Speed Control of a D.C. Servomotor using phase locked loop: Some test results of a practical design " I.E.E.E. Trans. Ind, Electronics and Control Instrumentation Vol. IECI-23 No.1 pp.22-26, Feb.1976.

- 7. T.J. Maloney " A digital method for DC Motor speed Control" I.E.E.E. Trans. Ind. Eletronics and Control Instrmentation, Vol IECI-23 pp.44-46, Feb.1976.

W.L. Kenley and B.K. Bose, "Triac Speed Control of three phase Induction Motor with phase-locked loop regulation" I.E.E.E. Trans. Industry Applications, Vol.IA-12, pp.492-498, Sept./Oct.1976. 5:0

Ţ

- 9. B.K. Bose and K.J. Jentzen, "Digital Speed Control of a DC Motor with phase locked loop regulation", I.E.E.E. Transaction on Industrial Electronics and Control Instrumenta Secon Yol. IECI-25 No.1, pp.10-13, Feb.1978.

- 10. S.C.Gupta, K. Venkatesan, K. Eapen and P.Pradhan, "A Fast measuring phase Detector for use in PLL Motor Control Systems" I.E.E.E. Transaction on Industrial Electronics and Control Instrumentation, Vol. IECI-25 No.1 pp.75-77 Feb. 1978.

- 11. Labinger," Designing P.L.L. Sewos with digital IC's Control Engg. Feb.1973.

- "Focus on Pulse Transformes" Electronic design June 21,1975 pp.78.

- 13. Mc dermott Jim " Monolithic phase locked loop IC's Electronic Design March 15,1975 pp.38.

- 14. G.Nash "Phase locked design fundamental " Motorola Appl. Note AN-535,1970.

θ.

- 15 Texas Instruments, TTL Data Book for design Engineers, 1973 p.405.

- 16. Gupta S.C." Phase Locked Loop" Proc. I.E.E.E. Vol.13 Feb.75.

- 17. Reddy C.P. and Gupta S.C. "A class of all digital Phase locked loops Modeling and Analysis " I.E.E.E. Trans. Ind. Electronics Control. Instrum. Vol.IECI-20 pp.239-251 Nov.1973.

- 18. Shup "Digital Motor Speed Control " Electro-Technology October 1963 pp.68.

- 19. Ponstingl J.C. " Digital.Techpneter Denerator Systems" I.E.E.E. Transactions on Industry and General Applications. Jan./Feb.1966 pp.65.

- 20. Tal J "Speed Control by phase-locked Serve Systems-New Possibilities and Limitations " I.E.E.E. Transactions on Industrial Electronics and Control Instrumentation Feb.1977 pp.118.

- 21. Offereins R.P. "A digital phase locked loop and its stability" I.E.E.E. Transactions on Ind. Electronés & Control Instrumentation Aug.1975 pp.401.

. 60

- 22. Adamson C. and Mosland D.P. "Automatic Check Synchronizing Equipment Using Static relaying principles" Proceedings of the I.E.E.1961 Vol.108A pp.331.

- Humpage W.D., Nellist B.D. and Sabberval S.P.

" Phase Comparison methods in Automatic Synchronizing

ibid, 1965 Vol.112, pp.396.

- 24. Malik D.P. and Cory B "Automatic Resynchronization of Synchronous machines " ibid,1966, Vol.113, pp.1972.

- 25. Raj Kumar A.D., Kappurajulu A and Hariharan S "Solid State Automatic Synchronizer" Journal of Instn.of Engineers (India) Vol.57 June 1977 pp.268.