# DEVELOPMENT OF FAULT TREE SIMULATOR

Ch. 77-78

109809

682

A DISSERTATION submitted in partial fulfilment of the requirements for the award of the degree of

MASTER OF ENGINEERING in

ELECTRICAL ENGINEERIG (System Engineering and Operations Research)

> By AVINASH SHRIDHAR GAVANE

DEPARTMENT OF ELECTRICAL ENGINEERING UNIVERSITY OF ROORKEE ROORKEE (INDIA) 1977

#### THE DISSERTATION

on

#### DEVELOPMENT OF FAULT TREE SIMULATOR

Under the Guidance

0f

Shri A.K. RAJA Lecturer Dept. of Electrical Engg. University of Roorkee -ROORKEE (U.P.) Dr. K.B. Mishra Associate Professor Department of Electrical Engg University of Roorkee ROORKEE (U.P.)

Fabricated By :-

AVINASH SHRIDHAR GAVANE M.E. II (S.E.O.R.) Department of Electrical Engineering University of Roorkee, Roorkee, (U.P.)

DEPARTMENT OF ELECTRICAL BNGINBERING UNIVERSITY OF ROORKEE ROORKEE (U.P.)

#### CBRTIFICATE

Certified that the dissertation on 'DEVELOPMENT OF FALLT TREE SIMULATOR', which is being submitted by SHRI AVINASH SHRIDHAR GAVANE, in partial fulfilment for the award of the degree of MASTER OF ENGINEERING in Systems Engineering and Operations Research of the University of Roorkee, Roorkee (U.P.), is a record of student's own work carried out by him under my supervision and guidance. The work embodied in this dissertation has not been submitted for the award of any other degree or diploma.

This is further to certify that he has worked for a period of 6 months from February 1977 for preparing dissertation for Master of Engineering Degree of this University.

(Shri A.K. Raja) Lecturer Dept. of Electrical Engg. University of Roorkee Roorkee (U.P.)

(Dr. K.B. Mishra) Associate Professor Dept. of Electrical Engg. University of Roorkee Roorkee (U.P.)

DATED: SEPT. 1977

#### ACKNOULEDGEHENT

I wish to express my deep and sincere gratitude to my guides Dr. K.B. Hishra and Shri A.K. Raja who have been a continuous source of inspiration throughout the course of work. Because of their consistant guidence and hard efforts this dissertation ended in a moss of complexity and perplamity. I ove them the time they have devoted to make this work a success.

Hy acknowlodgements are due to non teaching staff who took interest in completing the dissertation specially Mr. Yadav and Mr. Rajinder (from Power Electronics Lab) Mr. S.L. Eapoor (from Reliability Testing Lab) and Mr. Sharma and Mr. Chunnikal (from Blectrical Workshop).

> (AVINASH SHRIDHAR GAVALE) M.E. II (S.E.O.R.) Dopt. of Blect. Engg. University of Roorkee Roorkee (U.P.) 1977

CONTENTS

## CHAPTER S

## ABSTRACT

|                                                                                                     | •          |

|-----------------------------------------------------------------------------------------------------|------------|

| LIST OF COMPOHENTS USED                                                                             |            |

| I. INTRODUCTION                                                                                     | +++ 1-3    |

| 2. FAULT TREE ANALYSIS                                                                              | ••• 4-20   |

| 2.1 What is 'FAULT TREE'                                                                            | ••• 4      |

| 2.2 Advantages of Fault Tree Analysis                                                               | ··· 4      |

| 2.3 Dis-advantages of Rault Tree Analysis                                                           | •• 5       |

| 2.4 Dofination of Certain Torms used<br>in Fault Tree Analysis.                                     | ••• 5      |

| 2.5 Graphical Symbols used in Fault<br>Tree analysis                                                | ••• 9      |

| 2.6 Development of Rault Tree                                                                       | +++ 14     |

| 3. COMPONENTS DESCRIPTION                                                                           | ••• 21- 32 |

| 3.1 4 Bit Binary Counter 7493                                                                       | ••• 21     |

| 3.2 Quad Tuo input And Gato 7408                                                                    | 24         |

| 3.3 Hox Invorter 7404                                                                               | 26         |

| 3.4 Quad Tuo Input Hand Gate 7400                                                                   | ••• 27     |

| 3.5 Single Eight Input Nand Gate<br>7430                                                            | 29         |

| 3.6 Four Bit Binary Full Adder 7483                                                                 | 30         |

| 4. THE EQUIPMENT AND ITS DESIGN                                                                     | ••• 33-    |

| 4.1 Design Philosophy: Reliability<br>Evaluation Through Path Sets<br>and Cut cets.                 | ••• 33     |

| 4.2 Design Philosophy: Roliability<br>Evaluation Through Minimal Path Sets<br>And Minimal Cut-Sets. | ••• 38     |

# Page No.

| 4.3 Reliability Evaluation Using<br>Minimal Path sets and Minimal |        |  |  |

|-------------------------------------------------------------------|--------|--|--|

| Cut sets (Analytically)                                           | 50     |  |  |

| 4.4 The Equipment                                                 | 53     |  |  |

| 4.5 Experimental Procedure                                        | ••• 64 |  |  |

| 5.CIRCUIT MODIFICATIONS                                           | 67-73  |  |  |

|                                                                   | 74     |  |  |

| REFERENCES                                                        |        |  |  |

. \_

.

٠

. . .

• . . .

.

, ,

#### A B S T R A C T

Here the equipment 'FAULT TREE SIMULATOR' is developed. The priliminary informations like

1. Various Path Sets

2. Minimal Path Sets

3. Various Cut Sets

4. Minimal Cut Sets

which are necessary in the Fault Tree Analysis of system can be obtained from the equipment.

# LIST OF COMPONENTS USED

# PARTICULARS

| 1. 749 | 5 FOUR BIT BINARY C   | OUNTER           |       | 3         |

|--------|-----------------------|------------------|-------|-----------|

| 2. 748 | 5 FOUR BIT FULL AD    | DER              |       | 3         |

| 3. 740 | 8 QUAD TWO INPUT AI   | ND GATB          | •••   | 4         |

| 4. 740 | 4 HEX INVERTER        |                  | • • • | 2         |

| 5. 740 | O QUAD TWO INPUT NA   | ND GATE          | • • • | 1         |

| 6.743  | O SINGLE EIGHT INPU   | JT NAND GATE     |       | 1         |

| 7.     | L.E.D. INDICATING BUI | LBS              | * * * | 14        |

| 8.     | BANANA SOCKETS        | ·                |       | 111       |

| 9.     | SINGLE SIDED CU-CLADE | ED PLATE 3' x 2' | ***   | 3         |

|        |                       | 8' x 2'          | ***   | 1         |

| 10.    | DOUBLE SIDED CU-CLADE | SD PLATE 3' x 2' |       | 2         |

| 11.    | PUSH BUTTON SWITCHES  | ON -             | ***   | 2         |

|        | ON - OF SWITCH        |                  | ***   | 1         |

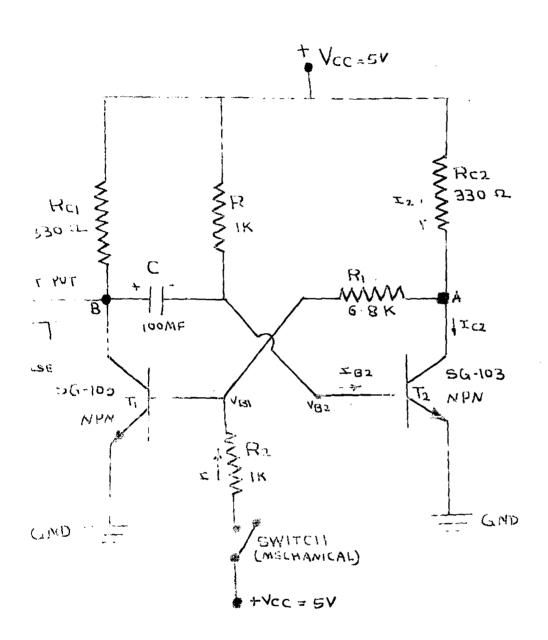

| 12. 80 | -103 TRANSISTORS      |                  |       | 2         |

| 13.    | FLEXIBLE AND HOOK-UP  | WIRE             | ***   | 40 Meters |

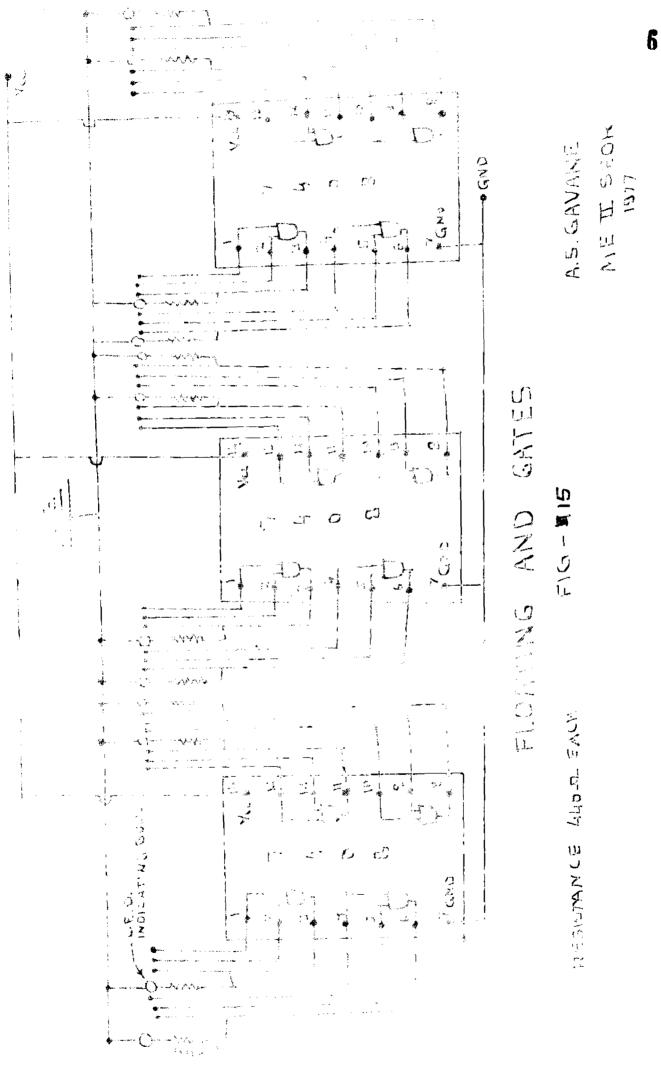

| 14.    | RESISTANCES           | 440              |       | 13        |

|        |                       | 330              | * * * | 3         |

|        |                       | 1 K              |       | 2         |

|        |                       | 6.8 K            | • • • | 1         |

| 15.    | CAPACITORS.           | 100 MBD          | • • • | 1         |

| 16.    | I.C. BASES            | 14 PIN TYPE      |       | 11        |

|        |                       | 16 PIN TYPE      | •••   | 3         |

| 17.    | NOTAL CASE DAD PARTON | FD 17/8          |       |           |

17. METAL CASE FOR EQUIPMENT

#### <u>CHAPTER -1</u>

#### INTRODUCTION

There has been a muchroom groth of electronic industries manufacturing lot of entertainment and power electronic equipment. However, reliability of these equipment manufactured currently in India is doubtfull. primarily on account of disregard of these industries in properly carrying out of reliability analysis of the design. These industries can not afford to have an exclusive group for such analysis.

It is therefore the main purpose of the proposed 'FAULT TREE SIMULATOR' to provide these industries with an anologue equipment which will help them in physically carrying out the studies mainly in identifying the various causes of components failure of the equipment through functional simulation of these components failures on fault tree simulation. Fault tree simulator is basically an anologue equipment which will provde an inside to the designer on the critically of the components used in an equipment with regard to the equipment performance.

The idea of fault tree simulation has not yet been exploited any where and is likely to revolunise thinking in equipment failure analysis methodology, basides its potentiality for bringing out patent.

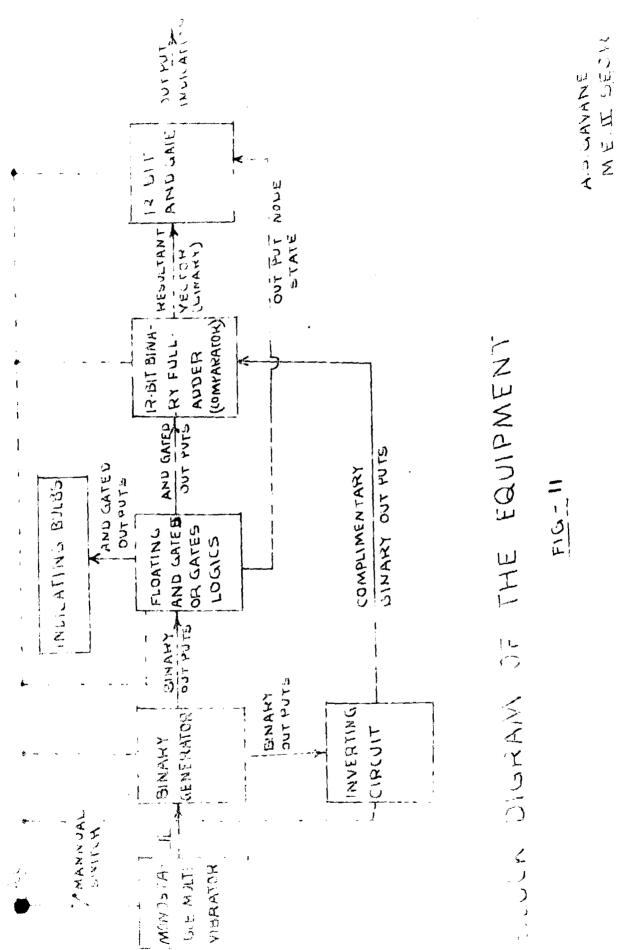

The preliminary informations like Path-sets, cut-sets Minimal Path-sets and Minimal cut-sets can be obtained from the equipment.

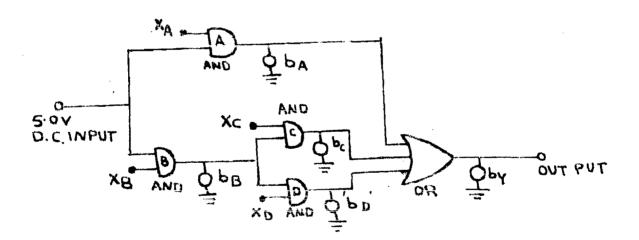

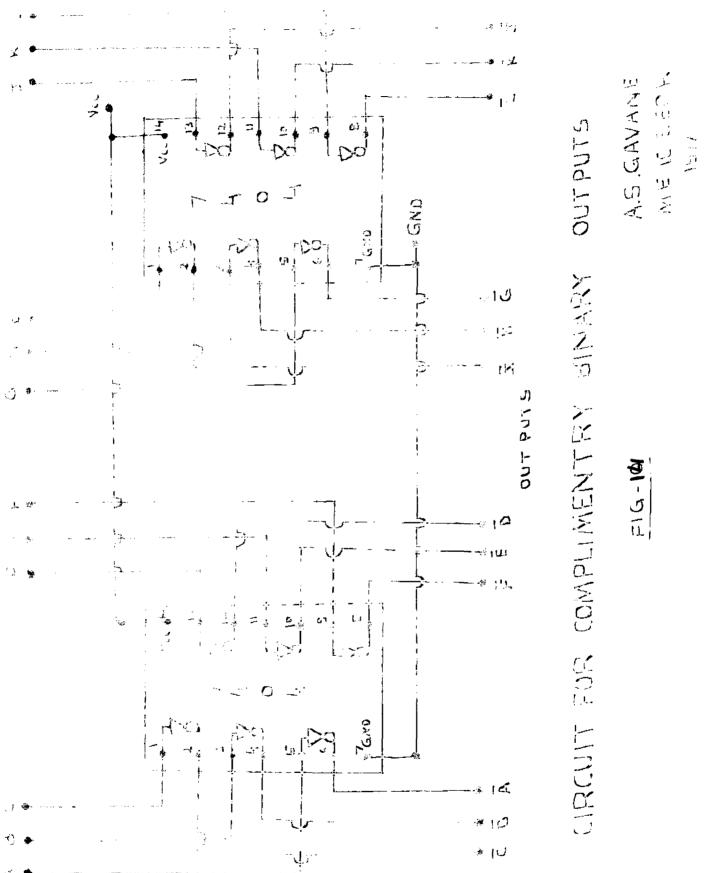

The given system is first represented by its functional interconnection. Each element of the network element is represented by a 2-input AND gate. One terminal of each AND gate is used to form the given system configuration, while the other terminals are supplied from the out put binary generation.

The input state vector to the AND gated system network for which the out put indication is obtained represents the various Path sets. And those input state rector which do not give the out put indication represents the various cut-sets.

To obtain Minimal Path-sets, first the path sets of various sizes are obtained by compairing the state vector at the input of AND gated network and state vector at the out put of AND gated network in a binary full adder. The out put of full adder and state of out put node condition are then feed to a final AND gate, which gives the out put indication, for paths of various sizes. Out of these paths of various sizes all paths of size up to and including

(n-1) represents minimal paths sets. Here n are number of nodes present in the network.

Minimal cut sets are nothing but the minimal path sets of DUAL system network.

In the chapter for circuit modification, design of switch operating a monostable multivibrator is given. The out put of this multivibrator is used to drive the input of binary generator.

#### CHAPTER 2

#### PAULT TREE ANALYSIS

#### 2.1 UHAT IS FAULT TREE

Fault tree analysis is a technique used for reliability analysis and is generally applicable to complex systems. The predictions from this type of analysis are important considerations in the design of many systems such as space vohicles, air crafts, ships and their electronic systems, missiles and nuclear reactor systems.

Fault tree analysis is considered to be the most simple and most sophisticated analytical technique for reliability analysis.

#### 2.2 ADVALTAGES OF FAULT THEE ANALYSIS:

Tochnqie of 'Fault Froe Analysis' is of major valve in the following respect.

- 1. Analyst can concentrate on one particular system at a time.

- 2. Analysis can be performed with different degrees of detail.

- 3. Analyst can know the internal behaviour of the system.

- 4. Points out the aspects of system which are important with respect to the failure of interest.

- 5. Provides the option for qualitative or quantitative system reliability analysis.

- 6. Makes easy translation of graphical symbols for methamatical simplification.

- 7. Allows an easy modification of the number and the characteristics of input random quantities and allowing different out put quantities to be related.

- 8. Provides a graphical aid giving visibility to those in system management and planning about the final results of the examinations in a syntific way.

- 9. External influences are just another input to the fault tree (environmental and operational etc.).

- 10. Analysis can easily be computerised.

#### 2.3 DISADVANTAGES OF FAULT TREE ANALYSIS:

Fault tree analysis has certain disadvantages as listed below:

- 1. High cost of development

- 2. Limitations of skilled persons in this techniques.

- 3. Non-availability of efficient mathematical techniques for analysis.

2.4 DEFINATIONS OF CERTAIN TERM USED IN FAULT TREE ANALYSIS

#### 1. COMPONENT:

A component is a functional unit. These functional

units are arranged and interconnected so as to form a system.

#### 2. SYSTEM:

Intercoupling of several components leads to a system. The system is designed to fulfil its function throughout a specified period of time.

#### 3. RELIABILITY:

The characteristic of an item expressed by the probability with which it will perform a required function under stated condition for a stated period of time. The term reliability is widely used in connection with non-maintained system. (where repair is not possible), such as air craft systems, equipments used in military and medical side etc.

#### 4. TOP EVENT:

It is an undepired event for the system and is obtained by the combinations of primary failures.

#### 5. PRIMARY FAILURE:

It is a failure for a system component

#### 6. FAILURE HODES:

Failure mode is the type of failure in which a

component or system fails to fulfil its function within a a specified period of time.

#### 7. COMMON MODE FAILURE:

Certain single failure that can result in several component failure simultaneously is called common mode failure.

#### 8. FAULT EVENT

It is a failure situation resulting from the logical interaction of primary failure.

9. BRANCH:

Development of any fault event results in a branch of a fault tree.

10. BASE EVENT:

Event being developed is called the base event of the branch.

11. TRANSPER EVENT:

Transfer of any base event from one part of the tree to the other is a transfer event.

#### 12. REPEAT EVENT:

Transfor of one primary event to the other branch of the tree is a repeat event.

#### 13. PATH SET (OR TIE SET)

Set of elements whose functioning will ensure system success.

#### 14. MINIHAL PATH SET:

It is a path set consisting of minimum number elements whose operation is necessary for the system success. Minimal path set is nothing but the forward path from input node to output node.

#### 15. CUT SET

Set of elements whose failure will ensure system to fail.

#### 16. MINIMAL CUT SET:

It is a cut-set consisting of minimum number of elements whose failure ensures the system failure.

Cut sets are nothing but the path sets of the 'DUAL' system of original system. Similarly minimal cut sets are the minimal path sets of this DUAL system.

#### 2.5 GRAPHICAL SYMBOLS USED IN FAULTREE ANALYSIS

Fault tree construction is a logical development of top event. A fault tree consist of events, branches and gates which define some undesired event the gates acts as mathematical operators which determine the probabilities of events preceding them. There are several operator theories for obtaining probabilities, three of the them which are commonly used in fault tree analysis being (a) Probabilistic set theory (b) Logic theory and (c) Boolean Algebra.

Of the three theories for fault tree analysis set theory is generally considered the best known and easiest to understand. Set operators can be calegorized as 'Union' operators, 'Intersection' operators or combination of these two. Fault tree gates basically fall into these three calegories.

- 'Union' operator

(a) OR gates

(b) Exclusive OR gates

- 2. 'Intersection' Operator

- (a) AND gates

- (b) Priority AND gates

- (c) Inhibit AND gates

#### 3. Combinations

The graphical symbols used in a fault tree basically fall in to two categories.

11

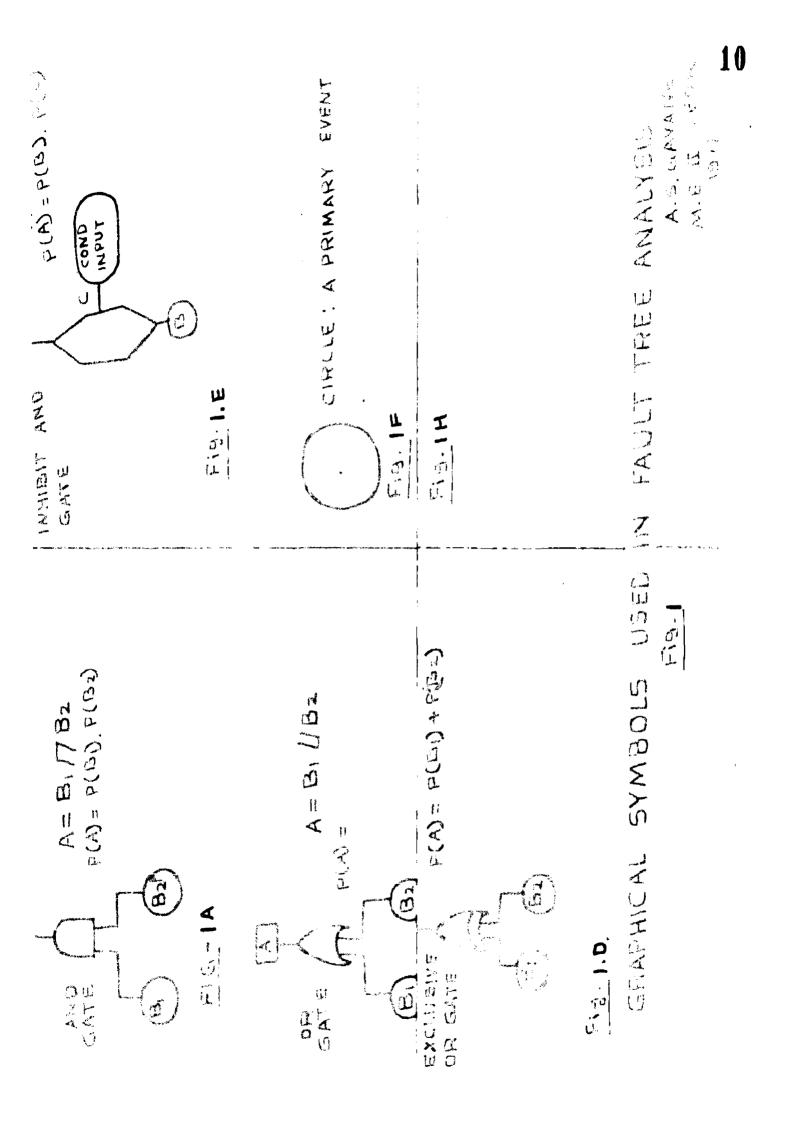

(a) Logic symbol [ fig....page 10 ]

(b) Event symbol [ fig....l...page 10 ]

The most commonly used Logic symbols

are described below:

THE AND GATE [fig.. 1A... page. 19....]

The set notation for event A is

$$A = B_1 \prod B_2$$

In other words event A will occure if both events  $B_1$  and  $B_2$  occure. The probability of A when  $B_1$  and  $B_2$  are independent is

$$P(A) = P(B_1), P(B_2)$$

In general formula for the AND gate containing K independent events is

$$P(A) = P(B_1) P(B_2) P(B_3) \dots P(B_k)$$

THE OR GATE [fig. \R... Page. 19...]

The set notation for event A 18

Event A will occure if either event  $B_1$  or event  $B_2$ occurs. The probability of A when  $B_1$  and  $B_2$  are independent is

$$P(A) = 1-(1-P(B_1)). (1-P(B_2))$$

In general formula for OR gate containing k independent events is

$$P(A) = 1 - (1 - P(B_1)) \cdot (1 - P(B_2)) \cdot (1 - P(B_3)) \cdot \dots \cdot (1 - P(B_k))$$

Priority AND gate is used when the occurance of events is important. As shown event A occurs only if event  $B_1$  occurs first  $B_2$  occurs next. Both events  $B_1$  and  $B_2$  can occurs in two different ways ( $B_1$  first  $B_2$  next or vice-versa), but the event A will occur only when  $B_1$  occurs first and  $B_2$  next. If both  $B_1$  and  $B_2$  have uniform probability distribution over the interval in question, the probability of A can be given by

$$P(A) = \frac{1}{2} P(B_1), P(B_2)$$

General formula is

$$P(A) = \frac{1}{K} P(B_1) P(B_2) P(B_3) \dots P(B_k)$$

where k is the number of ways the B can occurs, following permulation selection without replacement.

THE EXCLUSIVE OR GATE [fig. 1. page 10...]

Events immediately following the exclusive or gate are mutually exclusive, that is the occurance of  $B_1$  implies that  $B_2$  can not occur (i.e.  $P(B_1 \ B_2) = 0$ ) or vice-versa. The general formula for exclusive OR gate containing k events (mutually exclusive and independent)

$$P(A) = P(B_1) + P(B_2) + P(B_3) + \dots + P(B_k)$$

THE INHIBIT AND GATE [fig. 1: E. . . page 10. ...]

It requires the occurence of some out side event for flow thrugh. In order that B flow through the gate event C must occur. The set notation for the gate is

$A = B_1 \Pi B_2$

and  $P(A) = P(B_1)$ .  $P(B_2)$

The most commonly used 'Event Symbols' are described below

RECTANGLE ]fig. 1.F. page. 19...]

This represents a fault event resulting from the combination of more basic faults acting through the légical gates.

CIRCLE [fig. ]G. ... page. Q...]

This denotes primary events or failure inputs that are independent of all other events.

```

TRIANGLE: [fig. 1H.. page. JP...]

```

It is not strictly an event symbol but a transfer from one part of the fault tree to another. A line from the side of the triangle denotes an event transfer out from the associated logic gate. A line from the 9pex of the triangle makes an event transfer in to the associated logic gate from the transfer out triangle with the same identifications number.

#### 2.6 DEVELOPMENT OF FAULT TREE:

The following four steps generally can be present

in a fault troo analysis.

1. To defino system

2. Fault tree development

3. Qualitative analysis

4. Quantitative analysis

1. To Dofino System:

System defination is often the most difficult task associated with fault tree analysis. Of primary importance is a functional lay out diagram of the system showing all functional inter connections and identifying each system component.

The next step in the system description is to establish the system boundary conditions, System boundary condition is defined as the situation for which the fault tree is to be drawn. A most important system boundary condition is the top event. System boundary conditions also include any fault event declared to exist or to be not-allowed for the duration of the fault tree construction. These events are called existing system boundary conditions and 'not allowed system boundary conditions. An existing system boundary condition is treated as certain to occure and not allowed system boundary conditions is treated as an event with no possibility of occuring. Noither existing non not-allowed

cyctom boundary conditions appear as event in the final fault troe.

#### 2. PAULT TREE CONSTRUCTION

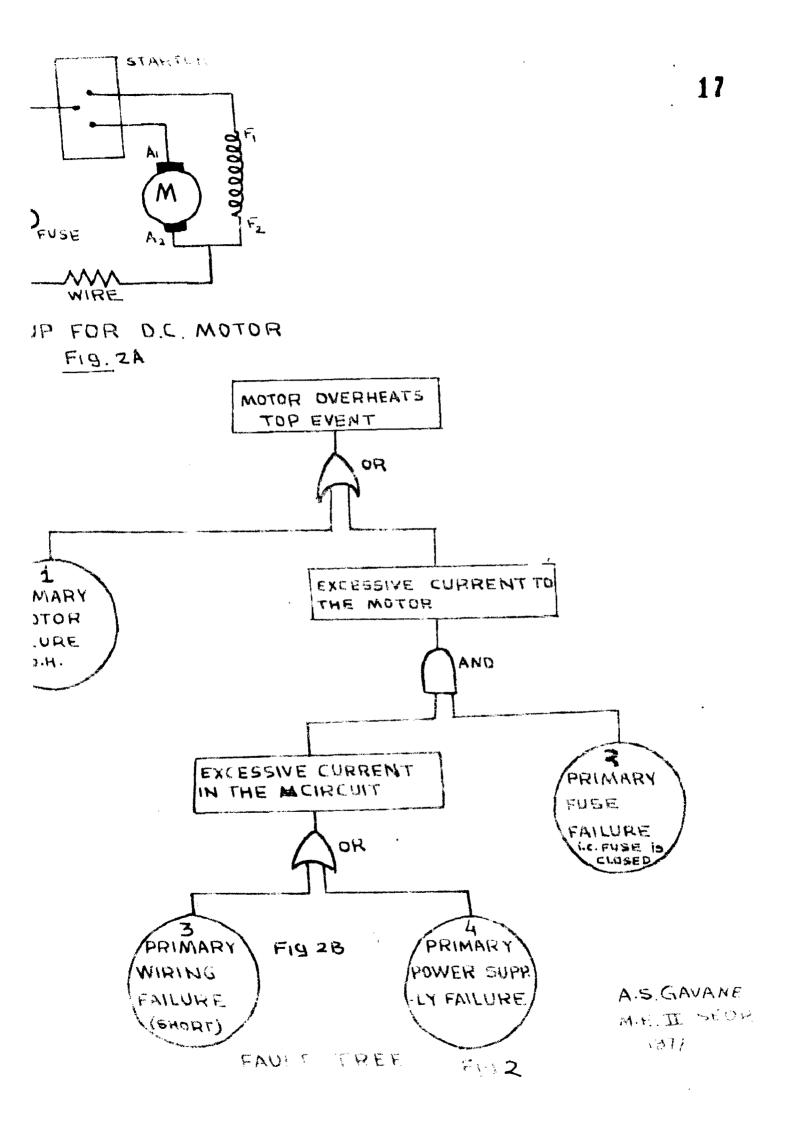

Here we will illustrate by an example that how a fault tree can be constructed.

Lot us consider the example of D.C. motor set up shown in [gig.?A...page.N...]

Top event: Motor overheats

The other boundary conditions are switch is closed and failure due to external system is not allowed event. The motor overheats if an electrical over load is supplied to the motor or a primary failure within the motor causes the overheating c.g. if the bearing lose their lubrication or a wiring failure occure withing the motor.

Fault tree is constructed as shown in [fig.....pag..] Excessive current to motor occurs if excessive current is present in the circuit and fuse fails to open. It also occurs if the wire fails shorted or the power supply surfes.

#### 3. QUALITATIVE ANALYSIS:

For the fault tree shown in [fig.2B. page.17...] it is

possible to find the minimal cutesets by inspection but an exhaustive method is required to be found out for larger tree configuration. The primary events are numbered from 1 to 4 which leads to top event. The minimal cut sets are (by inspection)

$$(1)$$

$(2,3)$ ,  $(2,4)$

The top event is given by the boolean equation.

Тор = 1 U 2 П 3 Ц 2 П 4

and the top event probability is given by

$P(TOP) = P(1 U 2 \Pi 3 U 2 \Pi 4)$

= 1-(1-P(1)), (1-P(2)), P(3), (1-P(2)), P(4)

'Vesely and Narwm' has suggested a computerized approach for determining the minimal cut-sets. The boolean equation implied by the fault tree is constructed by the computer. The primary events are thin turned-on one at a time and the equation is checked each time to determine wheather it is true. Next all possible combination of two primary events are turned on and again the equation is checked wheather it is true. Each time the equation is true, the collection of primary events that were turned on show cut set. After these cut sets are determined, all cut sets that are sub sets of other cut sets are discarded to obtain minimal cut sets.

Vesely and Narum have suggested a Mole carlo approach where by appropriato weighing of primary events is used to accelerate the process of determining minimal cut sets. However, doubt that all minimal cut sets have been found is always present when Monte Carlo approach is used.

In practice both of these methods requires excessive computer tize to obtain cut sets containing more than three primary events.

#### 4. QUANTITATIVE ANALYSIS:

There are three methods for solutions to fault trees

- (a) Direct simulation Apporoach

- (b) Monto Carlo Methods

- (c) Direct analytical solutions

The direct simulation approach uses boolean logic hard ware similar to those used in digital computer. Obviously this method is costly for implimentation.

Monte Carlo mothods are perhaps the most simple in principlo but in practice it is vory complex. The Monto Carlo methods is not practical without the use of digital computer In this mothod probability data are provided as input and simulation programme represents the fault tree on a computer to provide quantitative results.

Out of the various analytical techniques suggested, the technique of 'Kinetic tree theory' can be used for solving complex fault tree containing primary failures which are a complex function of time and repair possibilities. The solution of fault tree is obtained through the application of probability theory and differential calculus. The use of AND, OR and INHIBIT gate is allowed, Since the information is obtained as a function of time hence with regard to reliability.

#### CHAPTER 3

#### COMPONENT DESCRIPTION

#### 3.1 4-BIT BINARY COUNTER (TTL/MSI 9393/5493/7493):

#### DESCRIPTION:

The TTL/MSI 9393/5493/7493 is a 4-bit binary counter consisting of four master slave flip flops which are internally interconnected to provide a divide by two counter and a divide by eight counter. A gated direct reset time is provided which inhibts the count inputs and simulteneously returns the four flip flop outputs to a LOW level. As the out put from flip flop A is not internally connected to the succeeding flip flops the counter may be operated in two independent models:

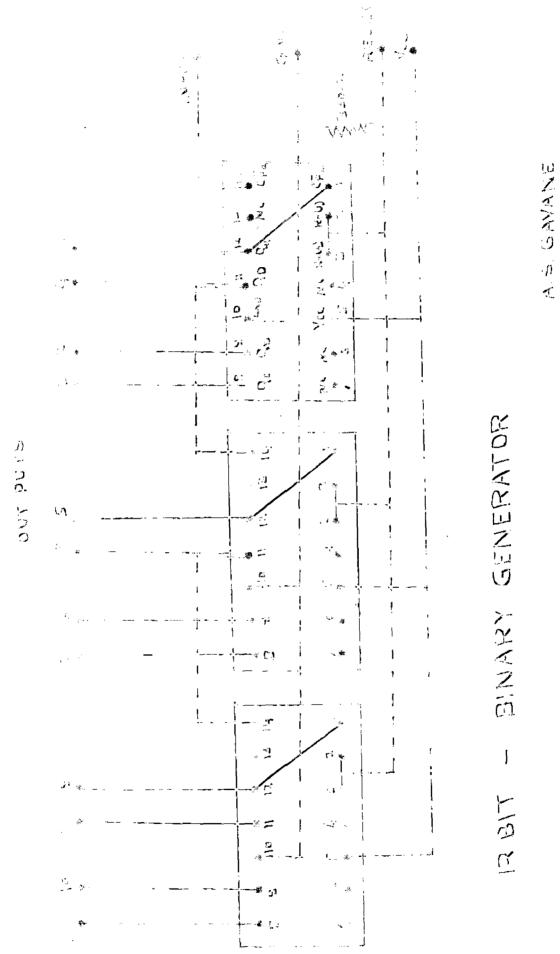

- (A) When used as a 4-bit ripple through counter, out put  $Q_A$  must be externally connected to input  $C_{PB}$ . The input count pulses are applied to  $C_{PA}$ . Simulteneously division of 2,4,8 and 16 are performed at  $Q_A$ ,  $Q_B$ ,  $Q_C$  and  $Q_B$  out puts as shown in truth table.

- (B) When used as a 3-bit ripple through counter, the input count pulses are applied to input C<sub>pp</sub>. Simulteneously

1-95 FOUR BIT BINARY

COUNTER

frequency division of 2,4 and 8 are available at  $Q_B$ ,  $Q_C$  and  $Q_D$  output. Independent use of flip flop A is available if the reset function conside with the reset of the 3 bit ripple through counter.

#### PIN NAMES:

#### Loading

| Ro                 | Reset Zero inj | put                   | 1 U.L.  |

|--------------------|----------------|-----------------------|---------|

| C <sub>PA</sub>    | Clock (Active  | low going edge) input | 2 U.L.  |

| C <sub>PB</sub>    | Clock (Active  | low going edge) input | 2 U.L.  |

| Q <sub>A</sub> , Q | B, Q and Q D   | out puts              | 10 U.L. |

1 U.L. = 40 µA HIGH/1.6 mA LOW

#### CONNECTION DIGRAM AND LOGIC DIGRAMS:

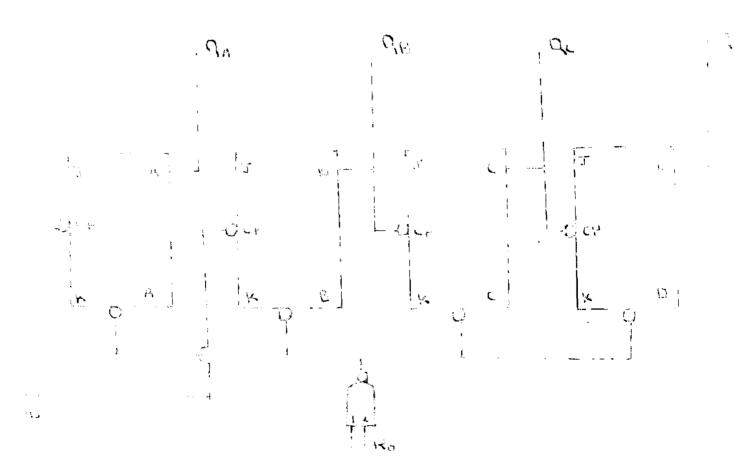

These digrams are shown in fig. 3. Page 22

#### TRUTH TABLE

| Count | 1  | Out            | puts | And the section of the |  |

|-------|----|----------------|------|------------------------------------------------------------------------------------------------------------------|--|

| -     | QD | Q <sub>C</sub> | QB   | QA                                                                                                               |  |

| 0     | L  | L              | L    | L                                                                                                                |  |

| 1     | L  | L              | L    | H                                                                                                                |  |

| 2     | L  | L              | H    | L                                                                                                                |  |

| 3     | L  | L              | H    | H                                                                                                                |  |

| 4     | L  | H              | L    | L                                                                                                                |  |

table contnue

#### table contd....

| Asunt - |                | Out | puts           |    |  |

|---------|----------------|-----|----------------|----|--|

| Count - | Q <sub>D</sub> | QC  | Q <sub>B</sub> | QA |  |

| 5       | L              | H   | L              | H  |  |

| 6       | L              | H   | H              | L  |  |

| 7       | L              | H   | H              | H  |  |

| 8       | H              | L   | L              | L  |  |

| 9       | H              | L   | L              | H  |  |

| 10      | H              | L   | H              | L  |  |

| 11      | H              | L   | H              | H  |  |

| 12      | H              | H   | L              | L  |  |

| 15      | H              | H   | L              | H  |  |

| 14      | H              | H   | H '            | L  |  |

| 15      | H              | H   | H              | Ħ  |  |

#### Notes

- 1. Out put Q<sub>A</sub> connected to input C<sub>PB</sub>.

- 2. To reset all out puts to LOW level both  $R_0(1)$  and  $R_0(2)$  input must be at HIGH Level.

- 3. Either (or both) resent inputs Ro(1) and Ro(2) must be at low level to count.

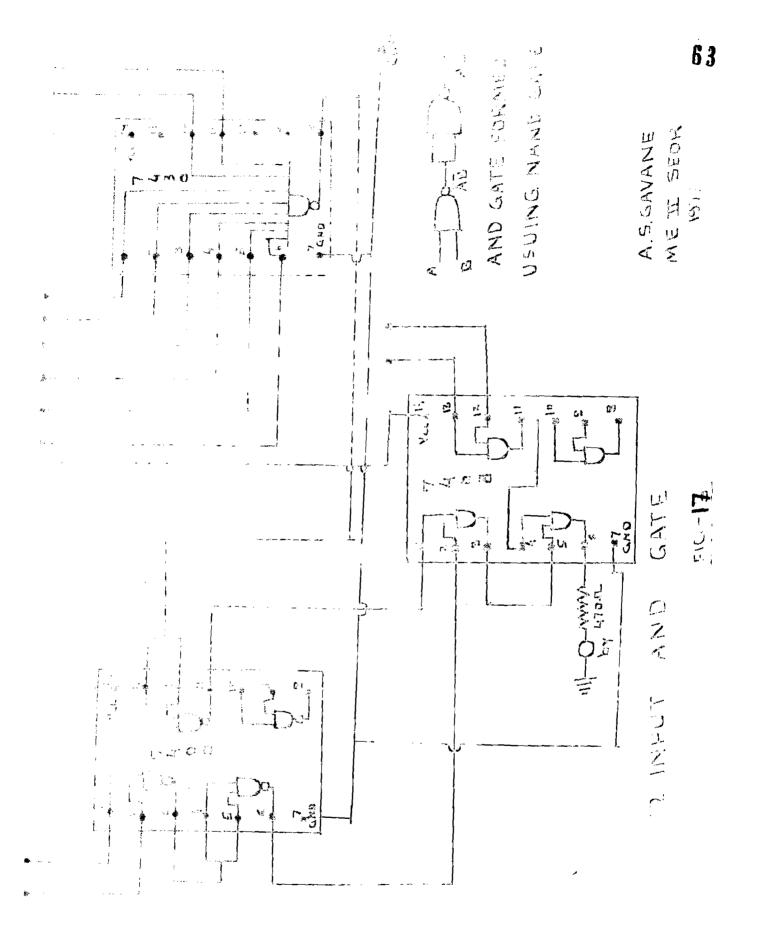

#### 3.2 QUAD TWO INPUT AND GATE (TTL2SSI 9408/5408.7408):

#### DESCRIPTION

The 7408 I.C. consist of four kndependent 2-input

A.S.GAVANE M.E.T. S.E.O.H. 1977

F16 - \$5

1404 HEX INVERTER

٠

# FIG. 34

SHOR DOND IND INFOLD OND CHIE

5 14 23

- 1,2 Input to AND gate A

- 3 Output of AND gate A

- 4,5 Input to AND gate B

- 6 Output of AND gate B

- 7 Ground terminal

- 9,10 Input to AND gate C

- 8 Output to AND gate C

- 12,13 Input to AND gate D

- 11 OUT put of AND gate D

- 14 Vcc supply terminal = 5.0V

If P and Q are (say) input to a AND gate then the out put  $(\gamma)$  of AND gate is given by the logic

#### Y =PQ

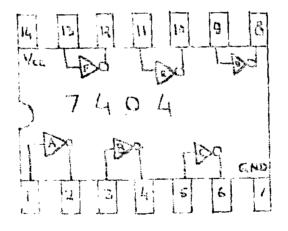

#### 3.3 <u>HEX\_INVERTER [TTL/SSI 9N04/5404/7404]</u>

#### DESCRIPTION

The 7404 I.C. consist of six independent inverters as given shown in fig. 5.Page 25 1. Input to inverter A

2. Output of inverter A

- 3. Input inverter B

- 4. Output of inverter B

- 5. Input to inverter C

- 6. Output of inverter C

- 7. Ground terminal

- 8. Output of inverter D

- 9. Input to inverter D

- 10. Output of inverter E

- 11. Input to inverter B

- 12. Output of inverter F

- 13. Input to inverter F

- 14. Vcc supply terminal = 5.0V

If P is the input to a inverter, the out put (Y) of inverter is given by logic

$\mathbf{Y} = \mathbf{\overline{P}}$

3.4 QUAD TWO INPUT NAND GATE [TTL/SSI 9N00/5400,7400]

#### DESCRIPTION:

The 7400 I.C. consist of four independent two input NAND gates as shown in fig.6. Page 28

FIG-57

14:00 SINGLE 8-INPUT NAND GATE

# THOO QUAD TWO INPUT WAND GATE

្រុំ រុំ ភ្នំ <u>.</u> V., 7400 1 c.xu 2. [ ]3.

,

- 1,2 Input to NAND gate A

- 3 Output of NAND gate A

- 4,5 Input to NAND gate B

- 6 OUT put of NAND gate B

- 7 Ground terminal

- 9,10 Input to NAND gate C

- 8 Output of NAND gate C

- 12,13 Input to NAND gate D

- 11 Output of NAND gate D

- 14 Vcc supply terminal = 5.0V

If P and Q are the inputs to a NAND gate then the out put (Y) of the NAND gate is given by the logic

## Y = FV

3.5 <u>SINGLE EIGHT INPUT NAND GATE</u>[TTL/SSI 9N30/5430,7430] <u>DESCRIPTION</u>: F19:7 Page 28

The 7430 I.C. consist of only one 8-input NAND gate as shown in fig. 1,2,3,4,5,6,11,12 input to NAND gate

- 8 out put of NAND gate

- 7 Ground terminal

- 14 Vcc supply terminal = 5.0V

- 9,10,13 N.C. terminals.

If P,Q,R,S,T,U,V,W forms input to NAND gate then the out put (Y) of NAND gate is given by logic

# Y = PORSTUVW

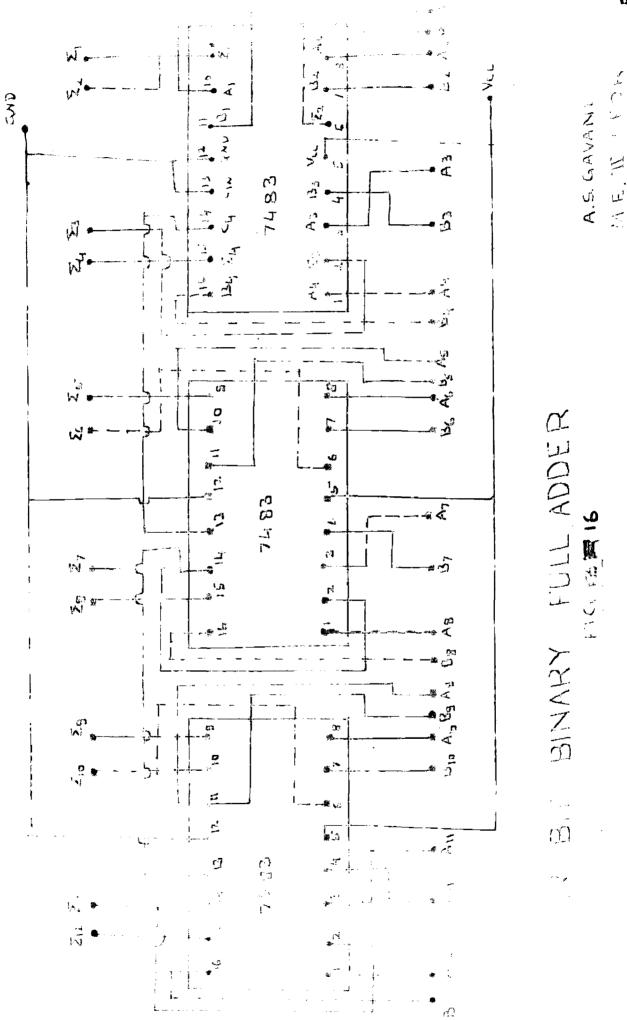

# 3.6 FOUR BIT BINARY FULL ADDER: [TTL/MSI 9383/5483,7483]

### DESCRIPTION:

The TTL/MSI 9383/5483,7483 is a FULL ADDER which performs the addition of two 4 bit binary numbers. The sum ( ) outputs are provided for each bit andthe resultant carry ( $C_4$ ) is obtained from 4th bit. Designed for medium to high speed, multiple bit, parallel add/serial-carry applications, the circuit utilized high speed high fan out TTL The implimentation of a single inversion, high speed, darlingtonconnected serial-carry circuit within each bit minimizes the necessary for extensive 'look ahed and carry cascading circuits.

#### PIN NAMES

|                                                                   |                 | Loading |

|-------------------------------------------------------------------|-----------------|---------|

| A1, B1, A3, B3                                                    | Data Inputs     | 4 U.L.  |

| A <sub>2</sub> , B <sub>2</sub> , A <sub>4</sub> , B <sub>4</sub> | Data Inputs     | 1 U.L.  |

| CIN                                                               | Carry Inpute    | 4 U.L.  |

| 1' 2' 3, 4                                                        | Sum Out puts    | 10 U.L. |

| C <sub>4</sub>                                                    | Carry Out bit 4 | 5 U.L.  |

7483 4-BIT BINARY FULL ADDER

-

|        | AL | A's | A2.                | <u>A</u> .        |

|--------|----|-----|--------------------|-------------------|

| -)<br> | ыц | E.  | 134                | الغرز             |

| C4     | E4 | Ź-j | $\tilde{\Sigma}_2$ | <u>د.</u><br>۲۰۰۱ |

. \*

31

AL. GAVANA.

MAL AL COLOR OF

# Connection digram is shown in fig. 8, Page 31

## TRUTH TABLE

|                        | Input | 3     |                               | Outputs                    |                             |                        |                  |    |                                           |  |  |  |

|------------------------|-------|-------|-------------------------------|----------------------------|-----------------------------|------------------------|------------------|----|-------------------------------------------|--|--|--|

| A1/A3                  |       | A2/A4 | <sup>B</sup> 2/B <sub>4</sub> | WHEN<br>C <sub>IN</sub> =0 | / w                         | HBN<br>2 <sup>=0</sup> | WHEN             |    | EN C2=1                                   |  |  |  |

| Maarinka sige oo saa k |       |       |                               | 1/3                        | <sup>2</sup> / <sub>4</sub> | °2/°4                  | <sup>1</sup> / 3 | 2/ | <sup>C</sup> <sub>2</sub> / <sub>C4</sub> |  |  |  |

| L                      | L     | L     | L                             | L                          | L                           | L                      | Н                | L  | L                                         |  |  |  |

| H                      | L     | L     | L                             | H                          | T ,                         | L                      | L                | H  | L                                         |  |  |  |

| L                      | H     | L     | L                             | н                          | L                           | B                      | L                | H  | L                                         |  |  |  |

| H                      | H     | Г     | L                             | Ľ                          | Ħ                           | L                      | H                | H  | L                                         |  |  |  |

| L                      | L     | H     | L                             | L                          | H                           | L                      | H                | H  | L                                         |  |  |  |

| H                      | L     | H     | L                             | H                          | H                           | L                      | L                | L  | H                                         |  |  |  |

| L                      | H     | H     | L                             | H                          | H                           | L                      | L                | L  | H                                         |  |  |  |

| H                      | H     | H     | L                             | L                          | L                           | н                      | H                | L  | H                                         |  |  |  |

| L                      | L     | L     | H                             | L                          | H                           | L                      | Ħ                | H  | L                                         |  |  |  |

| H                      | L     | L     | H                             | Ħ                          | H                           | L                      | L                | L  | H                                         |  |  |  |

| L                      | H     | L     | H                             | H                          | H                           | L                      | L                | L  | H                                         |  |  |  |

| H                      | H     | L     | H                             | L                          | L                           | H                      | H                | L  | н                                         |  |  |  |

| L                      | L     | H     | H                             | L                          | L                           | H                      | H                | L  | H                                         |  |  |  |

| Н                      | L     | H     | H                             | H                          | L                           | H                      | L                | H  | H                                         |  |  |  |

| L                      | H     | H     | H                             | H                          | L                           | H                      | L                | H  | H                                         |  |  |  |

| Ħ                      | H     | H     | H                             | L                          | H                           | H                      | H                | H  | H                                         |  |  |  |

|                        |       |       |                               |                            |                             |                        |                  |    |                                           |  |  |  |

Note: Input conditions at  $A_1, A_2, B_1, B_2$  and  $C_{1N}$  are used to determine outputs 1 and 2 and the value of internal carry  $C_2$ . The values at  $C_2, A_3, B_3, A_4$  and  $B_4$  are then used to determine outputs 3 4 and  $C_4$

### CHAPTER 4

#### THE EQUIPMENT AND ITS DESIGN

## 4.1 <u>DESIGN PHILOSOPHY</u>: (RELIABILITY EVALUATION THROUGH PATH SEDS AND CUT SETS).

Design approach is well explained by the following illustrative examples.

Consider the system given in [fig9A.page.34.] and the Table shown in [fig....page.37...] Let state [1] represents that a path is conducting and state [0] represents that a path is non-conducting.

Each element in the network has two states (a) conducting (b) non-conducting. There are four such elements in the system under consideration. Therefore, the maximum possible states in which the system can exists are 2<sup>4</sup> i.e. 16. These 16 states are shown in [table.]..page. 37. column. 2....] These states can be generated by binary generator.

Further a signal can flow from node 'X' to node 'Y' when (a) There is a path between X and Y and (b) Signal is present at node X

In other words it can be said that signal flows from

SYSTEM UNDER CONSIDERATION

FIS. OA

;

ARROW INDICATES DIRECTION OF SIGNAL FLOW

LOGICAL SYSTEM RERRESENTATION

F19.98

Fig. 9

A.S. GAVANE ME II SEOR 1977 node X to node Y only when conditions (a) AND (b) both exists. This is equivalent of having a 2-input AND gate between X and Y.

Therefore we represent each element of the given system by a 2-input AND gate which transmits the signal in a direction in which the original element transmitts one terminal of each AND gate is used to form the given system network configuration and other terminal of each AND gate is supplied from the out put of binary generation.

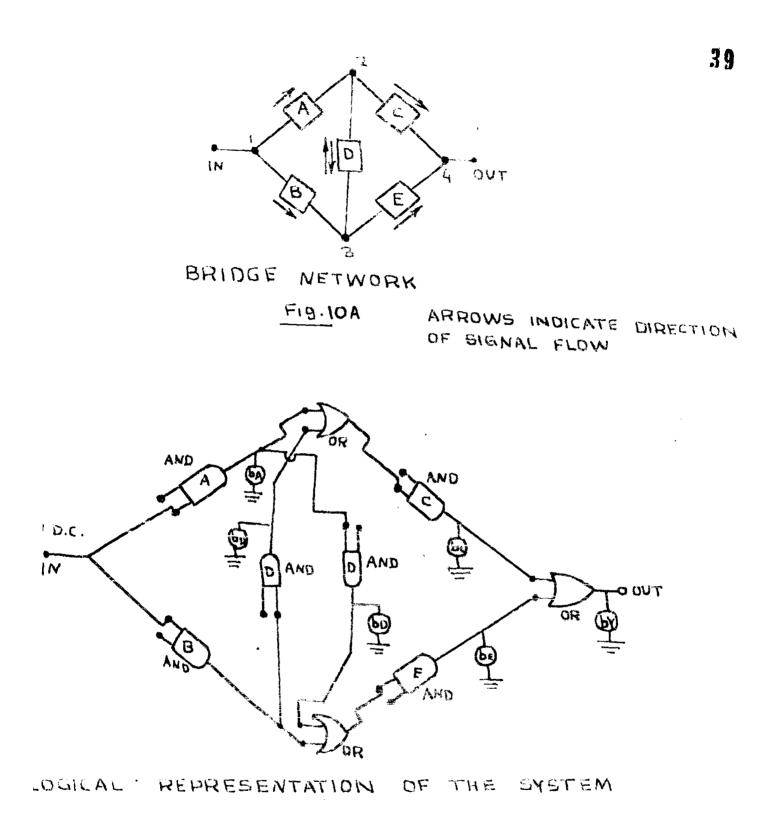

If the 'Signal Inputs' (Excluding the binary input to AND gated network) +O a AND gate (which is representing a particular element in thenetwork) are more than one, then these inputs are applied to the AND gate through an OR gate e.g. in the system of [fig.9A.page.34.] a OR gate is needed at node 3. The input to this OR gate is from the out put of, AND gate -A, AND gate-C, and AND gate D to obtain the out put indication. Similarly for the system of [fig.10A page.39...], OR gates are necessary at node 2,3 and 4 as showng

Now the state vectors for which the given system gives through and through passage to the input signal are noted [i.e. state vectors corresponding to 'l' out put in column-3 of table..l..page [37] These state vectors are the various 'PATH SETS' of the system and their sum gives the reliability of the given system.

Let  $p_A$ ,  $p_B$ ,  $p_c$  and  $p_D$  represents the reliabilities of the network elements A,B,C and D. Then reliability of whole network can be written as

$$B = p_{A} \cdot q_{B} \cdot q_{C} + p_{A} \cdot p_{B} \cdot q_{C} \cdot q_{D} + p_{A} \cdot q_{B} \cdot p_{C} \cdot q_{D} + q_{A} \cdot p_{B} \cdot q_{C} \cdot p_{D}$$

$$+ p_{A} \cdot p_{B} \cdot p_{C} \cdot q_{D} + p_{A} \cdot q_{B} \cdot q_{C} \cdot p_{D} + q_{A} \cdot p_{B} \cdot q_{C} \cdot p_{D}$$

equation..(1)

The state vectors which do not give passage to the input signal (i.e. the state gectors corresponding to 'O' of the column-3 table...page.....] are known as CUT-SETS and their sum gives the expression the un-reliability (Q)

$$d = [d^{\mathbf{V}} d^{\mathbf{B}} d^{\mathbf{C}} d^{\mathbf{D}} + d^{\mathbf{V}} d^{\mathbf{B}} d^{\mathbf{C}} d^{\mathbf{D}} + d^{\mathbf{V}} d^{\mathbf{B}} d^{\mathbf{C}} d^{\mathbf{D}} ]$$

(5)

The reliability of the given sysem is then found by the relation

R = [1-Q] .... (3)

TABLE -1

| unn                                                  | Col | บ⊐n-2                                    |      |      | Colur                        | Colum-5 |    |                                                        | Column-4 Column |      |                                     |  |            |  |

|------------------------------------------------------|-----|------------------------------------------|------|------|------------------------------|---------|----|--------------------------------------------------------|-----------------|------|-------------------------------------|--|------------|--|

| lco                                                  | tho | ary o<br>inut<br>ed no<br>X <sub>C</sub> | or A | LD - | Stato<br>of out-<br>put node | )       | 5D | Binary<br>at the<br>of AUD<br>notwor<br><sup>D</sup> C | ou<br>ga        | tput | 5<br>Outpu<br>fron<br>final<br>gago |  | 6<br>Patho |  |

| <b>ىلەتتىكە بىرىي</b> رىدىنىيىرىدىنىيىرىدىكە.بىرىدىي | 0   | 0                                        | 0    | 0    | Ο                            | CUP     | 0  | 0                                                      | 0               | 0    | 0                                   |  |            |  |

|                                                      | 0   | 0                                        | 0    | 1    | 1                            | PATH    | 0  | 0                                                      | 0               | 1    | 1                                   |  | A          |  |

|                                                      | 0   | 0                                        | 2    | 0    | 0                            | CUT     | 0  | 0                                                      | 1               | 0    | 0                                   |  |            |  |

|                                                      | 0   | 0                                        | 1    | 1    | 1                            | Path    | 0  | 0                                                      | 1               | 1    | 1                                   |  | ۵D*        |  |

|                                                      | 0   | 1                                        | 0    | 0    | 0                            | CUT     | 0  | 0                                                      | 0               | 0    | 0                                   |  |            |  |

|                                                      | 0   | 1                                        | 0    | 1    | 1                            | PATH    | 1  | 0                                                      | 0               | 1    | 0                                   |  |            |  |

|                                                      | 0   | 1                                        | 1    | 0    | 1                            | Path    | 0  | 1                                                      | 1               | 0    | 1                                   |  | EC         |  |

|                                                      | 0   | 1                                        | 1    | 1    | 1                            | PATH    | 0  | 1                                                      | 1               | 1    | 1                                   |  | ABC        |  |

|                                                      | 1   | 0                                        | 0    | 0    | 0                            | CUT     | 0  | 0                                                      | 0               | 0    | 0                                   |  |            |  |

|                                                      | 1   | 0                                        | 0    | 1    | 2                            | PATH    | 0  | 0                                                      | 0               | 1    | 0                                   |  |            |  |

| )                                                    | 1   | 0                                        | 1    | 0    | 2                            | Path    | 1  | 0                                                      | 1               | 0    | 1                                   |  | BD         |  |

| •                                                    | 1   | 0                                        | 1    | 1    | 1                            | Path    | 1  | 0                                                      | 1               | 1    | 1                                   |  | ABD        |  |

|                                                      | 1   | 1                                        | 0    | 0    | 0                            | Cut     | 0  | 0                                                      | 0               | 0    | 0                                   |  |            |  |

|                                                      | 1   | 1                                        | 0    | 2    | 1                            | PATH    | 0  | 0                                                      | 0               | 1    | 0                                   |  |            |  |

| <b>)</b>                                             | 1   | 1                                        | 1    | 0    | 1                            | ратн    | 1  | 1                                                      | 1               | 0    | 1                                   |  | BCD        |  |

| )                                                    | 1   | 1                                        | 1    | 1    | 1                            | ратн    | 1  | 1                                                      | 1               | 1    | 1                                   |  | ABCD       |  |

# Hotos

1. (9) Earkod pulce numbers are the desired pulse number to which the equipment should respond.

2.(\*) marked pulse number are the pulses which gives the undesired out put signal.

37

ø

Thus in general the various path-sets and cut-sets of the any given system can be found by the following procedure.

'Represent each element of the given system network by a 2-input AND gate. One terminal of each AND gate is used to form the given network configuration. The other terminal of each AND gate is supplied from the out put of binary generator. Use OR gate of signal input to the AND gate is more than one. Also use OR gate at out put node if out put is obtained from more than one source. Each input state vector which gives the out put indication represents a path set. Each input satate vector which does not give out put indication represents cut-sets. The reliability of the network between input and output node is then evaluated as explained by the above example'

This is the simplest way of evaluating reliability through path-sets and cut-sets. When the network grows complex and complex, the expression for reliability contains a large numbers of terms. This in turn needs large memory and increased mathematical operations if the equipment is to be made automatic and reliability of given system is desired in digital form.

## 4.2 <u>DESIGN PHILOSOPHY</u>:

## RELIABILITY EVALUATION THROUGH MINIMAL PATH SETS AND MINIMAL CUT SETS (DESIGN APPROACH)

The relability expression can also be determined if

Fig. 10B

F19. 10

A.S. GAVANE M.E.T. SEDR 1977 one can find out the paths of warious sizes existing in the system network under consideration.

Consider the system of [fig. Apage. 39..]. This system is a case of non-series parallel network. Since the network is of practical size, therefore paths of various sizes can be found out by inspection.

| Paths of | size        | 1 | \$ | None                           |

|----------|-------------|---|----|--------------------------------|

| Paths of | <b>size</b> | 2 | 8  | (A,C), (B.E.)                  |

| Paths of | 8120        | 3 | \$ | (A,D.E), (B,D,C,)              |

| Paths of | size        | 4 | \$ | (A,B,D,C), \$A,B,D,E,),        |

|          | ·           |   |    | (A, D, C, E, ), (B, D, C, E, ) |

|          |             |   |    | (A,C,B,E,)                     |

|          |             |   |    |                                |

\$

Paths of size 5

(A,B,C,D,E,), (A,B,C,D,E,

Here (A,C,), (B,E), (A,D,E,), (B,D,C,) are the forward paths are minimal paths. The remaining (A,B,D,C,), (A,B,D,E,), (A,D,C,E,), (B,D,C,E,), (A,C,B,B,), (A,B,C,D,E,) and (A,B,C,D,E,) are various 'forward paths with lopp'

Reliability expression is then given by

If  $p_A$ ,  $p_B$ ,  $p_C$ ,  $p_D$  and  $p_R$  are the reliabilities of elements

| lunn                                                                                                            | Ċ               | olu |      | 2           |      | Column-y Colu              |        |                          | 1125     | n-4 | •        |          | Column-5                            | Column-6         |

|-----------------------------------------------------------------------------------------------------------------|-----------------|-----|------|-------------|------|----------------------------|--------|--------------------------|----------|-----|----------|----------|-------------------------------------|------------------|

| loo<br>nbor                                                                                                     | at<br>All       | th  | .0 1 | npu<br>d no | t of | Stat<br>of<br>outp<br>nodo | ut Sot | the<br>ADD<br><u>N9X</u> | 00<br>00 | tod | nt<br>nc | 20<br>\$ | Output<br>from<br>final and<br>gato | Paths            |

| and the second secon | I <sub>II</sub> | X)  | ×c   | Ľ,          | X    |                            |        | D<br>E                   | D<br>D   | D   | d<br>B   | ð<br>A   |                                     |                  |

|                                                                                                                 | 0               | 0   | 0    | 0           | 0    | 0                          | CUT    | 0                        | 0        | 0   | Ò        | 0        | 0                                   |                  |

|                                                                                                                 | 0               | 0   | 0    | 0           | 1    | 0                          | CUT    | 0                        | 0        | 0   | 0        | 1        | 0                                   |                  |

|                                                                                                                 | 0               | 0   | 0    | 1           | 0    | 0                          | CUT    | 0                        | 0        | 0   | 1        | 0        | O                                   |                  |

|                                                                                                                 | 0               | 0   | 0    | 1           | 1    | 0                          | CUT    | 0                        | 0        | 0   | 1        | 1        | 0                                   |                  |

|                                                                                                                 | Q               | 0   | 1    | 0           | 0    | 0                          | CUT    | 0                        | 0        | 0   | 0        | 0        | 0                                   |                  |

| ł                                                                                                               | 0               | 0   | 1    | 0           | 1    | 1                          | PATH   | 0                        | 0        | 1   | 0        | 1        | 1                                   | AC               |

|                                                                                                                 | 0               | 0   | 1    | 1           | 0    | 0                          | Cut    | 0                        | 0        | 0   | 1        | 0        | 0                                   |                  |

| ξ.                                                                                                              | 0               | 0   | 1    | 1           | 1    | 1                          | PATH   | 0                        | 0        | 1   | 1        | 1        | 1                                   | ACB *            |

|                                                                                                                 | 0               | 1   | 0    | 0           | 0    | 0                          | CUT    | 0                        | 0        | 0   | 0        | 0        | 0                                   |                  |

|                                                                                                                 | 0               | 1   | 0    | 0           | 1    | 0                          | CUT    | 0                        | 1        | 0   | 0        | 1        | 0                                   |                  |

| )                                                                                                               | 0               | 1   | 0    | 1           | 0    | 0                          | Cut    | 0                        | 1        | 0   | 1        | 0        | 0                                   |                  |

| i i                                                                                                             | 0               | 1   | 0    | 1           | 1    | 0                          | CUT    | 0                        | 1        | 0   | 1        | 1        | 0                                   |                  |

| 1                                                                                                               | 0               | 1   | 1    | 0           | 0    | 0                          | CUT    | 0                        | 0        | 0   | 0        | 0        | 0                                   |                  |

| ×                                                                                                               | 0               | 1   | 1    | 0           | 1    | 1                          | PATH   | 0                        | 1        | 1   | 0        | 1        | 1                                   | ACD*             |

| Ŷ                                                                                                               | 0               | 1   | 1    | 1.          | 0    | 1                          | PATH   | 0                        | 1        | 1   | 1        | 0        | 1                                   | BCD              |

|                                                                                                                 | 0               | 1   | 1    | 1           | 1    | 1                          | PATH   | 0                        | 1        | 1   | 1        | 1        | 1                                   | ABDO             |

| I                                                                                                               | 1               | 0   | 0    | 0           | 0    | 0                          | CUT    | 0                        | Q        | 0   | 0        | 0        | 0                                   |                  |

| 1                                                                                                               | 1               | 0 - | 0    | 0           | 1    | 0                          | CUT    | 0                        | 0        | 0   | 0        | 1        | 0                                   |                  |

| ,₽<br>                                                                                                          | 1               | 0   | 0    | 1           | 1    | 1                          | Ратн   | 1                        | 0        | 0   | l        | 0        | 1                                   | BE               |

| ×                                                                                                               | 1               | 0   | 0    | 1           | 1    | 1                          | PATH   | 1                        | 0        | 0   | 1        | 1        | 1                                   | BEA <sup>*</sup> |

| )                                                                                                               | 1               | 0   | 1    | 0           | 0    | 0                          | CUT    | 0                        | 0        | 0   | 0        | 0        | 0                                   |                  |

| ,                                                                                                               | 1               | 0   | 1    | 0           | 1    | 1                          | рлтн   | 0                        | 0        | 2   | 0        | 1        | 0                                   |                  |

| )<br>;                                                                                                          | 1               | 0   | 1    | 2           | 0    | 1                          | PAPH   | l                        | 0        | 0   | 1        | 0        | 0                                   |                  |

>le contd...

|   |   |   |   | - |   |   | ***  | and the second state of th |   |   |   |   | والمراجعة ويشمر فتتلقنا مابيه فالم |       |

|---|---|---|---|---|---|---|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|------------------------------------|-------|

| ) | 1 | 0 | 1 | 1 | 1 | 1 | PATH | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0 | 1 | 1 | 1 | 1                                  | ABCE  |

|   | 1 | 1 | 0 | 0 | 0 | 0 | OUT  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0 | 0 | 0 | 0 | 0                                  |       |

| ) | 1 | 1 | 0 | 0 | 1 | 1 | PATH | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1 | 0 | 0 | 1 | 1                                  | ADB   |

| t | 1 | 1 | 0 | 1 | 0 | 1 | PATH | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1 | 0 | 1 | 0 | 1                                  | BED*  |

| ) | 1 | 1 | 0 | 1 | 1 | 1 | PATH | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1 | 0 | 1 | 1 | 1                                  | ABDE  |

|   | 1 | 1 | 1 | 0 | 0 | 0 | CUT  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0 | 0 | 0 | 0 | 0                                  |       |

| • | 1 | 1 | 1 | 0 | 1 | 1 | PATH | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1 | 1 | 0 | 1 | 1                                  | ADCE  |