# NANOSCALE FINFETS: DEVICE AND CIRCUIT DESIGN METHODOLOGY

# **A DISSERTATION**

Submitted in partial fulfillment of the requirements for the award of the degree

of

MASTER OF TECHNOLOGY

in

ELECTRONICS AND COMMUNICATION ENGINEERING (With Specialization in Semiconductor Devices and VLSI Technology)

By

SAURABH KUMAR NEMA

DEPARTMENT OF ELECTRONICS AND COMPUTER ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE-247 667 (INDIA) JUNE, 2010 I hereby declare that the work which is being presented in this dissertation report, entitled "Nanoscale FinFET: Device and Circuit Design Methodology", and is being submitted in partial fulfillment of the requirements for the award of the degree of Master of Technology in Semiconductor Devices and VLSI Technology, in the Department of Electronics and Computer Engineering, Indian Institute of Technology Roorkee, is an authentic record of my own work, carried out from June 2009 to June 2010, under the guidance and supervision of Dr. Anand Bulusu, Assistant Professor and Dr. A. K. Saxena, Professor, Department of Electronics and Computer Engineering, Indian Institute of Technology Roorkee.

The results embodied in this dissertation have not been submitted for the award of any other Degree or Diploma.

Date: 24/06/2010 Place: Roorkee

Saurabh Kumar Nema

#### CERTIFICATE

This is to certify that the statement made by the candidate is correct to best of my knowledge and belief.

Date: 24/6/10 Place: Roorkee

R . Anand

**Dr. Anand Bulusu,** Assistant Professor, Department of Electronics & Computer, Indian Institute of Technology, Roorkee

pesad en

**Dr. A. K. Saxena,** Professor, Department of Electronics & Computer, Indian Institute of Technology, Roorkee

Date: 3€1611♥ Place: Roorkee

# ACKNOWLEDGEMENT

I would like to express my deep and sincere gratitude to my supervisor, Dr. Anand Bulusu, Assistant Professor, Department of Electronics and Computer Engineering at Indian Institute of Technology Roorkee. His supervision, advice, and guidance from the very early stage of this research as well as giving me extraordinary experiences throughout the work have been of great value for me not only for this work but also for my life. Above all he provided me steady encouragement, care and support in various ways throughout my work. Working under him will always be a pleasant experience in my memory.

I gratefully acknowledge to Dr. A. K. Saxena, Professor, Department of Electronics and Computer Engineering at Indian Institute of Technology Roorkee for his advice, guidance and support as my supervisor. I am indebted to him for his lectures on physical electronics and semiconductor materials, which immensely helped me in understanding concepts of Nano-scale FinFET, which made him a backbone of this research and so to this thesis. He gave me freedom to explore ideas on my own and guided whenever I was in need for help. Again I gratefully thank him for his valuable comments on this thesis.

I am very grateful to Dr. Sanjeev Manhas and Dr. Sudeb Dasgupta for their comments and guidance on my work time to time.

I am very grateful to Angnada B. Sachid and Mayank Srivastava research scholar, IIT Bombay, for guiding me the fundamentals of tool, and device design which we used in this work. They are my role models for hard work.

I would like to convey my sincere gratitude to my senior and friend Tapas Dutta, who helped and guided me throughout my work in all matters regarding Sentaurus simulations and device designing concepts.

My hearty thanks to all my friends and research scholars of Microelectronics and VLSI lab their help and support during my dissertation work. I extend my sincere thanks to rest of the faculty in the Department of Electronics and Computer Engineering at Indian Institute of Technology Roorkee, from whom I learned a lot.

ii

My parents deserve special mention for their inseparable support, love and prayers. They are source of my motivation and cause of my being at this position, also lots of thanks for my loving and caring siblings.

> Saurabh Kumar Nema, M. Tech. (SDVT), IIT Roorkee.

# ABSTRACT

Double gate FinFET has emerged as one of the most promising device that can replace bulk MOSFET as we approach sub-45 nm technologies. In these devices, the short channel effects are reduced because of better gate control and the use of a thin and lightly doped channel. In this dissertation report, a detailed analysis of the various scaling issues pertaining to DG FinFETs has been carried out through 2D simulations using a state of the art device simulator. Underlap FinFET device is used in this work because of it's superior subthreshold leakage immunity than overlap FinFET devices.

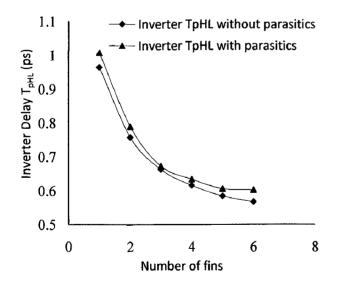

For analyzing circuit aspects of FinFET device, a Standard Cell consisting Inverter, NAND, NOR and SR Latch were simulated using mixed mode simulation with and without external parasitics. We observed that in combinational cells, impact of internal parasitics of the device is much more than that of interconnect parasitics.

We propose an optimized FinFET device design, such that circuit performance is improved. The Source/Drain extension parameters that we consider are pad doping concentration, extension spacer dielectric constant, gate oxide thickness ( $t_{ox}$ ), asymmetric doping profile and asymmetric spacer dielectric constants on source-drain side ( $K_{S Ext}$ ). We observed that by optimizing  $t_{ox}$ ,  $K_{S Ext}$  device performance can be further improved. The value of  $t_{ox}$  much more than its ITRS projected value can be used. We show using simulation that applying asymmetric device design with source spacer of a high dielectric constant improves device performance significantly.

iv

# **List of Figures**

| Title of Figure                                                                     | Page |

|-------------------------------------------------------------------------------------|------|

| Figure 2.1: The millions of instructions per second that can be purchased with      | 4    |

| \$1, showing growth path of semiconductor industry                                  |      |

| Figure 2.2: Schematic cross-section of planar bulk MOSFET                           | 5    |

| Figure 2.3: Cross-section of a tri-gate FinFET [27]                                 | 9    |

| Figure 3.1: (a) 3D structure of a FinFET (b) Cross-sectional view of the gate       | 12   |

| region                                                                              |      |

| Figure 3.2: N-channel underlap FinFET structure with Gaussian doping profile        | 13   |

| in extension regions                                                                |      |

| Figure 3.3: N-channel underlap FinFET structure doping profile                      | 14   |

| Figure 3.4: (a) Gate-First Process (b) Cross-sectional SEM and TEM images           | 14   |

| Figure 3.5: Fabrication sequence of a Gate-Last and Cross section of the silicon    | 15   |

| fin showing the current-carrying plane                                              |      |

| Figure 3.6: Typical tool flow for device simulation using Sentaurus Device          | 18   |

| Figure 3.7: A typical 2D FinFET structure used in the Sentaurus simulations         | 18   |

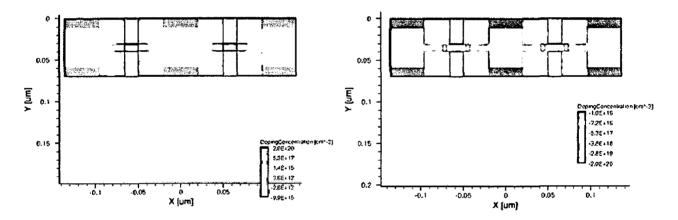

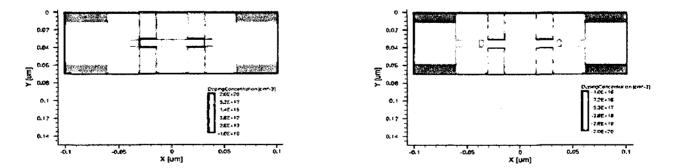

| Figure 4.1: Cross sectional top view of a FinFET, (a) overlap & (b) underlap        | 26   |

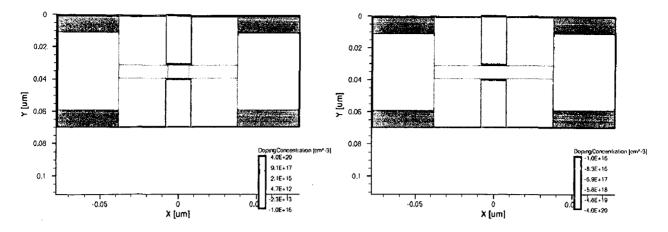

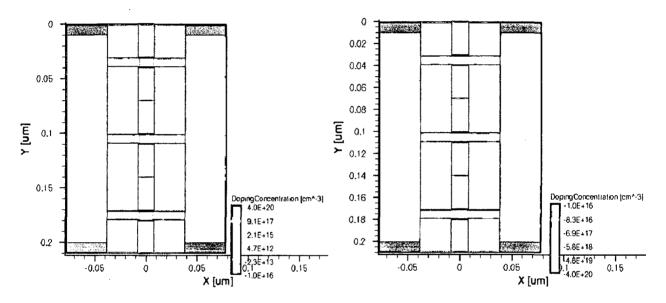

| Figure 4.2: Overlap device structure of single fin N-channel FinFET and P-          | 28.  |

| channel FinFET                                                                      |      |

| Figure 4.3: Overlap device structure of three fins N-channel FinFET and P-          | 28   |

| channel FinFET                                                                      |      |

| Figure 4.4: Underlap device structure of single fin N-channel FinFET and P-         | 28   |

| channel FinFET                                                                      |      |

| Figure 4.5: Device structure of multiple fins (three fins) N-channel FinFET and     | 29   |

| P-channel FinFET                                                                    |      |

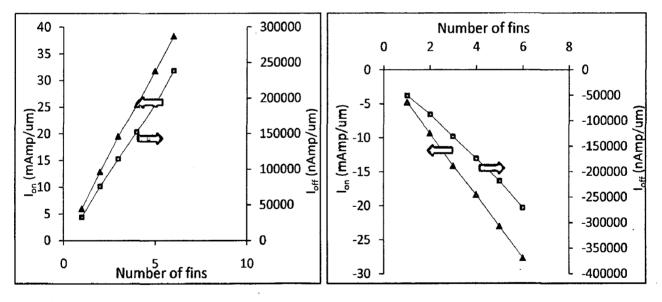

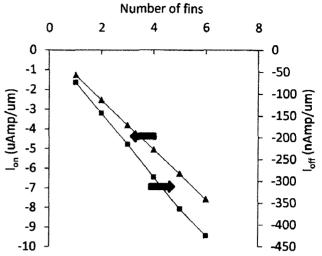

| Figure 4.6: $I_{on}$ and $I_{off}$ of overlap n-channel FinFET vs number of fins    | 29   |

| Figure 4.7: and $I_{off}$ of underlap p-channel FinFET vs. number of fins           | 29   |

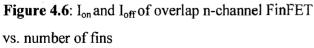

| Figure 4.8: $I_{on}$ and $I_{off}$ of underlap n-channel FinFET vs. number of fins  | 30   |

| Figure 4.9: $I_{on}$ and $I_{off}$ of underlap p-channel FinFET vs. number of fins  | 30   |

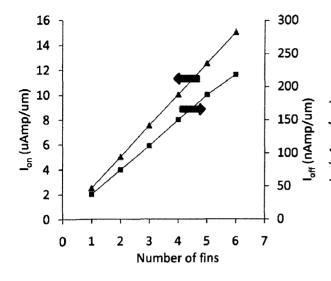

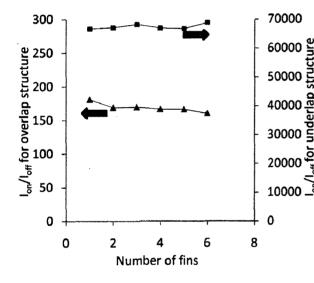

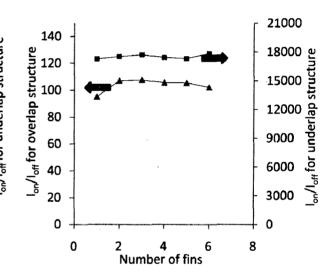

| Figure 4.10: $I_{on}/I_{off}$ for overlap & underlap n-channel FinFET vs. number of | 30   |

| fins                                                                                |      |

| Figure 4.11: $I_{on}/I_{off}$ for overlap & underlap p-channel FinFET vs. number of fins                                      | 30 |

|-------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 4.12: Parallel combinations of two n-channel and p-channel single fin FinFET devices                                   | 31 |

| <b>Figure 4.13</b> : Series combinations of two n-channel and p-channel single fin<br>FinFET devices                          | 31 |

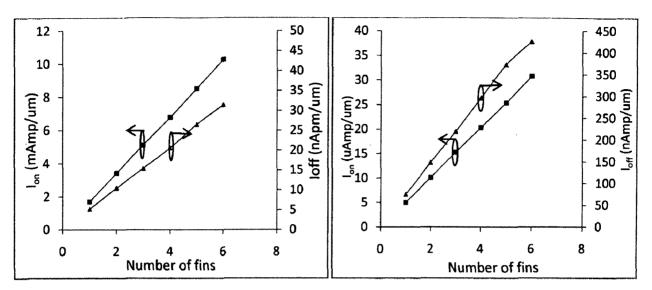

| <b>Figure 4.14</b> : $I_{on}$ and $I_{off}$ of series combination of two n-channels FinFET with multiple fins                 | 32 |

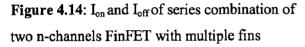

| <b>Figure 4.15</b> : I <sub>on</sub> and I <sub>off</sub> of parallel combination of two n-channels FinFET with multiple fins | 32 |

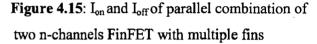

| <b>Figure 4.16</b> : $I_{on}$ and $I_{off}$ of series combination of two p-channels FinFET with multiple fins                 | 32 |

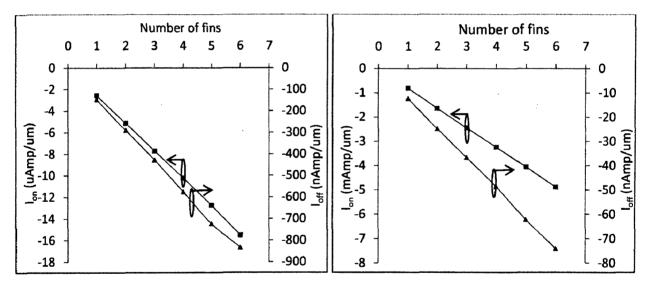

| <b>Figure 4.17:</b> $I_{on}$ and $I_{off}$ of parallel combination of two p-channels FinFET with multiple fins                | 32 |

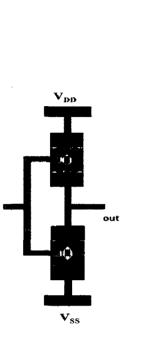

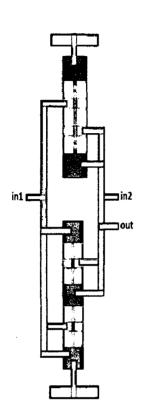

| Figure 4.18: Layout used for Inverter                                                                                         | 33 |

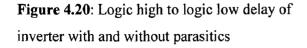

| Figure 4.19: Layout used for NAND-2                                                                                           | 33 |

| Figure 4.20: $T_{pHL}$ delay of inverter with and without parasitics                                                          | 33 |

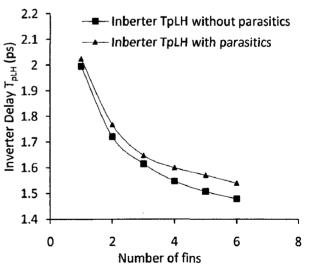

| Figure 4.21: $T_{pLH}$ delay of Inverter with and without parasitics                                                          | 33 |

| Figure 4.22: Layout used for NOR-2                                                                                            | 34 |

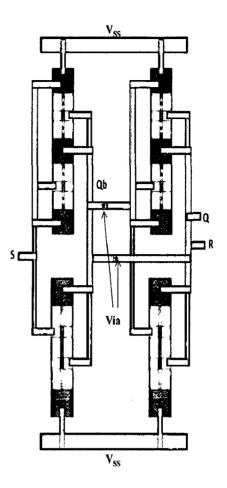

| Figure 4.23: Layout used for SR NAND latch                                                                                    | 34 |

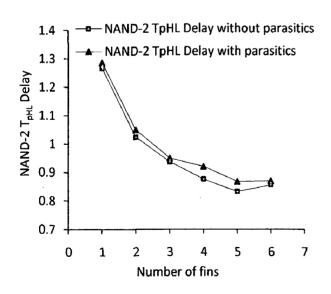

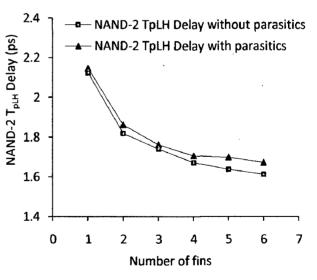

| Figure 4.24: T <sub>pHL</sub> delay of 2-input NAND gate with and without parasitics                                          | 34 |

| Figure 4.25: $T_{pLH}$ delay of 2- input NAND gate with and without parasitics                                                | 34 |

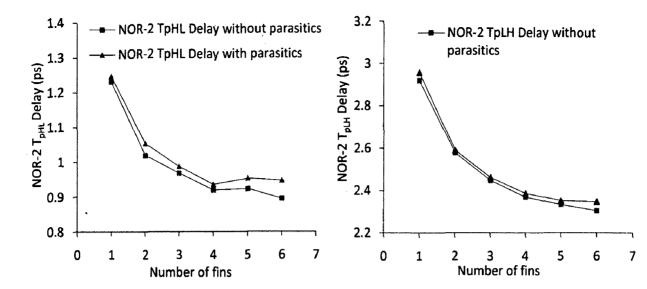

| Figure 4.26: T <sub>pHL</sub> delay of 2- input NOR gate with and without parasitics                                          | 35 |

| Figure 4.27: T <sub>pLH</sub> delay of 2- input NOR gate with and without parasitics                                          | 35 |

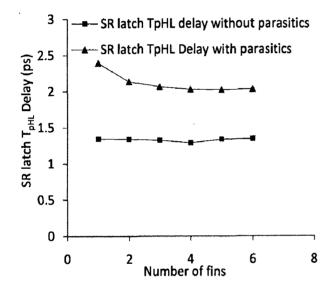

| Figure 4.28: T <sub>pHL</sub> delay of SR latch by NAND gate with and without parasitics                                      | 35 |

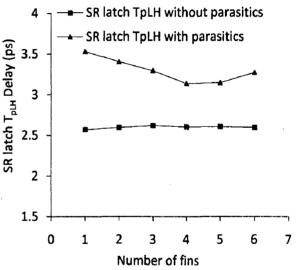

| Figure 4.29: $T_{pLH}$ delay of SR latch by NAND gate with and without parasitics                                             | 35 |

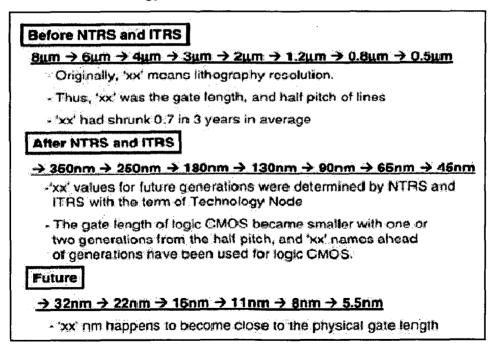

| Figure 5.1: Meaning of "xx nm" Technology                                                                                     | 37 |

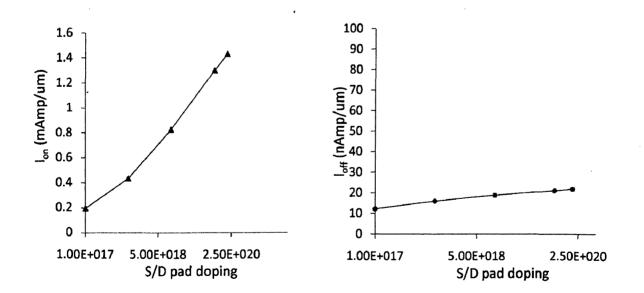

| Figure 5.2: Ion with varying pad S/D doping                                                                                   | 38 |

| Figure 5.3: I <sub>off</sub> with varying pad S/D doping                                                                      | 38 |

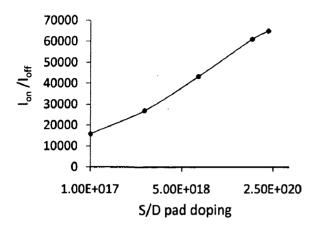

| Figure 5.4: I <sub>on</sub> /I <sub>off</sub> with varying pad S/D pad doping                                                 | 39 |

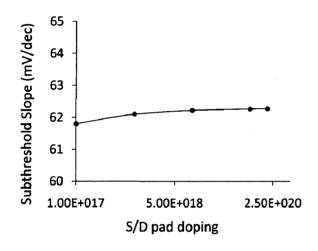

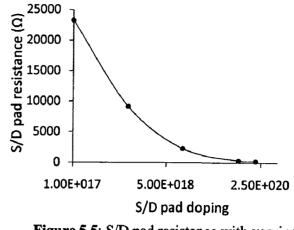

| Figure 5.5: S/D pad resistance with varying S/D pad doping                                                                    | 39 |

.

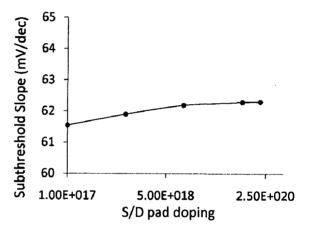

| Figure 5.6: Variation of SS with S/D pad doping at $V_d = 0.05V$                       | 39   |

|----------------------------------------------------------------------------------------|------|

| Figure 5.7: Variation of SS with S/D pad doping at $V_d = 1V$                          | 39   |

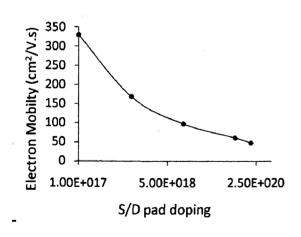

| Figure 5.8: Electron mobility (cm <sup>2</sup> /V.s) with varying S/D pad doping       | 39   |

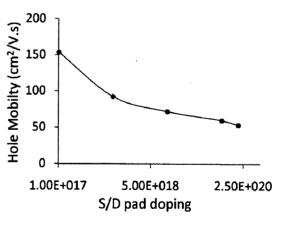

| Figure 5.9: Hole mobility (cm <sup>2</sup> /V.s) with varying S/D pad doping           | 39   |

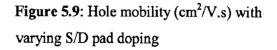

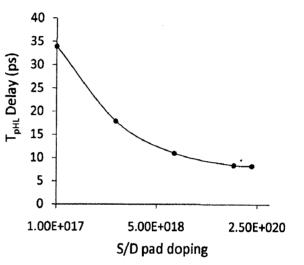

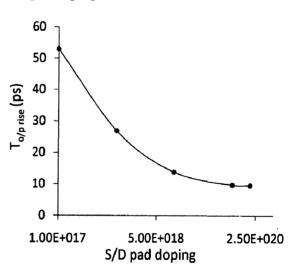

| Figure 5.10: Variation of inverter T <sub>pHL</sub> with S/D pad doping                | 40   |

| Figure 5.11: Variation of inverter T <sub>pHL</sub> with S/D pad doping                | 40   |

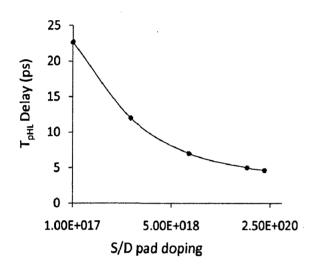

| Figure 5.12: Variation of $T_{o/p fall}$ with S/D pad doping                           | 40   |

| Figure 5.13: Variation of $T_{o/p fall}$ with S/D pad doping                           | 40   |

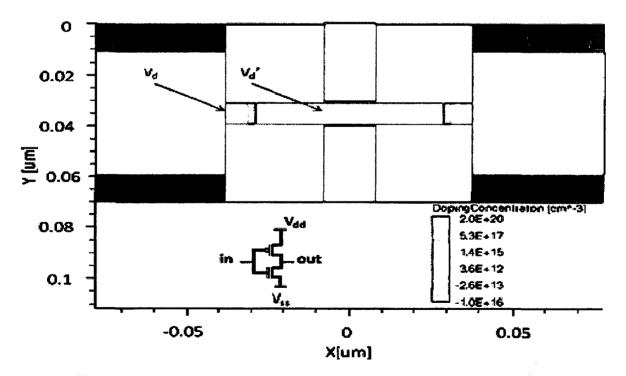

| Figure 5.14: N-channel FinFET device structure and scheme used in this work            | 41   |

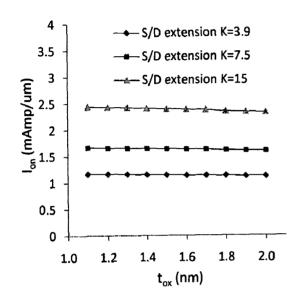

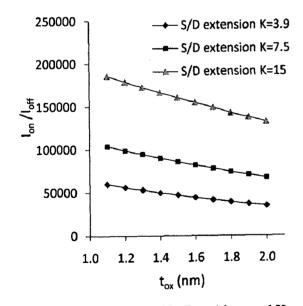

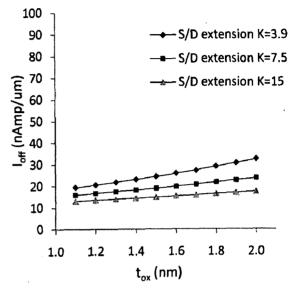

| Figure 5.15: Variation of Ion with tox and KS/D ext                                    | 42   |

| Figure 5.16: Variation of $I_{off}$ with $t_{ox}$ and $K_{S/D ext}$                    | 42   |

| Figure 5.17: Variation of $I_{on}/I_{off}$ with $t_{ox}$ and $K_{S/D ext}$             | 42   |

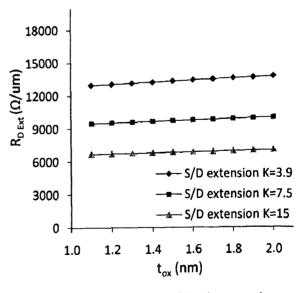

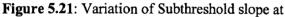

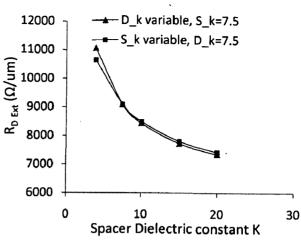

| Figure 5.18: Variation of $R_{D Ext}$ with $t_{ox}$ and $K_{S/D ext}$                  | 42   |

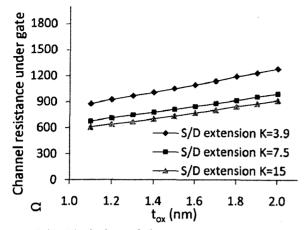

| Figure 5.19: Variation of channel resistance under gate region with $t_{ox}$ and       | 43   |

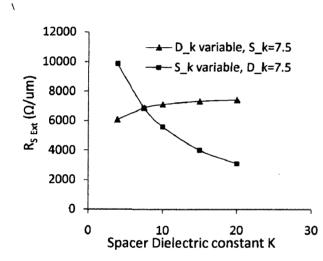

| Figure 5.20: Variation of $R_{S Ext}$ with $t_{ox}$ and $K_{S/D ext}$                  | 43   |

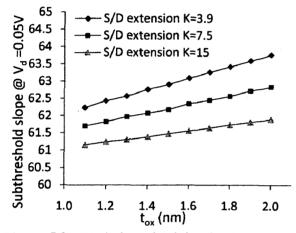

| Figure 5.21: Variation of SS at $V_d = 0.05 V$ with $t_{ox}$ and $K_{S/D ext}$         | 43   |

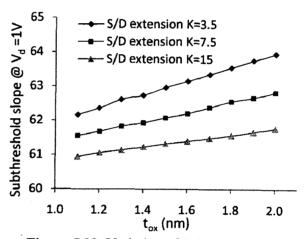

| Figure 5.22: Variation of SS at $V_d = 1$ V with $t_{ox}$ and $K_{S/D ext}$            | 43   |

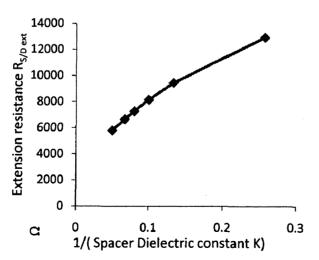

| Figure 5.23: Variation of $R_{S/D Ext}$ with 1/(spacer dielectric constant)            | 43   |

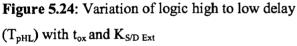

| Figure 5.24: Variation of $T_{pHL}$ delay with $t_{ox}$ and $K_{S/D ext}$              | 44   |

| Figure 5.25: Variation of $T_{pLH}$ delay with $t_{ox}$ and $K_{S/D ext}$              | 44   |

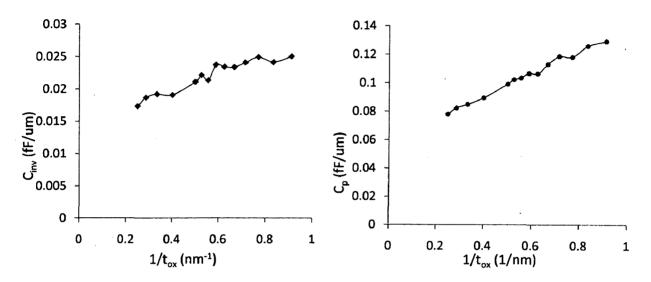

| Figure 5.26: Variation of $C_{inv}$ with $t_{ox}$ and $K_{S/D ext}$                    | 45   |

| Figure 5.27: Variation of $C_p$ with and $K_{S/D ext}$                                 | 45   |

| Figure 5.28: Variation Oscillation period and frequency of 3-stage ring                | 45   |

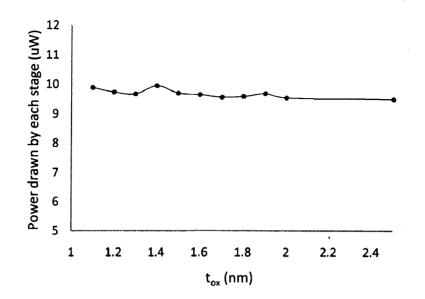

| Figure 5.29: Power drawn by each stage of 3-stage ring oscillator vs. $t_{ox}$ , K=7.5 | 46   |

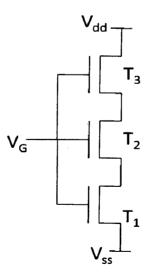

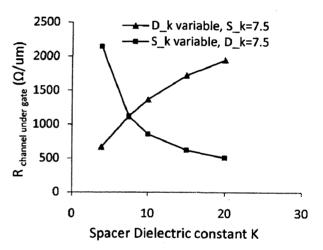

| Figure 5.30: Schematic diagram of a FinFET by 3 transistor equivalent circuit          | 46   |

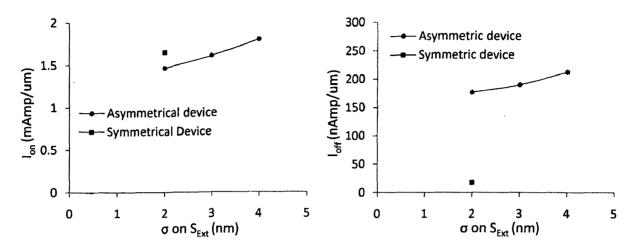

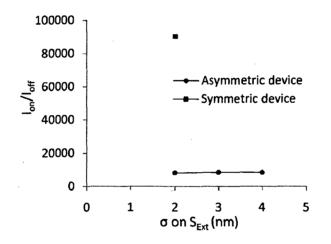

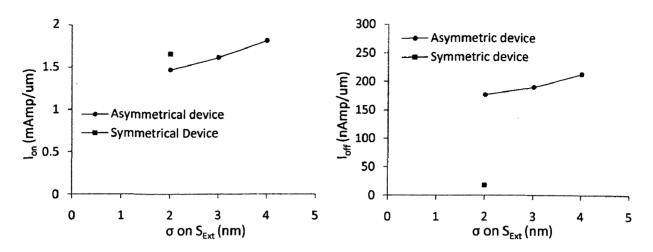

| Figure 5.31: Variation of Ion for Symmetric and Asymmetric extension profile           | - 48 |

| with $\sigma$ on $S_{Ext}$                                                             |      |

| Figure 5.32: Variation of $I_{off}$ for Symmetric and Asymmetric extension profile     | 48   |

| with $\sigma$ on $S_{Ext}$                                                             |      |

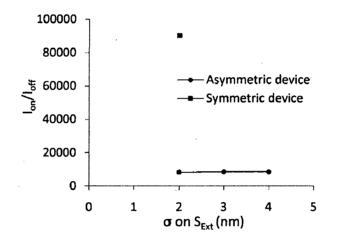

| Figure 5.33: Variation of $I_{on}/I_{off}$ for Symmetric and Asymmetric extension      | 48   |

| profile with $\sigma$ on $S_{Ext}$                                                     |      |

|                                                                                        |      |

ı.

vii

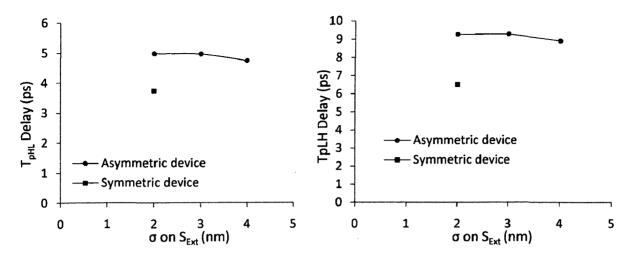

| Figure 5.34: Variation of $T_{pHL}$ Delay for Symmetric and Asymmetric extension       | 49 |

|----------------------------------------------------------------------------------------|----|

| profile with $\sigma$ on $S_{Ext}$                                                     |    |

| Figure 5.35: Variation of T <sub>pLH</sub> Delay for Symmetric and Asymmetric          | 49 |

| extension profile with $\sigma$ on $S_{Ext}$                                           |    |

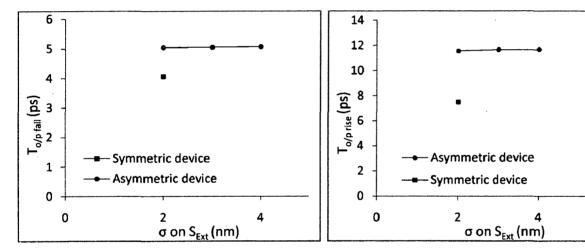

| Figure 5.36: Variation of T <sub>o/p fall</sub> for Symmetric and Asymmetric extension | 49 |

| profile with $\sigma$ on $S_{Ext}$                                                     |    |

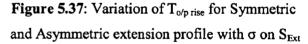

| Figure 5.37: Variation of $T_{o/p rise}$ for Symmetric and Asymmetric extension        | 49 |

| profile with $\sigma$ on $S_{Ext}$                                                     |    |

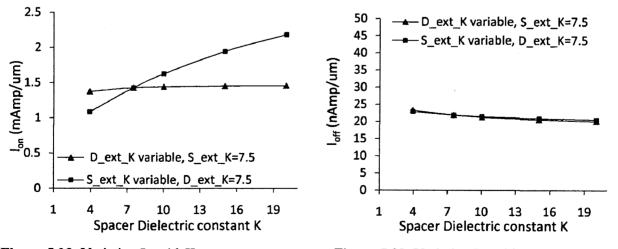

| Figure 5.38: Variation I <sub>on</sub> with K                                          | 50 |

| Figure 5.39: Variation I <sub>off</sub> with K                                         | 50 |

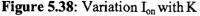

| Figure 5.40: Variation $I_{on}/I_{off}$ with K                                         | 51 |

| Figure 5.41: Variation R <sub>D Ext</sub> with K                                       | 51 |

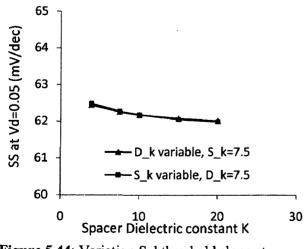

| Figure 5.44: Variation SS at $V_d$ =0.05 with K                                        | 51 |

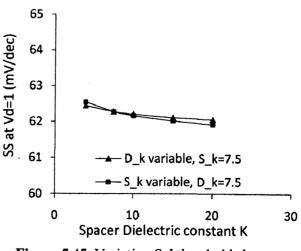

| Figure 5.45: Variation SS at $V_d=1$ with K                                            | 51 |

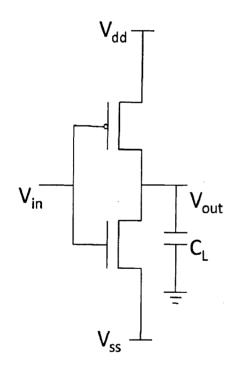

| Figure 5.46: Schematic diagram of inverter circuit                                     | 52 |

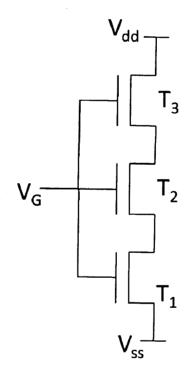

| Figure 5.47: Schematic diagram of FinFET by 3T equivalent circuit                      | 52 |

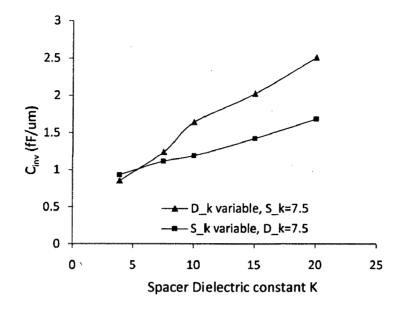

| Figure 5.48: Input capacitance of inverter $C_{inv}$ with K.                           | 53 |

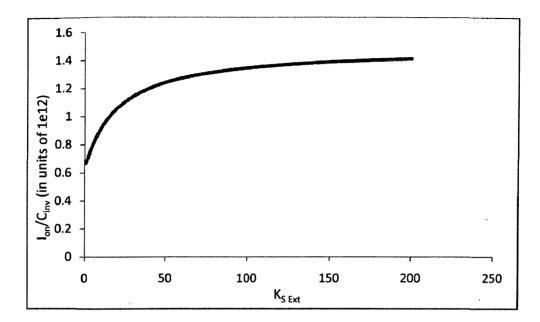

| Figure 5.49: I <sub>on</sub> /C <sub>inv</sub> with K <sub>S Ext</sub> .               | 56 |

.

# List of Tables

| Title of Table                                                       | Page No |

|----------------------------------------------------------------------|---------|

| Table 2.1: ITRS Roadmap 2003 showing the physical limits of scaling  | 7       |

| Table 3.1: Constant Mobility Model: Default coefficients for Si      | 20      |

| Table 3.2: Default parameters for the doping dependent SRH lifetimes | 22      |

| Table 3.3: Default parameters for parameters for silicon             | 23      |

| Table 4.1: Properties of various dielectrics.                        | 27      |

# List of Abbreviations

| Abbreviation      | Expansion                               |  |  |  |  |

|-------------------|-----------------------------------------|--|--|--|--|

| CMOS              | Complementary Metal-Oxide Semiconductor |  |  |  |  |

| DG                | Double Gate                             |  |  |  |  |

| FinFET            | Fin structure Field Effect Transistor   |  |  |  |  |

| SOI               | Silicon on Insulator                    |  |  |  |  |

| BTBT              | Band to Band Tunneling                  |  |  |  |  |

| I <sub>on</sub>   | ON state Current                        |  |  |  |  |

| $I_{off}$         | OFF state Current                       |  |  |  |  |

| TCAD              | Technology Computer-Aided Design        |  |  |  |  |

| SRH               | Shockley–Read–Hall                      |  |  |  |  |

| DIBL              | Drain Induced Barrier Lowering          |  |  |  |  |

| GIDL              | Gate Induced Drain Leakages             |  |  |  |  |

| SCE               | Short Channel Effect                    |  |  |  |  |

| PTM               | Predictive Technology Model             |  |  |  |  |

| TEM               | Transmission Electron Microscope        |  |  |  |  |

| SEM               | Scanning Electron Microscope            |  |  |  |  |

| GUI               | Graphical User Interface                |  |  |  |  |

| $T_{fin}$         | Fin Thickness                           |  |  |  |  |

| L <sub>g</sub>    | Gate Length                             |  |  |  |  |

| L <sub>ext</sub>  | Extension Region Length                 |  |  |  |  |

| T <sub>gate</sub> | Gate Thickness                          |  |  |  |  |

| t <sub>ox</sub>   | Gate Oxide Thickness                    |  |  |  |  |

| V <sub>t</sub>    | Threshold Voltage                       |  |  |  |  |

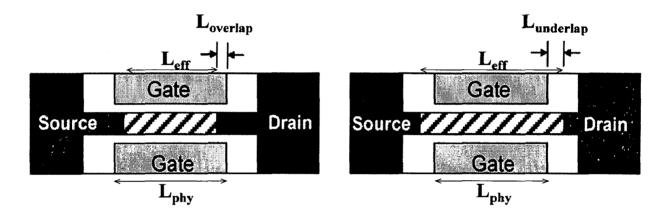

| L <sub>eff</sub>  | Effective gate length                   |  |  |  |  |

| L <sub>phy</sub>  | Physical gate length                    |  |  |  |  |

| Lunderlap         | Gate Underlap length                    |  |  |  |  |

| Lover             | Gate overlap length                     |  |  |  |  |

| SS                | Subthreshold slope                      |  |  |  |  |

| SDE                   | Source/Drain Extension                              |

|-----------------------|-----------------------------------------------------|

| W <sub>fin</sub>      | Fin Width                                           |

| L <sub>SD</sub>       | S/D Pad Length                                      |

| N <sub>fin</sub>      | Channel Doping                                      |

| N <sub>SD</sub>       | Pad Doping                                          |

| T <sub>pHL</sub>      | Logic High To Logic Low Delay                       |

| T <sub>pLH</sub>      | Logic Low To Logic High Delay                       |

| DRAM                  | Dynamic Random Access Memory                        |

| ITRS                  | International Technology Roadmap for Semiconductors |

| NTRS                  | National Technology Roadmap for Semiconductors      |

| C <sub>inv</sub>      | Input Capacitance of Inverter                       |

| C <sub>p</sub>        | Parasitic Capacitance at Drain Terminal             |

| K <sub>S Ext</sub>    | Spacer Dielectric Constant on Source Side           |

| K <sub>SD Ext</sub>   | Spacer Dielectric Constant on Drain Side            |

| S <sub>Ext</sub>      | Extension Region on Source Side                     |

| FO4                   | Fan-Out 4                                           |

| t <sub>rise</sub>     | Rise Time                                           |

| t <sub>fall</sub>     | Fall Time                                           |

| T <sub>o/p rise</sub> | Output Rise Time                                    |

| T <sub>o/p fall</sub> | Output Fall Time                                    |

| R <sub>D Ext</sub>    | Drain Extension Region Resistance                   |

| R <sub>S Ext</sub>    | Source Extension Region Resistance                  |

| R <sub>S/D pad</sub>  | Source / Drain Pad Resistance                       |

\_

xi

.

# **Table of Contents**

| Candidate's Declarationi                                                                      |

|-----------------------------------------------------------------------------------------------|

| Acknowledgementii                                                                             |

| Abstractiv                                                                                    |

| List of Figuresv                                                                              |

| List of Tablesix                                                                              |

| List of Abbreviationsx                                                                        |

| CHAPTER 1 INTRODUCTION1                                                                       |

| 1.1 Background1                                                                               |

| 1.2 Thesis Contribution2                                                                      |

| 1.3 Thesis Organization2                                                                      |

| CHAPTER 2 CURRENT LITERATURE OF MULTIPLE GATE STRUCTURES 4                                    |

| 2.1 History of Devices – Necessity for CMOS Scaling                                           |

| 2.2 Scaling Issues in Bulk MOSFET Scaling                                                     |

| 2.3 Non-Conventional CMOS structures                                                          |

| 2.3.1. Planar Devices: Silicon-On-Insulator (SOI) and Depleted Substrate<br>Transistors (DST) |

| 2.3.2 Tri-Gate MOSFET9                                                                        |

| 2.3.3 Gate-All-Around MOSFET (GAA) 10                                                         |

| 2.3.4 FinFET 10                                                                               |

| CHAPTER 3 FinFET Basics and Simulation Methodology12                                          |

| 3.1 FinFET Structure                                                                          |

| 3.2 Doping Densities                                                                          |

| 3.3 FinFET Fabrication Methods14                                                              |

| 3. 4 Simulation Methodology16                                                                 |

| 3.4.1 TCAD Device Simulations                                                                 |

| 3.4.2 Sentaurus TCAD Package from Synopsys16                                                  |

| 3.4.3 A typical FinFET device used in the simulations                                         |

| 3.5 Details of physical models used                                                           |

| 3.5.1 Band Gap Narrowing Model 19                                                             |

| 3.5.2 Mobility Models                                                                         |

| 3.5.3 Recombination Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.5.4 Quantization models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.5.5. Transport Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.6 Parameter Extraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.6.1 Ion Extraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.6.2 Ioff Extraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3.6.3 Threshold Voltage Extraction25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.6.4 Subthreshold Slope Extraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CHAPTER 4 Results & Impacts of Parasitics on FinFET Standard Cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4.1 Overlap & Underlap Device Structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.2 Current characteristics of Overlap & Underlap Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.3 Standard circuit by FinFET Device with different number of fins                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CHAPTER 5 Results & Optimization of FinFET Device based on circuit performance                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| performance       37         5.1 Meaning of "16 nm" Technology       37         5.2 Source/Drain Pad Doping Engineering       38                                                                                                                                                                                                                                                                                                                                                                                                            |

| performance       37         5.1 Meaning of "16 nm" Technology       37         5.2 Source/Drain Pad Doping Engineering       38         5.3 Gate Oxide thickness and Spacer Dielectric Constant Engineering       41                                                                                                                                                                                                                                                                                                                       |

| performance       37         5.1 Meaning of "16 nm" Technology       37         5.2 Source/Drain Pad Doping Engineering       38         5.3 Gate Oxide thickness and Spacer Dielectric Constant Engineering       41         5.3.1. Three transistor analogy and Novel Scaling Methodology       46                                                                                                                                                                                                                                        |

| performance       37         5.1 Meaning of "16 nm" Technology       37         5.2 Source/Drain Pad Doping Engineering       38         5.3 Gate Oxide thickness and Spacer Dielectric Constant Engineering       41         5.3.1. Three transistor analogy and Novel Scaling Methodology       46         5.4 Asymmetric Source/Drain Extension Doping Profile Engineering       47                                                                                                                                                      |

| performance       37         5.1 Meaning of "16 nm" Technology       37         5.2 Source/Drain Pad Doping Engineering       38         5.3 Gate Oxide thickness and Spacer Dielectric Constant Engineering       41         5.3.1. Three transistor analogy and Novel Scaling Methodology       46         5.4 Asymmetric Source/Drain Extension Doping Profile Engineering       47         5.5. Asymmetric Spacer Dielectric constant scheme       50                                                                                   |

| performance       37         5.1 Meaning of "16 nm" Technology       37         5.2 Source/Drain Pad Doping Engineering       38         5.3 Gate Oxide thickness and Spacer Dielectric Constant Engineering       41         5.3.1. Three transistor analogy and Novel Scaling Methodology       46         5.4 Asymmetric Source/Drain Extension Doping Profile Engineering       47         5.5. Asymmetric Spacer Dielectric constant scheme       50         5.6. Modeling the Circuit Performance based on Device Parameters       54 |

.

# CHAPTER 1

## INTRODUCTION

## **1.1 Background**

The evolution and growth of the semiconductor industry is governed by downscaling of device dimensions. CMOS technology played a major role in downsizing the device and so circuit dimensions because of its high compact density. International Technology Roadmap for Semiconductors (ITRS) guides and predicts the growth of semiconductor industry [1], it predicts to achieve gate length down to 20nm by 2014.

With scaling to this extent several malfunctions in the device operation start occurring, some major issues [2] are the non-linear scaling of the threshold voltage, the control of the short channel effects and the hot carrier reliability. Along with this some technology limitations are there such as the selection of the thin gate dielectric and lithography limitations. Answers to these problems will decide the scaling trends for future.

Hisamoto et al. [3] reported the first successful operation of FinFET for NMOS-devices in 2000 and Huang et al. [4] reported it for PMOS-device in 2001. The multi-gate device has some attracting features which motivated to continue scaling trends with them, these are resemblance of it's structure with that of conventional MOSFET and it's enhanced control over channel which reduce the subthreshold leakages to a great extend without increasing the substrate doping [5]. FinFET is a member of multi-gate devices having two gates so it is called as Double Gate FinFET or just DG-FinFET. Multi-gate devices can be achieved by changing device geometry in such a way that the body is kept thin enough, low doped and wrapped around by the gate. Thus the whole body is under the gate control. Devices with gate length of 18nm and gate oxide thickness of 2.5nm have been experimentally demonstrated with acceptable short-channel characteristics [4].

With shrinking device dimensions narrow dimension, effects start dominating and worsen the proper device operations. FinFET has reduced narrow dimension effects than bulk MOSFET. Thus it has lower subthreshold leakages, improved  $I_{on}/I_{off}$  and sharp subthreshold slopes which allows for better switching-off in the device. In FinFET structures threshold voltage is increased by increasing gate control and reducing  $I_{off}$  without the use of heavy channel doping, so it

reduces the problem of random doping fluctuations, mobility degradation in channel by carrier scattering, drain induced barrier lowering (DIBL) and drain to body BTBT leakage currents [6].

## **1.2 Thesis Contribution**

In this work, various scaling issues in FinFET with channel length of 16 nm are investigated in detail through device simulations using a numerical device simulator. The efforts of scaling gate insulator thickness, extension region doping profile, source/ drain pad doping and spacer dielectric constants are analyzed.

FinFET device with 16nm gate length is used to create different standard circuits such as Inverter, NAND, NOR, SR NAND latch without considering effects of the parasitic resistance and capacitance and with including their effect which dominate in deciding circuit performance.

Impact of these parameter variations on the circuit performance is analyzed and leads towards developing a device scaling methodology so as to maintain the optimized performance with respect to delay and power which also ensures simplicity in device fabrication. Ring oscillator with 3-stages and Inverter with fan out 4 load is simulated with the proposed methodology and the effect is analyzed.

## **1.3 Thesis Organization**

Rest of this report is organized as follows:

Chapter 2 gives the details of the semiconductor structures which are used prior to design and development of FinFETs and issues in those devices that lead to need research and development of new devices for continuing scaling trends called nonconventional structures. Then it introduces some of the nonconventional structures. It also gives brief details of roadmap proposed for growth of semiconductor industry.

Chapter 3 begins with description of the FinFET device structure, followed by some details of the device structure used in this work. Then it presents some brief of FinFET fabrication methods. It describes the simulation methodology used in this work. It uses Sentaurus TCAD from Synopsys. This further explains the tool flow in Syntaurus and different physical models used in simulations and details of methods used for parameter extraction.

Chapter 4 begins with the types of FinFET structures i.e. underlap and overlap and justification of the use of underlapped structure in this work. Multiple fin FinFET structures and their parameters are described. Then impact of parasitic resistance and capacitance in a FinFET standard cell is analyzed. This work analyses FinFET based Inverter, NAND, NOR and SR latch circuits.

Chapter 5 efforts for proposing a novel scaling methodology for underlap FinFET devices by variation of some of the device design parameters keeping the optimum circuit performance and ease of device fabrication issues. It also leads to propose a three transistor analogy for underlap FinFETs which is able to describe the behavior of device properly. Finally the performance parameters  $I_{on}$  and input capacitance of an inverter  $C_{inv}$  are modeled with design parameters to achieve the maximum performance.

In chapter 6, conclusions are drawn on the basis of this work.

# **CHAPTER 2**

# **CURRENT LITERATURE OF MULTIPLE GATE STRUCTURES**

## 2.1 History of Devices – Necessity for CMOS Scaling

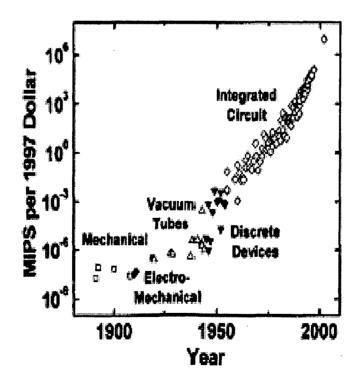

Semiconductor industry has experienced tremendous growth over the last 3 decades. Integrated Circuit (IC) design and computing technologies passed some great miles in progress journey from Small-Scale Integration (SSI), at less than 30 devices per chip, to Medium-Scale Integration (MSI), with 30 to  $10^{3}$  devices per chip, to Large-Scale Integration (LSI) with  $10^{3}$  to  $10^{5}$  devices per chip, to VLSI with  $10^{5}$  to  $10^{7}$  devices per chip, and now it's going to achieve Ultra-Large Scale Integration (ULSI) with  $10^{7}$  to  $10^{9}$  devices per chip. All this progress can be possible because of continued scaling device dimensions. Figure 2.1 shows the numbers of transistors in million, that can be purchased in \$1[7]. Development of silicon integrated circuits in the 1950's [8-9] has contributed the most significant role in the growth shown in figure 2.1. With CMOS transistor technologies [10], high-density, low-power computing became available.

Figure 2.1: The millions of instructions per second that can be purchased with \$1, showing growth path of semiconductor industry

With scaling transistor dimensions, peak operating oxide electric field, channel mobility, and subthreshold swing all should remain relatively constant, so Constant Field Scaling (CFS) scheme has been used as guidance to predict future device designs [11]. In constant field scaling supply voltage and device dimension are scaled equally so as to maintain the electric field constant to allow speed improvements for circuits without sacrificing reliability.

Gordon Moore predicted in the year 1975 that the number of transistors on a chip would be approximately doubled in every 18 months, [12] and this trend is still valid [13]. The industry has followed this Moore's law and achieved a continuous increase in transistor speed and density and a continuous decrease in power dissipation per transistor and cost per transistor.

For the circuits, the technology scaling enhances the performance and simultaneously reduces the layout area requirement resulting in enormous reduction in manufacturing costs.

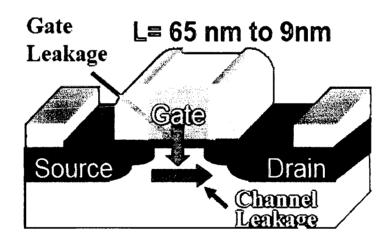

### 2.2 Scaling Issues in Bulk MOSFET Scaling

Conventional planar MOSFET device has been used to follow scaling trend in order to achieve the higher and higher speed and density and allowed semiconductor industry to follow Moore's law, till recently [14]. Figure 2.2 shows the leakage currents in planar bulk MOSFET.

Figure 2.2: Schematic cross-section of planar bulk MOSFET

However, as the planar devices scaled at gate lengths around 50nm and below, scaling of these devices becomes increasingly difficult and requires innovations to overcome the problems due to fundamental physics that constrains the conventional MOSFET. The major limiting physical, technological and electrical phenomena are [15-23] -

- V<sub>t</sub> roll-off

- Drain Induced Barrier Lowering (DIBL)

- Increasing leakage currents such as subthreshold S/D leakage

- Gate Induced Drain Leakages (GIDL)

- Gate direct tunneling and hot carrier effect.

- Random Dopant fluctuation

- Controlling junction and depletion depths.

- Quantum-mechanical tunneling of carriers from source to drain, and from drain to the body of the MOSFET.

- Control of the density and location of dopant atoms in the MOSFET channel and source/drain region to provide a high on-off current ratio and halo implants.

- Interconnect Resistance and Capacitance.

- Minimum Supply voltage.

- Lithography at nanoscale regime and its 3D integration.

Reducing the power supply  $V_{dd}$  helps to reduce power requirement and hot carrier effects, but worsens performance. Performance can be improved back by lowering  $V_t$  but at the cost of worsening S/D leakage. To reduce DIBL and increase adequate channel control by the gate, the oxide thickness can be reduced, but that increases gate leakage [6]. Solving one problem leads to another. Efforts are on to find a suitable high-k gate dielectric so that a thicker physical oxide can be used to help reduce gate leakage and yet have adequate channel control, but this search has not been successful to the point of being usable [6]. There are problems with band alignment (with respect to Si) and/or thermal instability problems and/or interface states problems (with Si). Polysilicon gate electrode suffers from thermal instability problem because insufficient activation leads to poly depletion effects. For reduction of SCE high channel doping is used. At small dimensions it leads to random dopant fluctuation as well as increased impurity scattering and therefore reduced mobility. [6] In technology roadmap [13], at the end of near term of ITRS2003, nearly all of the thirty or so transistor characteristics expected between 2005 and 2008 required for high performance IC devices to meet the expectations of Moore's law are listed as "no known solutions" (Table 2.1). This is a clear indication that IC transistor technology requires fundamental changes in the next half decade.

| Year of production                                                              | 2003 | 2004 | 2005  | 2006        | 2007       | 2008         | 2009 | Driver    |

|---------------------------------------------------------------------------------|------|------|-------|-------------|------------|--------------|------|-----------|

| Technology Node                                                                 |      | hp90 |       |             | hp65       |              |      |           |

| DRAM 1/2 pitch (nm)                                                             | 100  | 90   | 80    | 70          | 65         | 57           | 50   | DRAM      |

| MPU/ASIC 1/2 pitch (nm)                                                         | 107  | 90   | 80    | 70          | 65         | 57           | 50   | MPU       |

| MPU Printed Gate Length (nm)                                                    | 65   | 53   | 45    | 40          | 35         | 32           | 28   | MPU       |

| MPU Physical Gate Length (nm)                                                   | 45   | 37   | 32    | 28          | 25         | 22           | 20   | MPU       |

| Equiv. physical oxide thickness for<br>MPU/ASIC T <sub>ox</sub> (nm)            | 1.3  | 1.2  | 1.1   | 1.0         | 0£0        | 0.9          | 08   | MPU       |

| Gate dielectric leakage at 100C (nA/um)<br>High Performance                     | 100  | 170  | 170   | 170         | 230        | 280          | 280  | MPU       |

| Physical gate length low operating power (LOP) (nm)                             | 65   | 53   | 45    | 37          | 32         | 28           | 25   | Low Power |

| Physical gate length low standby power<br>(LSTP) (nm)                           | 75   | 65   | 53    | 45          | 37         | 32           | 28   | LSTP      |

| Equiv. physical oxide thickness for low operating power T <sub>ox</sub> (nm)    | 1.6  | 1.5  | 1.4   | 13          | 12         | 1.0          | 10   | LOP       |

| Gate dielectric leakage (nA/um) LOP                                             | 0.33 | 1.0  | 1.0   | 10          | 167        | 1.67         | 1.67 | LOP       |

| Equiv. physical oxide thickness for low standby power $T_{ox}$ (nm)             | 2.2  | 2.1  | 2.1   | 10          | 1.0        | 1.6          | 143  | LSTP      |

| Gate dielectric leakage (nA/um) LSTP                                            | 3    | 3    | 5     | 7           | 8          | 10           | 13   | LSTP      |

| Thickness control EOT (% 30)                                                    | <₫4  | <₫4  | <₫4   | <±4         | <b>€</b> 3 | ≪23          | ≪3   | MPU/ASIC  |

| Gate etch bias (nm) [D]                                                         | 20   | 16   | 14    | 12          | 10         | _10          | 8    | MPU/ASIC  |

| l <sub>gate</sub> 3o variation (nm) [E]                                         | 4.46 | 3.75 | 3.15  | 2.81        | 80         | 22           | 8    | MPU/ASIC  |

| Total max allowable lithography 3o (nm)                                         | 3.99 | 3.35 | 2.82  | 2.51        | 2.26       | 1.97         | 1.79 | MPU/ASIC  |

| Total max allowable etch 3σ (nm)including<br>photoresist trim and gate etch [F] | 1.99 | 1.68 | 0.430 | 123         | 1.02       | 0.93         | 0.69 | MPU/ASIC  |

| Resist trim max allowable 3o (nm)                                               | 1.16 | 0.97 | 0.62  | 0.78        | 063        | 057          | 0.52 | MPU/ASIC  |

| Gate etch max allowable 3σ (rim)                                                | 1.82 | 1.37 | 1.15  | 1.02        | 090        | 030          | 0.78 | MPU/ASIC  |

| CD bias bet. dense and isolated lines                                           | <±15 | <±15 |       | <b>S</b> II | ≪306       | <b>≪91</b> 5 | ≪300 | MPU/ASIC  |

Due to all above problems it was the best promising and practical solution felt for further scaling, to adopt some new alternative MOSFET structures, which are discussed now.

## **2.3 Non-Conventional CMOS structures**

Following device structures have shown considerable potential and attracted the researches as alternatives of planar MOSFETs and also have been identified by *International Technology Roadmap for Semiconductors* [13] as the emerging research and/or commercial devices for continuing scaling trends at very small dimensions with improved performance.

# 2.3.1. Planar Devices: Silicon-On-Insulator (SOI) and Depleted Substrate Transistors (DST)

As fundamental limit of the planar CMOS structure is approaching rapidly, to allow continued device scaling, some new structures and materials has to be searched. This section discusses the various improvements in planar structures for continuing scaling.

One of the major problems with planar MOSFET scaling is extensive subthreshold leakages and increased junction capacitance. Both of these problems can be addressed by using silicon on insulator (SOI) method for planar devices [24]. It minimizes substrate leakages, reduce junction capacitance substantially, and power dissipation simultaneously.

Ultra-thin body (UTB) SOI devices [25] have additional advantage of improved electrostatic integrity. UTB-SOI devices are built on a very thin silicon body typically less than 20nm (< 20nm) with buried oxide beneath. This is also known as fully depleted condition in which channel is depleted of mobile carries under all operating bias conditions.

One of the solutions is to fabricate the device on a SOI substrate [24]. It is well known that SOI devices provide advantages of substantially reduced junction capacitance that facilitates high speed operation. At the same time, power dissipation is minimized. Ultra-thin body (UTB) SOI devices [25] have the added benefit of improved electrostatic integrity. The transistor is built on a very thin silicon body typically <20nm with buried oxide beneath. This is known as the fully depleted condition in which the thin silicon channel is depleted of mobile carriers under all operating bias conditions, thus scaling to a shorter length as compared to bulk planar devices is possible. It leads to the subthreshold slope to the theoretical value of 60mV/dec [26]. Typically in bulk transistors with scaling, channel doping is increased to reduce subthreshold leakages and thus subthreshold slope degrades because of increased depletion capacitance. The expression for sunthreshold slope (SS) is as follows:

$$SS = (kT/q) \ln_{10}(1+C_D/C_{ox})$$

Where T is the temperature

q is the electronic charge

C<sub>D</sub> is the capacitance of the depletion region

Cox is the gate-oxide capacitance

In fully depleted structures depletion capacitance is greatly reduced, so subthreshold slope is improved.

However fully depleted transistors present a manufacturing challenge. The transistor is placed on an ultrathin layer of silicon having thickness approximately one third of the gate length. It is very difficult to achieve the precise thickness due to process variations like uneven oxidation rate across the wafer [26]. So the threshold voltage may vary widely if silicon layer thickness is not precisely controlled.

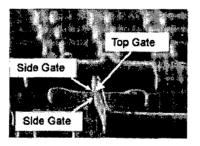

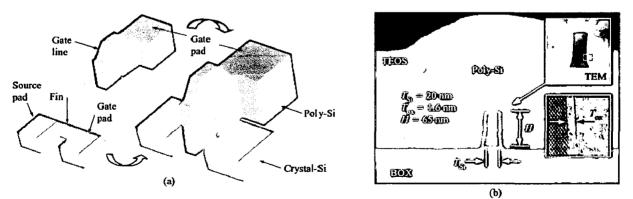

### 2.3.2 Tri-Gate MOSFET

L

τ

Triple-gate MOSFETs allow more flexibility and tolerance of silicon with acceptable control of short channel effects. Triple gate structure (as the name suggests) has three gates, one horizontal and two vertical side gates over the box like channel as a connected gate. The silicon channel is covered from three sides by gate insulator followed by gate. Inversion takes place on two vertical faces and one top surface of box like channel. A TEM cross-section of a tri-gate FinFET is shown in Figure 2.3. The fin width and height are comparable to the gate length and this "relaxes" the body dimensions in terms of the lithography challenges.

Figure 2.3: Cross-section of a tri-gate FinFET [27]

Tri-gates posses a major fabrication problem, as here thickness of all three gate insulators are same. But gate oxide (the most common gate insulator) is thermally grown. At different planes

of silicon surface rate of thermal oxidation is different. So it is very hard to get all three oxide of same thickness.

Apart from the tri-gate proposed by INTEL, there are many different gate configurations for SOI devices, namely Pi-Gate FET [29], Omega FET [30] and Surround-Gate FET [31] for number of gates greater or equal to 3. But these all has some manufacturing problem, so these are not commonly pursued by researchers.

## 2.3.3 Gate-All-Around MOSFET (GAA)

Gate-All-Around MOSFETs (GAA) or Silicon Nanowire attract significant interest as potential replacements or complements for traditional CMOS transistors around, or beyond the end of the current edition of the International Technology Roadmap for Semiconductors (ITRSs). In GAA, gate covers the wire like channel from all directions. So in GAA, the gate control over the lightly or undopped channel is very much improved. The thin channel is completely inverted. This improves immunity for short channel effect and transconductance performance, since volume inversion presents lesser scattering than surface inversion [32]. From simulation results it has found that the the drive current and transconductance of a gate-allaround is approximately four times that of the single gate device. Also it is more effective in suppressing short channel effects than other multiple gate structures [33].

However fabricating gate-all-around MOSFETs poses a technological challenge as it is not compatible with standard planar CMOS processing. Though it has the best scalability, it involves the most process complexity among all the multiple gate structures. The fabrication cost will be higher [34].

#### 2.3.4 FinFET

The double-gate MOSFET is considered the most attractive device to succeed the planar MOSFET [35]. With two gates controlling the channel, short channel effects can be greatly suppressed. Out of the many double gate structures, FinFET is considered the most promising. It consists of a channel formed in a vertical Si fin controlled by a self-aligned double-gate. The top gate dielectric thickness is made larger as compared to the side vertical gate dielectric layers so that effectively only two vertical channels induced when a gate voltage is applied. Fact from fabrication point of view is that Si has different oxide growth rates in different planes, so it is

very difficult to match thickness of top and side gate dielectric (oxide) thickness. The fin is made thin enough when viewed from above such that the two gates control the entire fully-depleted channel film. The features include:

1. An ultra-thin silicon fin for suppression of short-channel effects

2. Two gates which are self-aligned to each other and to the source/drain regions

3. Raised source/drain to reduce parasitic resistance

4. Gate-last process compatible with low temperature, high-k gate dielectrics.

N-channel FinFETs showed good short channel performance down to 17 nm gate lengths [3] whereby boron doped SiGe is used as a gate material. Promising results were obtained for PMOS structure [4].

But in FinFETs, the width of the fin is smaller than the gate length. In FinFET fabrication, the width of the fin becomes the critical dimension. Lithography would have to be extended to finer line-widths in order to pattern the fin and that accelerates the lithography roadmap.

# Chapter 3

# **FinFET Basics and Simulation Methodology**

Among the various types of multi - gate structures, FinFETs have been shown to be the most attractive alternative to the bulk MOSFETs as it's fabrication is compatible with the current CMOS fabrication technology.

## **3.1 FinFET Structure**

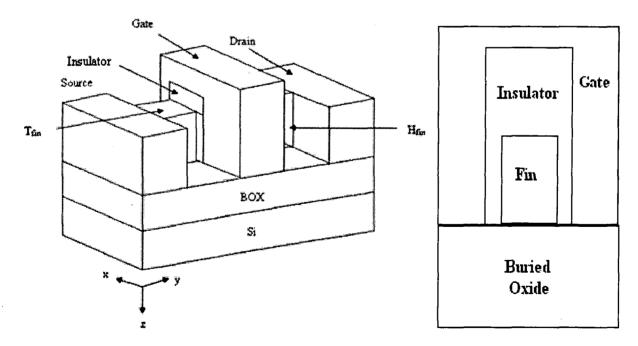

In a FinFET device, the channel is in the form of a thin vertical silicon structure referred to as the fin (as it resembles the tail fin of a fish). It is called a quasi-planar device because of this vertical fin, even though the current conduction is parallel to the plane of the silicon wafer [3]. FinFETs come in two flavors: double gate and triple gate. In triple gate FinFETs, the gate wraps around the fin from the top as well as from the side walls and the gate insulator thickness on the three sides are similar. In the double gate FinFETs, either the top insulator layer is made much thicker than the vertical insulator layers or a top gate is avoided altogether. In this work, only double gate FinFETs has been considered. Figure 3.1 shows 3<sup>D</sup> structure and cross sectional view of a FinFET device.

Figure 3.1: (a) 3D structure of a FinFET (b) Cross-sectional view of the gate region

The three dimensional structure and the 2-D cut-plane (y-z plane) view of the gate region of a typical double gate FinFET have been shown in figure 3.1 The fin height and fin thickness have been denoted by H<sub>fin</sub> and T<sub>fin</sub> respectively. The oxide thickness between the side gates and the fin is t<sub>ox</sub>. Fin engineering (balancing fin height, fin thickness, oxide thickness, and channel length) is crucial in minimizing the leakage currents I<sub>off</sub>, and maximizing the on current Ion [34].

For a double gate FinFET, the effective channel width is dependent on the fin height, given as

$W_{fin} = 2H_{fin}$ . For FinFET, the top gate oxide layer is made sufficient thick so that its effect is negligible, as gate oxide is thermally grown for FinFETs and due to different oxide growth rates in different plans, it is difficult to make all three oxide layers equithick. Hence the gate controls the channel from two sides each having width  $H_{fin}$  (Note: For a triple gate FinFET, the expression becomes  $W_{fin} = 2H_{fin} + T_{fin}$  since now we have additional gate control from the top).

### **3.2 Doping Densities**

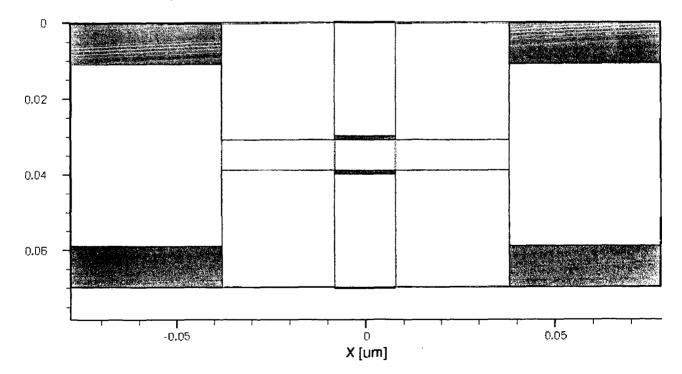

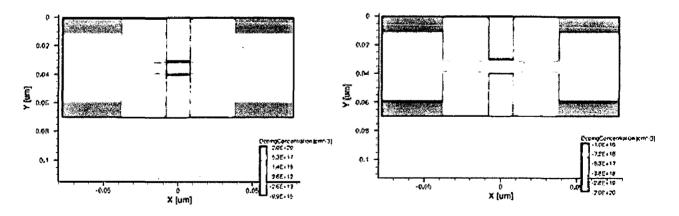

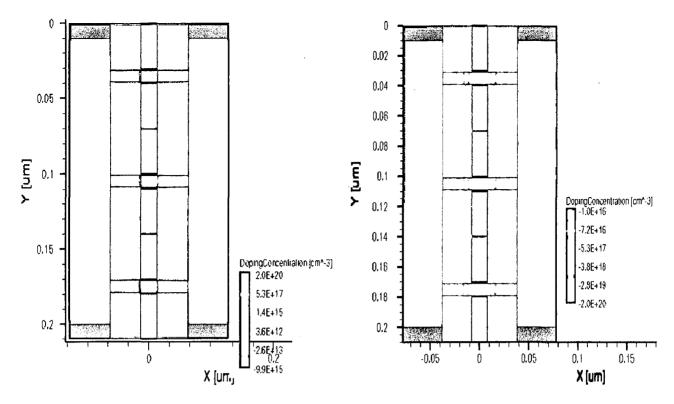

The fin is generally lightly doped (or even undoped). Source/Drain regions are heavily doped, while the Source/Drain extension regions have been subjected to different doping levels by different researchers – from undoped to constantly doped to Gaussian doped. Figures 3.2 & 3.3 show the structure and Gaussian doping profile in extension regions N-channel underlap FinFET respectively.

Figure 3.2: N-channel underlap FinFET structure with Gaussian doping profile in extension regions

Figure 3.3: N-channel underlap FinFET structure doping profile

### **3.3 FinFET Fabrication Methods**

FinFETs have been fabricated by mainly two different techniques:

Gate-First Approach: In this process, the source and drain regions are created after the formation (patterning) of the gate stack [36].

Gate-Last Approach: Here, the source and drain regions are formed before the formation of the gate stack [37, 3].

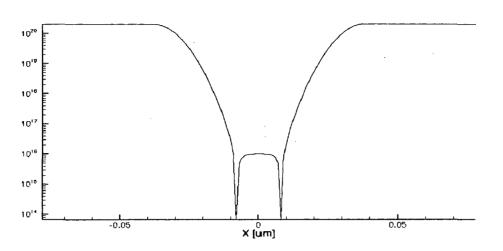

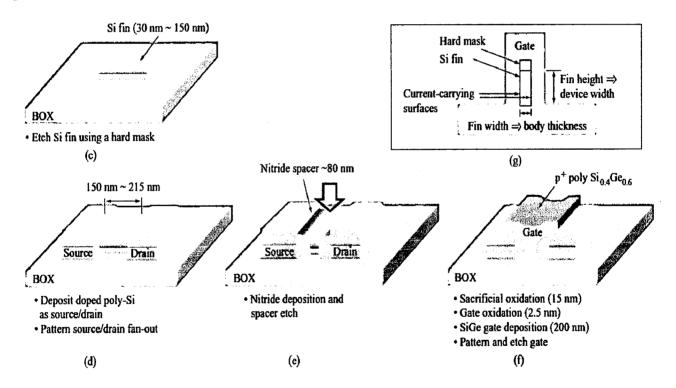

The fabrication of the FinFET begins with the patterning and etching of a thin fin on an SOI substrate using a hard mask which is retained throughout the fabrication process. The fin thickness is smaller than the gate length, and hence either electron-beam lithography or optical lithography with extensive linewidth trimming is used to pattern the thin fin. Figure 3.4 shows fabrication sequence of a Gate -First process and SEM & TEM images across the device width.

**Figure 3.4**: (a) Gate-First Process (b) Cross-sectional SEM and TEM images across the device width, llustrating the fin cross-sectional dimensions and the thin (1.6-nm) gate oxide grown on the sidewall of the fin. [6]

For the gate-first process, the fabrication steps after the fin formation are similar to the fabrication steps of the conventional bulk MOSFET. After the gate oxide is grown, the gate polysilicon is deposited, patterned and etched. A sidewall spacer is formed next to the gate.

Source/drain and extension implants can be performed before and/or after the gate spacer, using angled implants.

For the gate-last process, the source and drain regions are formed immediately after patterning. Doped polysilicon or polycrystalline SiGe is deposited on the fin, followed by lithographic patterning of the source/drain pads with a thin slot between the source and drain. This distance between the source and drain determines the gate length. The slot length is further reduced by a dielectric sidewall spacer. Then the gate oxide is grown, and the gate material is deposited and patterned [6]. Figure 3.5 shows fabrication sequence of a Gate-Last double gate FinFET process.

**Figure 3.5**: (a) –(d) Fabrication sequence of a Gate-Last double gate FinFET process. (e) Cross section of the silicon fin showing the current-carrying plane. Direction of current flow is into the plane of the diagram [7]

The gate-last process enables more flexibility in cases where metal-gate and high  $-\kappa$  dielectrics are used.

## 3. 4 Simulation Methodology

#### **3.4.1 TCAD Device Simulations**

Technology CAD (TCAD) refers to using computer simulations to develop and optimize semiconductor devices and processing technologies. TCAD simulation tools solve fundamental physical partial differential equations, such as transport equations for discretized geometries representing the silicon wafer or the layer system in a semiconductor device.

This deep physical approach gives TCAD simulation predictive accuracy. It is, therefore, possible to substitute TCAD computer simulations for costly and time-consuming test wafer runs when developing and characterizing a new semiconductor device or technology.

Device simulations can be thought of as virtual measurements of the electrical behavior of a semiconductor device. The device is represented as a meshed finite-element structure. Each node of the device has properties associated with it, such as material type and doping concentration. For each node, the carrier concentration, current densities, electric field, generation and recombination rates, etc. can be computed.

Electrodes are represented as areas on which boundary conditions, such as applied voltages, are imposed. The device simulator solves the Poisson equation and the carrier continuity equation (and other suitable equations). After solving these equations, the resulting electrical currents at the contacts can be extracted.

## 3.4.2 Sentaurus TCAD Package from Synopsys

The following tools from the Sentaurus package from Synopsys were used in this work:

Sentaurus Structure Editor: The device structures were created using this editor. The doping levels can be set and the meshing of the structure can also be done. It has a GUI as well as a command line interface.

The input files for this editor are written in the scheme programming language.

Sentaurus Device: Sentaurus Device can simulate the electrical, thermal, and optical characteristics of semiconductor devices. It contains a comprehensive set of physical models that can be applied to all relevant semiconductor devices and operating conditions. A real semiconductor device, such as a transistor, is represented in the simulator as a 'virtual' device

whose physical properties are discretized onto a non-uniform 'grid' (or 'mesh') of nodes. Continuous properties such as doping profiles are represented on a sparse mesh and, therefore, are only defined at a finite number of discrete points in space. The doping at any point between nodes (or any physical quantity calculated by Sentaurus Device) can be obtained by interpolation.

Each virtual device structure is described in the Synopsys TCAD tool suite by a *tdr* file containing the following information:

- The grid (or geometry) of the device contains a description of the various regions, that is, boundaries, material types and the locations of any electrical contacts. It also contains the locations of all the discrete nodes and their connectivity.

- The data fields contain the properties of the device, such as the doping profiles, in the form of data associated with the discrete nodes. By default, a device simulated in 2D is assumed to have a 'thickness' in the third dimension of 1  $\mu$ m.

For maximum efficiency of a simulation, a mesh must be created with a minimum number of vertices to achieve the required level of accuracy. For any given device structure, the optimal mesh varies depending on the type of simulation.

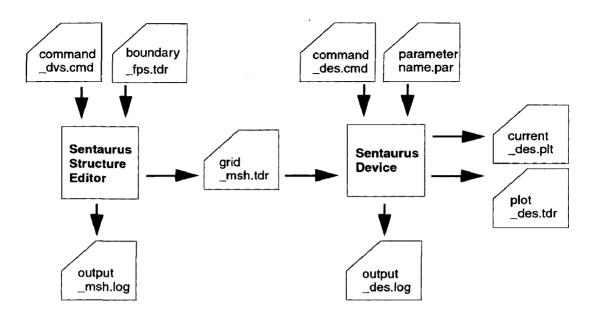

**Tool Flow:** In a typical device simulation tool flow, the Sentaurus Structure Editor generates a tdr file, which is then used in the Sentaurus Device along with other input files viz. command file (*.cmd*) and a parameter file to simulate the electrical characteristics of the device. The parameter file(*.par*) is used for changing the default values. The tdr file can be generated using the Sentaurus Structure Editor alone or it can also be created in an alternate manner: the generation of a device structure by process simulation (using Sentaurus Process) followed by remeshing using Sentaurus Structure Editor. In this scheme, control of mesh refinement is handled automatically through the command file.

The log files contain step-by-step information of the commands executed.

**Tecplot:** This tool is used for visualization purposes. It can plot solutions and derives variables like potential, carrier density, mobility, electrical field, etc.

Figure 3.6 shows the typical tool flow for device simulation using Sentaurus Device [38]

Figure 3.6: Typical tool flow for device simulation using Sentaurus Device [38]

### 3.4.3 A typical FinFET device used in the simulations

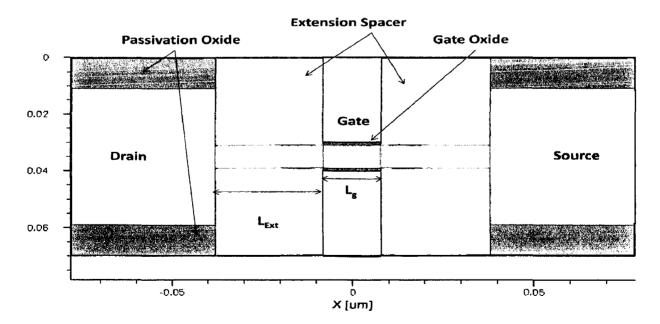

Two dimensional simulations were performed on the FinFET device, a typical one being shown in Figure 3.7. This diagram depicts a view from the top of the device. The various regions and geometrical parameters have been marked on the figure.  $T_{fin}$  is the fin thickness,  $L_g$  is the gate length,  $L_{spacer}$  and  $L_{ext}$  are the width of the spacer along the channel and total underlap length (including the spacer) respectively, while  $T_{gate}$  is the gate thickness.

Figure 3.7: A typical 2D FinFET structure used in the Sentaurus simulations

## 3.5 Details of physical models used

This section describes the various physical models used in the simulations.

#### **3.5.1 Band Gap Narrowing Model**

The energy bandgap and the intrinsic carrier concentration are very important characteristics of a semiconductor material. At high impurity concentrations, the density of energy states no longer has a parabolic energy distribution and becomes dependent on the impurity concentration and it has been found experimentally that the bandgap is effectively reduced with increasing doping densities [39] as

$$E_{g,eff}(T) = E_g(T) - E_{bgn}$$

where  $E_{bgn}$  is the amount of band gap narrowing.

The Old Slotboom model [39] was used, which gives the amount of band -gap narrowing as:

$$E_{bgn} = E_{ref} \left[ ln \left( \frac{N}{N_{ref}} \right) + \sqrt{\left( ln \left( \frac{N}{N_{ref}} \right)^2 + 0.5 \right)} \right]$$

with  $E_{ref} = 9 \times 10^{-3}$  and  $N_{ref} = 1 \times 10^{17}$ .

As a result of band-gap narrowing, the effective intrinsic carrier concentration also changes as

$n_i^2(N,T) = n_{i0}^2(T)exp(E_{g,eff}(N,T)/kT)$

#### **3.5.2 Mobility Models**

The following mobility models were included in the simulation:

(a) The constant mobility model: It is the default model in Sentaurus Device. It accounts only for phonon scattering and, therefore, it is dependent only on the lattice temperature:

$$\mu_{const} = \mu_L \left(\frac{T}{300K}\right)^{-\zeta}$$

The following table lists the values of the coefficients  $\mu_L$  and  $\zeta$ :

| Table 3.1: Constant M | Mobility Model | l: Default coeffici | ients for Si |

|-----------------------|----------------|---------------------|--------------|

|-----------------------|----------------|---------------------|--------------|

| Parameter | Electron         | Holes             |

|-----------|------------------|-------------------|

| $\mu_L$   | $1417 \ cm^2/Vs$ | $470.5 \ cm^2/Vs$ |

| ζ         | 2.5              | 2.2               |

(b) Doping Dependent Mobility Model: In doped semiconductors, the charged impurity ions cause scattering of the carriers, leading to degradation of the carrier mobility. In this work, the Masetti model [40] was used where

$$\mu_{dop} = \mu_{min1} \exp\left(-\frac{P_c}{N}\right) + \frac{\mu_{const} - \mu_{min2}}{1 + (N_{tot}/C_r)^{\alpha}} - \frac{\mu_1}{1 + (C_s/N_{tot})^{\beta}}$$

The reference motilities  $\mu_{min1}$ ,  $\mu_{min2}$ ,  $\mu_1$  and  $\mu_{const}$  the reference doping concentrations  $C_r$ ,  $C_s$ ,  $P_c$  and the exponents  $\alpha$  and  $\beta$  are available in [38]

#### (c) High Field Saturation Mobility model

Since the FinFET dimensions are sub -100nm, the electric fields in the channel can be pretty high. In high electric fields, the carrier drift velocity gets saturated. The Extended Canali model [41] was used for accounting for this effect in the device simulations as

$$\mu(F) = \frac{(\alpha + 1)\mu_{low}}{\alpha + \left[\left(\frac{(\alpha + 1)\mu_{low}F_{hfs}}{v_{sat}}\right)^{\beta}\right]^{\frac{1}{\beta}}} \xrightarrow{\text{CENTRAL LIBRY}}_{\text{Date.....}}$$

where  $\mu_{low}$  denotes the low-field mobility,  $v_{sat}$  the saturation velocity and  $\beta$  is a temperature dependent exponent given by  $\beta = \beta_0 \left(\frac{T}{300K}\right)^{\beta_{exp}}$  and  $F_{hfs} = |\nabla \phi|$ , is the electric field strength.

#### (d) Mobility degradation at interfaces

High perpendicular electric field in the channel region causes strong interaction of carriers at the silicon-insulator interface. Carriers are subjected to scattering by acoustic surface phonons and surface roughness. The Lombardi model [42] was used to include the degradation of carrier mobility at the interfaces.

The surface contribution due to acoustic phonon scattering has the form:

$$\mu_{ac} = \frac{B}{F_{\perp}} + \frac{C(N_{tot}/N_0)^{\lambda}}{F_{\perp}^{1/3}(T/300K)^k}$$

and the contribution attributed to surface roughness scattering is given by:

$$\mu_{sr} = \left(\frac{\left(F_{\perp}/F_{ref}\right)^{A*}}{\delta} + \frac{F_{\perp}^{3}}{\eta}\right)^{-1}$$

The values for the various coefficients are available in [38]

The net mobility is given by the combination of the mobility models described above, according to the well known Mathiessen's rule:  $\mu^{-1} = \mu_1^{-1} + \mu_2^{-1} + \mu_3^{-1} \dots$

#### **3.5.3 Recombination Model**

#### (a) Shockley-Read-Hall (SRH)

Electron-hole recombination is an important mechanism by which carrier concentrations tend to approach their equilibrium values. Phonon emission can occur during this recombination process in the presence of a trap (or defect) within the forbidden gap of the semiconductor. The doping dependent model of Shockley–Read–Hall (SRH) recombination was used to consider recombinations through deep defect levels in the band gap. In Sentaurus Device, the following form is implemented [38]:

$$R_{net}^{SRH} = \frac{np - n_{i,eff}^2}{\tau_p(n+n_1) + \tau_n(p+p_1)}$$

where, n and p are the electron and hole concentrations at the site, and

$$n_{1} = n_{i,eff} \exp(E_{trap}/kT)$$

$$p_{1} = p_{i,eff} \exp(-E_{trap}/kT)$$

where is  $E_{trap}$  the difference between the defect level and intrinsic level. The variable is accessible in the parameter file (.par file). It's default value for silicon is 0.  $n_{i,eff}$ , is the effective intrinsic electron concentration.  $\tau_p$  and  $\tau_n$  are the minority carrier lifetimes and are dependent on the doping, electric field and temperature. The doping dependence of the SRH lifetime  $\tau_{dop}$  is modeled in Sentaurus Device with the Scharfetter relation, written below [38].

$$\tau_{dop} (N_{A,0} + N_{D,0}) = \tau_{min} + \frac{\tau_{max} - \tau_{min}}{\left(1 + \frac{N_{A,0} + N_{D,0}}{N_{ref}}\right)^{Y}}$$

Table 3.2 lists the default parameters.

Table 3.2: Default parameters for the doping dependent SRH lifetimes [38]

| Parameter         | Electron           | Holes              | Unit             |   |

|-------------------|--------------------|--------------------|------------------|---|

| $	au_{min}$       | 0                  | 0                  | s                |   |

| τ <sub>max</sub>  | 1x10 <sup>-5</sup> | 3x10 <sup>-6</sup> | s                | · |

| N <sub>ref</sub>  | 1x10 <sup>16</sup> | 1x10 <sup>16</sup> | cm <sup>-3</sup> |   |

| Ŷ                 | 1                  | 1                  | 1                |   |

| E <sub>trap</sub> | 0                  | 0                  | eV               |   |

Since the simulations performed included quantum transport models to account for the quantum mechanical effects, the expression for  $R_{net}^{SRH}$  needs to be modified as follows

$$R_{net}^{SRH} = \frac{np - Y_n Y_p n_{i,eff}^2}{\tau_p (n + Y_n n_1) + \tau_n (p + Y_p p_1)}$$

where

$$Y_n = \frac{n}{N_c} \exp(-\eta_n), \qquad Y_p = \frac{p}{N_c} \exp(-\eta_p)$$

$$\eta_n = \frac{E_{F,n} - E_c}{kT}, \quad \eta_p = \frac{E_V - E_{F,p}}{kT}$$

#### (b) Auger recombination