# TCAD SIMULATION STUDY OF CRYSTALLINE SILICON SOLAR CELL AND RELIABILITY OF NANOWIRE FET

# **A DISSERTATION**

Submitted in partial fulfillment of the requirements for the award of the degree

of

MASTER OF TECHNOLOGY

in

ELECTRONICS AND COMMUNICATION ENGINEERING (With Specialization in Semiconductor Devices and VLSI Technology)

### By

# **PARAG UPADHYAY**

DEPARTMENT OF ELECTRONICS AND COMPUTER ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE-247 667 (INDIA) JUNE, 2010 I hereby declare that the work, which is presented in this dissertation report, titled "TCAD Simulation Study of Crystalline Silicon Solar Cell and Reliability of Nanowire FET ", being submitted in partial fulfillment of the requirements for the award of the degree of Master of Technology with specialization in Semiconductor Devices and VLSI Technology, in the Department of Electronics and Computer Engineering, Indian Institute of Technology, Roorkee is an authentic record of my own work carried out from July 2009 to June 2010, under guidance and supervision of Dr. A.K.Saxena and Dr. S.K.Manhas, Department of Electronics and Computer Engineering, Indian Institute of Technology, Roorkee.

The results embodied in this dissertation have not been submitted for the award of any other Degree or Diploma.

Date: 29 06 2010 Place: Roorkee

Parag Upadhyay

# CERTIFICATE

This is to certify that the statement made by the candidate is correct to the best of our knowledge and belief.

Alexand

Professor, E&C Department, Indian Institute of Technology, Roorkee Roorkee – 247667, (INDIA)

K.Manhas)

Asst. Professor, E&C Department, Indian Institute of Technology, Roorkee Roorkee – 247667, (INDIA)

#### ACKNOWLEDGEMENTS

I want to thank all those associated with the Microelectronics and VLSI Technology Group, Department of Electronics and Computer Engineering of the Indian Institute of Technology Roorkee for allowing me to carry-out this work, especially to my professors and guides Dr. A.K.Saxena and Dr. S.K.Manhas, who were always aware of my work and were at all times available when I needed their advice. I would specially like to thank Dr. A.K.Saxena for guiding me step by step to frame something that was very vague in my mind.

Dr S. Dasgupta, for his lecture on 'Research Ethics' which motivated me to keep my work systematic and documented at all times.

I thank the INUP, IIT Bombay for funding and providing the infrastructure for the project on reliability study of silicon nanowire MOSFETs.

I would also like to express my gratitude to my seniors at the VLSI Design Lab, Electronics and Computer Engineering Department, IIT Roorkee for their encouragement and criticism and for their help in solving software related issues.

Satish and Saurabh, for spending hours together trying to learn Sentaurus and solving the unfathomable errors that crept up. Seriously thanks a lot guys!

The IIT Roorkee football team, with whom i have spent many evenings playing football after tiring hours in the lab.

Shilpa Menon, for inspiring me to take up post graduation in my field of interest. Thanks Shilpa!

Kaumudi Mahajan, for making me better at everything that i do by simply criticizing it, always.

Lastly my family, mummy, daddy and keyur, who kept trying to understand what I was eventually trying to prove! Thanks for your love and support; I wouldn't have come this far without you.

ii

# CONTENTS

| AC  | KNO  | WLEDGEMENTS                                                    | ii |

|-----|------|----------------------------------------------------------------|----|

| LIS | T OF | TABLES                                                         | v  |

| LIS | T OF | FIGURES                                                        | vi |

| LIS | T OF | ABBREVIATIONS                                                  | ix |

| AB  | STRA | CT                                                             | x  |

| 1.  | INT  | RODUCTION                                                      | 1  |

|     | 1.1  | Objectives                                                     | 1  |

| 2.  | FUN  | DAMENTAL SOLAR CELL CONCEPTS                                   | 3  |

|     | 2.1  | Solar Energy                                                   | 3  |

|     | 2.2  | Technical Background                                           | 6  |

|     |      | 2.2.1 Photovoltaic Cell Operation                              | 6  |

|     |      | 2.2.2 Definitions for Characterization of Photovoltaic Devices | 9  |

| 3.  | GEN  | ERAL SIMULATION SETUP                                          | 12 |

|     | 3.1  | Device Structure in Sentaurus Structure Editor                 | 12 |

|     | 3.2  | Device Simulation in Sentaurus Device                          | 14 |

|     | 3.3  | Reflectance and Transmittance Calculation in Inspect           | 17 |

|     | 3.4  | Comparison of Simulated and Quantitative Results               | 20 |

| 4.  | DES  | IGN OF SOLAR CELLS & RESULTS                                   | 22 |

|     | 4.1  | Optical Losses                                                 | 23 |

|     | 4.2  | Anti-Reflection Coatings                                       | 24 |

|     | 4.3  | Material Thickness                                             | 27 |

|     | 4.4  | Recombination Losses                                           | 27 |

|     | 4.5  | Current Losses due to Recombination                            | 31 |

|     | 4.6  | Voltage Losses due to Recombination                            | 33 |

|     | 4.7  | Emitter Resistance                                             | 36 |

|     | 4.8  | Finger Resistance                                              | 37 |

-

# iii

|     | 4.9    | Effect of Intrinsic Electric Field                    | 38 |

|-----|--------|-------------------------------------------------------|----|

|     | 4.10   | Effect of Temperature                                 | 44 |

|     | 4.11   | Effect of Diode Ideality Factor                       | 44 |

| 5.  | OBS    | ERVATIONS AND DISCUSSION                              | 48 |

| 6.  | CON    | CLUSIONS                                              | 51 |

| 7.  | REL    | IABILITY ANALYSIS OF SILICON NANOWIRE MOSFETs         | 52 |

|     | 7.1    | Introduction                                          | 52 |

|     | 7.2    | Progression of Device Structure                       | 53 |

|     | 7.3    | GAA Nanowire Fabrication                              | 55 |

|     | 7.4    | Current GAA Nanowire Performance                      | 57 |

|     | 7.5    | Basic Concept of Hot Electron Degradation             | 59 |

|     | 7.6    | Experimental Setup                                    | 61 |

|     | 7.7    | Results                                               | 65 |

|     | 7.8    | Conclusions                                           | 67 |

| BIB | LIOG   | RAPHY                                                 | 68 |

| Apŗ | oendix | A: Optical properties of Silicon                      | 71 |

| App | endix  | B: Derivation for base, emitter and finger resistance | 73 |

| App | endix  | C: Standard AM1.5G sunlight spectra                   | 78 |

| App | endix  | D: Best research-cell efficiencies                    | 79 |

| PUE | BLICA  | TIONS                                                 | 80 |

.

iv

# LIST OF FIGURES

| Figure 2.1.1 | Spectral irradiance of the sun                                     | 5  |

|--------------|--------------------------------------------------------------------|----|

| Figure 2.1.2 | Path of sunlight to earth at different times                       | 5  |

| Figure 2.2.1 | Schematic cross-section diagram of a single-junction solar cell    | 6  |

| Figure 2.2.2 | Band diagram of a solar cell under illumination                    | 7  |

| Figure 2.2.3 | I-V characteristics of an illuminated junction                     | 9  |

| Figure 2.2.4 | Current versus Voltage curve (I-V) for a typical solar cell        | 10 |

| Figure 3.1.1 | Part of the solar cell generated by the Sentaurus Structure Editor | 13 |

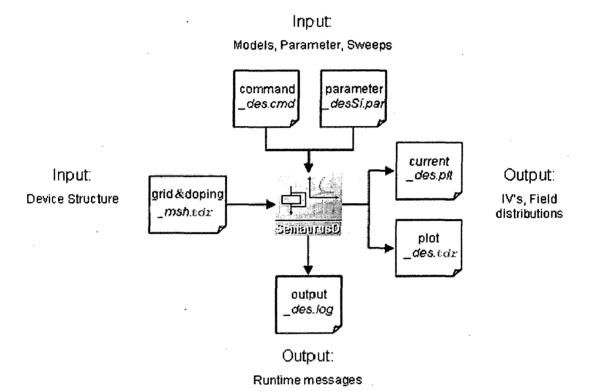

| Figure 3.2.1 | Flow of input and output files in Sentaurus Device                 | 14 |

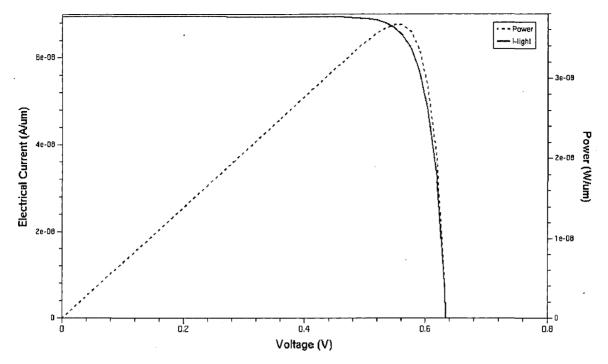

| Figure 3.2.2 | Current and power vs. voltage for the illuminated device           | 16 |

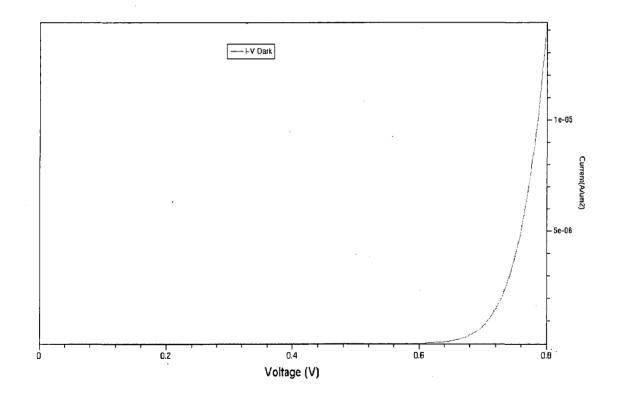

| Figure 3.2.3 | I-V curve of the diode without illumination                        | 16 |

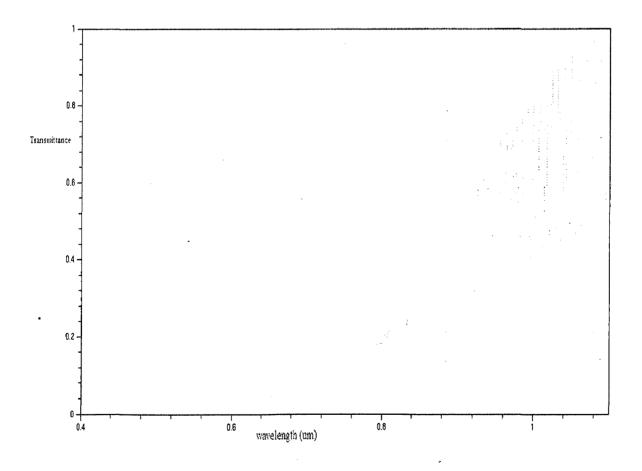

| Figure 3.3.1 | Transmittance spectra versus wavelength                            | 17 |

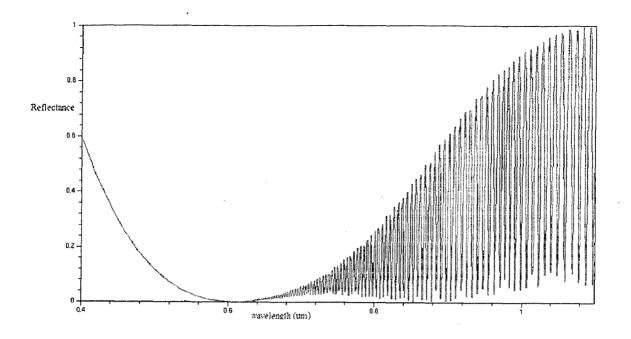

| Figure 3.3.2 | Reflectance spectra versus wavelength                              | 18 |

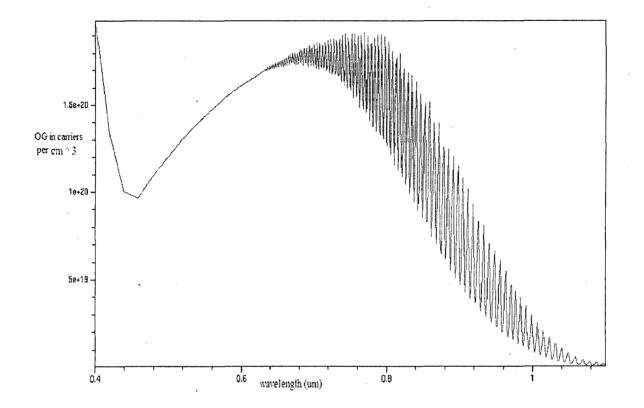

| Figure 3.3.3 | Optical generation versus wavelength                               | 19 |

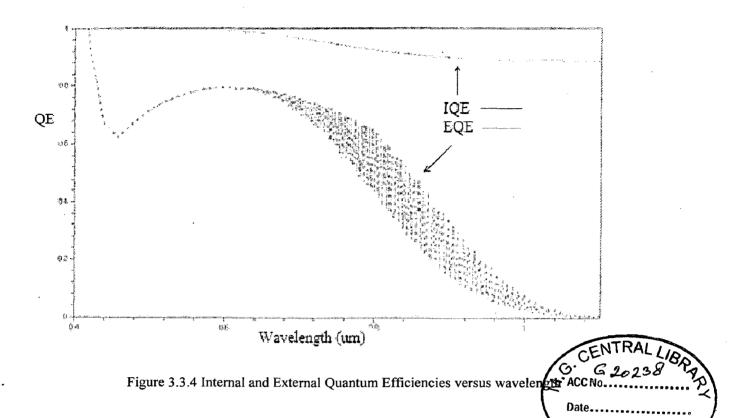

| Figure 3.3.4 | Internal and external quantum efficiencies versus wavelength       | 20 |

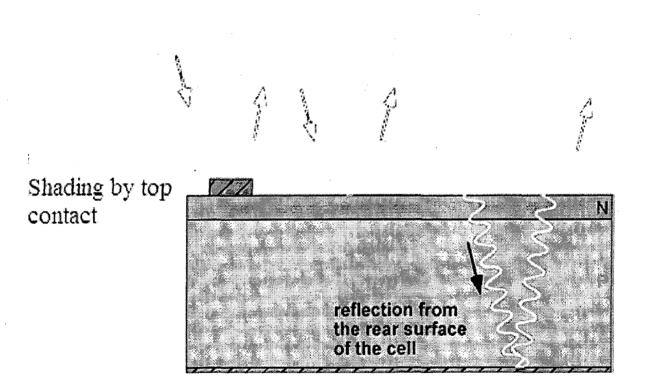

| Figure 4.1.1 | Sources of optical loss in a solar cell                            | 23 |

| Figure 4.2.1 | Use of a quarter wavelength anti-reflection coating to counter     |    |

|              | surface reflection                                                 | 25 |

| Figure 4.2.2 | Effect of ARC                                                      | 25 |

| Figure 4.2.3 | Reflectivity with changing ARC thicknesses                         | 26 |

| Figure 4.3.1 | Change in Voc and Jsc with increasing cell thickness               | 28 |

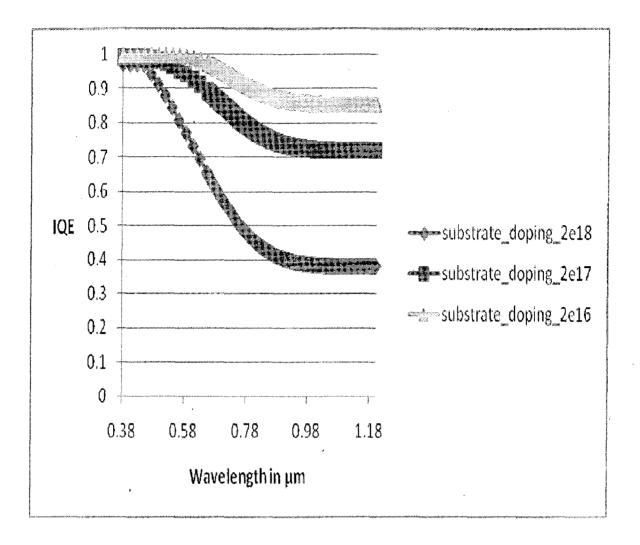

| Figure 4.4.1 | Various recombination losses                                       | 30 |

| Figure 4.5.1 | Change in short circuit current density with varying emitter       |    |

|              | and base doping                                                    | 32 |

| Figure 4.5.2 | Change in IQE with increasing substrate doping                     | 33 |

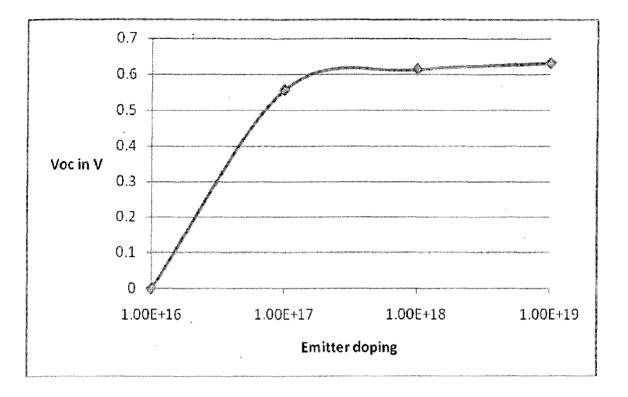

| Figure 4.6.1 | Effect of variation in emitter and base doping on Voc              | 35 |

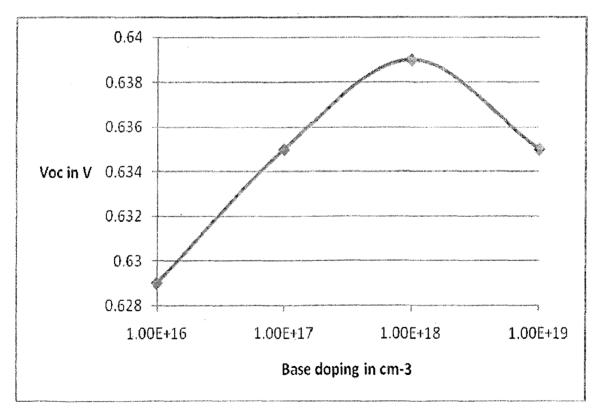

| Figure 4.7.1 | Power loss due to emitter resistance with variation in finger      |    |

|              | Spacing for a $(10 \times 10) \text{ mm}^2$ structure              | 36 |

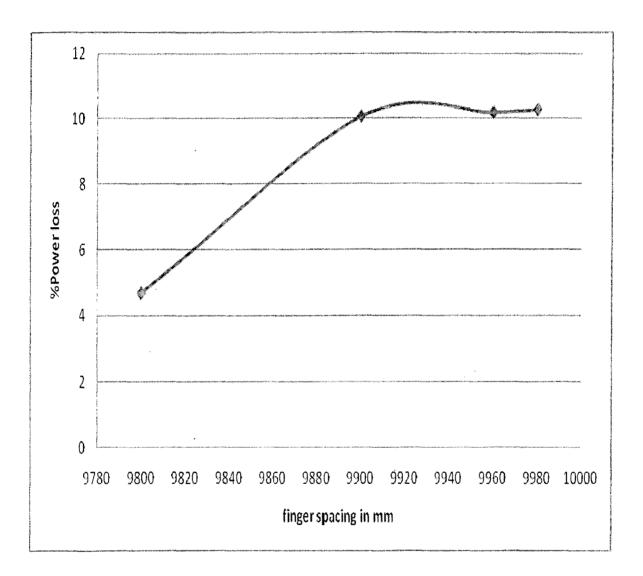

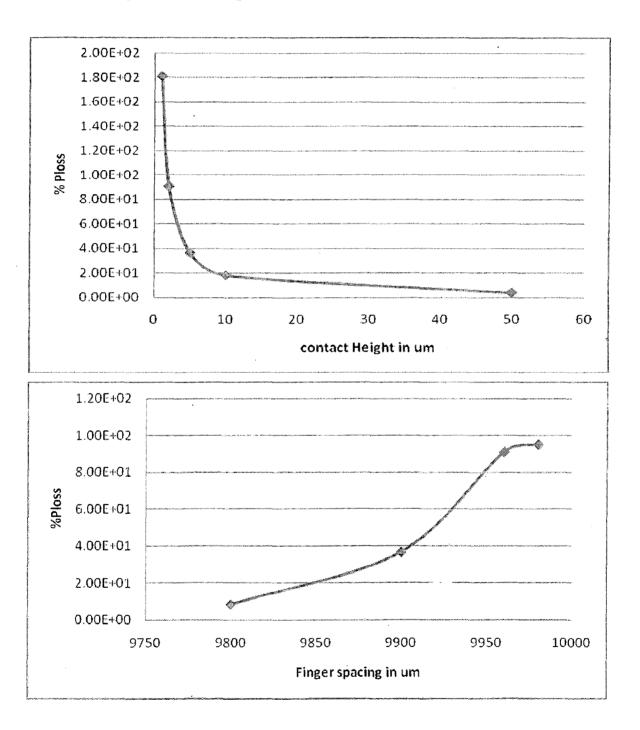

| Figure 4.8.1 | Power loss in finger due to varying finger height and finger width | 37 |

vi

|     | 4.9    | Effect of Intrinsic Electric Field                    | 38 |

|-----|--------|-------------------------------------------------------|----|

|     | 4.10   | Effect of Temperature                                 | 44 |

|     | 4.11   | Effect of Diode Ideality Factor                       | 44 |

| 5.  | OBS    | ERVATIONS AND DISCUSSION                              | 48 |

| 6.  | CON    | CLUSIONS                                              | 51 |

| 7.  | REL    | ABILITY ANALYSIS OF SILICON NANOWIRE MOSFETs          | 52 |

|     | 7.1    | Introduction                                          | 52 |

|     | 7.2    | Progression of Device Structure                       | 53 |

|     | 7.3    | GAA Nanowire Fabrication                              | 55 |

|     | 7.4    | Current GAA Nanowire Performance                      | 57 |

|     | 7.5    | Basic Concept of Hot Electron Degradation             | 59 |

|     | 7.6    | Experimental Setup                                    | 61 |

|     | 7.7    | Results                                               | 65 |

|     | 7.8    | Conclusions                                           | 67 |

| BIE | BLIOG  | RAPHY                                                 | 68 |

| App | oendix | A: Optical properties of Silicon                      | 71 |

| App | oendix | B: Derivation for base, emitter and finger resistance | 73 |

| App | oendix | C: Standard AM1.5G sunlight spectra                   | 78 |

| App | oendix | D: Best research-cell efficiencies                    | 79 |

| PUI | BLICA  | TIONS                                                 | 80 |

iv

# LIST OF TABLES

| Table 2.1   | Division of sun's energy into various EM regions    | 4  |

|-------------|-----------------------------------------------------|----|

| Table 3.4.1 | Comparison of simulated and calculated results      | 20 |

| Table 4.11  | Dependence of ideality factor on recombination type | 45 |

| Table 7.1   | Nanowire and FinFET transistor performance data     | 58 |

# LIST OF FIGURES

| Figure 2.1.1 | Spectral irradiance of the sun                                     | 5  |

|--------------|--------------------------------------------------------------------|----|

| Figure 2.1.2 | Path of sunlight to earth at different times                       | 5  |

| Figure 2.2.1 | Schematic cross-section diagram of a single-junction solar cell    | 6  |

| Figure 2.2.2 | Band diagram of a solar cell under illumination                    | 7  |

| Figure 2.2.3 | I-V characteristics of an illuminated junction                     | 9  |

| Figure 2.2.4 | Current versus Voltage curve (I-V) for a typical solar cell        | 10 |

| Figure 3.1.1 | Part of the solar cell generated by the Sentaurus Structure Editor | 13 |

| Figure 3.2.1 | Flow of input and output files in Sentaurus Device                 | 14 |

| Figure 3.2.2 | Current and power vs. voltage for the illuminated device           | 16 |

| Figure 3.2.3 | I-V curve of the diode without illumination                        | 16 |

| Figure 3.3.1 | Transmittance spectra versus wavelength                            | 17 |

| Figure 3.3.2 | Reflectance spectra versus wavelength                              | 18 |

| Figure 3.3.3 | Optical generation versus wavelength                               | 19 |

| Figure 3.3.4 | Internal and external quantum efficiencies versus wavelength       | 20 |

| Figure 4.1.1 | Sources of optical loss in a solar cell                            | 23 |

| Figure 4.2.1 | Use of a quarter wavelength anti-reflection coating to counter     |    |

|              | surface reflection                                                 | 25 |

| Figure 4.2.2 | Effect of ARC                                                      | 25 |

| Figure 4.2.3 | Reflectivity with changing ARC thicknesses                         | 26 |

| Figure 4.3.1 | Change in Voc and Jsc with increasing cell thickness               | 28 |

| Figure 4.4.1 | Various recombination losses                                       | 30 |

| Figure 4.5.1 | Change in short circuit current density with varying emitter       |    |

|              | and base doping                                                    | 32 |

| Figure 4.5.2 | Change in IQE with increasing substrate doping                     | 33 |

| Figure 4.6.1 | Effect of variation in emitter and base doping on Voc              | 35 |

| Figure 4.7.1 | Power loss due to emitter resistance with variation in finger      |    |

|              | Spacing for a $(10 \times 10) \text{ mm}^2$ structure              | 36 |

| Figure 4.8.1 | Power loss in finger due to varying finger height and finger width | 37 |

vi

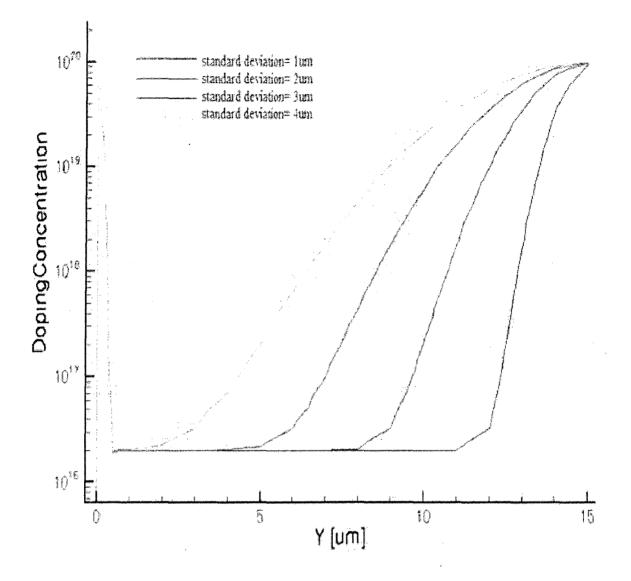

| Figure 4.9.1  | Variation in the doping concentration in the substrate with              |    |

|---------------|--------------------------------------------------------------------------|----|

|               | Different back doping depths                                             | 40 |

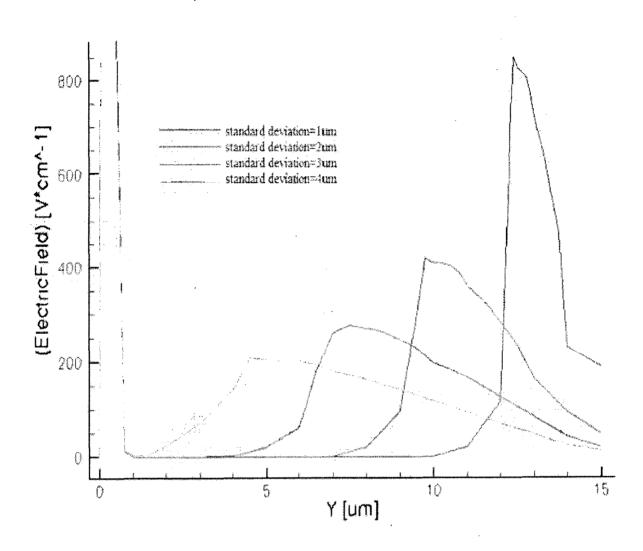

| Figure 4.9.2  | Electric field in the substrate due to different Gaussian doping         |    |

|               | Profiles                                                                 | 41 |

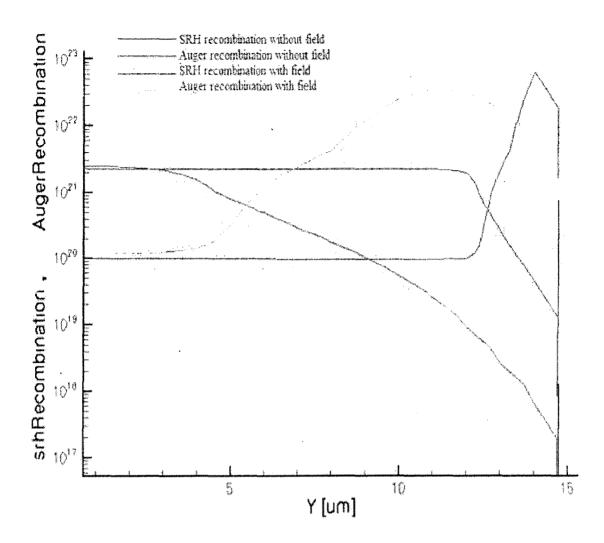

| Figure 4.9.3  | Variation in Auger and SRH recombination with and without                |    |

|               | electric field                                                           | 42 |

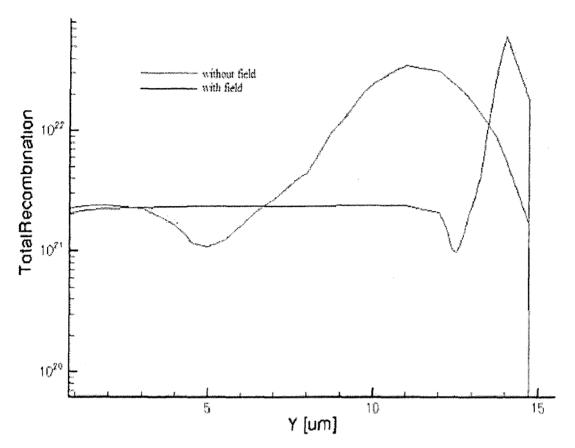

| Figure 4.9.4  | Variation in total recombination with and without electric field         | 43 |

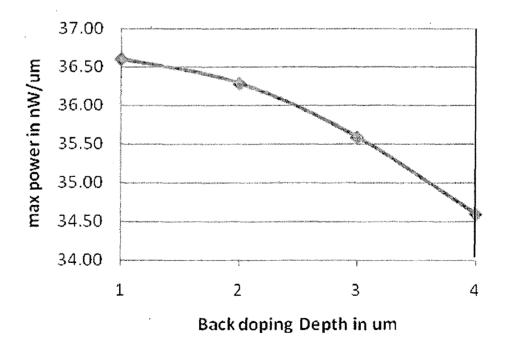

| Figure 4.9.5  | Maximum power points versus back doping depths                           | 43 |

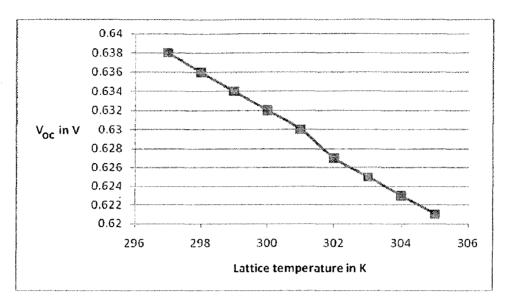

| Figure 4.10.1 | Effect of temperature on Voc                                             | 45 |

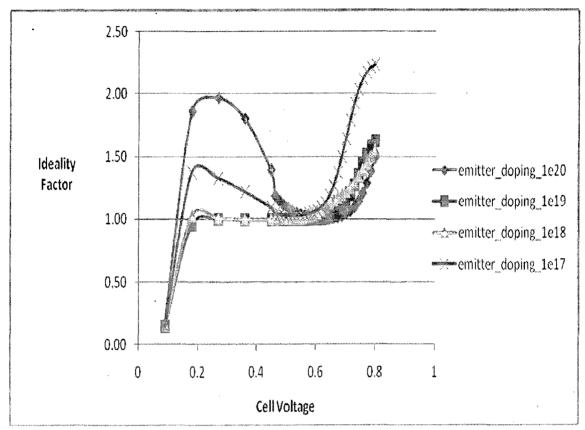

| Figure 4.11.1 | Effect of emitter doping on diode Ideality factor                        | 47 |

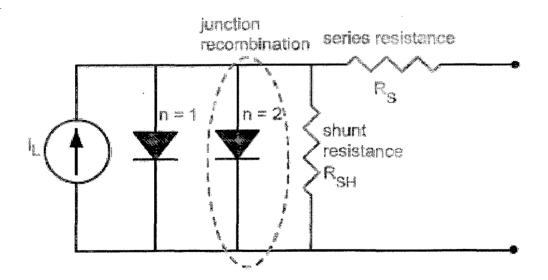

| Figure 4.11.2 | Circuit diagram of the double diode model including the                  |    |

|               | Parasitic series and shunt resistances                                   | 47 |

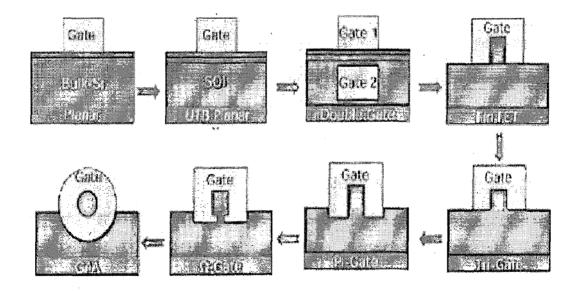

| Figure 7.2.1  | Progression of device structure from single-gated planar to fully        |    |

|               | GAA NW MOSFETs                                                           | 54 |

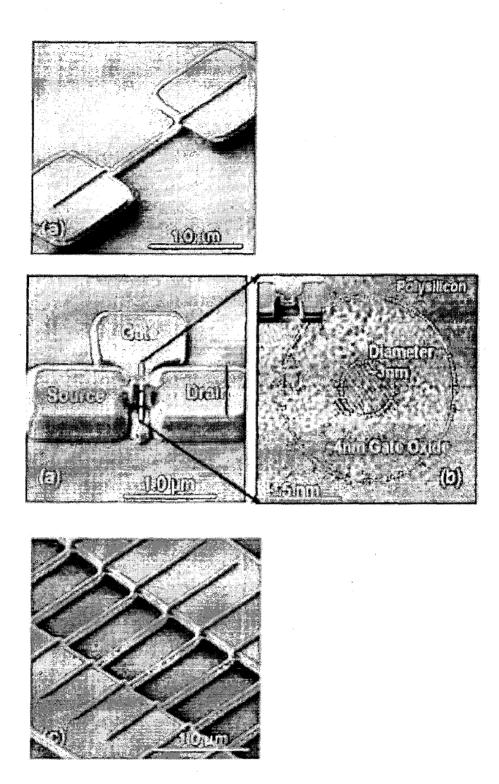

| Figure 7.3.1  | a) Single nanowire b) GAA NW transistor with gate length of              |    |

|               | 350 nm after gate patterning and (b) its TEM cross section in            |    |

|               | Which ~3-nm-thick Si-NW surrounded by 4-nm SiO2 followed                 |    |

|               | by poly-silicon is clearly seen. The inset shows the NW                  |    |

|               | channel before poly-gate deposition.(c)multi fin mosfet                  | 56 |

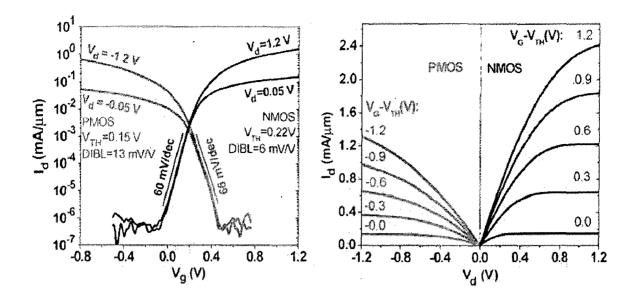

| Figure 7.4.1  | (a) Transfer characteristics of GAA n- and p-FETs (LG = $350 \text{ nm}$ |    |

|               | and $TOX = 4 \text{ nm}$ ) showing near-ideal subthreshold swing         |    |

|               | indicating the excellent electrostatic control. (b) Drain                |    |

|               | current characteristics showing that high drive currents are             |    |

|               | possible in GAA FETs                                                     | 58 |

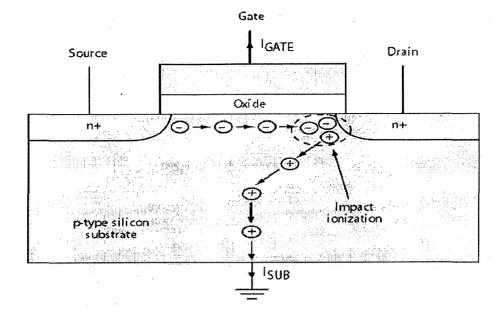

| Figure 7.5.1  | With reducing channel lengths the likelihood of impact ionization        |    |

|               | and the creation of hot carriers increase. These carriers have           |    |

|               | been proven to degrade transistor performance over time                  | 60 |

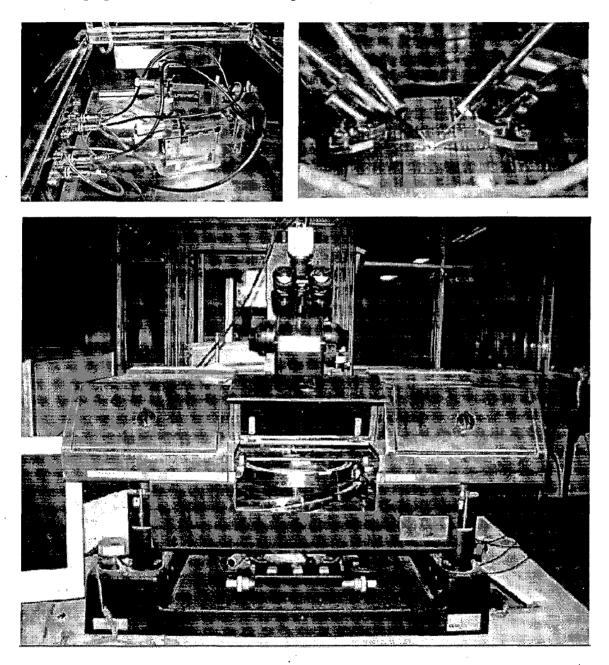

| Figure 7.6.1  | Entire experimental setup for reliability measurements                   | 61 |

| Figure 7.6.2  | Keithley 4200 SCS and KITE software                                      | 62 |

| Figure 7.6.3  | AGILENT 4284A LCR METER                                                  | 62 |

| Figure 7.6.4  | (8 X 11) Programmable FPGA cross points array                            | 63 |

| Figure 7.6.5  | KEITHLEY 237 SMU                                                         | 63 |

| Figure 7.6.6  | SUSS Microtec Probe station                                              | 64 |

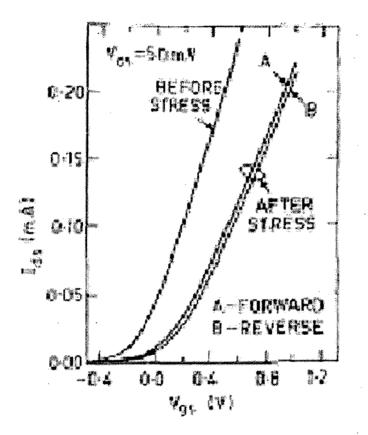

| Figure 7.7.1 | Curves showing the degradation of nMOSFET characteristics           |    |

|--------------|---------------------------------------------------------------------|----|

|              | due to applied stress on the gate terminal                          | 65 |

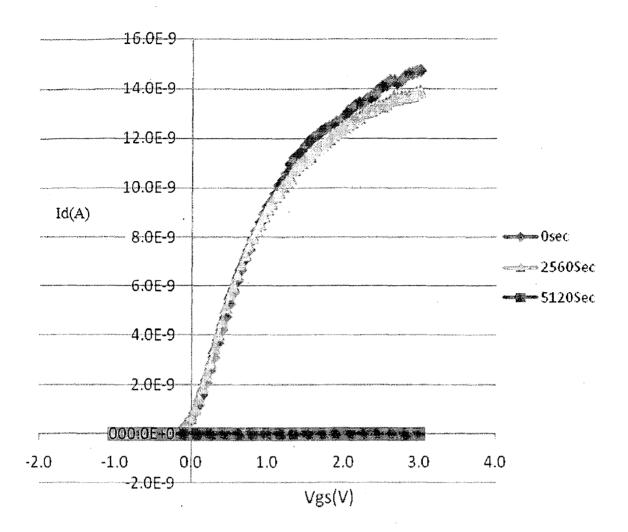

| Figure 7.7.2 | Experimental results obtained for lateral GAA silicon               |    |

|              | nanowire nMOSFETs                                                   | 66 |

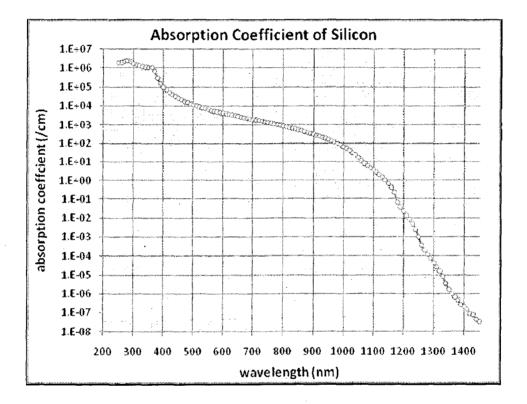

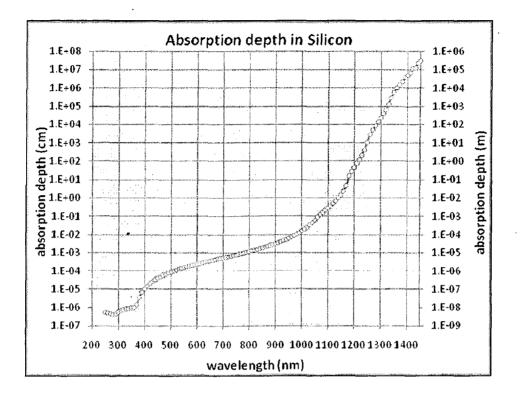

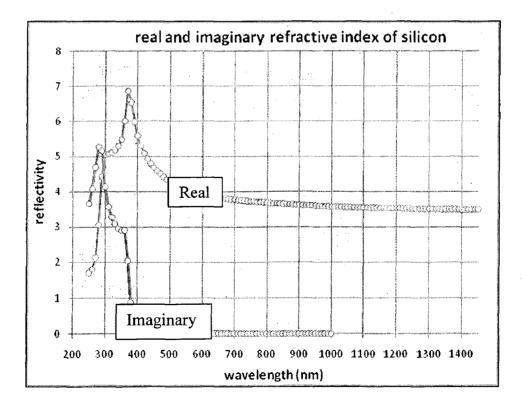

| Figure A1    | Absorption coefficient of silicon in $cm^{-1}$ as a function        |    |

|              | of the wavelength                                                   | 71 |

| Figure A2    | Absorption depth of silicon as a function of the wavelength         | 72 |

| Figure A3    | Real and (negative) imaginary components of the refractive          |    |

|              | index for silicon                                                   | 72 |

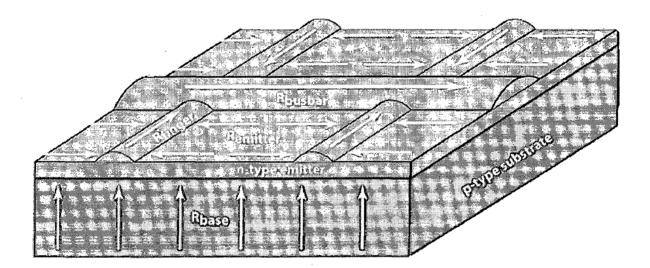

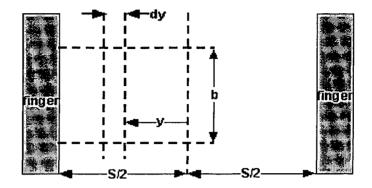

| Figure B1    | Resistive components and current flow in a solar cell               | 73 |

| Figure B2    | Idealized current flow from point of generation to external contact |    |

|              | in a solar cell. The emitter is typically much thinner than shown   |    |

|              | in the diagram                                                      | 74 |

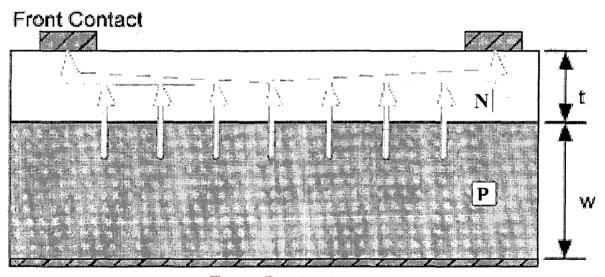

| Figure B3    | Dimensions needed for calculating power loss due to the lateral     |    |

|              | resistance of the top layer                                         | 75 |

| Figure B4    | Calculation of the power loss in a single finger. The width is      |    |

|              | assumed constant and it is assumed that the current is uniformly    |    |

|              | generated and flows perpendicularly into the finger, i.e., no       |    |

|              | current flow directly into the busbar                               | 76 |

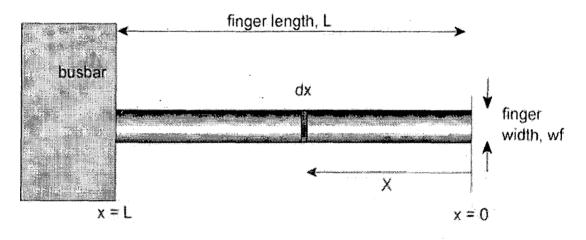

| Figure D1    | Best Research-cell efficiencies                                     | 79 |

.

# LIST OF ABBREVIATIONS

| AM     | Air mass                                          |

|--------|---------------------------------------------------|

| GAA    | Gate All Around                                   |

| EHP    | Electron Hole Pairs                               |

| QE     | Quantum Efficiency                                |

| TCAD   | Technology Computer Aided Design                  |

| TMM    | Transfer Matrix Method                            |

| IQE ·  | Internal Quantum Efficiency                       |

| EQE    | External Quantum Efficiency                       |

| OG     | Optical Generation                                |

| FF     | Fill Factor                                       |

| ARC    | Anti Reflective Coatings                          |

| SRH    | Shockley Read Hall                                |

| BSF    | Back Surface Field                                |

| MOSFET | Metal Oxide Semiconductor Field Effect transistor |

| DIBL   | Drain Induced Barrier Lowering                    |

| SS     | Subthreshold Slope                                |

| LDD    | Lightly Doped Drain                               |

| SMU    | Source Measure Unit                               |

| FN     | Fowler Nordhiem                                   |

| NW     | NanoWire                                          |

| CMOS   | Complementary Metal Oxide Semiconductor           |

ix

#### ABSTRACT

Photovoltaics' has gained importance with the failure of conventional energy resources to meet the energy requirements of various sectors. Crystalline silicon dominates the photovoltaic market today primarily due to its low cost. This work demonstrates a comprehensive study of a single junction two dimensional crystalline silicon solar cell through simulations carried out in Synopsys TCAD Sentaurus version 2007.12. Using the Transfer Matrix Method of the Sentaurus device simulator, the optical and electrical characteristics of the solar cell are simulated. Reflectance and quantum efficiency spectra, as well as dark and light current density-voltage (J-V) curves are calculated. A planar two dimensional silicon structure was used in the setup. The performance of the cell is studied considering various solar cell design parameters like cell thickness, doping of base and emitter, emitter thickness, front contact grid pattern and the design trade-offs are clearly defined.

Silicon nanowire based MOS devices are putting a strong claim as the solution to the scaling constraints on planar MOSFETS due to their strong gate electrostatic control over the channel. A study on the gate oxide reliability of these nanowires is carried out to determine the lifetime of these devices. A quantitative study supported with experimental data is shown to determine the hot carrier degradation on these nanowires.

х

#### **1 INTRODUCTION**

One of the largest challenges mankind will face in the twenty-first century and beyond is how to supply our increasing need for energy. With the rapid consumption rate of fossil fuels, we need to consider renewable energy sources such as photovoltaics. Photovoltaic's is a promising technology that directly takes advantage of our planet's ultimate source of power, the sun. When exposed to light, solar cells are capable of producing electricity without any harmful effect to the environment or device, which means they can generate power for many years while requiring only minimal maintenance and operational costs. Currently, the wide-spread use of photovoltaics over other energy sources is limited by the relatively high cost and low efficiency of solar cells.

The enormous gap between the potential of solar energy and our currently low conversion of it is due to low conversion efficiencies of silicon photovoltaic's, its fixed bandgap and cost of materials currently required. The cost effective raising of conversion efficiency is primarily a scientific challenge. A history of photovoltaic's goes back to 1839, when Edmund Becquerel observed a photovoltaic effect in liquid electrolytes [www.wikipedia.org]. However it was not until 1954 that the first solar cell was developed at Bell Laboratories [1]. Modern research in the area of photovoltaic technologies has lead to creation of a huge spectrum of solar cells, these are commonly classified into three generations which differ from one another based on the material and the processing technology used to fabricate the solar cells. The material used to make the solar cell determines the basic properties of the solar cell, including the typical range of efficiencies. The first generation of solar cells, also known as silicon wafer-based photovoltaic's, is the dominant technology for terrestrial applications today, accounting for more than 85 % of the solar cell market [www.solarbuzz.com].Single-crystalline and multi-crystalline wafers used in commercial production allow power conversion efficiencies up to 25 %, although the fabrication technologies at present limit them to about 15 to 20 % [2].

## 1.1 Objectives

This study aims to determine the performance in terms of electrical and optical characteristics of crystalline silicon solar cells operating under the Air Mass Index 1.5 (AM1.5) sun radiation. To achieve this, the cell is simulated in the Sentaurus version

2007.12 device simulator provided by Synopsys. Simulations include an electrical characterization (current-voltage curve) and an optical characterization (Transmission and Reflectance spectra). The data obtained from the simulations is used to determine performance parameters like conversion efficiencies, internal and external quantum efficiencies, fill factors, series resistance and temperature sensitivities. The choice of structure and dimensions used are meant to simplify the characterization and understanding of the cell.

In order to understand the results in detail this document presents a complete overview of the basic concepts related to solar energy and solar cell operation. Chapter 2 describes a general technical background required for solar cells and also describes the technical definitions commonly-used for solar cell characterization. Chapter 3 elaborates on the solar cell structure and the device specific setup used in the simulator. The effect of varying the various design parameters on the performance of the cell is discussed in the fourth chapter. Finally, the observations and conclusions are presented.

Chapter 7 describes how the GAA silicon nanowire structure seems to have possible novel solutions in the "more-than-moore" regime. It talks about the fabrication techniques of these nanowire FETs and discusses the current available performance of these devices by comparing critical FET parameters. A section within this chapter is devoted to the basic physics of hot carrier degradation mechanisms and the experimental setup used to assess the oxide reliability by observing the breakdown time during stress measuring.

#### 2

### FUNDAMENTAL SOLAR CELL CONCEPTS

Before reviewing the technical aspects of solar cells we take a look at solar radiation and its characteristics.

## 2.1 Solar Energy

Solar energy in one form or another is the source of nearly all energy on the earth. Photovoltaics' (often abbreviated as PV) is a simple and elegant method of harnessing the sun's energy. PV devices (solar cells) are unique in that they directly convert the incident solar radiation into electricity with no noise, pollution or moving parts making them robust, reliable and long lasting. Solar cells are semiconductor devices that are designed to generate electric power when exposed to electromagnetic radiation. Light may be viewed as consisting of "packets" or particles of energy, called photons. A photon is characterized by either a wavelength denoted by  $\lambda$  or equivalently an energy denoted by *E*. There is an inverse relationship between the energy of a photon (*E*) and the wavelength of the light ( $\lambda$ ) given by the equation

$$E = \frac{hc}{\lambda} \tag{2.1.1}$$

where h is Planck's constant ( $6.626 \times 10^{-34}$  Joule-s) and c is the speed of light( $3 \times 10^{8}$  m/s). The photon flux is defined as the number of photons per second per unit area.

$$\phi = \frac{No.of \ photons}{\sec m^2} \tag{2.1.2}$$

Since the photon flux gives the number of photons striking a surface in a given time, multiplying by the energy of the photons comprising the photon flux gives the energy striking a surface per unit time, which is equivalent to a power density. To determine the power density H in units of W/m<sup>2</sup>, the energy of the photons must be in Joules. The equation is

$$H(\frac{W}{m^2}) = \phi \frac{hc}{\lambda}(J) = q \phi \frac{1.24}{\lambda(\mu m)}$$

(2.1.3)

The spectral irradiance as a function of photon wavelength denoted by F is the most common way of characterizing a light source. It gives the power density at a particular wavelength. The units of spectral irradiance are in Wm<sup>-2</sup>µm<sup>-1</sup>. The Wm<sup>-2</sup> term is the power density at the wavelength  $\lambda$  (µm). Hence, the m<sup>-2</sup> refers to the surface area and the µm<sup>-1</sup> refers to the wavelength of interest.

$$F = \left(\frac{W}{m^{2} \mu m}\right) = q \phi \frac{1.24}{\lambda^{2} (\mu m)} = q \phi \frac{E^{2}(eV)}{1.24}$$

(2.1.4)

where F is the spectral irradiance in Wm<sup>-2</sup> $\mu$ m<sup>-1</sup>, $\Phi$  is the photon flux in number of photons m<sup>-2</sup>sec<sup>-1</sup>,E and  $\lambda$  are the energy and wavelength of the photon in eV and  $\mu$ m respectively and q, h and c are constants.

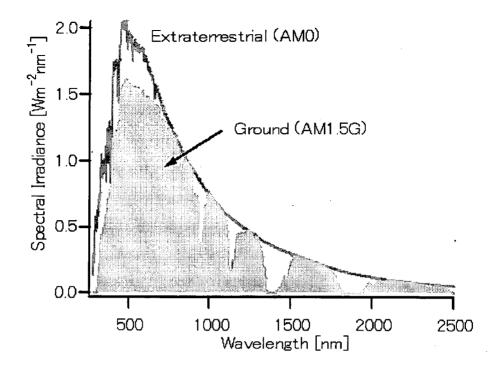

The solar irradiance is the power density incident on a surface due to illumination from the sun. A comparison of solar radiation outside the Earth's atmosphere with the amount of solar radiation reaching the Earth itself is shown in Figure 2.1.1. While the solar radiation incident on the Earth's atmosphere is relatively constant, the radiation at the Earth's surface varies widely due to atmospheric effects, including absorption and scattering, local variations in the atmosphere such as water vapour, clouds, and pollution, latitude of the location and the season of the year and the time of day. For this reason, the typical distribution of light on the surface of the earth shown in Figure 2.1.1 is different than the distribution of light in space. Engineers must consider the spectrum of incident light when designing solar cells.

From Table 2.1, we see that almost 90 % of the sun's energy is concentrated in the visible and infrared part of the electromagnetic spectrum. Hence ideally we should choose a material with a cut-off wavelength close to 4  $\mu$ m so that the entire spectrum is utilized. Silicon with a bandgap of 1.12 eV has a cut-off wavelength of 1.1 $\mu$ m and as a result is not an ideal material for solar cells. However this disadvantage is offset by its low cost of manufacturing. The Air Mass Index is the path length which light takes through the atmosphere normalized to the shortest possible path length (that is, when the sun is directly overhead).

| Radiation | Range of<br>wavelengths(μm) | % of energy<br>carried |

|-----------|-----------------------------|------------------------|

| UV        | 0.15 to 0.38                | 7.6                    |

| Visible   | 0.38 to 0.72                | 48.4                   |

| IR        | 0.72 to 4                   | 43                     |

| Other     | > 4                         | 1                      |

Table 2.1 Division of sun's energy into various EM regions

Figure 2.1.1 Spectral Irradiance of the sun [3]

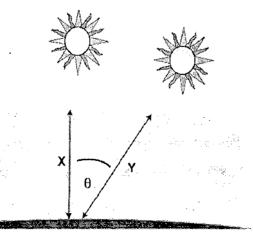

The Air Mass Index quantifies the reduction in the power of light as it passes through the atmosphere and is absorbed by air and dust. The Air Mass Index is defined as

$$AM = \frac{1}{\cos\theta} \tag{2.1.5}$$

where  $\theta$  is the angle shown in Fig 2.1.2.

The Air Mass Index represents the proportion of atmosphere that the light must pass through before striking the Earth relative to its overhead path length, and is equal to Y/X.

Figure 2.1.2 Path of sunlight to earth at different times [4].

The standard spectrum at the Earth's surface is called AM1.5G, (G stands for global and includes both direct and diffuse radiation). The standard AM1.5G spectrum has been normalized to give  $1 \text{ kW/m}^2$  due to the convenience of the round number and the fact that there are inherent variations in incident solar radiation. The standard spectrum is listed in the Appendix page.

### 2.2 Technical Background

Before describing the technical terms commonly used for solar cell characterization, the basic operation of a single junction cell will be discussed.

### 2.2.1 Photovoltaic cell operation

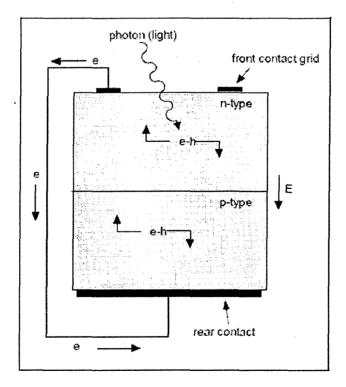

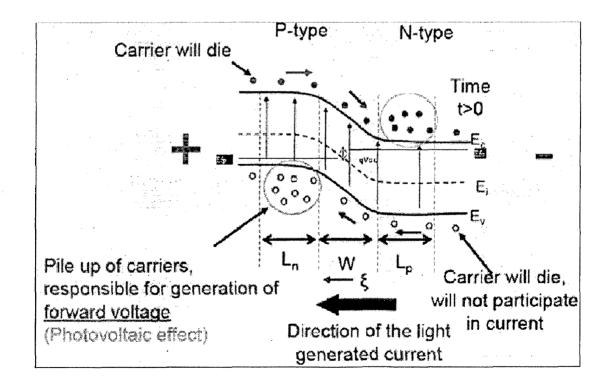

A single-junction photocell is just a p-n junction with metallic rear and front contacts that allow electron conduction to an external load. The front contacts cover only partially the semiconductor to allow the light to enter. In Figure 2.2.1, a schematic cross-section diagram of a single-junction solar cell is displayed. Light enters the semiconductor material through the n region and generates electron-hole pairs (EHP) in the material due to the photoelectric effect.

Figure 2.2.1 Schematic cross-section diagram of a single-junction solar cell [5]

In order to promote an electron into the conduction band, an incoming photon must have energy at least equal to the band gap (assuming all the electrons in the donor levels have already been thermally promoted). Therefore, photons of wavelength greater than the cut-off wavelength will make no contributions to generate electricity in the cell. However, photons with sufficient energy will promote electrons. The n region is designed to be thin while the depletion region is thick. If the EHP is generated in the depletion region, the built-in electric field drifts the electron and hole apart and they will, in the presence of an external load, produce a current through the cell. This current is called the photocurrent. If the EHP is generated in the n or p regions, the electrons and holes drift in random directions and may or may not become part of the photocurrent.

In the case when there is no load, the photons promote electrons into the conduction band on the n-type side, leaving holes in the valance band that can see the junction field and be swept across to the p-type side. Once they reach the p-type side, however, they cannot re-cross the junction; to do so would be to oppose the field. In the p-type material too, electrons become promoted to the conduction band and roll easily down the "hill" into the n-type side, but once they are there, they cannot re-climb the hill. This is analogous to an increase of the thermal current.

Figure 2.2.2 band diagram of a solar cell under illumination

Separation of charge begins to build up, because an excess of electrons become trapped on the n-type side while an excess of holes are trapped on the p-type side. This separation of charge contributes a voltage between the two contacts. This phenomenon is called the photovoltaic effect. The build up of carriers and the band positions are shown in figure 2.2.2. This newly created field competes with and eventually overcomes the junction field and forms a forward biased junction. If this continues, the forward bias will not last. However, the net current must be zero so the recombination current must somehow compensate. The sum of the total junction current and the newly created photocurrent must be zero, so that,

$$I_{J} = |I_{P}| = I_{S}(e^{\frac{qV_{oc}}{kT}} - 1)$$

(2.2.1)

where  $I_p$  flows from the n-type side to the p-type side, while  $I_J$  flows from the ptype material to the n-type material. In the above equation, the potential  $V_{oc}$  is the potential difference set up by the photocurrent. It is the voltage created by the photons, and is called the open circuit voltage. Physically, the majority carriers cross the junction until a situation has been reached in which the difference in potential between the p-type side and the n-type side has "unbent" the bands exactly. In such a situation, the system reaches equilibrium. Then the open circuit voltage must be exactly equal to the contact potential in the junction. Experimentally, this is exactly the case. The open circuit voltage of silicon photovoltaic cells is between 0.5 V and 0.7 V, which is the range of "turn-on potential" in silicon diodes. From this realization, the current equation (2.2.1) can be solved to find the open circuit voltage.

If the junction is uniformly illuminated by photons with energy greater than  $E_g$ an added generation rate  $g_{op}$  (EHP/cm<sup>-3</sup>- s) participates in the diode current. The number of holes created per second within a diffusion length on the n side is  $AL_pg_{op}$ . Similarly  $AL_ng_{op}$  electrons are generated per second within  $L_n$  and  $AWg_{op}$  carriers are generated within W. The resulting current due to collection of these optically generated carriers by the junction is

$$I_p = qAg_{op}(L_p + L_n + W)$$

The thermally generated current adds to the photocurrent and the diode current equation now becomes

$$I_{J} = I_{S}(e^{\frac{qV_{oc}}{kT}} - 1) - I_{p}$$

$$I_{j} = qA(\frac{L_{p}}{\tau_{p}}p_{n} + \frac{L_{n}}{\tau_{n}}n_{p})(e^{\frac{qV}{kT}} - 1) - (qAg_{op}(L_{n} + L_{p} + W))$$

(2.2.2)

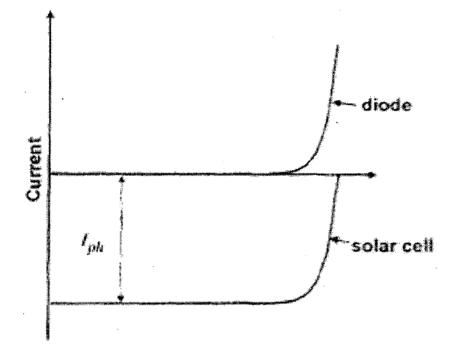

Thus the I-V curve is lowered by an amount proportional to the generation rate as seen in figure 2.2.3. For higher generation rates the graph moves further in the fourth quadrant, signifying an increase in the photocurrent obtained from the cell.

Figure 2.2.3 I-V characteristics of an illuminated junction [5].

When there is an open circuit across the device  $I_j$  is zero and the voltage is obtained by setting the current as zero in equation 2.2.2.

$$V_{OC} = \frac{kT}{q} (\ln(\frac{I_{P}}{I_{S}} + 1)).$$

(2.2.3)

The condition V= 0 gives the following expression for  $I_p$

$$I_{p} = -q A g_{op} \left( L_{n} + L_{p} + W \right)$$

Thus, it is a combination of the photoelectric and photovoltaic effects that produces current and voltage from the cell needed to generate power. The photocurrent is negative with respect to the junction current and hence the net power is negative, which translates to generation of power.

### 2.2.2 Definitions for characterization of photovoltaic devices

The following photovoltaic definitions are extensively used in this document. These are the basic concepts required to understand and characterize the performance of solar cells. As shown in figure 2.2.3 the solar cell I-V shifts down with illumination. Higher the optical generation, greater is the shift in magnitude. As a result, in the fourth quadrant we have positive voltage and negative current meaning a net gain in power. For ease in understanding we shift the characteristics to the 1<sup>st</sup> quadrant by reversing the current and identify the various points on a photovoltaic device I-V curve.

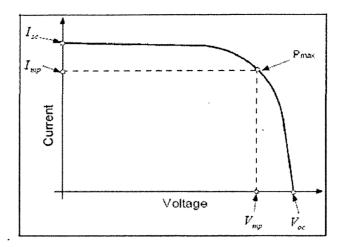

**Current-Voltage curves (I-V):** On an I-V plot, the ordinate refers to current, and the abscissa to voltage. This curve passes through two significant points, the *short-circuit current* ( $I_{sc}$ ) and the *open-circuit voltage* ( $V_{oc}$ ) as seen in Figure 2.2.4. The  $I_{sc}$  refers to the current when the output terminals of the cell are short-circuited. In the plot, this point is the intercept of the curve with vertical axis. The  $V_{oc}$  is the voltage measured at open circuit conditions and is represented as the intercept of the curve with the horizontal axis in the plot.

**Maximum Power point**: The Maximum Power  $(P_{mp})$  point occurs when the product of the current and voltage is maximum. The current and voltage at the maximum power point are denoted by  $I_{mp}$  and  $V_{mp}$ , respectively. This is the point that encloses the most amount of area in the fourth quadrant when vertical and horizontal lines are drawn from the point. The power point is shown in Figure 2.2.4.

**Fill factor, FF**: A percentage given by Equation (2.2.3) that describes how close the I-V curve of a solar cell resembles a perfect rectangle, which represents the ideal solar cell.

$$Fill \ Factor \ (FF) = \frac{I_{mp} V_{mp}}{I_{sc} V_{sc}} [\%]$$

(2.2.4)

Figure 2.2.4 Current versus Voltage curve (I-V) for a typical solar cell [6].

**Quantum efficiency**: Quantum efficiency (QE) is the ratio of the number of charge carriers collected by the solar cell to the number of photons of a given energy incident on the PV device. QE therefore is related to the response of a solar cell to the various wavelengths in the spectrum of incident light on the cell. The QE is given as a function of either wavelength or energy.

**Conversion efficiency**: The conversion efficiency of a solar cell is the percentage of the total incident solar energy on a photovoltaic device that is converted into electrical energy. This relation is given by

$$Conversion \ Efficiency = \frac{P_{mp}}{Incident \ Solar \ Energy} [\%]$$

(2.2.5)

### **3 GENERAL SIMULATION SETUP**

In the past decade, the capabilities of optoelectronic device simulation have advanced tremendously. Faster and more powerful computers enable the numeric simulation of microscopic physical phenomena to investigate and optimize complex state of- the-art optoelectronic devices. Currently, Technology Computer Aided Design (TCAD) is widely used for the development and optimization of new generations of silicon devices. As a powerful, general, semiconductor processing and device simulation suite, TCAD Sentaurus can simulate various optoelectronic devices. A comprehensive set of carrier transport models, combined with an extensive set of optical models implemented in Sentaurus Device, addresses the needs of the optoelectronic community to simulate various devices. In this work we have used TCAD Sentaurus to perform a 2D device simulation of a solar cell. The simulation is organized as a Sentaurus Work Bench (SWB) project. The tool flow of the project is discussed here. It consists of Sentaurus Structure Editor which creates the solar cell structure, Sentaurus Device which calculates the optical device characteristics and the visualization tool Inspect.

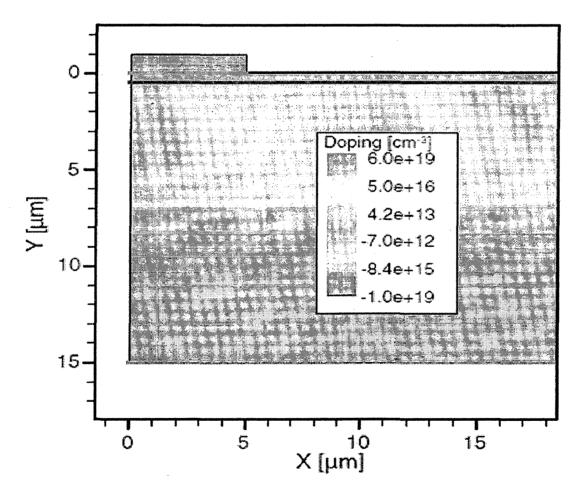

### 3.1 Device Structure in Sentaurus Structure Editor:

Sentaurus Structure Editor defines the two-dimensional solar cell made of silicon. The structure is made of a n-type layer on a p-type silicon substrate, an antireflective coating of silicon nitride, and silver metal contacts. The geometric parameters of the solar cell are defined by setting the following global SWB parameters (The 3rd dimension is assumed to be 1  $\mu$ m.)

- $\blacksquare$  *dfront*, top contact depth, 1 µm

- *wfront*, top contact width,  $5\mu m$

- *wback*, bottom contact width, 600  $\mu$ m

- *wtot*, the total width of the structure, 600  $\mu$ m

- $\blacksquare$  *darcfront*, depth of the antireflective film on top of the structure, 0.075 µm

- $\blacksquare$  dsub, thickness of the cell, 15µm

The solar cell structure is created with analytic doping profiles for the p and n regions and appropriate mesh refinements are added. After the structure is created, the generated mesh and doping information is stored in a file, which is then passed to Sentaurus Device. The solar cell device obtained with Sentaurus Structure Editor is shown in Figure 3.1.1. From the structure, we observe that the junction is formed at a depth of 0.48  $\mu$ m from the top of the device. The n-type doping near the top surface is gaussian with peak concentration of 6e<sup>19</sup>cm<sup>-3</sup> and the p-type doping near the back surface is also gaussian with peak concentration of 1e<sup>19</sup>cm<sup>-3</sup>. The substrate is a p-type silicon substrate with constant doping of 2e<sup>16</sup> cm<sup>-3</sup>. N-type silicon has a better surface quality than p-type, so it is placed at the front of the cell where most of the light is absorbed. A large fraction of the light is absorbed close to the surface, hence by making the front layer very thin; most of the carriers generated by the incoming light are created within a diffusion length of the p-n junction.

Figure 3.1.1 Part of the solar cell generated by the Sentaurus Structure Editor

### **3.2** Device Simulation using Sentaurus Device:

After the structure is created, the generated mesh and doping information is passed to Sentaurus Device. Figure 3.2.1 shows the flow of input and output files in Sentaurus Device. The input files consist of the structure, doping and meshing files passed from Sentaurus Structure Editor. The other input files are the parameter files for

Figure 3.2.1 Flow of input and output files in Sentaurus Device

silicon and silicon nitride. To analyze the performance of solar cells, numerical simulation of the device is done by solving the three governing semiconductor equations, Poisons equations and the electron and hole continuity equations, together with the drift-diffusion model. In simulation, the impurity scattering and carrier-carrier scattering were also considered. The band to band Auger recombination model was included and Shockley-Read-Hall recombination was also modeled. Sentaurus Device calculates the optical generation rate in the solar cell and couples it with the electrical simulation. In this setup, the rate of optical carrier generation for different wavelengths of the incident radiation is calculated using the Transfer Matrix Method (TMM) [7], which is subsequently used in Inspect to calculate the photo generated current. The incident light spectrum i.e. the sunlight AM1.5 spectrum is given as input

in an external file. Three types of calculation are performed in this step, the illuminated I-V, dark I-V and the reflectance and transmittance spectra. The reflectance/transmittance spectra are calculated for a discrete set of wavelengths controlled by the following SWB parameters:

- *wstart* [nm]: Set to 300.

- wend [nm]: Set to 1100.

- *wsteps*: Set to 12.

These parameters correspond to the initial wavelength, final wavelength, and the number of steps between the initial and final wavelengths used to calculate the spectra, respectively. The range of wavelengths is set from 0.38 to 1.1  $\mu$ m which is the range to which silicon responds. The light intensity is defined by the parameter: *intensity* [W m-2]: Set to 1000.

The number of electron hole pairs generated per photon is normalized to 1. The incident light spectrum i.e. the sunlight AM1.5 spectrum is given as input in an external file. Figure 3.2.2 demonstrates the I–V and power curves of the illuminated diode. The photocurrent is opposite to the dark current of the forward-biased diode. For low applied voltage, the photocurrent is independent of the voltage and dominates the I–V curve of the illuminated device. In this regime, the solar cell power grows linearly. When the voltage is increased after the maximum power point is reached, the contribution of the photocurrent to the total current through the diode becomes less important, and the total current changes sign.

The maximum current density and maximum power density are extracted and have the following values, respectively,  $6.932e^{-8}$  A/µm and  $3.664e^{-8}$  W/µm. The value for V<sub>oc</sub> is 0.634 V. The maximum power point is found out to be (0.548 V, 6.68e<sup>-8</sup> A/µm). The fill factor is then calculated from equation (2.2.3) to be 83.3 %.

For the dark characteristics, the optical generation model is not activated and the diode I-V curve is obtained with the same voltage ramping as for the case of illumination. From the dark current plot in Figure 3.2.3, we can see a characteristic I–V curve of a forward-biased diode in this plot.

Figure 3.2.2 Current and power versus voltage for the illuminated device.

Figure 3.2.3 I-V curve of the diode without illumination.

# 3.3 Device Reflectance and Transmittance Calculation in INSPECT:

To obtain the reflectance/transmittance and quantum efficiency spectra, the wavelength is ramped. At higher wavelengths, interference effects lead to fast oscillations in the optical and electrical characteristics. The transmittance and reflectance coefficients of the cell are also stored in the plot file and are presented in Figure 3.3.1 and Figure 3.3.2 respectively. These coefficients are calculated using the depths of the material layers and the complex refractive coefficients as set in the parameter file given as input. For the structure under consideration, the optical radiation is not transmitted for wavelengths below 600 nm. Above this wavelength, transmission grows and multiple reflections become important. Consequently, an occurrence of interference is visible in the fast oscillations of the reflectance/transmittance spectra. The reflectance and transmittance spectra have been normalized by the total incident light hence its maximum value is 1 and minimum 0.

Figure 3.3.1 Transmittance spectra versus wavelength

Figure 3.3.2 Reflectance spectra versus wavelength.

The number of carriers optically generated within the silicon substrate is shown in Figure 3.3.3. It is evident that high energy blue photons create more number of EHPs than low energy red photons. Beyond 1.1  $\mu$ m the carrier generation is almost zero because the photon energy is less than the bandgap of silicon. Near 0.4  $\mu$ m the optical absorption coefficient is very large which means that the absorption depth is very small (Refer Appendix for optical properties of silicon). Due to very small absorption depth, all of the generated carriers are lost in surface recombination at the Si/SiO<sub>2</sub> interface. Hence the UV part of the electromagnetic spectrum does not generate many EHPs in the substrate.

The internal quantum efficiency (IQE) is defined as the ratio of the number of carriers contributing to the electrical current to the total number of photogenerated carriers. The latter can be found through the carrier generation rate integrated over the substrate volume. The IQE is given as [5]

$$IQE = \frac{I}{Gq}$$

(3.3.1)

where I is the electrical current, q is the charge, and G is the optical generation rate. The external quantum efficiency (EQE) is defined as the ratio of the number of electrons in the current to the number of incident photons. The EQE is given as [5]

$$EQE = \frac{Ihc}{q\lambda I_o S}$$

(3.3.2)

where h is Plank's constant, c is the speed of light,  $\lambda$  is the wavelength, Io is the incident light intensity, and S is the incidence surface area.

Figure 3.3.3 Optical Generation versus wavelength

Figure 3.3.4 shows a plot of the Internal and External quantum efficiencies versus wavelength. The efficiencies are defined as a percentage and hence have a range from 0 to 1. As one can see, the quantum efficiencies initially grow with the wavelength. Comparing this to the reflectivity and transmittivity graphs, it is seen that this regime corresponds to the decreasing reflection and increasing absorption. As the wavelength increases, more radiation is transmitted through the structure or reflected from the surface. Consequently, less of the incident light is absorbed and the EQE decreases to almost zero at higher wavelengths. The optically created carriers are still effective in contributing to the electrical current as follows from the IQE curve that stays above 80 %.

# 3.4 Comparison of Simulated and Quantitative Results

The cell current and open circuit voltage values are quantitative calculated using equation 2.2.2. The calculations are done in MatLab and the tabulated results are shown below. The simulated values are obtained from the graphs discussed earlier. The current, voltage and power have units Ampere, Volt and Watt respectively.

|                |          |       | Sim      | ulated |          |             | Calcula     | ted   |

|----------------|----------|-------|----------|--------|----------|-------------|-------------|-------|

| Wavelength(um) | OG       | IQE   | lsc      | Voc    | Pmax     | Celicurrent | CellCurrent | Voc   |

| 0.3            | 1.24E+18 | 0.988 | 1.80E-11 | 0.418  | 5.89E-12 | 5.41E-09    | 3.58E-06    | 0.527 |

| 0.35           | 1.06E+18 | 0.988 | 7.97E-09 | 0.576  | 3.78E-09 | 2.39E-06    | 3.06E-06    | 0.523 |

| 0.4            | 1.95E+17 | 0.988 | 2.83E-09 | 0.549  | 1.27E-09 | 8.48E-07    | 5.64E-07    | 0.479 |

| 0.5            | 1.19E+17 | 0.944 | 2.64E-09 | 0.547  | 1.18E-09 | 3.53E-07    | 3.44E-07    | 0.466 |

| 0.6            | 1.59E+17 | 0.991 | 3.27E-09 | 0.553  | 1.48E-09 | 9.80E-07    | 4.59E-07    | 0.474 |

| 0.7            | 1.79E+17 | 0.963 | 3.03E-09 | 0.551  | 1.37E-09 | 9.10E-07    | 5.17E-07    | 0.477 |

| 0.8            | 1.22E+17 | 0.992 | 1.76E-09 | 0.537  | 7.71E-10 | 5.28E-07    | 3.53E-07    | 0.467 |

| 0.9            | 4.98E+16 | 0.896 | 5.05E-10 | 0.504  | 2.06E-10 | 1.52E-07    | 1.44E-07    | 0.444 |

| 1              | 1.72E+16 | 0.886 | 1.63E-10 | 0.476  | 6.19E-11 | 4.90E-08    | 5.00E-08    | 0.416 |

| 1.1            | 7.41E+14 | 0.884 | 3.90E-12 | 0.379  | 1.13E-12 | 1.17E-09    | 2.00E-09    | 0.334 |

| 1.2            | 1.01E+13 | 0.885 | 5.49E-14 | 0.269  | 1.04E-14 | 1.65E-11    | 6.30E-12    | 0.182 |

Table 3.4.1 Comparison of simulated and calculated results

:/.T.

ROOF

The difference in cell current and open circuit values as compared with the simulated values is due to the fact that that equation 2.2.2 assumes constant doping profile across the junction while the simulator has a gaussian doping profile for the emitter.

#### 4

#### **DESIGN OF SOLAR CELLS & RESULTS**

Solar cell design involves specifying the parameters of a solar cell structure in order to maximize efficiency, given a certain set of constraints. These constraints will be defined by the working environment in which solar cells are produced. For example, in a commercial environment where the objective is to produce a competitively priced solar cell, the cost of fabricating a particular solar cell structure must be taken into consideration. However, in a research environment where the objective is to produce a highly efficient laboratory-type cell, maximizing efficiency rather than cost is the main consideration.

The theoretical efficiency for photovoltaic conversion is in excess of 86.8 % [9]. However, the 86.8 % figure uses detailed balance calculations and does not describe device implementation. For silicon solar cells, a more realistic efficiency under one sun operation is about 29 % [10]. The maximum efficiency measured for a silicon solar cell is currently 24.7 % under AM1.5G. The difference between the high theoretical efficiencies and the efficiencies measured from terrestrial solar cells is due mainly to two factors. The first is that the theoretical maximum efficiency predictions assume that energy from each photon is optimally used, that there are no unabsorbed photons and that each photon is absorbed in a material which has a band gap equal to the photon energy. This is achieved in theory by modeling an infinite stack of solar cells of different band gap materials, each absorbing only the photons which correspond exactly to its band gap. The second factor is that the high theoretical efficiency predictions assume a high concentration ratio. Assuming that temperature and resistive effects do not dominate in a concentrator solar cell, increasing the light intensity proportionally increases the short-circuit current. Since the open-circuit voltage ( $V_{oc}$ ) also depends on the short circuit current,  $V_{oc}$  increases logarithmically with light level. Furthermore, since the maximum fill factor (FF) increases with  $V_{oc}$ , the maximum possible FF also increases with concentration. The V<sub>oc</sub> and FF increase with concentration, which allows concentrators to achieve higher efficiencies. This advantage of concentrator photovoltaics' has led to its wide use.

In designing such single junction solar cells, the principles for maximizing cell efficiency are:

- increasing the amount of light collected by the cell that is turned into carriers;

- increasing the collection of light-generated carriers by the *p-n* junction;

- minimising the forward bias dark current;

- extracting the current from the cell without resistive losses.

### 4.1 **Optical Losses**

Optical losses chiefly effect the power from a solar cell by lowering the shortcircuit current. Optical losses consist of light which could have generated an electronhole pair, but does not, because the light is reflected from the front surface or because it is not absorbed in the solar cell. For the most common semiconductor solar cells, the entire visible spectrum has enough energy to create electron-hole pairs and, therefore, all visible light would ideally be absorbed.

Surface Reflection

Figure 4.1.1 Sources of optical loss in a solar cell.

There are a number of ways to reduce the optical losses:

- Top contact coverage of the cell surface can be minimised (although this may result in increased series resistance).

- Anti-reflection coatings can be used on the top surface of the cell.

- Reflection can be reduced by surface texturing.

- The solar cell can be made thicker to increase absorption (although any light which is absorbed more than a diffusion length away from the junction will not typically contribute to short-circuit current since the carriers recombine).

- The optical path length in the solar cell may be increased by a combination of surface texturing and light trapping.

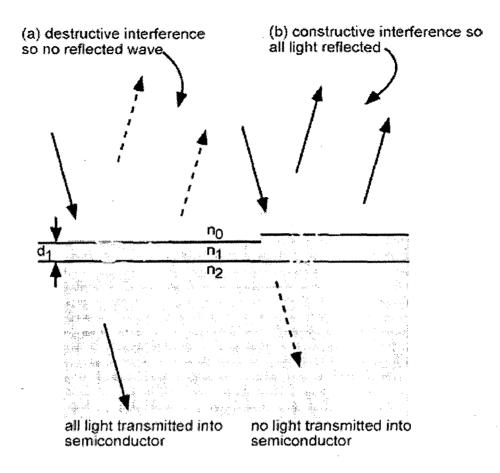

# 4.2 Anti-Reflection Coatings

Anti-reflection coatings on solar cells are similar to those used on other optical equipment such as camera lenses. They consist of a thin layer of dielectric material, with a specially chosen thickness so that interference effects in the coating cause the wave reflected from the anti-reflection coating top surface to be out of phase with the wave reflected from the semiconductor surfaces. These out-of-phase reflected waves destructively interfere with one another, resulting in zero net reflected energy. The thickness of the anti-reflection coating is chosen so that the wavelength in the dielectric material is one quarter the wavelength of the incoming wave. For a quarter wavelength anti-reflection coating of a transparent material with a refractive index  $n_1$  and light incident on the coating with a free-space wavelength  $\lambda_0$ , the thickness  $d_1$  which causes minimum reflection is calculated by [5]

$$d_1 = \frac{\lambda_0}{4n_1}$$

Reflection is further minimised if the refractive index of the anti-reflection coating is the geometric mean of that of the materials on either side; that is, glass or air and the semiconductor. Referring to Figure 4.2.1 the refractive index is expressed by [5]

$$n_1 = \sqrt{n_0 n_2}$$

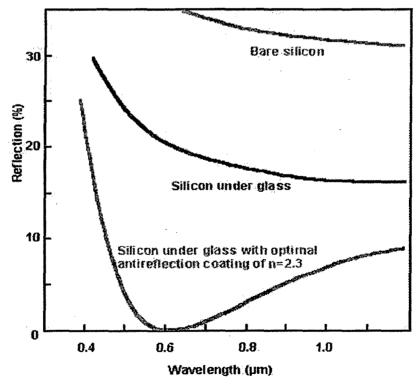

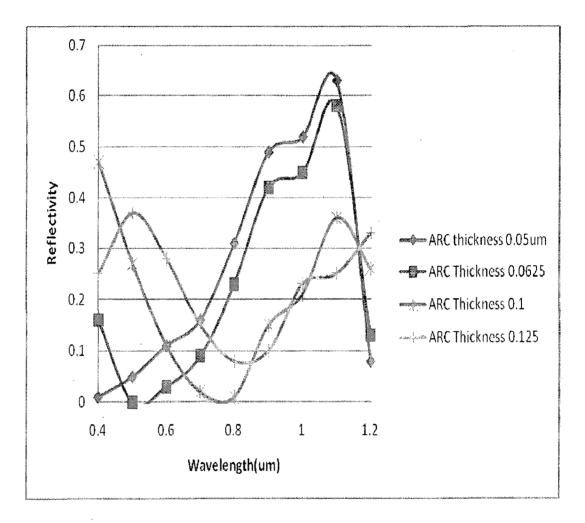

Figure 4.2.3 shows how the reflectivity varies with changing ARC thickness. As we increase the ARC thickness from 0.05 to 0.125  $\mu$ m, the zero reflectivity wavelength increases from 0.4 to 0.8  $\mu$ m. The ARC thickness with 0.0625  $\mu$ m gives zero reflectance around 0.6  $\mu$ m wavelength and is generally preferred as the ARC thickness as it maximizes the cell output.

Figure 4.2.2 shows a comparison of surface reflection from a silicon solar cell, with and without a typical anti-reflection coating. For simplicity, this simulation assumes a constant refractive index for silicon at 3.5. In reality, the refractive index of silicon and the coating is a function of wavelength.

Figure 4.2.1 Use of a quarter wavelength anti-reflection coating to counter surface reflection [4].

Figure 4.2.2 Effect of ARC [11]

Figure 4.2.3 Reflectivity with changing ARC thicknesses.

#### 4.3 Material Thickness

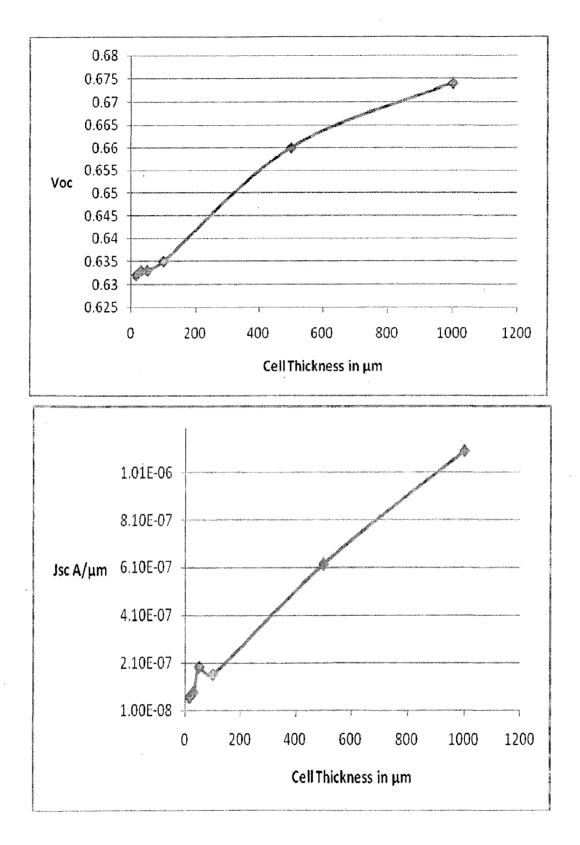

While the reduction of reflection is an essential part of achieving a high efficiency solar cell, it is also essential to absorb all the light in the silicon solar cell. The amount of light absorbed depends on the optical path length and the absorption coefficient. For silicon material in excess of 10 mm thick, essentially all the light with energy above the band gap is absorbed. The 100% of the total current refers to the fact that at 10 mm, all the light which can be absorbed in silicon is absorbed. In material of 10 microns thick, only 30% of the total available current is absorbed. The photons which are lost are the orange and red photons. Figure 4.3.1 shows that with increasing cell thickness more light is absorbed in the cell which translates to an increase in Voc and Jsc.

The optimum device thickness is not controlled solely by the need to absorb all the light. For example, if the light is not absorbed within a diffusion length of the junction, then the light-generated carriers are lost to recombination. As discussed in the "voltage losses due to recombination" section, a thinner solar cell which retains the absorption of the thicker device may have a higher voltage. Consequently, an optimum solar cell structure will typically have "light trapping" in which the optical path length is several times the actual device thickness, where the optical path length of a device refers to the distance that an unabsorbed photon may travel within the device before it escapes out of the device. This is usually defined in terms of device thickness. For example, a solar cell with no light trapping features may have an optical path length of one device thickness, while a solar cell with good light trapping may have an optical path length of 50 times the device thickness, indicating that light bounces back and forth within the cell many times.

#### 4.4 **Recombination Losses**

Photons incident on the solar cell generate electron hole pairs; these generated pairs are called as excess carriers. The generated carriers need to be separated before they recombine, with emission of energy. Recombination causes loss of carriers and affects the performance of the cell. Open circuit voltage  $V_{oc}$  of the cell is affected by recombination of carriers. As recombination increases  $V_{oc}$  reduces. Various techniques are used to reduce the recombination in the solar cells and improve  $V_{oc}$ . Generation of carriers is in the entire volume of the solar cell material. The carriers

Figure 4.3.1 Change in Voc and Jsc with increasing cell thickness

generated near depletion region are separated out very quickly as they get swept away by the electric field present in the depletion region. Whereas the carriers which are generated away from the depletion region that is in the bulk region, on the surface, or at the back surface have less probability of getting separated. These carriers will be lost and would not contribute to the current flow if they recombine. Recombination of carriers generated in the Solar cells due to photo excitation is one of the most dominating loss mechanisms occurring in the solar cell. Various mechanisms which contribute to the recombination phenomenon are included and are shown in Figure 4.4.1. These and described below

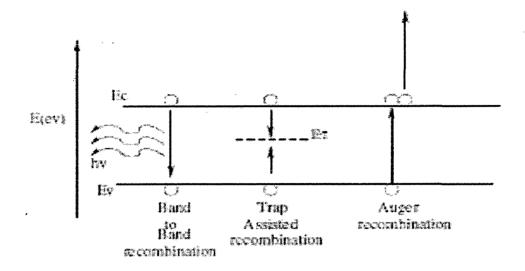

1. Band to band recombination: It is a radiative form of recombination in which an electron from conduction band combines with the hole in the valence band with emission of energy (light). Band to band recombination most efficiently occurs in direct band gap semiconductors. The emitted photon has an energy similar to the band gap and is therefore only weakly absorbed such that it can exit the piece of semiconductor.

2. Trap assisted recombination: It is the dominant form of recombination mechanism in most of the solar cells. Recombination through defects, also called Shockley-Read-Hall or SRH recombination, does not occur in perfectly pure, defect free materials. Due to the impurities present in the semiconductor an additional energy level  $E_t$  is introduced within the forbidden energy gap. This energy level acts as a trap and captures electrons and holes, leading to recombination. Trap assisted recombination is a two step process in which electrons and holes recombine in traps and then fall back into the valence band, completing the recombination process. The rate at which carriers move into the energy level in the forbidden gap depends on the energy difference distance of the introduced energy level from either of the band edges. Therefore, if an energy level is introduced close to either band edge, recombination is less likely as the electron is likely to be re-emitted to the conduction band edge rather than recombine with a hole which moves into the same energy state from the valence band. For this reason, energy levels near mid-gap are very effective for recombination.

3. *Surface recombination*: Surface of the solar cell has a large number of dangling bonds due to abrupt termination of crystal structure. These dangling bond acts as recombination centres. Carriers generated at the surface fall in to the dangling bonds and recombine with holes.

Figure 4.4.1 various recombination losses

4. Auger recombination: Solar cells when exposed to high intensity of photons, exhibit the phenomenon of Auger recombination. It involves three particle electron-electron-hole or hole-hole-electron. When hole from the valence band recombines with the electron in the conduction band, the excess energy released during recombination is absorbed by the neighbouring electron in the conduction band which then goes to some higher energy level and then again falls back to the conduction band with release of energy. Auger recombination is most important in heavily doped or heavily excited materials.

Recombination losses affect both the current collection (and therefore the short-circuit current) as well as the forward bias injection current (and therefore the open-circuit voltage). Recombination is frequently classified according to the region of the cell in which it occurs. Typically, recombination at the surface (surface recombination) or in the bulk of the solar cell (bulk recombination) are the main areas of recombination. The depletion region is another area in which recombination can occur (depletion region recombination). Surface recombination can have a major impact both on the short-circuit current and on the open-circuit voltage. High recombination rates at the top surface have particularly detrimental impact on the short-circuit current since top surface also corresponds to the highest generation region of carriers in the solar cell. Lowering the high top surface recombination is

typically accomplished by reducing the number of dangling silicon bonds at the top surface by growing a "passivating" layer (usually silicon dioxide) on the top surface. Since the passivating layer for silicon solar cells is usually an insulator, any region which has an ohmic metal contact cannot be passivated using silicon dioxide. Instead under the top contacts, the effect of the surface recombination can be minimised by increasing the doping. While typically such a high doping severely degrades the diffusion length, the contact regions do not participate in carrier generation and hence the impact on carrier collection is unimportant.

A similar effect is employed at the rear surface to minimize the impact of rear surface recombination velocity on voltage and current if the rear surface is closer than diffusion length to the junction. A "Back Surface Field" (BSF) consists of a higher doped region at the rear surface of the solar cell. The interface between the high and low doped region behaves like a p-n junction and an electric field forms at the interface which introduces a barrier to minority carrier flow to the rear surface. The minority carrier concentration is, thus, maintained at higher levels in the undoped region and the BSF has a net effect of passivating the rear surface.

#### 4.5 Current Losses Due to Recombination

In order for the p-n junction to be able to collect all of the light-generated carriers, both surface and bulk recombination must be minimised. In silicon solar cells, the two conditions commonly required for such current collection are:

- The carrier must be generated within a diffusion length of the junction, so that it will be able to diffuse to the junction before recombining and

- In the case of a localised high recombination site (such as at an unpassivated surface or at a grain boundary in multicrystalline devices), the carriers must be generated closer to the junction than to the recombination site. For less severe localised recombination sites, (such as a passivated surface), carriers can be generated closer to the recombination site while still being able to diffuse to the junction and be collected without recombining.

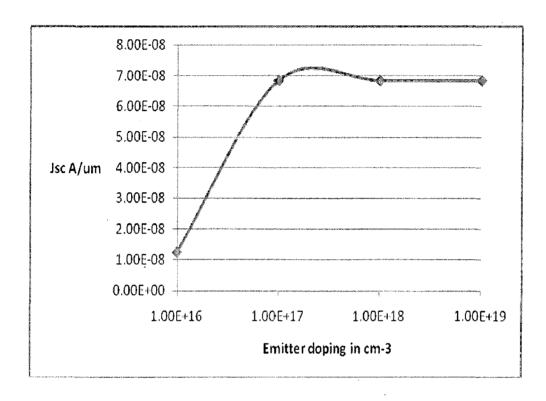

Figure 4.5.1 shows how the cell short circuit current reduces with increasing doping for the base and emitter. Increasing the doping takes the junction deeper into the cell and hence should increase the number of carriers collected by the contacts. However, bulk recombination dominates due to reduced material quality. This reduces

the current. The presence of localised recombination sites at both the front and the rear surfaces of the silicon solar cell means that photons of different energy will have different collection probabilities.

Figure 4.5.1 Change in short circuit current density with varying emitter and base doping

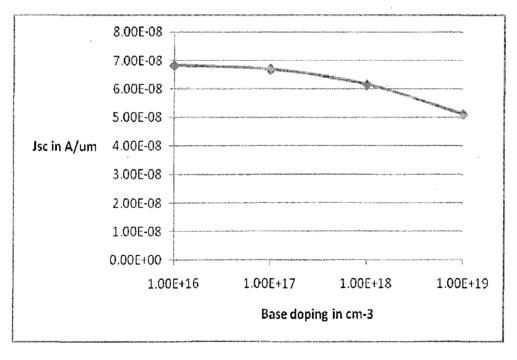

Figure 4.5.2 Change in IQE with increasing substrate doping

The quantum efficiency of a solar cell quantifies the effect of recombination on the light generation current. Figure 4.5.2 shows how the IQE reduces with increasing substrate doping. This translates to a reduction in current obtained from the cell. Since blue light has a high absorption coefficient and is absorbed very close to the front surface, it is not likely to generate minority carriers that can be collected by the junction if the front surface is a site of high recombination. Similarly, a high rear surface recombination will primarily affect carriers generated by infrared light, which can generate carriers deep in the device.

# 4.6 Voltage Losses Due to Recombination

The open-circuit voltage is the voltage at which the forward bias diffusion current is exactly equal to the short circuit current. The forward bias diffusion current is dependent on the amount of recombination in a p-n junction and increasing the recombination increases the forward bias current. Consequently, high recombination increases the forward bias diffusion current, which in turn reduces the open-circuit voltage. The material parameter which gives the recombination in forward bias is the diode saturation current. The recombination is controlled by the number of minority carriers at the junction edge and depends as to how fast they move away from the junction and how quickly they recombine. Consequently, the dark forward bias current, and hence the open-circuit voltage is affected by the following parameters:

- <u>The number of minority carriers at the junction edge</u>. The number of minority carriers injected from the other side is simply the number of minority carriers in equilibrium multiplied by an exponential factor which depends on the voltage and the temperature. Therefore, minimising the equilibrium minority carrier concentration reduces recombination. Minimising the equilibrium carrier concentration is achieved by **increasing the doping**;

- <u>The diffusion length in the material</u>. A low diffusion length means that minority carriers disappear from the junction edge quickly due to recombination, thus, allowing more carriers to cross and increasing the forward bias current. Consequently, to minimise recombination and achieve a high voltage, a **high diffusion length is required**. The diffusion length depends on the type of material, the processing history of the wafer and the doping in the wafer. High doping reduces the diffusion length, thus introducing a trade-off between maintaining a high diffusion length (which affects both the current and voltage) and achieving a high voltage;

- The presence of localised recombination sources within a diffusion length of the junction. A high recombination source close to the junction (usually a surface or a grain boundary) will allow carriers to move to this recombination source very quickly and recombine, thus dramatically increasing the recombination current. The impact of surface recombination is reduced by **passivating the surface**.

The net effect of previous trade-offs is shown in the graphs below.

Figure 4.6.1Effect of variation in emitter and base doping on Voc

# 4.7 Emitter Resistance

Based on the sheet resistivity, the power loss due to the emitter resistance can be calculated as a function of finger spacing in the top contact. Refer to Appendix for the derivation of total power lost due to emitter resistance. Using equation (B.4) the power lost due to emitter resistance is shown in Figure 4.7.1.

Figure 4.7.1 Power loss due to emitter reisitance with variation in finger spacing for a (10X10) mm structure.

# 4.8 Finger Resistance

To provide higher conductivity, the top of the cell has a series of regularly spaced fingers. The resistive loss in a finger is calculated and given in the Appendix. The structure has been altered to have two contacts, one each at either ends of the top surface. The spacing between the fingers is varied and using equation (B.6), the power loss due to finger resistance is plotted below.

Figure 4.8.1 Power loss in finger due to varying finger height and finger width

It is seen that as the finger width is increased or the finger spacing is reduced, the power loss is reduced. However this occurs at the expense of shading losses which increase due to increased contact area. Similarly, varying the contact height reduces the contact resistance significantly but increasing the height can increase the shadow losses since light is not always perpendicular to the cell.

## 4.9 Effect of Intrinsic Electric Field

It is well known that the presence of electric field can improve solar cell performance [18], although an electric field is not an essential requirement for photovoltaic conversion. Doping gradients can induce built-in fields in solar cells [8]. The effect of electric fields created by doping gradients is quantitatively analyzed and clear boundaries are found as to when built-in fields are beneficial or deleterious. In the case of a doping gradient  $N_A(x)$  in the p-type material, approximate balance between majority carrier hole drift and diffusion generates a field E ideally given by

$$E_{p} = \frac{kT}{qN_{A}} \frac{dN_{A}}{dx}$$

(4.9.1)

where kT/q is the thermal voltage (25.852mV at 300K). This field acts in the opposite direction on electrons as compared to holes and can aid the collection of the minority carrier electrons [12].

Under low injection - a regime of particular importance for solar cell operation the majority carrier concentration can be assumed excitation independent, and the effect of recombination can be discussed in terms of minority- carrier lifetime. In p-type material, for example the recombination rate can be written as

$$U = \frac{1}{\tau_n} (n - n_0)$$

(4.9.2)

where  $\tau_n$  is the minority-carrier (electron) lifetime and  $(n-n_o)$  is the excess electron concentration. The inverse of the lifetime – the rate constant – is a sum of the different contributions to the lifetime.

$$\frac{1}{\tau} = \frac{1}{\tau_{rad}} + \frac{1}{\tau_{Auger}} + \frac{1}{\tau_{SRH}}$$

(4.9.3)

Radiative recombination is very less for an indirect bandgap semiconductor like silicon. SRH recombination dominates for doping levels below 10<sup>18</sup> cm<sup>-3</sup>. However, there is no general agreement about the dominant mechanism that limits the minority carrier lifetime in heavily doped silicon (in the range of 10<sup>18</sup>-10<sup>20</sup> cm<sup>-3</sup>). There is a common observation that lifetime decreases with increasing dopant concentration. Phonon assisted band to band Auger recombination appears to explain the measured lifetimes satisfactorily in p-type silicon [13,14]. The effect of lifetime on transport properties by carrier diffusion can be discussed in terms of diffusion length defined by .

$$L_n = \sqrt{D_n \tau} \tag{4.9.4}$$

where  $D_n$  is the diffusion constant for the minority carriers in question. The contribution to lifetime due to defects has been empirically observed to follow the equations [5]

$$\frac{1}{\tau_{SRH}} = (\frac{1}{2.5^* 10^{-3}} + 11.76^* 10^{-13} N_A) (\frac{300}{T})^{0.57}$$

(4.9.5)

Similarly the contribution by band to band Auger recombination can be described by the expression [5]

$$\frac{1}{\tau_{AUGER}} = 1.83 * 10^{-31} N_A^{2} \left(\frac{T}{300}\right)^{1.18}$$

(4.9.6)