# A RECONFIGURATION TECHNIQUE FOR MULTILEVEL INVERTER INCORPORATING A DIAGNOSTIC SYSTEM BASED ON ANFIS

# **A DISSERTATION**

# Submitted in partial fulfillment of the requirements for the award of the degree of MASTER OF TECHNOLOGY

in

# ELECTRONICS AND COMMUNICATION ENGINEERING (With Specialization in Control & Guidance)

By SURYANARAYANA.V

DEPARTMENT OF ELECTRONICS AND COMPUTER ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE -247 667 (INDIA) JUNE, 2010

# CANDIDATE'S DECLARATION

I hereby declare that the work presented in this dissertation report entitled "A **Reconfiguration Technique for Multilevel Inverter Incorporating a Diagnostic System Based on ANFIS**" submitted for the award of the degree of Master of Technology with specialization in Control & Guidance in the department of Electronics & Computer Engineering, Indian Institute of Technology Roorkee, is an authentic record of my own work carried out from June 2009 to June 2010, under the guidance of Dr. Vijay kumar, Department of Electronics & Computer Engineering, Indian Institute of Technology Roorkee.

I have not submitted the mater embodied in this dissertation for the award of any other degree.

Date: Place: Roorkee

YANARAYANA)

# **CERTIFICATE**

This is to certify that the above statement made by the candidate is true to the best of my knowledge and belief.

<sup>r</sup> Kumar)

Date: 22-06-16 Place: Roorkee. Department of Electronics & Computer Engineering, Indian Institute of Technology Roorkee, Roorkee-247667,India.

#### ACKNOWLEDGEMENT

I express my foremost and deepest gratitude to **Dr.Vijay Kumar**, Department of Electronics & Computer Engineering, Indian Institute of Technology Roorkee, Roorkee for his valuable guidance, support and motivation throughout this work. The valuable hours of discussion and suggestions that I had with him have undoubtedly helped in supplementing my thoughts in the right directions for attaining the desired objective. I consider myself extremely fortunate for having got the opportunity to learn and work under his able supervision over the entire period of my association with him.

My sincere thanks to all faculty members of Control & Guidance for their constant encouragement, caring words, constructive criticism and suggestions towards the successful completion of this work. I would like to thank the head of the department for providing lab facilities and lab staff for their help in using lab requirements.

Last but not the least, I am highly indebted to my parents and family members, whose sincere prayers, best wishes, moral support and encouragement have a constant source of assurance, guidance, strength and inspiration to me.

> (V.SURYANARAYA) IITRoorkee June, 2010

### ABSTRACT

Multilevel Inverter have become a research hotspot in high voltage and high power applications because of their many advantages, such as their low voltage stress on power switches, low harmonic and EMI output. However, the increasing of the power devices improves the system's fault rate. How to ensure stable operation of the system has become an important research question.

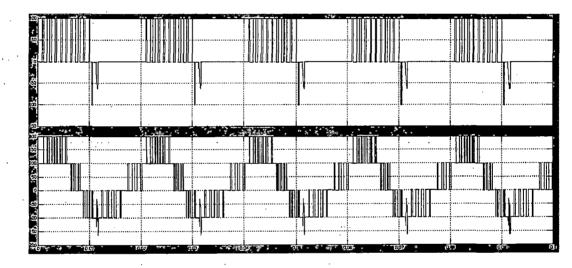

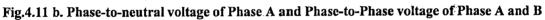

In this thesis work, a fault diagnostic system in a multilevel-inverter using Fuzzy inference System and an Adaptive Neuro Fuzzy Inference System are developed. These techniques are applied to the fault diagnosis of a Multi Level Inverter (MLI) system to avoid the difficulties in using mathematical models. This thesis work presents a fault detection method for open-circuit and short circuit faults of a switching device in diode-clamped inverter systems, which is based on the inherent characteristic of continuous pulse width modulation and its reconfiguration method to avoid feeding faulted output to load.

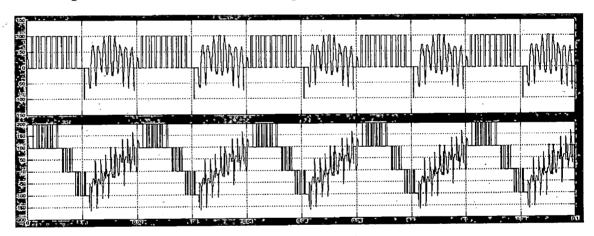

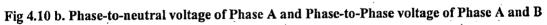

The phase-to-phase and phase-to-Neutral voltages include information of switching states in the inverter system corresponding to their respected legs but not affected by the load. Therefore, a fault condition of the inverter system itself can be diagnosed through analysis of any of these voltages. Compared to conventional fault detection methods, the present fault detection method has faster detection capability that is within 1 cycle period it can detect the fault and is much simpler to implement. Therefore, the use of the method presented could minimize harmful effects such as imbalance of dc-link voltage and overstress on other switching devices.

| CANDIDATE  | S DECLARATION                                                | i    |

|------------|--------------------------------------------------------------|------|

| ACKNOWLE   | DGEMENT                                                      | ii   |

| ABSTRACT   | · · · · · · · · · · · · · · · · · · ·                        | iii  |

| CHAPTER-1  | INTRODUCTION                                                 | 1    |

|            | 1.1 Problem Description                                      | 4    |

|            | 1.2 Organization of the Thesis work                          | 6    |

| CHAPTER-2  | A SURVEY OF TOPOLOGIES, CONTROL METHODS,                     |      |

|            | APPLICATIONS AND THEIR SIMULINK MODELS                       | 7    |

|            | 2.1 Inverter Topologies                                      | 9    |

|            | 2.1.1 Diode-Clamped Inverter                                 | 9    |

|            | 2.1.2. Capacitor-Clamped Inverter                            | 11   |

| · · · ·    | 2.1.3. Cascaded Multilevel Inverters                         | . 13 |

|            | 2.2 Control Methods for Inverter                             | 14   |

| <b>x</b> ' | 2.2.1 Need for the Control of the Inverter                   | 14   |

| ۰.         | 2.2.2 Sinusoidal Pulse Width Modulation                      | 15   |

| CHAPTER -  | 3 THREE LEVEL INVERTERS                                      | 19   |

|            | 3.1 General discussion                                       | 17   |

|            | 3.2 Three-Level Inverter                                     | 18   |

|            | 3.2.1 Operation of Three-Phase 3-Level Inverter              | 18   |

|            | 3.3 Sinusoidal PWM for A Three-Level Inverter                | 20   |

|            | 3.4 Simulation and Analysis                                  | 20   |

| ,          | 3.4.1 Simulation of three-level inverter with Sinusoidal PWM | 23   |

|            | 3.4.2 Sinusoidal PWM Control Block                           | 24   |

|            | 3.4.3 3-Level Bridge Using Diode-Clamped Topology            | 25   |

| CHAPTER -4 | FAULT DETECTION IN MULTI LEVEL INVERTER                      |      |

|            | USING FUZZY INFERENCE SYSTEM AND ANFIS                       | 26   |

|            | 4.1 Fuzzy Inference Systems and ANFIS                        | 27   |

|            | 4.2 General Structure of the fault diagnostic system         | 36   |

|            | 4.3 Fault detection using Fuzzy Inference system             | 37   |

|            | 4.4 Fault detection using Adaptive Neuro Fuzzy Inference System | 40     |

|------------|-----------------------------------------------------------------|--------|

|            | 4.4.1 Normal Operation                                          | 43     |

|            | 4.4.2 Fault on switch 1                                         | 44     |

|            | 4.4.3 Fault on switch 2                                         | 47     |

|            | 4.4.4 Fault on switch 3                                         | 50     |

|            | 4.4.5 Fault on switch 4                                         | 53     |

|            | 4.4.6 Fault on switch 5                                         | 56     |

|            | 4.4.7 Fault on switch 6                                         | 59     |

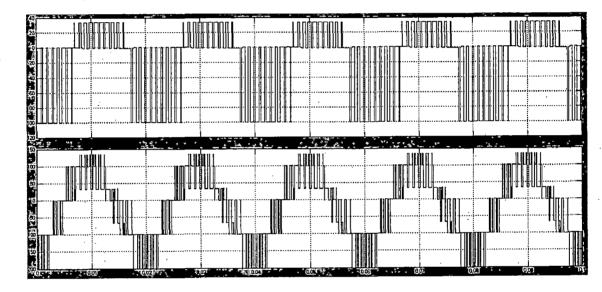

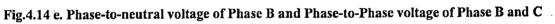

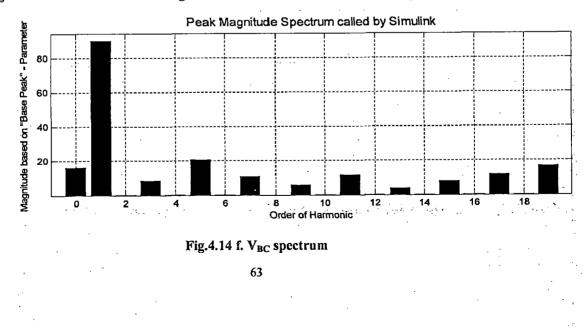

|            | 4.4.8 Fault on switch 7                                         | 62     |

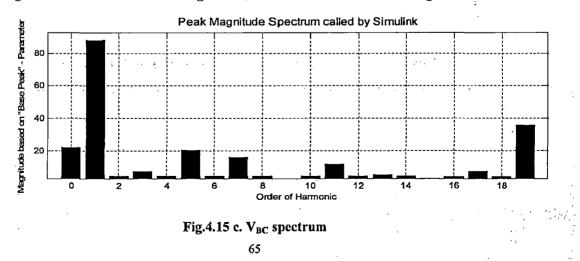

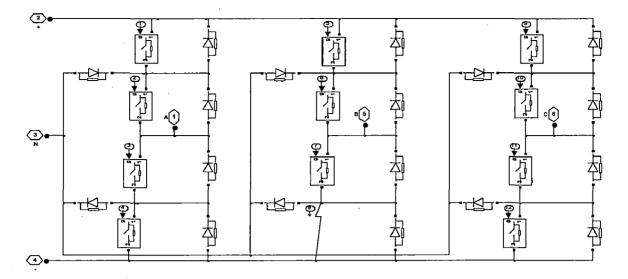

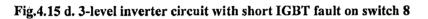

|            | 4.4.9 Fault on switch 8                                         | 65     |

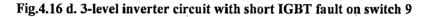

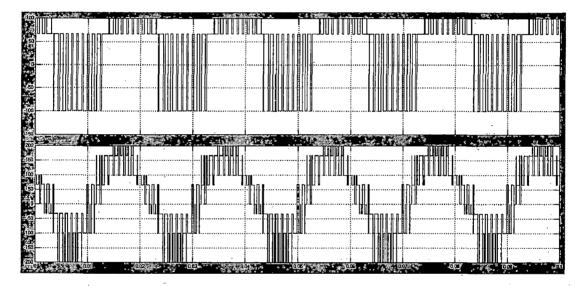

|            | 4.4.10 Fault on switch 9                                        | 68     |

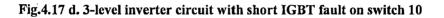

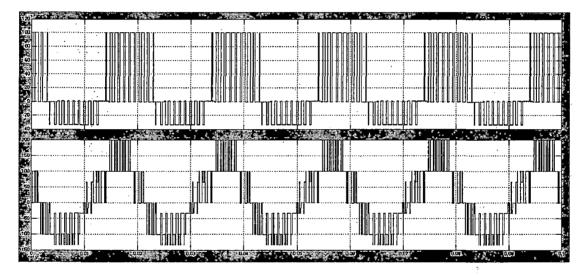

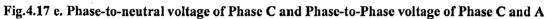

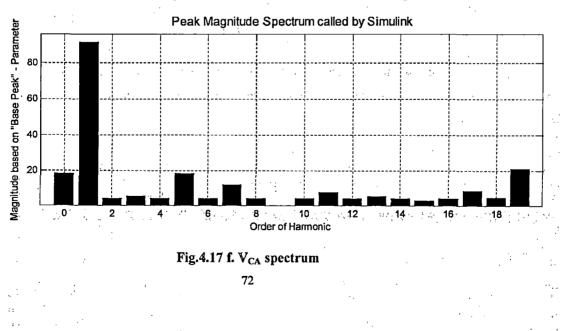

|            | 4.4.11 Fault on switch 10                                       | 71     |

|            | 4.4.12 Fault on switch 11                                       | 74     |

|            | 4.4.13 Fault on switch 12                                       | 77     |

| CHAPTER -5 | <b>RECONFIGURATION TECHNIQUES</b>                               | 80     |

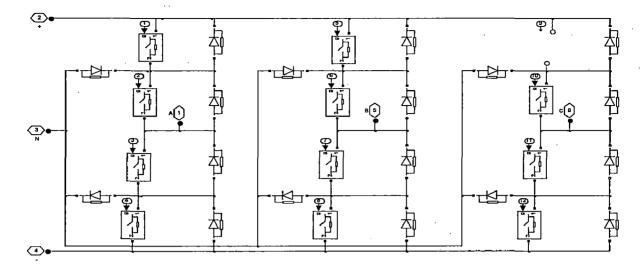

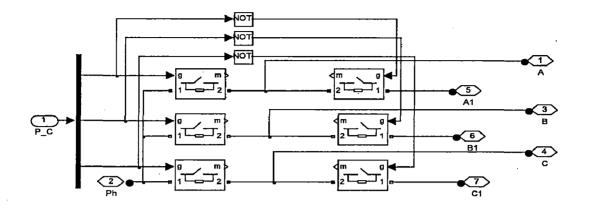

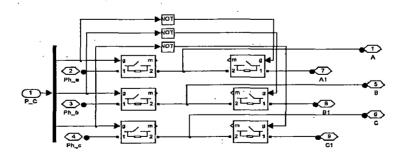

|            | 5.1 Reconfiguration using addition of 1-extra leg               | 82     |

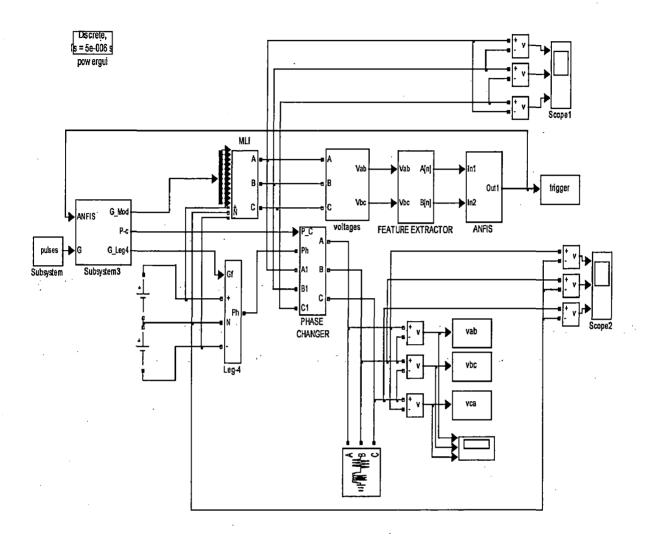

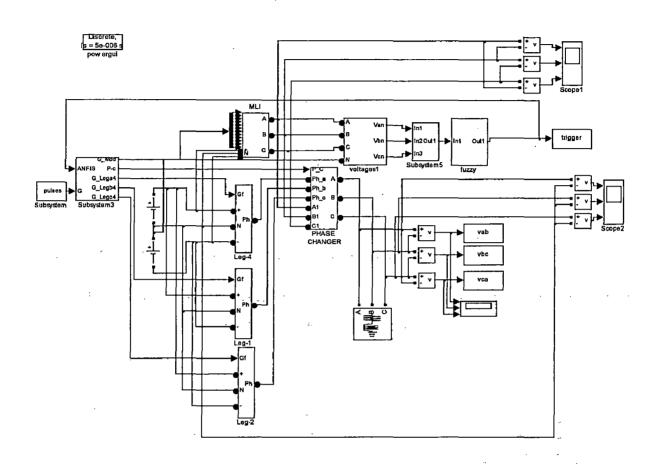

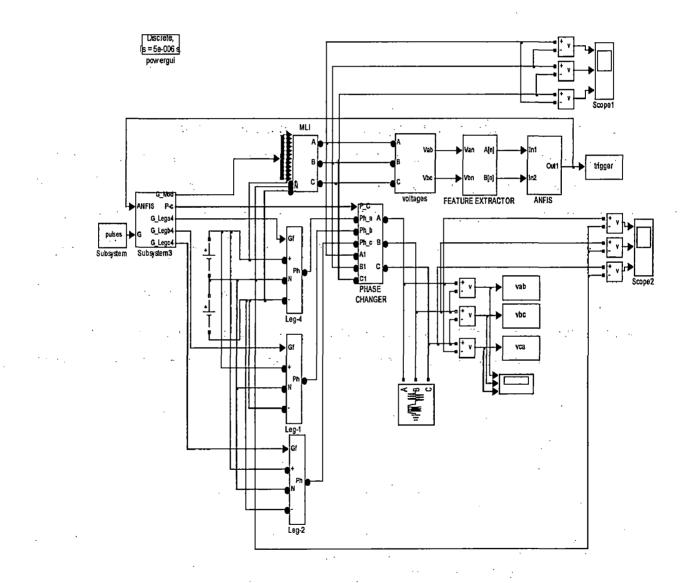

|            | 5.1.1 Fault diagnosis using Fuzzy Inference System              | 84     |

|            | 5.1.2 Fault diagnosis using ANFIS                               | 85     |

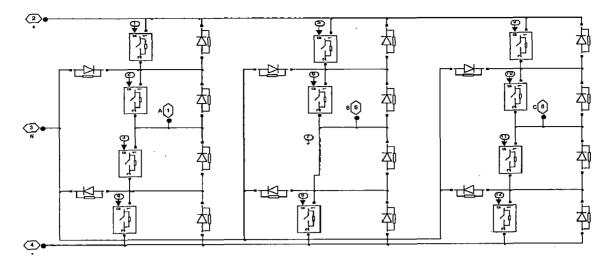

|            | 5.2 Reconfiguration using addition of 3-extra legs              | 85     |

|            | 5.2.1 Fault diagnosis using Fuzzy Inference System              | 86     |

|            | 5.2.2 Fault diagnosis using ANFIS                               | 87     |

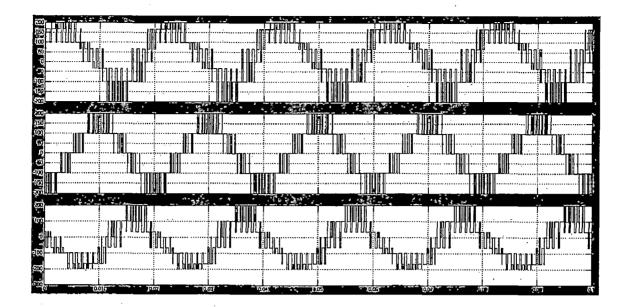

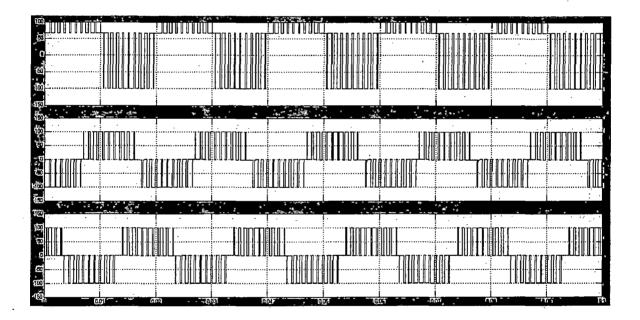

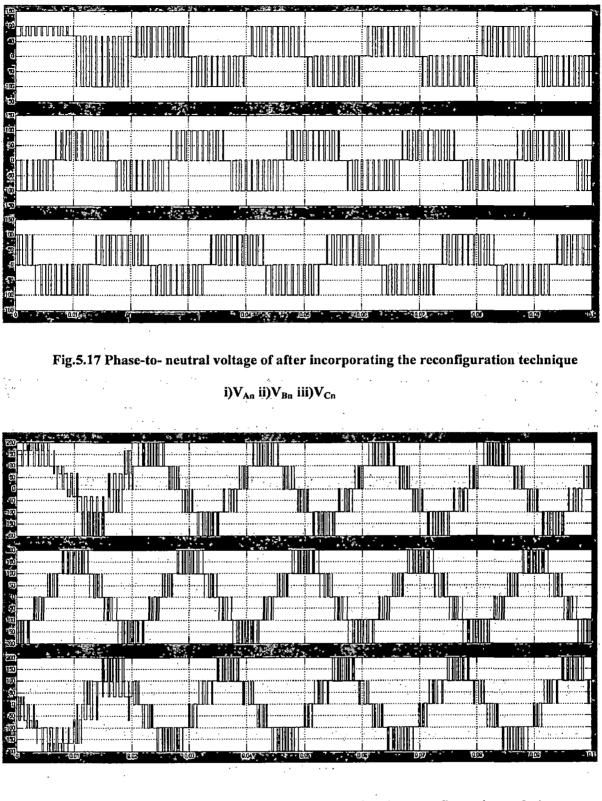

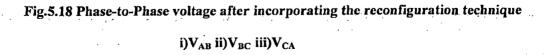

|            | 5.3 Wave Forms Corresponding To Reconfiguration Using           |        |

|            | an Additional Leg                                               | 88     |

|            | 5.3.1 Open IGBT fault of switch-1                               | 88     |

|            | 5.3.2 Short IGBT Fault of Switch-1                              | 90     |

| CHAPTER-6  | <b>CONCLUSION &amp; SCOPE OF THE FUTURE WORK</b>                | 93     |

| REFERENCES |                                                                 | 95     |

|            |                                                                 | ·<br>• |

|            |                                                                 |        |

|            |                                                                 | ÷.     |

|            |                                                                 |        |

|            |                                                                 |        |

|            |                                                                 | :<br>: |

|            |                                                                 |        |

|            |                                                                 |        |

|            |                                                                 |        |

#### **CHAPTER-1**

# INTRODUCTION

In recent years, industry has begun to demand higher power ratings. and multilevel inverter drive (MLID) systems have become a solution for high-power applications. The results of a patent search show that multilevel inverter circuits have been around for more than 25 years. An early traceable patent appeared in 1975, in which the cascade inverter was first defined with a format that connects separately dcsourced full-bridge cells in series to synthesize a staircase ac output voltage. Through manipulation of the cascade inverter, with diodes blocking the sources, the diodeclamped multilevel inverter was then derived. The diode-clamped inverter was also called the neutral-point clamped (NPC) inverter when it was first used in a three-level inverter in which the mid-voltage level was defined as the neutral point. Because the NPC inverter effectively doubles the device voltage level without requiring precise voltage matching, the circuit topology prevailed in the 1980s. The cascade MLID is a general fit for large automotive all-electric drives because of the high Volt-Ampere (VA) rating possible and because it uses several level dc voltage sources which would be available from batteries or fuel cells. Mainly three-phase Pulse Width Modulated (PWM) inverters have been utilized in variety of industrial applications like Uninterrupted Power supply (UPS), electric motor drives and active power filters and so on. Due to environmental pollution and exhaustion of fossil fuel, inverters are being used for renewable energy conversion systems and hybrid vehicles. Various control techniques have been implemented to reduce the harmonics. A multilevel inverter not only achieves high power ratings, but also enables the use of renewable sources [1].

However, different types of unexpected faults are frequent in industrial fields. These inverter faults may influence the operation of whole system. In order to avoid these harmful effects and to improve the reliability the fault detection and diagnosis are very important.

· Second second

ション・キャンション

1.200

and the second second second

المراجع والمراجع

عادأ فحادي أعريها ويرتحا والد

化试验 注意 医内口的

1. A. A. A.

and a second second

1. 1. 1.

× . .

and the second second

Different faults in 3-phase inverters are classified in to

- Single-line-to ground faults of input supply

- Short-circuit faults of diode rectifier

- Earth faults of input supply

- Earth faults on dc-bus

- Short-circuit faults of dc-link capacitors

- Switching device faults

- Line-to-line short circuits at machine terminals

- Single line-to-ground faults at machine terminals, etc.

Our main concentration is on switching device faults which occurs inside the inverters. Switching device faults results in harmonics in the output voltage and currents. In this research, we will attempt to diagnose the fault location in a Multi Level Inverter (MLI) system from its output voltage waveform because the output voltages are normally independent from the load and correspond with fault types and locations. MLI open and short circuit faults at each switch are considered. The proposed Fault diagnostic system utilizes output voltage signals of the MLI systems to detect the fault location in the inverter. The unbalanced voltage and current may result in vital damage because of overheating in the ac load if the ac load is supplied with unbalanced voltages for a long time. The unbalanced condition from fault can be corrected if the fault location is identified.

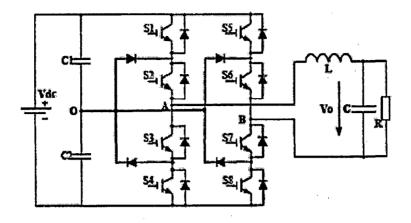

A voltage-fed inverter system, as shown in Fig.1.1, can develop various types of switching device faults that can be classified as follows:

2 6 2 3

1.19.1

- 1) Open-circuit fault of semiconductor device

- 2) Short-circuit fault of semiconductor device

- 3) Two semiconductor device of one leg open-circuit fault

In order to maintain continuous operation for a multilevel inverter system, knowledge of fault behaviors, fault prediction, and fault diagnosis are necessary. So the

most important factor, however, is how the system could operate continuously while there is an abnormal condition.

Fig.1.1. Single-phase multilevel-inverter system.

Faults should be detected and corrected and the faulted part should be isolated as soon as possible after they occur, because if a motor drive runs continuously under abnormal conditions, the drive or motor may quickly fail. Many engineers and researchers have focused on incipient fault detection and preventive maintenance to avert inverter and motor faults [4]-[6].

Research on fault diagnostic techniques initially focused on conventional pulse width modulation (PWM) voltage source inverters (VSI). This integrated system introduced remedial control strategies soon after failure occurrences; therefore system reliability and fault tolerant capability are improved.

Three different methods which are mainly used for in fault detection and diagnosis are model-based techniques, expert systems, and artificial intelligence methods. Model-based techniques are very outstanding if an accurate model of the process can be obtained. But accurate model of the whole Inverter system is difficult to obtain. The inverter model (including Snubber capacitance and power electronic switches) is not only hard to obtain but also inaccurate due to component values, parasitic components, and unavoidable assumptions and limitations. Therefore, methods that do not require model knowledge are of great interest. Expert systems usually

3

dedicated to big systems are useful if minor modifications are made in the process and above all assume the existence of an expert to build the rules and the reasoning tree. The introduction of artificial intelligence methods (fuzzy logic and artificial neural network) will have more flexibility, as there is no need for a model. The accuracy of these methods depends upon the initial training data in healthy and faulty conditions. Nevertheless, this is not a major drawback in this case because reliable simulation tools exist that can furnish appropriate data. A general review of recent developments in the field of AI-based diagnostic systems in machine drives has been proposed in [9].

Thus far, limited research has focused on MLI systems fault diagnosis. Therefore, an MLI fault diagnostic system is discussed in this thesis work that only requires measurement of the MLI's voltage waveforms.

#### **1.1 Problem Description**

A

ĥ,

Because multilevel inverter systems are utilized in high power applications, the reliability of the power electronics is very important. For example industrial applications such as industrial manufacturing are dependent upon induction motors and their inverter systems for process control. Generally, the conventional protection systems are passive device such as fuses, overload relays, and circuit breakers to protect the inverter systems and the induction motors. The protection devices will disconnect the power sources from the multilevel inverter system whenever a fault occurs, stopping the operated process. Downtime of manufacturing equipment can add up to be thousands or hundreds of thousands of dollars per hour, therefore fault detection and diagnosis is vital to a company's bottom line.

The inverter switching devices are normally controlled by isolated base drive amplifiers. Malfunctioning of one of these units can result in a missing base drive, and so device open-circuit fault occurred in the inverter. It may also occur by several reasons such as lifting of bonding wires due to thermal cycling, drive failures, and IGBT breakage due to short-circuit faults, etc. Open-circuit faults might cause the system shutdown depending on the state of system, however the system can also keep operating under the fault since it doesn't always result in the incapability of system operation. But

it may lead to the secondary faults such as thermal defects of the other switches, winding and bearing faults of the motor and so on, by continuous operation without any recovery. Usually, a diagnosis of open-circuit faults of the switching devices is based on the current signal.

The device short-circuit fault is due to reverse breakdown of the device, or may due to insulation breakdown of the leg, or sucking circuit paralleling with the device is short. This type of fault is a serious fault and it may be resulting in fault of other device. Unfortunately it is also a commonly occurring fault. For such a fault, base drive to the healthy IGBT of the same leg should be immediately suppressed in order to prevent a shoot through fault [7]-[24].

A 3-phase MLI system (3-level) using diode-clamped technique is represented in Fig.1.2 is able to generate 3-level staircase form of voltage which is nearly sinusoidal which are displaced by 120° apart. By increasing the number of levels we can reduce the harmonic content present in the output. Due to the great demand of medium-voltage high-power inverters, the inverter has drawn tremendous interest ever since. The field applications include use in laminators, mills, conveyors, pumps, fans, blowers, compressors, and so on [3]-[8].

#### Fig.1.2. 3-phase multilevel-inverter system.

However, the use of inverters has some drawbacks. The introduction of power electronic converters came with an increased possibility of component failures. It is the power electronic stage of the drive, including its dc link and control circuitry, which becomes the system's weakest part in the sense of operational reliability. High costs due to standstill and repair, as well as the general need to improve reliability have led to research in fault detection in inverters. Short circuit detection has become a standard feature of driver ICs. However, much fewer research results have been published on open circuit faults. An open switch fault can lead to over stresses on the healthy switches as well as to pulsating current. In turn this can lead to failures in other components, for example by causing a torque ripple in a drive fed by such inverter [25].

#### **1.2 Organization of the Thesis**

Chapter 1 introduces to the prominence of the inverters and major changes that have been undergone over past 50 years and different causes for faults in inverters. Chapter 2 gives the literature survey I have done on different topologies, inverter applications and controlling techniques from various IEEE papers which I studied for the work. In chapter 3 it gives the general discussion about 3-level inverter and its operation using Sinusoidal Pulse Width Modulation (SPWM) control techniques in order to control the output voltage of the 3-level inverter, the Simulink models designed for three-level inverters with SPWM technique and the results obtained from the simulation of the block models in MATLAB/SIMULINK 7.1 version. Chapter 5 deals with different fault detection methods and its importance and proposed two techniques for detection of fault location. They are Adaptive Neuro Fuzzy Inference Systems which uses Fast Fourier Transform (FFT) analysis and Fuzzy Inference System which uses 3rd harmonic content present in the output voltages. Chapter 5 deals with different reconfiguration techniques. In Chapter 6 concludes the thesis work and scope for future work drawn is drawn. . . . . .

• 6

# A SURVEY OF TOPOLOGIES, CONTROL METHODS, APPLICATIONS AND THEIR SIMULINK MODELS

As the demand for higher power equipment has been increasing rapidly, this may be up to the megawatt level. Controlled ac drives in the megawatt range are usually connected to the medium-voltage network. Today, it is difficult to connect a single power semiconductor switch directly to medium voltage grids (2.3, 3.3, 4.16, or 6.9 kV). Due to these reasons, a new family of multilevel inverters has emerged as the solution for working with higher voltage levels [1].

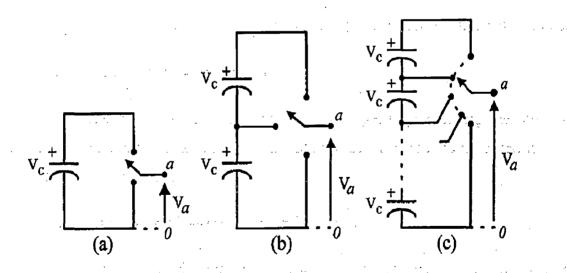

Multilevel inverters include an array of power semiconductors and capacitor voltage sources, the output of which generate voltages with stepped waveforms. The commutation of the switches permits the addition of the capacitor voltages, which reach high voltage at the output, while the power semiconductors must withstand only reduced voltages. Fig.2.1 shows a schematic diagram of one phase leg of inverters with different numbers of levels, for which the action of the power semiconductors is represented by an ideal switch with several positions. A two-level inverter generates an output voltage with two values (levels) with respect to the negative terminal of the capacitor [see Fig. 2.1(a)], while the three-level inverter generates three voltages, and so on. Considering that m is the number of steps of the phase voltage with respect to the negative terminal of the inverter, then the number of steps in the voltage between two phases of the load k is

#### k=2m+1

And the number of steps in the phase voltage of a three-phase load in Y connection is

#### p=2k-1

By increasing the number of levels in the inverter, the output voltages have more steps generating a staircase waveform, which has a reduced harmonic distortion. However, a high number of levels increases the control complexity and introduces

7

· · · · · · · ·

voltage imbalance problems [1]. Three different topologies for multilevel inverters are diode-clamped (neutral-clamped), capacitor- clamped (flying capacitors) and cascaded Multicell with separate dc sources [16].

The most attractive features of multilevel inverters are as follows.

- They can generate output voltages with extremely low distortion and lower dv/dt.

- They draw input current with very low distortion.

- They generate smaller common-mode (CM) voltage, thus reducing the stress in the motor bearings. In addition, using sophisticated modulation methods, CM voltages can be eliminated.

- They can operate with a lower switching frequency.

This dissertation work presents state of the art multilevel technology, considering well-established and emerging topologies as well as their modulation and control techniques. Special attention is dedicated to the latest and more relevant industrial applications of these converters.

From Fig. 2.1(a) as there is only one charging capacitor which acts as dc source, the output will be a single level. As the number of charging capacitors increases there

will be a proportionate increment in switches this in turn produce a multi level output. If there are 'n' numbers of switches, the output stages will be of 2n+1[1].

### 2.1 Inverter Topologies

#### 2.1.1 Diode-Clamped Inverter

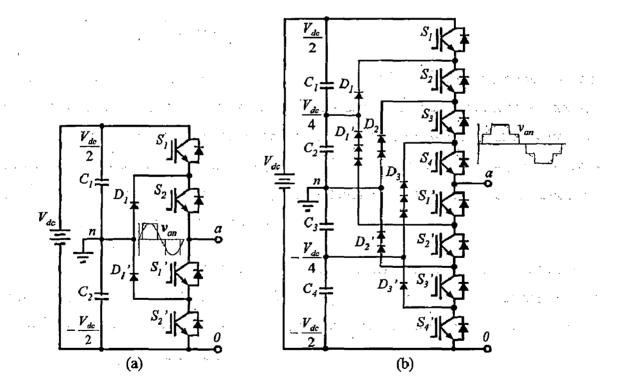

A three-level diode-clamped inverter is shown in Fig. 2(a). In this circuit, the dcbus voltage is split into three levels by two series-connected bulk capacitors,  $C_1$  and  $C_2$ . The middle point of the two capacitors 'n' can be defined as the neutral point. The output voltage  $V_{an}$  has three states:  $V_{dc}/2$ , 0,  $-V_{dc}/2$ . For voltage level  $V_{dc}/2$ , switches  $S_1$  and  $S_2$  need to be turned on; for  $-V_{dc}/2$ , switches  $S_1$ ' and  $S_2$ ' need to be turned on; and for the 0 level,  $S_2$  and  $S_1$ ' need to be turned on.

The key components that distinguish this circuit from a conventional two-level inverter are  $D_1$  and  $D_1$ '. These two diodes clamp the switch voltage to half the level of the dc-bus voltage. When both  $S_1$  and  $S_2$  turned on, the voltage across 'a' and '0' is  $V_{dc}$  i.e., in this case,  $D_1$ ' balances out

Fig.2.2. Diode-clamped multilevel inverter circuit topologies. (a) Three-level. (b) Five-level.

The voltage sharing between  $S_1$ 'and  $S_2$ 'with  $S_1$ 'blocking the voltage across  $C_1$  and  $S_2$ ' blocking the voltage across  $C_2$ . Notice that output voltage  $V_{an}$  is ac, and  $V_{a0}$  is dc. The difference between  $V_{an}$  and  $V_{a0}$  is the voltage across  $C_2$ , which is  $V_{dc}/2$ . If the output is removed out between 'a' and '0', then the circuit becomes a dc/dc converter, which has three output voltage levels:  $V_{dc}$ ,  $V_{dc}/2$ , and 0.

Fig.2.2(b) shows a five-level diode-clamped converter in which the dc bus consists of four capacitors,  $C_1$ ,  $C_2$ ,  $C_3$ , and  $C_4$ . For dc-bus voltage  $V_{dc}$ , the voltage across each capacitor is  $V_{dc}/4$ , and each device voltage stress will be limited to one capacitor voltage level  $V_{dc}/4$  through clamping diodes. To explain how the staircase voltage is synthesized, the neutral point n is considered as the output phase voltage reference point. There are five switch combinations to synthesize five level voltages across a and n.

For voltage level  $V_{an}=V_{dc}/2$ , turn on all upper switches  $S_1-S_4$ .

For voltage level  $V_{an}=V_{dc}/4$ , turn on three upper switches  $S_2-S_4$ , one lower switch  $S_1$ '. For voltage level  $V_{an}=0$ , turn on two upper switches  $S_3-S_4$ , two lower switches  $S_1'-S_2'$ . For voltage level  $V_{an}=-V_{dc}/4$ , turn on one upper switch  $S_4$ , three lower switches  $S_1-S_3'$ . For voltage level  $V_{an}=-V_{dc}/2$ , turn on all lower switches  $S_1'-S_4'$ .

Four complementary switch pairs exist in each phase. The complementary switch pair is defined such that turning on one of the switches will exclude the other from being turned on. In this example, the four complementary pairs are  $(S_1, S_1^2)$ ,  $(S_2, S_2^2)$ ,  $(S_3, S_3^2)$ , and  $(S_4, S_4^2)$  although each active switching device is only required to block a voltage level of  $V_{dc}/(m-1)$ , the clamping diodes must have different voltage ratings for reverse voltage blocking. Using D<sub>1</sub>'of Fig.2.2(b) as an example, when lower devices  $S_2^2$ - $S_4^2$  are turned on, D<sub>1</sub>'needs to block three capacitor voltages, or  $3V_{dc}/4$ . Similarly, D<sub>2</sub> and D<sub>2</sub>' need to block  $2V_{dc}/4$ , and D3 needs to block  $3V_{dc}/4$ . Assuming that each blocking diode voltage rating is the same as the active device voltage rating, the number of diodes required for each phase will be  $(m-1)^*(m-2)$ .

. . .

This number represents a quadratic increase in m. When m is sufficiently high, the number of diodes required will make the system impractical to implement. If the inverter runs under PWM, the diode reverse recovery of these clamping diodes becomes the major design challenge in high-voltage high-power applications [1]-[2].

#### 2.1.2. Capacitor-Clamped Inverter

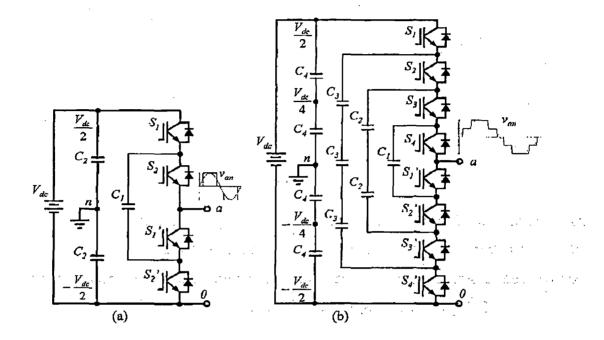

Fig.2.3. Capacitor-clamped multilevel inverter circuit topologies. (a)Three-level (b) Five-level

Fig. 2.3 illustrates the fundamental building block of a phase-leg capacitorclamped inverter. The circuit has been called the flying capacitor inverter with independent capacitors clamping the device voltage to one capacitor voltage level. The inverter in Fig.2.3(a) provides a three-level output across 'a' and 'n', i.e.,  $V_{an}=V_{dc}/2$ , 0, or  $-V_{dc}/2$ . For voltage level  $V_{dc}/2$ , switches S<sub>1</sub> and S<sub>2</sub> need to be turned on; for  $-V_{dc}/2$ , switches S<sub>1</sub>'and S<sub>2</sub>' need to be turned on; and for the 0 level, either pair (S<sub>1</sub>, S<sub>1</sub>') or (S<sub>2</sub>, S<sub>2</sub>') needs to be turned on. Clamping capacitor C<sub>1</sub> is charged when S<sub>1</sub> and S<sub>1</sub>'are turned on, and is discharged when S<sub>2</sub> and S<sub>2</sub>' are turned on. The charge of C<sub>1</sub> can be balanced by proper selection of the 0-level switch combination.

The voltage synthesis in a five-level capacitor-clamped converter has more flexibility than a diode-clamped converter. Using Fig. 2.3(b) as the example, the voltage

of the five-level phase-leg output with respect to the neutral point n,  $V_{an}$ , can be synthesized by the following switch combinations [1]-[2].

- 1) For voltage level Van= $V_{do}/2$ , turn on all upper switches  $S_1-S_4$ .

- 2) For voltage level  $V_{an}=V_{dc}/4$ , there are three combinations:

$$S_1, S_2, S_3, S_1'$$

( $V_{an} = V_{dc}/2$  of upper  $C_4$ 's  $-V_{dc}/4$  of  $C_1$ );

- $S_2$ ,  $S_3$ ,  $S_4$ ,  $S_4$ ' ( $V_{an}=3V_{dc}/4$  of  $C_3$ 's  $-V_{dc}/2$  of lower  $C_4$ 's); and

- $S_1$ ,  $S_3$ ,  $S_4$ ,  $S_3$ ' ( $V_{an} = V_{dc}/2$  of upper C<sub>4</sub>'s -3 $V_{dc}/4$  of C<sub>3</sub>'s + $V_{dc}/2$  of C<sub>2</sub>'s).

- 3) For voltage level  $V_{an}=0$ , there are six combinations:

$$S_1, S_2, S_1', S_2' (V_{an} = V_{dc}/2 \text{ of upper } C_4's - V_{dc}/2 \text{ of } C_2's);$$

$S_3, S_4, S_3', S_4' (V_{an} = V_{dc}/2 \text{ of } C_2 - V_{dc}/2 \text{ of lower } C_4);$

$$S_1$$

,  $S_3$ ,  $S_1$ ',  $S_3$ ' ( $V_{an} = V_{dc}/2$  of upper  $C_4$ 's  $-3V_{dc}/4$  of  $C_3$ 's  $V_{dc}/2$  of  $C_2$ 's  $-V_{dc}/4$  of  $C_1$ );

$$S_1$$

,  $S_4$ ,  $S_2$ ',  $S_3$ ' ( $V_{an} = V_{dc}/2$  of upper  $C_4$ 's  $-3V_{dc}/4$  of  $C_3$ 's  $+V_{dc}/4$  of  $C_1$ );

S<sub>2</sub>, S<sub>4</sub>, S<sub>2</sub>', S<sub>4</sub>'( $V_{an}$ =3V<sub>dc</sub>/4 of C<sub>3</sub>'s -V<sub>dc</sub>/2 of C<sub>2</sub>'s +V<sub>dc</sub>/4 of C<sub>1</sub> -V<sub>dc</sub>/2 of lower C<sub>4</sub>'s); S<sub>2</sub>, S<sub>3</sub>, S<sub>1</sub>', S<sub>4</sub>'( $V_{an}$ =3V<sub>dc</sub>/4 of C<sub>3</sub>'s of -V<sub>dc</sub>/4 of C<sub>1</sub> -V<sub>dc</sub>/2 of lower C<sub>4</sub>'s).

4) For voltage level  $V_{an} = -V_{dc}/4$ , there are three combinations:

$$S_1, S_1', S_2', S_3'(V_{an} = V_{dc}/2 \text{ of upper } C_4's - 3V_{dc}/4 \text{ of } C_3's);$$

$S_4, S_2', S_3', S_4' (V_{an} = V_{dc}/4 \text{ of } C_1 - V_{dc}/2 \text{ of lower } C_4's);$  and

$S_3, S_1', S_3', S_4'(V_{an}=V_{dc}/2 \text{ of } C_2's - V_{dc}/4 \text{ of } C_1 - V_{dc}/2 \text{ of lower } C_4's).$

5) For voltage level  $V_{an}$  = - $V_{dc}/2$ , turn on all lower switches,  $S_1$ ' -  $S_4$ '.

In the preceding description, the capacitors with positive signs are in discharging mode, while those with negative sign are in charging mode. By proper selection of

capacitor combinations, it is possible to balance the capacitor charge. Similar to diode clamping, the capacitor clamping requires a large number of bulk capacitors to clamp the voltage. Provided that the voltage rating of each capacitor used is the same as that of the main power switch, an m-level converter will require a total of (m-1)\*(m-2)/2 clamping capacitors per phase leg in addition to (m-1) main dc-bus capacitors.

#### 2.1.3. Cascaded Multilevel Inverters

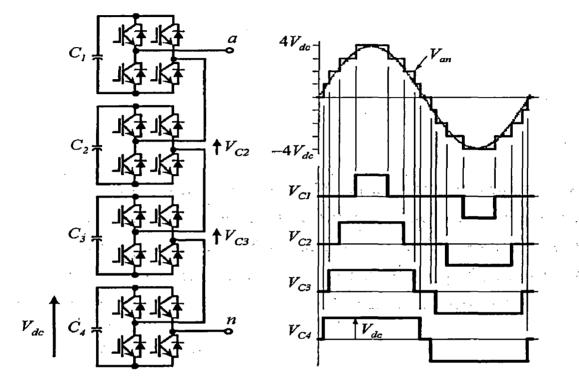

Fig.2.4. Cascaded inverter circuit topology and its associated waveform

A different converter topology is introduced here, which is based on the series connection of single-phase inverters with separate dc sources. Fig.2.4 shows the power circuit for one phase leg of a nine-level inverter with four cells in each phase. The resulting phase voltage is synthesized by the addition of the voltages generated by the different cells. Each single-phase full-bridge inverter generates three voltages at the output:  $+V_{dc}$ , 0, and  $-V_{dc}$ . This is made possible by connecting the capacitors sequentially to the ac side via the four power switches. The resulting output ac voltage swings from  $4V_{dc}$  to  $-4V_{dc}$  with nine levels, and the staircase waveform is nearly sinusoidal, even without filtering [1]-[2]-[3].

#### 2.2 Control Methods for Inverter

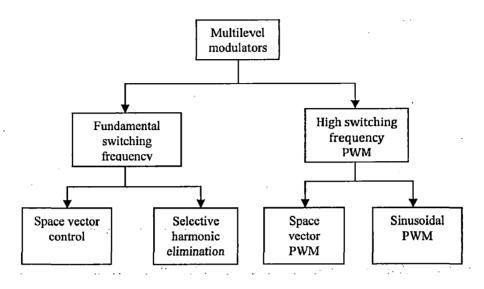

Different modulation methods used in multilevel inverters can be classified according to switching frequency is shown in Fig.2.5. Methods that work with high switching frequencies have many commutations for the power semiconductors in one period of the fundamental output voltage.

Fig.2.5. Classification of multilevel modulation methods.

A very popular method in industrial applications is the classic carrier-based Sinusoidal Pulse Width Modulation (SPWM) that uses the phase shifting technique to reduce the harmonics in the load voltage. Another interesting alternative is the Space Vector Pulse Width Modulation (SVM) strategy, which has been used in three-level inverters. Methods that work with low switching frequencies generally perform one or two commutations of the power semiconductors during one cycle of the output voltages, generating a staircase waveform. Selective harmonic elimination and the space-vector control (SVC) are the different modulation techniques in this family [1].

#### 2.2.1 Need for the Control of the Inverter

In many industrial applications, it is often required to vary the output voltage of the inverter due to the following reasons:

14

• To compensate for the variations in the input voltage.

- To compensate for the regulation of the inverters.

- To supply some special loads which need variation of voltage with frequency, such as an induction motor.

The inverter output voltage can be controlled by various techniques. Here we use SINE-PWM technique for control of the inverter.

### 2.2.2 Sinusoidal Pulse Width Modulation

Pulse width modulation (PWM) techniques are effective means to control the output voltage frequency and magnitude. It has been the subject of intensive research during the last few decades. Here we mainly consider the carrier based PWM approaches that are often applied to the single phase applications [15].

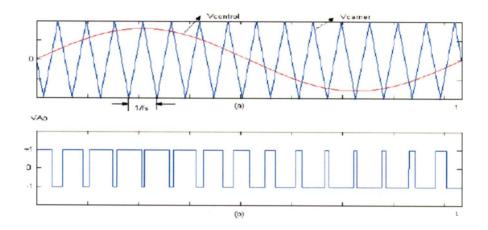

Fig.2.6. a Reference and carrier wave b.Pulses generated on comparison

Fig.2.6 is a general scheme of PWM modulation. In order to produce a sinusoidal voltage at desired frequency, say  $f_1$ , a sinusoidal control signal  $V_{control}$  at the desired frequency ( $f_1$ ) is compared with a triangular waveform  $V_{carrier}$  as shown in Fig.2.7, at each compare match point, a transition in PWM waveform is generated as shown in Fig.2.7. When  $V_{control}$  is greater than  $V_{carrier}$ , the PWM output is positive and When  $V_{control}$  is smaller than  $V_{carrier}$ , the PWM waveform is negative. The frequency of triangle waveform  $V_{carrier}$  establishes the inverter's switching frequency  $f_s$ . We define the modulation index  $m_i$  as follows:

$$m_i = \frac{V_{control}}{V_{tri}}$$

Where  $V_{control}$  is the peak amplitude of the control signal, while  $V_{tri}$  is the peak amplitude of the triangle signal (carrier), the frequency modulation ratio is defined as

$$m_f = \frac{f_s}{f_1}$$

$m_f$  is the ratio between the carrier and control frequency. The fundamental component  $(V_{out})_1$  of the H bridge output voltage  $(V_{out})_1$  has the property as depicted in equation below in a linear modulation region:

$$(\mathbf{V}_{out})_{1} = \mathbf{m}_{i} * \mathbf{V}_{d}$$

$$m_{i} < 1.0$$

This equation shows an interesting result that the amplitude of the fundamental component of the output voltage varies linearly with the modulation index. The m<sub>i</sub> value from zero to one is defined as the linear control range of sinusoidal carrier PWM.

Fig.2.7. a. shows the comparison of carrier with sine wave b. shows pulses generated for positive device c. pulses for negative device d. obtained output wave for one-cycle

# THREE LEVEL INVERTERS

#### **3.1 General Discussion**

As we know that the output obtained from a two-level inverter is not a pure sinusoidal waveform. It is due to the presence of harmonics in the inverter output voltage which may cause heavy losses and may lead to low efficiency of the induction motors or any other applications which may take the supply from the inverter. So, there is a need for us to reduce these harmonics [8]-[13].

The harmonics in a two level inverter is reduced by increasing the switching frequency. But the switching frequency is restricted by the switching losses in high power applications. In such applications multilevel inverters have been widely used in recent years for the advantage of low harmonic output at low switching frequency. At the same time low blocking in the switching devices can be achieved. The more the number of levels of the output voltage the lesser will be the harmonic content. Multi level inverters have advantages of good power quality, good electromagnetic compatibility, low switching losses, high voltage capability. Because of these reasons the multi level inverters are used in the active rectifiers and the FACTS applications [2].

The multi level inverters synthesize several voltage levels from the various levels of the DC input. A near sinusoidal voltage waveform can be generated from the various levels of the DC input. They have become attractive in the high power and high voltage applications. By using the multilevel inverters the stress on each device is reduced proportional to the number of the output levels present [2]. With several levels in the output waveform the switching dv/dt stresses are reduced, and hence the lifetime of motor and cables are increased. By using a multilevel inverter the power rating of the equipment can be enhanced without any dangerous consequences [18].

and the second state in the second state of the se

• • •

17 17

and the second second

and the second second second second

and the second second

and the second second

Sec. Sta

este se tu

### **3.2 Three-Level Inverter**

The three-level implementation is based on the digital implementation of the diode-clamped three-phase three-level SPWM control based inverter. It is well known that multilevel inverter have been receiving more and more attention for high-voltage and high power applications. Numbers of topologies and modulation strategies have been investigated for utility and drive applications recent years.

Multi-level inverters are suitable in high-voltage and high power applications due to their ability to synthesize waveforms with better harmonic spectrum and attain higher voltages with a limited maximum device rating. Based on the analysis of the diode-clamped three-level inverter topology, this chapter presents SPWM modulation strategy to reduce switching loss.

# **3.2.1 Operation of Three-Phase 3-Level Inverter**

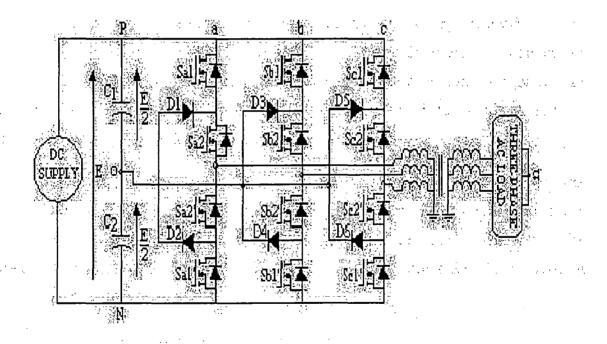

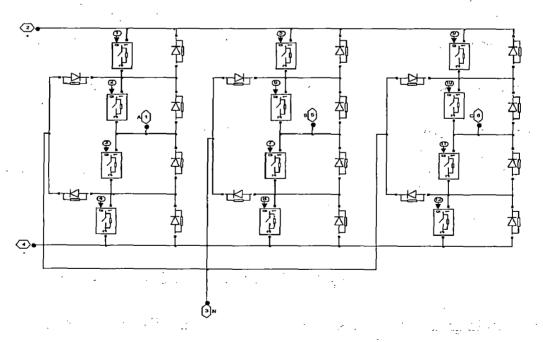

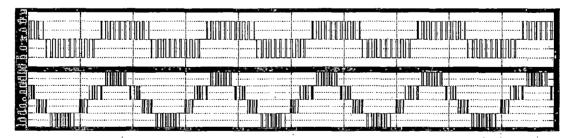

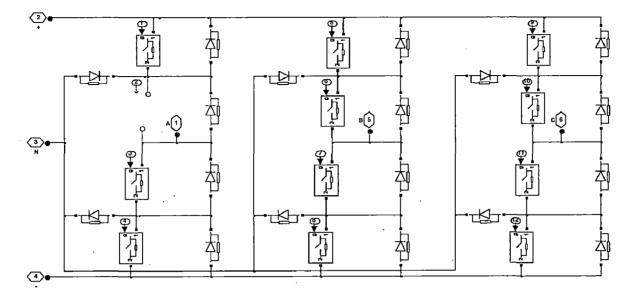

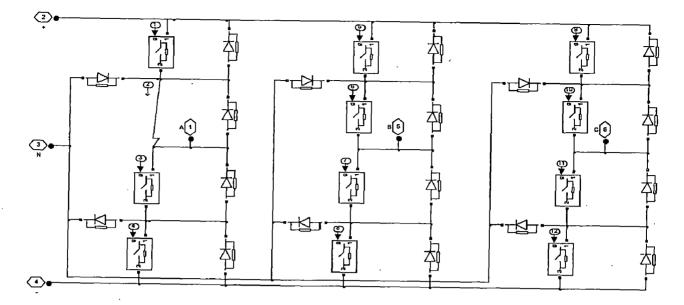

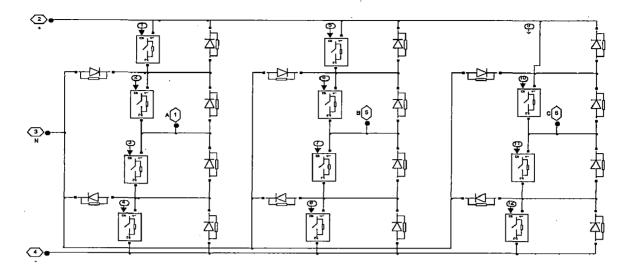

Fig.3.1. Power Circuit for Three-Phase Three-Level Inverter

The Fig.3.1 shown above gives the basic circuit for the 3-phase three-level diode clamped inverter. The circuit employs 12 power switching devices  $(S_{a1}-S_{a4})$  and 6 clamped diodes  $(D_1-D_6)$ . And the dc-bus voltage is split into three-level by two series-connected bulk capacitors can be defined as the neutral point 0. as the result of the

diode-clamped the dc-bus voltage  $V_{dc}/2$ . Thus, the voltage stress of the switching device is greatly reduced. The output voltage  $V_{a0}$  has three different states:  $+V_{dc}/2$ , 0,  $-V_{dc}/2$ .

Here take phase-A as an example for voltage. For voltage  $-V_{dc}/2$ ,  $S_{a3}$  and  $S_{a4}$ need to be turned on. We can define these states as 2, 1, and 0, respectively. Then, the switching variable S<sub>a</sub> is shown in table 3.1. be similar to three-phase two-level inverter, the switching states of each bridge leg of three-phase three-level inverter is described by using switching variables S<sub>a</sub>, S<sub>b</sub> and S<sub>c</sub>. Whereas the difference is that, in three-level inverter, each bridge leg has three different switching states [4]- [11].

· · · · · · · · · · ·

# Table 3.1 Switching Variable of Phase A

|   | V <sub>ao</sub>     | S <sub>a1</sub> | S <sub>a2</sub> | S <sub>a3</sub> | S <sub>a4</sub> | $\mathbf{S}_{\mathbf{a}}$ | 8 |

|---|---------------------|-----------------|-----------------|-----------------|-----------------|---------------------------|---|

|   | +V <sub>dc</sub> /2 | ON              | ON              | OFF             | OFF             | 2                         |   |

|   | 0                   | OFF             | ON              | ON              | OFF             | 1                         |   |

| - | -V <sub>dc</sub> /2 | OFF             | OFF             | ON              | ON: The P       | 0                         |   |

Using switching variable Sa and dc-bus voltage Vdc, the output phase voltage V<sub>ao</sub> is obtained as follows:

· . . . ·

$$V_{an} = (S_a - 1) V_{dc}/2$$

2 × 10 2 1 × 1

:

And the output line voltage of phase A and B can be expressed as follows:

$$V_{ab} = V_{ao} - V_{bo} = 1/2 * V_{dc} (S_a - S_b)$$

#### 3.3 Sinusoidal PWM for A Three-Level Inverter

If the fundamental output voltage and corresponding power level of the PWM inverter are to be increased to a high value, the dc link voltage  $V_{dc}$  must be increased and the devices must be connected in series. By using matched devices in series, static voltage sharing may be somewhat easy, but dynamic voltage sharing during switching is always difficult. The problem may be solved by using a multi-level inverter or neutral point clamped (NPC), inverter. In this thesis work we mainly confined to the three-level inverter.

As shown in Fig.3.1 three-level, three-phase inverter using MOSFET devices. In the Fig.3.1, the dc link capacitor C has been split to create the neutral point '0'. Since the operation of all the phase groups is essentially identical, consider only the operation of the half-bridge for phase A. A pair of devices with bypass diodes is connected in series with an additional diode connected between the neutral point and the center of the pair as shown. The devices  $S_{a1}$  and  $S_{a2}$  function as main devices(like a two-level inverter), the  $S_{a2}$  and  $S_{a3}$  function as auxiliary devices which help to clamp the output potential to the neutral point with the help of clamping diodes  $D_1$  and  $D_2$ .

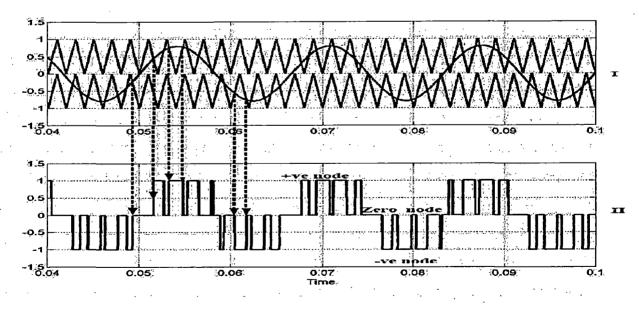

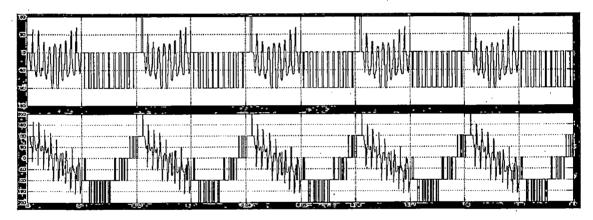

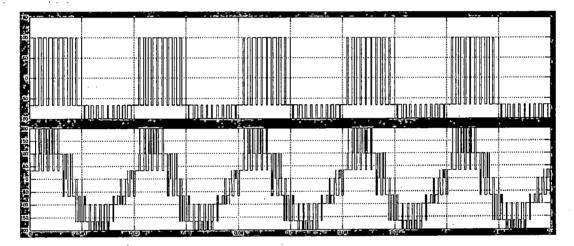

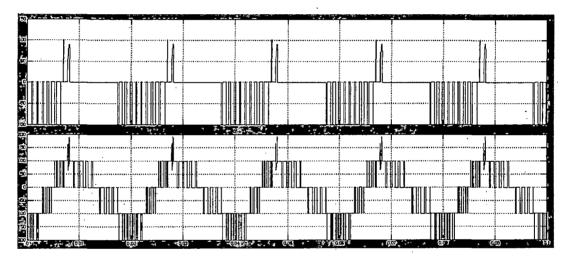

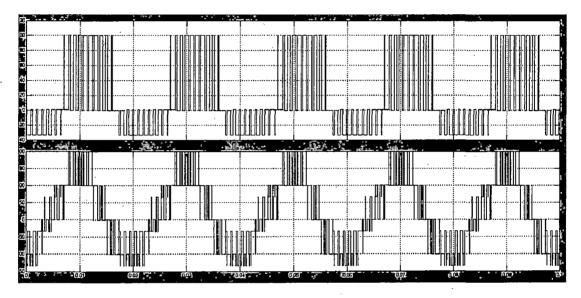

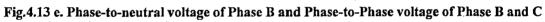

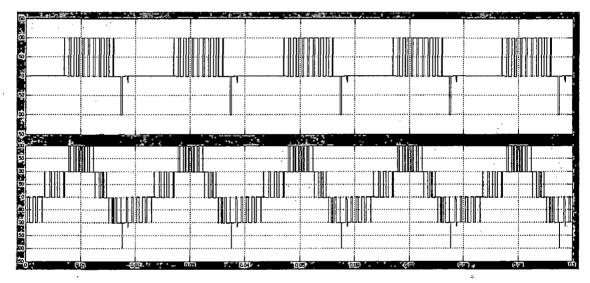

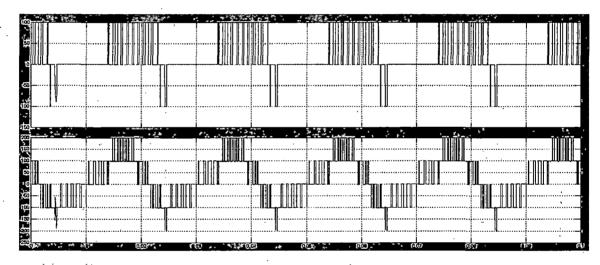

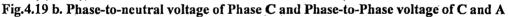

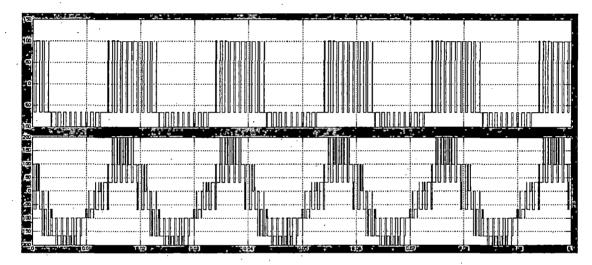

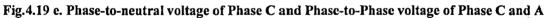

All the PWM techniques can be applied to this inverter. The main devices ( $S_{a1}$  and  $S_{a4}$ ) generate the  $V_{a0}$  wave, whereas the auxiliary devices ( $S_{a3}$  and  $S_{a2}$ ) are driven complementary to the respective main devices. With such control, each output potential is clamped to the neutral potential in the off periods of the PWM control. Evidently, the positive phase current  $+i_a$  will be carried by devices  $D_1$  and  $S_{a2}$  at the neutral clamping condition. On the other hand, negative phase current  $-i_a$  will be carried by  $D_1$  and  $D_2$  when  $V_{a0}$  is positive, by  $S_{a3}$  and Sa4 when  $V_{a0}$  is negative, and by  $S_{a3}$  and diode at the neutral clamping condition. This operation mode gives three voltage levels ( $+0.5V_{dc}$ , 0, and  $-0.5V_{dc}$ ) at the  $V_{a0}$  wave as shown in the Fig.3.2 of phase voltage below. Likewise the wave forms for all the other phases are generated and the resultant Phase-to-Phase

voltages are obtained.

. ROORKEE

#### **Sinusoidal PWM:**

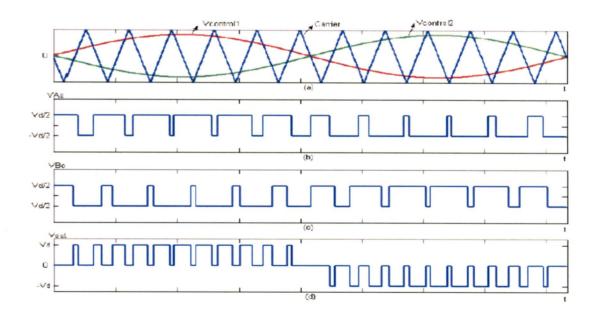

The implementation of a three-level inverter by sine-PWM is carried out using two carrier waves. They are compared with the single sinusoidal wave and corresponding pulses are generated which are to be supplied to the inverter gate devices. And for the other phases the sinusoidal wave is displaced by an angle  $2\Pi/3$  and  $4\Pi/3$ . Let us see an example for a single leg of a three-level inverter bridge.

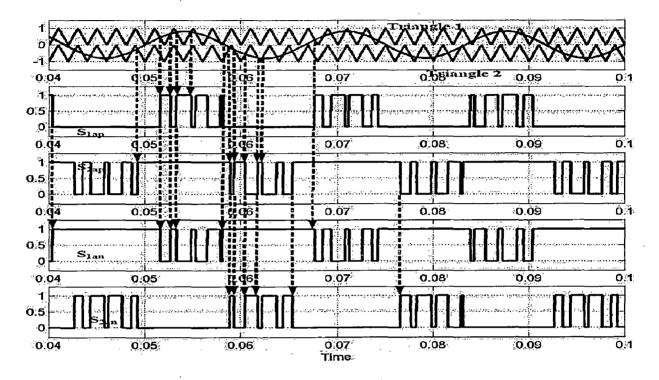

The sinusoidal with frequency  $f_o$  is taken and two carrier waves, i.e., a carrier wave which is starting at 0 time period and the other carrier wave is a negative going one and is the negative going carrier wave with frequency  $f_s$  i.e., switching frequency. The magnitude of the carrier wave is always greater than the reference wave. The positive going carrier wave generates the pulses for the devices by which the inverter phase generate a positive voltage. The negative going carrier wave generates the pulses for the inverter which in turn give the negative phase voltage in a particular leg. The above procedure can be shown for a single phase of one leg in the Fig.3.2. From the above procedure we can obtain the pulses for the two devices of a single leg but totally we want four set of pulses for a single leg in order to generate the required output wave form. The other two set of pulses are generated by taking the negation of the above obtained two set of pulses as shown in Fig.3.3 [1]-[15].

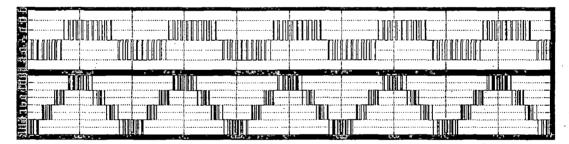

Fig 3.2 Sine-PWM switching patterns for single-phase of three-level inverter

Following conditions are fulfilled in order to generate the pulses for the inverter legs:

Sinusoidal > carrier 1 then the pulse will be1 else 0

Sinusoidal < carrier 2 then the pulse will be 1 else 0

Fig.3.3. Sine-PWM switching pattern for three-level inverter

Similarly the same logic is employed to the other two legs but with a phase displacements of  $2\Pi/3$  and  $4\Pi/3$  for sinusoidal reference wave for other two legs for the two-phase B and C respectively.

#### **3.4 Simulation and Analysis**

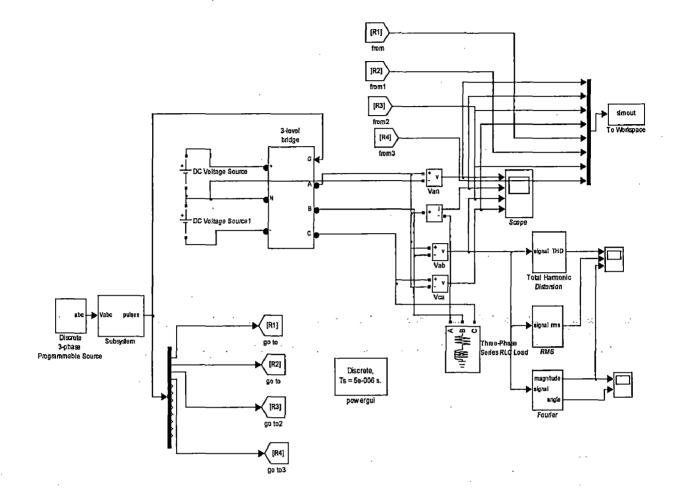

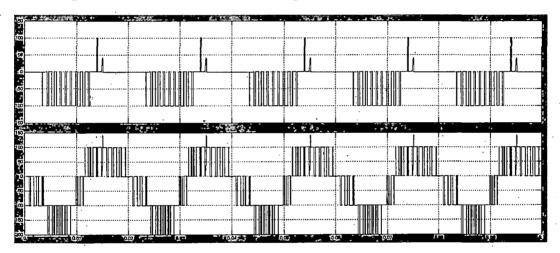

# 3.4.1 Simulink block for Three Level Inverter with sinusoidal PWM

The model given in Fig.3.4 gives the three-level inverter with the sinusoidal PWM as the control technique. The input DC voltage is split into two halves and given to a three-level bridge which is built by three-arms and 12 power devices in total. Each leg has four power devices and diodes are connected in parallel with these power devices. IGBTs are taken as the power devices. The block properties of the three-level bridge can be modified by double clicking on the block. The ABC is taken as the output

terminals. The output is measured across a three-phase load whose specifications are given below. The load current and the load voltage are taken as the output in a scope.

Fig.3.4. Simulink Model for Three-Phase Three-Level Inverter

# **MODEL PARAMETERS:**

| Input DC voltage    | : 200V                              | • .  |        | · · · · |  |

|---------------------|-------------------------------------|------|--------|---------|--|

| Load                | : resistance= 10hm; Inductance= 0.0 | )01H |        |         |  |

| Output frequency    | : 50Hz                              |      | •<br>• |         |  |

| Output peak voltage | : 400V                              |      |        | -<br>X  |  |

|                     |                                     |      |        |         |  |

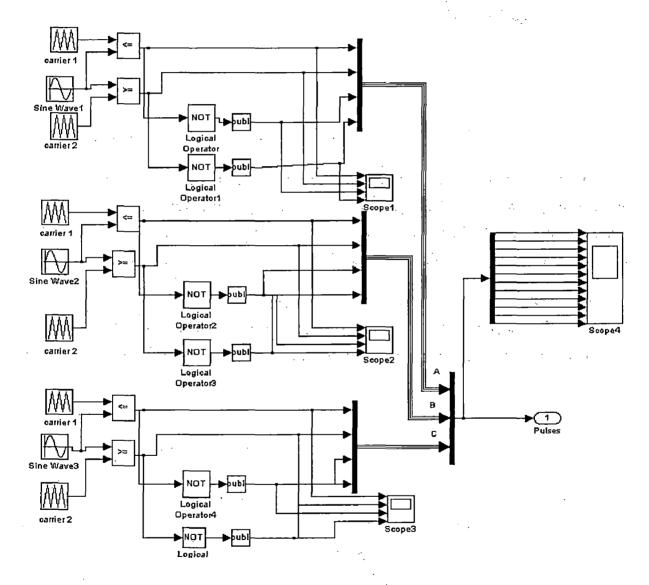

#### 3.4.2 Sinusoidal PWM Control Block

The Fig.3.5 shown below gives the control block of the sine-PWM for the three-level inverter. A positive going carrier-1 and a negative going carrier-2 are generated and are compared with the sinusoidal wave form and the pulses are obtained. The sinusoidal and the carrier waves are generated by the repeating signal block in the SIMULINK browser.

The repeating signal is found in the SIMULINK/SOURCES/REPEATING SEQUENCE. The sine wave form can be obtained from the SIMULINK/SOURCES/SINE-WAVE block. The properties of the blocks can be changed by double clicking on the block.

# Table 3.2 PARAMETERS:

| Carrier 1                  | l:                                               | Carrier 2:     |                                         |  |

|----------------------------|--------------------------------------------------|----------------|-----------------------------------------|--|

| Frequency : 1000Hz         | Frequency : 1000Hz initial value $\rightarrow 0$ |                | : 1000Hz initial value $\rightarrow$ -1 |  |

| Magnitude                  | : IV                                             | Magnitude : 1V |                                         |  |

| Sine 1 :                   | Sine 2 :                                         |                | Sine 3 :                                |  |

| Frequency = 50Hz,          | Frequency = 50Hz,                                |                | Frequency = 50Hz,                       |  |

| Magnitude = 0.9V Magnitude |                                                  | = 0.9V         | Magnitude = 0.9V                        |  |

| Phase = 0 Phase            |                                                  | = 2π/3         | Phase $= 4\pi/3$                        |  |

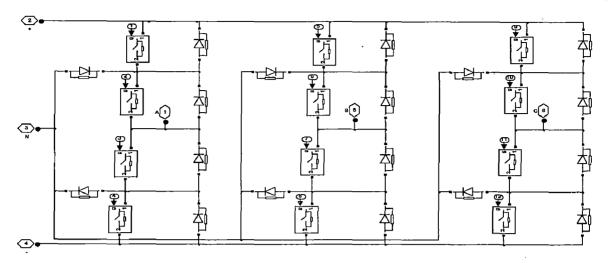

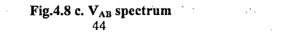

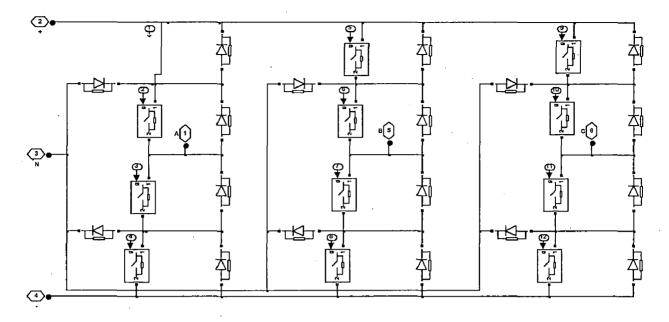

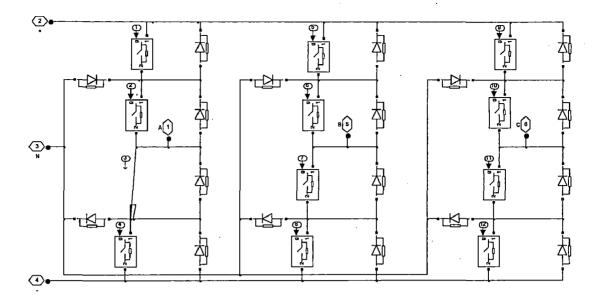

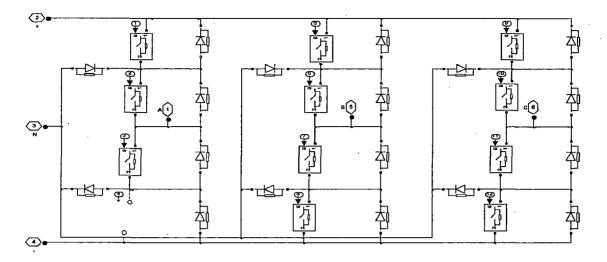

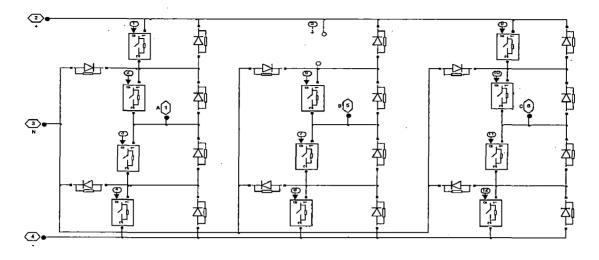

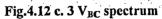

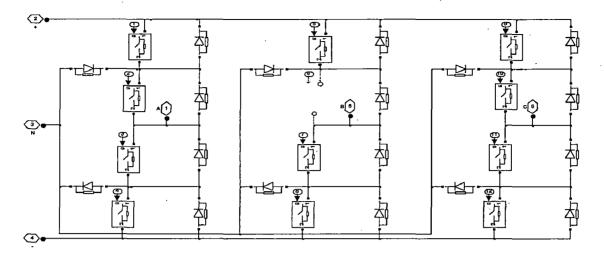

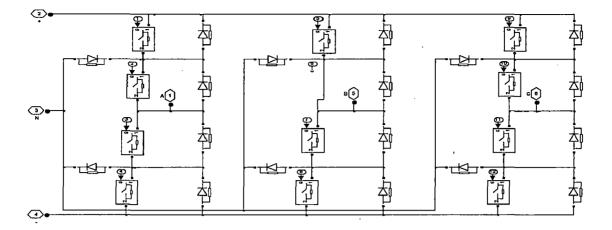

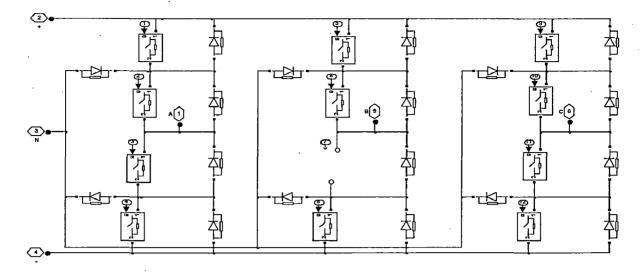

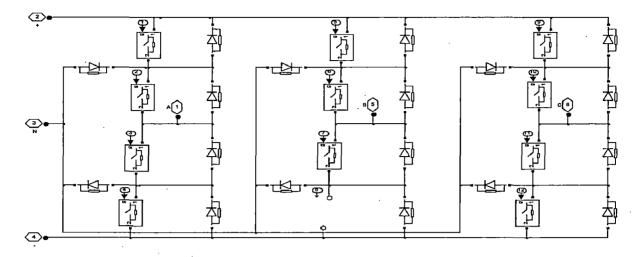

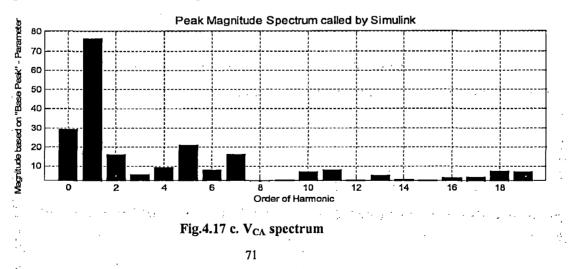

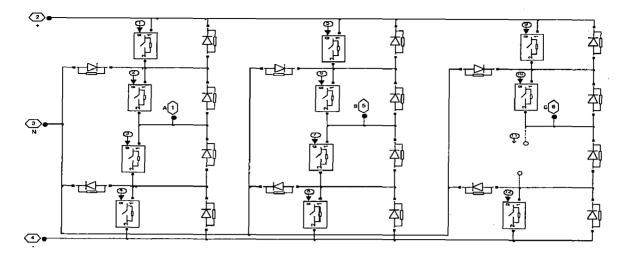

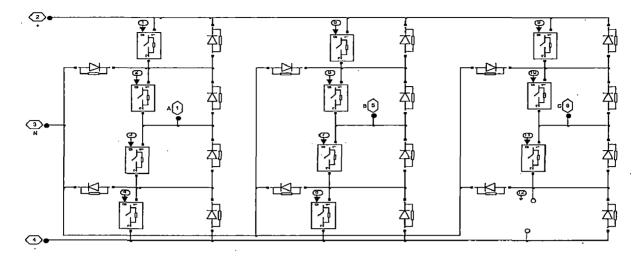

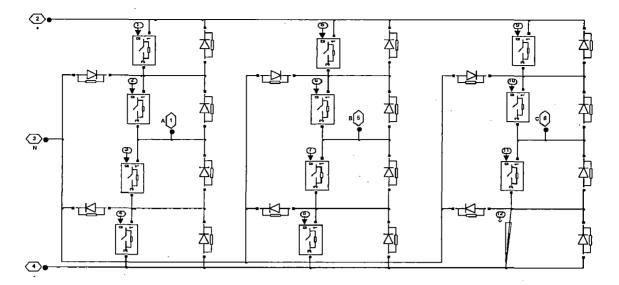

# 3.4.3 3-Level Bridge Using Diode Clamped Topology

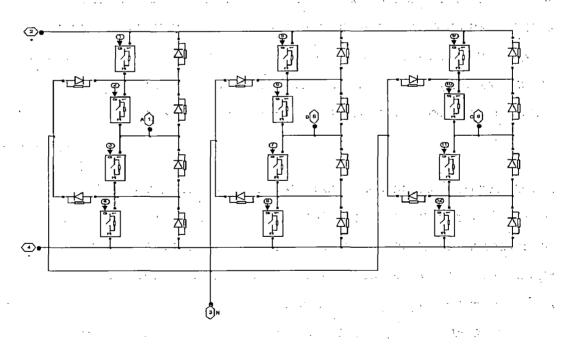

Fig.3.6 shows the Simulink model for three phase inverter using diode clamped configuration for generating the multilevel output.

#### Fig.3.6. Subsystem for the 3-Level Bridge

# FAULT DETECTION IN MULTI LEVEL INVERTER USING FUZZY INFERENCE SYSTEM AND ANFIS

### **Introduction to Fuzzy and ANFIS:**

The term expert system (ES), Fuzzy logic (FL), artificial neural network (ANN), and genetic algorithm (GA) belong to an area called ARTIFICIAL INTELLIGENCE (AI). Recently, the area of AI has penetrated deeply into electrical engineering, and their applications in power electronics and motion control appears very promising. The goal of AI is to plant human or natural intelligence in a computer so that a computer can think intelligently like a human being.

A system with embedded computational intelligence is often defined as an "intelligent system" that has "learning," "self-organizing," or "self-adapting" capability. However, there is no denying the fact that computers can have adequate intelligence to help solving our problems that are difficult to solve by traditional methods. Therefore, it is true that AI techniques are now being extensively used in industrial process control, image processing, diagnostics, medicine, space technology, and information management system, just to name a few.

System modeling based on conventional mathematical tools like differential equations is not perfectly suited for dealing with uncertain systems. By contrast a Fuzzy inference system employing Fuzzy IF-THEN rules can model the qualitative aspects of human knowledge and reasoning process without employing precise quantitative analyses. This Fuzzy modelling or Fuzzy identification, first explored systematically by Takagi and Sugeno, has found numerous practical applications in control, prediction and inference. However, there are some basic aspects of this approach which are in need of better understanding.

More specifically:

- 1) No standard methods exist for transforming human knowledge or experience into the rule base and database of a Fuzzy inference system.

- There is a need for effective methods for tuning the membership functions (MF's) so as to minimize the output error measure or maximize performance index.

An Adaptive-Neuro Fuzzy Inference System, or simply ANFIS, which can serve as a basis for constructing a set of Fuzzy if-then rules with appropriate membership functions to generate the stipulated input-output pairs.

The basic structure of the type of Fuzzy inference system is a model that maps input characteristics to input membership functions, input membership function to rules, rules to a set of output characteristics, output characteristics to output membership functions, and the output membership function to a single-valued output or a decision associated with the output. We have only considered membership functions that have been fixed, and somewhat arbitrarily chosen. Also, we've only applied Fuzzy inference to modeling systems whose rule structure is essentially predetermined by the user's interpretation of the characteristics of the variables in the model.

#### 4.1 Fuzzy Inference Systems and ANFIS

#### A. Fuzzy If-Then Rules

Fuzzy if-then rules are expressions of the form IF A THEN B, where A and B are labels of Fuzzy sets characterized by appropriate membership functions. Due to their concise form, Fuzzy if-then rules are often employed to capture the imprecise modes of reasoning that play an essential role in the human ability to make decisions in an environment of uncertainty and imprecision [10]-[26].

والمحمور والمراجع وا

An example that describes a simple fact is

"If pressure is high, then volume is small"

Where pressure and volume are linguistic variables, high and small are linguistic values or labels that are characterized by membership functions.

Another form of Fuzzy if-then rule, proposed by Takagi and Sugeno, has Fuzzy sets involved only in the premise part. By using Takagi and Sugeno's Fuzzy if-then rule, we can describe the resistant force on a moving object as follows:

"If velocity is high, then force =  $k^*$ (velocity)<sup>2</sup>"

• • • • • •

Where, again, high in the premise part is a linguistic label characterized by an appropriate membership function. However, the consequent part is described by a non-Fuzzy equation of the input variable, velocity. Both types of Fuzzy if-then rules have been used extensively in both modelling and control. Through the use of linguistic labels and membership functions, a Fuzzy if-then rule can easily capture the spirit of a "rule of thumb" used by humans. From another angle, due to the qualifiers on the premise parts, each Fuzzy if-then rule can be viewed as a local description of the system under consideration [25]. Fuzzy if-then rules form a core part of the Fuzzy inference system to be introduced below.

A Modeling Scenario

Suppose we want to apply Fuzzy inference to a system for which we already have a collection of input/output data that we would like to use for modeling, modelfollowing, or some similar scenario. We don't necessarily have a predetermined model structure based on characteristics of variables in our system.

Alter States and States

القسي التركي ترفي جري في التركي الترفيل مردة

There will be some modeling situations in which we can't just look at the data and discern what the membership functions should look like. Rather than choosing the parameters associated with a given membership function arbitrarily, these parameters could be chosen so as to tailor the membership functions to the input/output data in order to account for these types of variations in the data values. This is where the socalled Neuro-Adaptive learning techniques incorporated into ANFIS in the Fuzzy Logic can help [10].

. . • •

The basic idea behind these Neuro-Adaptive learning techniques is very simple. These techniques provide a method for the Fuzzy modeling procedure to learn information about a data set, in order to compute the membership function parameters that best allow the associated Fuzzy inference system to track the given input/output data. This learning method works similarly to that of neural networks [5]-[9].

#### What Is ANFIS?

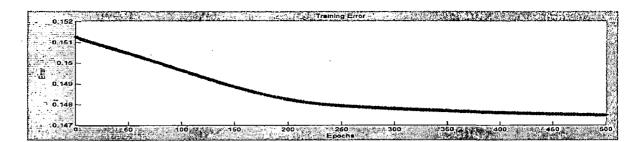

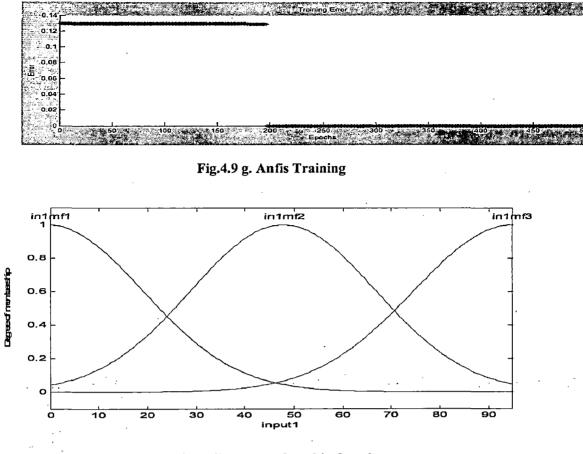

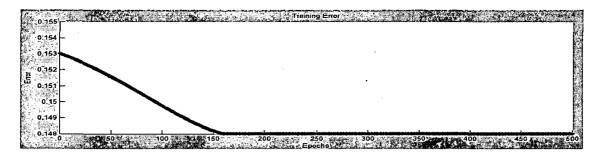

The acronym ANFIS derives its name from Adaptive Neuro-Fuzzy Inference System. Using a given input/output data set, ANFIS constructs a Fuzzy inference system (FIS) whose membership function parameters are tuned (adjusted) using either a Back propagation algorithm alone, or in combination with a least squares type of method. This allows our Fuzzy systems to learn from the data they are modeling [27].

Simply we can say that it's a network-type structure similar to that of a neural network, which maps inputs through input membership functions and associated parameters, and then through output membership functions and associated parameters to outputs, can be used to interpret the input/output map. The parameters associated with the membership functions will change through the learning process. The computation of these parameters (or their adjustment) is facilitated by a gradient vector, which provides a measure of how well the Fuzzy inference system is modeling the input/output data for a given set of parameters. Once the gradient vector is obtained, any of several optimization routines could be applied in order to adjust the parameters so as to reduce some error measure (usually defined by the sum of the squared difference between actual and desired outputs). ANFIS uses either back propagation or a combination of least squares estimation and back propagation for membership function parameter estimation [5]-[9].

### Familiarity Breeds Validation: Know Your Data

The modeling approach used by ANFIS is similar to many system identification techniques. First, we hypothesize a parameterized model structure (relating inputs to membership functions to rules to outputs to membership functions, and so on). Next,

29

. /

ан на развити 1911 г. – Прила Паради, на развити 1911 г. – Прила Паради, на развити you collect input/output data in a form that will be usable by ANFIS for training. You can then use ANFIS to train the FIS model to emulate the training data presented to it by modifying the membership function parameters according to a chosen error criterion.

In general, this type of modeling works well if the training data presented to ANFIS for training (estimating) membership function parameters is fully representative of the features of the data that the trained FIS is intended to model. This is not always the case, however. In some cases, data is collected using noisy measurements, and the training data cannot be representative of all the features of the data that will be presented to the model. This is where model validation comes into play [9].

# Model Validation Using Checking and Testing Data Sets

One problem with model validation for models constructed using adaptive techniques is selecting a data set that is both representative of the data the trained model is intended to emulate, yet sufficiently distinct from the training data set so as not to render the validation process trivial. If we have collected a large amount of data, hopefully this data contains all the necessary representative features, so the process of selecting a data set for checking or testing purposes is made easier. However, if we expect to be presenting noisy measurements to our model, it is possible the training data set does not include all of the representative features we want to model.

### **Constraints of ANFIS:**

ANFIS is much more complex than the Fuzzy inference systems, and is not available for all of the Fuzzy inference system options. Specifically, ANFIS only supports Sugeno-type systems, and these must have the following properties:

A. A. Star A.

. . .

- > Be first or Zeroth order Sugeno-type systems.

- ➢ Have a single output, obtained using weighted average Defuzzification. All output membership functions must be the same type and either linear or constant.

- Have no rule sharing. Different rules cannot share the same output membership function, namely the number of output membership functions must be equal to the number of rules.

- $\triangleright$  Have unity weight for each rule.

- > An error occurs if our FIS structure does not comply with these constraints.

- Moreover, ANFIS cannot accept all the customization options that basic Fuzzy inference allows. That is, we cannot make our own membership functions and Defuzzification functions; we must use the ones provided.

#### Architecture of ANFIS:

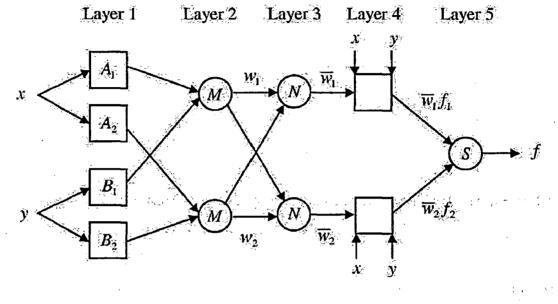

The ANFIS is a Fuzzy Sugeno model put in the framework of adaptive systems to facilitate learning and adaptation. Such framework makes the ANFIS modelling more systematic and less reliant on expert knowledge. To present the ANFIS architecture, two fuzzy if-then rules based on a first order Sugeno model are considered:

Rule 1: If  $(x ext{ is } A_1)$  and  $(y ext{ is } B_1)$  then  $(f_1 = p_1 x + q_1 y + r_1)$

Rule 2: If (x is  $A_2$ ) and (y is  $B_2$ ) then ( $f_2 = p_2x + q_2y + r_2$ )

Where x and y are the inputs,  $A_i$  and  $B_i$  are the fuzzy sets,  $f_i$  are the outputs within the Fuzzy region specified by the Fuzzy rule,  $p_i$ ,  $q_i$  and  $r_i$  are the design parameters that are determined during the training process. The ANFIS architecture to implement these two rules is shown in Fig.4.1, in which a circle indicates a fixed node, whereas a square indicates an adaptive node.

In the first layer, all the nodes are adaptive nodes. The outputs of layer 1 are the fuzzy membership grade of the inputs, which are given by:

$$O_i^l = \mu A_i(x)$$

$i = 1, 2;$  (4.1.1)

$$O_i^l = \mu B_{i-2}(y)$$

i=3,4; (4.1.2)

31

. . . .

Where  $\mu A_i(x)$ ,  $\mu B_{i-2}(y)$  can adopt any Fuzzy membership function. For example, if the bell shaped membership function is employed and is given by

Fig 4.1 ANFIS architecture.

Where  $a_i$ ,  $b_i$  and  $c_i$  are the parameters of the membership function, governing the bell shaped functions accordingly. In the second layer, the nodes are fixed nodes. They are labelled with M, indicating that they perform as a simple multiplier. The outputs of this layer can be represented as:

$$O_i^2 = w_i = \mu A_i(x) \mu B_i(y)$$

i=1,2 (4.1.4)

Which are the so-called firing strengths of the rules. In the third layer, the nodes are also fixed nodes. They are labelled with N, indicating that they play a normalization role to the firing strengths from the previous layer. The outputs of this layer can be represented as

$$O_i^3 = \overline{w_i} = \frac{w_i}{w_1 + w_2}$$

i=1,2 (4.1.5)

32

na se se se se se temperature name anne se se

• • • • •

which are the so-called normalized firing strengths. In the fourth layer, the nodes are adaptive nodes. The output of each node in this layer is simply the product of the normalized firing strength and a first order polynomial (for a first order Sugeno model). Thus, the outputs of this layer are given by:

$$O_i^4 = \overline{w_i} f_i = \overline{w_i} \left( p_i x + q_i y + r_i \right) \quad i=1,2$$

$$(4.1.6)$$

In the fifth layer, there is only one single fixed node labelled with S. This node performs the summation of all incoming signals. Hence, the overall output of the model is given by:

$$O_i^5 = \sum_{i=1}^2 \overline{w_i} f_i = \frac{\sum_{i=1}^2 w_i f_i}{w_1 + w_2}$$

(4.1.7)

It can be observed that there are two adaptive layers in this ANFIS architecture, namely the first layer and the fourth layer. In the first layer, there are three modifiable parameters  $\{a_i, b_i, c_i\}$ , which are related to the input membership functions. These parameters are the so-called premise parameters. In the fourth layer, there are also three modifiable parameters  $\{p_i, q_i, r_i\}$ , pertaining to the first order polynomial. These parameters are so-called consequent parameters [27].

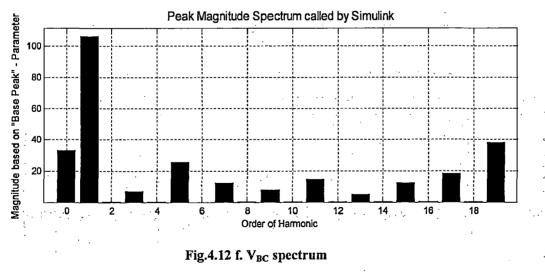

## Learning algorithm of ANFIS:

The task of the learning algorithm for this architecture is to tune all the modifiable parameters, namely  $\{a_i, b_i, c_i\}$  and  $\{p_i, q_i, r_i\}$ , to make the ANFIS output match the training data. When the premise parameters  $a_i$ ,  $b_i$  and  $c_i$  of the membership function are fixed, the output of the ANFIS model can be written as:

;

$$f = \frac{w_1}{w_1 + w_2} f_1 + \frac{w_2}{w_1 + w_2} f_2$$

(4.1.8)

Substituting Eq. (4.1.5) into Eq. (4.1.8) yields:

$$f = \overline{w_1}f_1 + \overline{w_2}f_2 \tag{4.1.9}$$

Substituting the fuzzy if-then rules into Eq. (4.1.9), it becomes:

$$f = \overline{w_1} (p_1 x + q_1 y + r_1) + \overline{w_2} (p_2 + q_2 y + r_2)$$

(4.1.10)

After rearrangement, the output can be expressed as:

$$f = \left(\overline{w_1}x\right)p_1 + \left(\overline{w_1}y\right)q_1 + \left(\overline{w_1}\right)r_1 + \left(\overline{w_2}x\right)p_2 + \left(\overline{w_2}y\right)q_2 + \left(\overline{w_2}y\right)r_2$$

(4.1.11)

This is a linear combination of the modifiable consequent parameters  $p_1$ ,  $q_1$ ,  $r_1$ ,  $p_2$ ,  $q_2$  and  $r_2$ . The least squares method can be used to identify the optimal values of these parameters easily. When the premise parameters are not fixed, the search space becomes larger and the convergence of the training becomes slower. A hybrid algorithm combining the least squares method and the gradient descent method is adopted to solve this problem. The hybrid algorithm is composed of a forward pass and a backward pass. The least squares method (forward pass) is used to optimize the consequent parameters with the premise parameters fixed. Once the optimal consequent parameters are found, the backward pass starts immediately. The gradient descent method (backward pass) is used to adjust optimally the premise parameters corresponding to the Fuzzy sets in the input domain. The output of the ANFIS is calculated by employing the consequent parameters found in the forward pass. The output error is used to adapt the premise parameters by means of a standard Back-propagation algorithm. It has been proven that this hybrid algorithm is highly efficient in training the ANFIS.

There are number of intelligent systems approaches that have been investigated in signal fault diagnosis. Decision trees and Rule-based expert systems are two normally used diagnostic techniques, but they have serious limitations. A rule-based system often has difficulties in dealing with novel faults and acquiring a complete knowledge to build a reliable rule base. A decision tree can be very large for a complex system, and it is also system dependent such that even small engineering changes can mean significant updates. More recently model based approaches, Fuzzy logic, Artificial Neural Networks (ANN), case-based reasoning (CBR) are popular techniques used in various fault diagnostics problems in electrical systems [23].

ومرتبع أجامع محفرة المتعاد المعاري المعتب والمتعين والمتعالي والمتعار والمتعار والمتعار والمتعار والمتعار

والمحاج والمحاج والمراجع والمراجع والمحاج والمحاج والمحاج والمحاج والمحاج والمحاج والمحاج والمحاج والمحاج والمح

The diagnostic system has the capability of accurately detecting whether a fault has occurred, and show the faulty location in the electric drive within 20 ms or less. The contribution of this work is important because in many applications it is extremely important to detect a fault immediately after it occurs and pin-point to the cause of fault. As soon as a fault is detected and located, for example switch  $S_1$  short or  $S_5$  open and so on, it should be isolated and the damaged part should be shut down immediately to minimise the damage to other parts of the system. Identifying the location and type of the fault fast enough can also allow smooth transition to a gracefully degradable mode, which enhances the overall system availability [30]-[14].

It is to point out that generating short circuit faults is in an inverter can cause significant damage (if not total destruction) to the closed-loop controlled electrical system. To prevent such a situation, an electrical system in a lab setting needs various protective mechanisms built in it to shut down the system before any signals in a faulty condition can be sampled. Regarding the possibility of setting up hardware-based experiment where catastrophic failure will not occur during a short circuit fault, it should be noted that this catastrophic failure pertains initially to the solid state power electronic switches, which will try to short circuit the source. Hence, to save the system (both the source and the power electronics switch) we must have to trip it off. If not the source it self, in addition to the switch, may suffer damage. The issue, therefore, is more related to be able to diagnose the fault before it is tripped off. Otherwise the power electronics circuit can soon become unbalanced. At that point, if the motor still has mechanical load connected to it, the situation can lead to both electrical and mechanical damage to the motor because of unbalanced operation.

All the above items point to the difficulty of designing a physical experiment under the above circumstances. Therefore the simulated systems are important means to study fault diagnostic problems in closed-loop situation. Due to these difficulties, the results generated in this thesis work are primarily from the data produced by a simulation model. The simulation model has been validated on the single open switch faults and short-circuits faults in inverter [4].

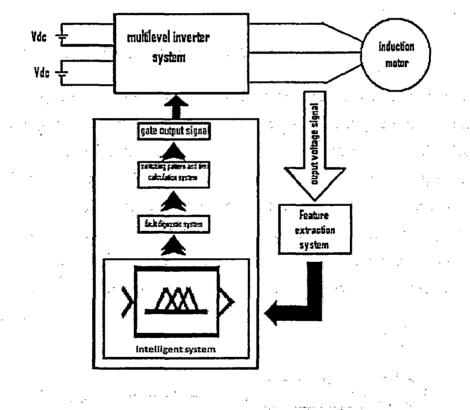

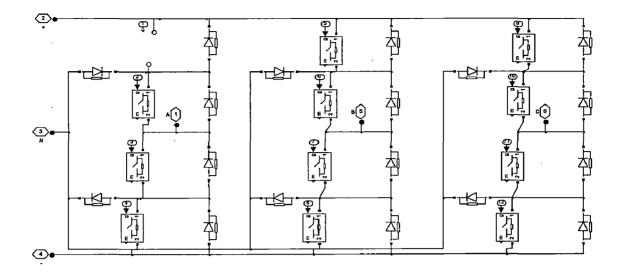

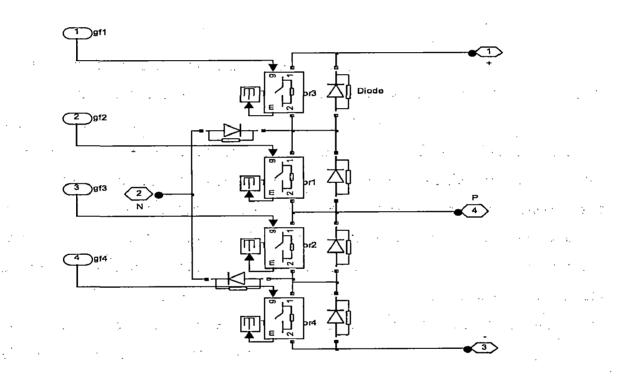

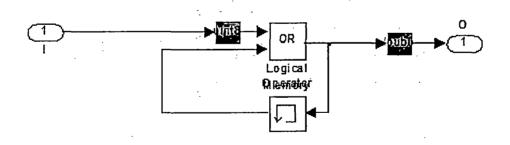

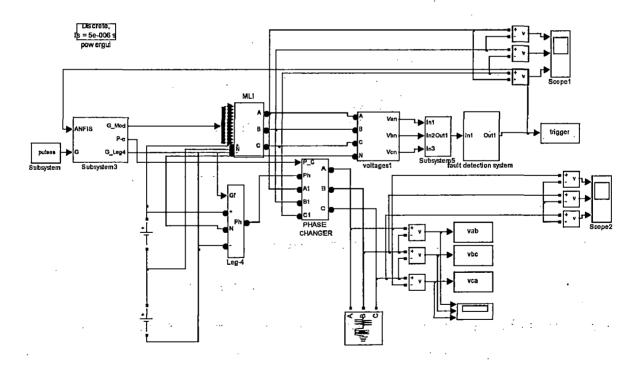

#### 4.2 General Structure of the fault diagnostic system:

The fault diagnostic system is composed of four major states: feature extraction, Artificial Intelligent systems, fault diagnosis, and switching pattern calculation with gate signal output. The Feature extraction, Intelligent system, and Fault diagnosis are the focus of this research. The Feature extraction performs the voltage input signal transformation, with rated signal values as important features, and the output of the transformed signal is transferred to the Intelligent system. The Intelligent system is designed to give output as 1 for abnormal conditions and 0 for normal conditions. By decoding this binary code the fault location can be detected. After decoding the switching pattern is calculated.

Fig 4.2 Structure of Fault diagnosis system

Since the output of the multilevel inverter is a staircase form, we can't give this output voltages directly to any fault detection system for detection of fault. So we extract the fault features from the output of the multilevel inverter using Feature

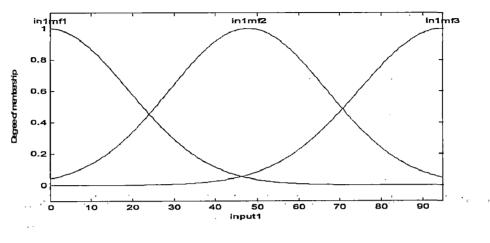

Extraction system; these features are given as input for Intelligent system to detect fault location. For Fuzzy inference system we have used the 3<sup>rd</sup> harmonic magnitude to represent the fault features, for ANFIS we have used the FFT samples to represent the fault features of the system.

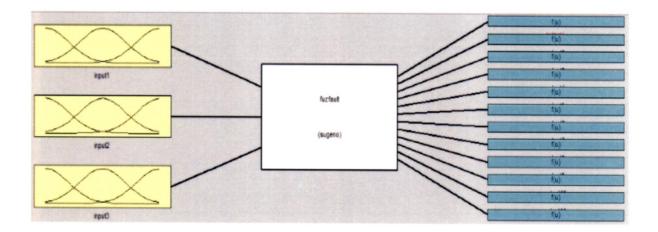

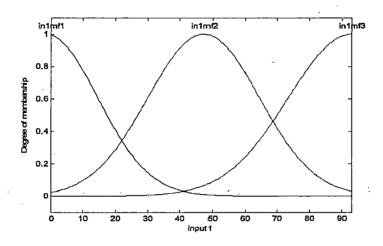

#### 4.3 Fault detection using Fuzzy Inference System

The Fuzzy inference system is of Sugeno type. The magnitudes of third harmonic content present in the Phase-to-neutral voltages are taken as input for Fuzzy to detect the type of fault. The number of inputs for Fuzzy inference system is 3, they are  $3^{rd}$  harmonic magnitudes of Phase-to-neutral voltages and the number of outputs of Fuzzy is 12. These 12 outputs are suitably modified to generate the triggering pulses for the extra added leg(s) which is used for reconfiguration and to isolate the faulted inverter leg(s). The variation in magnitudes  $3^{rd}$  harmonic present in each phase-to-neutral output voltage is shown in the last row of the Table 4.1. The range of  $3^{rd}$  harmonic content present in the phase-to-neutral voltages is shown at the end of the Table 4.1. And the structure of the Fuzzy Inference system is shown in Fig.4.3.

Fig.4.3. Structure of the fuzzy inference system

The member ship functions are of type triangular. In the first step we create membership functions based on the variation of the magnitude of  $3^{rd}$  harmonic. The range of values is given in the table below.

| Type of fault         | Magnitude ranges of                         | Magnitude ranges of                         | Magnitude ranges of                         |

|-----------------------|---------------------------------------------|---------------------------------------------|---------------------------------------------|

|                       | 3 <sup>rd</sup> harmonic in V <sub>an</sub> | 3 <sup>rd</sup> harmonic in V <sub>bn</sub> | 3 <sup>rd</sup> harmonic in V <sub>cn</sub> |

| Open S <sub>1</sub>   | 2.53-2.57                                   | .2834                                       | .194206                                     |

| Short S <sub>1</sub>  | .276277                                     | .2934                                       | .237242                                     |

| Open S <sub>2</sub>   | 4.1-4.25                                    | .2228                                       | .1611615                                    |

| Short S <sub>2</sub>  | .2126                                       | .3153                                       | .204207                                     |

| Open S <sub>3</sub>   | 4.1-4.7                                     | .20526                                      | .13251335                                   |

| Short S <sub>3</sub>  | .2731                                       | .2936                                       | .21522                                      |

| Open S <sub>4</sub>   | .27285                                      | .2935                                       | .184188                                     |

| Short S <sub>4</sub>  | .097098                                     | .31365                                      | .2224                                       |

| Open S <sub>5</sub>   | .1724                                       | 3.1-3.33                                    | .2426                                       |

| Short S <sub>5</sub>  | .243                                        | .015022                                     | .233238                                     |

| Open S6               | .1118                                       | 4.3-4.7                                     | .224245                                     |

| Short S <sub>6</sub>  | .2532                                       | .3137                                       | .235245                                     |

| Open S <sub>7</sub>   | .227                                        | 3.75-3.95                                   | .142                                        |

| Short S <sub>7</sub>  | .1723                                       | .2932                                       | .25265                                      |

| Open S <sub>8</sub>   | .232                                        | 2.3-2.4                                     | .20523                                      |

| Short S <sub>8</sub>  | .2126                                       | .0913                                       | .21222                                      |

| Open S <sub>9</sub>   | .215245                                     | .2732                                       | 2.33-2.35                                   |

| Short S <sub>9</sub>  | .2431                                       | .336                                        | .015038                                     |

| Open S <sub>10</sub>  | .152                                        | .243                                        | 3.75-3.9                                    |

| Short S <sub>10</sub> | .2531                                       | .3345                                       | .224226                                     |

| Open S <sub>11</sub>  | .19285                                      | .24529                                      | 3.8-4.6                                     |

| Short S <sub>11</sub> | .2227                                       | .336                                        | .27528                                      |

| Open S <sub>12</sub>  | .22305                                      | .2934                                       | 2.4-3.2                                     |

| Short S <sub>12</sub> | .21255                                      | .3136                                       | .1216                                       |

| Range                 | .097-4.25                                   | .015-4.7                                    | .015-4.6                                    |

# Table 4.1: Variation 3<sup>rd</sup> Harmonic in the phase-to-Neutral Voltages

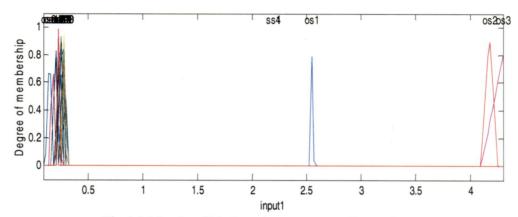

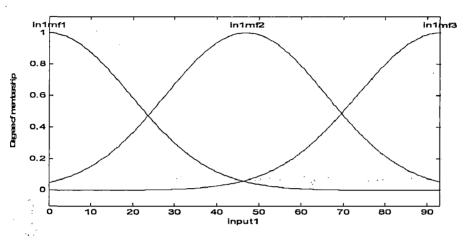

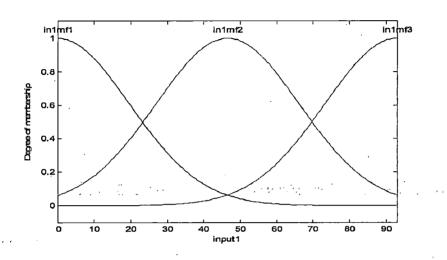

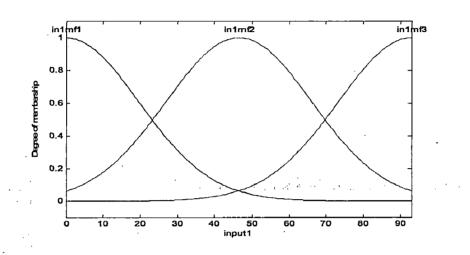

Here the number of membership functions is 24 corresponding to 24 different types of faults. These are shown in Fig.4.4.

Fig.4.4. Member Ship functions corresponding to Van

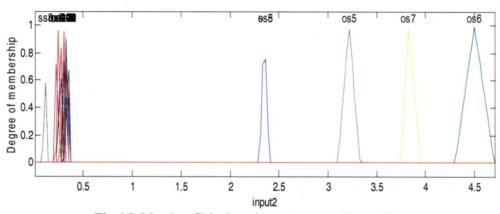

Fig.4.5. Member Ship functions corresponding to  $V_{bn}$

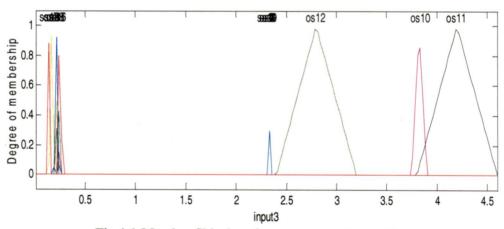

Fig.4.6. Member Ship functions corresponding to V<sub>cn</sub>

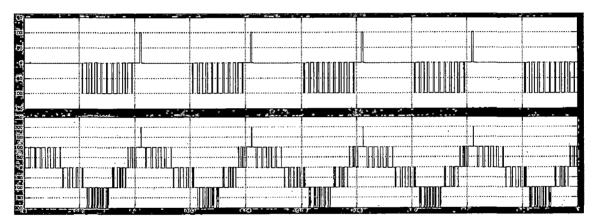

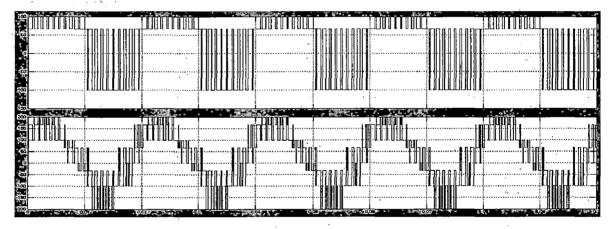

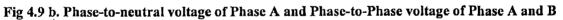

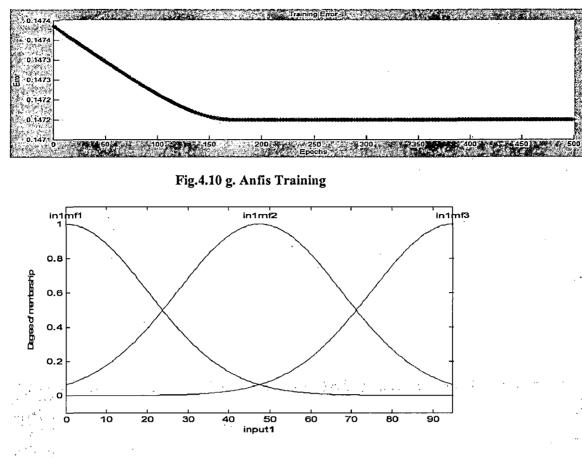

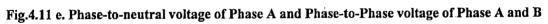

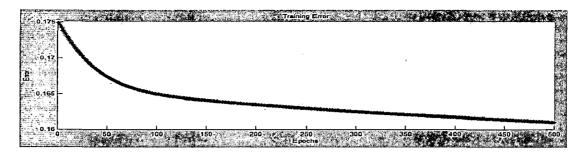

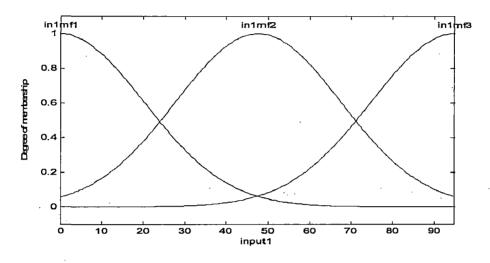

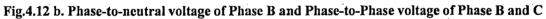

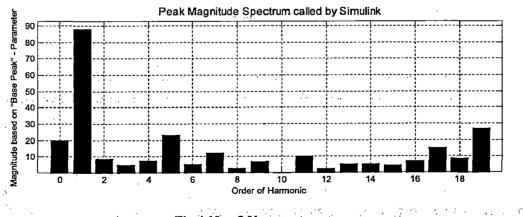

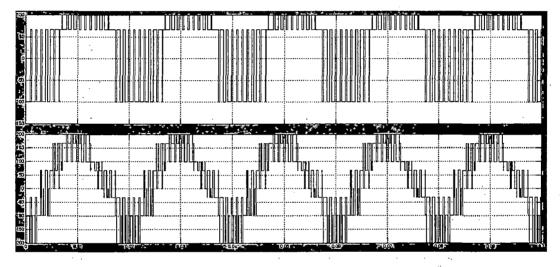

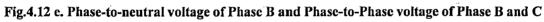

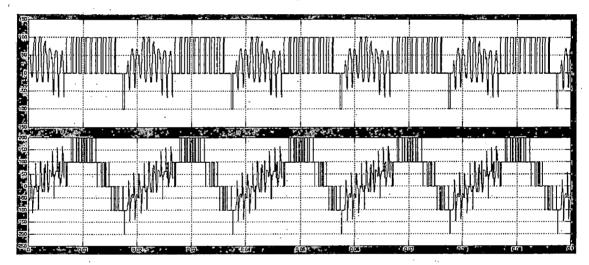

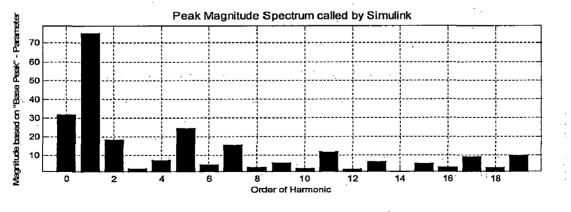

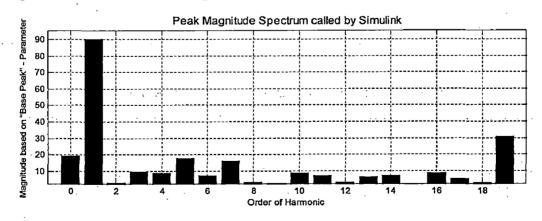

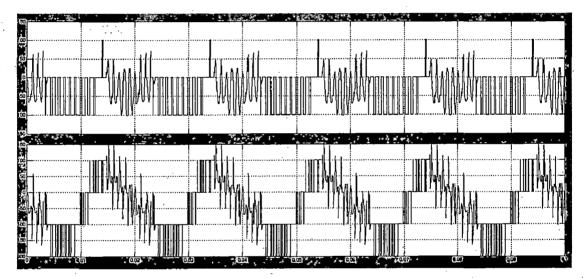

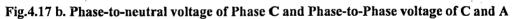

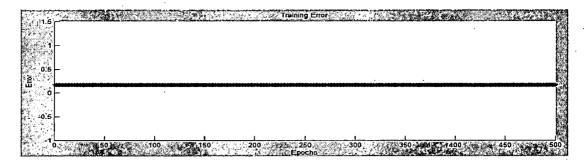

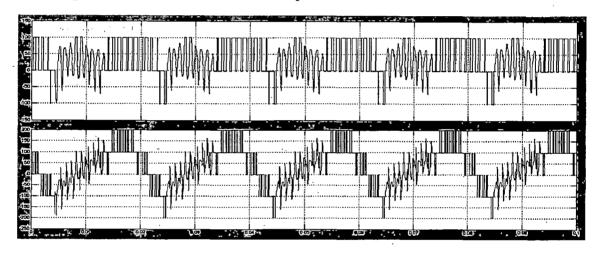

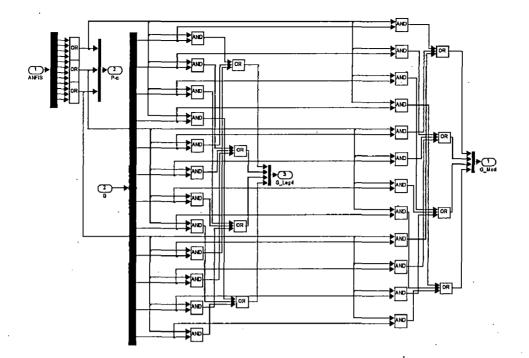

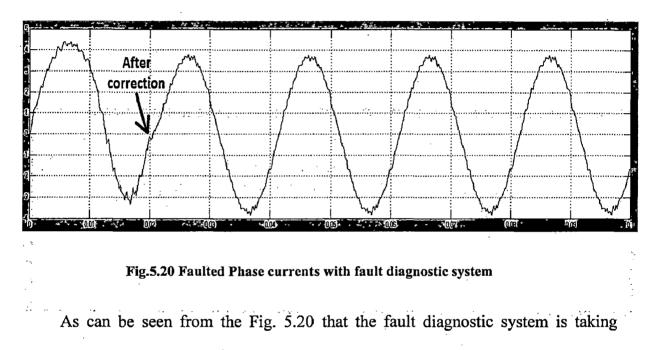

#### 4.4 Fault detection using Adaptive Neuro Fuzzy Inference System

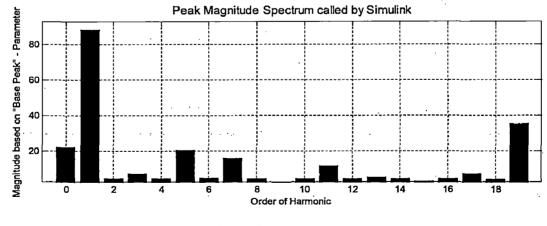

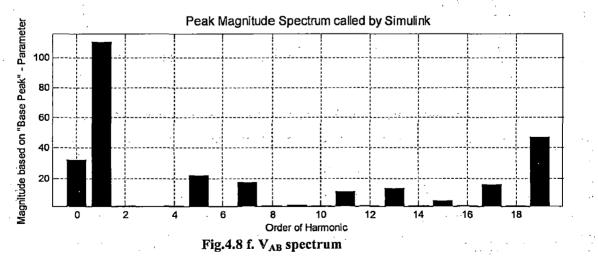

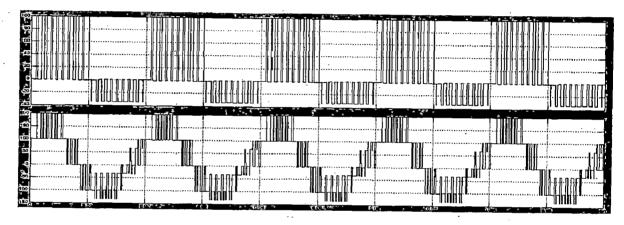

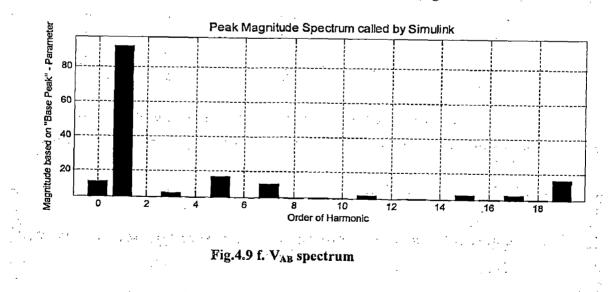

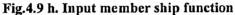

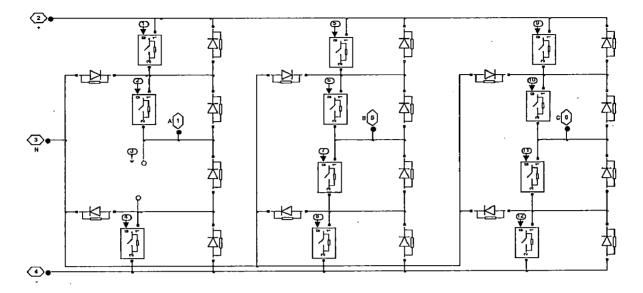

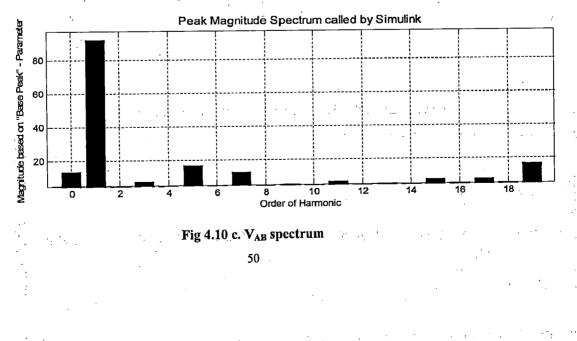

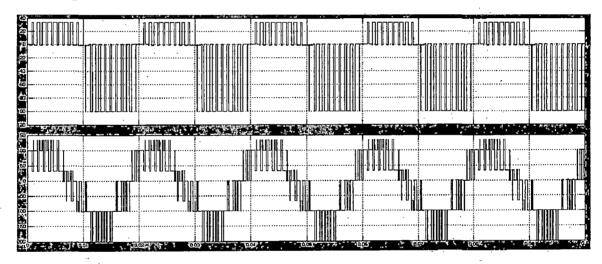

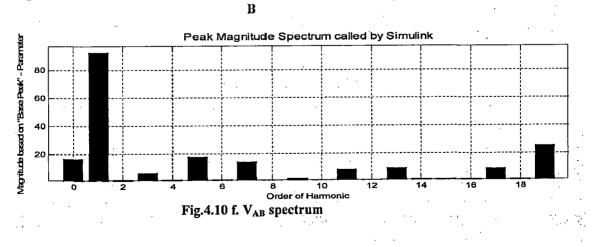

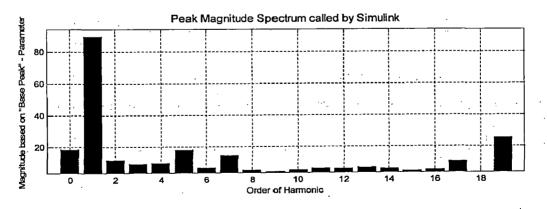

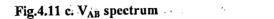

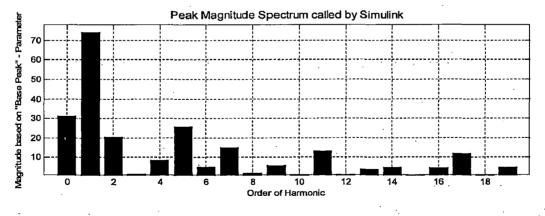

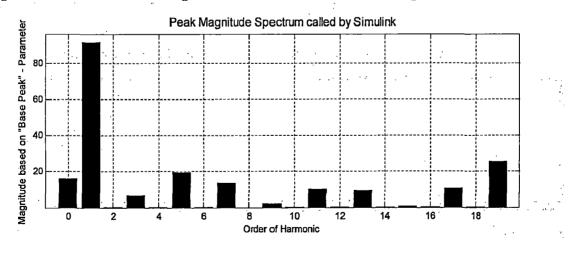

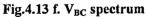

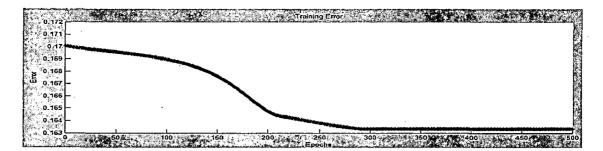

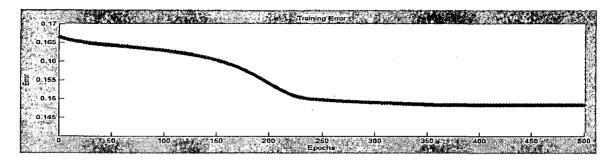

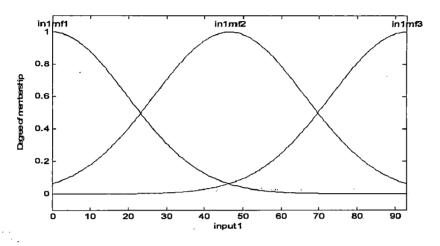

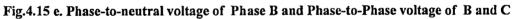

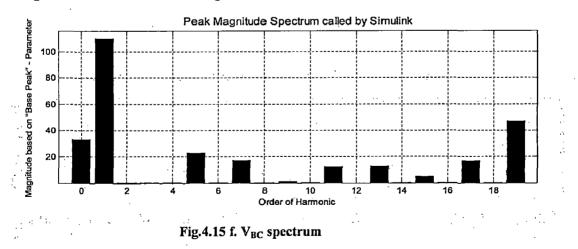

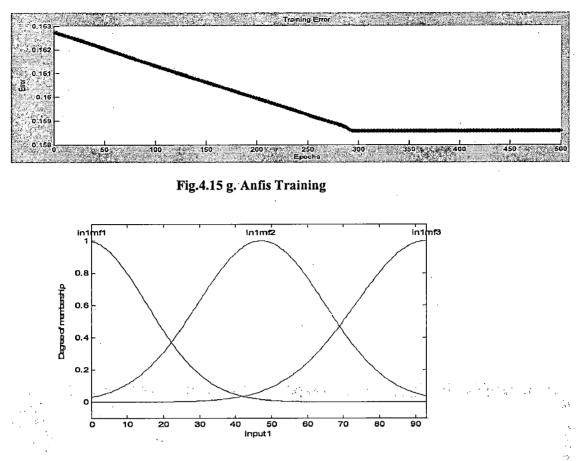

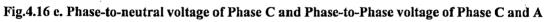

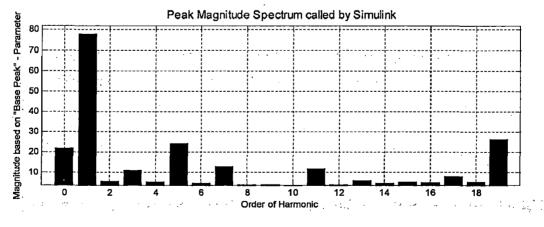

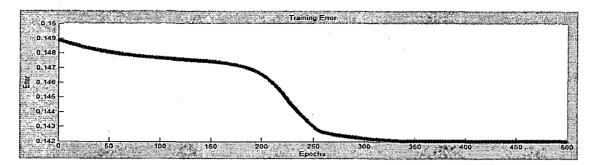

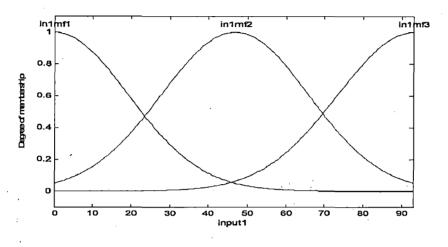

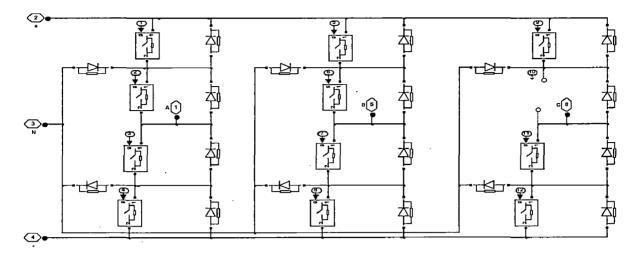

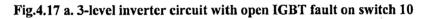

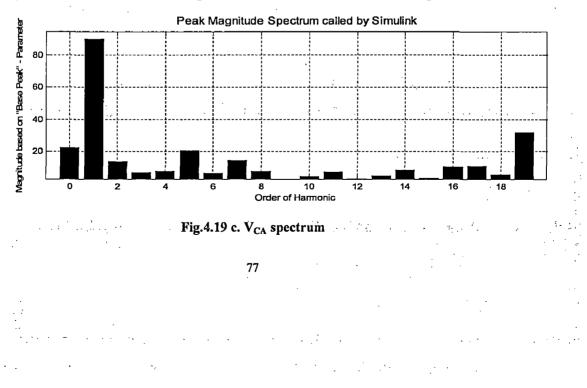

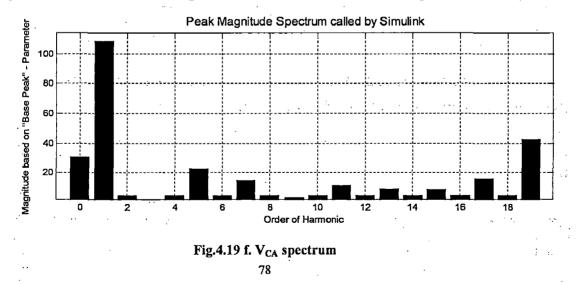

In this type of fault detection system we use FFT samples as the fault features of the inverter. The FFT used here is going to generate 20 FFT samples of the Phase-to-Phase output voltage of the inverter. Among them we have used 5 samples for training purpose. And these 5 samples are given as input to ANFIS. An appropriate selection of feature extractor is to provide the ANFIS with adequate significant details in the pattern set so that the highest degree of accuracy in the ANFIS performance can be obtained.