# AUTOMATED MEASUREMENT OF RESISTIVITY OF THIN FILMS

## **A DISSERTATION**

Submitted in partial fulfillment of the requirements for the award of the degree of MASTER OF TECHNOLOGY in SOLID STATE ELECTRONIC MATERIALS

By

# MD FAISAL KHAN

DEPARTMENT OF PHYSICS INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE - 247 667 (INDIA)

**JUNE, 2006**

# **CANDIDATE'S DECLARATION**

I hereby declare that the work which is being presented in this dissertation report entitled "AUTOMATED MEASUREMENT OF RESISTIVIY OF THIN FILMS" for the partial fulfillment of the requirement for the award of degree of "MASTER OF TECHNOLOGY" in "SOLID STATE ELECTRONIC MATERIALS" and submitted in the department of Physics, Indian Institute of Technology Roorkee, Roorkee, is an authentic record of my own work carried out under the supervision and guidance of Dr. S.K.Barthwal, Associate Professor, Department of Physics, Indian Institute of Technology Roorkee, Roorkee, Roorkee during the period from July 2005 to June 2006.

The matter embodied in this dissertation report has not been submitted by me for the award of any other degree or diploma.

Date: 30/06/2006 Place: Roorkee

MD. FAISAL KHAN

### CERTIFICATE

This is to certify that the work related to the Dissertation entitled "AUTOMATED MEASUREMENT OF RESISTIVITY OF THIN FILMS", has been carried out by MD FAISAL KHAN of M.Tech (Solid State Electronic Materials) under my supervision.

Prof. S. K. Barthawal

Prof. S. K. Barthawal Associate Professor Department of physics Indian Institute of Technology Roorkee

i

# ACKNOWLEDGEMENTS

This dissertation is not by far created by me alone, without encouraging support and appreciation from my guide **Dr. S. K. Barthawal**, Associate Professor, Department of Physics, Indian Institute of Technology Roorkee, Roorkee, it would not have been as enjoyable working here and writing this dissertation as it really has been. Under his guidance I have not only gained technical expertise but also learnt to apply my presence of mind and to tackle practical problems. Moreover he enhanced my self confidence whenever work seemed difficult to proceed.

I like to thanks **Dr. J. Rai**, Head of Department, Physics, Indian Institute of Technology Roorkee, and **Dr. R. Nath** Coordinator, M.Tech, Solid State Electronic Materials Indian Institute of Technology Roorkee, for giving inspiration and providing every possible support.

I wish to express my sincere thanks to Mr. Adarsh Gupta for providing me valuable suggestions and accurate comments on my work to direct me in the right direction when I needed it.

I have also the pleasure of having **Rajesh Jourwal**, M.Tech. Student and **Neelima Agrawal**, Research Scholar, as a very valuable colleagues by contributing with well contemplated comments on this dissertation, they have made me realize new aspects of my work.

Finally, I would like to give my appreciation to all my classmates of Solid State Electronic Materials, who cooperated all the time during the course of this work.

Date: 30/06/2006 Place: Roonkee

MD FAISAL KHAN

# ABSTRACT

In the area of measurements, a big part of the technical expertise is gained from practical experience. Therefore, the learning period require to become a skilled engineer is usually very long. Nowadays, when more industries/companies go into the area of measurement by choosing hardware and software solutions instead old manual methods there is a rising need for more efficient measurement methods for engineers.

The programming ease and falling cost of PC make it very attractive to be used in automated measurements. The availability of high performance computing software can be used for data management, processing and presentation.

Computer aided measurements needs interfacing hardware which has been presented in this dissertation. First, the subject of data acquisition has been structured into adequate work areas and the required human knowledge for engineers in the measurement area is classified and described. Each part of the hardware design including, unipolar and bipolar configuration of digital to analog converter for writing digital data, selecting channels and acquiring data using multiplexing, reading digital data and controlling parameters using analog to digital converter, generating clock signal have been explained.

In a subject like measurement, which is strongly connected to practical knowledge, it is vital that presented theory is accompanied by practical related information thus finally required programs and graphs have been presented to support the proper working of interface using MATLAB and data acquisition toolbox.

To facilitate the learning of component behaviors and circuit performance in this dissertation, there is a methodology presented how to develop comprehensible hardware for automated measurement and to facilitate the understanding of programming language, structured programs for data acquisition have been explained.

This work may help engineers to find more structured ways of designing data acquisition hardware.

iii

# CONTENTS

|           | Candidate's Declaration<br>Acknowledgements<br>Abstract<br>Contents<br>List of Figures<br>List of Tables | i<br>ii<br>iii<br>iv<br>v<br>viii |

|-----------|----------------------------------------------------------------------------------------------------------|-----------------------------------|

| Chapter 1 | Introduction                                                                                             | 1                                 |

| Chapter 2 | Data Acquisition                                                                                         | 3                                 |

|           | 2.1 The Data Acquisition System                                                                          | 3                                 |

|           | 2.2 The Analog Input Subsystem                                                                           | 13                                |

|           | 2.3 Making Quality Measurements                                                                          | 24                                |

| Chapter 3 | Description of Hardware                                                                                  | 33                                |

|           | 3.1 Parts of Hardware                                                                                    | 33                                |

|           | 3.2 Circuitry for Writing Digital Data                                                                   | 34                                |

|           | 3.3 Circuitry for Selecting Channels                                                                     | 38                                |

|           | 3.4 Circuitry for Reading Digital Data                                                                   | 43                                |

|           | 3.5 Circuitry for Generating Clock                                                                       | 54                                |

| Chapter 4 | Software for Acquiring Data                                                                              | 56                                |

| -         | 4.1 Introduction to MATLAB                                                                               | 56                                |

|           | 4.2 Data Acquisition Tool Box                                                                            | 58                                |

|           | 4.3 Digital Input/Output Object                                                                          | 59                                |

|           | 4.4 Reading and Writing Operation                                                                        | 66                                |

|           | 4.5 Generating Timer Events                                                                              | 70                                |

|           | 4.6 Evaluating Digital I/O Object Status                                                                 | 72                                |

| Chapter 5 | PCI 1751 Digital I/O Card                                                                                | 73                                |

|           | 5.1 General Information                                                                                  | 73                                |

|           | 5.2 Installation                                                                                         | 76                                |

|           | 5.3 Operation                                                                                            | 82                                |

| Chapter 6 | Thin Films and Resistivity Measurement                                                                   | 90                                |

| -         | 6.1 Elementary                                                                                           | 90                                |

|           | 6.2 Practical Schemes                                                                                    | 94                                |

|           | 6.3 Low Impedance Measurement                                                                            | 97                                |

| Chapter 7 | Results and Discussions                                                                                  | 103                               |

| Chapter 8 | Conclusion                                                                                               | 119                               |

| · •       | References                                                                                               | 120                               |

|           |                                                                                                          |                                   |

Appendices Appendix A: - Programs for Data Acquisition

122

# LIST OF FIGURES

| Figure 2.1-Components of Data Acquisition                                            | 4  |

|--------------------------------------------------------------------------------------|----|

| Figure 2.2-Multifunction Board                                                       | 5  |

| Figure 2.3-Relationship b/w User, Driver Software, Application Software and Hardware | 12 |

| Figure 2.4-ADC with Multiplexer                                                      | 14 |

| Figure 2.5-Plot of Channels and Time using Scanning Hardware                         | 15 |

| Figure 2.6-Plot of Channels and Time using SS/H Hardware                             | 16 |

| Figure 2.7-Sine Wave Quantized by ADC                                                | 17 |

| Figure 2.8-Plot Quantization Error and Time                                          | 18 |

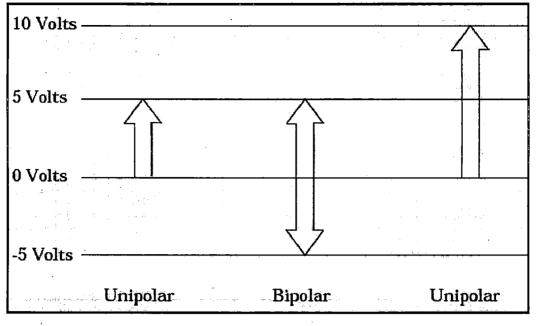

| Figure 2.9-Unipolar and Bipolar Signal                                               | 19 |

| Figure 2.10-Differential Input                                                       | 21 |

| Figure 2.11-Single Ended Input                                                       | 21 |

| Figure 2.12-Precision Vs Accuracy                                                    | 25 |

| Figure 2.13-Occurance of Aliasing                                                    | 30 |

| Figure 2.14-Effect of Low and High Sample Rate                                       | 31 |

| Figure 3.1-Functional Block Diagram                                                  | 33 |

| Figure 3.2-Digital Input Analog Output                                               | 34 |

| Figure 3.3-Pin diagram of AD 7521                                                    | 34 |

| Figure 3.4-Functional Diagram of AD7521                                              | 35 |

| Figure 3.5-Circuit Diagram for Unipolar Binary Operation                             | 35 |

| Figure 3.6-Circuit Diagram for Bipolar Operation                                     | 37 |

| Figure 3.7-Selection of Channels                                                     | 38 |

| Figure 3.8-Pin diagram of LS154                                                      | 39 |

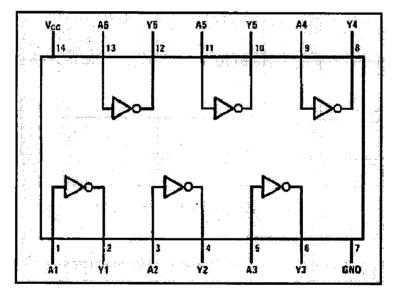

| Figure 3.9-Pin diagram of CD4066                                                     | 40 |

| Figure 3.10-Working of CD4066                                                        | 41 |

| Figure 3.11-Pin Diagram of LS04                                                      | 41 |

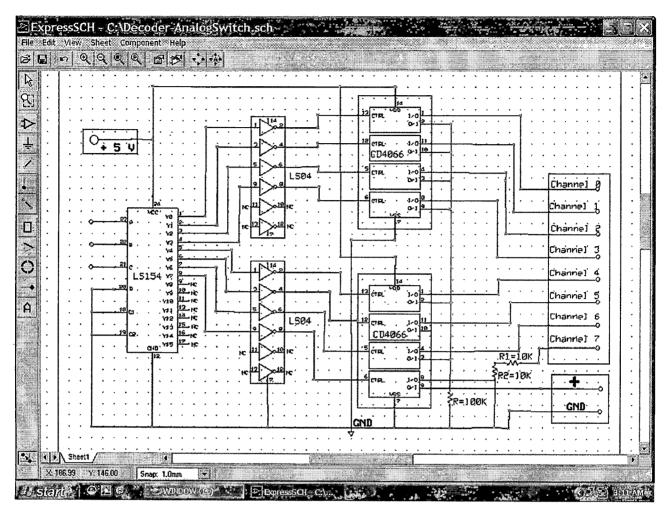

| Figure 3.12-Circuit Diagram for Selecting Channels                                   | 42 |

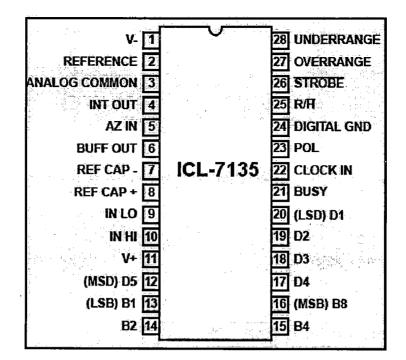

| Figure 3.13-Pin Diagram of ICL7135                                                   | 44 |

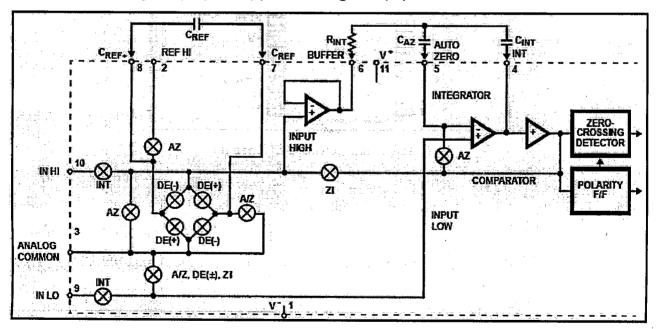

| Figure 3.14-Block Diagram of Analog Section of ICL7135                               | 44 |

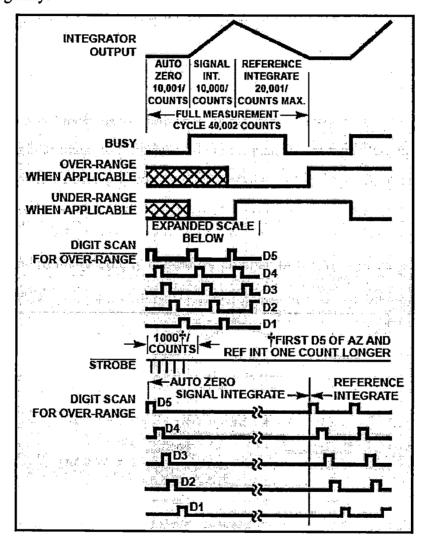

| Figure 3.15-Timing Diagram for Outputs                                               | 50 |

0

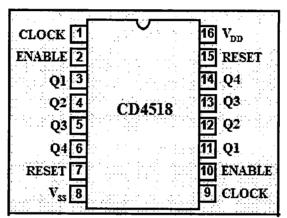

| Figure 3.16-Pin Diagram of CD4520                                           | 52  |

|-----------------------------------------------------------------------------|-----|

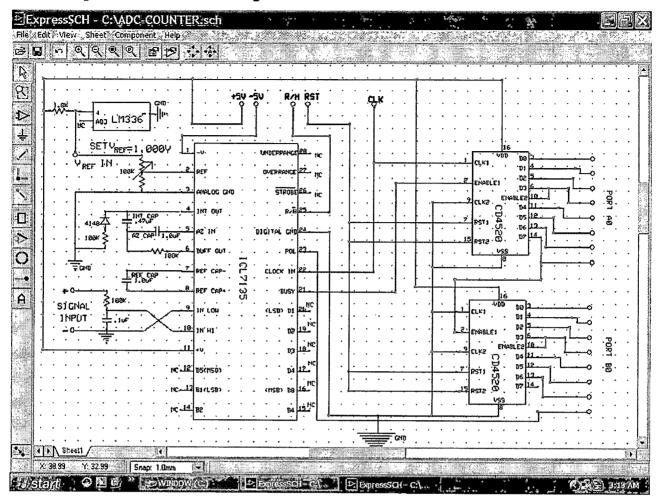

| Figure 3.17-Circuit Diagram for Reading Data                                | 53  |

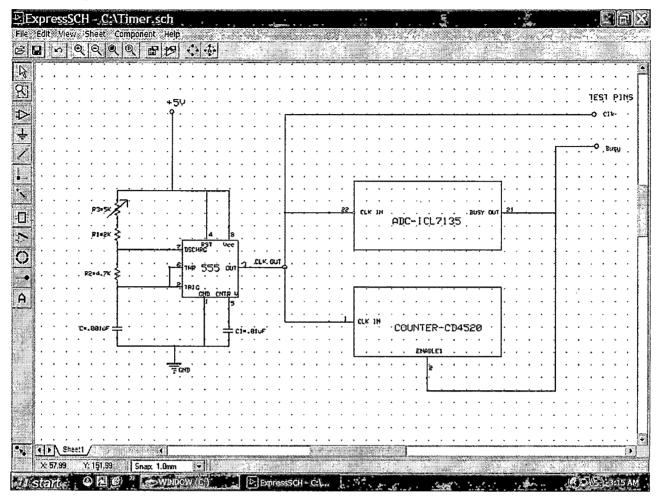

| Figure 3.18-Pin Diagram of 555                                              | 54  |

| Figure 3.19-Circuitry for Generating Clock                                  | 55  |

| Figure 4.1-Device Object as a Container                                     | 60  |

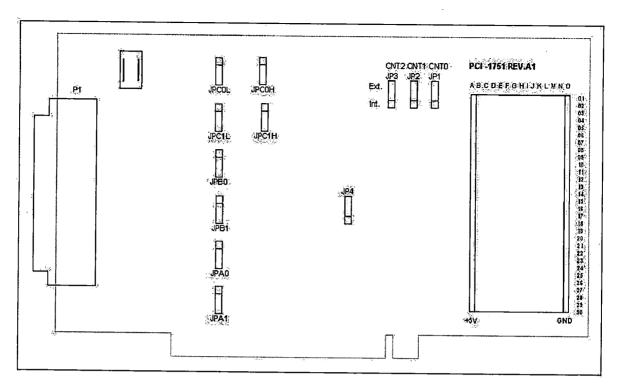

| Figure 5.1-Location of Connectors and Jumpers                               | 77  |

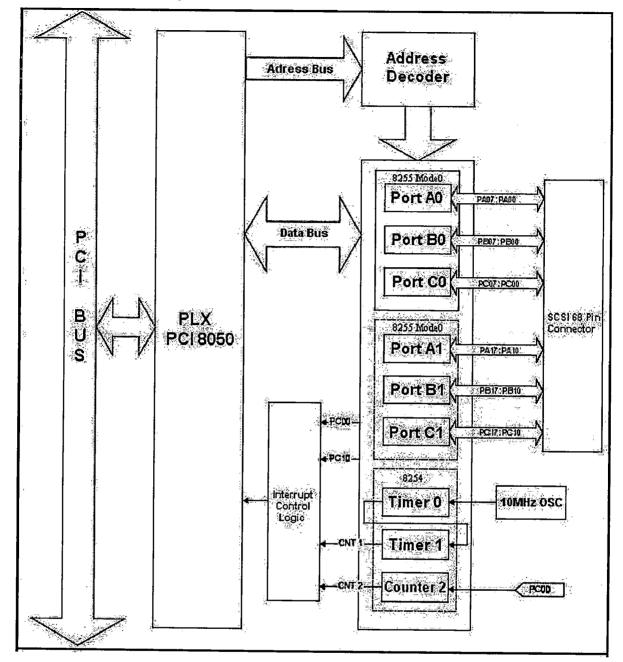

| Figure 5.2-PCI-1751 Block Diagram                                           | 80  |

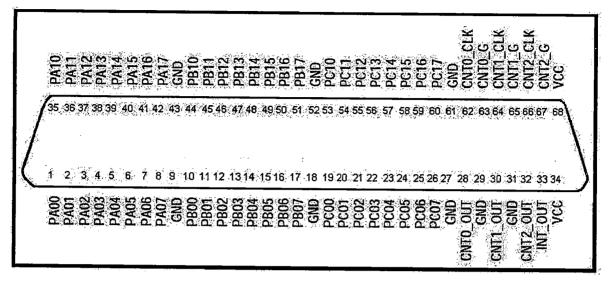

| Figure 5.3-Pin Diagram of PCI-1751                                          | 81  |

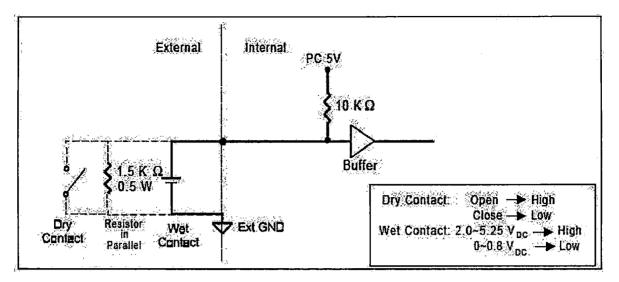

| Figure 5.4-Wet and Dry Contact Inputs                                       | 85  |

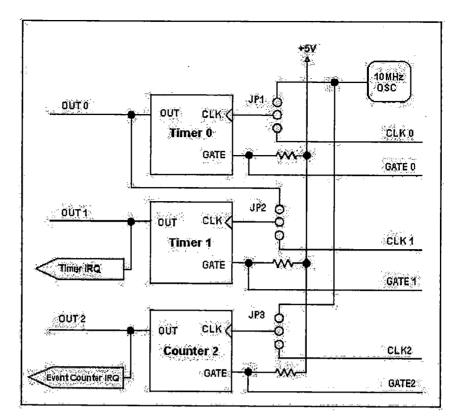

| Figure 5.5-Timer and Counter Structure                                      | 86  |

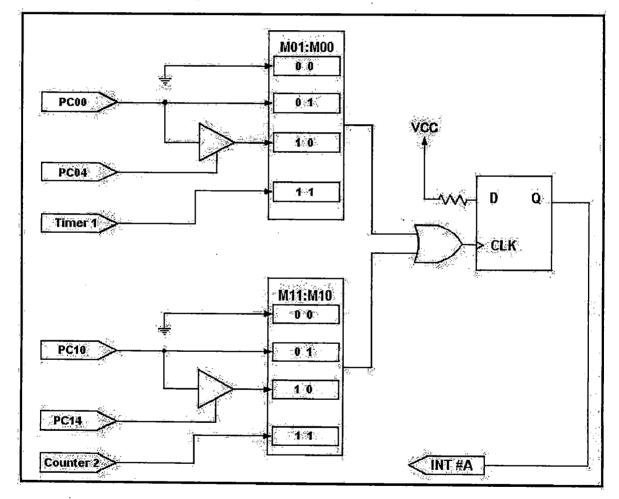

| Figure 5.6-Interrupt Sources                                                | 88  |

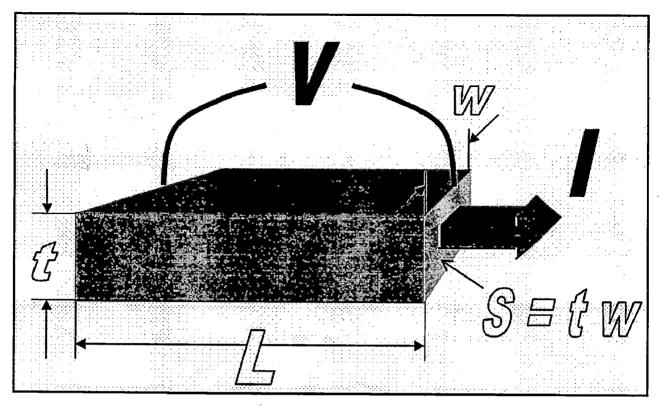

| Figure 6.1-Elementary Geometry of Resistance Measurements                   | 91  |

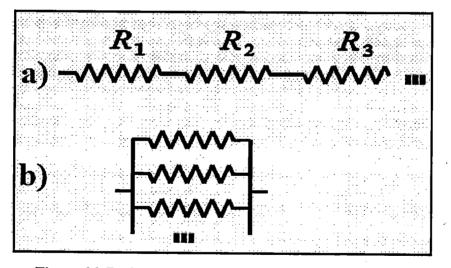

| Figure 6.2-Resistances Connected in (a) Series (b) Parallel                 | 91  |

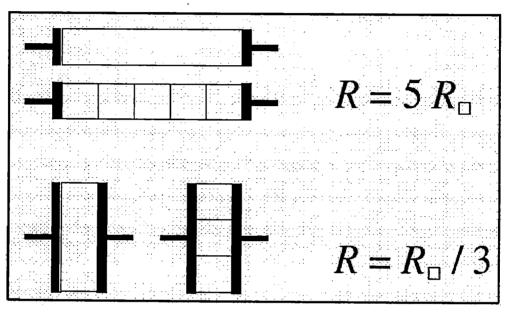

| Figure 6.3-Sheet Resistance                                                 | 92  |

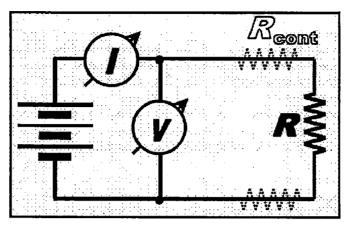

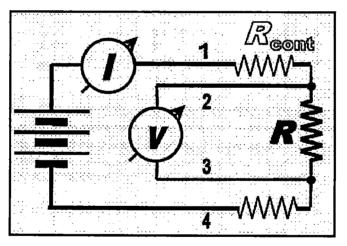

| Figure 6.4-Two-Probe Resistance Measurements                                | 93  |

| Figure 6.5-Four-Probe Resistance Measurements                               | 93  |

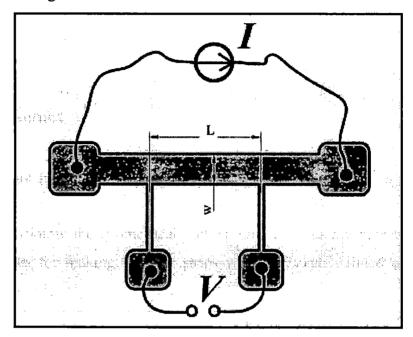

| Figure 6.6-Slab-Shape Pattern of Thin Film                                  | 94  |

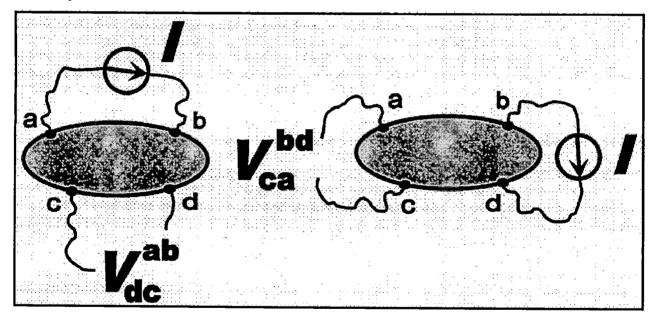

| Figure 6.7-Van der Pauw Method                                              | 95  |

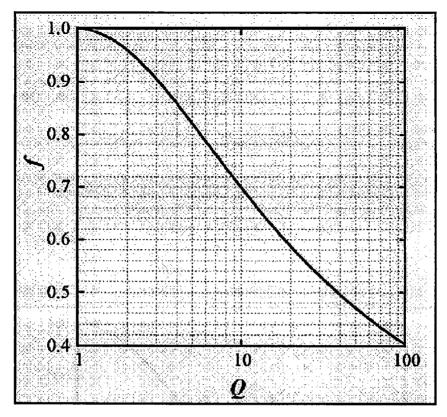

| Figure 6.8-The Relationship between f and Q                                 | 96  |

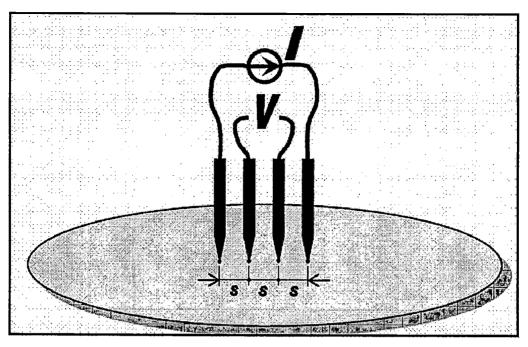

| Figure 6.9-Sheet Resistance of a Large-Area Thin Film                       | 97  |

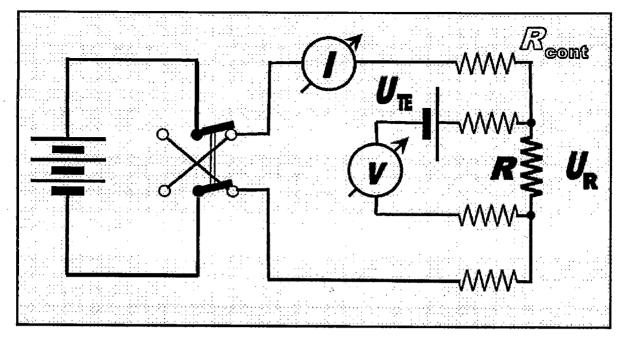

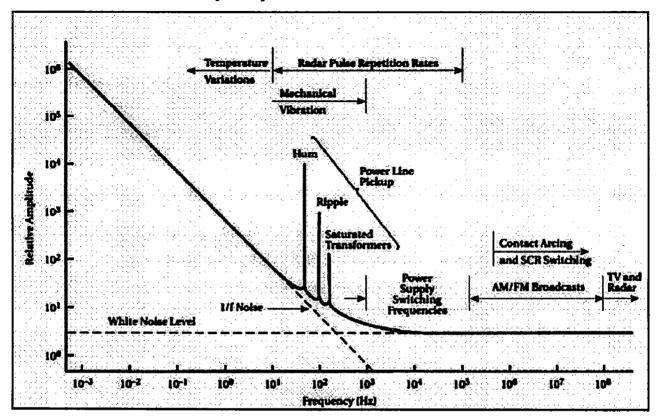

| Figure 6.10-Bias Reversal Schematic                                         | 99  |

| Figure 6.11-Frequency Spectrum of Interference Signal                       | 100 |

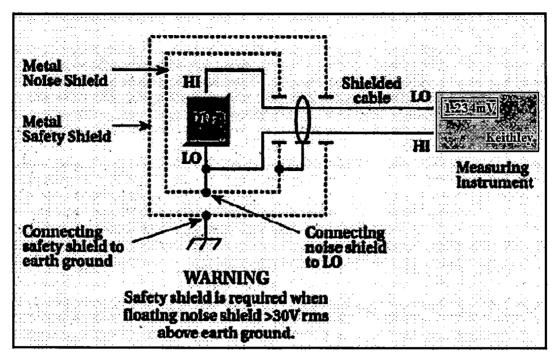

| Figure 6.12-Shielding from RFI/EMI Signals                                  | 101 |

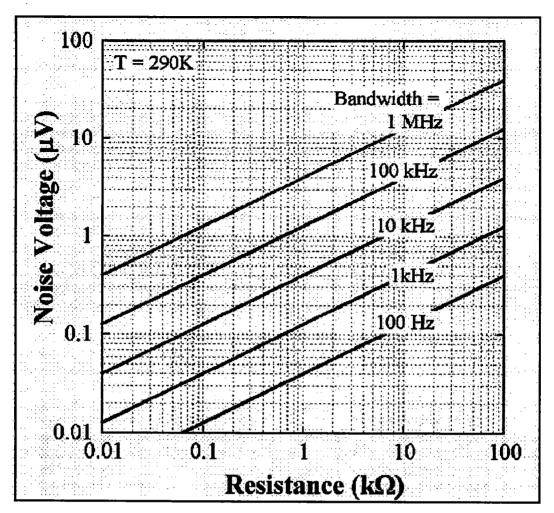

| Figure 6.13-Thermal Noise Voltage as a Function of Resistance and Bandwidth | 102 |

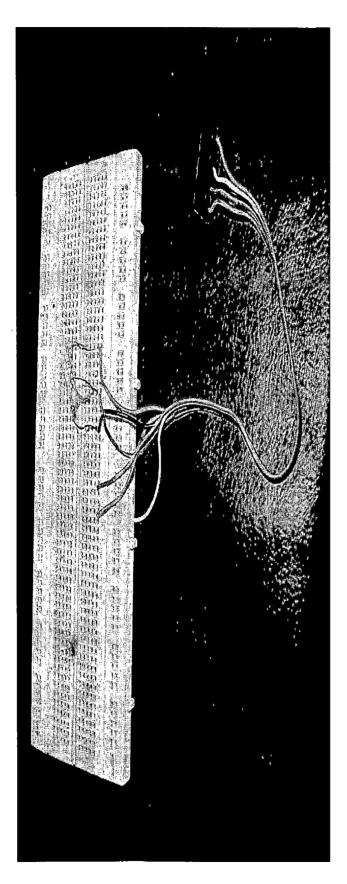

| Figure 7.1 (a)-Hardware (Picture-1)                                         | 104 |

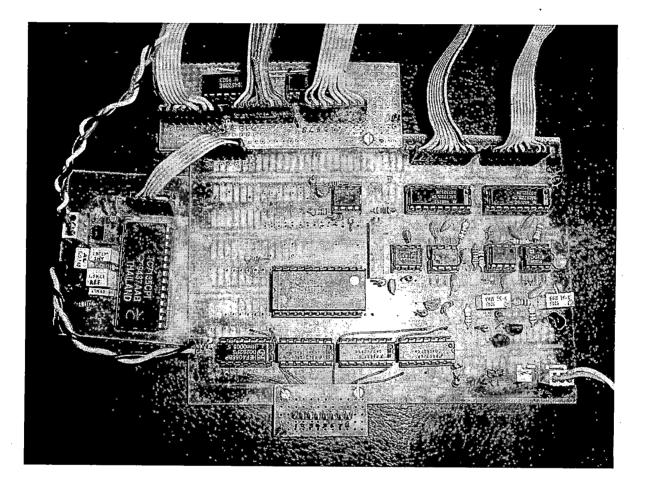

| Figure 7.1 (b)-Hardware (Picture-2)                                         | 105 |

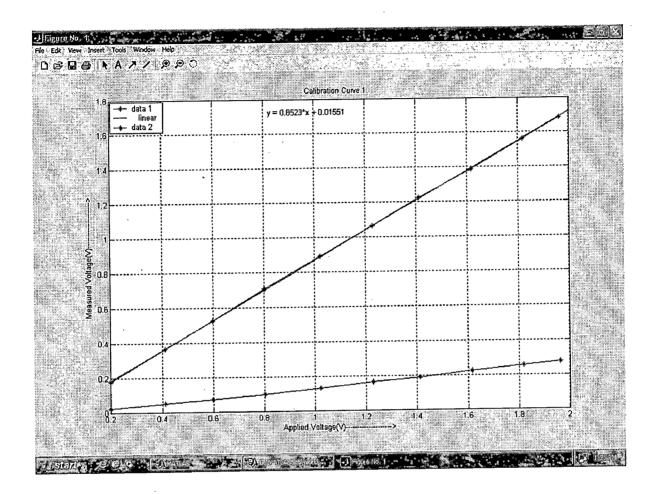

| Figure 7.2 (a)-Applied Voltage Vs Measured Voltage of ADC (ref=1.2V)        | 106 |

| Figure 7.2 (b)-Applied Voltage Vs Measured Voltage of ADC (ref=1.002V)      | 107 |

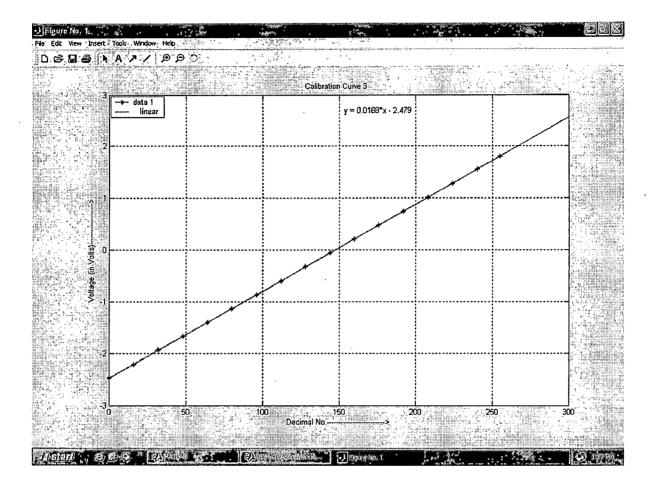

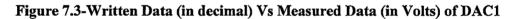

| Figure 7.3-Written Data (in decimal) Vs Measured Data (in Volts) of DAC1    | 108 |

| Figure 7.4-Written Data (in decimal) Vs Measured Data (in Volts) of DAC2    | 109 |

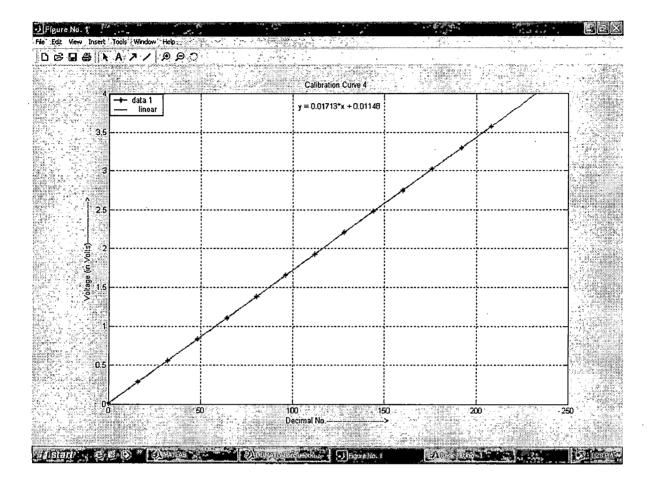

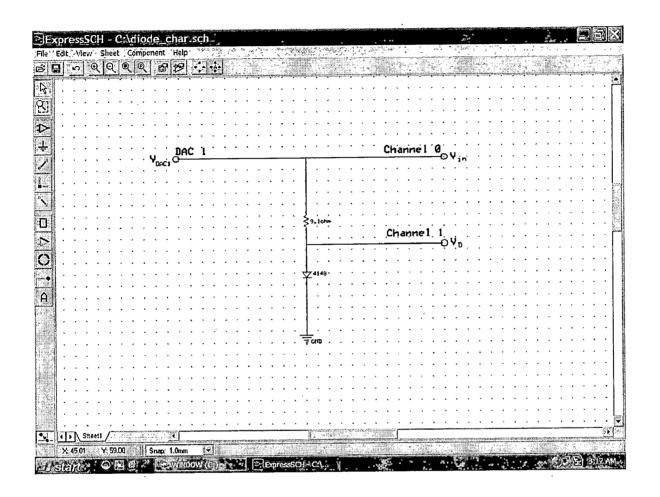

| Figure 7.5 (a)-Schematic Circuit Diagram for I-V Characteristic of Resistor | 110 |

.

.

.

|   | Figure 7.5 (b)-Circuit for I-V Characteristic of Resistor                       | 111 |

|---|---------------------------------------------------------------------------------|-----|

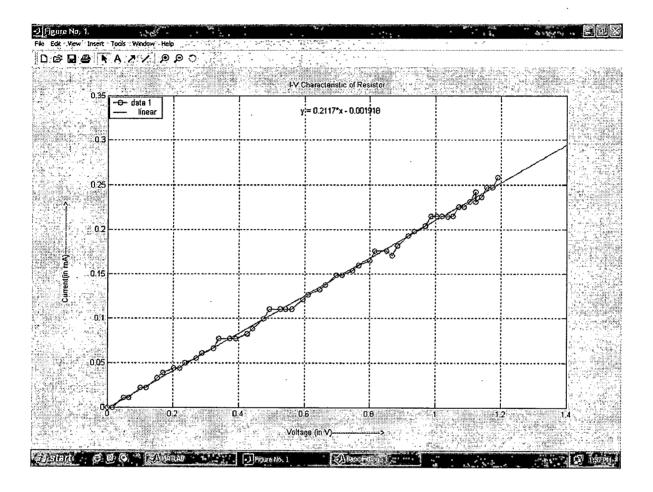

|   | Figure 7.6-I-V Characteristic of Resistor                                       | 112 |

|   | Figure 7.7 (a)-Schematic Circuit Diagram for I-V Characteristic of Diode        | 113 |

|   | Figure 7.7 (b)-Circuit for I-V Characteristic of Diode                          | 114 |

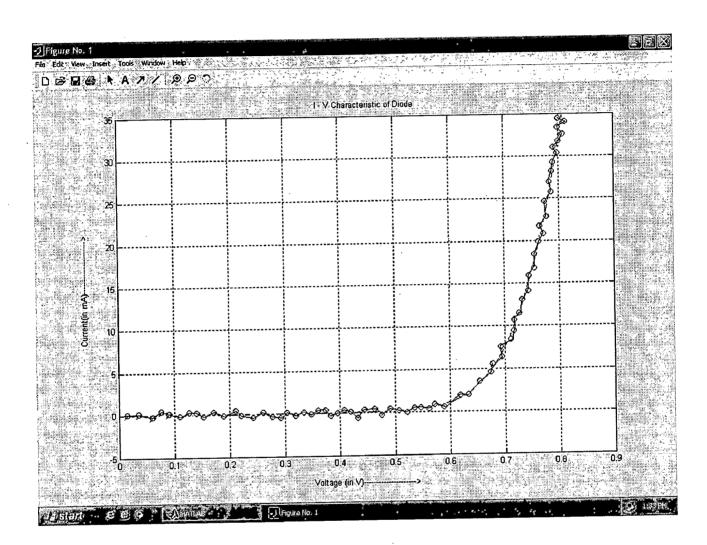

|   | Figure 7.8-I-V Characteristic of Diode                                          | 115 |

|   | Figure 7.9 (a)-Schematic Circuit Diagram for Measuring Resistivity of Thin Film | 116 |

|   | Figure 7.9 (b)-Thin Film with Electrode Connections                             | 117 |

| - | Figure 7.9 (c)-Circuit for Measuring Resistivity of Thin Film                   | 118 |

1

.

.

# LIST OF TABLES

| Table 2.1-Common Analog Sensors                                 | 7  |

|-----------------------------------------------------------------|----|

| Table 2.2-Relationship between Input Range, Gain, and Precision | 27 |

| Table 3.1-Code Table-Unipolar Binary Operation                  | 36 |

| Table 3.2-Code Table-Bipolar (Offset Binary) Operation          | 38 |

| Table 3.3-Truth Table LS154                                     | 40 |

| Table 3.4-Truth Table of LS04                                   | 41 |

| Table 4.1-Descriptive Digital I/O Properties                    | 60 |

| Table 4.2-Descriptive Digital I/O Line Properties               | 62 |

| Table 4.3-Digital I/O Timer Event Properties                    | 70 |

| Table 5.1-Summary of Jumper Settings                            | 79 |

| Table 5.2-Bit Map of Port Configuration Register                | 83 |

| Table 5.3-Interrupt Control Register Bit Map                    | 87 |

| Table 5.4-Interrupt Mode Bit Values                             | 89 |

| Table 5.5-Triggering Edge Control Bit Values                    | 89 |

| Table 5.6-Interrupt Flag Bit Values                             | 89 |

# **Chapter-1**

# **INTRODUCTION**

In the area of measurements, a big part of the technical expertise is gained from practical experience. Therefore, the learning period require to become a skilled engineer is usually very long. Nowadays, when more industries /companies go into the area of measurement by choosing hardware and software solutions instead old manual methods there is a rising need for more efficient measurement methods for engineers. The easy availability of personal computers has revolutionized the area of automated measurement and control of experiments. In olden times the experiments were either performed manually or by dedicated instruments incorporating embedded microprocessors. These instruments could perform a specified job in a unique configuration using a program which was stored in ROM, thus prohibiting any modification in terms of data acquisition or control of the experiment.

The programming ease and falling cost of PC make it very attractive to be used in automated measurements. Further, the availability of high performance computing software can be used for data management, processing and presentation.

Computer aided measurements need interfacing hardware which has been presented in this dissertation. First, the subject of data acquisition has been structured into adequate work areas and the required human knowledge for engineers in the measurement area has been classified and described. Each part of the hardware design including, unipolar and bipolar configuration of digital to analog converter for writing digital data, selecting channel and acquiring data using decoder, reading digital data and controlling parameters using analog to digital converter, generating clock signal have been explained. In a subject like measurement, which is strongly connected to practical knowledge, it is vital that presented theory is accompanied by practical related information thus finally required programs and graphs have been presented to support the proper working of interface using MATLAB and data acquisition toolbox.

From a technical point of view, for automated measurement, knowledge in three main areas is needed: component behaviors, circuit performance and programming language. To facilitate the learning of component behaviors and circuit performance in this dissertation, there is a methodology presented how to develop comprehensible hardware for automated measurement

1

and to facilitate the understanding of programming language, structured programs for data acquisition have been explained.

This work may help engineers to find more structured ways of designing data acquisition hardware.

# **DATA ACQUISITION**

# 2.1-The Data Acquisition System

#### **2.1.1-Introduction**

The purpose of any data acquisition system is to provide the tools and resources necessary to measure and analyze physical phenomena [16].

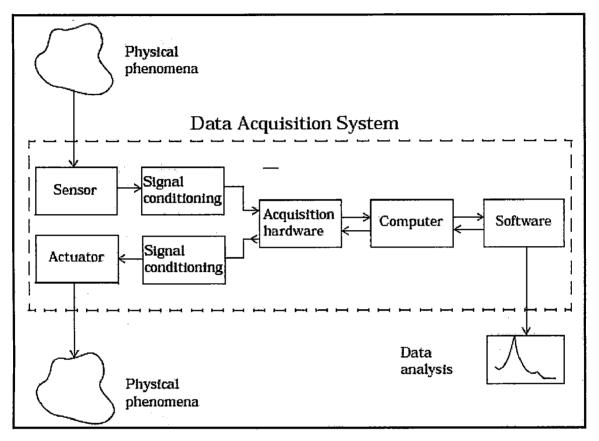

Data acquisition system can be thought as a collection of software and hardware that connects us to the physical world. A typical data acquisition system consists of these components:

#### • Data Acquisition Hardware

At the heart of any data acquisition system lies the data acquisition hardware. The main function of this hardware is to convert analog signals to digital signals, and to convert digital signals to analog signals.

#### • Sensors and Actuators (transducers)

Sensors and actuators can both be *transducers*. A transducer is a device that converts input energy of one form into output energy of another form. For example, a microphone is a sensor that converts sound energy (in the form of pressure) into electrical energy, while a loudspeaker is an actuator that converts electrical energy into sound energy.

#### • Signal Conditioning Hardware

Sensor signals are often incompatible with data acquisition hardware. To overcome this incompatibility, the signal must be conditioned. For example, we may need to condition an input signal by amplifying it or by removing unwanted frequency components. Output signals may need conditioning as well.

#### • Computer

The computer provides a processor, a system clock, a bus to transfer data, and memory and disk space to store data.

#### • Software

Data acquisition software allows us to exchange information between the computer and the hardware. For example, typical software allows us to configure the sampling rate of our board, and acquire a predefined amount of data.

The data acquisition components, and their relationship to each other, are shown below.

Figure 2.1-Components of Data Acquisition

The Figure 2.1 depicts the two important features of a data acquisition system:

- Signals are input to a sensor, conditioned, converted into bits that a computer can read, and analyzed to extract meaningful information. For example, sound level data is acquired from a microphone, amplified, digitized by a sound card, and stored in MATLAB for subsequent analysis of frequency content.

- Data from a computer is converted into an analog signal and output to an actuator. For example, a vector of data in MATLAB is converted to an analog signal by a sound card and output to a loudspeaker.

#### 2.1.2-Data Acquisition Hardware

Data acquisition hardware is either internal and installed directly into an expansion slot inside our computer, or external and connected to our computer through an external cable. For example, VXI modules are installed in an external VXI chassis, and data is transferred between MATLAB and the module using an external link such as FireWire.

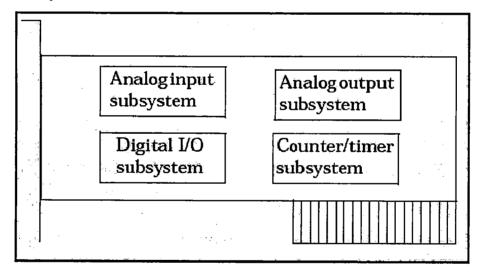

At the simplest level, data acquisition hardware is characterized by the *subsystems* it possesses. A subsystem is a component of our data acquisition hardware that performs a specialized task. Common subsystems include:

- Analog input

- Analog output

- Digital input/output

- Counter/timer

Hardware devices that consist of multiple subsystems, such as the one depicted below in Figure 2.2, are called *multifunction boards*.

**Figure 2.2-Multifunction Board**

#### **Analog Input Subsystems**

Analog input subsystems convert real-world analog input signals from a sensor into bits that can be read by computer. Perhaps the most important of all the subsystems commonly available are typically multichannel devices offering 12 or 16 bits of resolution.

Analog input subsystems are also referred to as AI subsystems, A/D converters, or ADCs.

#### **Analog Output Subsystems**

Analog output subsystems convert digital data stored on computer to a real-world analog signal. These subsystems perform the inverse conversion of analog input subsystems. Typical acquisition boards offer two output channels with 12 bits of resolution, with special hardware available to support multiple channel analog output operations.

Analog output subsystems are also referred to as AO subsystems, D/A converters, or DACs.

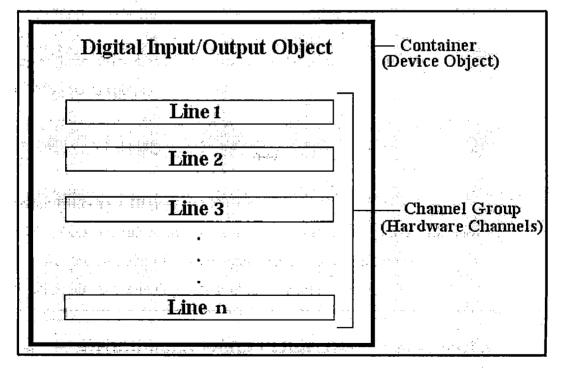

#### **Digital Input/Output Subsystems**

Digital input/output (DIO) subsystems are designed to input and output digital values (logic levels) to and from hardware. These values are typically handled either as single bits or *lines*, or as a *port*, which typically consists of eight lines.

While most popular data acquisition cards include some digital I/O capability, it is usually limited to simple operations, and special dedicated hardware is often necessary for performing advanced digital I/O operations.

#### **Counter/Timer Subsystems**

Counter/Timer (C/T) subsystems are used for event counting, frequency and period measurement, and pulse train generation.

#### 2.1.3-Sensors

A sensor converts the physical phenomena of interest into a signal that is input into data acquisition hardware. There are two main types of sensors based on the output they produce: digital sensors and analog sensors.

Digital sensors produce an output signal that is a digital representation of the input signal, and has discrete values of magnitude measured at discrete times. A digital sensor must output logic levels that are compatible with the digital receiver. Some standard logic levels include transistor-transistor logic (TTL) and emitter-coupled logic (ECL). Examples of digital sensors include switches and position encoders.

Analog sensors produce an output signal that is directly proportional to the input signal, and is continuous in both magnitude and in time. Most physical variables such as temperature, pressure, and acceleration are continuous in nature and are readily measured with an analog sensor. For example, the temperature of an automobile cooling system and the acceleration produced by a child on a swing all vary continuously.

The sensor to be used depends on the phenomena to be measured. Some common analog sensors and the physical variables they measure are listed below.

| Sensor                                 | Physical Variable |  |

|----------------------------------------|-------------------|--|

| Accelerometer                          | Acceleration      |  |

| Microphone                             | Pressure          |  |

| Pressure gauge                         | Pressure          |  |

| Resistance temperature<br>device (RTD) | Temperature       |  |

| Strain gauge                           | Force             |  |

| Thermocouple                           | Temperature       |  |

#### **Table 2.1-Common Analog Sensors**

When choosing the best analog sensor to use, we must match the characteristics of the physical variable we are measuring with the characteristics of the sensor. The two most important sensor characteristics are:

- The sensor output

- The sensor bandwidth

#### **Sensor Output**

The output from a sensor can be an analog signal or a digital signal, and the output variable is usually a voltage although some sensors output current.

#### • Current Signals

Current is often used to transmit signals in noisy environments because it is much less affected by environmental noise. The full scale range of the current signal is often either 4-20 mA or 0-20 mA. A 4-20 mA signal has the advantage that even at minimum signal value, there should be a detectable current flowing. The absence of this indicates a wiring problem.

Before conversion by the analog input subsystem, the current signals are usually turned into voltage signals by a current-sensing resistor. The resistor should be of high precision, perhaps 0.03% or 0.01% depending on the resolution of hardware. Additionally, the voltage signal should

match the signal to an input range of the analog input hardware. For 4-20 mA signals, a 50 ohm resistor will give a voltage of 1 V for a 20 mA signal by Ohm's law.

#### • Voltage Signals

The most commonly interfaced signal is a voltage signal. For example, thermocouples, strain gauges, and accelerometers all produce voltage signals. There are three major aspects of a voltage signal that is needed to be considered:

1. Amplitude: If the signal is smaller than a few millivolts, then the signal should be amplified. If it is larger than the maximum range of analog input hardware (typically  $\pm 10$  V), it has to be divided down using a resistor network. The amplitude is related to the sensitivity (resolution) of hardware.

2. Frequency: Whenever data is acquired, the highest frequency to be measured should be decided. The highest frequency component of the signal determines how often the input should be sampled. If there is more than one input, and only one analog input subsystem, then the overall sampling rate goes up in proportion to the number of inputs. Higher frequencies may be present as noise, which can be removed by filtering the signal before it is digitized.

If the input signal is sampled at least twice as fast as the highest frequency component, then that signal will be uniquely characterized. However, this rate may not mimic the waveform very closely. For a rapidly varying signal, sampling rate of roughly 10 to 20 times the highest frequency is needed to get an accurate picture of the waveform. For slowly varying signals, the minimum time for a significant change in the signal is needed to be considered.

The frequency is related to the bandwidth of measurement. Bandwidth is discussed in the next section.

**3. Duration:** How long should the signal be sampled? If the data is to be stored in memory or to a disk file, then the duration determines the storage resources required. The format of the stored data also affects the amount of storage space required. For example, data stored in ASCII format takes more space than data stored in binary format.

#### Sensor Bandwidth

In a real-world data acquisition experiment, the physical phenomena to be measured have expected limits. For example, the temperature of automobile's cooling system varies continuously between its low limit and high limit. The temperature limits, as well as how rapidly the temperature varies between the limits, depends on several factors including habit of driving, the weather, and the condition of the cooling system. The expected limits may be readily approximated, but there are an infinite number of possible temperatures that can be measured at a given time. (As explained in section 2.2.2-Quantization on page 16, these unlimited possibilities are mapped to finite set of values by data acquisition hardware.)

The *bandwidth* is given by the range of frequencies present in the signal being measured. The bandwidth can also be thought as being related to the rate of change of the signal. A slowly varying signal has a low bandwidth, while a rapidly varying signal has a high bandwidth. To properly measure the physical phenomena of interest, the sensor bandwidth must be compatible with the measurement bandwidth.

Sensors need to be used with the widest possible bandwidth when making any physical measurement. This is the one way to ensure that the basic measurement system is capable of responding linearly over the full range of interest. However, the wider the bandwidth of the sensor, the more concern should be to eliminating sensor response to unwanted frequency components.

#### 2.1.3-Signal Conditioning

Sensor signals are often incompatible with data acquisition hardware. To overcome this incompatibility, the sensor signal must be conditioned. The type of signal conditioning depends on the sensor being used. For example, a signal may have small amplitude and require amplification, or it may contain unwanted frequency components and require filtering. Common ways to condition signals include:

- Amplification

- Filtering

- Electrical isolation

- Multiplexing

- Excitation source

#### Amplification

Low-level signals – less than around 100 millivolts – usually need to be amplified. High level signals may also require amplification depending on the input range of the analog input subsystem.

For example, the output signal from a thermocouple is small and must be amplified before it is digitized. Signal amplification allows reduction in noise and use of the full range of hardware, thereby increasing the resolution of the measurement.

#### Filtering

Filtering removes unwanted noise from the signal of interest. A noise filter is used on slowly varying signals such as temperature to attenuate higher frequency signals that can reduce the accuracy of measurement.

Rapidly varying signals such as vibration often require a different type of filter known as an antialiasing filter. An antialiasing filter removes undesirable higher frequencies that may lead to erroneous measurements.

#### **Electrical Isolation**

If the signal of interest may contain high-voltage transients that could damage the computer, then the sensor signals should be electrically isolated from the computer for safety purposes.

Electrical isolation can also be used to ensure that the readings from the data acquisition hardware are not affected by differences in ground potentials. For example, when the hardware device and the sensor signal are each referenced to ground, problems occur if there is a potential difference between the two grounds. This difference can lead to a *ground loop*, which may lead to erroneous measurements. Using electrically isolated signal conditioning modules eliminates the ground loop and ensures that the signals are accurately represented.

#### Multiplexing

A common technique for measuring several signals with a single measuring device is multiplexing.

Signal conditioning devices for analog signals often provide multiplexing for use with slowly changing signals such as temperature. This is in addition to any built-in multiplexing on the DAQ board. The A/D converter samples one channel, switches to the next channel and samples it, switches to the next channel, and so on. Because the same A/D converter is sampling many

channels, the effective sampling rate of each individual channel is inversely proportional to the number of channels sampled.

Care should be taken when using multiplexers so that the switched signal has sufficient time to settle.

#### **Excitation Source**

Some sensors require an excitation source to operate. For example, strain gauges, and resistive temperature devices (RTDs) require external voltage or current excitation. Signal conditioning modules for these sensors usually provide the necessary excitation. RTD measurements are usually made with a current source that converts the variation in resistance to a measurable voltage.

#### 2.1.4-Computer

The computer provides a processor, a system clock, a bus to transfer data, and memory and disk space to store data.

The processor controls how fast data is accepted by the converter. The system clock provides time information about the acquired data. Recording sensor reading is generally not enough. It is also needed to know when that measurement occurred.

Data is transferred from the hardware to system memory via dynamic memory access (DMA) or interrupts. DMA is hardware controlled and therefore extremely fast. Interrupts may be slow due to the latency time between when a board requests interrupt servicing and when the computer responds. The maximum acquisition rate is also determined by the computer's bus architecture.

#### 2.1.5-Software

Regardless of the hardware being used, information must be sent to the hardware and information should be received from the hardware. Configuration information is sent to the hardware such as the sampling rate, and information is received from the hardware such as data, status messages, and error messages. The information needs to be supplied to the hardware so that it can be integrated with other hardware and with computer resources. This information exchange is accomplished with software.

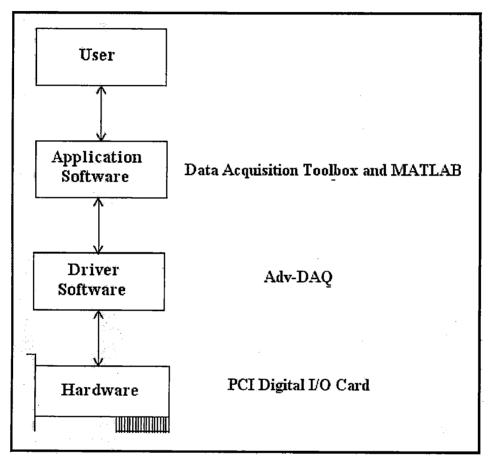

There are two kinds of software:

- Driver software

- Application software

For example, suppose the Data Acquisition Toolbox is being used with an Advantech PCI-1751 48-bit Digital Input/Output Card and its associated Adv-DAQ driver.

The relationship between us, the driver software, the application software, and the hardware is shown below.

Figure 2.3-Relationship between User, Driver Software,

#### Application Software and Hardware

The diagram illustrates that information is supplied to the hardware, and information is received from the hardware.

#### **Driver Software**

For data acquisition device, there is associated driver software that must be used. Driver software allows accessing and controlling the capabilities of hardware. Among other things, basic driver software allows to:

- Bring data on to and get data off of the board

- Control the rate at which data is acquired

- Integrate the data acquisition hardware with computer resources such as processor interrupts, DMA, and memory

- Integrate the data acquisition hardware with signal conditioning hardware

- Access multiple subsystems on a given data acquisition board

- Access multiple data acquisition boards

#### **Application Software**

Application software provides a convenient "front-end" to the driver software. Basic application software allows us to:

- Report relevant information such as the number of samples acquired

- Generate events

- Manage the data stored in computer memory

- Condition a signal

- Plot acquired data

# 2.2-The Analog Input Subsystem

Many data acquisition hardware devices contain one or more subsystems that convert (digitize) real-world sensor signals into numbers computer can read. Such devices are called analog input subsystems (AI subsystems, A/D converters, or ADCs). After the real world signal is digitized, it can be analyzed, it can be stored in system memory, or it can be stored to a disk file.

The function of the analog input subsystem is to *sample* and *quantize* the analog signal using one or more *channels*. The channel can be thought as a path through which the sensor signal travels. Typical analog input subsystems have eight or 16 input channels available. After data is sampled and quantized, it must be transferred to system memory.

Analog signals are continuous in time and in amplitude (within predefined limits). Sampling takes a "snapshot" of the signal at discrete times, while quantization divides the voltage (or current) value into discrete amplitudes. Sampling, quantization, channel configuration, and transferring data from hardware to system memory are discussed below.

#### 2.2.1-Sampling

Sampling takes a "snapshot" of the sensor signal at discrete times. For most applications, the time interval between samples is kept constant (for example, sample every millisecond) unless externally clocked.

For most digital converters, sampling is performed by a sample and hold (S/H) circuit. An S/H circuit usually consists of a signal buffer followed by an electronic switch connected to a capacitor. The operation of an S/H circuit follows these steps:

- 1. At a given sampling instant, the switch connects the buffer and capacitor to an input.

- 2. The capacitor is charged to the input voltage.

- 3. The charge is held until the A/D converter digitizes the signal.

- 4. For multiple channels connected (multiplexed) to one A/D converter, the previous steps are repeated for each input channel.

- 5. The entire process is repeated for the next sampling instant.

Hardware can be divided into two main categories based on how signals are sampled: *scanning* hardware, which samples input signals sequentially, and *simultaneous sample and hold* (SS/H) hardware, which samples all signals at the same time. These two types of hardware are discussed below.

#### **Scanning Hardware**

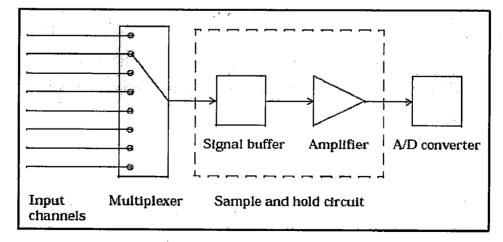

Scanning hardware samples a single input signal, converts that signal to a digital value, and then repeats the process for every input channel used. In other words, each input channel is sampled sequentially. A *scan* occurs when each input in a group is sampled once. As shown below, data acquisition device should have one A/D converter that is multiplexed to multiple input channels.

Figure 2.4-ADC with Multiplexer

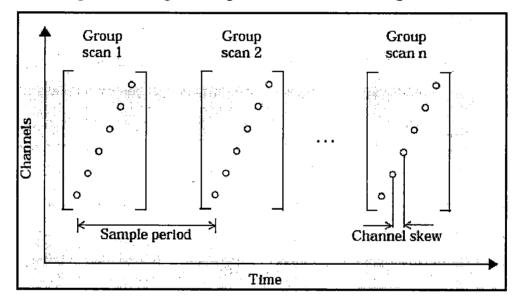

Therefore, if the multiple channels are used, those channels cannot be sampled simultaneously and a time gap exists between consecutive sampled channels. This time gap is called the *channel skew*. The channel skew can be thought as the time it takes the analog input subsystem to sample a single channel.

Additionally, the maximum sampling rate hardware is rated at typically applies for one channel. Therefore, the maximum sampling rate per channel is given by the formula:

Maximum Sampling rate per channel= (Maximum Board Rate)/(No of channels scanned)

Typically, this maximum rate can be achieved only under ideal conditions. In practice, the sampling rate depends on several characteristics of the analog input subsystem including the settling time and the gain, as well as the channel skew. The sample period and channel skew for a multichannel configuration using scanning hardware is shown in Figure 2.3.

Figure 2.5-Plot of Channels and Time using Scanning Hardware

If the channel skew can not be tolerated in an application, then the hardware that allows simultaneous sampling of all channels must be used. Simultaneous sample and hold hardware is discussed in the next section.

#### Simultaneous Sample and Hold Hardware

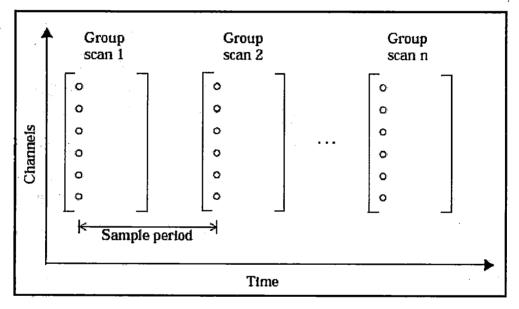

Simultaneous sample and hold (SS/H) hardware samples all input signals at the same time and holds the values until the A/D converter digitizes all the signals. For high-end systems, there can be a separate A/D converter for each input channel.

For example, suppose it is needed to simultaneously measure the acceleration of multiple accelerometers to determine the vibration of some device under test. To do this, SS/H hardware must be used since it does not have a channel skew. In general, SS/H hardware is used if sensor signal changes significantly in a time that is less than the channel skew, or if transfer function is to be used or frequency domain correlation is to be performed.

The sample period for a multichannel configuration using SS/H hardware is shown in Figure 2.6. Note that there is no channel skew.

Figure 2.6-Plot of Channels and Time using SS/H Hardware

#### 2.2.2-Quantization

As discussed in the previous section, sampling takes a snapshot of the input signal at an instant of time. When the snapshot is taken, the sampled analog signal must be converted from a voltage value to a binary number that the computer can read. The conversion from infinitely precise amplitude to a binary number is called *quantization*.

During quantization, the A/D converter uses a finite number of evenly spaced values to represent the analog signal. The number of different values is determined by the number of bits used for the conversion. Most modern converters use 12 or 16 bits. Typically, the converter selects the digital value that is closest to the actual sampled value.

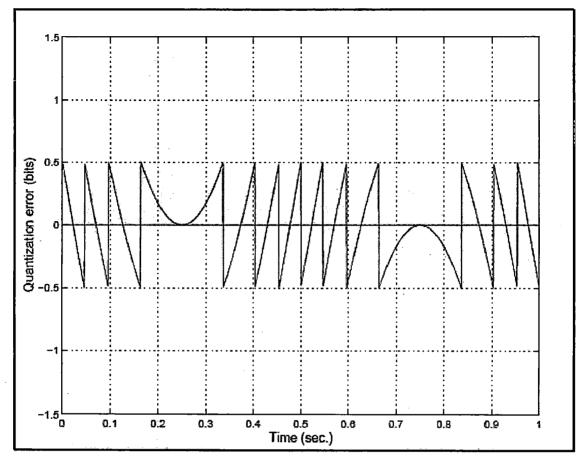

The Figure 2.7 shows a 1 Hz sine wave quantized by a 3-bit A/D converter.

Figure 2.7-Sine Wave Quantized by ADC

The number of quantized values is given by  $2^3 = 8$ , the largest representable value is given by  $111 = 2^2 + 2^1 + 2^0 = 7.0$ , and the smallest representable value is given by 000 = 0.0.

#### **Quantization Error**

There is always some error associated with the quantization of a continuous signal. Ideally, the maximum quantization error is  $\pm 0.5$  least significant bits (LSBs), and over the full input range, the average quantization error is zero.

As shown in Figure 2.8, the quantization error for the previous sine wave is calculated by subtracting the actual signal from the quantized signal.

Figure 2.8-Plot Quantization Error and Time

#### **Input Range and Polarity**

The *input range* of the analog input subsystem is the span of input values for which a conversion is valid. Input range can be changed by selecting a different *gain* value. For example, National Instruments' AT-MIO-16E-1 board has eight gain values ranging from 0.5 to 100. Many boards include a programmable gain amplifier that allows changing the device gain through software.

When an input signal exceeds the valid input range of the converter, an *overrange* condition occurs. In this case, most devices saturate to the largest representable value, and the converted data is almost definitely incorrect. The gain setting affects the precision of measurement – the higher (lower) the gain value, the lower (higher) the precision.

An analog input subsystem can typically convert both *unipolar* signals and *bipolar* signals. A unipolar signal contains only positive values and zero, while a bipolar signal contains positive values, negative values, and zero. Unipolar and bipolar signals are depicted below. Refer to the Figure 2.7 on page 17 in section 2.2.2 for an example of a unipolar signal.

In many cases, the signal polarity is a fixed characteristic of the sensor and the input range must be configured to match this polarity.

As it can be seen, it is crucial to understand the range of signals expected from sensor so that the input range of the analog input subsystem can be configured to maximize resolution and minimize the chance of an overrange condition.

#### How Are Acquired Samples Clocked?

Samples are acquired from an analog input subsystem at a specific rate by a clock. Like any timing system, data acquisition clocks are characterized their resolution and accuracy. Timing resolution is defined as the smallest time interval that can be measured accurately. The timing accuracy is affected by clock *jitter*. Jitter arises when a clock produces slightly different values for a given time interval.

For any data acquisition system, there are typically three clock sources that can be used: the onboard data acquisition clock, the computer clock, or an external clock. The Data Acquisition Toolbox supports all of these clock sources, depending on the requirements of the hardware.

• The Onboard Clock: The onboard clock is typically a timer chip on the hardware board that is programmed to generate a pulse stream at the desired rate. The onboard clock generally has high accuracy and low jitter compared to the computer clock. The onboard clock should always be used when the sampling rate is high and when a fixed time interval between samples is required. The onboard clock is referred to as the *internal clock* in this report.

- The Computer Clock: The computer (PC) clock is used for boards that do not possess an onboard clock. The computer clock is less accurate and has more jitter than the onboard clock, and is generally limited to sampling rates below 500 Hz. The computer clock is referred to as the *software clock* in this report.

- External Clock: An external clock is often used when the sampling rate is low and not constant. For example, an external clock source is often used in automotive applications where samples are acquired as a function of crank angle.

#### **2.2.3-Channel Configuration**

The input channels can be configured in any one of these two ways:

- Differential

- Single-ended

The choice of input channel configuration may depend on whether the input signal is *floating* or *grounded*.

A floating signal uses an isolated ground reference and is not connected to the building ground. As a result, the input signal and hardware device are not connected to a common reference, which can cause the input signal to exceed the valid range of the hardware device. To circumvent this problem, the signal must be connected to the onboard ground of the device. Examples of floating signal sources include ungrounded thermocouples and battery devices.

A grounded signal is connected to the building ground. As a result, the input signal and hardware device are connected to a common reference. Examples of grounded signal sources include nonisolated instrument outputs and devices that are connected to the building power system.

Note: For more information about channel configuration, refer to hardware documentation.

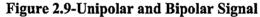

### • Differential Inputs

When the hardware is configured for differential input, there are two signal wires associated with each input signal – one for the input signal and one for the reference (return) signal. The measurement is the difference in voltage between the two wires, which helps reduce noise and any voltage that is common to both wires.

As shown in Figure 2.10, the input signal is connected to the positive amplifier socket (labeled +) and the return signal is connected to the negative amplifier socket (labeled –). The amplifier has a third connector that allows these signals to be referenced to ground.

**Figure 2.10-Differential Input**

It is recommended that the differential inputs should be used under any of these conditions:

- $\checkmark$  The input signal is low level (less than 1 volt).

- $\checkmark$  The leads connecting the signal are greater than 10 feet.

- ✓ The input signal requires a separate ground-reference point or return signal.

- $\checkmark$  The signal leads travel through a noisy environment.

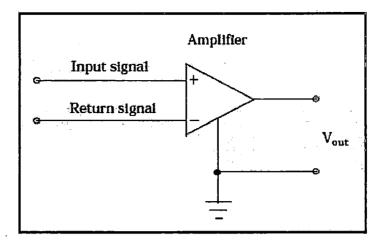

#### • Single-Ended Inputs

When the hardware is configured for single-ended input, there is one signal wire associated with each input signal, and each input signal is connected to the same ground. Single-ended measurements are more susceptible to noise than differential measurements due to differences in the signal paths.

As shown in Figure 2.11, the input signal is connected to the positive amplifier socket (labeled +) and the ground is connected to the negative amplifier socket (labeled –).

Figure 2.11-Single Ended Input

It is suggested that single-ended inputs should be used under any of these conditions:

- $\checkmark$  The input signal is high level (greater than 1 volt).

- $\checkmark$  The leads connecting the signal are less than 10 feet.

- $\checkmark$  The input signal can share a common reference point with other signals.

The differential input connectors should be used for any input signal that does not meet the preceding conditions.

#### 2.2.4-Transferring Data from Hardware to System Memory

The transfer of acquired data from the hardware to system memory follows these steps:

- 1. Acquired data is stored in the hardware's first-in first-out (FIFO) buffer.

- 2. Data is transferred from the FIFO buffer to system memory using interrupts or DMA.

These steps happen automatically. Typically, all that's required from us is some initial configuration of the hardware device when it is installed.

#### The FIFO Buffer

The FIFO buffer is used to temporarily store acquired data. The data is temporarily stored until it can be transferred to system memory. The process of transferring data into and out of an analog input FIFO buffer is given below:

- 1. The FIFO buffer stores newly acquired samples at a constant sampling rate.

- 2. Before the FIFO buffer is filled, the software starts removing the samples. For example, an interrupt is generated when the FIFO is half full, and signals the software to extract the samples as quickly as possible.

- 3. Since servicing interrupts or programming the DMA controller can take up to a few milliseconds, additional data is stored in the FIFO for future retrieval. For a larger FIFO buffer, longer latencies can be tolerated.

- 4. The samples are transferred to system memory via the system bus (for example, PCI bus or AT bus). After the samples are transferred, the software is free to perform other tasks until the next interrupt occurs. For example, the data can be processed or saved to a disk file. As long as the average rates of storing and extracting data are equal, acquired data will not be missed and any application should run smoothly.

#### Interrupts

The slowest but most common method to move acquired data to system memory is for the board to generate an interrupt request (IRQ) signal. This signal can be generated when one sample is acquired or when multiple samples are acquired. The process of transferring data to system memory via interrupts is given below:

- 1. When data is ready for transfer, the CPU stops whatever it is doing and runs special interrupt handler routine that saves the current machine registers, and then sets them to access the board.

- 2. The data is extracted from the board and placed into system memory.

- 3. The saved machine registers are restored, and the CPU returns to the original interrupted process.

The actual data move is fairly quick, but there is a lot of overhead time spent saving, setting up, and restoring the register information. Therefore, depending on specific system, transferring data by interrupts may not be a good choice when the sampling rate is greater than around 5 kHz.

#### **Direct Memory Access (DMA)**

Direct memory access (DMA) is a system whereby samples are automatically stored in system memory while the processor does something else. The process of transferring data via DMA is given below:

- 1. When data is ready for transfer, the board directs the system DMA controller to put it into in system memory as soon as possible.

- 2. As soon as the CPU is able (which is usually very quickly), it stops interacting with the data acquisition hardware and the DMA controller moves the data directly into memory.

- 3. The DMA controller gets ready for the next sample by pointing to the next open memory location.

- 4. The previous steps are repeated indefinitely, with data going to each open memory location in a continuously circulating buffer. No interaction between the CPU and the board is needed.

Computer supports several different DMA channels. Depending on the application, one or more of these channels can be used, For example, simultaneous input and output with a sound card requires one DMA channel for the input and another DMA channel for the output.

### **2.3-Making Quality Measurements**

For most data acquisition applications, the signal produced by a sensor needs to be measured at a specific rate.

In many cases, the sensor signal is a voltage level that is proportional to the physical phenomena of interest (for example, temperature, pressure, or acceleration). If the slowly changing (quasistatic) phenomena like temperature is being measured a slow sampling rate usually suffices. If the rapidly changing (dynamic) phenomena like vibration or acoustic measurements are being measured, a fast sampling rate is required.

To make high-quality measurements, these rules should be followed:

- Maximize the precision and accuracy

- Minimize the noise

- Match the sensor range to the A/D range

#### **2.3.1-Accuracy and Precision**

Whenever measured data is acquired, every effort should be made to maximize its accuracy and precision. The quality of measurement depends on the accuracy and precision of the entire data acquisition system, and can be limited by such factors as board resolution or environmental noise.

In general terms, the *accuracy* of a measurement determines how close the measurement comes to the true value. Therefore, it indicates the correctness of the result. The *precision* of a measurement reflects how exactly the result is determined without reference to what the result means. The *relative precision* indicates the uncertainty in a measurement as a fraction of the result.

For example, suppose a table top is measured with a meter stick and its length is found to be 1.502 meters. This number indicates that the meter stick (and our eyes) can resolve distances down to at least a millimeter. Under most circumstances, this is considered to be a fairly precise measurement with a relative precision of around 1/1500. However, suppose the measurement is performed again and a result of 1.510 meters is obtained. After careful consideration, it is discovered that initial technique for reading the meter stick was faulty because it was not read from directly above. Therefore, the first measurement was not accurate.

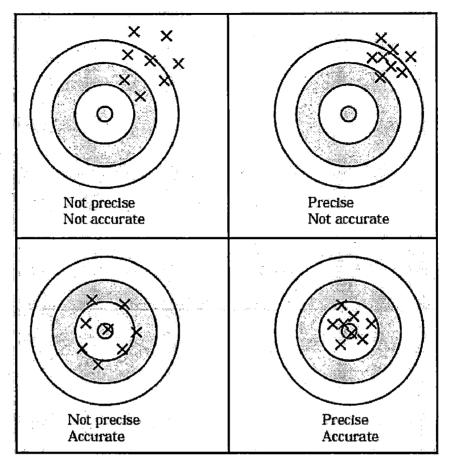

Precision and accuracy are illustrated in Figure 2.12.

Figure 2.12-Precision Vs Accuracy

For analog input subsystems, accuracy is usually limited by calibration errors while precision is usually limited by the A/D converter. Accuracy and precision are discussed in more detail below.

#### Accuracy

Accuracy is defined as the agreement between a measured quantity and the true value of that quantity. Every component that appears in the analog signal path affects system accuracy and performance. The overall system accuracy is given by the component with the worst accuracy.

For data acquisition hardware, accuracy is often expressed as a percent or a fraction of the least significant bit (LSB). Under ideal circumstances, board accuracy is typically  $\pm 0.5$  LSB. Therefore, a 12-bit converter has only 11 usable bits.

Many boards include a programmable gain amplifier, which is located just before the converter input. To prevent system accuracy from being degraded, the accuracy and linearity of the gain must be better than that of the A/D converter. The specified accuracy of a board is also affected

by the sampling rate and the *settling time* of the amplifier. The settling time is defined as the time required for the instrumentation amplifier to settle to a specified accuracy. To maintain full accuracy, the amplifier output must settle to a level given by the magnitude of 0.5 LSB before the next conversion, and is on the order of several tenths of a millisecond for most boards.

Settling time is a function of sampling rate and gain value. High rate, high gain configurations require longer settling times while low rate, low gain configurations require shorter settling times.

#### Precision

The number of bits used to represent an analog signal determines the precision (resolution) of the device. The more bits provided by hardware board, the more precise measurement will be. A high precision, high resolution device divides the input range into more divisions thereby allowing a smaller detectable voltage value. A low precision, low resolution device divides the input range into fewer divisions thereby increasing the detectable voltage value.

The overall precision of data acquisition system is usually determined by the A/D converter, and is specified by the number of bits used to represent the analog signal. Most boards use 12 or 16 bits. The precision of measurement is given by

Precision = one part in  $2^{(number of bits)}$

The precision in volts is given by

Precision = voltage range /  $2^{(number of bits)}$

For example, if a 12-bit A/D converter configured for a 10 volt range are being used, then

Precision =  $10 \text{ volts}/2^{(12)}$

This means that the converter can detect voltage differences at the level of 0.00244 volts (2.44 mV).

## How Are Range, Gain, and Measurement Precision Related?

When the input range and gain of analog input subsystem are configured, the end result should maximize the measurement resolution and minimize the chance of an overrange condition. The actual input range is given by the formula:

## Actual input range = Input range/Gain

The relationship between gain, actual input range, and precision for a Unipolar and bipolar signal having an input range of 10 V is shown in Table 2.2.

| Input Range | Gain | Actual Input Range | Precision (12 Bit A/D) |

|-------------|------|--------------------|------------------------|

| 0 to 10 V   | 1.0  | 0 to 10 V          | 2.44 mV                |

|             | 2.0  | 0 to 5 V           | 1.22 mV                |

|             | 5.0  | 0 to 2 V           | 0.488 mV               |

|             | 10.0 | 0 to 1 V           | 0.244 mV               |

| -5 to 5 V   | 0.5  | -10 to 10 V        | 4.88 mV                |

|             | 1.0  | -6 to 5 V          | 2.44 mV                |

|             | 2.0  | -2.5 to 2.5 V      | 1.22 mV                |

|             | 5.0  | -1.0 to 1.0 V      | 0.488 mV               |

|             | 10.0 | -0.5 to 0.5 V      | 0.244 mV               |

Table 2.2-Relationship between Input Range, Gain, and Precision

As shown in the table, the gain affects the precision of measurement. If a gain is selected that decreases the actual input range, then the precision increases. Conversely, if a gain is selected that increases the actual input range, then the precision decreases. This is because the actual input range varies but the number of bits used by the A/D converter remains fixed.

Note With the Data Acquisition Toolbox, the range and gain need not to be specified. Instead, the actual input range desired is specified.

#### 2.3.2-Noise

Noise is considered to be any measurement that is not part of the phenomena of interest. Noise can be generated within the electrical components of the input amplifier (internal noise), or it can be added to the signal as it travels down the input wires to the amplifier (external noise). Techniques that can be used to reduce the effects of noise are described below.

#### Removing Internal Noise

Internal noise arises from thermal effects in the amplifier. Amplifiers typically generate a few microvolts of internal noise, which limits the resolution of the signal to this level. The amount of noise added to the signal depends on the bandwidth of the input amplifier.

To reduce internal noise, an amplifier with a bandwidth that closely matches the bandwidth of the input signal should be selected.

#### • Removing External Noise

External noise arises from many sources. For example, many data acquisition experiments are subject to 50 Hz noise generated by a.c. power circuits. This type of noise is referred to as *pick-up* or *hum*, and appears as a sinusoidal interference signal in the measurement circuit. Another common interference source is fluorescent lighting. These lights generate an arc at twice the power line frequency (100 Hz).

Noise is added to the acquisition circuit from these external sources because the signal leads act as aerials picking up environmental electrical activity.

Much of this noise is common to both signal wires. To remove most of this common-mode voltage:

- $\checkmark$  The input channels should be configured in differential mode.

- $\checkmark$  Signal wires should be used that are twisted together rather than separate.

- $\checkmark$  The signal wires should be kept as short as possible.

- ✓ Signal wires should be kept as far as possible from environmental electrical activity.

• Filtering

Filtering also reduces signal noise. For many data acquisition applications, a low-pass filter is beneficial. As the name suggests, a low-pass filter passes the lower frequency components but attenuates the higher frequency components. The cut-off frequency of the filter must be compatible with the frequencies present in the signal of interest and the sampling rate used for the A/D conversion.

A low-pass filter that's used to prevent higher frequencies from introducing distortion into the digitized signal is known as an antialiasing filter if the cut-off occurs at the Nyquist frequency. That is, the filter removes frequencies greater than one-half the sampling frequency. These filters generally have a sharper cut-off than the normal low-pass filter used to condition a signal. Antialiasing filters are specified according to the sampling rate of the system and there must be one filter per input signal.

#### 2.3.3-Matching the Sensor Range and A/D Converter Range

When sensor data is digitized by an A/D converter, these two issues must be considered:

• The expected range of the data produced by sensor. This range depends on the physical phenomena being measured and the output range of the sensor.

• The range of A/D converter. For many devices, the hardware range is specified by the gain and polarity.

The sensor and hardware ranges should be selected such that the maximum precision is obtained, and the full dynamic range of the input signal is covered.

For example, suppose a microphone is being used with a dynamic range of 20 dB to 140 dB and an output sensitivity of 50 mV/Pa. If street noise is being measured in application, then it might be expected that the sound level never exceeds 80 dB, which corresponds to a sound pressure magnitude of 200 mPa and a voltage output from the microphone of 10 mV. Under these conditions, the input range of data acquisition card should be set for a maximum signal amplitude of 10 mV, or a little more.

#### 2.3.4-How Fast Should a Signal Be Sampled?

Whenever a continuous signal is sampled, some information is lost. The key objective is to sample at a rate such that the signal of interest is well characterized and the amount of information lost is minimized.

If the signal is sampled at a rate that is too slow, then the signal is *undersampled*, and *aliasing* can occur. Aliasing can occur for both rapidly varying signals and slowly varying signals. For example, suppose the temperature is being measured once a minute. If the acquisition system is picking up a 50 Hz hum from an a.c power supply, then that hum will appear as constant noise level if it is being sampled at 30 Hz.

Aliasing occurs when the sampled signal contains frequency components greater than one-half the sampling rate. The frequency components could originate from the signal of interest in which case we are undersampling and should increase the sampling rate. The frequency components could also originate from noise in which case we may need to condition the signal using a filter. The rule used to prevent aliasing is given by the *Nyquist theorem*, which states that:

- An analog signal can be uniquely reconstructed, without error, from samples taken at equal time intervals.

- The sampling rate must be equal to or greater than twice the highest frequency component in the analog signal. A frequency of one-half the sampling rate is called the Nyquist frequency.

However, if the input signal is corrupted by noise, then aliasing can still occur.

For example, suppose the A/D converter is configured to sample at a rate of 4 samples per second (4 S/s or 4 Hz), and the signal of interest is a 1 Hz sine wave. Since the signal frequency is one-fourth the sampling rate, then according to the Nyquist theorem, it should be completely characterized. However, if a 5 Hz sine wave is also present, then these two signals cannot be distinguished. In other words, the 1 Hz sine wave produces the same samples as the 5 Hz sine wave when the sampling rate is 4 S/s. This situation is shown in Figure 2.13.

Figure 2.13-Occurance of Aliasing

In a real-world data acquisition environment, it may be needed to condition the signal by filtering out the high frequency components.

Even though the samples appear to represent a sine wave with a frequency of one-fourth the sampling rate, the actual signal could be any sine wave with a frequency of

## $(n \pm 0.25) \times$ Sampling rate

where n is zero or any positive integer. For this example, the actual signal may be at a frequency of 3 Hz, 5 Hz, 7 Hz, 9 Hz, and so on. The relationship is called the *alias* of a signal that may be at another frequency. In other words, aliasing occurs when one frequency assumes the identity of another frequency.

If the input signal is sampled at least twice as fast as the highest frequency component, then that signal may be uniquely characterized but this rate would not mimic the waveform very closely.

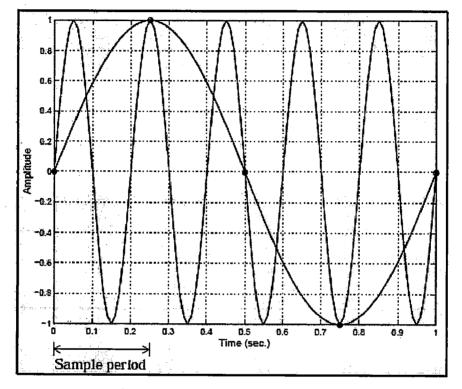

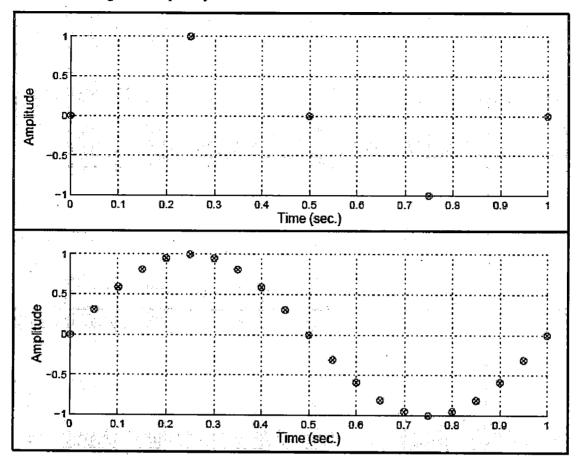

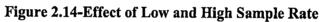

As shown in Figure 2.14, to get an accurate picture of the waveform, a sampling rate of roughly 10 to 20 times the highest frequency is needed.

As shown in the top figure, the low sampling rate produces a sampled signal that appears to be a triangular waveform. As shown in the bottom figure, a higher fidelity sampled signal is produced when the sampling rate is higher. In the latter case, the sampled signal actually looks like a sine wave.

#### **2.3.5-How Can Aliasing be Eliminated?**

The primary considerations involved in antialiasing are the sampling rate of the A/D converter and the frequencies present in the sampled data. To eliminate aliasing, following rules should be obeyed:

- Establish the useful bandwidth of the measurement.

- Select a sensor with sufficient bandwidth.

- Select a low-pass anti-aliasing analog filter that can eliminate all frequencies exceeding this bandwidth.

- Sample the data at a rate at least twice that of the filter's upper cutoff frequency.

## **Chapter-3**

## **DESCRIPTION OF HARDWARE**

#### 3.1- Parts of Hardware

After breaking the large circuits into smaller primitive building blocks large circuits can be understood by simple hand calculations, the bottle-necks in a circuit can easily be seen by circuit understanding. Thereby, circuit topology can be changed to eliminate one bottle-neck at a time, until the requirement specification is fulfilled.

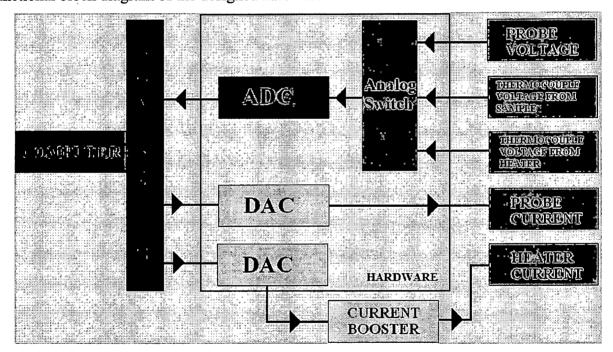

There is, of course, a rather wide range of knowledge to learn, from detailed component properties up to overall circuit performance, before the circuit is design. Figure 3.1 shows the functional block diagram of the designed hardware.

**Figure 3.1-Functional Block Diagram**

The hardware can be divided into following parts

- Circuitry for writing data (DAC)

- Circuitry for selecting channels

- Circuitry for reading data (ADC)

- Circuitry for generating clock

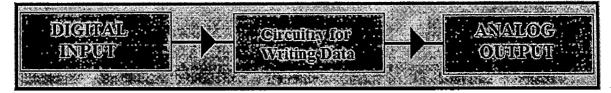

#### **3.2-Circuitry for Writing Digital Data**

Figure 3.2-Digital Input Analog Output

This circuitry mainly consists of following components:

- 1. AD7521

- 2. LM741

- 3. LM336-2.5V

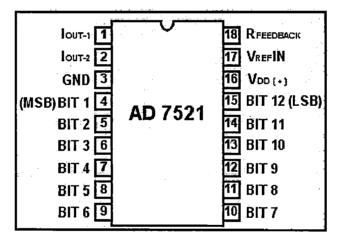

#### 3.2.1-AD7521

The AD7521 is a low cost, monolithic 12-bit multiplying digital to analog converter packaged in an18 pin DIP [1]. The devices use advanced CMOS and thin film technologies providing up to 10 bit accuracy.

The AD7521 operates from +5V to -5V supply and dissipates only 20 mW, including the ladder network.

Figure 3.3-Pin diagram of AD 7521

The AD751 consists of a highly stable thin film R-2R ladder and twelve CMOS current switches on a monolithic chip. Most applications require the addition of only an output operational amplifier [11] and a voltage reference [12].

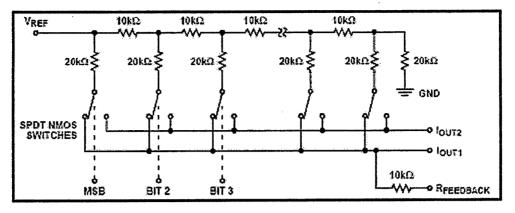

The simplified D/A circuit is shown in Figure 3.4 An inverted R-2R ladder structure is used, that is, the binary weighted currents are switched between the  $I_{OUT1}$  and  $I_{OUT2}$  bus lines, thus maintaining a constant current en each ladder leg independent of the switch state.

#### Figure 3.4-Functional Diagram of AD7521

The DAC AD7521 can be used in two ways: Unipolar Operation and Bipolar Operation. Unipolar operation means that current is unidirectional (either positive or negative) and Bipolar Operation means that current is bidirectional (both positive and negative).

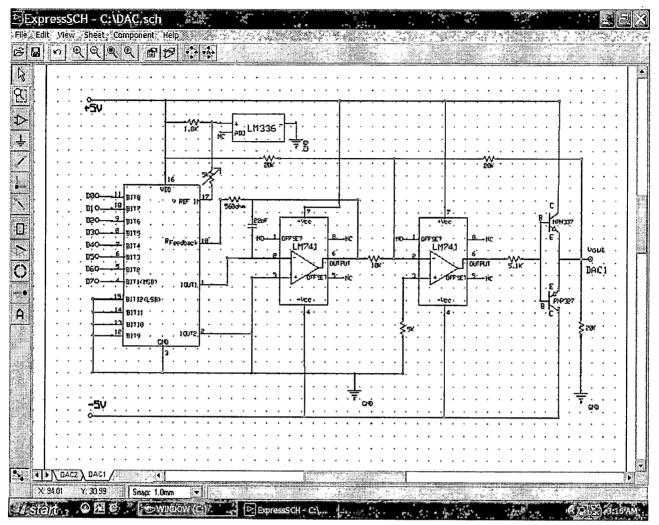

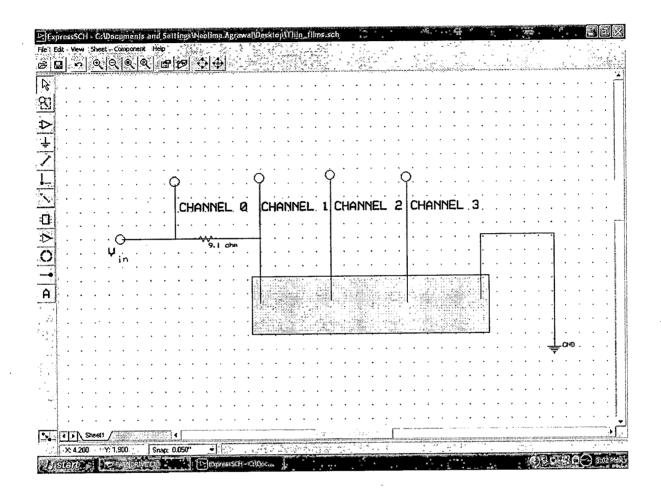

- ×. ExpressSCH - C:\DAC.sch File Edit View: Sheet Component 8 B 1 9 9 9 9 8 B 15 -> +> R 8] +SV ⊅ LM336 Ŧ Ń Į **}**... ^ 9118 nac 19 DIO B177 Π 1220 B176 BB. 030 8115 ÷ La 1340 **D**40 BJ74 1741 133 0 8173 Vout 760 8172 8171(158) 070 វពាក TAC2 **ธ**มา์ 12 งไรซว์ A **ย**เร่ม 1 191710 19179 11 101 0 CHO 51 04C2 ( 0AC1 / 10AG ) \$240 199 199 1 PV X 109.00 Y 100.00 Snap: 1.0mm • WINDOW (C) - ··· ExpressSCH - C:V. K (5 5) 3:17 AM a start

- Unipolar Operation

Figure 3.5-Circuit Diagram for Unipolar Binary Operation

Above figure shows the analog circuit connections required for unipolar binary operation. With a dc reference voltage (positive or negative polarity) applied at pin 17, the circuit is Unipolar D/A converter [7]. The input /output relationship is shown in Table 3.1

| DIGITAL INPUT | ANALOG OUTPUT                         |  |  |

|---------------|---------------------------------------|--|--|

| 1111111111    | V <sub>REF</sub> (1-2 <sup>-N</sup> ) |  |  |

| 100000001     | $V_{\text{REF}} (^{1}/_{2} + 2^{-N})$ |  |  |

| 100000000     | V <sub>REF</sub> /2                   |  |  |

| 0111111111    | $V_{\text{REF}}$ (1/2-2-N)            |  |  |

| 000000001     | V <sub>REF</sub> (2 <sup>-N</sup> )   |  |  |

| 000000000     | 0                                     |  |  |

Table 3.1-Code Table-Unipolar Binary Operation

R1 at pin 17 provides full scale trim capability (i.e. load the DAC register to 11 1111 1111, adjust R1 for  $V_{OUT} = V_{REF} (1 - 2^{-10})$ . Alternatively, full scale can be adjusted by omitting R1 and R2 and trimming the reference voltage magnitude.

C1 Phase compensation (10 to 25 pF) may be required for stability when using high speed amplifiers.

Amplifier A1 should be selected or trimmed to provide  $V_{OS} \leq 10\%$  of the voltage resolution at  $V_{OUT}$ . Additionally, the amplifier should exhibit a bias current which is low over the temperature range of interest (bias current causes output offset at  $V_{OUT}$  equal to  $I_B$  times the DAC feedback resistance, nominally 15 k $\Omega$ ).

## • Bipolar Operation

Figure 3.6-Circuit Diagram for Bipolar Operation

Figure 3.6 illustrate the circuitry for bipolar operation. With a dc reference (positive or negative polarity) the circuit provides offset binary operation [7]. The input /output relationship is shown in Table 3.2

| DIGITAL INPUT | ANALOG OUTPUT                              |

|---------------|--------------------------------------------|

| 1111111111    | -V <sub>REF</sub> (1-2 <sup>-(N-1)</sup> ) |

| 100000001     | -V <sub>REF</sub> (2 <sup>-(N-1)</sup> )   |

| 100000000     | 0                                          |

| 0111111111    | V <sub>REF</sub> (2 <sup>-(N-1)</sup> )    |

| 000000001     | V <sub>REF</sub> (1-2 <sup>-(N-1)</sup> )  |

| 000000000     | V <sub>REF</sub>                           |

Table 3.2-Code Table-Bipolar (Offset Binary) Operation

With the DAC register loaded to 10 0000 0000, adjust R1 for  $V_{OUT} = 0V$  (alternatively, one can omit R1 and R2 and adjust the ratio of R3 to R4 for  $V_{OUT}=0V$ ). Full scale trimming can be accomplished by adjusting the amplitude of  $V_{REF}$  or by varying the value of R5.

As in Unipolar operation, A1 must be chosen for low  $V_{OS}$  and low I<sub>B</sub>. R3,R4 and R5 must be selected for matching and tracking/ Mismatch of 2R3 to R4 causes both offset and Full Scale error. Mismatch of R5 to R4 or 2R3 causes full scale error. C1 phase compensation (10pF to 25pF) may be required for stability.

# **3.3-Circuitry for Selecting Channels**

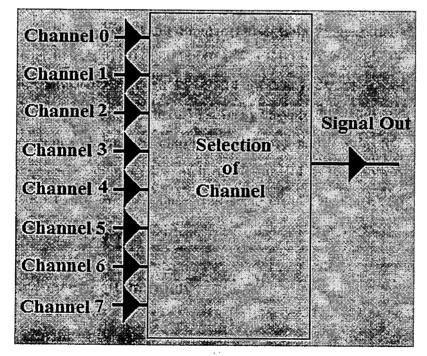

**Figure 3.7-Selection of Channels**

This circuitry mainly consists of following components:

- 1. LS154

- 2. CD4066

- 3. LS04

## 3.3.1-LS154

LS154 is a 4-line-to-16-line decoder; it utilizes TTL circuitry to decode four binary-coded inputs into one of sixteen mutually exclusive outputs when both the strobe inputs, G1 and G2, are low [5]. The demultiplexing function is performed by using the 4 input lines to address the output line, passing data from one of the strobe inputs with the other strobe input low. When either strobe input is high, all outputs are high. All inputs are buffered and input clamping diodes are provided to minimize transmission-line effects and thereby simplify system design.

By grounding Y8 to Y15 and D we have used it as a 3-line to 8-line decoder

| Y0 1                                                                                                            | 24 Vcc |

|-----------------------------------------------------------------------------------------------------------------|--------|

| Y1 2                                                                                                            | 23 A   |

| ¥23                                                                                                             | 22 B   |

| Y3 4                                                                                                            | 21 C   |

| ¥4 <b>5</b>                                                                                                     | 20 D   |

| Y5 6 LS154                                                                                                      | 19 G2  |

| ¥6 7                                                                                                            | 18 G1  |

| Y7 8                                                                                                            | 17 Y15 |

| Y8 9                                                                                                            | 16 Y14 |

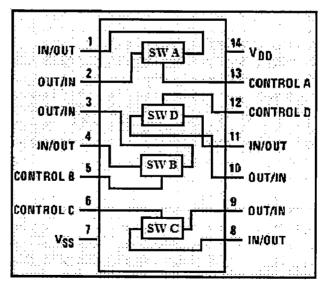

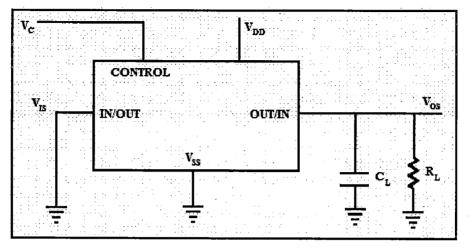

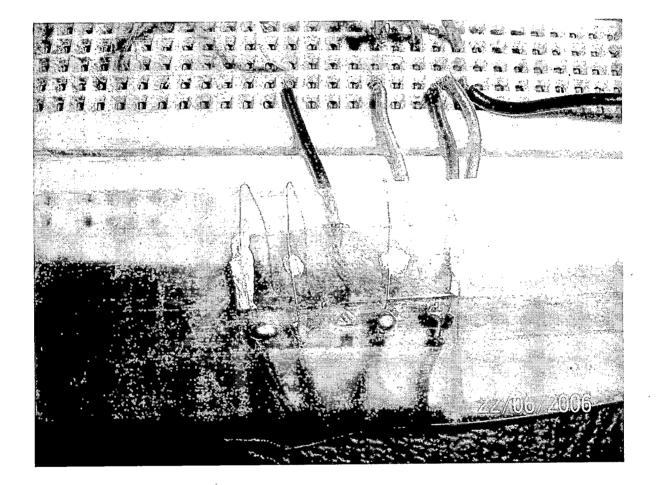

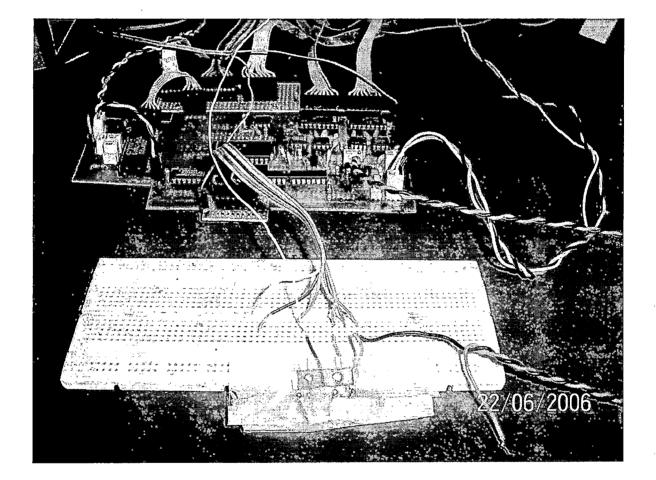

| <b>Y9 10</b>                                                                                                    | 15 Y13 |