# HIGH PERFORMANCE ADVANCE ENCRYPTION STANDARD IMPLEMENTATION ON FPGA

# **A DISSERTATION**

# Submitted in partial fulfillment of the requirements for the award of the degree

of

# **MASTER OF TECHNOLOGY**

in

# ELECTRONICS AND COMPUTER ENGINEERING (With Specialization in Semiconductor Devices & VLSI Technology)

By

# VISHWANATH PATEL

DEPARTMENT OF ELECTRONICS AND COMPUTER ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE -247 667 (INDIA) JUNE, 2009

# **CANDIDATE'S DECLARATION**

I hereby declare that the work, which is presented in this thesis, entitled "HIGH PERFORMANCE ADVANCE ENCRYPTION STANDARD IMPLEMENTATION ON FPGA", being submitted in partial fulfillment of the requirements for the award of the degree of MASTER OF TECHNOLOGY with specialization in SEMICONDUCTOR DEVICES AND VLSI TECHNOLOGY in department of Electronics & Computer Engineering, Indian Institute of Technology, Roorkee is an authentic record of my won work carried out from July 2008 to June 2009, under the guidance and supervision of Dr. R. C. Joshi and Dr. A. K. Saxena, professors, Department of Electronics & Computer Engineering, Indian Institute of Technology, Roorkee, INDIA.

The result embodied in this dissertation, have not submitted for the award of any other Degree or Diploma.

Date: 08/06/09 Place: Roorkee

(Vishwanath Patel)

# CERTIFICATE

This is to certify that the statement made by the candidate is correct to best my knowledge and belief.

(Dr. R. C. Joshi) Professor

gade

(Dr. A. K. Saxena) Professor

Department of Electronics & Computer Engineering, Indian Institute of Technology Roorkee,

Roorkee-247667, INDIA

Date: **969** Place: Roorkee

# ACKNOWLEDGEMENT

It is my privilege and pleasure to express my profound sense of respect, gratitude and indebtedness to my guides, **Dr. R. C. Joshi** and **Dr. A. K. Saxena**, Professors, department of electronics and computer engineering, Indian Institute of Technology Roorkee, for their inspiration, guidance, constructive criticisms and encouragement throughout this dissertation work. The valuable hours of discussion and suggestions that I had with them have undoubtedly helped in supplementing my thoughts in the right direction for attaining the desired objective. I consider myself extremely fortunate for having got the opportunity to learn and work under their able supervision over the entire period of my association with them.

Thanks are due to lab staff of VLSI Design and Sponsored Project Laboratory, Department of Electronics & Computer Engineering, Indian Institute of Technology Roorkee for providing necessary facilities and support.

I am greatly indebted to all my friends, who have graciously applied themselves to the task of helping me with ample moral supports and valuable suggestions. Finally, I would like to extend my gratitude to all those persons who directly or indirectly helped me in the process and contributed towards this work.

# ABSTRACT

In today's world most of the communication is done using electronic media. Data Security plays a vital role in such communication. In October 2000, the National Institute of Standards and Technology (NIST) selected the Rijndael as the Advanced Encryption Standard (AES) algorithm to replace the old Data Encryption Standard (DES). Till then four modes has been proposed by NIST.

A fourth and recent mode of operation of AES proposed by NIST in November 2006, SP800-38D, Galois/Counter Mode of Operation (GCM), that provide not only data security through encryption but also massage authentication.

Before GCM, SP800-38A only provided confidentiality and SP800-38B provided authentication. SP800-38C provided confidentiality using the counter mode and authentication. However the authentication technique in SP800-38C was not parallelizable and slowed down the throughput of the cipher. Hence, none of these three recommendations were suitable for high speed network and computer system applications.

This work includes, demonstration and analysis of FPGA architectures for, SP800-38A (AES-ECB) and SP800-38D (AES-GCM) modes of AES algorithm with the view of enhancing their performance. AES-GCM is a complex unit, AES-ECB (Electronic Code-Book) is used as one of its internal component; so this thesis first presents efficient iterative and fully pipelined based hardware architectures for AES-ECB mode and then finally presents fully pipelined and parallelized hardware architecture for AES-GCM.

Area optimization in above stated designs has been approached through implementing Sboxes of AES by Composite Field Arithmetic (CFA) technique and their comparison is made with respective LUTs (Look-Up tables) based designs.

Since modular multiplier is a very important unit of AES-GCM, which not only very crucial to determine speed of design but also covers 50% of overall area of the design, there are two multipliers has been analyzed and used in final AES-GCM design.

In this thesis, all the designs are implemented on multi-core Xilinx's virtex-4 FPGA platform.

# CONTENTS

| Title   Page                                                    | No.  |

|-----------------------------------------------------------------|------|

| Candidate's Declaration                                         | i    |

| Certificate                                                     | i    |

| Acknowledgement                                                 | ii   |

| Abstract                                                        | iii  |

| Contents                                                        | iv   |

| List of Tables                                                  | viii |

| List of Figures                                                 | ix   |

| Chapter 1 Introduction and Statement of the Problem             | 1    |

| 1.1 Introduction                                                | 1    |

| 1.2 Statement of the problem                                    | 3    |

| 1.4 Organization of Thesis                                      | 3    |

| Chapter 2 Historical Review and General Consideration           | 6    |

| 2.1 Historical Review.                                          | 6    |

| 2.2 Mathematical Background                                     | 7    |

| 2.2.1 Finite Fields                                             | 7    |

| 2.2.2 Operations over Binary Finite Fields GF (2 <sup>m</sup> ) | 8    |

| 2.2.3 Composite Field Arithmetic                                | 11   |

| 2.3 Field Programmable Gate Arrays (FPGA)                       | 13   |

| 2.3.1 Advantages of FPGA in Cryptographic Applications          | 14   |

| 2.3.2 Virtex-4                                                  | 15   |

| Chapter 3 Security Standard                                     | 17   |

| 3.1 Advanced Encryption Standard (AES)                          | 17   |

| 3.1.1 AES Cipher                                                | 19   |

| 3.1.2 Byte Substitution (SubBytes)                              | 19   |

| 3.1.3 Shift Rows                                                | 20   |

| 3.1.4 Mix Columns                                         | 21 |

|-----------------------------------------------------------|----|

| 3.1.5 Key Schedule                                        | 22 |

| 3.2 Confidentiality Mode of Operation Background          | 23 |

| 3.2.1 Electronic Codebook Mode (ECB)                      | 23 |

| 3.2.2 Counter Mode (CTR)                                  | 24 |

| 3.3 Galois/Counter Mode (GCM)                             | 26 |

| 3.3.1 Block Cipher                                        | 26 |

| 3.3.2 Input and Output Data                               | 26 |

| 3.3.3 Types of Applications of GCM                        | 27 |

| 3.3.4 GHASH Function                                      | 28 |

| 3.3.5 GCTR Function                                       | 29 |

| 3.3.6 GCM Specification                                   | 31 |

| Chapter 4 Parallel Multiplier Designs for GCM             | 35 |

| 4.1 Mastrovito Multiplier                                 | 35 |

| 4.1.1 Matrix Vector Product                               | 35 |

| 4.1.2 Mastrovito Multiplier Design using MVP              | 36 |

| 4.2 Karatsuba Algorithm Sub-quadratic Multiplier          | 37 |

| 4.2.1 KA Multiplier Formulation                           | 38 |

| 4.2.2 Modulo Reduction                                    | 39 |

| 4.2.3 KA Multiplier Design for GCM                        | 40 |

| 4.3 FPGA Implementation Results                           | 42 |

| Chapter 5 FPGA Implementation of AES-ECB Architectures    | 43 |

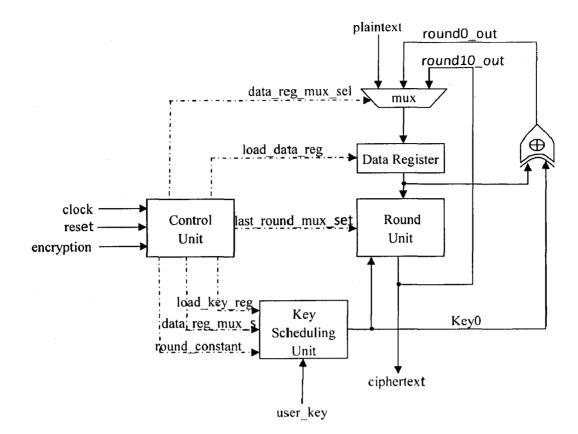

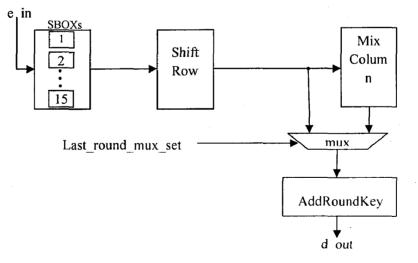

| 5.1 Compact Single Round AES Design                       | 43 |

| 5.1.1 Single Round Compact Design                         | 43 |

| 5.1.2 Composite Field Arithmetic based SubBytes function  | 46 |

| 5.1.3 Implementation Results                              | 47 |

| 5.1.4 Performance Comparison with other Designs           | 47 |

| 5.2 High Speed Sub-pipelined Design                       | 49 |

| 5.2.1 The AES Algorithm And Its Subpipelined Architecture | 49 |

|                                                           |    |

| V .                                                       |    |

|                                                           |    |

| 5.2.2 Detailed Hardware Implementation Architectures   | 50 |

|--------------------------------------------------------|----|

| 5.2.3 Implementation Result and Comparison             | 57 |

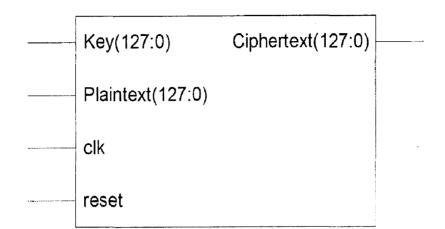

| Chapter 6 FPGA Implementation of AES-GCM Architecture  | 60 |

| 6.1 Modules Design                                     | 60 |

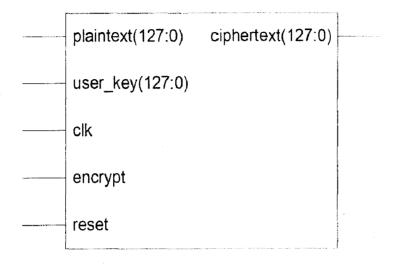

| 6.1.1 AES Module                                       | 60 |

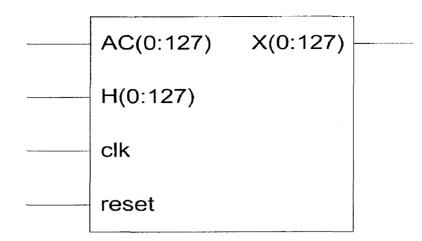

| 6.1.2 GHASH Module                                     | 62 |

| 6.2 High Speed Hardware Implementation of AES-GCM      | 64 |

| 6.2.1 Format of Data Packet of IPsec ESP               | 64 |

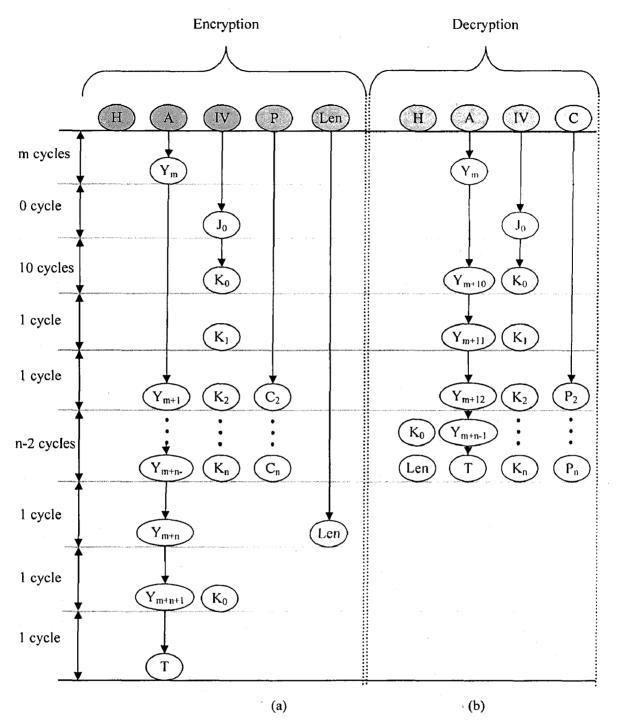

| 6.2.2 Data Flow in GCM                                 | 65 |

| 6.2.3 Hardware Implementation Bidirectional GCM        | 67 |

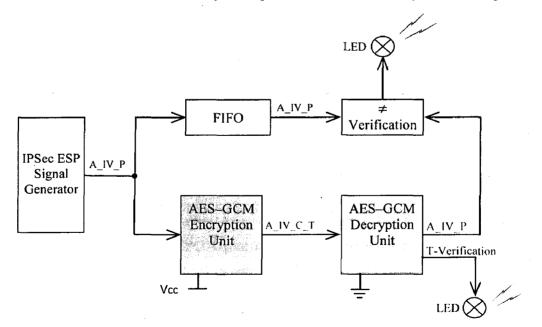

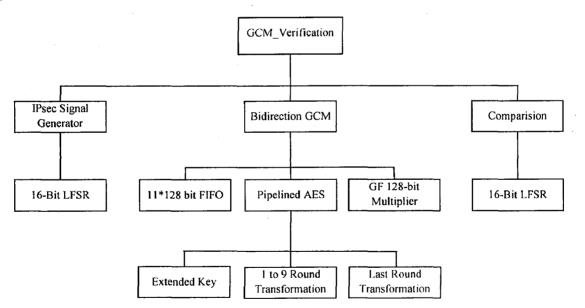

| 6.3 Verification of AES-GCM Functionality              | 72 |

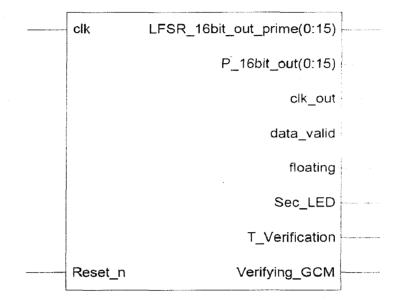

| 6.3.1 IPsec Signal Generator                           | 72 |

| 6.3.2 Verifying Both AES-GCM-AE and AES-GCM-AD on FPGA | 73 |

| Chapter 7 Conclusion and Future Work                   | 75 |

| 7.1 Conclusion                                         | 75 |

| 7.2 Future Work                                        | 76 |

| References                                             | 77 |

| Papers Published                                       | 81 |

| Appendices                                             | 82 |

| Appendix A : Test-Vectors for AES-GCM                  | 82 |

| Appendix B : Simulation Result of Implemented Designs  | 84 |

|                                                        |    |

# LIST OF TABLES

| Table No. | Page No.                                                           |    |

|-----------|--------------------------------------------------------------------|----|

| Table 2.1 | : Resources of Virtex-4 FPGA Family Members                        | 15 |

| Table 4.1 | : Area of KA Multiplier with varied ending conditions              | 41 |

| Table 4.2 | : Multiplier's Place and Route Results Summary                     | 42 |

| Table 5.1 | : Synthesis and Place & Route results of compact AES designs       | 48 |

| Table 5.2 | : The logic and routing delay of compact AES designs               | 48 |

| Table 5.3 | : Performance comparison of compact AES designs                    | 48 |

| Table 5.4 | : Gate counts and critical paths functional blocks in the SubBytes |    |

|           | Transformation [17]                                                | 52 |

| Table 5.5 | : Comparison of FPGA implementation of the AES algorithm           | 58 |

| Table 5.6 | : Power consumed                                                   | 58 |

| Table 6.1 | : Comparison between Iterative and Pipelined AES                   | 61 |

| Table 6.2 | : Comparison between different GHASH architectures                 | 63 |

| Table 6.3 | : Place and Route Results Summary of other important units of AES- |    |

|           | GCM                                                                | 70 |

| Table 6.4 | : Full AES-GCM's Place and Route Results Summary                   | 70 |

| Table 6.5 | : Power analysis of the designs                                    | 70 |

# LIST OF FIGURES

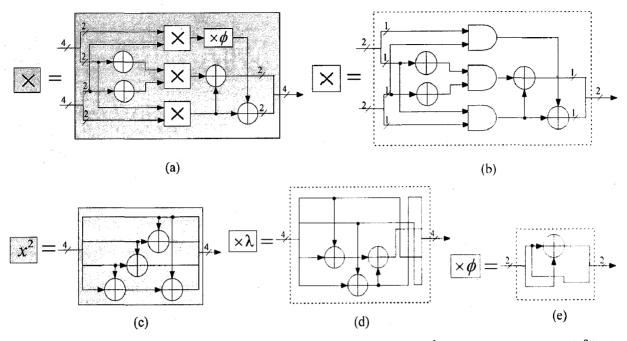

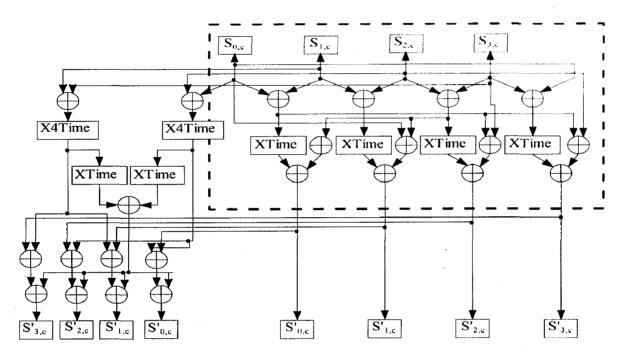

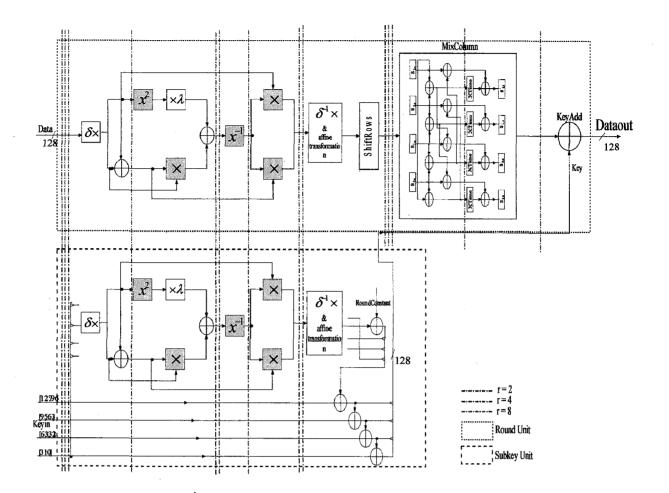

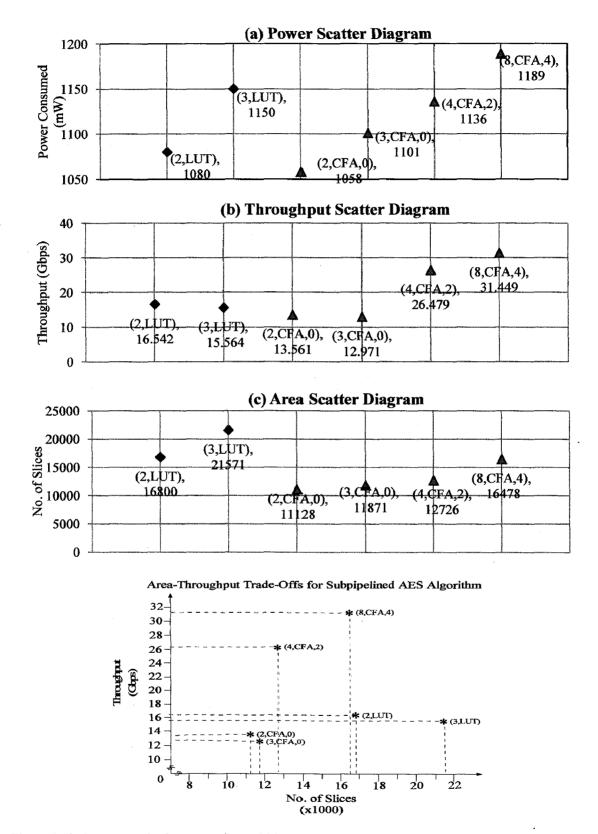

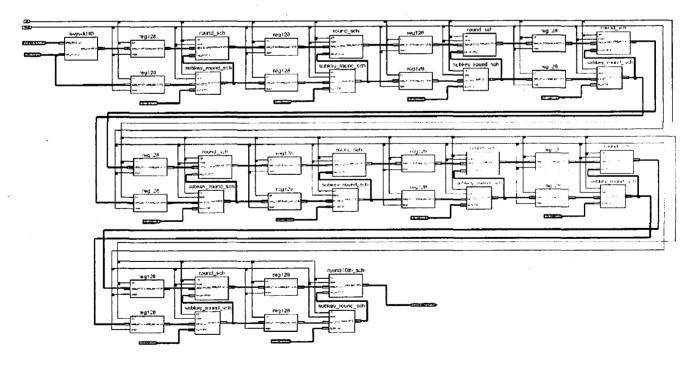

#### Figure No. Page No. Figure 2.1 : Simplified virtex-4 CLB.... 16 Figure 3.1 : (a) AES Encryption, (b) AES Decryption algorithm..... 18 Figure 3.2 18 : AES Round State Array Transformation..... Figure 3.3 : (a) Visual diagram, (b) Block diagram of composite Sbox..... 20 Figure 3.4 : AES Shift Rows..... 21 Figure 3.5 : AES 128 bit Key Schedule Round..... 22 : ECB Encryption and ECB Decryption. [1]..... Figure 3.6 24 : CTR Encryption and CTR Decryption [1]..... Figure 3.7 25 : $GHASH_H(X_1 || X_2 || ... || X_m) = Y_m.[4]...$ Figure 3.8 29 : GCTR<sub>K</sub> (ICB, $X_1 || X_2 || ... || X_n^*$ ) = $Y_1 || Y_2 || ... || Y_n^*.[4]$ ..... Figure 3.9 30 : AES-GCM-AE<sub>K</sub> (IV, P, A) = (C, T).[4].... Figure 3.10 32 Figure 3.11 : AES-GCM-AD<sub>K</sub> (IV, C, A, T) = P or FAIL.[4].... 34 Figure 4.1 : Mastrovito Multiplier for GCM..... 37 Figure 4.3 : (a) Abstract view, and (b) Full view of the Karatsuba Multiplier. 41 : Multiplier performance comparison..... Figure 4.4 42 Figure 5.1 : Compact single round AES FPGA architecture..... 44 Figure 5.2 : Round unit..... 44 Figure 5.3 : Key Scheduler Unit..... 45 Figure 5.4 : State diagram..... 46 Figure 5.5 : The architecture of Subpipelining..... 50 Figure 5.6 : Implementation of the subBytes Transformation..... 51 : Implementations of individual blocks: (a) Multiplier in $GF(2^4)$ ; Figure 5.7 (b) Multiplier in $GF(2^2)$ ; (c) Squarer in $GF(2^4)$ ; (d) Constant multiplier ( $\times \lambda$ ); and (e) Constant multiplier ( $\times \phi$ )..... 52 Figure 5.8 : Efficient implementation of the MixColumns (red dashed rectangle 55 only) and InvMixColumns transformation.....

| Figure 5.9  | : Different cutest of Round and Subkey unit for sub-pipelined         |    |

|-------------|-----------------------------------------------------------------------|----|

|             | architecture                                                          | 56 |

| Figure 5.10 | : Scatter graphs for comparison of (a) Power, (b) Throughput, (c) No. |    |

|             | of slices and (d) both (b)&(c), of subpipelined AES designs           | 59 |

| Figure 6.1  | : AES CTR over ECB Mode Cipher Structure                              | 62 |

| Figure 6.2  | : GHASH Hardware Architecture                                         | 63 |

| Figure 6.3  | : The Use of GCM in IPsec ESP [31]                                    | 65 |

| Figure 6.4  | : (a) The Data Flow of GCM Encryption (b) The Data Flow of GCM        |    |

|             | Decryption                                                            | 66 |

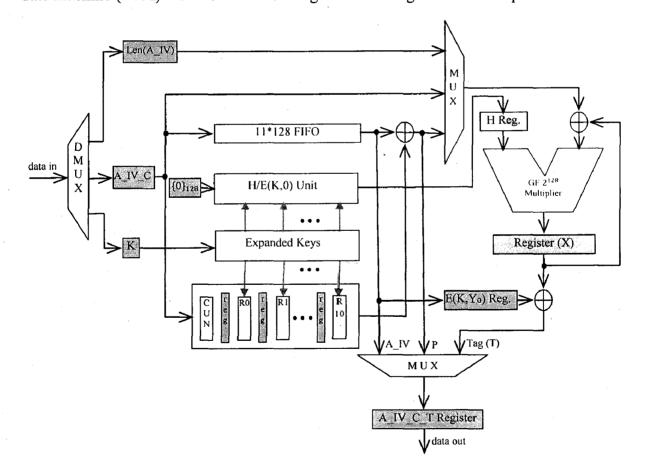

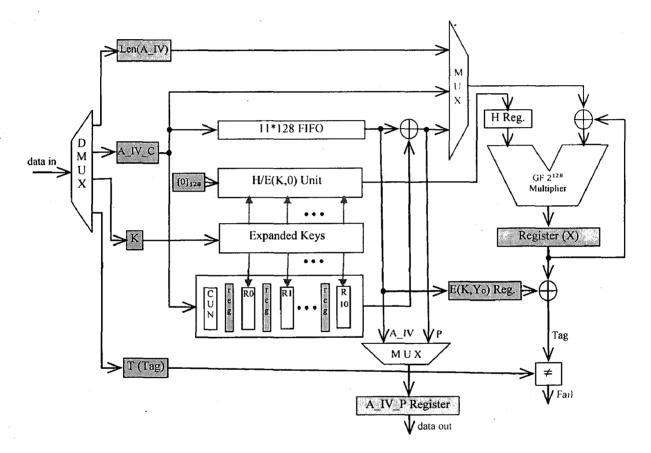

| Figure 6.5  | : AES-GCM Encryption Architecture                                     | 67 |

| Figure 6.6  | : AES-GCM Decryption Architecture.                                    | 69 |

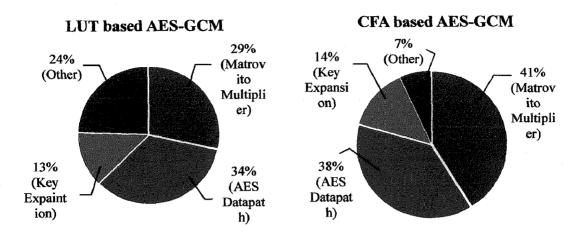

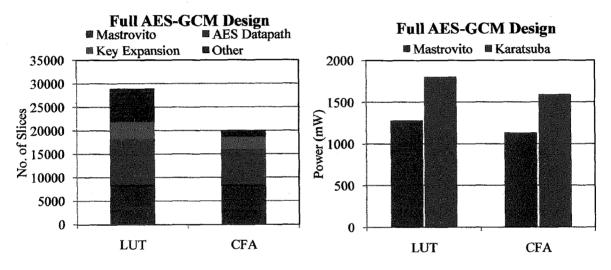

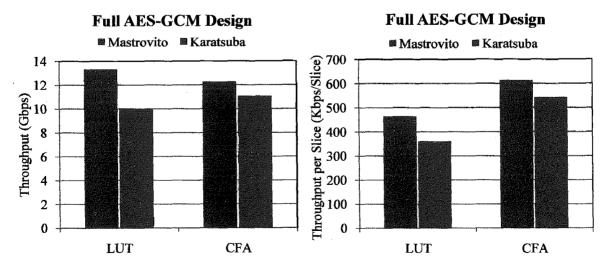

| Figure 6.7  | : Comparison of various units of Full AES-GCM                         | 71 |

| Figure 6.8  | : Area and power comparison of two type of AES-GCM                    | 71 |

| Figure 6.9  | : Throughput and throughput per slice comparison of two type of       |    |

|             | AES-GCM                                                               | 71 |

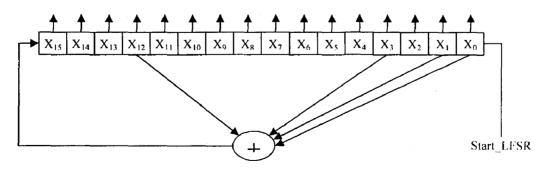

| Figure 6.10 | : 16-bit LFSR for IPsec ESP Signal Generator                          | 72 |

| Figure 6.11 | : AES-GCM Verification System.                                        | 73 |

| Figure 6.12 | : AES-GCM Hierarchical HDL Codes Design                               | 74 |

# **CHAPTER 1**

# INTRODUCTION AND STATEMENT OF THE PROBLEM

#### **1.1 Introduction**

In the past traditional communications were based on letters, payments were done using checks or cash, and secret documents were saved in sealed boxes. Today everything is changed, and is changing quickly. Everyday more people buy cell phones, the number of e-mail users goes up, and more people pay their payments over the internet. Paperless office strategies save and process documents in electronic format. These trends are going to make the life easier but at the same time produce security risks. The rapid development of electronic communication systems requires a secure infrastructure, too. Cryptography is the mathematical tool which is used by security engineers to secure data against unauthorized access or manipulation.

Like every other useful service, security will not be achieved for free. Implementing cryptography tasks costs time, money (chip area), and energy. To meets these constraints of upcoming modern applications, intensive work is required in this field.

Implementing cryptographic algorithms on reconfigurable hardware provides major benefits over ASIC (application-specific integrated circuit) and software platforms, since they offer high speed similar to ASIC and high flexibility similar to software. ASIC implementations are fast but must be designed all the way from behavioral description to the physical layout. They have to follow an expensive and time consuming fabrication process. Software implementations offer high flexibility but they are not fast enough for the applications where time factor is vital.

In nutshell, reconfigurable devices are attractive, since the time and costs of VLSI design and fabrication can be reduced. Moreover, they offer high potential for reprogramming and experimenting on multiple architectures or several revisions of the same architecture, which enhance robustness of security system.

The AES algorithm is a private-key encryption algorithm. In January 1997, the National Institute of Standards and Technology (NIST) invited proposals for new algorithms for

1

the Advanced Encryption Standard (AES) to replace the old Data Encryption Standard (DES). After two rounds of evaluation on the 15 candidate algorithms, NIST selected the Rijndael as the AES algorithm [1] in October 2000.

Since then, the NIST has published a total of four recommendations for Block Cipher AES Modes of Operation, specifically SP800-38A [1], SP800-38B [2], SP800-38C [3], and SP800-38D [4]. A block cipher mode of operation is an algorithm that uses a symmetric key block cipher to provide confidentiality, authentication or both for information security.

In SP800-38A, NIST recommends five confidentiality modes of operation for use with an underlying symmetric key block cipher algorithm: Electronic Codebook (ECB) mode, Cipher Block Chaining (CBC) mode, Cipher Feedback (CFB) mode, Output Feedback (OFB) mode, and Counter (CTR) mode. These five modes can be separated into two groups: one is a non-feedback mode group, including ECB and CTR; one is a feedback mode group, including CBC, CFB and OFB. In the feedback modes, the current computation/execution step depends on the result of the previous step. Therefore, to implement these kinds of modes in hardware, an iterative architecture is typically adapted for low throughput requirements rather than a pipelined architecture. In contrast, the use of ECB or CTR mode, or non-feedback modes, supports pipelined or parallelized architecture designs for processing high-speed data flows.

As the forth security standard of Block Cipher Mode of Operation, SP800-38D, *Galois/Counter Mode of Operation (GCM)*, fills the need above. GCM features the use of an approved symmetric key block cipher with a block size of 128 bits and a universal hash function that is defined over a binary Galois field. The most recently approved symmetric key block cipher with a block size of 128 bits is the Advanced Encryption Standard (AES) algorithm that is specified in Federal Information Processing Standard (FIPS) Pub.197 [3]. The specified universal hash function in GCM is defined over a binary Galois field (GF) and is a 128-bit polynomial multiplier over GF (2<sup>128</sup>), called GHASH. GHASH can provide a secure, parallelizable, and efficient authentication mechanism. For the confidentiality mechanism of GCM, the CTR mode embedded by ECB mode, called GCTR, is adopted using an underlying block cipher. GCM, i.e. SP800-

2

38D, was officially published in November 2006. However except one or two, there are no known high performance FPGA (field programmable gate array) architectures or implementations of this standard.

#### **1.2** Statement of the problem

The objective of this thesis is to demonstrate, analyze and implement FPGA architectures for, SP800-38A (ECB) and SP800-38D (GCM) modes of AES algorithm with the view of enhancing their performance.

In above stated two modes, GCM comparatively a big and complex design. It includes AES engine (SP800-38A), GHASH (modular multiplier), and Key-expanded modules. So to achieve our objectives, the problem can be subdivided as follows:

- 1. To implement iterative and pipelined architectures of AES-ECB (Electronic Code-Book) mode on FPGA and investigate their performance.

- 2. To investigate different type of modular multipliers used in GHASH and analyze their performance by implementing on FPGA.

- 3. To integrated various GCM modules together, along with control logic to implement the highly parallel, pipelined and entire new security standard, AES-GCM.

- 4. To optimize the AES designs in term of area, CFA (Composite Field Arithmetic) technique analyzed for making Sbox (sub unit of AES).

- 5. To verify the feasibility, efficiency and cost of each hardware module of AES, the architectural designs synthesized, timing simulated, and downloaded to the FPGA virtex-4 platform.

#### **1.3 Organization of Thesis**

10

This thesis is organized as follows: Chapter 2 provides historical review of different implemented architectures in this thesis. An overview of the mathematical definitions over GF and composite field arithmetic is provided as mathematical background. Introduction to the FPGA device structures and its advantage in security systems also

provided in this chapter. **Chapter 3** presents security standards, AES, other confidential modes of AES and GCM. **Chapter 4** describe two type of parallel multiplier used in GCM and their implementation result. In **chapter 5**, the proposed hardware architectures of AES are presented. The proposed hardware architectures of AES-GCM are presented in **chapter 6**. The bit parallel multiplier over GF, and the pipelined AES discussed in chapter 4 and 5 are chosen as the modules to build AES-GCM. A methodology, to verify the AES-GCM hardware implementation is also discussed during this chapter. Finally, **chapter 7** provides conclusion and future work.

# CHAPTER 2

# HISTORICAL REVIEW AND GENERAL CONSIDRATION

This chapter provides the review and concepts necessary in order to understand implemented architectures: Section 2.1 provides historical review. Section 2.2 introduces to the concepts of finite fields, and Composite Field Arithmetic (CFA); an area reduction technique. Section 2.3 gives quick overview of FPGA and describes the advantages of FPGA technology for cryptographic system.

#### 2.1 Historical Review

In November 2001, after a 5-year standardization process in which fifteen competing designs were presented and evaluated, Rijndael [32] (developed by two Belgian cryptographers, Joan Daemen and Vincent Rijmen) was selected as the most suitable for Advance Encryption Standard. Details of [32] given in section 3.1.

Since then, the NIST has published a total of four recommendations for Block Cipher AES Modes of Operation, specifically SP800-38A [1], SP800-38B [2], SP800-38C [3], and SP800-38D [4].

Out of five confidentiality sub-modes of SP800-38A; Electronic Codebook (ECB) mode is focused in this work. FPGA based architecture point of view, all important research of this mode can be divided into two fields; small iterative design and high speed pipelined design.

There are very few number of designs proposed for small design in literature, [18], [19], [20], [21] and [22] are some important one. Initially, memory (RAM) based nonparallelization Sbox implementation is used, but it is not area efficient. Although, parallelization of Sbox [19] helped in area reduction along with some speed improvement, but there not any specific area reduction technique adopted. Internal pipelining of single round is also employed in [18] which is effective for speed but not for area. In spite of that their speed is again limited by memory based Sbox. Some efforts of area reduction are also spoiled because of their complex control unit, since control unit can covers lots of

5

area if not properly designed. In 2005, CAF approached adopted for cryptographic systems, which is very efficient in area reduction, but as per of author knowledge up to now not any design based on this approach claimed in small AES design.

High speed pipelined AES architectures ([16], [17], [21], [26], [27], [28] and [29]) is quite famous among the researcher because of its requirement in modern application. Initially, parallelized outer 10 stage pipelined [27] or inner sub-pipelined ([26], [29]) are generally employed for speed improvement but their speed is limited by memory based Sbox. This problem is solved in [17], by making highly sub-pipelined CFA based Sbox implementation and achieved highest 21.5 Gbps throughput, but design is tested for 3 and 7 pipeline stages only.

In November 2006, fourth mode of AES proposed; SP800-38D or GCM. Research on hardware architectures or implementations of GCM is fairly small. This is likely due to the new mode of operation. As per knowledge of author there is not any design found on FPGA. Although design [33] demonstrates AES-GCM ASIC based architecture. using 0.18 um CMOS standard cell library, but it can be a good design to implement on FPGA.

From the above historical review, it can be concluded that, the following major research gaps still exist.

- Not any particular architecture technique of area optimization has been used till now in small (iterative) AES design. So CFA area reduction technique can be proved efficient for area optimization by implementing Sbox of small (iterative) AES design.

- ii. In high speed pipelined architecture, maximally 7 stage pipelined has been employed till now. But still speed improvement can be possible by further exploration of pipelined architecture to more stages.

- iii. AES-GCM being a recent mode, has been implemented only on ASIC, but not over FPGA. So detailed analysis and implementation of GCM mode on FPGA can be a good work to be carried out.

Thus, this dissertation work is to effectively fill above stated research gaps.

6

#### 2.2 Mathematical Background

The fundamentals of AES and GHASH (Multiplying unit of GCM) are based on operations over the finite field. This section provides an introduction to these operations. The concepts and methods have been gathered from [6] and [7].

# 2.2.1 Finite Fields

A field can be considered as a set whose elements form a group G under two operations: multiplication indicated by symbol "." and addition indicated by symbol "+". These operations obey the basic algebraic properties. The relative finite field concepts are list as follows:

**Concept 1**.  $(F, +, \cdot)$  is a field if the following properties hold:

- The elements of F form a group under addition.

- The non-zero elements of F form a group under multiplication.

- The addition and multiplication operations are commutative, i.e. x + y = y

+ x and xy = yx for all x, y ∈ F.

- The multiplication operation can be distributed through the addition operation, i.e.  $x \cdot (y + x) = x \cdot y + x \cdot z$  for all x, y, and  $z \in F$ .

**Concept 2**. A field F with a finite number of elements is a finite field.

- **Concept 3.** A non-zero element of a finite field F is said to be a primitive element or generator of F if its powers cover all nonzero field elements.

- **Concept 4.** A unique finite field exists for every prime number. These fields are denoted  $GF(p^{m})$  where p is prime and m is a positive integer. One kind of field which is commonly used in cryptography applications is the binary finite fields  $GF(2^{m})$  where m is a large integer.

- **Concept 5.** A basis for  $GF(2^m)$  over GF(2) is a set of m linearly independent elements of  $GF(2^m)$ . Any element of  $GF(2^m)$  can be represented as an algebraic sum of the basis elements.

The binary field  $GF(2^m)$  contains  $2^m$  elements. Each element is represented by the selected basis. The most common representation is based on polynomial basis. With the polynomial basis  $\alpha = \{1, \alpha, \alpha^2, ..., \alpha^{m-1}\}$ , the elements of  $GF(2^m)$  can be represented as polynomial of degree m-1 as follows:

$$GF(2^{m}) = \{A | A = a_{0} + a_{1} \alpha + \dots + a_{m-1} \alpha^{m-1} \text{ where } a_{j} \in GF(2), 0 \le j \le m-1\}$$

where  $\alpha$  is the root of an irreducible polynomial F(x) of degree m over GF(2).

Let

$$F(x) = 1 + f_1 x + f_2 x^2 + \dots + f_{m-1} x^{m-1} + x^m$$

where  $f_i \in GF(2), 0 \le i \le m-1$ . The irreducible polynomial F(x) is often referred to as the field polynomial. The arithmetic in AES-GCM is based on polynomial basis and uses the polynomial  $F(x) = 1 + x + x^2 + x^7 + x^{128}$  as field polynomial.

# 2.2.2 Operations over Binary Finite Fields GF $\binom{m}{2}$

Both operations, field addition and field multiplication, map a pair of field elements A and B onto another field element C, all A, B, and  $C \in GF(2^m)$ . The following introduction on field addition and multiplication is based on polynomial basis. The field elements A, B, and C are the following polynomials, respectively:

$$A(\alpha) = a_0 + a_1 \alpha + \dots + a_{m-1} \alpha^{m-1}$$

$$B(\alpha) = b_0 + b_1 \alpha + \dots + b_{m-1} \alpha^{m-1}$$

$$C(\alpha) = c_0 + c_1 \alpha + \dots + c_{m-1} \alpha^{m-1}.$$

## 2.2.2.1 Field Addition

Over a finite field  $GF(2^m)$ , a field addition of two elements A and B consists of adding the two polynomials together. Because the coefficients in A and B are over GF(2) and each pair of coefficients are added independently, their sum C is written as

$$C(\alpha) = A(\alpha) + B(\alpha) = \sum_{i=0}^{m-1} (a_i + b_i)\alpha_i$$

(2.1)

The pair of coefficients addition  $a_i + b_i$  in Eq.(2.1) is performed modulo 2 and translated to an exclusive- OR (XOR) operation in FPGA technology. That is to say that the field addition in Eq.(2.1) is computed by an m-bit XOR operation and does not require a carry chain.

## 2.2.2.2 Field Multiplication

## • Bit Serial Multiplier

Field multiplication over a finite field  $GF(2^m)$ , is executed by straightforward multiplying two polynomials  $A(\alpha)$  and  $B(\alpha)$ , then dividing the resulting 2m-bit polynomial by  $F(\alpha)$ ; the m-bit remainder is the result  $C(\alpha)$ . The product C of field elements A and B is expressed as

$$C(\alpha) = A(\alpha) \times B(\alpha) \mod F(\alpha) = \sum_{i=0}^{m-1} c_i \alpha_i = \sum_{i=0}^{m-1} \sum_{i=0}^{m-1} a_i b_j \alpha^{i+j} \mod F(\alpha) \quad (2.2)$$

A simple method of computing this involves the use of a linear feedback shift register (LFSR). The pseudo code for this multiplier given below simply loops through the summation in Eq.(2.2) and accumulates a modulo reduced answer. The LFSR contains one of the operands A, and depending on its most significant bit, the field polynomial is XORed to the LFSR at each step. The result of the multiplication is generated in the register C by the end of m iterations. This register adds the value of A at each step depending on the coefficients of the other multiplicand H. This design is called a serial multiplier design, totally m iteration are needed for calculating a multiplication over  $GF(2^m)$  if  $A(\alpha)$  can be loaded in parallel. Other multiplier designs exist such as the parallel multiplier that is able to compute  $C(\alpha)$  in a single iteration. More details will be provided in next section.

# Algorithm 2.1: $GF(2^m)$ multiplier

Input:  $A, H \in GF(2^m)$ ; F(x) Field Polynomial. Output:  $C(\alpha)$  C = 0for i = 0 to m do if  $H_i = 1$  then  $C \leftarrow C \oplus A$ end if if  $A_{127} = 0$  then  $A \leftarrow rightshift(A)$ else  $A \leftarrow rightshift(A) \oplus F(\alpha)$ end if end for return C

# • Bit Parallel Multiplier

Compared to the bit serial multiplier which needs m clock cycles to complete a multiplication over  $GF(2^m)$ , a bit parallel multiplier can complete computation in only 1 clock cycle over the same GF. (Because the circuit delays are very different between the bit serial multiplier and the bit parallel multiplier, the minimum clock period of clock for parallel multiplier is much larger than the minimum one for serial multiplier. i.e., 1 clock cycle computation time for parallel multiplier should be roughly equal to several or tens clock cycles computation time for serial multiplier.)

A dedicated polynomial basis finite field bit parallel multiplier has been proposed in [7], called the Mastrovito multiplier. This multiplier is adapted to a fixed field polynomial  $F(\alpha)$ . The implementation procedure of the Mastrovito multiplier and Karatsuba multiplier are described in chapter 4.

#### 2.2.3 Composite Field Arithmetic

The non-LUT-based implementations of the AES algorithm are able to exploit the advantage of subpipelining further. Nevertheless, these approaches may have high hardware complexities. Although two *Galois Fields* of the same order are isomorphic, the complexity of the field operations may heavily depend on the representations of the field elements. Composite field arithmetic can be employed to reduce the hardware complexity. We call two pairs  $\{GF(2^n), Q(y) = y^n + \sum_{i=0}^{n-1} q_i y^i, q_i \in GF(2)\}$  and  $\{GF((2^n)^m), p(y) = x^m + \sum_{i=0}^{m-1} p_i x^i, p_i \in GF(2^n)\}$  a composite field [12] if

- $GF(2^n)$  is constructed from GF(2) by Q(y),

- $GF((2^n)^m)$  is constructed from  $GF(2^n)$  by p(x).

Composite fields will be denoted by  $GF((2^n)^m)$ , and a composite field  $GF((2^n)^m)$  is isomorphic to the field  $GF(2^k)$  for k = nm. Additionally, composite fields can be built iteratively from lower order fields. For example, the composite field of can be built iteratively from using the following irreducible polynomials [7]:

$$\begin{cases} GF(2) \implies GF(2^2): & P_0(x) = x^2 + x + 1 \\ GF(2^2) \implies GF((2^2)^2): & P_1(x) = x^2 + x + \phi \\ GF((2^2)^2) \implies GF(((2^2)^2)^2): & P_2(x) = x^2 + x + \lambda \end{cases}$$

(2.3)

where  $\phi = \{01\}_2$  and  $\lambda = \{1100\}_2$ . Meanwhile, an isomorphic mapping function  $f(x) = \delta \times x$  and its inverse need to be applied to map the representation of an element in  $GF(2^8)$  to its composite field and vice versa. The  $8 \times 8$  binary matrix are decided by the field polynomials of  $GF(2^8)$  and its composite fields. Such a matrix can be found by the exhaustive-searchbased algorithm in [12]. The  $\delta$  matrix corresponding to  $P(x) = x^8 + x^4 + x^3 + x + 1$  and the field polynomials in Eq.(2.3) can be found as below:

$$\delta = \begin{bmatrix} 1 & 1 & 0 & 0 & 0 & 0 & 1 & 0 \\ 0 & 1 & 0 & 0 & 1 & 0 & 1 & 0 \\ 0 & 1 & 1 & 1 & 1 & 0 & 0 & 1 \\ 0 & 1 & 1 & 0 & 0 & 0 & 1 & 1 \\ 0 & 1 & 1 & 1 & 0 & 1 & 0 & 1 \\ 0 & 0 & 1 & 1 & 0 & 1 & 0 & 1 \\ 0 & 1 & 1 & 1 & 1 & 0 & 1 & 1 \\ 0 & 0 & 0 & 0 & 0 & 1 & 0 & 1 \end{bmatrix}$$

Taking the isomorphic mapping into consideration, not all the transformations in the AES algorithm are suitable to be implemented in the composite field. In order to facilitate substructure sharing, the constant multiplications in the MixColumns/InvMixColumns transformation are implemented by first computing  $\{02\}_{16}S_{i,j}, \{04\}_{16}S_{i,j}$  and  $\{08\}_{16}S_{i,j}$ . then adding those terms corresponding to the nonzero bits in the constants. For example. the constant multiplication of  $\{0b\}_{16} = \{00001011\}_2$  can be computed by adding  $S_{i,j}$ ,  $\{02\}_{16}S_{i,j}$  and  $\{08\}_{16}S_{i,j}$ . In this approach, the  $\{02\}_{16}S_{i,j}$ ,  $\{04\}_{16}S_{i,j}$  and  $\{08\}_{16}S_{i,j}$ , can be computed once and shared by all the constant multiplications. Meanwhile, the number of terms, which need to be added is determined by the number of nonzero bits in the constants. Using the  $\delta$  matrix defined in (8), the constant multiplications of  $\{02\}_{16}$ and  $\{03\}_{16}$  in  $GF(2^8)$  in the MixColumns are mapped to constant multiplications of  $\{5f\}_{16}$  and  $\{5e\}_{16}$  in the composite field, respectively. Although the hardware overhead of the mapping of constants can be eliminated by computing the mapping beforehand, the composite field representations of  $\{02\}_{16}$  and  $\{03\}_{16}$  have more nonzero bits, which makes the constant multiplications more expensive. The same argument also holds for the constant multiplications used in the InvMixColumns transformation, where  $\{09\}_{16}$ ,  $\{0b\}_{16}$  and  $\{0c\}_{16}$  are mapped to  $\{75\}_{16}$ ,  $\{2a\}_{16}$  and  $\{57\}_{16}$  in the composite field. respectively. The only exception is that the composite field representation of  $\{0d\}_{16}$ . which is  $\{09\}_{16}$ , has one less nonzero bit, but this is offset by the larger number of nonzero bits in the composite field representations of the other three constants.

(2.4)

Furthermore,  $\{10\}_{16}S_{i,j}$ ,  $\{20\}_{16}S_{i,j}$  and  $\{40\}_{16}S_{i,j}$  also need to be computed as a result of the higher-weight nonzero bits in  $\{75\}_{16}$ ,  $\{2a\}_{16}$  and  $\{57\}_{16}$ , which adds more complexity to the hardware implementations. Therefore, it is more efficient to implement

$GF(2^8).$ MixColumns/InvMixColumns the original field The the in ShiftRows/InvShiftRows is a trivial transformation, only cyclical shifting is involved, and thus its implementation does not depend on the representation of Galois Field elements. Meanwhile, the field addition, which is simply XOR operation, has the same complexity in the composite field and the original field. Additionally, the affine/inverse affine transformation can be combined with the inverse isomorphic/isomorphic mapping. Based on the above observations, it is more efficient to carry out only the multiplicative inversion in the SubBytes/InvSubBytes in the composite field, while keep the rest of the transformations in the original field  $GF(2^8)$ .

#### 2.3 Field Programmable Gate Arrays (FPGA)

The thesis presents the architecture of FPGA implementation of AES security algorithms. The common implementation approaches are corresponding to three different technologies. They are:

- Application Specific Integrated Circuits (ASICs)

- Software-Programmed General Purpose CPU (SPGPC)

- Field Programmable Gate Arrays (FPGAs)

**ASICs** are specifically designed for a fixed solution, and are thus very efficient. However, the circuit cannot be changed after fabrication. This requires a redesign of the chip if any modification needs to be done.

**SPGPCs** are a flexible solution. CPUs execute a set of instructions to perform an algorithm. By changing the software code, the functionality of the system is altered without touching the hardware. But the SPCGPC's efficiency is much lower than that of an ASIC.

**FPGAs** offer a compromise between the ASIC and the SPGPC, achieving higher performance than software, while maintaining a higher level of flexibility than hardware.

## 2.3.1 Advantages of FPGA in Cryptographic Applications

The following attributes of the FPGA technology are particularly advantageous for cryptographic applications [8].

Algorithm Agility: More and more security applications intend to be algorithm independent and allow switching encryption algorithms on the flying. The encryption algorithm can be chosen through the negotiation made by two communication parties.

**Algorithm Upload**: From a cryptographic point of view, algorithm upload can be necessary because a current algorithm is out of date or broken; a new algorithm is created. The security designer of the corresponding security company can upload the new bit streams of security standard to reconfigure FPGA device through the networks.

**Throughput**: Although FPGA implementations are typically slower than ASIC implementations, FPGA implementations are obviously faster than software implementations. In a cryptosystem, if a software solution is chosen for clients, then, a FPGA implementation should be adapted for servers in high-speed backbones.

**Cost Efficiency**: The production costs of an ASIC are often too high for a small number of servers in security systems. Thus, the use of FPGAs is a common alternative. Furthermore, this is the one of reasons why the FPGA is chosen for security research in institutes and universities.

Therefore, it is often best to choose an FPGA to implement cipher, such as AES-GCM standard. The CMC-FPGA-prototype-platform was chosen in this thesis for prototyping since it represents a generalized multi-core platform, appropriate for security applications. This FPGA platform will be discussed next.

# 2.3.2 Vertex-4

A traditional FPGA is usually an integrated circuit consisting of

- Configurable Logic Blocks (CLBs),

- Input/Output Blocks (IOBs) and

- Programmable routing resources.

More specifically, Table 2.1 shows all the main resources of the Virtex-4 xc2vp100 targeted in this thesis.

| Devices   | No. of slices<br>(1CLB=4 Slices) | No. of 4<br>input LUTs | No. of RAM<br>Block (18K) | Max User<br>I/Os | Max. operating<br>frequency<br>(MHz) |

|-----------|----------------------------------|------------------------|---------------------------|------------------|--------------------------------------|

| XC4VLX25  | 10,752                           | 21504                  | 72                        | 448              | 500                                  |

| XC4VLX100 | 49,152                           | 98,304                 | 240                       | 960              | 500                                  |

| XC4VLX200 | 89,088                           | 178,176                | 360                       | 960              | 500                                  |

Table 2.1: Resources of Virtex-4 FPGA Family Members.

# • Configurable Logic Blocks (CLBs)

The CLBs in the Virtex-4 are comprised of both combinational and sequential logic. The combinational logic can be configured to become possible Boolean functions. Flip-Flops are provided to support sequential logic and can be utilized or bypassed depending on the configuration.

One CLB has four slices. Each slice is identical and contains:

- Two function generators F and G

- Two storage elements

- Arithmetic logic gates

- Multiplexers

- Fast carry look-ahead chain

- Horizontal cascade chain

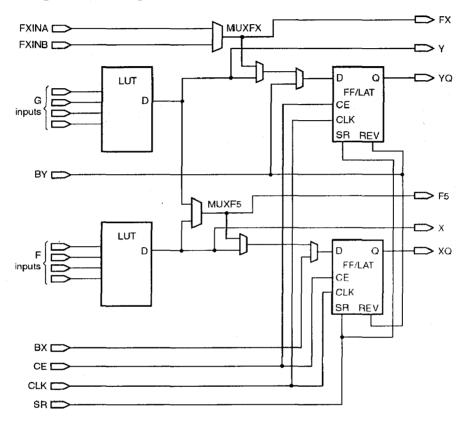

A general slice structure of Virtex-4 is shown in Figure 2.1. The function generators F and G can be configured as 4-input look-up tables (LUTs), as 16-bit shift registers, or as

16-bit distributed SelectRAM+ memory. The multiplexers, MUXF5 and MUXFX can provide any function of five, six, seven, or eight inputs when combined with function generators. The two storage elements can be configured either edge-triggered flip-flops or level-sensitive latches. Each CLB has internal fast interconnect and connects to a switch matrix to access general routing resources.

# CHAPTER 3

# SECURITY STANDARD

This chapter provides the details of various modes of AES, which are implemented in this thesis: Section 3.1 introduces to Advance Encryption Standard security algorithm, Section 3.2 provides background of confidentiality mode of operation and Section 3.3 gives detail of GCM mode of AES.

## 3.1 Advanced Encryption Standard (AES)

The Advanced Encryption standard is a 128 bit block cipher that has been widely used since its acceptance in 2001 [5]. The design of AES was intended to be a more secure replacement of DES (Data Encryption Standard). Many efficient hardware and software designs have been documented, taking into consideration various tradeoffs of speed and area resources. The following sections will provide a general functional description of AES with an increased focus on the hardware design of AES components.

# 3.1.1 AES Cipher

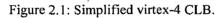

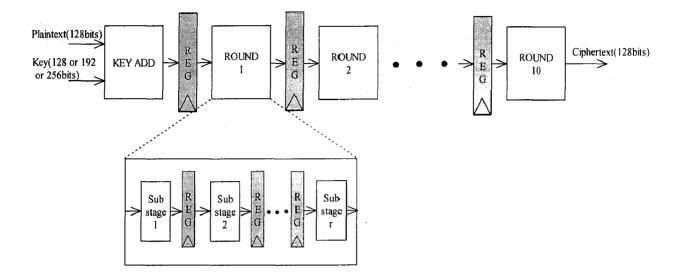

Figure 3.1 showing schematic of AES encryption and decryption. Different hardware datapaths can be created from these modular round structures. An iterative design can be made by simply adding a 128 bit data register at the end of the round structure. After a maximum of 14 cycles the AES encryption result can be obtained. This iterative design can be unrolled to create a pipelined implementation that has registers placed between round blocks. This is an outer pipelined AES design and a 128 bit output can be generated at each clock cycle with a full pipeline. There is enough flexibility, however, in choosing locations of the pipelined registers. Within each of the round components, additional pipelined stages can be added within the Sub-bytes operation which will be described in Section 3.1.2. This is labeled as an inner pipelined AES design, and although a higher latency and area is present, higher throughputs are possible.

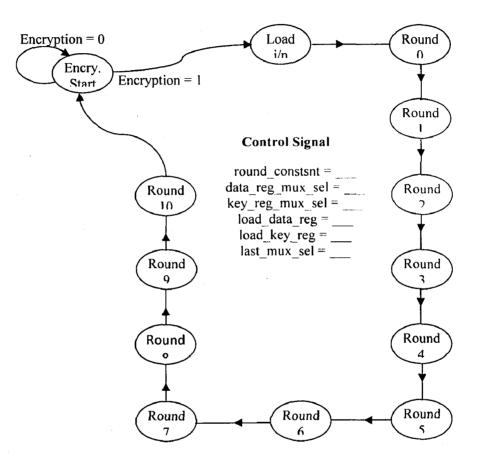

Figure 3.1: (a) AES Encryption, (b) AES Decryption algorithm.

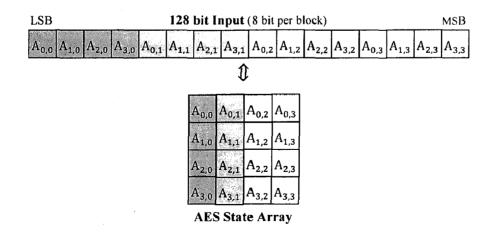

The 128 bit plain text input is mapped into a state array which is a 4x4 block of 8 bit words that is manipulated in each round. For the following sections the state array block will be used to describe the different round operations so it is important to understand how the input is transformed into the state array. Figure 3.2 shows this transformation, by filling bytes of data into the state array by columns. After the AES encryption round, the last state array outputted is transformed back into a 128 bit stream.

Figure 3.2: AES Round State Array Transformation.

## **3.1.2 Byte Substitution (Subbytes)**

The subbytes operation uses multiple substitution box components (Sbox) each of which performs an 8 bit substitution. Each 8-bit word of data in the state array, is substituted using the Sbox. This results in 16 Sbox components used for each round block, and is the most hardware area consuming part of an AES round. The Sbox computation is essentially a multiplicative inverse in  $GF(2^8)$  followed by an affine transformation which is a linear mapping from one vector space to another [9]. A lookup table of  $2^8$  values can be used to implement the Sbox component, but it can also be mathematically computed using logic gates.

# • Sbox Designs

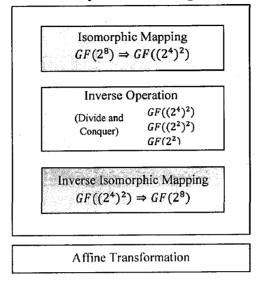

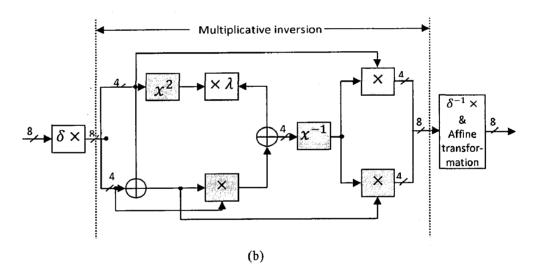

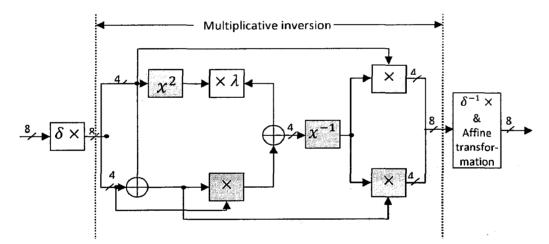

Rijimen, one of the creators of AES showed in [10] a method of computing the Sbox by breaking operations in  $GF(2^8)$  down to a composite field  $GF((2^4)^2)$  resulting in significant hardware area savings which would otherwise not be possible using look-up table implementations. The inverse formula for the Sbox is given in its reduced version, in Eq.(3.1), where  $\lambda$  is (1100)<sub>2</sub>. The addition, multiplication, and inverse operations are computed in  $GF((2^4)^2)$ , and can be further broken down to the smaller composite fields,  $GF((2^2)^2)$  and  $GF(2^2)$ , using the divide and conquer method.

$$a'x + b' = (ax + b)^{-1} = a(a^2\lambda + b(a + b))^{-1}x + (b + a)(a^2\lambda + b(a + b))^{-1} \quad (3.1)$$

Figure 3.3 shows a visual diagram of the composite Sbox. The isomorphic mapping to the composite field,  $(GF(2^8) \rightarrow GF((2^4)^2))$  can be implemented using a matrix vector multiplication. The affine transformation consists of a linear transformation followed by a translation which can be achieved by a matrix vector multiplication and vector addition respectively. The isomorphic mapping and affine transformation both use fixed matrices that are sparse so the computation costs of these operations are minimal [9].

#### **Composite SBox Stages**

(a)

Figure 3.3: (a) Visual diagram, (b) Block diagram of composite Sbox.

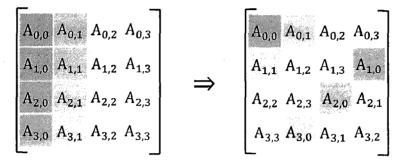

# 3.1.3 Shift Rows

The Shift Rows operations consists of cyclically moving elements around in all but the first row of the 128 bit input block. The rows are left shifted by 1, 2, and 3 times respectively for rows 2, 3 and 4. The following mapping illustrates this process. In

hardware no logic is required for this step and simple wire connections are used for this step to route the input to the output.

Figure 3.4: AES Shift Rows

# 3.1.4 Mix Columns

The mix columns operation consists of a multiplication and reduction operation over  $GF(2^8)$ . Each column of the state array is multiplied by the polynomial  $3x^3 + x^2 + x + 2$  and reduced modulo the field generating polynomial  $x^4 + 1$ . This operation is generally optimized into a single matrix vector product. The four column blocks are used as the vectors, while a constant 4x4 matrix is used that combines the modulo operation. The result vector is stored in the next state array at the same location as the original column vector. All elements are 8 bits in width and the multiplication and addition operations are performed over  $GF(2^8)$ .

$$\begin{bmatrix} 2 & 3 & 1 & 1 \\ 1 & 2 & 3 & 1 \\ 1 & 1 & 2 & 3 \\ 3 & 1 & 1 & 2 \end{bmatrix} \cdot \begin{bmatrix} a_0 \\ a_1 \\ a_2 \\ a_3 \end{bmatrix}$$

(3.2)

Since the elements of the matrix are of low degree the multiplications are simplified. A multiplication with 2 in  $GF(2^8)$  consists of a shift operation along with a modulo reduction if an overflow occurs. This operation can be reused with multiplying by 3, but an extra addition is required since  $3 \cdot a_i = (2 \cdot a_i) \oplus a_i$ .

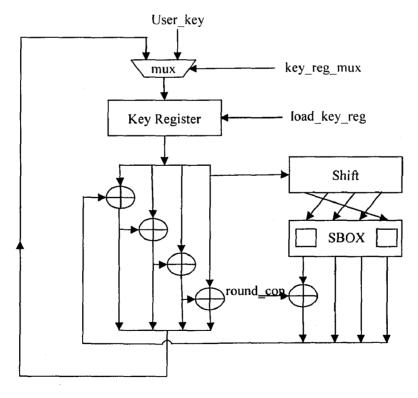

## 3.1.5 Key Schedule

Round keys are XORed at the end of every round and are generated using a Key Schedule. These keys can be pre-computed or generated at each round. The Sbox components used in the subbytes section are also used here for the round key generation. For each inputted key length, the method of generating keys is slightly different, but they contain similar logic components.

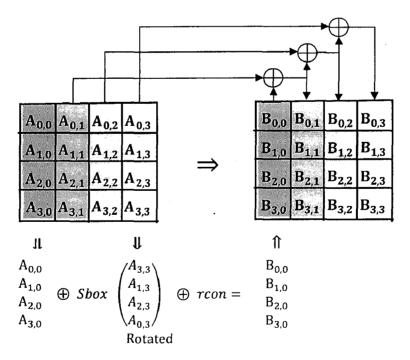

The 128 bit key has a Sbox operation done on the last column of the cipher key state array after the column bytes are rotated. This is followed by a *rcon* value XOR addition. The *rcon* value is generated based on the exponentiation formula  $rcon(i) = x^{254+1} \mod x^8 + x^4 + x^3 + x + 1$  performed over  $GF(2^8)$ . These values are usually pre-computed and once the *rcon* value is added, there is an XOR chain on the columns of the state array that creates the next 128 bit round key. Figure 3.5 shows a single round key computation. This process is repeated by using the round key as a cipher for generating the next 128 bits of key material. The *rcon i* value starts at 1 and increments for each round key.

Figure 3.5: AES 128 bit Key Schedule Round.

In order to compute the key schedule operation in hardware, most designs generally pre-compute roundkeys before starting data encryption or decryption. Computing the key schedule on the fly, while rounds are being computed is possible for encryption, and has been implemented for iterative AES [11]. There is added complexity when supporting all keys primarily because of the overlap occurring in operations. In this thesis, 128 bit key employed for various design, so there is no need to explain 192 and 256 bit key schedules.

## 3.2 Confidentiality Mode of Operation Background

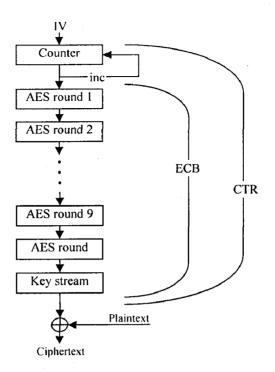

Two modes of operation for Symmetric Key Block Ciphers, ECB and CTR, are selected to create the confidentiality in AES-GCM because they can admit pipelined, parallelized implementations and have minimal computational latency for high data rates. These modes are introduced below and more details can be obtained from [1].

#### **3.2.1 Electronic Codebook Mode (ECB)**

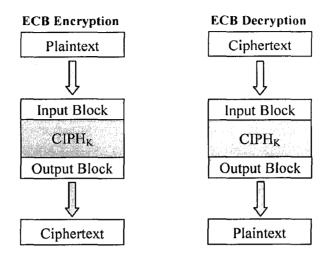

The ECB mode is defined as follows and shown in Figure 3.6:

ECB Encryption:  $C_j = CIPH_K(P_j) for \ j = 1, ..., n.$ ECB Decryption:  $P_i = CIPH_K^{-1}(C_i) for \ j = 1, ..., n.$

where,  $\text{CIPH}_{K}(P_{j})$  is the forward cipher function of the block cipher algorithm, such as AES, under the key K applied to the plaintext  $P_{j}$ ;  $\text{CIPH}^{-1}_{K}(C_{j})$  is the inverse cipher function of the block cipher algorithm under the key K applied to the ciphertext  $C_{j}$ .

In ECB encryption and ECB decryption, multiple forward cipher functions and inverse cipher functions can be computed in parallel or pipeline. In the GCTR module of AES-GCM, ECB encryption block is embedded into a CTR block (see Figure 6.1).

Figure 3.6: ECB Encryption and ECB Decryption. [1]

# 3.2.2 Counter Mode (CTR)

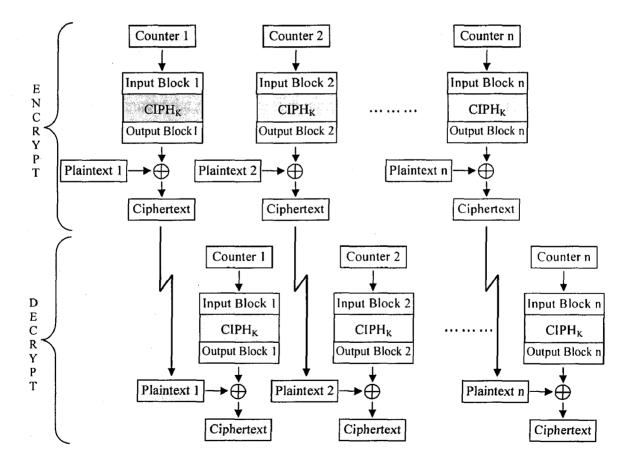

The CTR mode is a confidentiality mode also that features the application of the block cipher to a set of input data groups, called counters, to produce a set of keystreams that are XORed with the plaintext to produce the ciphertext, and vice versa. The CTR mode is defined as follows and shown in Figure 3.7.

CTR Encryption:

$$O_j = CIPH_K(T_j) for \ j = 1, ..., n,$$

$$C_j = P_j \ XOR \ O_j \ for \ j = 1, ..., n - 1,$$

$$C_n^* = P_n^* \ XOR \ MSB_u(O_n).$$

CTR Decryption:

$$O_j = CIPH_K(T_j) for \ j = 1, ..., n,$$

$$P_j = C_j \ XOR \ O_j \ for \ j = 1, ..., n - 1,$$

$$P_n^* = C_n^* \ XOR \ MSB_u(O_n).$$

The symbols used in the CTR encryption and decryption are :

$T_j$ : the counters for the jth input data group,

O<sub>j</sub> : the key stream for the jth input data group,

$P_j$ : the jth plaintext group,

$C_j$  : the jth ciphertext group.

$C_n^*$ : the last group of the ciphertext, which may be a partial group.

$P_n^*$ : the last group of the plaintext, which may be a partial group.

$MSB_u(O_n)$ : the bit string consisting of the u most significant bits of the bit string  $O_n$ .

In CTR encryption and CTR decryption, only the forward cipher function is invoked on each counter group, no inverse cipher function. The resulting key streams are XORed with the corresponding plaintext or ciphertext blocks to produce the ciphertext or plaintext blocks. For the last group, which may be a partial group of u bits, the most significant u bits of the last output group are used for the XOR operation; the remaining bits of the last output group are discarded. The forward cipher functions can be performed in parallel and pipelined.

Figure 3.7: CTR Encryption and CTR Decryption [1].

Both CTR encryption and CTR decryption are invoked in AES-GCM encryption and AES-GCM decryption, respectively.

#### 3.3 Galois/Counter Mode (GCM)

The elements of GCM and the associated notation and requirements are introduced in the three sections below. The block cipher and key are discussed in Sec. 3.3.1. The data elements of the authenticated encryption and authenticated decryption functions of GCM are discussed in Sec. 3.3.2. The types of application of GCM supposed in [4] are summarized in Sec. 3.3.3. The GHASH function, GCTR function and GCM specification are described in section 3.3.4, 3.3.5 and 3.3.6, respectively.

## 3.3.1 Block Cipher

The AES-GCM standard depends on the symmetric key block cipher AES. The AES-GCM key is the block cipher key. The key shall be generated uniformly at random, or close to uniformly at random. The key should be established secretly among the parties to communicate. AES-GCM designates the encryption function of the block cipher AES as the forward cipher function denoted CIPH<sub>K</sub> which actually is AES in ECB mode (see Figure 3.1). GCM does not employ the inverse cipher function.

#### **3.3.2 Input and Output Data**

COOR ST

GCM consists of the two functions that are called authenticated encryption and authenticated decryption. The requirements and notation for the input and output data of these functions are introduced in Section 3.2.2.1 and 3.2.2.2.

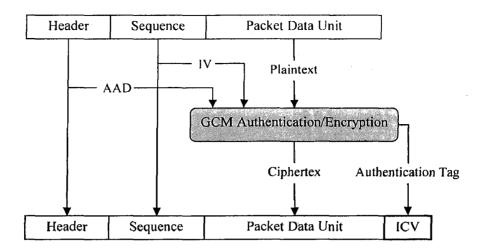

## **3.3.2.1** Authenticated Encryption

There are three input bit streams to the authenticated encryption operation:

- A plaintext, denoted as P that can have up  $to2^{39}$  bits;

- Additional authenticated data (AAD), denoted as A that can have up to  $2^{64}$  bits;

• An initialization vector denoted, as IV that can have up to  $2^{64}$  bits.

In this thesis, a 96-bit IV is adopted for efficiency following the suggestion in [13]. GCM verifies the authenticity of both P and AAD; GCM also protects the confidentiality of P, while the AAD is transmitted in the clear. The IV is a nonce that is associated with the data to be against related attack.

The following two bit strings comprise the output data of the authenticated encryption function:

- A ciphertext, denoted by C, with the same bit length as that of the plaintext.

- An authentication tag, denoted T that have up to 128 bits. The T's bit length is denoted as t.

#### **3.3.2.2** Authenticated Decryption

The inputs to the authenticated decryption function are values for IV, A, C, and T, as described in Sec. 3.2.2.1 above. The output is one of the following:

- The plaintext P that corresponds to the ciphertext C, or

- An indication that the inputs are not authentic, denoted as FAIL.

GCM authenticated decryption computes the authentication tag T' based on received data, and compares it with the received authentication tag T. If the two tags T and T' are equal, then P will be the output of the authenticated decryption function. Otherwise. FAIL will be the output.

#### **3.3.3** Types of Applications of GCM

There are four types of applications of GCM that are recommended in SP800-380D. They are

- a. GCM with an arbitrary length IV,

- b. GCM with the default IV, i.e. the length of the IV is restricted to exactly 96 bits.

- **c.** GMAC, i.e. the algorithm generates a stand-alone authentication tag T on the AAD with the arbitrary length IV. The plaintext P is the empty string.

#### d. GMAC with the default IV.

In the thesis, GCM with the default IV is chosen with size shown in Appendix A.

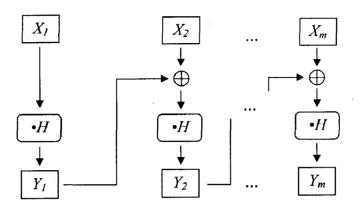

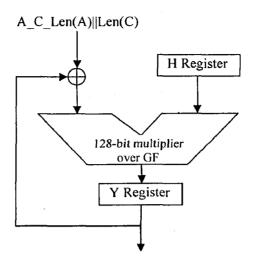

# **3.3.4 GHASH Function**

The authentication mechanism within GCM is based on the hash function, GHASH, that features multiplication by a fixed hash subkey, over a binary Galois field  $GF(2^{128})$ . The hash subkey, denoted as H, is generated by applying the block cipher to the 128-bit "0" string. GHASH is a keyed hash function. Algorithm 3 below specifies the function that will be invoked within the AES-GCM authenticated encryption and authenticated decryption functions:

#### Algorithm 3.1: $GHASH_H(X)$

**Input:** 1. Bit string X with length  $len(X) = 128 \cdot m$  for some integer m. 2. The hash subkey H.

**Output**: Block  $Y_m$ .

Steps:

- **1.** Let  $X_1, X_2, ..., X_{m-1}, X_m$  represents the unique sequence of blocks such that  $X = |X_1| ||X_2| ||...| ||X_{m-1}| ||X_m|$ .

- **2**. Let  $Y_0$  be the "zero block," which means  $Y_0$  is a bit string comprised by 128 binary 0.

- 3. For i = 1, ..., m, let  $Y_i = (Y_i 1 \oplus X_i) \cdot H$ . where "

" indicates multiplication over finite field as discussed in chapter 2.

**4**. Return  $Y_m$ .

The GHASH function is illustrated in Figure 3.8 below.

Figure 3.8:  $GHASH_H(X_1 || X_2 || ... || X_m) = Y_m.[4]$

## 3.3.5 GCTR Function

The mechanism for the confidentiality of GCM is a variation of the CTR mode (see section 3.2.2.), called GCTR, with a particular incrementing function, denoted inc. for generating the necessary sequence of counter blocks. The first counter block for the plaintext encryption is generated by incrementing a block that is derived from IV.

Algorithm 3.2 below specifies the GCTR function that will be invoked within the algorithms for the GCM authenticated encryption and authenticated decryption functions:

# Algorithm 3.2: GCTR<sub>K</sub> (ICB, X)

*Input*: **1**. *Bit string X*, *of arbitrary length*;

2. Initial counter block ICB, i.e. IV or some value generated from IV;

**3**. Approved block cipher CIPH (such as AES) with a 128 – bit block size;

**4**. Key K;

**Output**: Bit string Y of bit length len(X).

Steps:

**1**. Let n = [Len(X)/128]

**2.** Let  $X_1, X_2, \dots, X_{n-1}, X_n^*$  represents the unique sequence of blocks such that  $X = |X_1| |X_2| |\dots || |X_{n-1}| |X_n^*$ .

**3.** Let  $CB_1 = ICB$ . **4.** For i = 2 to n, let  $CB_i = inc(CB_i - 1)$ . **5.** For i = 1 to n - 1, let  $Y_i = X_i \oplus CIPH_K(CB_i)$ . **6.** Let  $Y_n^* = X_n^* \oplus MSB_{len}(X * n)(CIPH_K(CB_i))$ . **7.** Let  $Y = Y_1 || Y_2 || ... || Y_{n-1} || Y_n^*$ . **8.** Return Y.

Note:

- 1. Len(X) indicates the bit length of the bit string X.

- 2.  $X_i \parallel X_{i+1}$  indicates the concatenation of two bit strings  $X_i$  and  $X_{i+1}$ .

- 3. LSBs (X) indicates the bit string consisting of the s right-most bits of the bit string X.

- 4. MSBs (X) indicates the bit string consisting of the s left-most bits of the bit string X.

- 5. Int(X) indicates the integer for which the bit string X is a binary representation.

- Inc(X) indicates the output of the GCM incrementing function applied to the block X, the more specifically, inc(X)=MSB<sub>96</sub>(X) ||[(int(LSB<sub>32</sub>(X))+1) mod 2<sup>32</sup>]<sub>32</sub>.

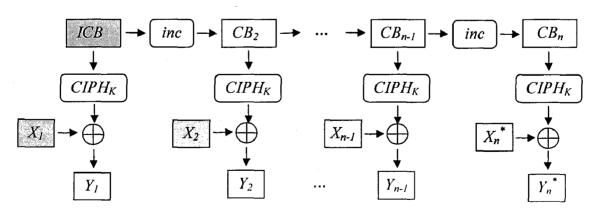

Figure 3.9 below illustrates the GCTR function.

Figure 3.9: GCTR<sub>K</sub> (ICB,  $X_1 \parallel X_2 \parallel ... \parallel X_n^*$ ) =  $Y_1 \parallel Y_2 \parallel ... \parallel Y_n^*$ .[4]

# **3.3.6 GCM Specification**

Algorithms for the authenticated encryption and authenticated decryption functions of GCM are specified in Section 3.2.6.1, and 3.2.6.2 below. The block cipher is AES (see section 3.1).

# 3.3.6.1 Authenticated Encryption

Algorithm 3.3 below performs the authenticated encryption function.

# Algorithm 3.3: AES-GCM-AE<sub>K</sub> (IV, P, A)

```

Input: 1. Block cipher CIPH (i.e. AES) with a 128 – bit block size;

```

**2**. Key K;

**3**.Tag length t.

4. Initialization vector IV;

**5**. *Plaintext P*;

6. Additional authenticated data A.

**Output**: 1.Cipher text C;

**2**. Authentication tag T.

Steps:

**1.** Let  $H = CIPH_{\kappa}(0^{128})$

**2**. Define a block,  $J_0$ , as follows:  $J_0 = IV || 0^{31}1$ , i.e.  $J_0$  is a 128 – bit string consisted of 96 – bit IV, 31 '0' bits, and 1 '1' bit.

3. Let  $C = GCTR_{\kappa}(inc(J_0), P)$ .

4. Let  $u = 128 \cdot [len(C)/128] - len(C)$ , and let  $v = 128 \cdot [len(A)/128] - len(C)$

len(A)

**5**. *Define a block*, *S*, *as follows*:

$S = GHASH_{H}(A||0^{v}||C||0^{u}||[len(A)]_{64}||[len(C)]_{64}).$ 6. Let  $T = MSB_{t}(GCTR_{K}(J_{0},S)).$ 7. Return (C,T).

Note:

- 1.  $[x]_s$  indicates the binary representation of the non-negative integer x as a string of s bits, where x < 2s.

- 2.  $0^s$  denotes the string that consists of s '0' bits, e.g.  $0^5 = B00000$ .

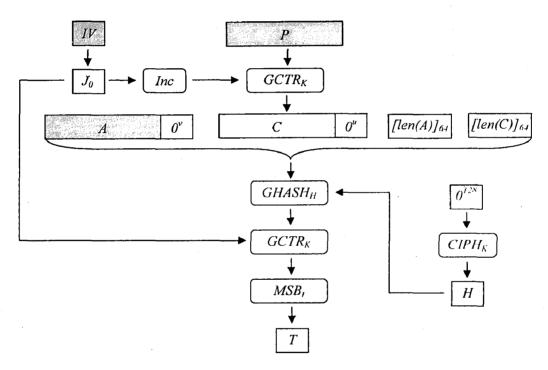

The authenticated encryption function is illustrated in Figure 3.10 below.

Figure 3.10: AES-GCM-AE<sub>K</sub> (IV, P, A) = (C, T).[4]

# 3.3.6.2 Authenticated Decryption

Algorithm 3.4 below performs the authenticated decryption function.

Algorithm 3.4: AES-GCM-AD<sub>K</sub> (IV, C, A, T)

*Input*: **1**.*Block cipher CIPH* (*i.e. AES*) with a 128 – bit block size;

**2**. Key K;

**3**.*Tag length t*.

**4.** *Initialization vector IV*;

**5**. *Cipher text C*;

**6**. Additional authenticated data A.

**7**. Authentication tag T.

**Output:** Plaintext P or indication of inauthenticity FAIL;

Steps:

**1.** Let  $H = CIPH_{K}(0^{128})$

**2**. Define a block,  $J_0$ , as follows:  $J_0 = IV || 0^{31}$ **1**. *i.e.*  $J_0$  is a 128 – bit string consisted of 96 – bit IV, 31 '0' bits, and**1 '1'** bit.

3. Let  $P = GCTR_K(inc(J_0), C)$ .

- 4. Let  $u = 128 \cdot [len(C)/128] len(C)$ , and let  $v = 128 \cdot \left[\frac{len(A)}{128}\right] len(A)$

- **5**. Define a block, S, as follows:

$S = GHASH_{H}(A||0^{\nu}||C||0^{u}||[len(A)]_{64}||[len(C)]_{64}).$

**6.** Let  $T' = MSB_t(GCTR_K(J_0, S)).$

**7.** If T = T', then return P; else return FAIL.

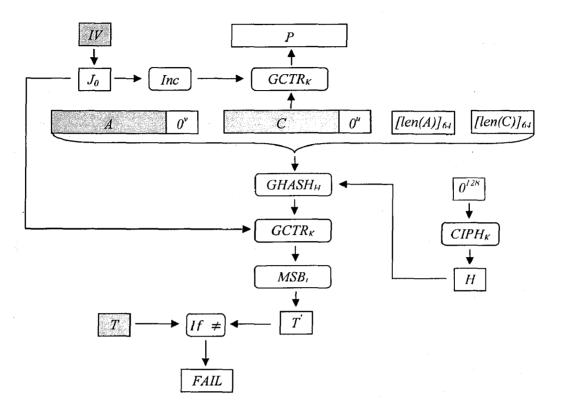

The authenticated decryption function is illustrated in Figure 3.11 below.

Figure 3.11: AES-GCM-AD<sub>K</sub> (IV, C, A, T) = P or FAIL.[4]

# CHAPTER 4

# PARALLEL MULTIPLIER DESIGNS FOR GCM

Due to the feedback chaining present for the Galois multiplication operation in the GCM, pipelined designs have generally chosen parallel multipliers to complete the multiplication step in a single clock cycle. There are two type of multiplier fulfilling these criteria. First is, Mastrovito multiplier, it has been a prime choice for its low critical path but it unfortunately has a quadratic space complexity. Second is, A popular Subquadratic multiplier based on the Karatsuba multiplication algorithm (KA).

A comparison of these parallel multipliers, with FPGA implementation results will be provided toward the end of the chapter. The multipliers are designed specifically for the GCM operation but may be generalized for other applications as well.

## 4.1 Mastrovito Multiplier

The Mastrovito multiplier uses a matrix vector product (MVP) which can compute modulo reduced result in a single step. The matrix used in the operation is constructed from the field defining polynomial, so this method is applicable when a field polynomial or a set of polynomials is known ahead of time which is the case for GCM. The MVP approach is first described before going into Mastrovito multiplier for GCM.

#### 4.1.1 Matrix Vector Product

The original GF multiplication operation given in Eq.(4.1) can be modified to formulate the matrix vector product and the rearranged equation is provided below. The polynomial matrix P is computed using the coefficients of  $A(\alpha)$  while the vector portion is simply the transposed coefficients of  $B(\alpha)$ . The matrix vector product shown here computes the multiplication and reduction operations in a single step.

$$C(\alpha) \equiv A(\alpha) \cdot B(\alpha) \mod F(\alpha)$$

$$C(\alpha) \equiv \sum_{i=0}^{m-1} (\alpha^{i} \cdot a \mod F(\alpha)) \cdot b_{i}$$

$$C = P \cdot b^{T}$$

$$P = \{a^{(0)}, a^{(1)}, a^{(2)}, \dots, a^{(m-1)}\}$$

$$(4.1)$$

In Eq.(4.1), C is the column vector corresponding to the polynomial  $C(\alpha)$ . An expansion of the polynomial matrix P is given in Eq.(4.2). The  $a^{(i)}$  coefficients are essentially column vectors that are modulo reduced versions of  $x^i a \mod F(\alpha)$ .

$$a \equiv a\alpha^{0} \mod F(\alpha)$$

$$a^{(1)} \equiv a\alpha^{1} \mod F(\alpha)$$

$$a^{(2)} \equiv a\alpha^{2} \mod F(\alpha) \equiv a^{(1)}\alpha \mod F(\alpha)$$

$$a^{(3)} \equiv a\alpha^{3} \mod F(\alpha) \equiv a^{(2)}\alpha \mod F(\alpha)$$

$$\dots$$

$$a^{(i)} \equiv a^{(i-1)}\alpha \mod F(\alpha)$$

(4.2)

The first column of P,  $a^{(0)}$  has the coefficients of  $A(\alpha)$  while each subsequent column is the previous column multiplied by  $\alpha$  and modulo reduced by  $F(\alpha)$ . When this matrix is multiplied by the coefficients of  $B(\alpha)$ , the result  $C(\alpha)$  is achieved.

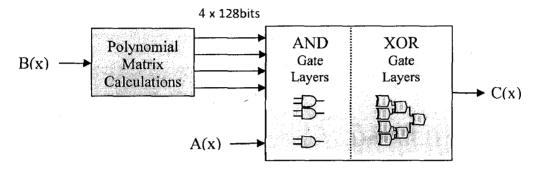

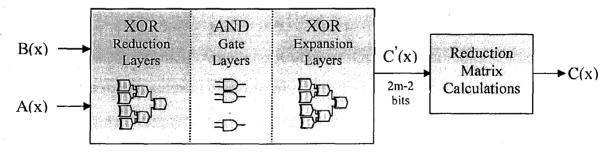

# 4.1.2 Mastrovito Multiplier Design using MVP

The Mastrovito multiplier is a widely used parallel multiplier with a quadratic space complexity [7]. The design is essentially a brute force multiplier in the sense that the MVP is computed like traditional matrix multiplication. It does optimize the operation since the repeated values that are present in the polynomial matrix can be computed once and then reused as signals in hardware for the brute force multiplication portion. Hardware resources are saved to some extent in this way. Elements in P are in GF(2), so AND and XOR gates are used for element wise multiplication and addition respectively. Since the Mastrovito multiplier uses the brute force approach, after computing elements in P, the Mastrovito design has a single layer of AND gates for element multiplication followed by layers of XOR gates to compute the final result. The simplicity of the Mastrovito design is evident in Figure 4.1 which provides an overview of the multiplier. The design is easy to code into a low level design using any hardware description language such as VHDL.

Figure 4.1: Mastrovito Multiplier for GCM.

The area complexity of the Mastrovito multiplier design for the brute force portion is  $m^2$ AND gates while the number of XOR gates is  $m^2 - m$ . The XOR gate count for the polynomial matrix computations will vary based on the field polynomial, and is computed using the Hamming weight of the matrix. For the GCM this is equal to 784 XOR gates.

The time complexity can be summarized as  $T_A + ([log_2m] + [log_2\theta + 1])T_X$ , where  $T_A$  and  $T_X$  is the AND gate and XOR gate delays respectively. The  $\theta$  constant is the maximum Hamming weight from all the columns of the polynomial matrix.

## 4.2 Karatsuba Algorithm Sub-quadratic Multiplier

The Karatsuba Algorithm (KA) was originally used to compute digit multiplication [12], and was mapped to polynomials by [14]. It has a Sub-quadratic area complexity but with a larger delay in comparison with the Mastrovito multiplier. Sub-quadratic multipliers such as KA generally decrease the number of multiplication operations while increasing the number of addition computations. Since the cost of adding GF elements is low and

equivalent to XORing bit streams in hardware, the KA is a suitable approach for GF multiplication. Using divide and conquer techniques the multiplication operation is divided up into smaller and smaller operations followed by an expansion to get the final product. This reduction and subsequent expansion is constructed by levels of XOR operations and as a result causes the delay of the multiplier to increase.

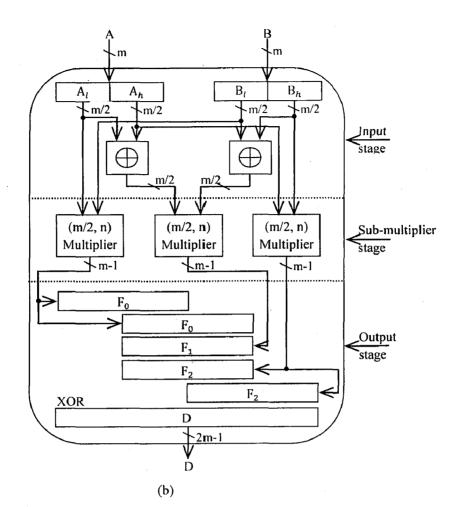

# 4.2.1 KA Multiplier Formulation

The elements  $A(\alpha), B(\alpha) \in GF(2^m)$  are first each split into two polynomials of max degree  $\frac{m}{2} - 1$ .  $A_h$  and  $B_h$  represents the upper polynomial coefficients while  $A_l$  and  $B_l$ represents the lower coefficients of the elements. The following equations show  $A(\alpha)$ split into two smaller polynomial elements,  $A_h$  and  $A_l$ .

$$A(\alpha) = \alpha^{m/2} A_h + A_l$$

$$A_h = (a_{m-1}, a_{m-2}, \dots, a_{\frac{m}{2}+2}, a_{\frac{m}{2}+1})$$

$$A_l = (a_{m/2}, a_{m/2-1}, \dots, a_1, a_0)$$

(4.3)

The multiplication of the two elements in  $GF(2^m)$  is first computed to get a polynomial of max degree  $2m - 2(C'(\alpha))$ . The  $\oplus$  operation represents XORing bit streams in Eq.(4.4) and multiplication operations shown are with sub-polynomials. The original multiplication is divided into three lower degree polynomial multiplications and this can be further split recursively. The  $C'(\alpha)$  element is obtained once the recursion unrolls, and this is then modulo reduced separately to get the final  $C(\alpha)$  element.

$$D_{0}, D_{1}, D_{2} have max degree \frac{m}{2} - 1$$

$$D_{0} = A_{l}B_{l}$$

$$D_{1} = (A_{h} \oplus B_{l})(A_{l} \oplus B_{h}) \qquad (4.4)$$

$$D_{2} = A_{h}B_{h}$$

$$C'(\alpha) = \alpha^{m}D_{2} \oplus \alpha^{\frac{m}{2}}(D_{1} \oplus D_{0} \oplus D_{2}) \oplus D_{0}$$

$$C(\alpha) = C'(\alpha) \mod F(\alpha)$$

#### 4.2.2 Modulo Reduction

Modulo reduction of  $C'(\alpha)$  using the field polynomial can be performed by a multiplication with a fixed reduction matrix. Using the GCM field polynomial as an example, the higher order coefficients of  $C'(\alpha)$  can be modulo reduced based on the following equations.

$$0 \equiv \alpha^{128} + \alpha^7 + \alpha^2 + \alpha + 1 \mod F(\alpha)$$

$$\alpha^{128} \equiv \alpha^7 + \alpha^2 + \alpha + 1 \mod F(\alpha)$$

$$\alpha^{129} \equiv \alpha^8 + \alpha^3 + \alpha^2 + \alpha \mod F(\alpha)$$

(4.5)

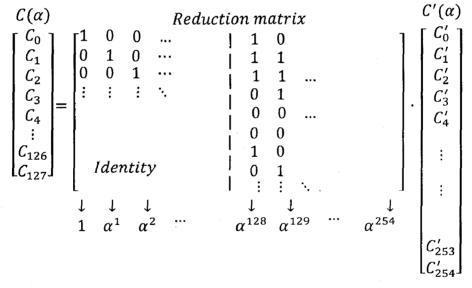

The reduction matrix has 2m - 2 columns and m rows. The matrix essentially maps  $C'(\alpha)$  to  $C(\alpha)$  and is shown in Figure 4.2 for the GCM. The first m columns of the matrix form an identity matrix since elements of degree 1 to m - 1 do not need to be reduced. Using Eq.(4.5), all elements of degree m to 2m - 2 can be modulo reduced and then used in creating the remaining m - 2 columns of the reduction matrix.

Figure 4.2: Reduction matrix for GCM.

The cost of this operation in relation to the KA multiplication is small and is dependent on the field polynomial. The Hamming weight of the reduction matrix for the GCM shows that this operation requires 527 XOR gates. Having low order terms within

the field polynomial helps reduce the cost of the operation since higher order terms have additional feedback terms which increase the cost of the operation. For a field polynomial such as  $\alpha^{128} + \alpha^{40} + \alpha^2 + \alpha + 1$  the cost of the operation is 623 XOR gates. The delay for the reduction operation can be computed by  $([log_2\theta + 1])T_X$ , where  $\theta$  is the largest Hamming weight computed by row of the reduction matrix. For the GCM reduction matrix this delay is computed to be  $3T_X$ .

#### 4.2.3 KA Multiplier Design for GCM

The Karatsuba algorithm generally works best with elements of even degree since each step in the recursion splits polynomials equally. The input element size for the GCM Galois operation is 128 bits, a power of 2, so the KA multiplier can be easily applied without any changes required. A high level view of the Karatsuba multiplier is provided here with all the major components required.

The polynomial elements can be conveniently split down to single element multiplications but this is not always desirable in terms of area efficiency. When the ending condition of the recursion is changed and brute force multiplication per- formed instead, this leads to some savings in terms of AND and XOR gates. The following table shows the number of gates required for halting at different polynomial sizes. The gate counts do not include the reduction operation which has a fixed number of gates and a fixed delay of  $3T_X$ . The ending condition delays are based on the brute force multiplication delay which is  $T_A + log_2(n)T_X$ , where *n* is the halting value.

(a)

Figure 4.3: (a) Abstract view, and (b) Full view of the Karatsuba Multiplier.

| Halt | XOR gates | AND gates | Total gates | NAND gates | Delay         |

|------|-----------|-----------|-------------|------------|---------------|

| 2    | 9913      | 2916      | 12829       | 45484      | $T_A + 19T_x$ |

| 4    | 8455      | 3888      | 12343       | 41596      | $T_A + 17T_x$ |

| 8    | 7969      | 5184      | 13153       | 42244      | $T_A + 15T_x$ |

| 16   | 8455      | 6912      | 15367       | 47644      | $T_A + 13T_x$ |

| 32   | 9913      | 9216      | 19129       | 58084      | $T_A + 11T_x$ |

| 64   | 12415     | 12288     | 24703       | 74236      | $T_A + 9T_x$  |

Table 4.1: Area of KA Multiplier with varied ending conditions.

We can see from Table 4.1 that it is worthwhile halting the KA when the polynomial size is 4 since it provides the lowest area and delay complexity. Since the cost of XOR gates in hardware is usually larger than that of AND gates, in order to get more accurate area estimates for ASIC implementations, the NAND gate count is included. The area

cost of 1 XOR gate is bounded by the area of 4 NAND gates while one AND gate is bounded by the area of 2 NAND gates. When taking the NAND gate count into consideration the results still showed halting at 4 as the optimal choice in terms of area.

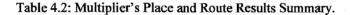

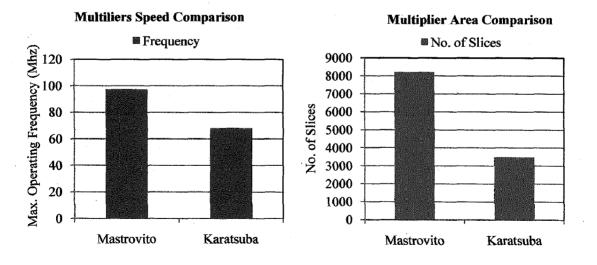

#### 4.3 FPGA Implementation Results

Table 4.2 showing FPGA implementation results and Figure 4.4 showing performance comparison of above discussed multipliers. On analyzing the result we find that, Karatsuba multiplier used 58% (Approx.) less area as compared to Mastrovito because of sub-quadratic complexity nature of former, but cost for small area of Karatsuba have to paid in term of speed, its throughput is 32% (Approx.) less than that of Mastrovito.

The preferences of multiplier mostly depend on type of application and desired critical parameters, otherwise in overall performance Karatsuba proof better than Mastrovito.

| Multiplier | Delay<br>(ns) | Frequency<br>(MHz) | Throughput<br>(Gbps) | Slices | gates  | Kbps/Slice | Power<br>(mW) |

|------------|---------------|--------------------|----------------------|--------|--------|------------|---------------|

| Mastrovito | 10.260        | 97.465             | 12.476               | 8,229  | 85,161 | 1516.10    | 990           |

| Karatsuba  | 14.705        | 68.004             | 8.706                | 3,486  | 40,497 | 2497.42    | 1438          |

Figure 4.4: Multiplier performance comparison.

# CHAPTER 5

# **FPGA IMPLEMENTATION OF AES-ECB ARCHITECTURES**

This chapter includes details of proposed architectures of AES in ECB mode and discussion on their implementation result followed by comparison with previous claim. Section 5.1 cover iterative compact single round AES design, which is optimize for small area and section 5.2 describe pipeline based high speed architecture of AES.

## 5.1 Compact Single Round AES Design