## DESIGN AND SIMULATION OF 32 BIT ALU BASED ON FEEDBACK SWITCH LOGIC

#### **A DISSERTATION**

# Submitted in partial fulfillment of the requirements for the award of the degree of

## MASTER OF TECHNOLOGY

#### ELECTRONICS AND COMMUNICATION ENGINEERING (With Specialization in Semiconductor Devices & VLSI Technology)

By

PATANJALI PRAKASH

DEPARTMENT OF ELECTRONICS AND COMPUTER ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE -247 667 (INDIA) JUNE, 2009

#### **CANDIDATE'S DECLARATION**

I hereby declare that the work, which is being reported in this dissertation report, entitled "Design and Simulation of 32 bit ALU based on Feedback Switch Logic", is being submitted in partial fulfillment of the requirements for the award of the degree of Master of Technology in Semiconductor Devices and VLSI Technology, in the Department of Electronics and Computer Engineering, Indian Institute of Technology, Roorkee is an authentic record of my own work, carried out from June 2008 to June 2009, under the guidance and supervision of Dr. A. K. Saxena, Professor, Department of Electronics and Computer Engineering, Indian Institute of Technology, Roorkee.

The results embodied in this dissertation have not submitted for the award of any other Degree or Diploma.

Date : 24-06-2009 Place : Roorkee

Patanjali Prakash

#### CERTIFICATE

This is to certify that the statement made by the candidate is correct to best of my knowledge and belief.

Dr. A. K. Saxena

Professor

#### ACKNOWLEDGEMENT

At the outset, I express my heartfelt gratitude to Dr. A.K Saxena, Professor, Department of Electronics and Computer Engineering at Indian Institute of Technology Roorkee, for his valuable guidance, support, encouragement and immense help. I consider myself extremely fortunate for getting the opportunity to learn and work under his able supervision. I have deep sense of admiration for his innate goodness and inexhaustible enthusiasm. It helped me to work in right direction to attain desired objectives. Working under his guidance will always remain a cherished experience in my memory and I will adore it throughout my life.

My sincere thanks are also due to rest of the faculty in the Department of Electronics and Computer Engineering at Indian Institute of Technology Roorkee, for the technical knowhow and analytical abilities they have imbibed in us which have helped me in dealing with the problems I encountered during the project. I also extend my sincere thanks to all the technical and non-technical staff of VLSI Design Lab for providing me various tools and encouraging me through out my work.

I am greatly indebted to all my friends, who have graciously applied themselves to the task of helping me with ample morale support and valuable suggestions. Finally, I would like to extend my gratitude to all those persons who directly or indirectly helped me in the process and contributed towards this work.

Patanjali Prakash M. Tech. (SDVT)

#### ABSTRACT

This thesis presents the employment of Feedback Switch Logic (FSL) in the development of a 32-bit ALU unit. For the design of ALU, we have chosen Feedback Switch Logic (FSL) because it offers reduced capacitance, fast switching and input-switching dependent activity factor without the need of clock connection.

The Arithmetic Logic Unit is a digital circuit that performs an arithmetic operation (addition, subtraction, etc.) and logic operations (Exclusive-OR, AND, etc.) between two numbers. Demand for performance at low power consumption in today's general purpose processor has put severe limitations on ALU design. ALU are also one of the most power consumed blocks in the processor and are often the possible location of hot-spots. Hence this thesis aims to reduce power consumption and improve performance using FSL.

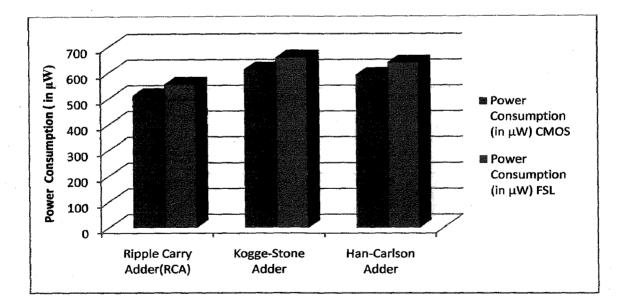

Three types of adders, two types of shifter structures and one logical unit have been designed in FSL and static CMOS logic styles. Comparisons are drawn among the various designed units and the best one in terms of high speed and low power is chosen. Finally we have done the proper organization of adders, shifter and logic unit to make complete ALU.

Simulations have been performed in CADENCE Virtuoso Front to Back Design Environment on 90nm technology node. Simulation results show that 14% increase in speed has been achieved with FSL trading-off with an 8% increase in power consumption when compared to static CMOS logic.

## **CONTENTS**

| Candidate's   | declaration and certificate  | i    |

|---------------|------------------------------|------|

| Acknowledg    | gement                       | ii   |

| Abstract      |                              | iii  |

| List of Figur | res                          | vi   |

| List of Table | es                           | vii  |

| List of Abbr  | eviations                    | viii |

| Chapter 1:    | Introduction                 | 1    |

| 1.1           | Background                   | 1    |

| 1.2           | Thesis Contribution          | 2    |

| 1.3           | Thesis Organization          | 3    |

| Chapter 2:    | Feedback Switch Logic (FSL)  | . 4  |

| 2.1           | Introduction                 | 4    |

| 2.2           | Operation and Analysis       | 8    |

| 2.3           | Simulation Results           | 11   |

| Chapter 3:    | Design of an Adder           | 13   |

| 3.1           | Adders                       | 14   |

|               | 3.1.1 Basics of Adder        | 14   |

|               | 3.1.2 Ripple Carry Adder     | 15   |

|               | 3.1.3 Carry Look-ahead Adder | 16   |

| 3.2           | Prefix Adder                 | 18   |

|               | 3.2.1 Kogge-Stone Adder      | 19   |

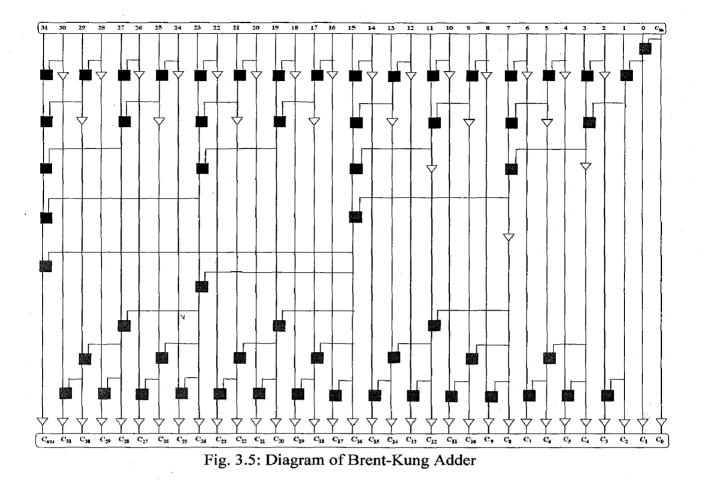

|               | 3.2.2 Brent-Kung Adder       | 19   |

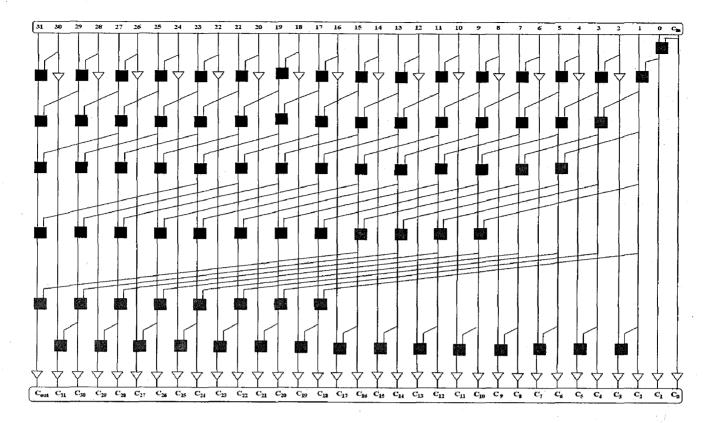

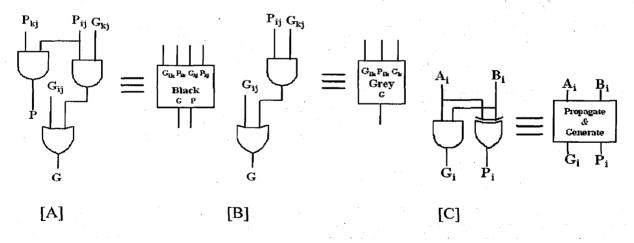

|               | 3.2.3 Han-Carlson Adder      | 20   |

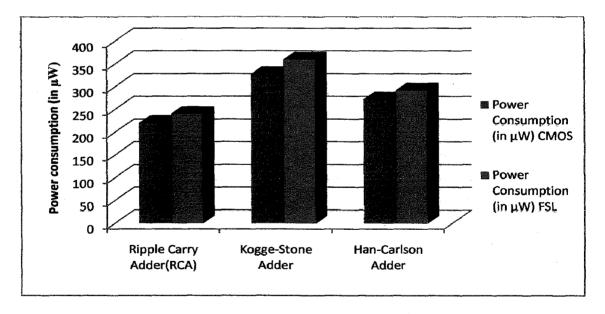

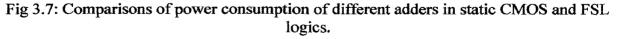

| 3.3           | Adder Comparisons            | 22   |

| Chapter 4:    | Shifter Design               | 24   |

| 4.1           | Array Shifter                | 24   |

| 4.2           | Barrel Shifter               | 26   |

| 4.3           | Logarithmic Shifter          | 27   |

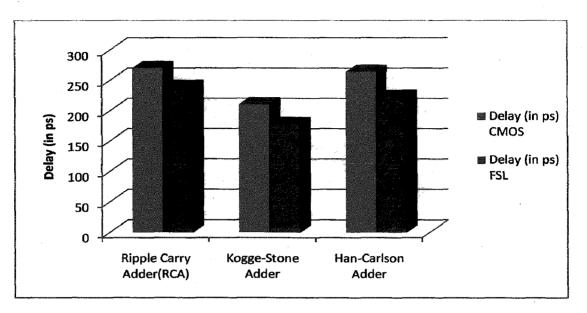

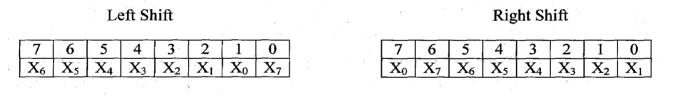

| 4.4           | Design of Cyclic Shifter     | 28   |

|            | 4.4.1 Cyclic Array Shifter       | 29 |

|------------|----------------------------------|----|

|            | 4.4.2 Cyclic Logarithmic Shifter | 29 |

| 4.5        | Simulation Results               | 33 |

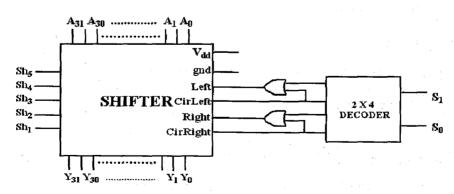

| Chapter 5: | ALU Design                       | 35 |

| 5.1        | Introduction                     | 35 |

| 5.2        | ALU Architecture                 | 35 |

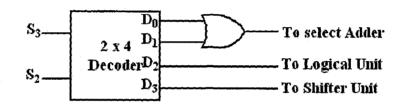

|            | 5.2.1 Control Unit               | 37 |

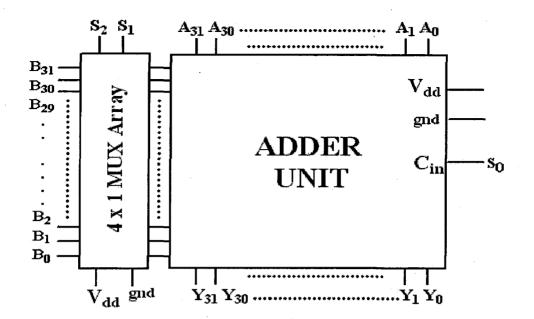

|            | 5.2.2 Arithmetic Unit            | 37 |

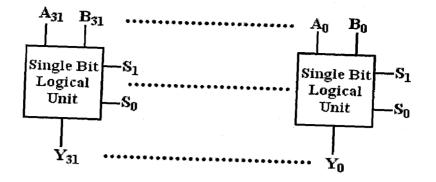

|            | 5.2.3 Logical Unit               | 39 |

|            | 5.2.4 Shifter Unit               | 40 |

| 5.3        | Performance and Results          | 42 |

| Chapter 6: | Conclusions                      | 47 |

| 6.1        | Conclusion                       | 47 |

| 6.2        | Future Scope                     | 48 |

| References |                                  | 49 |

v

#### Fig. No. Title of Fig. Page No. Fig. 1.1 Basic ALU Structure [1] 2 Fig. 2.1(a) A Possible Structure 1 of FSL Logic [2] 7 Fig. 2.1(b) A Possible Structure 2 of FSL Logic [2] 7 Fig. 2.2(a) A NAND/AND gate based on Structure 1 of FSL Logic 8 Fig. 2.2(b) A NAND/AND gate based on Structure 2 of FSL Logic 8 Fig. 2.2(c) A NOR/OR gate based on Structure 1 of FSL Logic 9 Fig. 2.2(d) A NOR/OR gate based on Structure 2 of FSL Logic 9 Fig. 2.3 FSL NAND/AND operation 10 Fig. 2.4 FSL NOR/OR operation 10 Fig. 2.5 Comparisons of power consumption of different logic gates in static CMOS and FSL logics 11 Fig. 2.6 Comparisons of power consumption of different logic gates in static CMOS and FSL logics 12 Fig. 3.1 4-bit Ripple Carry Adder 15 Fig. 3.2 A Single-Bit Mirror Full Adder [12] 16 Fig. 3.3 4-bit Carry Look-ahead Adder 17 Fig. 3.4 Diagram of Kogge-Stone Adder 19 Fig. 3.5 Diagram of Brent-Kung Adder 20 Fig. 3.6 Diagram of Han-Carlson Adder 21 Fig. 3.7 Different blocks in prefix adders, (A) Black block, (B) Grey block (C) Propagate and Generate block 21 Comparisons of power consumption of different adders in Fig. 3.8 static CMOS and FSL logics 22 Comparisons of delays of different adders in static CMOS Fig. 3.9 and FSL logics 23 Fig. 4.1 Structure of an Array Shifter [20] 25 Fig. 4.2 A simple one Bit Bidirectional Array Shifter [5] 25 Fig. 4.3 A 4-Bit Barrel Shifter [5] 26 Fig. 4.4 A 4-Bit Right Shift Logarithmic Shifter [5] 27 Fig. 4.5 A Structure of Logarithmic Shifter [5] 28

## **List of Figures**

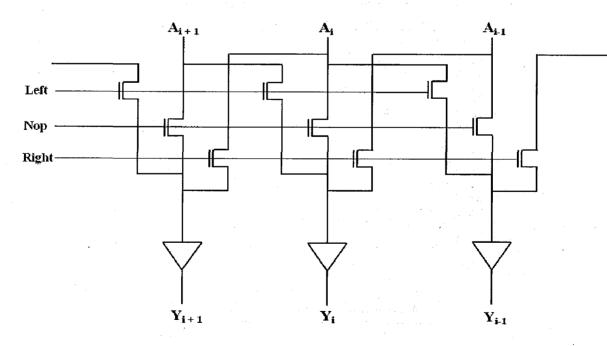

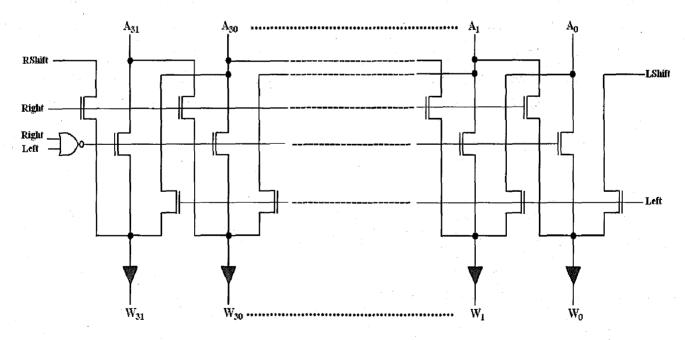

| Single Bit Array Shifter                                     | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

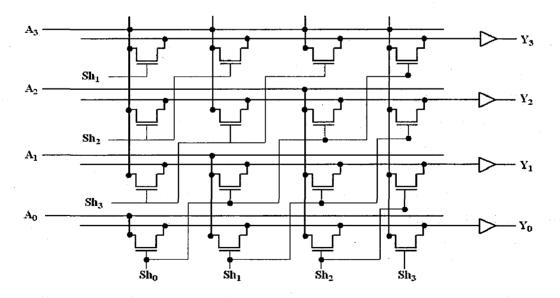

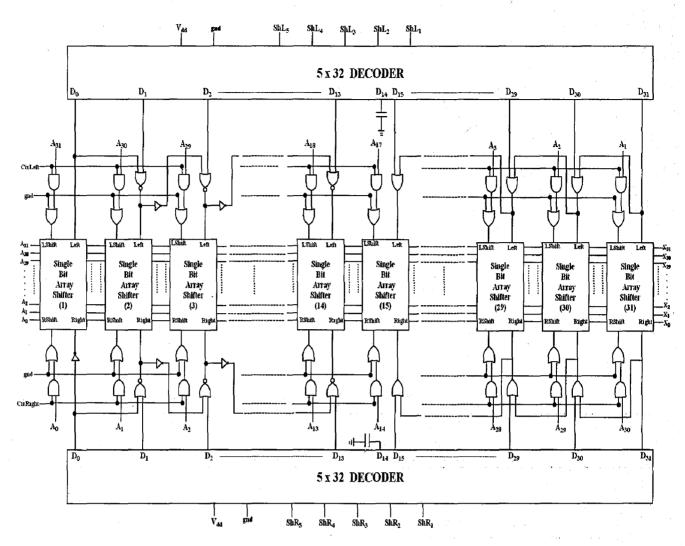

| Cyclic Array Shifter                                         | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

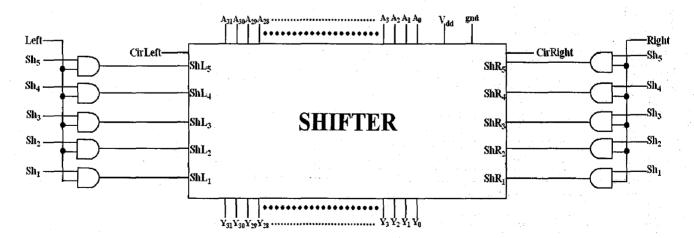

| Final schematic of cyclic enable shifter                     | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

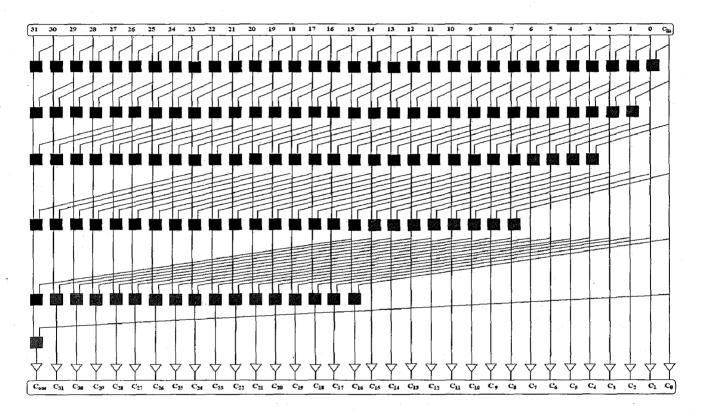

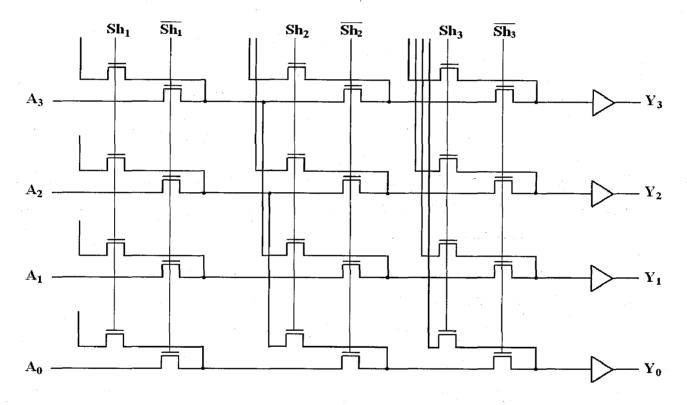

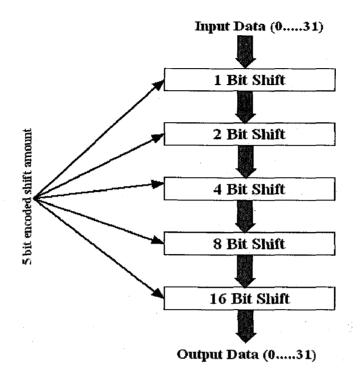

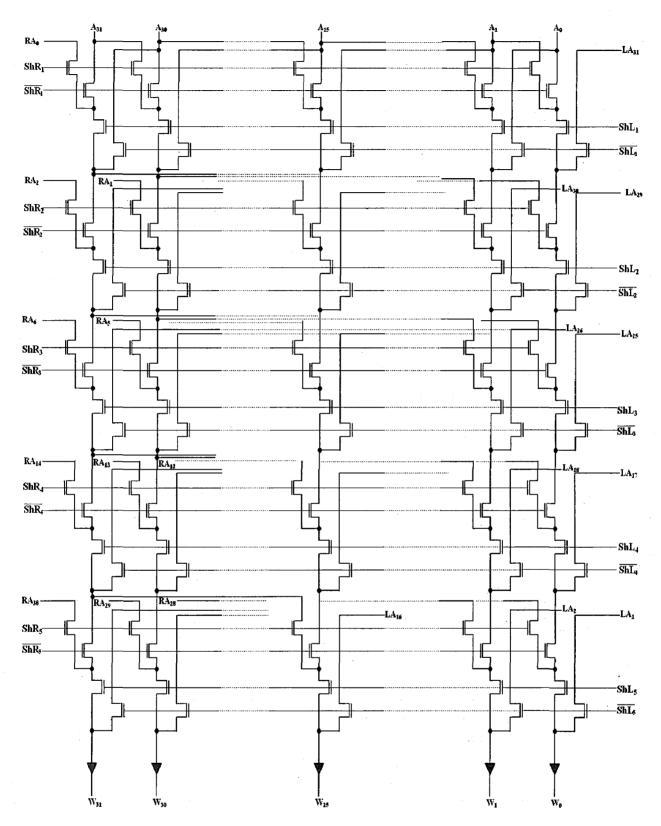

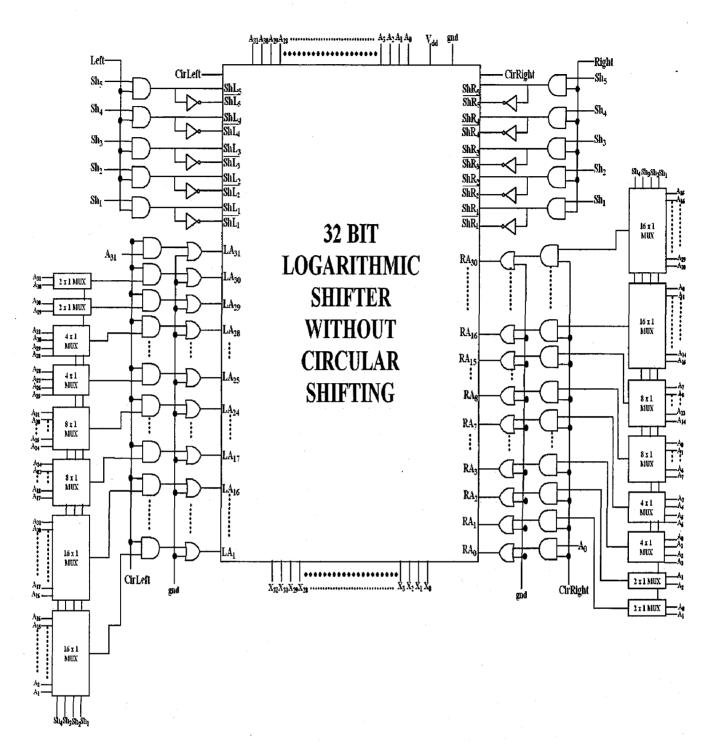

| 32 Bit Logarithmic Shifter without circular shifting         | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 32 Bit Cyclic Enable Logarithmic Shifter                     | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

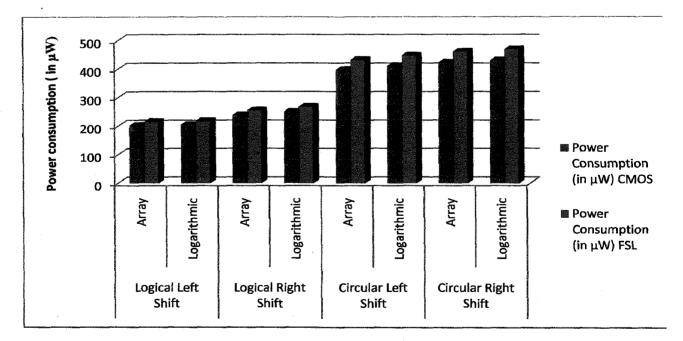

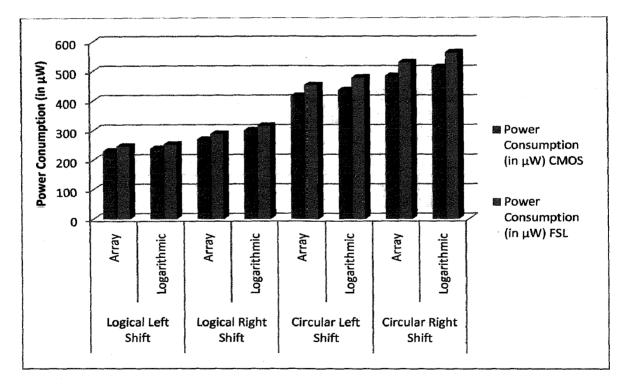

| Comparisons of power consumption of different shifters in    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| static CMOS and FSL logics                                   | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

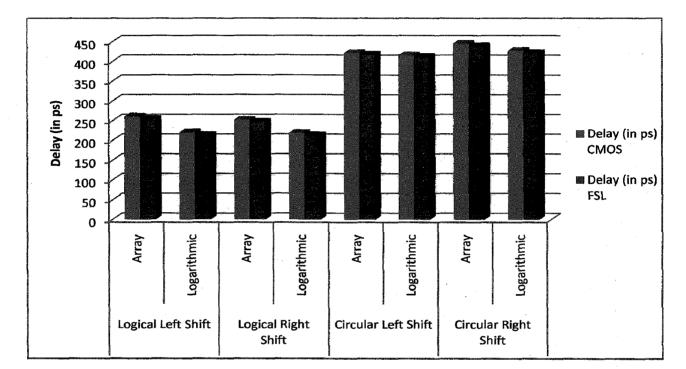

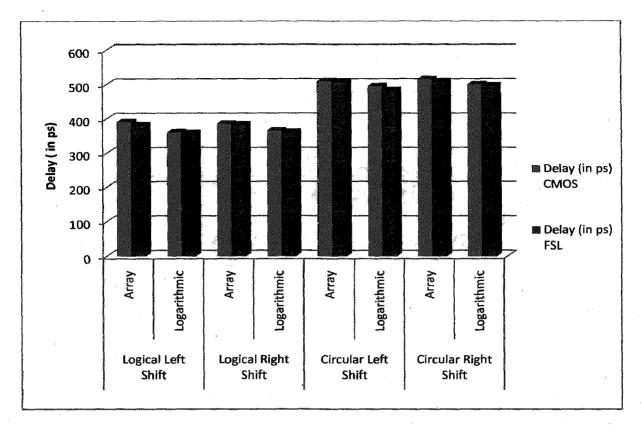

| Comparisons of delay of different shifters in static CMOS    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| and FSL logics                                               | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

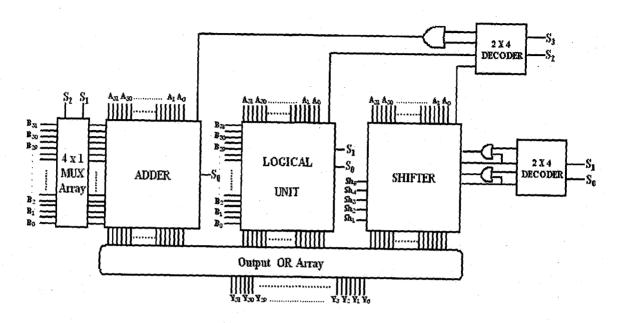

| Implemented Design of ALU                                    | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Control Unit of ALU                                          | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| An Arithmetic Unit of ALU                                    | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

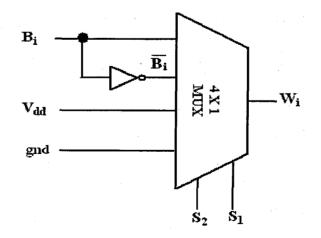

| A Symbol of 4x1 Mux                                          | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| The Logical Unit of ALU                                      | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| A Single Bit Logical Unit for Logical Unit of ALU            | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| A Shifter Unit of ALU                                        | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Comparisons of power consumption in arithmetic operations in |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| static CMOS and FSL logics                                   | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

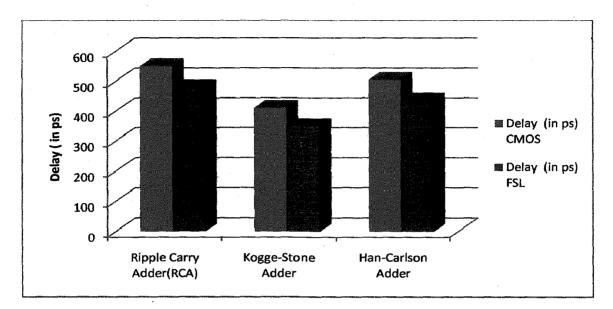

| Comparisons of delay in arithmetic operations in static      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CMOS and FSL logics                                          | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

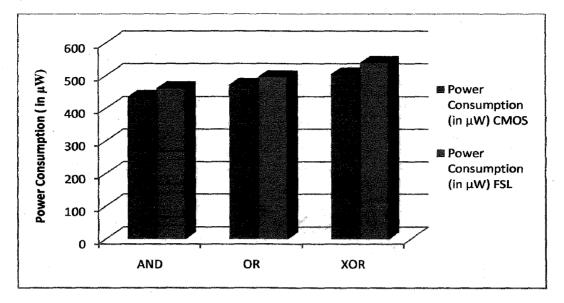

| Comparisons of power consumption in logical operations in    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| static CMOS and FSL logics                                   | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

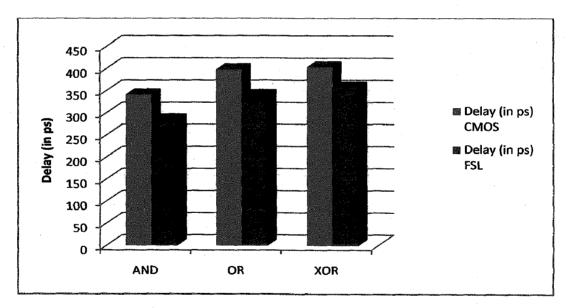

| Comparisons of delay in logical operations in static CMOS    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| and FSL logics                                               | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Comparisons of delay in shifting operations in static CMOS   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| and FSL logics                                               | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Comparisons of power consumption in shifting operations in   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| static CMOS and FSL logics                                   | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                              | Cyclic Array Shifter<br>Final schematic of cyclic enable shifter<br>32 Bit Logarithmic Shifter without circular shifting<br>32 Bit Cyclic Enable Logarithmic Shifter<br>Comparisons of power consumption of different shifters in<br>static CMOS and FSL logics<br>Comparisons of delay of different shifters in static CMOS<br>and FSL logics<br>Implemented Design of ALU<br>Control Unit of ALU<br>An Arithmetic Unit of ALU<br>An Arithmetic Unit of ALU<br>A Symbol of 4x1 Mux<br>The Logical Unit of ALU<br>A Single Bit Logical Unit for Logical Unit of ALU<br>A Shifter Unit of ALU<br>Comparisons of power consumption in arithmetic operations in<br>static CMOS and FSL logics<br>Comparisons of delay in arithmetic operations in static<br>CMOS and FSL logics<br>Comparisons of power consumption in logical operations in<br>static CMOS and FSL logics<br>Comparisons of delay in logical operations in static CMOS<br>and FSL logics<br>Comparisons of delay in shifting operations in static CMOS<br>and FSL logics<br>Comparisons of delay in shifting operations in static CMOS<br>and FSL logics<br>Comparisons of delay in shifting operations in static CMOS<br>and FSL logics<br>Comparisons of delay in shifting operations in static CMOS<br>and FSL logics<br>Comparisons of delay in shifting operations in static CMOS<br>and FSL logics<br>Comparisons of delay in shifting operations in static CMOS<br>and FSL logics |

## List of Tables

| Table No. | Title of table                                          | Page No. |

|-----------|---------------------------------------------------------|----------|

| Table 2.1 | Summary of simulation results for various logical gates | 11       |

| Table 3.1 | Generate and propagate information for a CLA            | 16       |

| Table 3.2 | Summary of simulation results for various adders        | 22       |

| Table 4.1 | Summary of simulation results for shifters              | 33       |

| Table 5.1 | Functional table of the designed ALU                    | 36       |

| Table 5.2 | Functional table of the control unit                    | 37       |

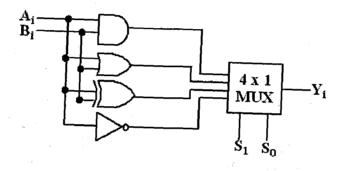

| Table 5.3 | Functional table of the $4x1$ multiplexer (MUX)         | 39       |

| Table 5.4 | Functional table of the arithmetic Operation            | 39       |

| Table 5.5 | Functional table of the logical unit                    | 40       |

| Table 5.6 | Functional table of the shifter unit                    | 41       |

| Table 5.7 | Summary of simulation results for arithmetic operation  |          |

|           | in designed ALU                                         | 42       |

| Table 5.8 | Summary of simulation results for logical operation in  |          |

|           | designed ALU                                            | 43       |

| Table 5.9 | Summary of simulation results for shifting operation in |          |

|           | designed ALU                                            | 45       |

## List of Abbreviations

| Abbreviation | Meaning                                   |

|--------------|-------------------------------------------|

| ALU          | Arithmetic Logic Unit                     |

| VLSI         | Very Large Scale Integration              |

| IC           | Integrated Circuit                        |

| DCT          | Discrete Cosine Transform                 |

| FSL          | Feedback Switch Logic                     |

| CMOS         | Complementary Metal Oxide Semiconductor   |

| CVSL         | Cascode Voltage Switch Logic              |

| DCVSL        | Differential Cascode Voltage Switch Logic |

| RCA          | Ripple Carry Adder                        |

| LSB          | Least Significant Bit                     |

| MSB          | Most Significant Bit                      |

| CLA          | Carry Look-ahead Adder                    |

| DSP          | Digital Signal Processing                 |

| MUX          | Multiplexer                               |

ix

## Chapter 1 Introduction

#### 1.1 Background

Much of the research effort of the past years in the area of digital electronics has been directed towards increasing the speed of digital systems. But due to the demand and popularity of portable electronics, designers are striving to achieve smaller silicon area, higher speeds, longer battery life and more reliability. Power is one of the premium resources to which a designer tries to save when designing a system. However, the advancement of digital computer technology requires higher circuit speed also.

The three most widely accepted parameters to measure the quality of a circuit or to compare various circuit styles are area, delay and power dissipation. Portability imposes a strict limitation on power dissipation while still demanding high computational speeds. Hence, in recent VLSI systems, the power delay product becomes the most essential metric of performance. The reduction of power dissipation and the improvement of speed requires optimization at all levels of the design procedure.

Arithmetic Logic Units (or ALUs) are important components in many moderns IC such as processors and re-configurable cores. Demand for performance at low power consumption in today's general purpose processors has put severe limitations on ALU design. ALUs are also one of the most power hungry sections in the processor and are often the possible location of hot-spots. The presence of multiple ALUs in superscalar pipelines further deteriorates the power and thermal issues. Technology scaling has resulted in faster devices but at the same time, the die-to-die delay variations have increased due to different lithographic subtleties. Therefore, low power ALU design while maintaining high yield under tighter delay constraint turns out to be a multidimensional problem [1].

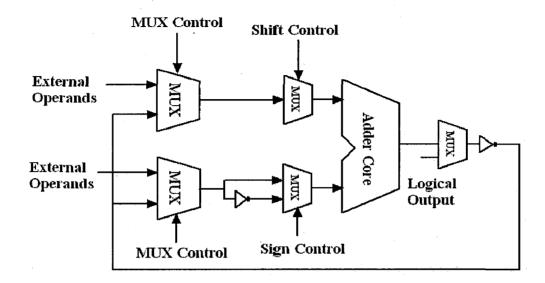

ALU is the heart of a microprocessor and the adder cell is the elementary unit of an ALU. It is basically a combinational circuit that performs a number of arithmetic and logic functions. Hence, its performance is crucial for the design of high performance digital computer system. The basic structure of the ALU is shown in Fig. 1.1. It consists of input

(1)

multiplexers, adder core and an output multiplexer. The adder takes operands from register file, data cache or ALU write-back bus. The input multiplexers select the proper operands among these and provide the ALU inputs. The adder output is multiplexed with the logical output through an output multiplexer.

Fig. 1.1: Basic ALU Structure [1].

Since multiplication is a less frequent operation than addition/subtraction/shift operation, the multipliers are usually isolated from the ALU. This also ensures high speed operations of the more frequent instructions in processors. However, for signal processing applications (e.g., filters, DCT), multipliers can be an integral part of the ALU.

#### **1.2** Thesis Contribution

The aim of this thesis is to design a 32-bit low power, high speed logic ALU based on Feedback Switch Logic (FSL) [2]. FSL offers low power consumption and high speed because of fast switching, reduced capacitance and input-switching dependent activity factor without the need of clock connection. The objectives of the thesis are following:

- Study the concept of low power high speed logic, which is Feedback Switch Logic (FSL).

- Design different adders using static CMOS logic and FSL.

- Estimation and comparison of power consumption and delay of different adders with static CMOS logic and FSL logic.

- Design of various shifters using static CMOS and FSL logics.

- Extraction and comparison of power consumption and delay of shifter with both the logics.

- Design of 32-bit ALU by taking best adders and shifters from comparisons in terms of speed and power consumption using static CMOS and FSL logics.

- Finally, power consumption and delay of 32-bit ALU using static CMOS and FSL logics are calculated and compared.

#### **1.3** Thesis Organization

The thesis organization is as follows:

Chapter 2 gives an overview of FSL. This chapter presents the overview of our new logic Feedback Switch Logic. A comparative study between various logics is done, followed by various simulation results and discussions.

In chapter 3, designs of different adders using static CMOS and FSL are presented. It also discusses about comparison results of different adders using both the logics.

Chapter 4 presents design of different shifter units. These shifters are capable of bidirectional and cyclic shifting up to 31-bits and it also presents simulation results and comparison of these shifters using static CMOS logic and FSL in terms of speed and power consumption.

In chapter 5, implementation details of 32-bit ALU have been discussed and simulation results are also presented.

Chapter 6 concludes the thesis and discusses future scope of work.

#### Chapter 2

### Feedback Switch Logic (FSL)

#### 2.1 Introduction

Since the invention of CMOS, speed improvement has been the main goal in the research of both circuit design and device design. Designing high speed low power circuits with CMOS technology has been a major research problem for many years. Several logic families have been proposed to improve circuit performance beyond static CMOS family [3].

In deep submicron technologies, the performance benefits obtained from process scaling decreases as feature size decreases, hence fast circuit families become more attractive now a days. Static CMOS logic is widely used due to its features like low power dissipation, ease of design and higher stability. Static CMOS logic gate is built up by pull up (PUN or PMOS network) and pull down network (PDN or NMOS network). The advantage of having both pull up and pull down networks is that except for the very brief period when the output or the inputs are making transitions, no current flows and no power is consumed. The problem with this fully complementary approach is that for complex gates, substantial amounts of area can be wasted. As a result of the extra area and extra transistors, the capacitive loads on gates of a fully complementary circuit are very high. Each output goes to both a PMOS and NMOS transistors in every gate it drives. PMOS transistor are generally twice the size of NMOS transistor to obtain more balanced rise and fall times. As a result, the total gate load on each output will be three times higher. Hence even though static CMOS consumes less power and gives good noise margin but it slows down the circuit speed.

In order to remove the above problems, many dynamic circuit schemes have been described [4], but they all show some basic features as a common one. Basically, they involve pre charging the output node to a particular level (usually high for NMOS), while the current path to the other level (ground for NMOS) is turned off. Any charging of inputs to the gate must occur during the pre charge phase. At the completion of pre charge, the path to the high level is turned off by a clock and the path to ground is turned

on. Then depending on the state of the inputs, the output will either float at the high level or will be pulled down. The advantage of dynamic circuit is that it has lesser load capacitance on gates than static CMOS logic. In addition, there is no static current path, so power would be much closer to CMOS. However, there are serious problems involved in realizing these apparent speed advantages in real circuits. This happens because useful circuits generally have several logic gates in series and in the dynamic approach, no gate can be activated until its inputs have been stabilized. In practice, considerably more than one gate delay would be needed between successive edges to assure a full gate delay in worst case. Overall then, in a circuit of reasonable complexity, the dynamic approach would not be any faster than conventional CMOS logic [4].

A Domino logic consists of an n-type dynamic logic block followed by a static inverter, so only noninverting logic can be implemented. In domino logic, during precharge, the output of the n-type dynamic gate is charged up to  $V_{dd}$ , and the output of the inverter is set to 0. During evaluation, the dynamic gate conditionally discharges and the output of the inverter makes a conditional transition from  $0 \rightarrow 1$ . Due to static inverter, it has additional advantage that the fan-out of the gate is driven by a static inverter with a lowimpedance output which increases noise immunity [5].

Domino logic allows high-speed circuit design due to the low switching threshold of dynamic gates and their reduced load capacitance and also the ability to implement complex functions in a single gate. On the other hand, domino logic suffers from high switching activity since the activity factor of a dynamic gate is input-state dependent and the gate switches twice a cycle. However, unlike static logic, domino logic does not allow false outputs before a gate settles down to its correct output which helps in reducing the activity overhead of domino circuit. One of the drawbacks of domino logic is the inability to recover after noise upsets. Noise tolerant pre charge solves this problem at the price of increased gate capacitance [6]. Another major disadvantage of domino logic is the inability in the need to deliver the clock signal to every gate, which in turn increases power, routing area and design complexity.

However, the inability of inversion in domino logic poses another major limitation on widely using this high speed circuit family. Dual rail domino, which is a derivative of the differential Cascode Voltage Switch Logic (CVSL) family [7], solves this problem by implementing the logical function and its complement.

(5)

The static version of Differential Cascode voltage switch (DCVSL) is a differential style of logic that provides the complementary outputs with true and complementary inputs to the gate. When the input switches, output of the DCVSL gate and its complement are pulled either high or low. This static version slowly transits and highly consumes current since the PMOS pull-up fights the NMOS pull-down trees during the switching period. To increase the performance and reduce the power consumption, many clocked versions of the DCVSL gate have been introduced [7].

One of clocked CVSL is a dual-rail domino logic which combines both domino and CSVL logic in order to solve the problems of both families. Dual-rail domino does not suffer from contention problems, which makes it as fast as standard domino. Also, dual rail domino logic provides both inverting and non-inverting functions, which makes it easy to use in digital logic design. The main disadvantage of dual rail domino gate is its unity activity factor since an evaluate/precharge transition is guaranteed at every cycle regardless of the input activity or input states. Therefore, dual-rail domino logic suffers from high power consumption due to the extra clocking power. Also, dual-rail domino can not recover from noise upsets similar to standard domino logic.

Feed back switch logic [2] is an improved design among all these logic families. This is a dynamic like static circuit family suitable for high speed and low power circuit designs. It is free from contention problem of clocked CVSL. The major advantage of FSL is fast switching speed, reduced capacitance, and input-switching dependent activity factor without the need of clock connection.

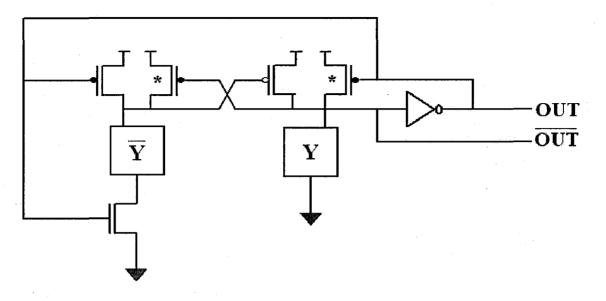

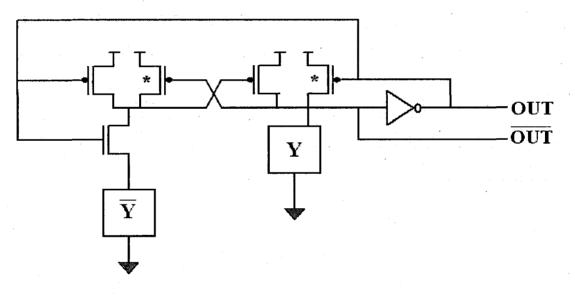

FSL is a clock less differential circuit family that provides the output and its complement from a single side of the gate. Fig. 2.1(a) and (b) present two possible structures of FSL gates. In this work, FSL structure shown in Fig. 2.1(a) has been considered. However, the structure in Fig. 2.1(b) can be useful for FSL tree implementations since it allows transistor sharing between complementary networks. Similar to CVSL, the logic function and its complement in FSL are implemented using NMOS networks. Also, two cross coupled PMOS pull-ups are employed. However, one of these pull-ups is a weak keeper and the other one is a strong output driver. The latter provides high drive current during a low-to-high  $\overline{OUT}$  transition, while it does not affect the high-to-low transition due to the output feedback that turns it off when it is not needed. The feedback acts as a switch that decides which of the two pull-down networks should be used to provide the functionality of the gate based on the current output state.

Fig 2.1(a): A Possible Structure 1 of FSL Logic [2].

Fig 2.1(b): A Possible Structure 2 of FSL Logic [2].

FSL takes the advantage of the fact that low-to-high transitions are the speed-critical transitions for all CVSL circuit families since only NMOS networks are used, while high-to-low transitions are less important in terms of speed. Therefore, the high-to-low transition can follow its complementary low-to-high transition, while the speed is effectively based on the earlier low to-high transition. Thus, even though a signal in an FSL gate can pass through three serial stages in the worst case, which are  $\overline{OUT}$ , OUT, and the output inverter stage, the effective FSL gate delay is always based on two stages. FSL

offers the switching speed of dynamic logic, while providing activity-dependent switching behavior similar to static logic without the need of a clock connection. However, FSL is slower than dynamic logic since the load of a gate is driven from a single side.

#### 2.2 Operation and Analysis:

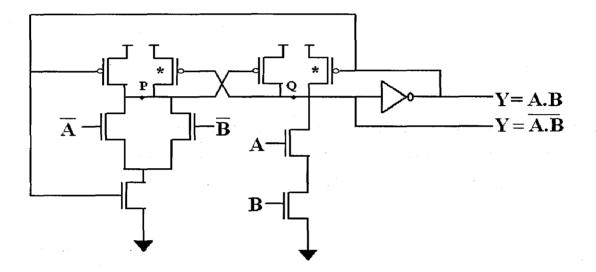

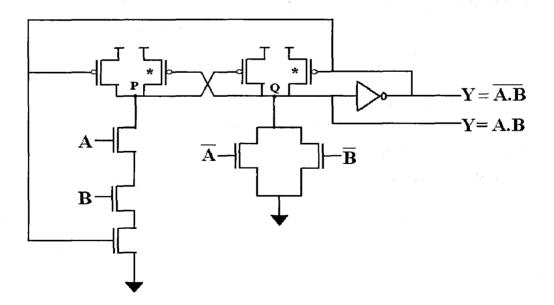

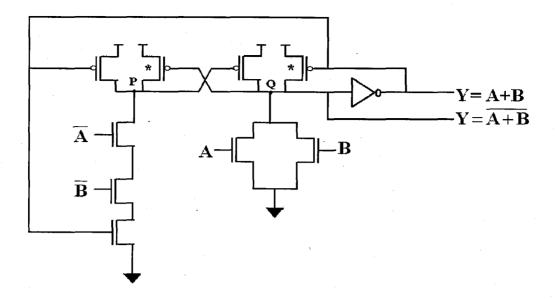

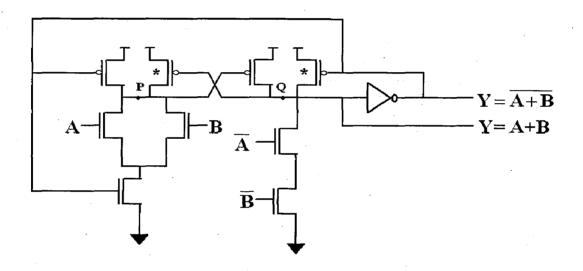

There are two possible FSL structures for any basic logic gate. In Fig 2.2 (a-d) two-inputs NOR/OR and NAND/AND gates based on FSL are shown. To understand the operation of FSL based gate, consider figure 2.2(a).

Fig 2.2(a): A NAND/AND gate based on Structure 1 of FSL Logic.

Fig 2.2(b): A NAND/AND gate based on Structure 2 of FSL Logic.

(8)

Fig 2.2(c): A NOR/OR gate based on Structure 1 of FSL Logic.

Fig 2.2(d): A NOR/OR gate based on Structure 2 of FSL Logic.

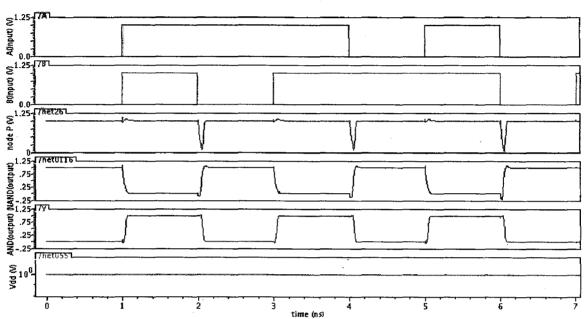

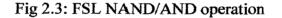

In Fig.2.2 (a), when Y is on and  $\overline{Y}$  is off, the NAND node is at state "0" and the AND node is at state '1', the feedback-driven NMOS and PMOS are on and off, respectively, and node P is high. When Y turns off and  $\overline{Y}$  turns on, node P discharges since it is held high by weak transistor. While the strong PMOS pulls, the NAND node is high which inturn discharges the AND node causing node P to charge again turning off the strong PMOS driver. Now the state of the gate is held at node  $\overline{Y}$  by a weak feedback keeper and  $\overline{Y}$  is ready to evaluate and so on. The simulation waveforms of 2-input NAND/AND gate is shown in Fig. 2.3 From the simulation waveforms, node P is high all the time except when  $\overline{Y}$  turns on where a fast and short high low high pulse appears. This gives FSL gate an extra advantage by making a strong speed critical PMOS device tolerant against aging and Negative Bias Temperature Instability (NBTI) effects. Similarly for NOR/OR operation in FSL, simulated waveform is shown in Fig. 2.4.

Transient Response

(10)

#### 2.3 Simulation Results

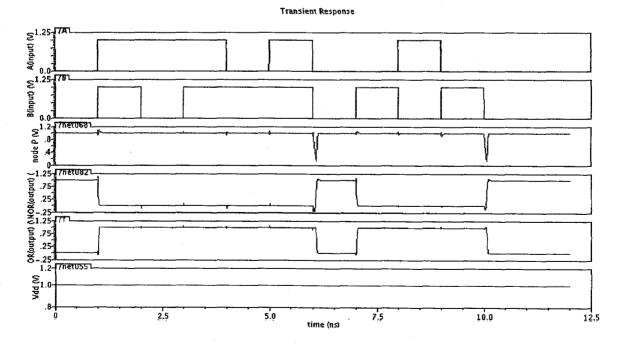

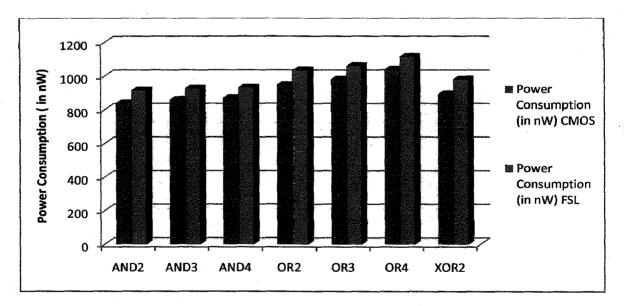

The following are the comparison results of various logic gates using static CMOS and FSL logics.

The power consumption and delay of various logic gates using FSL and static CMOS are tabulated in Table 2.1.

| Logical Gates | Power Consumption<br>(in nW) |        | Delay<br>(in ps) |        |

|---------------|------------------------------|--------|------------------|--------|

|               | CMOS                         | FSL    | CMOS             | FSL    |

| AND2          | 839.3                        | 914.8  | 21.595           | 17.805 |

| AND3          | 860                          | 927.1  | 28.45            | 22.988 |

| AND4          | 871.2                        | 932.2  | 33.205           | 29.552 |

| OR2           | 947.9                        | 1036.1 | 20.275           | 17.213 |

| OR3           | 981.8                        | 1061.3 | 25.725           | 22.021 |

| OR4           | 1040.8                       | 1116.8 | 31.185           | 27.786 |

| XOR2          | 892.5                        | 981.75 | 27.215           | 23.786 |

Table 2.1: Summary of simulation results for various logical gates

The power consumption comparison of different logic gates using FSL and static CMOS logic is shown in Fig.2.4.

Fig 2.4: Comparisons of power consumption of different logic gates in static CMOS and FSL logics.

Since FSL is a combination of static and dynamic logic, the power consumption of logic gates using FSL is very much close to the power consumption of static CMOS gates.

The delay comparison of various logic gates using FSL and static CMOS is shown in Fig.2.5.

Fig 2.5: Comparisons of delays of different logic gates in static CMOS and FSL logics.

From the simulation results logic gates using FSL having lesser delay compared to static CMOS logic because FSL offers reduced capacitance and fast switching.

#### Chapter 3

#### **Design of an Adder**

#### 3.1 Introduction

Addition is one of the fundamental arithmetic operations. It is extensively used in many VLSI systems such as application-specific DSP architectures and microprocessors. In addition to its main task, that is the adding of two binary numbers, it is the nucleus of many other useful operations such as subtraction, multiplication, division, address calculation, etc [8]. In most of these systems, the adder is the part of the critical path that determines the overall performance of the system. That is why enhancing the performance of the adder is a significant goal. It often referred as the speed-limiting element as well [5].

Addition is most often is one of the critical paths of modern day microprocessor. Adder is also the "hot spot" among all other execution units in a processor core. Thus, a fast and energy-efficient adder is essential to a high-performance microprocessor. Implementing fast addition has been an important subject since the 1950s. Ripple carry adder is the first and the most fundamental adder that is capable of performing binary number additions. Since its delay is proportional to the length of its input operands, it is not very useful. Weinberger and Smith [9] have made the first major break-through in speeding-up additions by proposing the well-known scheme, Carry Look-ahead adder [10]. Rather than rippling carries throughout the adder, it uses parallelism to propagate carries much quickly.

There are several levels of hierarchy which can improve addition operations. First, it can be improved at architecture level. By using an algorithm that incorporates a faster carry propagation method such as prefix tree adder schemes, addition time can be reduced. By adding clock gating and sleep mode, power can be saved when the adder is not in use. Multiple power supplies can also be used to supply lower voltage to less critical paths in order to reduce power. For mobile applications, dynamic voltage scaling is a widely used technique to reduce power consumption. It automatically optimizes the supply voltage and the operation frequency for a given workload. To reduce the adder delay and power, one can also improve it at circuit level. For example, selecting dynamic instead of static CMOS logic would improve the speed of operation. Transistor sizing can be used to improve speed and power. A transistor sizing tool parameterizes the sizes of transistors in a circuit based on circuit characteristics such as driver size, load, supply voltage, operating temperature etc. After completing a transistor level design, the customized cell placement can be used, which may produce a better layout than automatic place and route tool. With today's advanced technology, a careful planning of wires and cells before placement is often necessary in achieving a better timing and power.

Finally, speed can be improved at process level. A more advanced process technology can be used. This could be scaling the transistor's feature size, using copper interconnects rather than aluminum interconnects, using SOI (Silicon on Insulator) CMOS technology rather than Bulk CMOS technology, using thinner and higher K dielectric insulator as gate oxide, etc.

#### 3.1. Adders

Adders are basic components of microprocessors and any arithmetic circuit and are frequently on the critical path. Fast adders speed up the addition calculation through a rearrangement of the adder equations or through some intelligent observations about the addition process. While adder speed is essential, adder area is also important, especially for arithmetic circuits that may require many adders. The next few sections would discuss about different adder designs and their comparisons.

#### 3.1.1 Basics of Adder

A multi-bit addition operation can be decomposed into half adder and full adder structures, with fast adders containing some additional circuitry. Half adders and full adders compute the well-known logic functions given as follows:

| Half adder: | Sum = $A \oplus B$ ,         | C <sub>out</sub> =AB     |

|-------------|------------------------------|--------------------------|

| Full adder: | $Sum = A \oplus B \oplus C,$ | $C_{out} = AB + BC + CA$ |

(14)

#### 3.1.2 Ripple Carry Adder

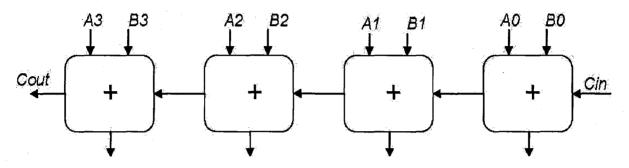

This is the simplest adder circuit. An N-bit ripple carry adder [11] consists of N full adders with the carry signal propagating from one full-adder stage to the next from LSB to MSB. A 4-bit ripple carry adder structure is shown in Fig. 3.1. It consists of four cascaded full adder which takes input A, B and Cin and generates sum and carry out (Cout).

Fig. 3.1: 4-bit Ripple Carry Adder

The ripple carry adder is a good baseline design for comparison with other adders. It has many advantages which include low power, low area and a simple layout. The drawback of the ripple carry adder, though, is its slow speed. The delay of the adder is linearly dependent on the bit-width (N) of the adder. The critical path of the ripple carry adder consists of the carry chain from the first full adder to the last. Therefore, during circuitlevel design, the carry signal is frequently assigned to the transistor closest to the gate output for the carry computation.

Circuits are optimized to produce fast carries because it constitutes a large fraction of the critical path. The delay of a ripple carry adder is given by the following equation [5]:

$$T(RCA) = (N-1) \times T(Carry) + T(Sum)$$

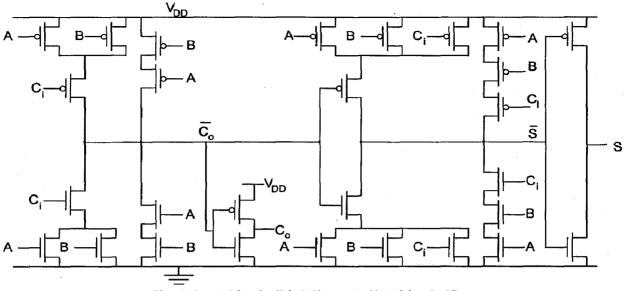

For designing a single bit of full adder for a RCA, we can use different types of full adder as reported by Alioto and Palumbo [12]. For our design of RCA, we used Mirror Full adder [13] as shown in Fig. 3.2. Mirror Full adder CMOS Full adder is a simple implementation of following equations.

$$Sum = A \oplus B \oplus C = ABC + \overline{C_{out}} (A + B + C)$$

Carry (C<sub>out</sub>) = AB + BC + AC = AB + (B + A)C

and

Fig. 3.2: A Single-Bit Mirror Full Adder [12].

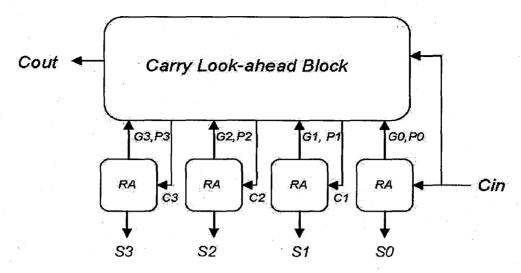

#### 3.1.3 Carry Look-ahead Adder

The Carry Look-ahead Adder (CLA) is theoretically one of the fastest methods for addition. Weinberger and Smith invented the CLA in 1958 [9]. The CLA uses intermediate information to determine in advance if there will be a carry out of a given bit position. Table 3.1 shows the truth table for a full adder, including this extra carry information. For the delete condition, there will be no carry out of the bit position. For the propagate condition, there will only be a carry out if there is a carry in. For the generate/propagate condition, there will always be a carry out at that position.

| Α | B  | C  | Sum | Cout | Condition          |

|---|----|----|-----|------|--------------------|