# HARMONICS AND VOLTAGE STABILITY ANALYSIS IN POWER SYSTEMS USING FACTS BY THYRISTOR-CONTROLLED REACTOR

# **A DISSERTATION**

Submitted in partial fulfillment of the requirements for the award of the degree

of

MASTER OF TECHNOLOGY

in

## ALTERNATE HYDRO ENERGY SYSTEMS

By

# **RUDRA RAMESHWAR**

ALTERNATE HYDRO ENERGY CENTRE INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE - 247 667 (INDIA)

JUNE, 2007

I hereby declare that the work is being presented in the dissertation entitled "Harmonics and Voltage Stability Analysis in Power Systems using FACTS by Thyristor Controlled Reactor" in partial fulfillment of the requirements for the award of the degree of Master of Technology in "Alternate Hydro Energy Systems" submitted at Alternate Hydro Energy Centre, Indian Institute of Technology, Roorkee is an authentic record of my own work carried out during a period from July 2006 to June 2007 under the supervision of Shri S. N. Singh, Senior Scientific Officer, Alternate Hydro Energy Centre, Indian Institute of Technology, Roorkee.

I have not submitted the matter embodied in this report for the award of any other degree or diploma.

Rindra Rameshwar

(RUDRA RAMESHWAR)

Date: June 27, 2007 Place: Roorkee

This is to certify that the above statement made by the candidate is correct to the best of my knowledge.

(S. N. Singh)

Senior Scientific officer, Alternate Hydro Energy Centre, Indian Institute of Technology, Roorkee-247667 My foremost and profound gratitude goes to my guide Shri S. N. Singh, Senior Scientific Officer, Alternate Hydro Energy Center (A.H.E.C.), Indian Institute of Technology Roorkee, for his proficient and enthusiastic guidance, encouragement and immense help. I have deep sense of admiration for his innate goodness and inexhaustible enthusiasm. The valuable hours of discussions and suggestions that I had with him have undoubtedly helped in supplementing my thoughts in the right direction for attaining the desired objective. Working under his guidance will always remain a cherished experience in my memory and I will adore it throughout my life.

My heartfelt gratitude and indebtedness goes to the Shri Arun Kumar, Head, Alternate Hydro Energy Center (A.H.E.C.) and the entire staff of AHEC who, with their encouraging and caring words, constructive criticism and suggestions, have contributed directly or indirectly in a significant way towards completion of this dissertation.

I would like to convey my special thanks to all of my class fellows who helped me directly or indirectly during my dissertation work and staff members for providing me the necessary equipments, etc.

Finally, I can't forget to recall with my heartiest regards, the never-ending stream of carrying and blessing of my parents who gave me courage and confidence to materialize their dream.

Rudue Rai

(RUDRA RAMESHWAR)

Date: June 27, 2007

In this study, non-sinusoidal quantities and voltage stability, both known as power quality criteria, are examined together in detail. The widespread use of power electronics elements causes the existence of significant non-sinusoidal quantities in the system. These non-sinusoidal quantities can create serious harmonic distortions in transmission and distribution systems. In this dissertation, harmonic generation of a static VAR compensator with Thyristor-Controlled Reactor and effects of the harmonics on steady-state voltage stability are examined for various operational conditions.

# **KEYWORDS**

Harmonics, Stability, Thyristor-Controlled Reactor (TCR), etc.

| CON | <b>FENTS</b> |

|-----|--------------|

|-----|--------------|

| Chapt | ter Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page No.                                                             |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

|       | CANDIDATE'S DECLARATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | i                                                                    |

|       | ACKNOWLEDGEMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ii                                                                   |

|       | ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | iii                                                                  |

|       | CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | iv                                                                   |

|       | LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ix                                                                   |

| 1     | INTRODUCTION AND LITERATURE REVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1.                                                                   |

| 2     | <ul> <li>Introduction of FACTS <ol> <li>Electrical Transmission Systems <ol> <li>Transmission Line Loading Capability</li> </ol> </li> <li>Power Flow in AC Transmission System <ol> <li>The Concept of AC Transmission System Compensation</li> <li>The Concept of AC Transmission Line Power Flow</li> </ol> </li> <li>Flexible AC Transmission Systems (FACTS) <ol> <li>Conventional Thyristor – Based FACTS Schemes</li> <li>Switching Converter Type FACTS Schemes</li> </ol> </li> <li>Contributions and Thesis Outline</li> </ol></li></ul>                                                                                                                                    | 1<br>1<br>2<br>2<br>3<br>5<br>6<br>7<br>9<br>10<br>13                |

|       | <ul> <li>2.1 Static Synchronous Compensator (STATCOM) <ul> <li>2.1.1 Voltage- Source Converter Operation</li> <li>2.1.2 Basic Control of the STATCOM</li> <li>2.1.3 Vector Control Analysis</li> <li>2.1.4 Reference Signal and Regulation Slope</li> <li>2.1.5 STATCOM Decoupled Control Strategy</li> </ul> </li> <li>2.2 Static Synchronous Series Compensator (SSSC) <ul> <li>2.2.1 Effect of Capacitive Series Compensation on the Power Flow</li> <li>2.2.2 Voltage-Source Converter- Based SSSC</li> <li>2.3 Basic Control Scheme of the SSSC</li> </ul> </li> <li>2.3 Design and Simulation of a 24-Pulse Converter</li> <li>2.3.1 Modeling and Digital Simulation</li> </ul> | 13<br>15<br>16<br>18<br>19<br>21<br>22<br>24<br>25<br>26<br>27<br>32 |

| <ul> <li>3.1 Power System Description</li> <li>3.2 Control System Description</li> <li>3.2.1 Phase-Locked Loop</li> <li>3.2.2 Regulation Slope</li> </ul> | 35 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 Control System Description<br>3.2.1 Phase-Locked Loop                                                                                                 |    |

| 3.2.1 Phase-Locked Loop                                                                                                                                   | 37 |

|                                                                                                                                                           | 37 |

|                                                                                                                                                           | 38 |

| 3.3 Digital Simulation                                                                                                                                    | 39 |

| 3.3.1 Simulation Result                                                                                                                                   | 39 |

| 3. A STATCOM STABILITY ENHANCEMENT                                                                                                                        | 47 |

| 3. A.1 Dynamic Performance of the STATCOM                                                                                                                 | 47 |

| 3. A.2 Effect of the Power System Strength                                                                                                                | 49 |

| 3. A.2.1 Digital Simulation                                                                                                                               | 50 |

| 3. A.3 Effect of the Phase-Locked Loop                                                                                                                    | 51 |

| 3. A.4 Automatic Gain Controller                                                                                                                          | 55 |

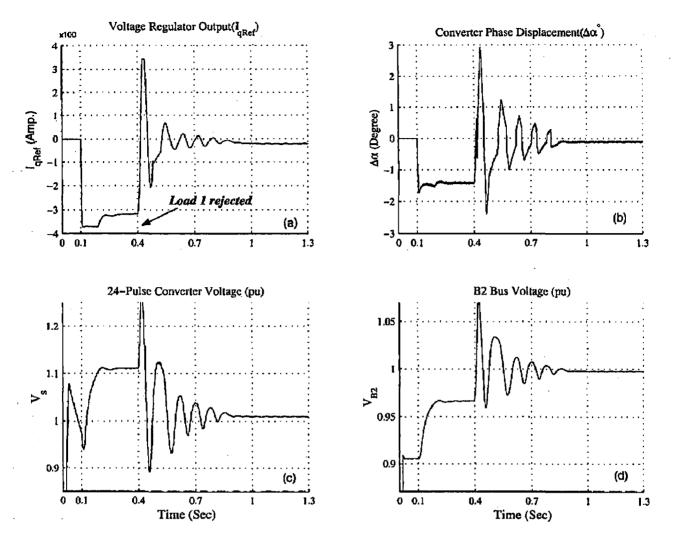

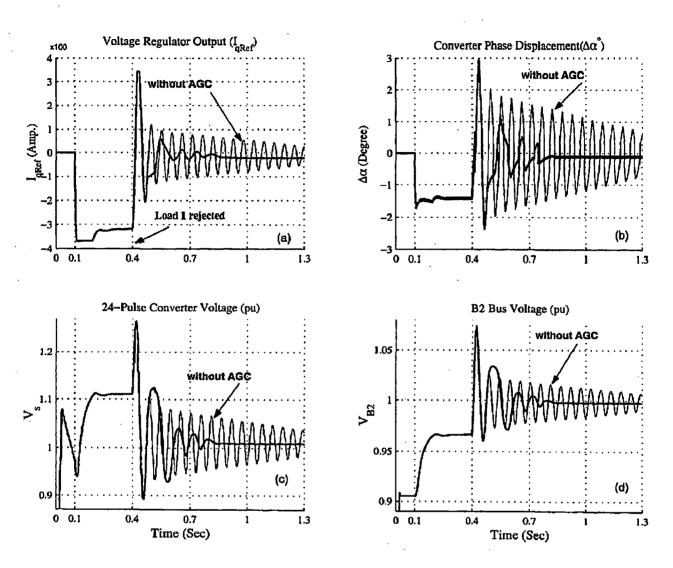

| 3. A.4.1 Digital Simulation of the AGC                                                                                                                    | 57 |

| 3. A.5 Conclusion                                                                                                                                         | 60 |

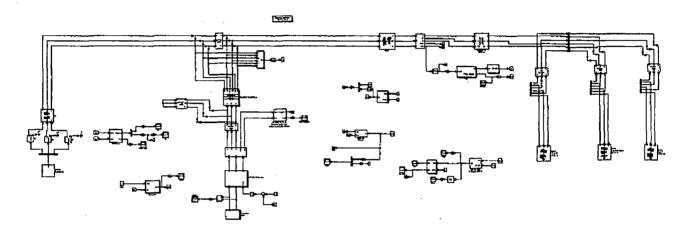

| <b>SSSC: A COMPLETE DIGITAL SIMULATION STUDY</b>                                                                                                          | 61 |

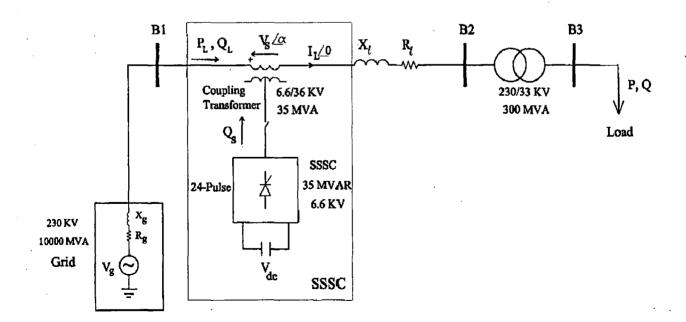

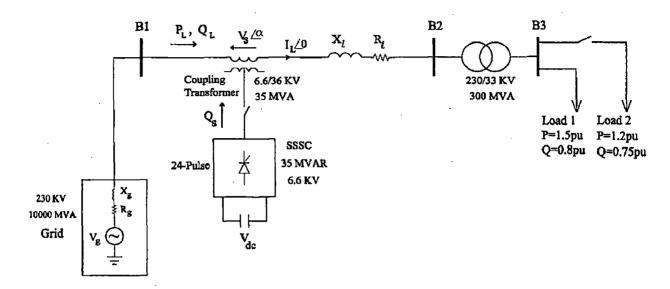

| 4.1 System Description                                                                                                                                    | 61 |

| 4.1.1 Power System                                                                                                                                        | 61 |

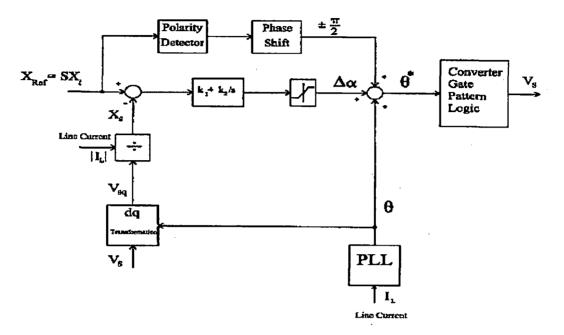

| 4.1.2 Control System                                                                                                                                      | 63 |

| 4.2 Digital Simulation                                                                                                                                    | 63 |

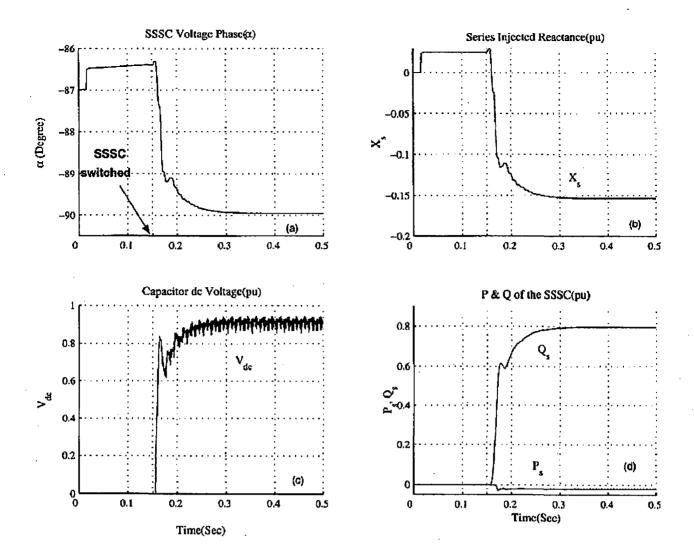

| 4.2.1 Capacitive Operation                                                                                                                                | 63 |

| 4.2.2 Inductive Operation                                                                                                                                 | 66 |

| 4. B DYNAMIC PERFORMANCE OF THE SSSC                                                                                                                      | 69 |

| 4. B.1 Dynamic Operation of the SSSC                                                                                                                      | 69 |

| 4. B.1.1 Digital Simulation                                                                                                                               | 69 |

| 4. B.2. Auxiliary Control Design                                                                                                                          | 73 |

| 4. B.2.1 Digital Simulation                                                                                                                               | 75 |

| 4. B.3 Conclusion                                                                                                                                         | 76 |

|                                                                                                                                                           |    |

| 4. C PSB/SIMULINK MODELS                                                                                                                                  | 80 |

| 4. C.1 24- Pulse Converter                                                                                                                                | 80 |

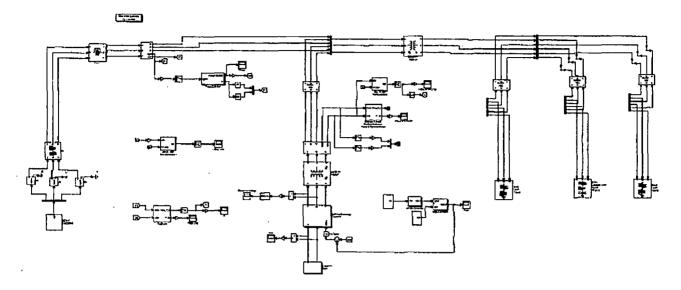

| 4. C.2 STATCOM                                                                                                                                            | 83 |

| 4. C.3 SSSC                                                                                                                                               | 84 |

| 4. C.4. Automatic Gain Controller (AGC)                                                                                                                   | 84 |

| 4. C.5 Auxiliary Regulator                                                                                                                                | 85 |

| 5 THYRISTOR CONTROLLED REACTOR STUDY                                                                                                                      | 86 |

| 5.1 Thyristor- Controlled Reactor as Harmonic Source                                                                                                      | 87 |

| 5.2 Stability and Harmonics                                                                                                                               | 89 |

| 5.2.1 Harmonic Power Flow Algorithm                                                                                                                       | 89 |

| 5.3 TCR Analysis Method                                                                                                                                   | 91 |

| 5.4 Numerical Application                                                                                                                                 | 94 |

| V                                                                                                                                                         | 27 |

|                                                                                                                                                           |    |

#### 6 RESULTS, CONCLUSION AND FUTURE WORK

#### **BIBLIOGRAPHY**

# PUBLICATIONS

- 1. Abstract is Selected and Full Paper is submitted on "Harmonics and Voltage Stability Analysis in Power Systems Using FACTS by Thyristor Controlled Reactor" in International Conference in Energy Research, Organised by Indian Institute of Technology, Bombay, Dec. 12-14, 2007.

- 2. Paper Accepted on "FACTS, HVDC Controls and Their Applications" in the All India Conference conducted by Institution of Engineers India, Guwahati Centre, Dec. 14-16, 2006.

98

# LIST OF FIGURES

| Figur      | re No. Title                                                                                      | Page No. |

|------------|---------------------------------------------------------------------------------------------------|----------|

| 1 1        |                                                                                                   |          |

| 1.1<br>1.2 | A Two-Bus Power Transmission System                                                               | 2        |

| 1.2        | Phasor Diagram of the Two-Bus Transmission System<br>Effect of $ E_1 $ on the Transmission System | 3        |

| 1.5        | Effect of $X_1$ on Power-Angle Curves                                                             | 4        |

| 1.4        | Effect of Series Capacitor on the Total Line Reactance                                            | 4<br>5   |

| 1.5.       | Fixed Capacitor, Thyristor-Controlled Reactor (FC-TCR)                                            | 8        |

| 1.7        | Thyristor-Controlled Series Capacitor (TCSC)                                                      | o<br>8   |

| 1.8        | General Diagram of the Static Synchronous Compensator (STATCOM)                                   | o<br>9   |

| 1.9        | General Diagram of the Static Synchronous Series Compensator (SSSC)                               | 13       |

| 1.9        | Scherar Diagram of the State Synchronous Series Compensator (355C)                                | 15       |

| 2.1        | Static Synchronous Compensator                                                                    | 14       |

| 2.2        | Real Power Exchange of the STATCOM                                                                | 17       |

| 2.3        | Direct and Quadrature Components of Current Vector                                                | 18       |

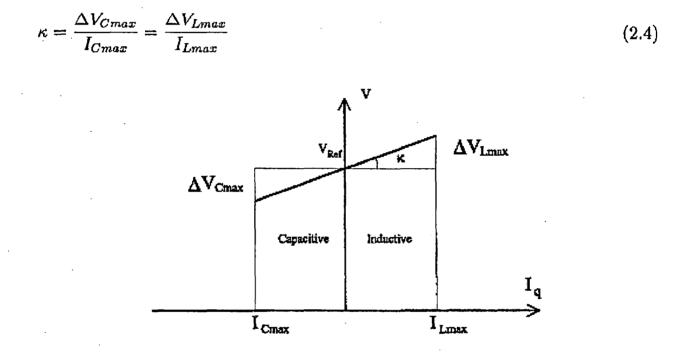

| • 2.4      | Voltage Regulation and Regulation Slope                                                           | 20       |

| 2.5        | Decoupled Control Structure of the STATCOM with Regulation Slope                                  | 21       |

| 2.6        | Capacitive Series Compensation                                                                    | 23       |

| 2.7        | Synchronous Series Compensation                                                                   | 23 -     |

| 2.8        | Phasor Diagram of Capacitive Synchronous Series Compensation                                      | 24       |

| 2.9        | Static Synchronous Series Compensator                                                             | 25       |

|            | Control Structure of the SSSC                                                                     | 27       |

|            | Three Phase, 6-Pulse, Voltage-Source GTO Converter                                                | 28       |

|            | Gating Pulses of the 6-Pulse Converter                                                            | 28       |

|            | Phase-Neutral and Phase-Phase Voltages of the 6-Pulse Converter                                   | 29       |

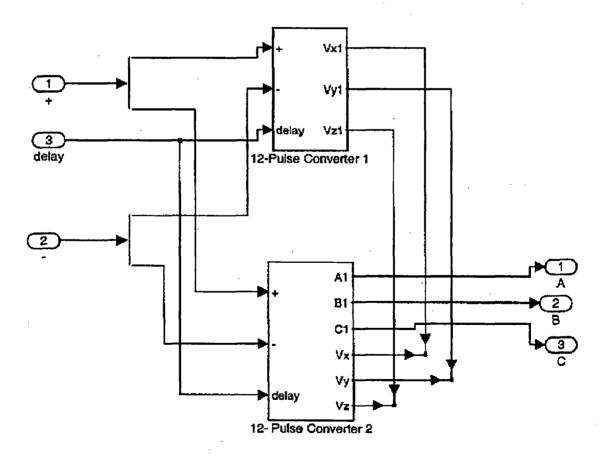

|            | Configuration of a 12-Pulse Converter                                                             | 31       |

|            | Configuration of a 24-Pulse Converter                                                             | 31       |

|            | PSB Simulation of a 12-Pulse Converter                                                            | 32       |

|            | PSB Simulation of a 24-Pulse Converter                                                            | 33       |

| 2.18       | THD of the 24-Pulse Voltage                                                                       | 34       |

| 3.1        | Single Line Diagram of the Power Transmission System with the STATCO                              | M 35     |

| 3.2        | STATCOM Decoupled Control Structure                                                               | 37       |

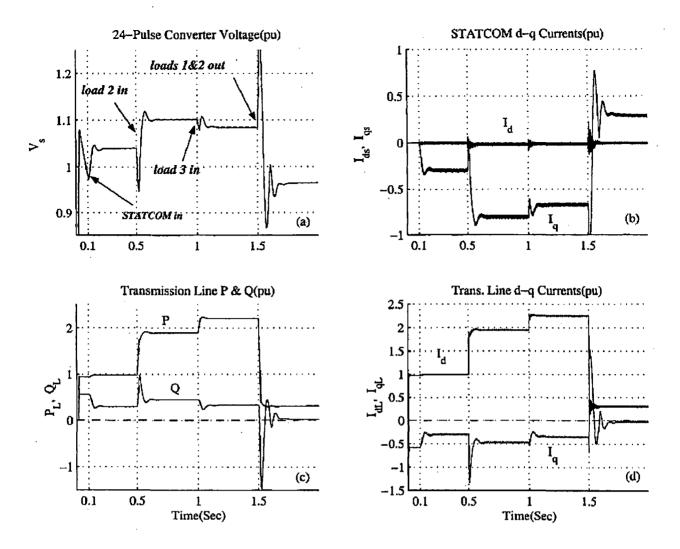

| 3.3        | STATCOM Simulation Results (1)                                                                    | 42       |

| 3.4        | STATCOM Simulation Results (2)                                                                    | 43       |

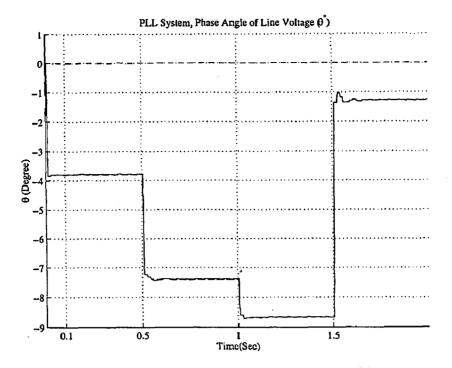

| 3.5        | Synchronizing Signal, $\theta$ , Generated by PLL                                                 | 45       |

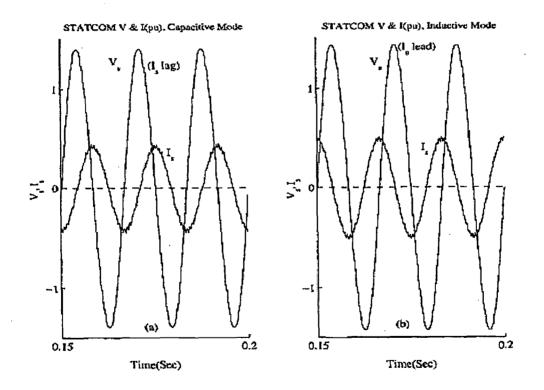

| 3.6        | STATCOM Voltage and Current                                                                       | 45       |

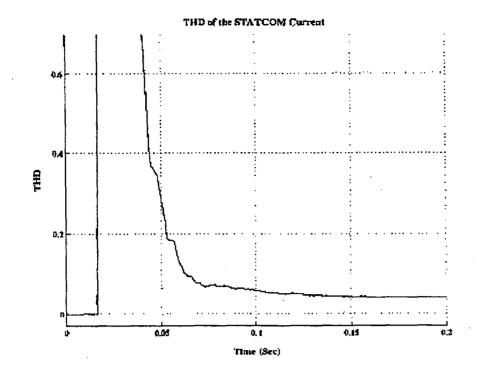

| 3.7        | THD of the STATCOM Current (THD: 0.041)                                                           | 46       |

| A.1        | Power System Representation with STATCOM                                                          | 47       |

| A.2        | Basic Block Diagram Representation of the STATCOM                                                 | 48       |

| A.3        | Single Line Diagram of Power Transmission System with the STATCOM                                 | 48<br>50 |

| A.4        | Demonstration of the STATCOM Response for a Weak Power System                                     | 51       |

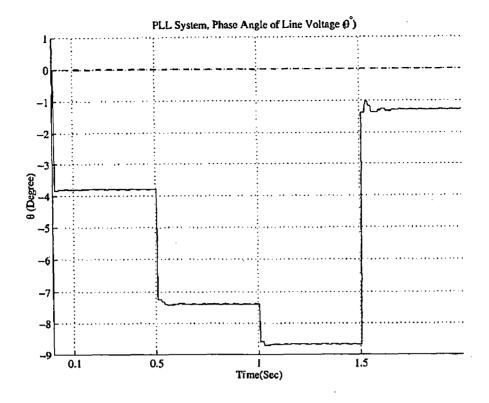

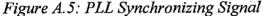

|            | PLL Synchronizing Signal                                                                          | 53       |

|            | Demonstration of the Effect of PPL Delay on the STATCOM Response                                  | 54       |

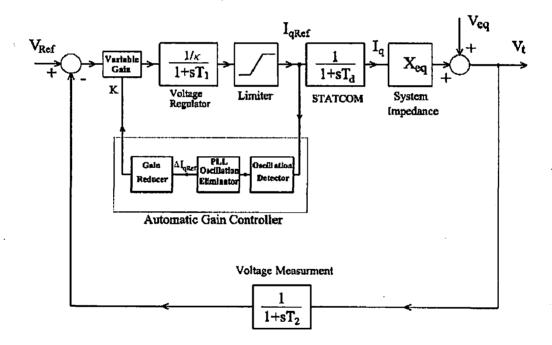

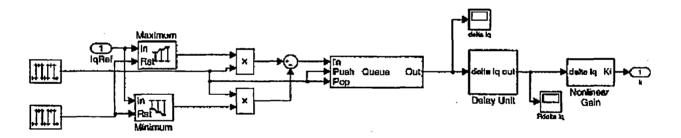

| A.7        | Block diagram of the STATCOM with the AGC                                                         | 56       |

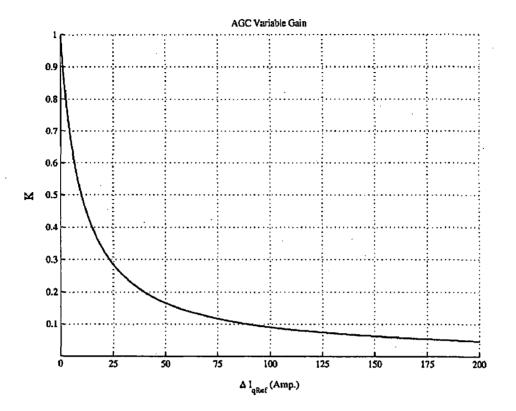

| A.8  | Variable Gain of the AGC Versus $\Delta Iq_{Ref}$                               | 57 |

|------|---------------------------------------------------------------------------------|----|

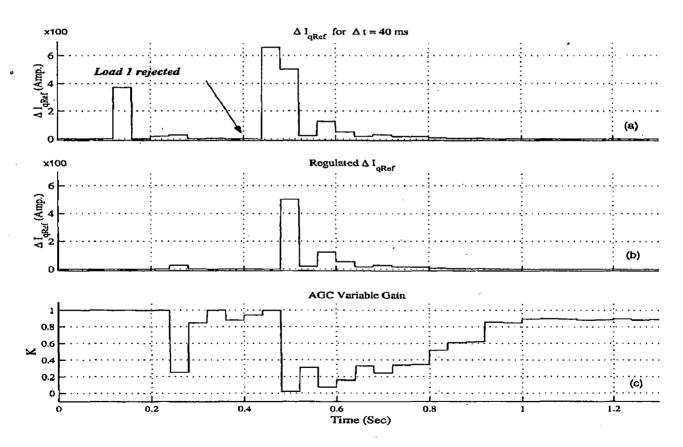

|      | Digital Simulation of the Effect of the AGC on STATCOM Stabilization            | 58 |

|      | Demonstration of the STATCOM Response with and without the AGC                  | 59 |

|      | AGC Simulation Results                                                          | 60 |

|      |                                                                                 |    |

| 4.1  | Single Line Diagram of the Power Transmission System with the SSSC              | 61 |

| 4.2  | Basic Control Structure of the SSSC                                             | 63 |

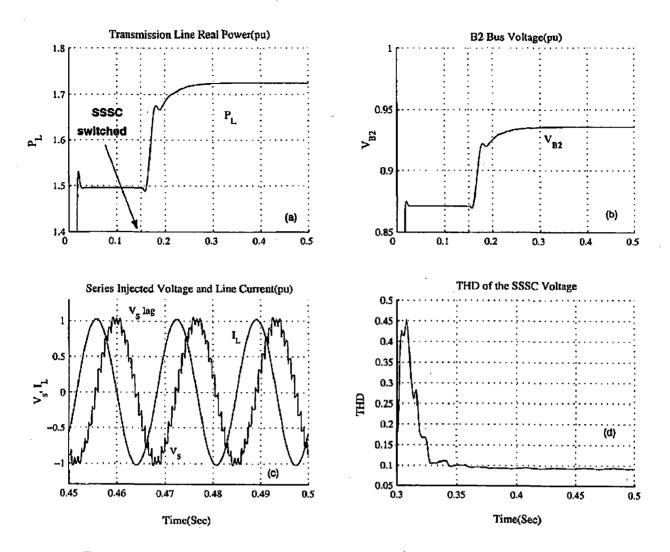

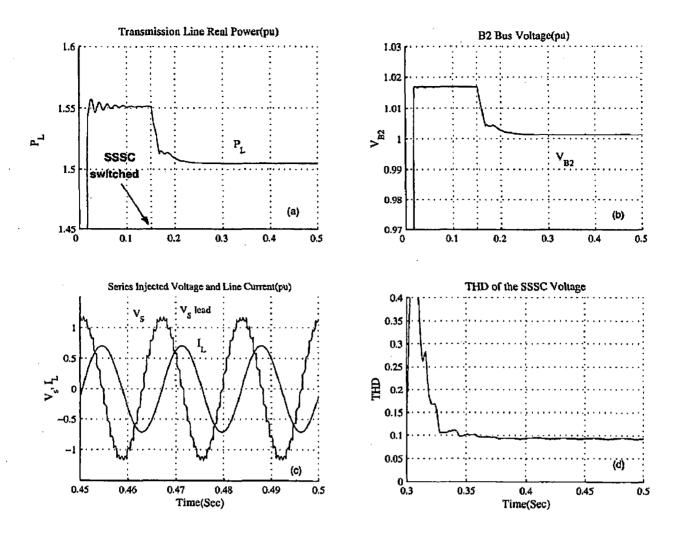

| 4.3  | Digital Simulation Results of the SSSC in Capacitive Mode (1)                   | 65 |

| 4.4  | Digital Simulation Results of the SSSC in Capacitive Mode (2)                   | 66 |

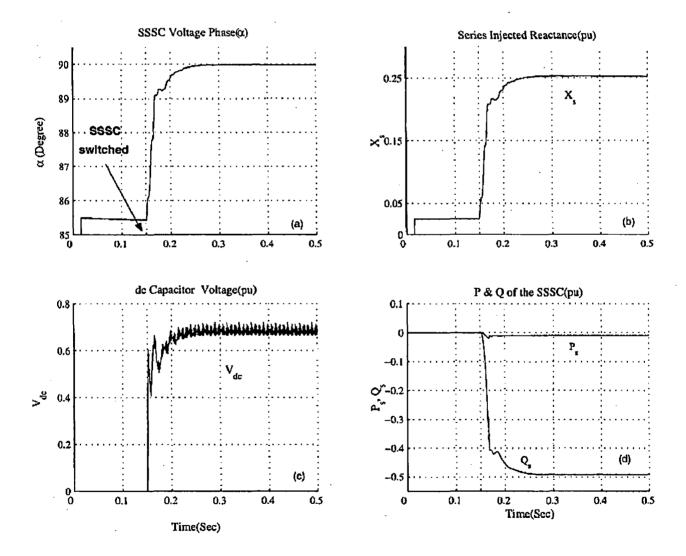

| 4.5  | Digital Simulation Results of the SSSC in Inductive Mode (1)                    | 67 |

| 4.6  | Digital Simulation Results of the SSSC in Inductive Mode (2)                    | 68 |

| B.1  | Single Line Diagram of the Power Transmission System with the SSSC              | 70 |

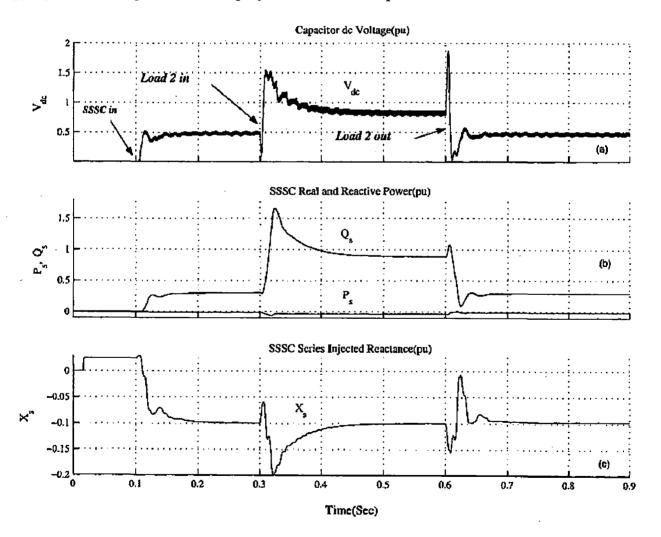

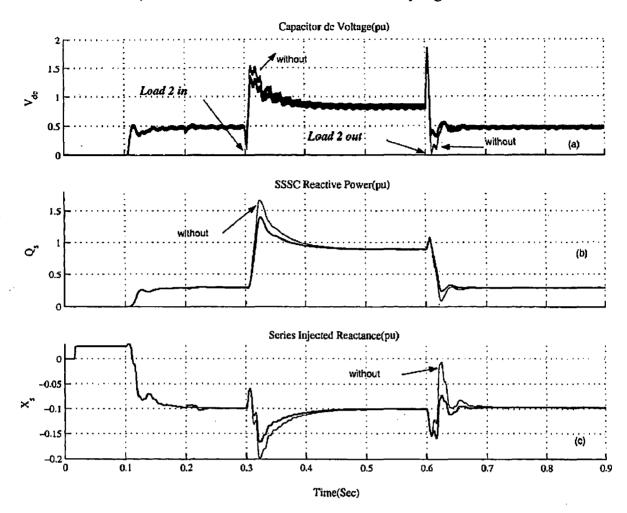

| B.2  | Simulation Results of the SSSC Response to Load Switchings                      | 71 |

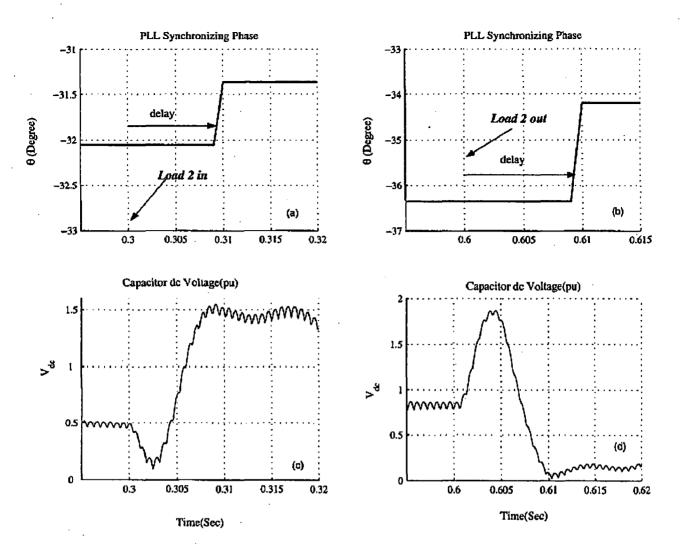

| B.3  | PLL Phase Angle and dc Capacitor Voltage, Load Switching                        | 72 |

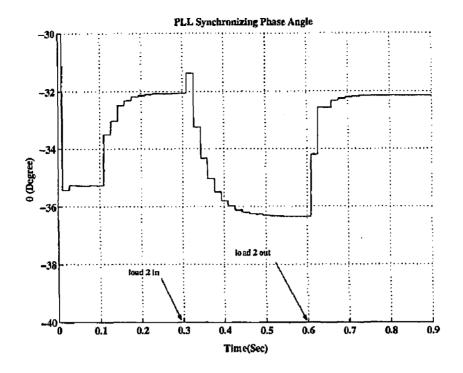

| B.4  | PLL Synchronizing Phase Angle of the SSSC                                       | 73 |

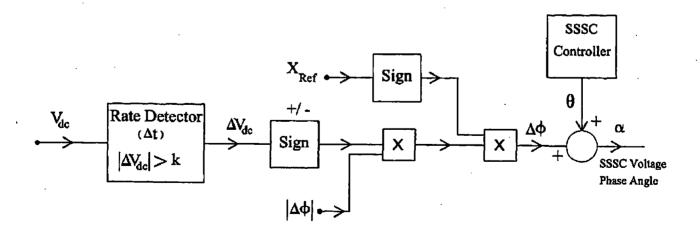

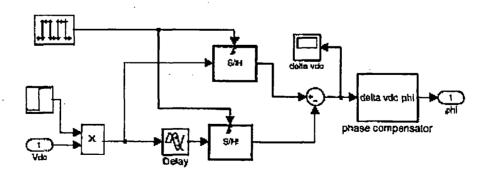

| B.5  | Block Diagram of the Auxiliary Regulator for the SSSC                           | 74 |

| B.6  | Simulation of the SSSC with or without the Auxiliary Regulator                  | 76 |

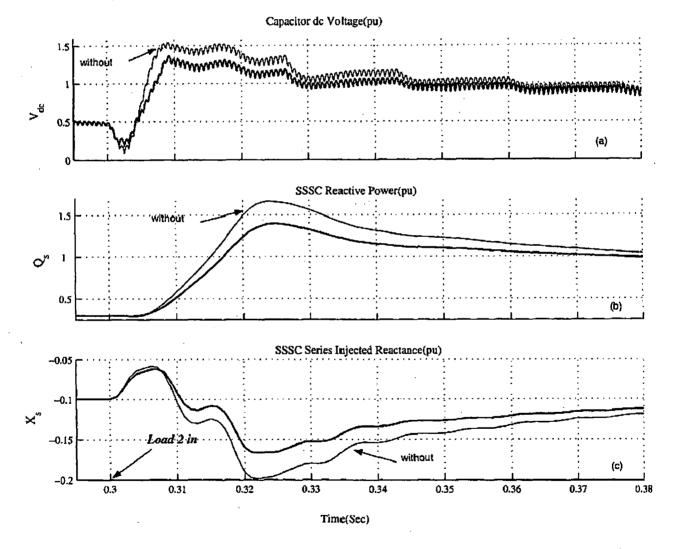

| B.7  | SSSC Performance with and without the Auxiliary Regulator (Load Switched in )   | 77 |

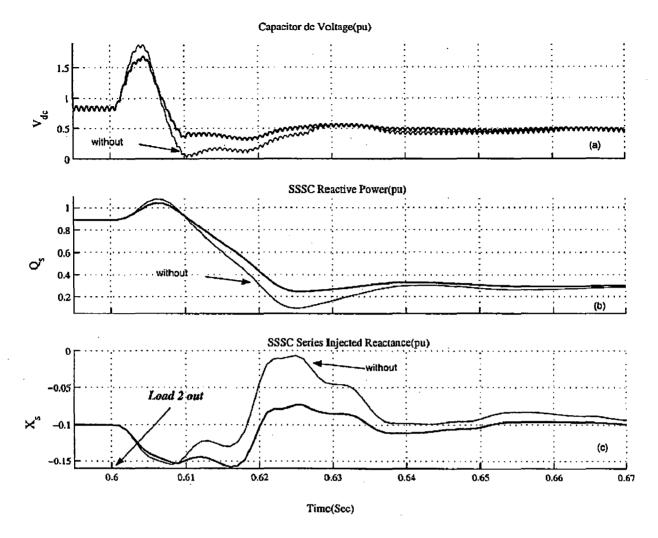

| B.8  | SSSC Performance with and without the Auxiliary Regulator (Load Switched out)   | 78 |

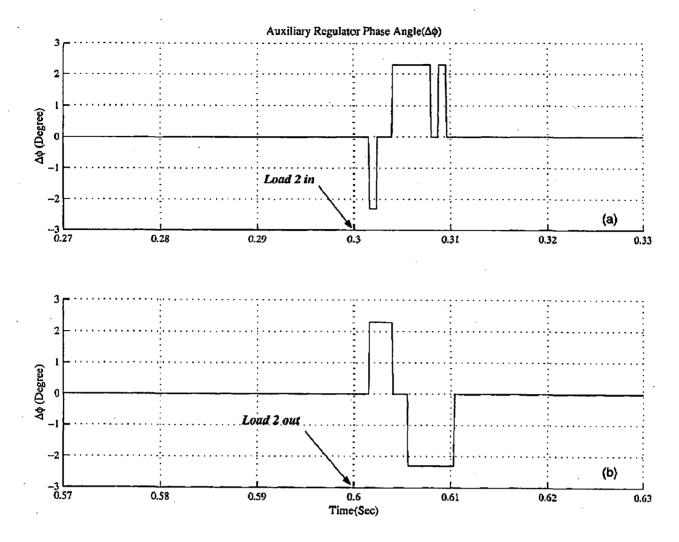

| B.9  | Auxiliary Regulator Phase Angle, $\Delta \Phi$ , at Switching Instants          | 79 |

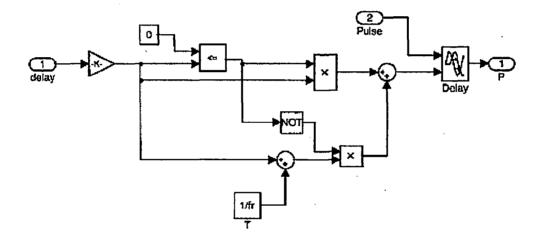

| C.1  | Basic Phase Angle Delay Unit for the GTO Gate Pulses                            | 80 |

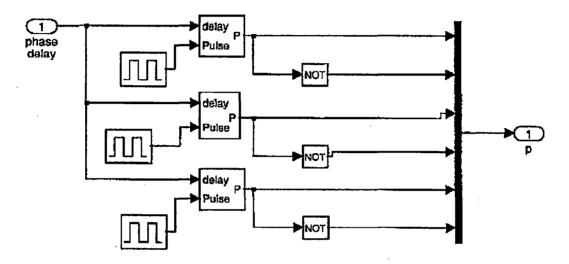

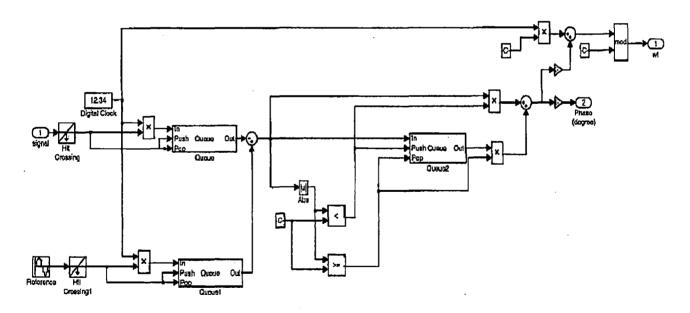

| C.2  | Gate Pulse Generator of a 6-Pulse Converter with the Variable Phase Angle Delay | 81 |

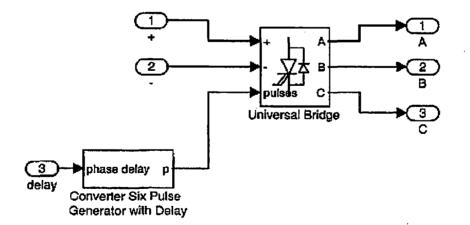

|      | Six-Pulse GTO Converter with Variable phase Angle Delay                         | 81 |

| C.4  | PSB Model of the 12-Pulse Converter                                             | 82 |

| C.5  | PSB Model of the 24-Pulse Converter                                             | 82 |

| C.6  | Phase-Locked Loop Model                                                         | 83 |

| C.7  | STATCOM Model within a Power Transmission System                                | 84 |

| C.8  | SSSC Model within a Power Transmission System                                   | 85 |

| C.9  | Automatic Gain Controller Model                                                 | 85 |

| Ċ.10 | Auxiliary Regulator Model                                                       | 85 |

|      |                                                                                 |    |

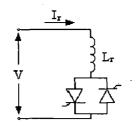

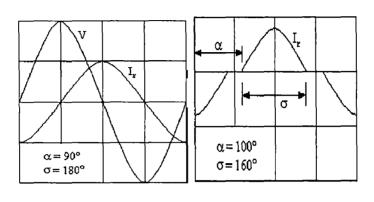

| 5.1  | (a) Main Elements of a TCR (b) Voltage and Current Waveforms in a TCR           | 88 |

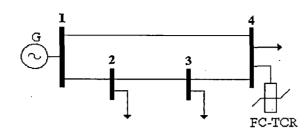

| 5.2  | Single Line Diagram of Example System Including FC-TCR                          | 94 |

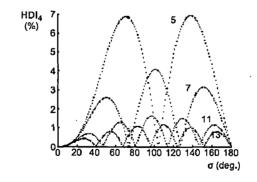

| 5.3  | Variations of Individual Harmonic Distortion as a Function of Conduction Angle  | 95 |

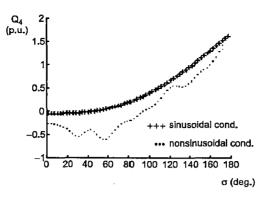

|      | Variations of Reactive Power at bus-4 for all Conduction Angles                 | 96 |

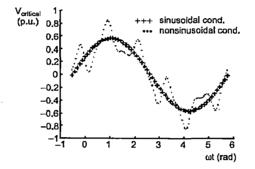

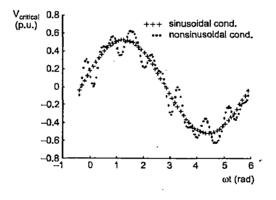

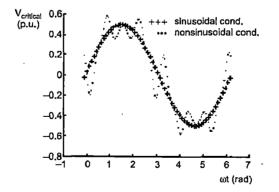

| 5.5  | Variations of Critical Voltage at bus-4 for $\sigma = 70^{\circ}$               | 96 |

| 5.6  | Variation of Critical Voltage at bus-4 for $\sigma = 105^{\circ}$               | 96 |

| 5.7  | Variations of Critical Voltage at bus-4 for $\sigma = 160^{\circ}$              | 96 |

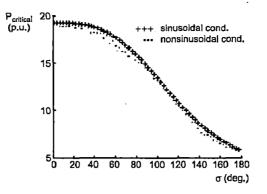

| 5.8  | Critical Power Values Versus Conduction Angle at bus-4                          | 97 |

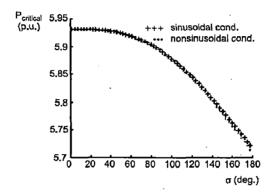

| 5.9  | Critical Power Values Versus Conduction Angle at bus-3                          | 97 |

viii

#### **INTRODUCTION AND LITERATURE REVIEW**

#### **1.0 INTRODUCTION TO FACTS**

The main objective of any AC transmission or distribution line compensation is to increase the steady state and short term power transfer capability of the existing transmission systems. This chapter describes the general concept of AC transmission system compensation using tools such as shunt and series capacitive or reactive compensation and then the new concept of solid-state, converter-based Flexible AC Transmission Systems (FACTS) is introduced. The chapter reviews the previous works on FACTS schemes and presents the full thesis outline and structure also incorporated in Literature Review.

## 1.1 ELECTRICAL TRANSMISSION SYSTEMS

Almost all electrical energy in the world is generated in the form of three phase AC power and transmitted via high voltage AC transmission systems. Rapid growth in electrical energy utilization, combined with the increased demand for efficient low cost electrical energy has gradually led to the development of generation sites remotely located from the major load centers. To enhance the AC system stability, security and reliability multiple AC transmission grids, connecting load centers to remote generation and neighboring utilities, are constructed. These interconnections have led to the evolution of complex transmission grids that pool power plants and load centers all for the sole purpose of minimizing the total power generation capacity and cost, while ensuring supply reliability and security. They enable taking advantage of time diversity of electric loads, availability of other local generation resources and fuel price to supply the power to the loads at minimum cost with specified reliability index. On the other hand, the increased demand on the transmission grid, absence of long term planning and deregulated open market with multiple companies and large customer pools have created new system security and reliability problems [1],[2].

### 1.1.1 Transmission Line Loading Capability

Basically, there are three factors that limit the lading capability of a transmission line [1],[3]. These factors can be classified to thermal, dielectric and stability limits. Thermal capability of an overhead line is a function of the ambient temperature, wind conditions, and conductor-to-ground clearance. The nominal thermal rating of a transmission line is generally determined on a conservative basis [3].

The dielectric limit is determined by voltage limit of insulators. Since insulators are usually designed very conservatively (2.5-3pu), for a given nominal voltage it is often possible to increase the line voltage by 10% without exceeding the specified Basic Insulation Level [4]. From the stability viewpoint, there are several issues that limit the transmission capability. They are Transient Stability, Dynamic Stability, Steady-State Stability, Voltage Stability and Harmonic Stability [5], [6], [7].

#### 1.2 POWER FLOW IN AN AC TRANSMISSION SYSTEM

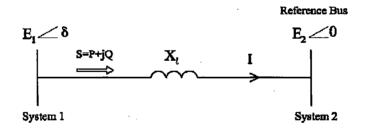

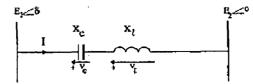

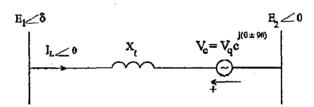

Figure 1.1 shows a two-bus interconnected power transmission system.

Figure 1.1: A Two-Bus Power Transmission System

Assuming  $E_1$  and  $E_2$  are the magnitudes of the internal voltages of the two equivalent machines representing buses 1 and 2, the real and reactive power at bus 2 can be obtained as:

$$I = \frac{E_1 \angle \delta - E_2}{jX_l} = \frac{E_1 \sin \delta}{X_l} + j \left(\frac{E_2 - E_1 \cos \delta}{X_l}\right)$$

(1.1)

$$S = E_2 I^* = \frac{E_1 E_2 \sin \delta}{X_l} + j \left( \frac{E_1 E_2 \cos \delta - E_2^2}{X_l} \right) = P + jQ$$

(1.2)

$$P = \frac{E_1 E_2}{X_l} \sin \delta \tag{1.3}$$

$$Q = \frac{E_1 E_2 \cos \delta - E_2^2}{X_l}$$

(1.4)

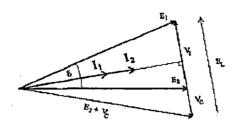

Figure 1.2 shows the phasor diagram of this transmission system where  $(E_L = E_1 - E_2)$  is the voltage drop across the transmission line. Since  $I = E_L/jX_1$ , line current is perpendicular to  $E_L$ .

Figure 1.2: Phasor Diagram of the Two-Bus Transmission System

#### **1.2.1** The Concept of AC Transmission System Compensation

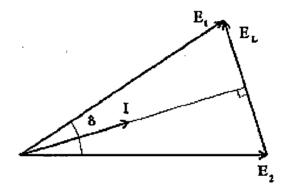

The effects of changing the magnitudes of sending bus voltage,  $E_1$ , and system reactance,  $X_1$ , on the power flow as well as transient and steady state stability are presented in this section. Figure 1.3 shows the effect of changing  $|E_1|$  by a small value. Changing  $|E_1|$  by the small value,  $\Delta E_1$ , does not change the magnitude of the transmission system voltage drop,  $E_L$ , by an appreciable value, however it does change its phase angle by much and also the phase angle of line current,  $\Phi$ . Therefore regulating the magnitude of  $E_1$  has profound influence on reactive power flow but not real power.

Figure 1.3: Effect of  $|E_I|$  on the Transmission System

As equations (1.3) and (1.4) indicate, when the real power demand of the line increases, the reactive power demand is also increased. In other words, to provide and increase in real power demand, reactive power has to be increased [3],[6]. Hence shunt capacitive compensation, may be required to maintain the system bus voltage  $E_1$  within specified limits and provide the required reactive power.

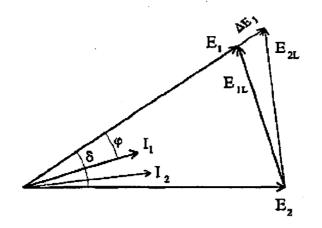

Controlling the magnitude of transmission line reactance,  $X_1$ , can control the real power flow within the specified maximum line capacity [3],[8]. Figure 1.4 shows the power angle curves for variations in system equivalent reactance,  $X_1$ , as described by equation (1.3). For a given power angle,  $\delta$ , and bus voltage magnitude, reducing  $X_1$  will increase the real power flow by increasing the steady state stability or maximum power.

Figure 1.4: Effect of X<sub>l</sub> on Power-Angle Curves

4

This can be easily achieved by capacitive series compensation that cancels as portion of line reactance as shown in Figure 1.5. Therefore series compensation is a powerful approach to increase the transmission line capability or power capacity [3],[5].

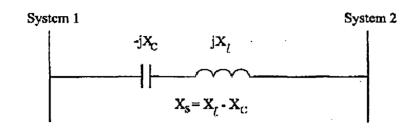

Figure 1.5: Effect of Series Capacitor on the Total Line Reactance

Besides, for a given real power, P, reducing  $X_1$ , corresponds to a reduction in operating power angle,  $\delta$ . Therefore series capacitive compensation improves both transient and steady-state stability limits of the transmission system [5],[6]. This is an important aspect of a power system and power flow. Series capacitive sizing and location as well as control strategies depend on system topology and operating conditions [9].

### 1.2.2 Conventional Control of Transmission Line Power Flow

The conventional techniques to control the power flow over HV transmission lines are generally implemented in the generating stations to provide the power requirements of the load [2]. They include speed-governors, excitation systems, tap-changing transformers and phaseshifting transformers.

The speed-governors system provides full control of synchronous generator output power by regulating the input power or prime mover torque while the excitation system of synchronous generator provides as fast-regulating field current control, hence controlling the generated voltage. However, when the synchronous generator is connected to very large power system, voltage is almost stabilized and the excitation control can result in changing the reactive power [10],[11]. Tap-changing transformers provide a limited range of voltage control and therefore can be used to slowly control the reactive power flow within limits ( $\pm 10\% - \pm 15\%$ ). Finally, phaseshifting transformers are special series-connected transformers that introduced phase shift in the transmission system voltages and hence control the power flow [1],[2].

#### **1.3 FLEXIBLE AC TRANSMISSION SYSTEMS (FACTS)**

Flexible AC Transmission Systems (FACTS) is a new concept based on power electronic switching devices and controllers to enhance the transmission grid utilization and power capacity as well as stability, security, reliability, power quality and efficient interconnections. This concept can be more clarified by the IEEE definitions of *Flexibility*; FACTS and FACTS Controllers [1].

Flexibility of Electric Power Transission: The ability to accommodate changes ion the electric transmission or operating conditions while maintaining sufficient steady-state and transient margins.

Flexible AC Transmission Systems: Alternating current transmission systems incorporated power electronic-based and other static controllers to enhance controllability and increase power transfer capability.

FACTS Controllers: Power electronics-based systems and other static equipment that provide control of one or more AC transmission parameters.

The possibility that the current and power of a transmission line can be fully controlled at a reasonable cost enables a large potential of increasing the capacity of the existing transmission systems. These new opportunities are provided through the ability of FACTS controllers to control the interrelated parameters that govern the operation of a transmission system.

FACTS technology is based on high power line or self-commutated solid-state devices such as thyristors and Gate Turn-off thyristors (GTO) that provide the ability to continuously control the transmission system in order to meet the power flow requirements. Recent advances in solid-state technology have introduced thyristors and GTOs in higher voltage and current ratings such as (5.5 KV, 4KA) for thyristors and (4.5 KV, 4KA) for GTOs [1]. Therefore FACTS controllers with a reasonable capacity of a few hundred of Megawatts can be realized in large interconnected power pools.

#### 1.3.1 Conventional Thyristor-Based FACTS Schemes

By definition, capacitors generate and reactors absorb reactive power in AC systems. They have been used with mechanical switches for shunt and series compensation since the early days of AC power transmission [3],[5].

Since the early 1970s line commutated thyristors in conjunction with capacitors and reactors have been employed in various circuit configurations for variable shunt and series compensation. The shunt compensation device is called Static Var Compensator (SVC) and is defined as [1]:

Static Var Compensator: A shunt-connected static Var generator or absorber whose output is adjusted to exchange capacitive or inductive current so as to maintain or control specific parameters of the electrical power system. (typically bus voltage)

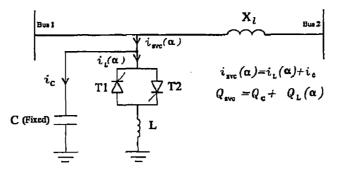

SVC is based online-commutated thyristor-switched capacitors and modulated reactors. Fixed Capacitor, Thyristor-Controlled Reactor(FC-TCR) is an example of SVC scheme as shown in Figure 1.6. By controlling the firing angles of T1 and T2 reactive power compensation can be adjusted to the desired value. At the maximum capacitive Var output, the thyristor- controlled reactor is off ( $\alpha = 90^{\circ}$ ). By decreasing the delay angle,  $\alpha$ , the inductive current increases and therefore the net capacitive Var output decreases. At zero delay angle maximum inductive Var output is obtained and the total SVC Var output is the difference between the capacitor and thyristor-controlled reactor Vars [12].

7

Figure 1.6: Fixed Capacitor, Thyristor-Controlled Reactor (FC-TCR)

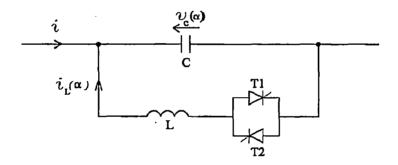

Thyristor-Controlled Series Capacitor (TCSC) is another example of thyristor-controlled series compensation. Figure 1.7 shows the basic configuration of TCSC. It was proposed in 1986 by Vithayathil with others [1] as a method of rapid adjustment of equivalent system reactance,  $X_1$ . The TCSC presents a smoothly variable parallel LC series blocking circuit. The total series reactance of TCSC is function of the delay angle of thyristors,  $\alpha$ .

Figure 1.7: Thyristor-Controlled Series Capacitor (TCSC)

The total TCSC reactance is:

$$X_{TCSC}(\alpha) = \frac{X_C X_L(\alpha)}{X_L(\alpha) - X_C}$$

(1.5)

At  $\alpha = 90^{\circ}$ , the inductor is off  $(X_L = \infty)$  and the maximum capacitive series reactance is obtained. By reducing  $\alpha$ , the capacitive reactance of TCSC decreases until parallel resonance at  $X_C = X_L (\alpha)$  is established and the total reactance is theoretically infinite. Therefore the operation of TCSC should be avoided in this region. Further reducing of  $\alpha$  creates an inductive series reactance and the maximum inductive reactance is obtained at  $\alpha = 0$  [1].

#### 1.3.2 Switching Converter Type FACTS Schemes

The most significant difference between the new approach of FACTS implementation and the conventional one is that it does not employ discrete capacitor or reactor banks for shunt or series compensation, but rather it employs dc-ac link converters to exchange shunt or series reactive power with the transmission system. It should be noted that "*converter*" is used as general description of any solid-state device (converter or inverter) that converts either AC or DC voltage to the other form. Since in FACTS applications the flow of real power can be from either DC or AC side to the other side, "*converter*" is used as a general term. For reasons of economics and design simplicity, voltage-source converters are often preferred over currentsource converters for FACTS applications [1].

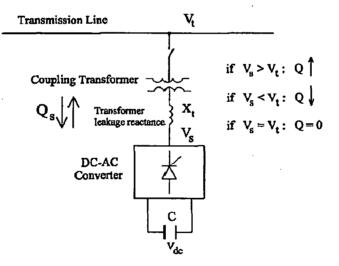

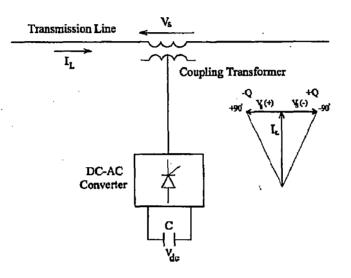

The FACTS shunt compensation scheme is called *Static Synchronous Compensator* (STATCOM) as shown in Figure 1.8.

Figure 1.8: General Diagram of the Static Synchronous Compensator (STATCOM)

The basic concept of the STATCOM is that a set of three phase voltage in phase with line voltage can transfer reactive power between the power system and STATCOM. The direction of reactive power flow,  $Q_s$ , depends on the relative magnitudes of line and STATCOM voltages,  $V_t$  and  $V_s$ , respectively. Since  $V_t$  and  $V_s$  are in phase there is no real power exchange between the STATCOM and the transmission system. In Figure 1.8 the direction of reactive

power flow is from the STATCOM to the transmission system if  $(V_s > V_t)$  and vice versa. Therefore by controlling the magnitude of  $V_s$  reactive power exchange can be continuously adjusted to meet any compensation level [13].

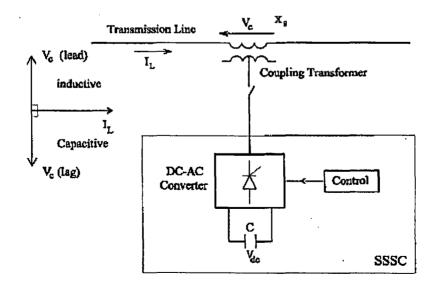

Similarly the series compensation device is called *Static Synchronous Series Compensator* (SSSC) as shown in Figure 1.9. It is well-known that a series capacitor can reduce the equivalent line reactance and hence increase the transmission capability.

Figure 1.9: General Diagram of the Static Synchronous Series Compensator (SSSC)

This can be performed by injecting a series boosting voltage across the line which lags the line current by 90<sup>0</sup>. In Figure 1.9,  $V_s$  is essentially in quadrature with  $I_L$  and by controlling the magnitude of  $V_s$  series line reactance compensation can be adjusted. Since  $V_s$  is in quadrature with  $I_L$  there is no real power exchange between the SSSC and the transmission line. It should be noted that if  $V_s$  leads line current by 90<sup>0</sup>, inductive series compensation will be obtained [14].

#### 1.4 CONTRIBUTIONS AND THESIS OUTLINE

Before presenting the thesis outline an brief literature review of voltage-source converterbased FACTS (VSC-FACTS) is presented. The possibility of generating controllable reactive power without the use of Ac capacitor or reactor banks by various switching power converters was disclosed by Gyugyi in 1979 [15]. Edwards *et al.* reported the operation of a  $\pm$  1 MVA prototype advanced static Var generator (ASVG) in 1988 [16]. They used a 12-pulse converter scheme to test the operation of a STATCOM. The control fundamental of VSC-FACTS was developed by Schauder and Mehta in 1991 [17]. They developed a decoupled control theory of VSC-FACTS by Park transformation which is the basic control approach in switching type FACTS controllers. The concept of solid-state series compensation without using series capacitors or reactors was introduced by Gyugyi in 1989 [13]. The operation of the SSSC was introduced in 1994 [18] and 1996 [14] by Gyugyi, Schauder and K.Sen.

After developing the basic theory, control and operation of the STATCOM and SSSC by FACTS pioneers in late 1980s and mid 1990s, numerous papers have been published for further control development and validation of the STATCOM and SSSC by digital simulation. The previous investigations and simulations have been performed using either mathematical model of the STATCOM and SSSC [17], [19], [20], [21], [22], [23], [24], [25], [26], [27], [28], [29], [30], or a low-pulse converter such as a 6 or 12-pulse converter [31], [32], [33]. The mathematical model, which is usually a simple Laplace domain model, does not represent the exact physical model of the converter and therefore some key aspects of the practical operation such as transient operation, harmonic contents and inherent delays can not be considered which are important in practical applications. The low-pulse converters have the problems of high harmonics contents and are never used in practical FACTS applications and therefore can not be used for in-depth and accurate investigations and simulation of the interconnected power system and FACTS.

The thesis investigated the theory, control, complete digital simulation and design of two novel controllers for the STATCOM and SSSC. The basic theory and control of the STATCOM and SSSC will be presented in Chapter 2. For full validation and digital simulation purposes a 24-pulse GTO converter with all the required magnetic circuit was modeled. The lowest harmonic content of this converter is of 23th order and therefore is quite acceptable in FACTS applications. Since Pulse Width Modulation (PWM) methods are limited to low and medium voltage power converters, this converter simulates that exact practical approach in large FACTS implementation.

A complete and exact digital simulation of the STATCOM will be presented in Chapter 3 which includes all practical concepts such as using a 24-pulse converter, regulations slope and decoupled control. An exact and complete digital simulation of the SSSC will be presented in Chapter 4 using a 24- pulse converter.

After developing the models of the STATCOM and SSSC, their control and dynamic performance is investigated in great details. It also presents an in-depth investigation of the STATCOM stability. In order to stabilize the STATCOM under various power system operating conditions an Automatic Gain Controller (AGC) is designed and validated by digital simulation. The AGC is a powerful tool to ensure stable operation of the STATCOM.

Dynamic operation of the SSSC is investigated. A new supplementary regulator is designed to enhance the transient operation of the SSSC. The exact modeling of the SSSC made it possible for this in-depth investigation, as the mathematical modeling can not lead to the presented results.

The MATLAB Power System Blockset (PSB) of Simulink was utilized for the complete digital simulation of both the STATCOM and SSSC. They provide a powerful tool to represent the power system and power electronic components such as GTOs as well as signal processing and control components.

12

# 2.0 OPERATION AND CONTROL FUNDAMENTALS

The Static Synchronous Compensator (STATCOM) and the Static Synchronous Series Compensator (SSSC) as the shunt and series Voltage-Source Converter-Based FACTS (VSC-FACTS) devices were introduced in Chapter 1.

In this chapter the basic operation and control strategy of the STATCOM and SSSC is presented. The control of VSC-FACTS is based on d-q transformation and decoupled control. Therefore the concept of direct and quadrature axes and Park Transformation is presented. The basic component of VSC-FACTS is a converter capable of generating a three phase, almost sinusoidal voltage. The design fundamentals of a 24-pulse GTO converter, as one of the best choices for power quality reasons, are explained and the complete Matlab/Simulink digital simulation using Power System Blockset (PSB) is presented. This 24-pulse converter is the basic building block of the STATCOM and SSSC and will be used for digital simulation of them in the next chapters.

# 2.1 STATIC SYNCHROUNOUS COMPENSATOR (STATCOM)

Shunt compensation is well-known concept in AC power systems to control the reactive power flow and hence regulate the bus voltage. As explained in Chapter 1 when the real power demand of the load increases the amount of the required reactive power also increases and shunt compensation is required to provide this additional reactive power demand.

The IEEE definition of the STATCOM is [1]:

STATCOM: A static synchronous generator operated as a shunt-connected static Var compensator whose capacitive or inductive output current can be controlled independent of the AC voltage system.

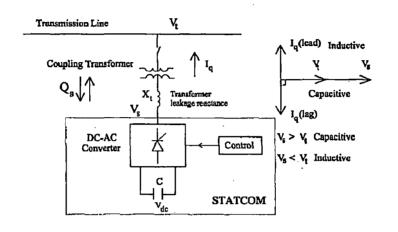

Figure 2.1 shows the basic diagram of the STATCOM. Basically, the STATCOM is a Synchronous Voltage Generator (SVG) that generates a three phase voltage from a dc source in synchronism with the line voltage. The magnitude of the STATCOM voltage can be controlled in order to adjust the amount of reactive power exchange between the STATCOM and the controlled transmission system. Therefore in Figure 2.1,  $V_s$  is in phase with  $V_t$  and there is no real power exchange between the STATCOM and the transmission system.

Figure 2.1: Static Synchronous Compensator

However, there is usually a small amount of converter switching and coupling transformer losses that should be supplied by the transmission system. Since  $V_s$  and  $V_t$  are in phase, the STATCOM current is essentially in quadrature with bus voltage,  $V_t$ , and the STATCOM voltage,  $V_s$ , and therefore it is a reactive current, Iq. The magnitude of Iq and the corresponding reactive power exchange between the STATCOM and the transmission system in per unit are:

$$|I_{q}| = \frac{V_{s} - V_{t}}{X_{t}}$$

$$Q_{s} = V_{s}I_{q} = \frac{V_{s}^{2}}{X_{t}} (1 - \frac{V_{t}}{V_{s}})$$

(2.1)

(2.2)

If  $V_s > V_t$ , the STATCOM operates in capacitive mode and supplies reactive power into the transmission system and if  $V_s < V_t$ , the STATCOM operates in inductive mode and consumes reactive power from the transmission system.

The power rating of the STATCOM depends on the required reactive power compensation at the point of connections. The load flow calculations determine the unregulated bus voltage and how much reactive power is needed to regulate the bus voltage. By knowing the STATCOM power and voltage ratings, the voltage and current ratings of the GTO's can also be determined.

#### 2.1.1 Voltage-Source Converter Operation

The basic building block of the STATCOM is converter that generates a synchronous sinusoidal voltage. For operational, control and economical reasons Voltage-Source Converters (VSC) are currently employed in FACTS applications [1].

The most practical and economical configuration that is currently used and recommended in high power utility applications is multiphase converters. The details of a multiphase converter will be presented later in this chapter. However, the mechanism by which the converter internally generates reactive power can be explained without considering the detailed operation of the solid-state switches, and only by considering the input and output powers of the converter [18]. The key to this explanation resides in the physical fact that since there is no source of internal energy in the converter, the net instantaneous power at the AC output terminals (assuming no switching losses of the converter). If the converter is operated to supply only reactive power, the real power provided by dc capacitor is zero. Furthermore since reactive power at zero frequency (capacitor voltage) is by definition zero, the dc capacitor plays no part in the reactive power generation. In other words, the reactive power is generated only due to interconnection of the AC phases by the converter in such a way that the reactive current of the AC system can flow freely between the phases. However, although reactive power is internally generated by the action of solid-state switches, it is still necessary to have a relatively small dc capacitor across the terminals of the converter. The need for the dc capacitor is primarily required to satisfy the equality of the instantaneous input and output powers of the converter. The output voltage waveform of the converter is not a perfect sine wave. However the multipulse converter injects a smooth almost sinusoidal current through the tie reactance to the transmission system. As a result the net three phase instantaneous power (VA) at the output terminals of the converter has reduced ripple content. Thus in order no to violate the equality of the instantaneous powers, the converter must draw a fluctuating current from the dc capacitor. The presence of the input ripple current components is thus entirely due to the ripple components of the output voltage, which are a function of the output wave form fabrication technique. In a high power converter, using sufficiently high pulse number, the output voltage distortion and capacitor current can be theoretically reduced to any desired value. Thus a perfect converter would generate sinusoidal output voltage and draw pure dc input current without harmonics. In practice due to system unbalance and other imperfections, as well as to economic considerations, these ideal conditions are not achieved, but approximated satisfactorily by converters of sufficiently high pulse numbers (24 or higher). For economical and hardware assembly reasons, 24-pulse or higher converters are usually employed in electric Utility Grid.

# 2.1.2 Basic Control of the STATCOM

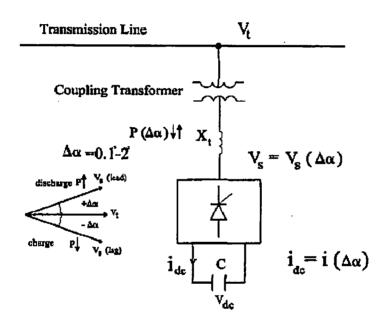

As mentioned earlier, the STATCOM voltage,  $V_s$ , is always in phase with transmission line voltage,  $V_t$ , and by fast control of the magnitude of  $V_s$  the reactive power exchange can be regulated according to compensation level. Since two level, multipulse converters are the most practical and economical converters in FACTS applications, this section deals with this type of converters.

Unlike the PWM and three level converters, two level converters do not have internal capability of voltage magnitude control and only the phase angle of the output AC voltage can

be regulated by gating signals. Therefore the only way to control the magnitude of the AC output voltage is by adjusting the input DC voltage should increase and vice-versa. In other words charging or discharging the dc capacitor voltage control is achieved by a small phase displacement,  $\Delta \alpha$ , between the STATCOM voltage, V<sub>s</sub>, and the transmission system voltage, V<sub>t</sub>. If V<sub>s</sub> lags V<sub>t</sub>, real power flows from transmission system to dc side and the capacitor is charged. Similarly if V<sub>s</sub> leads V<sub>t</sub>, real power flows from the dc side to the transmission system and the capacitor is discharged. Therefore the real power exchange is a function of phase displacement,  $\Delta \alpha$ , as shown in Figure 2.2.

Figure 2.2: Real Power Exchange of the STATCOM

This phase displacement is also required to compensate the converter switching losses by the transmission system. In practice,  $V_s$  always lags  $V_t$  by a small value (0.1<sup>o</sup>-2<sup>o</sup>) and a small real power flows from the transmission system to dc capacitor in order to compensate the converter switching and transformer losses. Additional temporary positive or negative phase displacement is required to charge or discharge the capacitor as apart of additional control system requirements.

#### 2.1.3 Vector Control Analysis

The concept of vector control of the VSC-FACTS was developed by Schauder and Mehta [17]. A decoupled control is obtained by using the Park transformation. The AC output current iof the STATCOM can be considered as a two-component current vector. The major part of the current is reactive current and performs the basic function of the STATCOM. Besides, a small portion of the current is real current that compensates for converter switching losses and charges or discharges the dc capacitor. Therefore if the STATCOM current is decomposed into real and reactive components, a decoupled control can be obtained which makes the STATCOM control simple.

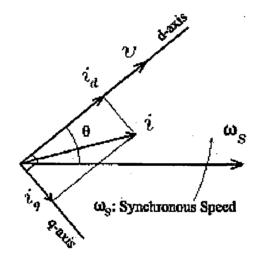

Figure 2.3: Direct and Quadrature Components of Current Vector

In general using the Park transformation, asset of three phase, symmetric variables can be decomposed into direct and quadrature components, also known as d-q transformation. Figure 2.3 shows d-q components of a current vector with respect to a reference voltage vector. The direct and quadrature coordinates within this synchronously rotating reference frame are given by the following time-varying transformation, which is called Park or d-q transformation [17]:

$$\begin{bmatrix} i_d \\ i_q \\ i_0 \end{bmatrix} = \frac{2}{3} \begin{bmatrix} \cos\theta & \cos(\theta - 120^\circ) & \cos(\theta + 120^\circ) \\ -\sin\theta & -\sin(\theta - 120^\circ) & -\sin(\theta + 120^\circ) \\ \frac{1}{2} & \frac{1}{2} & \frac{1}{2} \end{bmatrix} \begin{bmatrix} i_a \\ i_b \\ i_c \end{bmatrix}$$

(2.3)

Where  $i_a$ ,  $i_b$  and  $i_c$  are the three phase currents,  $i_d$  and  $i_q$  are the direct and quadrature components of current vector with respect to the rotating reference and  $\theta$  is the phase angle of the rotating reference.  $I_0$  is the zero component of the current vector and for a symmetric three phase variable, is always zero. Under balanced, steady-state conditions, the coordinates of the voltage and current vectors in the synchronous reference frame are constant quantities. This feature is useful for decoupled control strategy of the VSC-FACTS.

By using this transformation and considering the transmission system voltage,  $V_s$ , as the rotating reference vector, the STATCOM current can be decomposed into direct axis component, which is in phase with  $V_t$ , and quadrature axis component, which is in quadrature with  $V_t$ . The d-axis current is the real current and compensates the converter switching and coupling transformer losses as well as charges or discharges the dc capacitor. The q-axis current is the reactive current and performs the basic operation of the STATCOM which is generation or absorption of reactive power.

#### 2.1.4 Reference Signal and Regulation Slope

Since the basic purpose of the STATCOM is to regulate the transmission system voltage by reactive power compensation, line voltage,  $V_t$ , is the basic reference signal for the control of the STATCOM operation. It provides an external reference value for the STATCOM control. In many applications the STATCOM is not a perfect voltage regulator, i.e. it does not provide a fixed voltage for the transmission system, instead, a regulation slope is considered for the voltage and it is allowed to be less than the nominal voltage at full capacitive operation and

higher than the nominal voltage at full inductive operation of the STATCOM. The reasons are [1]: (1) A practical STATCOM has maximum capacitive and inductive current ratings. The linear operation range of the STATCOM can be extended if a regulation slope is allowed. (2) Perfect regulation (zero slope) could result in poorly defined steady state operating point and a tendency of oscillations. (3) A regulation slope tends to enforce automatic load sharing between static compensators, as well as other regulator devices in the grid.

A typical regulation characteristic of the STATCOM is shown in Figure 2.4. The regulation slope, k, is defined as:

#### Figure 2.4: Voltage Regulation and Regulation Slope

Where  $\Delta V_{Cmax}$  is the maximum line voltage drop at full capacitive and  $\Delta V_{Lmax}$  is the maximum overvoltage at full inductive operation of the STATCOM. I<sub>Cmax</sub> and I<sub>Lmax</sub> are the corresponding STATCOM current ratings. The reference voltage with regulation slope,  $V^*_{Ref}$ , will be:

$$V_{Ref}^* = V_{Ref} + \kappa I_q \tag{2.5}$$

$I_{Lmax}$  and  $I_{Cmax}$  are determined by the STATCOM Var capacity. Depending on the maximum capacitive or reactive power compensation,  $I_{Lmax}$  and  $I_{Cmax}$  can be determined. The voltage regulation of the STATCOM is linear if the required compensation current is between  $I_{Cmax}$  and  $I_{Lmax}$  and beyond these currents it is no longer linear and additional capacitive or reactive compensation by parallel capacitor or reactor banks can be added to meet the compensation requirements.

### 2.1.5 STATCOM Decoupled Control Strategy

As stated earlier, the magnitude and angle of the ac output voltage are the internal parameters of the STATCOM that determine the real and reactive power exchange and therefore control the operation of the STATCOM, while the transmission system voltage is the external reference signal.

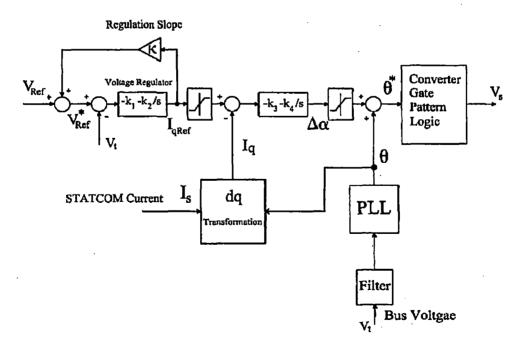

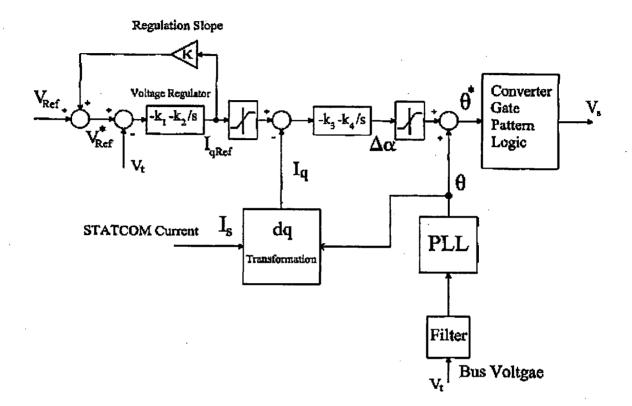

In order to synchronize the STATCOM voltage,  $V_s$ , with the line voltage,  $V_t$ , a Phase-Locked Loop (PLL) system is required. PLL provides the phase angle of the STATCOM bus voltage,  $\theta$ . This angle is also required for d-q transformation of the STATCOM current. Figure 2.5 shows the control structure of the STATCOM.

21

Transmission system voltage is compared with the reference voltage,  $V_{Ref}$  and the voltage regulator, which is a PI controller, determines the required STATCOM q-axis current,  $I_{qRef}$ , which should be limited to the STATCOM ratings. PLL system provides the basic synchronization signal,  $\theta$ , and the STATCOM q-axis current is compared with  $I_{qRef}$ . A PI controller determines the required phase displacement,  $\Delta \alpha$ , in order to charge or discharge the dc side capacitor. The phase angle  $\theta^*$  is the phase of the AC output voltage. If  $\Delta \alpha$  is negative, STATCOM voltage lags  $V_t$  and real power flows from the transmission system to the STATCOM and the dc capacitor is charged in order to make  $V_s$  higher. If  $\Delta \alpha$  is positive, real power flows from the STATCOM to the transmission system and the dc capacitor is discharged in order to make  $V_s$  lower.

## 2.2 STATIC SYNCHRONOUS SERIES COMPENSATOR (SSSC)

The series device of VSC-FACTS is the SSSC and it is basically a Synchronous Voltage Generator (SVG) that generates a three phase voltage in quadrature with the transmission system current. The IEEE definition of the SSSC is [1]:

Static Synchronous Series Compensator: A static synchronous generator operated without an external energy source as a series compensator whose output voltage is in quadrature with an controllable independently of the line current for the purpose of increasing or decreasing the overall reactive voltage drop across the line and thereby controlling the transmitted electric power.

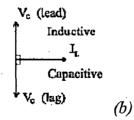

It is well-known that a series capacitor cancels a portion of the line series reactance and therefore increases the power transfer capacity of the transmission line as well as transient and steady-state stability limits. Figure 2.6 (a) shows a simple two-machine transmission system with capacitive series compensation and the corresponding phasor diagram in Figure 2.6 (b).

Figure 2.6: (a)Capacitive Series Compensation

Figure 2.6: (b) Phasor Diagram

From the phasor diagram, the effect of series capacitor can be seen as a voltage source whose voltage,  $V_c$ , is in opposite with the voltage drop of the line reactance,  $V_1$ . Therefore the total driving voltage, ( $E_L=E_1-E_2-V_c$ ), increases and hence the line current increases as well [14]. By this explanation the physical nature of the series element is irrelevant as long as it produces the desired compensating voltage. Therefore the compensating element may be considered as an ac voltage source which directly injects as voltage,  $V_c$ , in quadrature with the line current and in series the transmission system as shown in Figure 2.7 (a).

Figure 2.7: (a) Synchronous Series Compensation

Figure 2.7: (b)Phasor Diagram

If  $V_c$  lags the line current by 90<sup>0</sup>, a capacitive series compensation is obtained and if  $V_c$  leads the line current by 90<sup>0</sup>, an inductive series compensation is obtained.

## 2.2.1 Effect of Capacitive Series Compensation on the Power Flow

The effect of capacitive series compensation on real power flow in a transmission system can be investigated analytically by assuming  $|E_1| = |E_2| = E$  in Figure 2.7. The equations for real and reactive power flow without series compensation, as described in Chapter 1 are:

$$P = \frac{E^2}{X_l} \sin \delta$$

$$Q = -\frac{E^2}{X_l} (1 - \cos \delta)$$

(2.6)

(2.7)

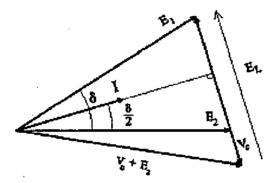

The phasor diagram of the transmission system, when  $|E_1| = |E_2| = E$  and V<sub>c</sub> lags the line current by 90<sup>0</sup> is shown in Figure 2.8.

Figure 2.8: Phasor Diagram of Capacitive Synchronous Series Compensation

Since  $|E_1| = |E_2|$  and I is perpendicular to EL, the phase angle of current vector is  $\delta / 2$ . The real and reactive power equations can be obtained as:

$$I = \frac{E \angle \delta - E - V_q \angle (\frac{\delta}{2} - \frac{\pi}{2})}{j X_l}$$

(2.8)

$$= \left(\frac{E\sin\delta + V_q\cos\frac{\delta}{2}}{X_l}\right) + j\left(\frac{E - E\cos\delta + V_q\sin\frac{\delta}{2}}{X_l}\right)$$

(2.9)

$$E_2 I^* = \left(\frac{E^2 \sin \delta + EV_q \cos \frac{\delta}{2}}{X_l}\right) + j \left(\frac{E^2 \cos \delta - E^2 - EV_q \sin \frac{\delta}{2}}{X_l}\right)$$

(2.10)

$$P_{new} = \frac{E^2}{X_l} \sin \delta + \frac{EV_q}{X_l} \cos \frac{\delta}{2} = P_{old} + \Delta P$$

(2.11)

$$Q_{new} = -\frac{E_2}{X_l} (1 - \cos \delta) - \frac{EV_q}{X_l} \sin \frac{\delta}{2} = Q_{old} + \Delta Q$$

(2.12)

Where  $\delta$  is the phase angle between the two bus voltages. Comparing with equations 2.6 and 2.7, the transmitted real power is increased by  $\left(\frac{EV_q}{X_l}\cos\frac{\delta}{2}\right)$  and the transmitted reactive power is increased by  $\left(\frac{EV_q}{X_l}\sin\frac{\delta}{2}\right)$ . The additional real power is a function of the magnitude of the injected series voltage, V<sub>q</sub>, and is limited by the series device Var capacity.

#### 2.2.2 Voltage-Source Converter-Based SSSC

The basic building block of the SSSC is a voltage-source converter that is capable of generating a synchronous three phase voltage. Like the STATCOM, two level, multiphase converter is the most practical and economical converter for the SSSC.

Figure 2.9: Static Synchronous Series Compensator

Figure 2.9 shows the basic diagram of the SSSC.  $V_c$  is in quadrature with line current,  $I_L$ , there is no real power exchange between the SSSC and the transmission system. There are two operating modes: If  $V_c$  lags by  $I_L$  by 90<sup>0</sup>, capacitive series compensation is obtained and inductive series compensation is obtained if  $V_c$  leads the line current by 90<sup>0</sup>.

The power and voltage ratings of the SSSC depend on the required series injected reactance,  $X_s$ , and the transmission line current. The required  $X_s$  is obtained from the power flow calculations and is usually less than 50% of the series line reactance.

For a higher transmission line current a bigger SSSC voltage and thus more reactive power is required. By knowing the range of  $X_s$  and the transmission line current, the required SSSC voltage and power can be calculated.

#### 2.2.3 Basic Control Scheme of the SSSC

The main function of the SSSC is to control the real power flow. This can be accomplished either by direct control of the line current (power) or alternatively by indirect control of either the compensating impedance,  $X_s$ , or the compensating voltage, Vc [1]. The direct power flow control has the advantage of maintaining the transmitted power in a closed loop manner by the defined reference. However, under some network contingency, the maintenance of the constant power flow may not be either possible or even desirable. Therefore in some applications the impedance (or voltage) control that maintains the impedance characteristic of the line may be preferred from the operating standpoint. The degree of series impedance compensation, S, is usually expressed as the ratio of the series injected reactance, X<sub>s</sub>, to the line reactance, X<sub>1</sub>, i.e.

$S = X_s / X_l$ . Therefore for a capacitive series compensation, the line series reactance is  $X_{Line} = X_l - X_s$ , where  $X_s = SX_l$ . Similarly, for an inductive series compensation, the line series reactance is  $X_{Line} = X_l + X_s$ , where  $X_s = SX_l$ . The basic function of tehcontrol system is to keep the SSSC voltage,  $V_c$ , in quadrature with the line current,  $I_L$ , and the control the magnitude of

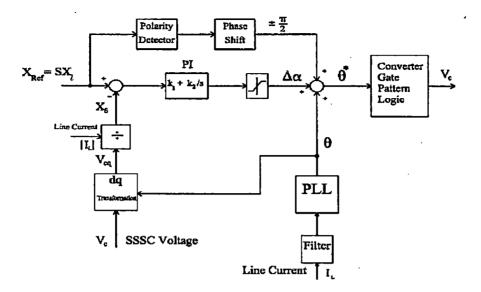

$V_c$  to meet the compensation requirement, which the degree of series compensation. The control structure of the SSSC is shown in Figure 2.10.

Figure 2.10: Control Structure of the SSSC

The basic synchronization signal,  $\theta$ , is the phase angle of line current. The SSSC injected impedance is measured as the ratio of q-axis voltage of the SSSC,  $V_{cq}$ , to the magnitude of the line current,  $I_L$ . This impedance is then compared with the reference compensation impedance,  $SX_I$ . A PI controller generates the required phase displacement,  $\Delta \alpha$ , in order to charge or discharge the dc capacitor. A negative  $\Delta \alpha$  yields to the real power flow from the transmission system to the SSSC and charges the dc capacitor, while a positive  $\Delta \alpha$  discharges the dc capacitor. When  $X_{Ref}$  is negative,  $V_c$  lags  $I_L$  by 90<sup>0</sup> plus  $\Delta \alpha$  (capacitive compensation) and when it is positive  $V_c$  leads  $I_L$  by 90<sup>0</sup> plus  $\Delta \alpha$  (inductive compensation). The final output of the control system is the phase angle of the SSSC output voltage,  $\theta^*$ .

#### 2.3 DESIGN AND SIMULATION OF A 24-PULSE CONVERTER

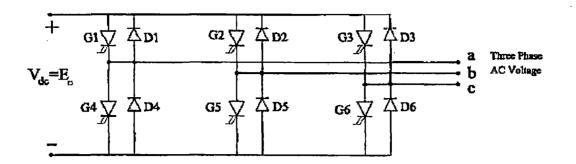

It was explained that the two level, multipulse converter as given in 1.3.2 is the most practical and economical converter in the STATCOM and SSSC applications. Figure 2.11 shows the configuration of the three phases, voltage-source, 6-pulse, GTO converter. The gating pulses of the GTOs are such that each is closed for  $180^{\circ}$ .

Figure 2.11: Three Phase, 6-Pulse, Voltage-Source GTO Converter

G2 is closed  $120^{\circ}$  after G1 and G3,  $120^{\circ}$  after G2. When a switch in one leg is closed, the other one is open and vice versa. The diodes are to provide current path during the interval that a switch is closed and the inductive load current is not zero [34].

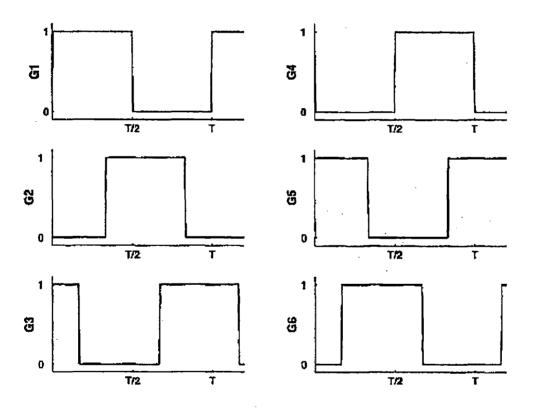

Figure 2.12: Gating Pulses of the 6-Pulse Converter

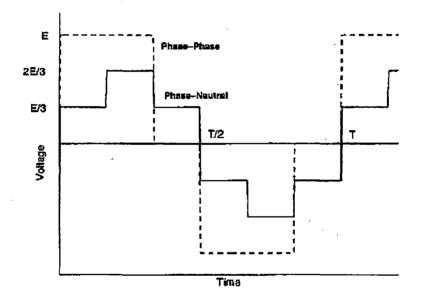

Figure 2.12 shows the gating pulses of the basic 6-pulse converter, generated by the Simulink. Figure 2.13 shows the phase to neutral and phase to phase voltages of the 6-pulse converter. The Fourier expansion of phase to neutral voltage,  $V_{an}$ , is:

$$V_{an} = \frac{2E_{\circ}}{\pi} (\sin \omega t + \frac{1}{5} \sin 5\omega t + \frac{1}{7} \sin 7\omega t + \frac{1}{11} \sin 11\omega t + \cdots)$$

(2.13)

Where  $E_0$  is the dc source voltage. Equation 2.13 can be written as:

$$V_{an} = \sum_{n=1,5,7,11,\dots} \frac{2E_{\circ}}{n\pi} \sin n\omega t$$

(2.14)

Similarly the Fourier expansion of phase-phase voltage,  $V_{ab}$ , is:

$$V_{ab} = \frac{2\sqrt{3}E_{\circ}}{\pi} [\sin\left(\omega t + \frac{\pi}{6}\right) - \frac{1}{5}\sin 5(\omega t + \frac{\pi}{6}) - \frac{1}{7}\sin 7(\omega t + \frac{\pi}{6}) + \frac{1}{11}\sin 11(\omega t + \frac{\pi}{6}) + \cdots]$$

(2.15)

Figure 2.13: Phase-Neutral and Phase-Phase Voltages of the 6-Pulse Converter

Which can be written as:

$$V_{ab} = \sum_{n=1,5,7,11,\dots} \frac{4E_{\circ}}{n\pi} \cos \frac{n\pi}{6} \sin n(\omega t + \frac{\pi}{6})$$

(2.16)

It can be seen that  $V_{ab}$  is phase shifted by  $\Pi/6$  and multiplied by  $\sqrt{3}$  in comparison with Van. Now shifting  $V_{ab}$  by -  $\pi/6$  and dividing it by  $\sqrt{3}$ , then adding to  $V_{an}$  gives:

$$\frac{1}{\sqrt{3}}V_{ab}e^{-j\frac{\pi}{6}} + V_{an} = \frac{4E_{\circ}}{\pi}(\sin\omega t + \frac{1}{11}\sin 11\omega t + \frac{1}{13}\sin 13\omega t + \cdots)$$

(2.17)

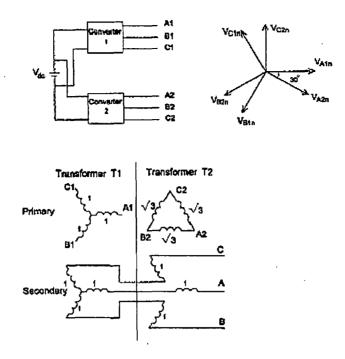

The importance of this process is that only  $12k \pm 1$  harmonics exist in the resulting ac voltage, instead of  $6k \pm 1$  harmonics in a 6-pulse converter and hence a 12-pulse converter is obtained with less harmonic distortion and a waveform closer to sinusoidal. One practical approach to obtain a 12-pulse converter is to combine two 6-pulse converters by two transformers as shown in Figure 2.14. Transformer T1 is a Y-Y transformer and is connected to converter1. The primary of transformer T2 is  $\Delta$  connected in order to provide phase-phase voltage in the secondary. Gating pulses of converter 2 lag the pulses of converter 1 by  $30^{0}$ , so that the required time shifting of phase-phase voltage of converter 2 is also multiplied by  $1/\sqrt{3}$ .

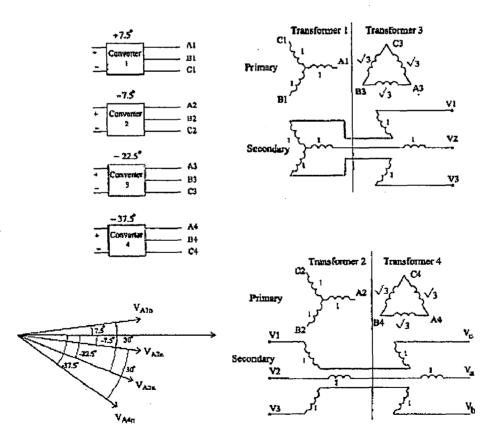

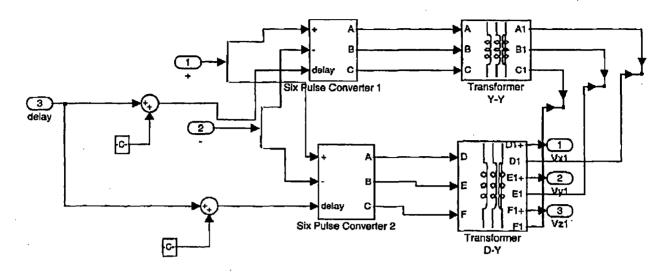

The harmonic contents of a 12-pulse converter may not be acceptable in many FACTS applications, so a 24-pulse converter may be desirable. The phase displacement between two consecutive 6-pulse converters in a multiphase converter configuration is  $2\pi/6m$ , where *m* is the total number of 6-pulse converters [30]. Therefore for a 24-pulse converter this phase displacement is  $15^{0}$ . By combining four 6-pulse converters a 24-pulse converter can be obtained which only has  $24k \pm 1$  harmonics and hence the lowest harmonic will be of 23th order. Figure 2.15 shows the configuration of a 24-pulse converter.

Converter 3 lags converter 1 by  $30^{\circ}$  and converter 4 lags converter 2 by  $30^{\circ}$ . Hence converters 1 and 3 make a 12-pulse converter and converters 2 and 4 make the other 12-pulse converter. The two 12-pulse converts are combined to generate the desired 24-pulse voltage.

Figure 2.14: Configuration of a 12-Pulse Converter

Figure 2.15: Configuration of a 24-Pulse Converter

#### 2.3.1 Modeling and Digital Simulation

Simulink and Power System Blockset (PSB) of Simulink were used to implement a full digital simulation of 12 and 24-pulse converters. The configurations of Figures 2.14 and 2.15 were digitally simulated by Simulink/PSB in order to provide the basic building block of the STATCOM and SSSC that will be used in the next chapters.

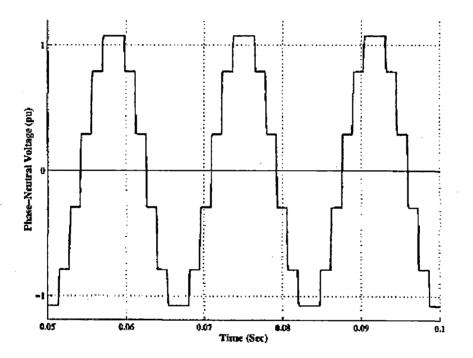

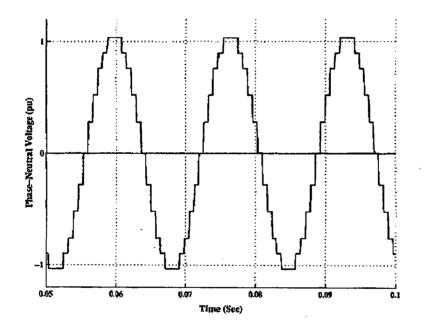

Figure 2.16 shows the digital simulation of the 12-pulse converter voltage with the fundamental frequency of 60Hz. Similarly, the digital simulation of the 24-pulse converter voltage is shown in Figure 2.17. It should be noted that the 24-pulse converter was designed with variable phase angle and therefore the phase angle of the output ac voltage can be controlled which is a requirement for the STATCOM and SSSC applications.

Figure 2.16: PSB Simulation of a 12-Pulse Converter

In order to measure the harmonic contents of the 24-pulse converter, Total Harmonic Distortion (THD) was measured by PSB model of the converter. Defining THD as:

$$THD = \frac{\sqrt{V_2^2 + V_3^2 + \dots + V_n^2}}{V_1} = \frac{V_h}{V_1}$$

(2.18)

32

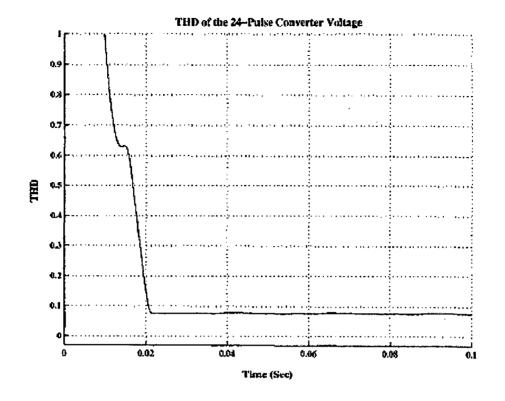

Where  $V_1$  is rms value of the *i*th harmonic,  $V_h$  is rms value of total harmonic content and  $V_1$  is rms value of fundamental harmonic. Figure 2.18 shows the THD measurement of the 24pulse voltage. THD was measured to be 0.075. Since the total rms value of voltage,  $V_{rms}$ , is

$$\sqrt{V_1^2 + V_h^2}$$

and  $V_h = 0.075 V_1$ , we conclude that:

$$V_{rms} = \sqrt{V_1^2 + V_h^2} = \sqrt{V_1^2 + (0.075V_1)^2} = 1.00280V_1$$

(2.19)

Or  $V_1 = 0.997$ Vrms. Thus it results in only 0.3% of ripple harmonic contents. Therefore the generated 24-pulse voltage at the ac side of the converter can be considered almost a sinusoidal waveform.

Figure 2.17: PSB Simulation of a 24-Pulse Converter

Figure 2.18: THD of the 24-Pulse Voltage

# **3.0 STATCOM: A COMPLETE DIGITAL SIMULATION STUDY**

The operation and control fundamentals of the STATCOM were introduced in Chapter 2. A complete digital simulation of the STATCOM within a power system is presented in this chapter. The digital simulation is performed in MATLAB/Simulink environment using the Power System Blockset (PSB). The basic building block of the STATCOM is a 24-pulse converter whose complete digital simulation was presented in Chapter 2. The control process is based on a decoupled strategy using direct and quadrature components of the STATCOM current. The operation of the STATCOM is validated in both capacitive and inductive modes in a power transmission system.

#### **3.1 POWER SYSTEM DESCRIPTION**

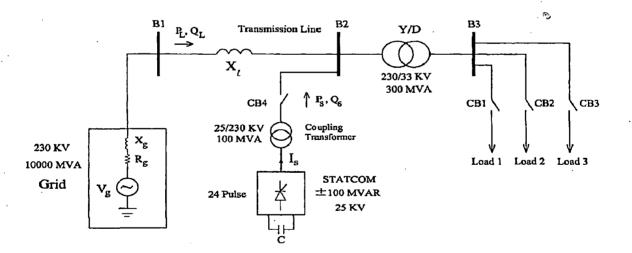

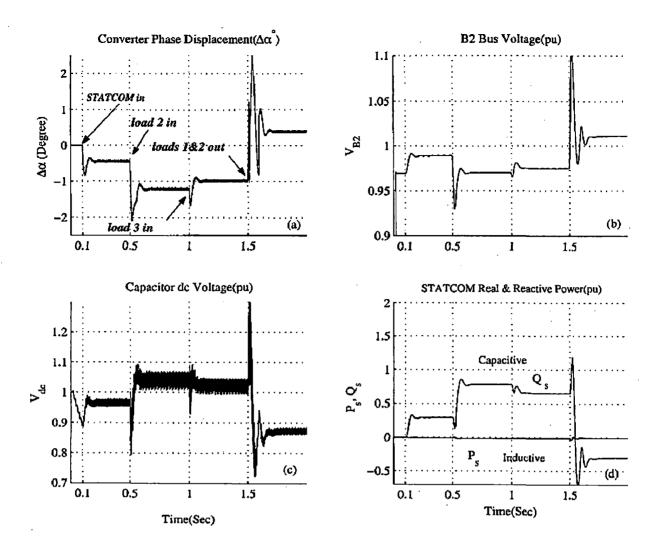

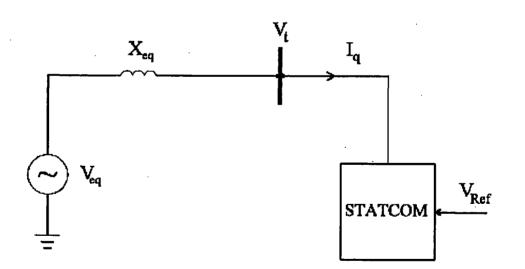

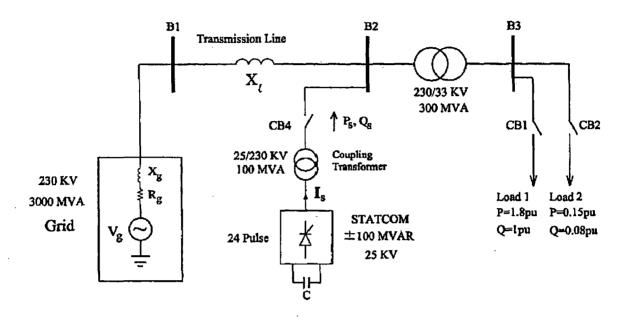

The single line diagram of the sample power transmission system that will be used to validate the operation of the STATCOM is shown in Figure 3.1.

Figure 3.1: Single Line Diagram of the Power Transmission System with the STATCOM The grid is represented by a 230KV source with 10000 MVA short circuit power with a resistance of 0.1 pu and a reactance of 0.3 pu. The system parameters are as below:

- (a) *Transmission Line*:

- Reactance, X<sub>1</sub>: 0.2 pu (230 KV, 300 MVA)

- (b) Power Tranformers:  $(Y/\Delta)$

- Rated Voltage: 230/33 KV

- Rated Power: 300 MVA

- Leakage Reactance: 0.01 pu

# (c) STATCOM:

- Type of Valves: GTO

- Number of Pulses: 24

- Nominal AC Voltage: 25KV

- Nominal DC Voltage: 2 KV

- Rated Power: ±100 MVAR

- GTOs Forward Resistance:  $1m \Omega$

## (d) Capacitor Bank(dc):

- Total Capacitance: 10 mF

- Rated DC Voltage: 2 KV

# (e) CouplingTransformer:(Y/Y)

- Rated Voltage: 25/230 KV

- Rated Power: 100 MVA

- Resistance: 0.001 pu

- Leakage Reactance: 0.08 pu

## 3.2 CONTROL SYSTEM DESCRIPTION

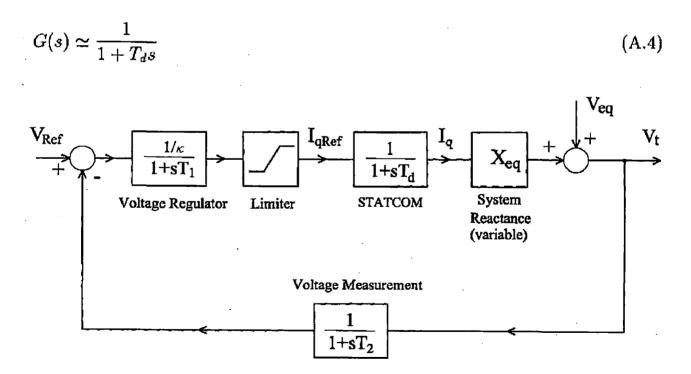

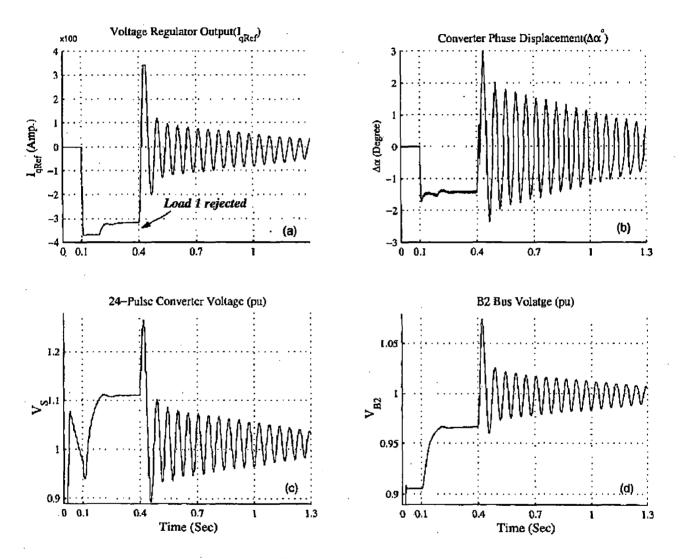

The decoupled control structure was developed in Chapter 2 and is shown in Figure 3.2. The voltage regulator is a PI controller with  $K_p = 0.004$  and  $K_i = 3$ .