# DESIGN OF LOW LEAKAGE HIGH PERFORMANCE MGDG BASED SRAM at 32nm TECHNOLOGY NODE

### **A DISSERTATION**

Submitted in partial fulfillment of the requirements for the award of the degree

of

MASTER OF TECHNOLOGY

in

ELECTRONICS AND COMMUNICATION ENGINEERING (With Specialization in Semiconductor Devices and VLSI Technology)

### By

## VENKATA KOMAL KUMAR K

DEPARTMENT OF ELECTRONICS AND COMPUTER ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE - 247 667 (INDIA)

**JUNE, 2008**

## **CANDIDATE'S DECLARATION**

I hereby declare that the work, which is being in this dissertation report, entitled "Design of Low Leakage High Performance MGDG Based SRAM at 32nm Technology Node", is being submitted in partial fulfillment of the requirements for the award of the degree of Master of Technology in Semiconductor Devices and VLSI Technology, in the Department of Electronics and Computer Engineering, Indian Institute of Technology, Roorkee is an authentic record of my own work, carried out from June 2007 to June 2008, under guidance and supervision of Dr. R. C. Joshi, and Dr. S. Dasgupta, Department of Electronics and Computer Engineering, Indian Institute of Technology.

The results embodied in this dissertation have not been submitted for the award of any other Degree or Diploma.

Date: 30/06/08 Place: Roorkee

Konnelte k v

Venkata komal Kumar K

CERTIFICATE

This is to certify that the statement made by the candidate is correct to best of my knowledge and belief.

Lu 50/6/08

Dr. R. C Joshi, Professor Dept. of Electronics & Computer Engg., IIT Roorkee, Uttarakhand, India E-mail: joshifcc@iitr.ernet.in

30 06 08

Dr. S. Dasgupta, Assistant Professor Dept. of Electronics & Computer Engg., IIT Roorkee, Uttarakhand, India E-mail: sudebfec@iitr.ernet.in

### ACKNOWLEDGEMENT

I would like to express my sincere gratitude to my dissertation supervisors, Dr. R. C. Joshi and Dr. S. Dasgupta. Their research visions and sharp insights were instrumental in the completion of this work. I have deep sense of admiration for their innate goodness and inexhaustible enthusiasm. It helped me to work in right direction to attain desired objectives. They believed in me and cherished high hopes for me and their optimistic attitude taught me to overcome my doubts. They brought out the best in me as a graduate student and I feel privileged to have worked with them. I have learnt from them how to analyze complex problems in simple way.

I feel fortunate to discuss my ideas with Research scholars S. K. Vishvakarma and Balwinder Raj in SDVT group and I am grateful to them for the constructive criticism which helped me to finish work with more accuracy. This work could not have been possible without the constant encouragement and strong support of all my friends at IIT Roorkee.

My sincere thanks are also due to rest of the faculty in the Department of Electronics and Computer Engineering at Indian Institute of Technology Roorkee, for the technical knowhow and analytical abilities they have imbibed in us which have helped me in dealing with the problems I encountered during the project.

Venkata Komal Kumar K

### ABSTRACT

Logic and memory circuit design in nanoscale regime requires control over leakage currents and process parameter variations. Metal Gate Double Gate (MGDG) MOSFET has been proved to be vital in nanoscale regime for its leakage reduction with appropriate second gate bias and reduced sensitivity to process parameter variations. Unfortunately leakage minimization techniques using body bias forces the design to have increased transition time. We demonstrated that SRAM cell designed with MGDG-MOSFET has the benefit of reduced transition time. We did analytical modeling of the small signal capacitances that affect circuit operation from which glitch voltage at the output has been evaluated and validated through HSPICE simulations and less glitch voltage has been observed for MGDG MOSFET compared to the bulk case. Also, we estimated all leakage currents by considering interconnect effect and used them in finding voltage rise/fall at the critical nodes of SRAM cell. We have emphasized on low leakage, high performance robust cache subarray design with the help of MGDG devices. Suppressing leakage currents and maintaining constant Static Noise Margin (SNM) in ultra low voltage operation is crucial for circuit designers. We did SNM analysis of SRAM designed using our gate work function Engineered MGDG MOSFET and it is confirmed through HSPICE simulations that the cell is able to maintain constant SNM at ultra low voltage operation and more robust to process variations.

# CONTENTS

| Candidate's   | declaration and certificate                                     | i   |

|---------------|-----------------------------------------------------------------|-----|

| Acknowledg    | gement                                                          | ii  |

| Abstract      |                                                                 | iii |

| List of Figur | res                                                             | vi  |

| List of Tabl  | es                                                              | ix  |

| Chapter 1:    | Introduction and statement of the problem                       | 1   |

| 1.1           | Introduction                                                    | . 1 |

| 1.2           | Motivation                                                      | 2   |

| 1.3           | Problem Statement                                               | 2   |

| 1.4           | Organization of the report                                      | 3   |

| Chapter 2:    | Review of Design Problems in Nanometer Cache Memories           | 5   |

| 2.1           | Design Problems in Nanometer Bulk CMOS Technologies             | 5   |

| 2.2           | High Performance Low Leakage Circuit Design in Nanoscale Regime | 6   |

| 2.3           | Conventional Leakage Reduction Methods of SRAM and Their        | 7   |

|               | Performance                                                     |     |

| 2.4           | Reliability Issues of SRAM cell                                 | 8   |

| Chapter 3:    | Leakage Currents Estimation of MGDGMOSFET                       | 10  |

| 3.1           | Proposed Gate workfunction engineered MGDG MOSFET               | 10  |

| 3.2           | Modeling of Leakage Current in MGDGMOSFET                       | 11  |

| 3.3           | Stack Effect Analysis of MGDG MOSFET                            | 18  |

| 3.4           | Effect of Back Gate Bias on Leakage Currents                    | 19  |

| Chapter 4:    | Leakages and Nanometer Cache design using MGDGMOSFET            | 21  |

| 4.1           | Leakage currents present in MGDG SRAM                           | 21  |

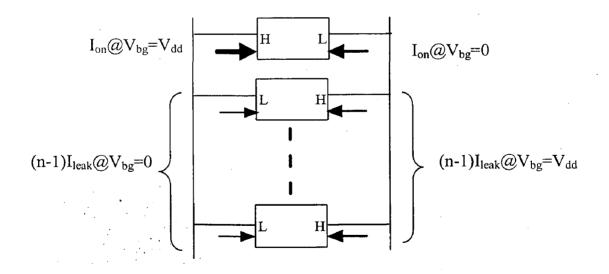

| 4.2           | Proposed Backgate biasing scheme using MGDG MOSFET              | 22  |

| 4.3           | Estimation of Semiconductor Capacitance and transition time     | 23  |

| Chapter 5:    | Small Signal capacitance and glitch voltage estimation          | 25  |

| 5.1           | Causes of Potential rise at output                              | 25  |

| 5.2           | Estimation of small signal capacitances of MGDG MOSFET          | 25  |

| 5.3           | Estimation of Voltage Rise during Signal Transitioning Events   | 29  |

| 5.4                                     | Failure Probabilities and their dependency on Leakage Currents 33                                     |    |        |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------|----|--------|

| Chapter 6:                              | Ultra Low Voltage SRAM design Using MGDG MOSFET                                                       |    |        |

| 6.1                                     | Design Problems at Ultra Low Voltage SRAM                                                             |    | 38     |

| 6.2                                     | Data Retention Voltage Analysis of MGDG MOSFET                                                        |    | 38     |

| 6.3                                     | Description of sub threshold SRAM architecture                                                        |    | 40     |

| 6.4                                     | Results for Ultralow Voltage SRAM cell design                                                         |    | 45     |

| Chapter 7:                              | Conclusion and Further Scope                                                                          |    | 50     |

| Appendix A:<br>Afrendix B<br>References | Power Dissipation analysis of the decoder using Stack effect<br>List of Parameters Used in Simulation |    | Con Co |

| List of Publi                           | cations                                                                                               | 61 |        |

# List of Figures

| Figure No.  | Title of Figure Pag                                                     | e No. |

|-------------|-------------------------------------------------------------------------|-------|

| Figure 1.1  | Power trends according to ITRS-2007 roadmap                             | 1     |

| Figure 2.1  | Poly- depletion Effect                                                  | 5     |

| Figure 2.2  | Biasing Schemes of SRAM Cell                                            | 8     |

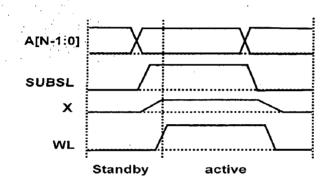

| Figure 2.3  | Wake up of Subarray in Backgate biased SRAM                             | 8     |

| Figure 3.1  | MGDG MOSFET and associated leakage current components                   | 10    |

| Figure 3.2  | Variation of subthreshold current with drain bias                       | 13    |

| Figure 3.3  | Variation of gate to channel current with gate bias                     | 14    |

| Figure 3.4  | Variation of gate to channel current with oxide thickness               | 15    |

| Figure 3.5  | Variation of edge direct tunneling current with gate to drain bias      | 16    |

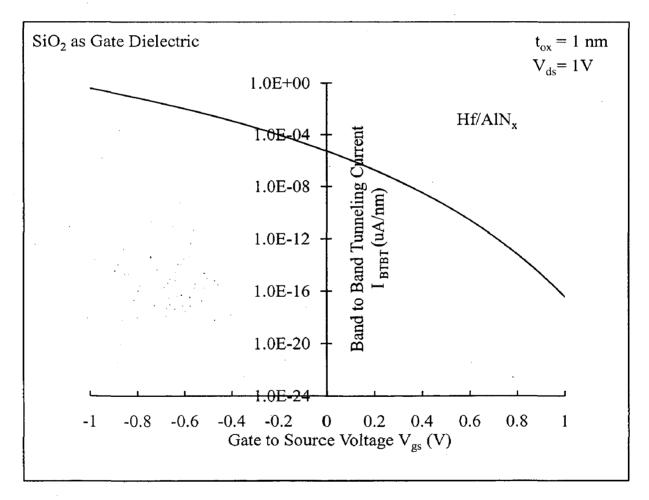

| Figure 3.6  | Variation of band to band tunneling current with gate to source voltage | 15    |

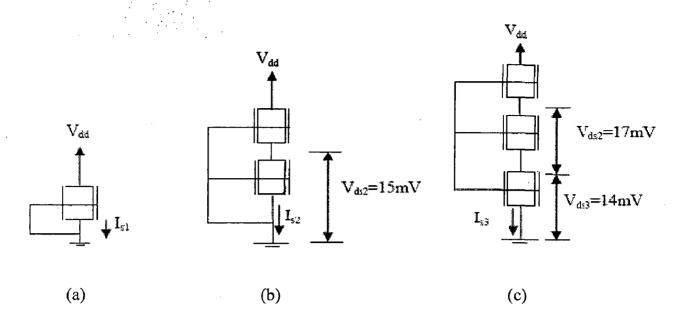

| Figure 3.7  | Stacked DG-NMOS transistors with $V_{gs} = 0$                           | 18    |

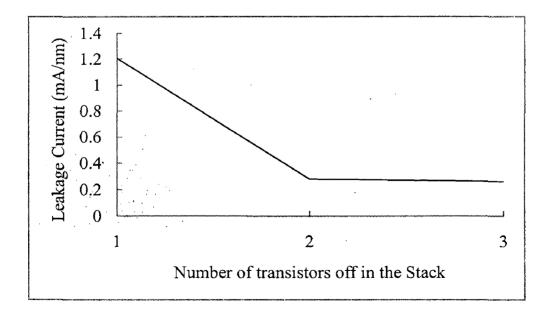

| Figure 3.8  | Leakage Current reduction with increasing number of off transistors.    | 18    |

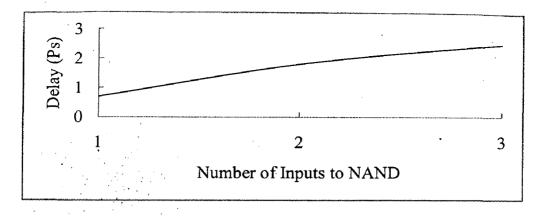

| Figure 3.9  | Delay increase observed usign Hspice with increasing number of inputs   | s 19  |

| Figure 3.10 | Variation of subthreshold current with Back Gate Bias.                  | 20    |

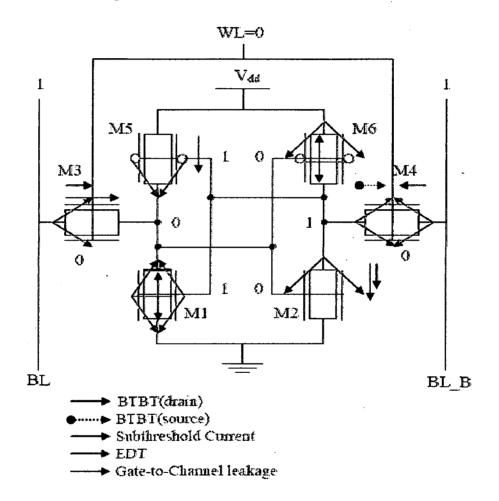

| Figure 4.1  | leakage components in MGDG SRAM cell during idle mode                   | 21    |

| Figure 4.2  | Proposed leakage reduction scheme using MGDG MOSFET.                    | 22    |

| Figure 4.3  | Semiconductor capacitance variation with back gate bias                 | 23    |

| Figure 5.1  | Gate-Drain capacitance variation with drain potential from              | 27    |

|             | analytical modeling of MGDG MOSFET vs DESIS-ISE simulation              |       |

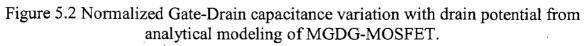

| Figure 5.2  | Normalized Gate-Drain capacitance variation with drain potential from   | n 27  |

|             | analytical modeling of MGDG MOSFET                                      |       |

| Figure 5.3  | Normalized Gate-Drain capacitance variation with gate potential from    |       |

|             | analytical modeling of MGDG MOSFET                                      | 28    |

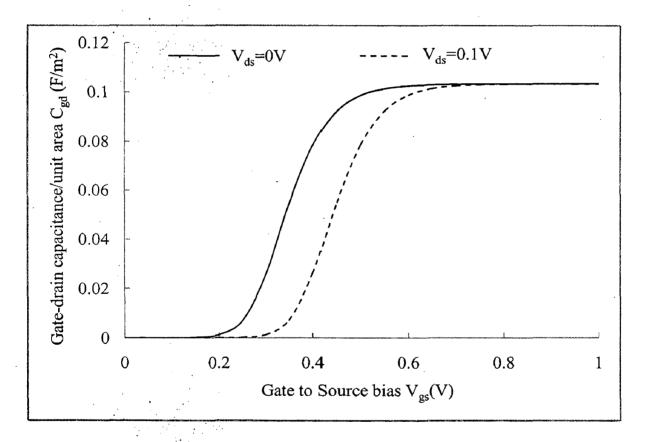

| Figure 5.4  | Gate-Source capacitance variation with drain potential from analytical  |       |

|             | modeling of MGDG MOSFET                                                 | 29    |

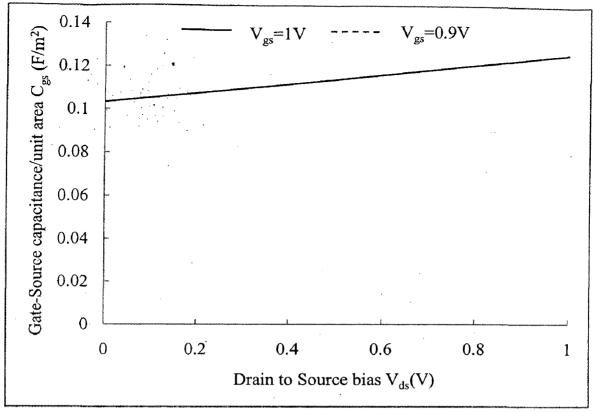

| Figure 5.5  | Glitch model of general CMOS logic circuits                             | 30    |

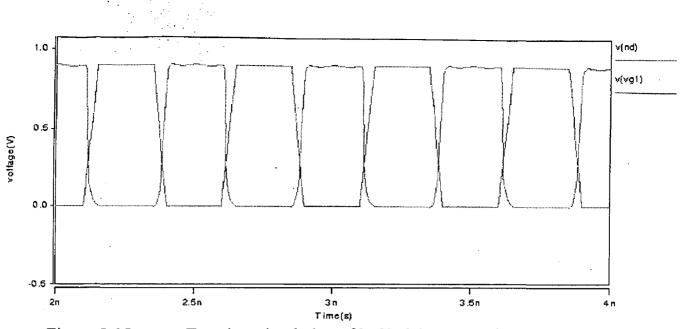

| Figure 5.6  | Inverter Transient simulation of MGDG inverter using HSPICE             | 31    |

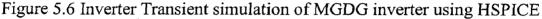

| Figure 5.7  | Validation of Potential fall using our model and HSPICE Simulations     | 31    |

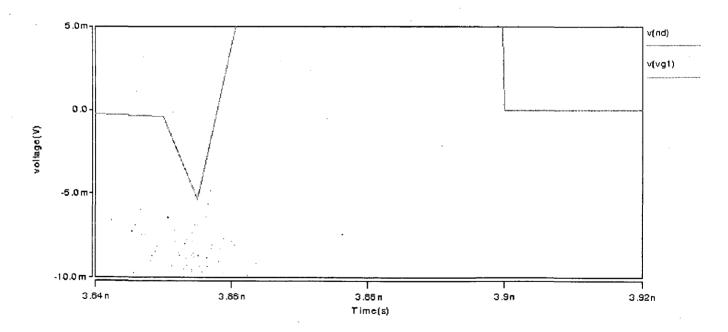

| Figure 5.8  | Inverter Transient simulation of Bulk CMOS inverter using HSPICE        | 32    |

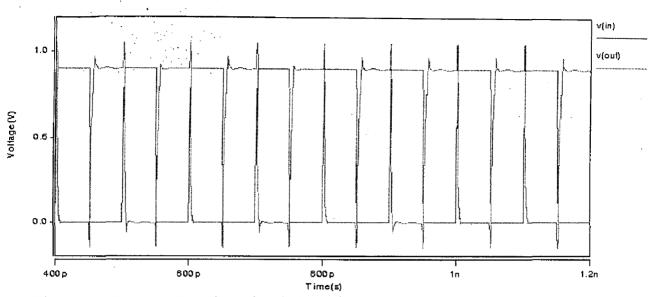

| Figure 5.9  | Magnified view of Potential rise using HSPICE simulations of b    | ulk        |

|-------------|-------------------------------------------------------------------|------------|

|             | MOSFET                                                            | 32         |

| Figure 5.10 | Leakage components in nanoscale DG SRAM cell during read          | operation  |

|             |                                                                   | 34         |

| Figure 5.11 | Leakage components in nanoscale DG SRAM cell during write         | operation  |

| ,           |                                                                   | 34         |

| Figure 6.1  | Read disturbance caused in nanoscale SRAM                         | 40         |

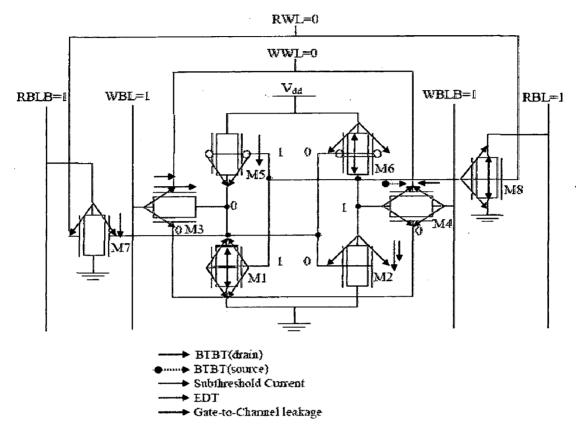

| Figure 6.2  | SRAM cell designed for subthreshold operation                     | 41         |

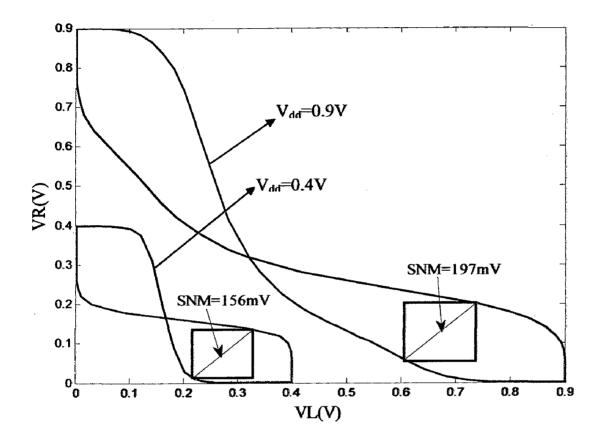

| Figure 6.3  | SNM under Read/Hold modes at different supply voltages            | 42         |

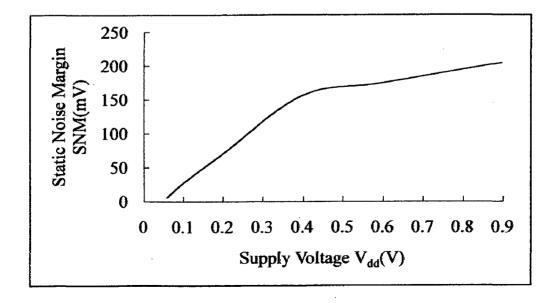

| Figure6.4   | Variation of read/Hold mode SNM with supply voltage               | 42         |

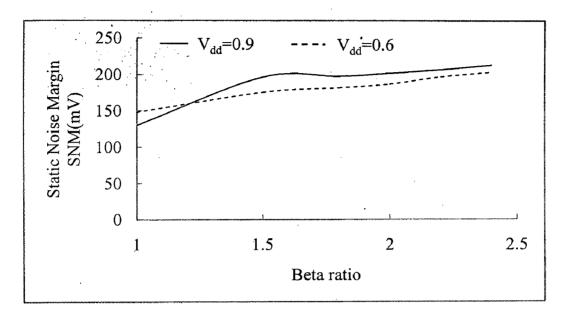

| Figure6.5   | Variation of read/Hold mode SNM with Beta ratio                   | 43         |

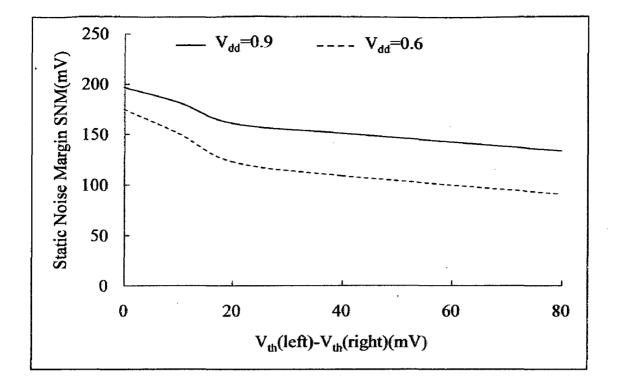

| Figure 6.6  | Variation of read/hold mode SNM with threshold voltage difference | es         |

|             | of cross coupled inverters                                        | 44         |

| Figure6.7   | SNM Variation due to Process variation                            | 44         |

| Figure 6.8  | Worst case condition during read operation                        | 45         |

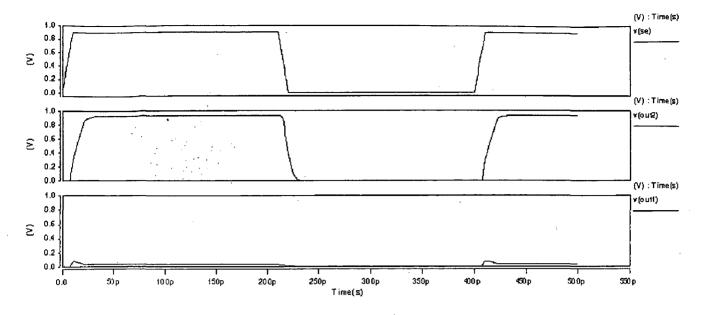

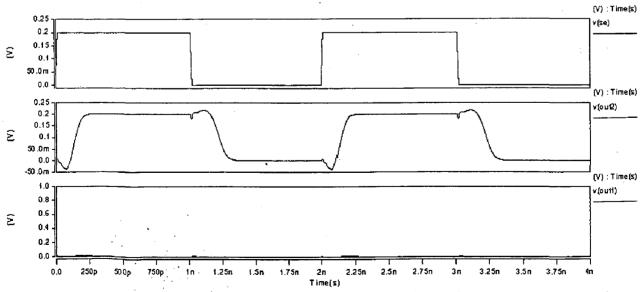

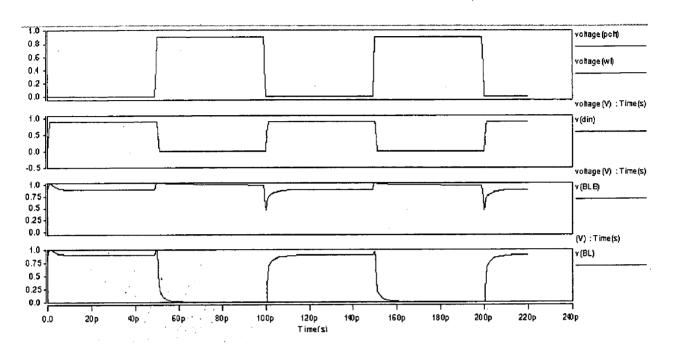

| Figure 6.9  | Output of Sense amplifier during reading phase of SRAM cell       | 46         |

| Figure 6.10 | Output of Sense amplifier during reading phase of SRAM cell at    |            |

|             | ultra low voltage                                                 | 46         |

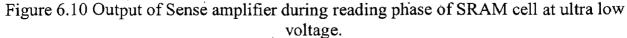

| Figure 6.11 | Read delay degradation of proposed scheme                         | 47         |

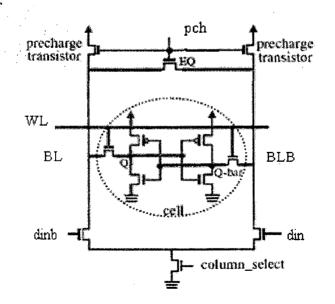

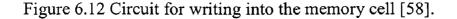

| Figure 6.12 | Circuit for Writing into the memory cell                          | 47         |

| Figure 6.13 | Output of writing circuitry of MGDG-SRAM cell at 0.9V supply      | voltage 48 |

| Figure 6.14 | Output of complete SRAM cell at ultra low voltage operation       | 48         |

vii

.

# List of Tables

| Table No. | Title of Table                                               | Page No. |

|-----------|--------------------------------------------------------------|----------|

| Table 2.1 | Selection of Codesign Scheme                                 | 7        |

| Table 5.1 | Leakage Currents estimated using our analytical modeling for | 35       |

|           | NMOS and their variation with potential fall at source.      |          |

| Table 5.2 | Leakage Currents estimated using our analytical modeling for | 35       |

|           | PMOS and their variation with potential fall at source.      |          |

| Table A.1 | Parameters of BSIM SOI 3.2 NMOS Model card for 32nm FINFI    | ET 52    |

# Chapter 1

### Introduction

#### **1.1 Introduction**

A closer look in recent technology nodes reveals that early signs of scaling limits were seen in high-performance devices. To obtain the projected performance gain of 30% per technology generation, device designers have been forced to relax the device subthreshold leakage continuously. Consequently, passive power density is now a significant portion of the power budget of a high-speed microprocessor.

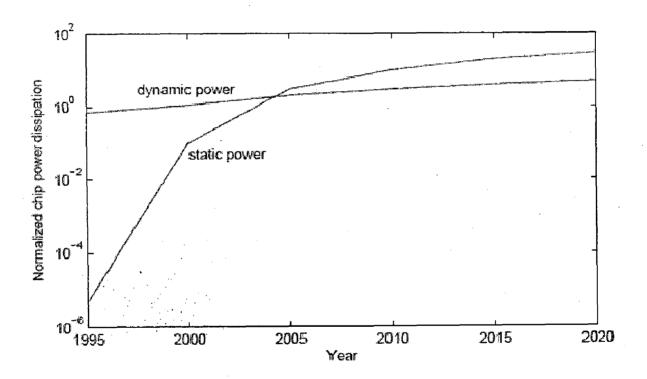

Figure 1.1 Power trends according to ITRS-2007 roadmap [1].

The increased variation of process parameters of nanoscale devices not only results in higher average leakage power (mean) but also in a larger spread of leakage power (standard variation). Some low leakage chips with too slow speed and some other faster chips with too high leakage have to be discarded. As a result, both power yield and timing yield are seriously affected by the process variations. Process variations are basically separated into inter-die and intra-die variation [2]. Inter-die variation or global variation refers to variations from wafer to wafer, or die to die on a same wafer while

intra-die variation or local variation occurs across an individual die that means on same chip devices at different locations may have different process parameters. Since inter-die variation affects all the devices on a chip in the same way, it has a stronger effect on circuit power and performance.

According to ITRS predictions, by 2014 memory is going to occupy 94% of chip area, so power consumption, performance and reliability of total system is determined by memory. Also, many high performance processors dedicate large fraction of their area to caches which are designed using SRAM. Proper attention is needed for standby power estimation, robust high performance subarray design of nanometer cache and its associated timing. Also, in sensor network nodes burst of activity occurs in response to an input event, and the system is otherwise idle for most of the time. Hence one should be able to operate at ultra low voltages [3].

#### 1.2 Motivation

Design of nanoscale device providing high performance and reduced leakage currents with reduced sensitivity to process parameter variations is challenging at nanoscale dimensions. Estimation of small signal capacitances and leakages helps to estimate glitch voltage present at output and gives idea on robustness and performance of the circuit which reduces design time at higher levels of abstraction [4]. Also, leakage current determination using interconnection effect gives better insight into reliability of the circuit. At lower voltages ratio of on current ratio with backgate voltage of  $V_{dd}$  and 0V is more for MGDG MOSFET and this feature can be used for obtaining superior ultra low voltage characteristics than bulk MOSFET which will be more useful in sensor network nodes and improves battery lifetime.

#### **1.3 Problem Description**

Leakage and process variation are two major problems faced by the semiconductor nanometer technologies [2], [5], [6]. Designers have been forced to relax limits on subthreshold leakage to have 30% performance increase with each technology generation [1]. In addition aggressive scaling of gate dielectric causes catastrophic gate leakage [7] in nanometer regime. Further, as the silicon industry is moving towards the possible end of the roadmap, controlling the variation in device parameters during fabrication becomes a great challenge. Variations in process parameters such as oxide

thickness, channel length, channel thickness and dopant placement result in large variations in threshold voltage which subsequently threatens the yield of nanoscale circuits/memories [8]. Further the leakage minimization schemes involve additional transition time and lot of complexity in row decoder design.

In circuits operating at nanoscale regime voltage rise or fall at output node during signal transitioning events creates timing, noise and glitch related problems. So, to perform early power and timing estimates, one needs an efficient method to estimate the small signal capacitances of the selected device structure and leakage currents at respective nodes in the circuit using interconnection effect. Leakage currents also determines the potential rise or fall, so leakage current estimation using interconnection effect and solution of nodal current equations at different nodes of circuit gives better insight into the robustness of the circuit. Also, transition time and energy overhead required for the backgate biasing schemes needs to be considered for high performance and low leakage which can be estimated by finding semiconductor capacitance at optimum biasing point. Due to increased composition of memory in today's high performance processors power consumption, performance and reliability of total system is determined by Memory. Stand by Power can be minimized by reducing the supply voltage to a limit called data retention voltage (DRV) [9], [10] at which memory cell can just retain the data stored while reducing all leakage currents. Data retention voltage is further influenced by process variations of minimum geometry transistors used in present day technology. Maintaining almost constant Static Noise Margin (SNM) [2], [11], [12] across different process corners in ultralow voltage operation is still challenging.

#### **1.4 Dissertation Organization**

The dissertation organization is as follows:

Chapter 1 deals with introduction portion of the thesis.

**Chapter 2** deals with review of design problems present in nanoscale bulk CMOS and introduce MGDG MOSFET as its solution. It reviews high performance low leakage circuit design in nanometer regime and leakage reduction methods of SRAM cell and their performance.

**Chapter 3** deals with work function engineered MGDG MOSFET as its solution. It also describes leakage current estimation techniques of MGDG MOSFET.

**Chapter 4** describes transition time and optimum biasing configuration and method to reduce the transition time. It also presents different types of failures present in conventional SRAM.

**Chapter 5** deals with Small signal capacitance and glitch voltage modeling and estimation of leakage currents using interconnection effect and voltage rise/fall at critical nodes of SRAM cell and its validation through **HSPICE Simulations**.

**Chapter 6** deals with ultra low voltage operation of SRAM cell designed using MGDG MOSFET. It also shows SNM variation across different process corners.

Chapter 7 gives conclusion and future scope of the work.

Chapter 2

## **Review of Design Problems in Nanometer Cache Memories**

#### 2.1 Design Problems in Nanometer Bulk CMOS Technologies

Main Problems faced by CMOS Nanometer technologies are

- Maintaining a Good on to off current ratio.

- Exponential increase in leakage current.

- Process parameter variations.

In addition to above poly-depletion causes severe transconductance degradation as shown below.

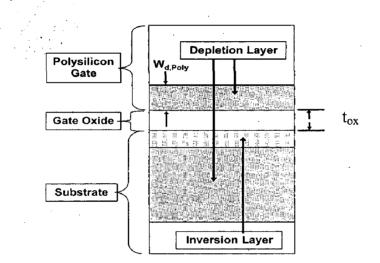

Figure 2.1 Poly-Depletion Effect [1].

Due to poly depletion effective oxide thickness will increase to [13],

$t_{ox,electric} = t_{ox} + (K_{ox}/K_{si})^* (W_{d,Poly}); \text{ where } K_{ox} = 3.9 \text{ for } SiO_2, K_{si} = 11.9$  (2.1)

From ITRS specifications Poly-doping is limited and its depletion become more critical with insulator thickness scaling, leading to severe transconductance degradation. Performance and robustness of the design decreases due to degraded transconductance. Unfortunately scalability of bulk devices is limited by process variations and severe short channel effects there by forcing the designers to search for new channel materials, unconventional devices. Double gate MOSFET is one such promising device which can extend the scaling limit to sub20nm [14]. A special class of DGMOSFET called MGDG MOSFET was reported in [15], which reduces sensitivity of leakage currents to process

parameter variations and also it eliminates poly-depletion effect. It has been proposed in [16] that midgap gates reduce performance of the design. Hence one should go for dual metal gate processes as reported in [17] for improved performance.

#### 2.2 High Performance Low Leakage Circuit Design in Nanoscale Regime

High performance low power Nanoscale circuit design requires estimation and reduction of standby leakage power [4]-[6], [18]-[19]. A. Agrawal et. al [4] has reported leakage estimation procedure but it is limited to bulk MOSFET's. Circuit level technique of 'stacking' has been proposed in [18] as a way to reduce leakage currents and estimation of leakage currents in stacking has been reported in [20]-[21]. Stack effect is more effective in scaled devices due to increased stack factor and if MGDGMOSFET is used then due to reduced short channel effects there is not much benefit of stacking, also reduced driving capability limits the benefits of stacking in Double gate devices [15]. So, only option left for either improving performance in critical paths or reducing leakage in noncritical paths is backgate biasing. Backgate biasing fails if the channel is left almost intrinsic [22]. In case of DG devices one can finely tune threshold voltage with back gate biasing [23], [24] to achieve required leakage reduction as well as improved performance. Timing analysis of problems caused by backgate bias is required for estimating timing requirements of design. For MGDG MOSFET's timing analysis reported in [25] is not applicable since it does not give estimation of semiconductor film capacitance. A method of estimating semiconductor capacitance has been reported in [26]. Also, small signal capacitances present in the device causes voltage rise/fall in output levels and causes reliability problems [8], [27]. Moldovan et. al [28] have obtained small signal capacitances of intrinsic channel double gate device from explicit expression for mobile charge sheet density/unit area but, they have not given measure of glitch voltage present at the output of the circuit due to small signal capacitances. Modeling and analysis of various failure mechanisms present in the circuit is essential for finding reliability of the total system [8] [29]. Failure probability estimation in [8] does not include effect of leakage currents determined using interconnection effects and glitch voltage at the data storing nodes of the cell. Reduction of leakage currents and operation at subthreshold regime based on application demands [30]-[34] helps to reduce most of leakage currents to minimum. SRAM's uses minimum geometry transistors and they can be better used for characterizing the performance of nanoscale devices.

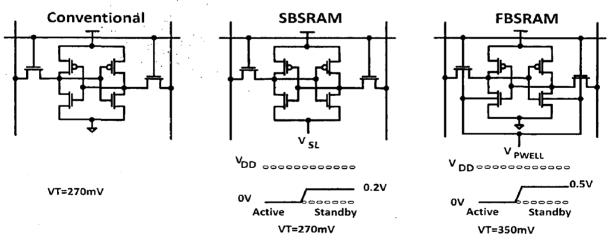

## 2.3 Conventional Leakage Reduction Methods of SRAM and Their Performance

The selection of leakage reduction scheme is governed by percentage leakage reduction and delay overhead caused by the scheme [25] as shown in figure 2.2. Study of effect on the read/write delay by each low leakage technique is required to estimate the circuit performance. The popular Device/Circuit co-designing schemes of low power SRAM cell are given in **Table 2.1**. Here sub: double down arrow indicates large reduction of subthreshold leakage If only one arrow is there only marginal reduction is available. Similarly Gate: double down arrow indicates large reduction of gate leakage and the same applies for BTBT.

| Scheme              | Source<br>Biasing | Fwd/Reverse<br>Biasing BG | Dynamic V <sub>dd</sub> | Floating BL          | Negative<br>WL                   |

|---------------------|-------------------|---------------------------|-------------------------|----------------------|----------------------------------|

| Leakage             | Sub: ↓↓           | Sub: ↓↓                   | Sub, gate: ↓            | Sub:↓                | Sub:↓                            |

| reduction           | Gate: ↓↓          | BTBT:†(RBB)               | Bitline leakage         | Gate: ↓              | Gate: ↑                          |

| Delay               | Increases         | No Increase               | No Increase             | No Increase          | No Increase                      |

| Transition overhead | Low               | Large                     | Large                   | Precharge<br>latency | Low charge<br>pump<br>efficiency |

Table 2.1 Selection of Co-design Scheme

Figure 2.2 Biasing Schemes of SRAM Cell

Most commonly used methods of reducing leakage power are,

#### A. Self-Reverse Bias

Self reverse biasing schemes raise the source voltage of MOSFET thereby increase threshold voltage. The effect of transistor stacking on circuit topology was first proposed for subthreshold Current. In transistors connected serially, gate-to-source voltage is

more negative, when the transistor is top of the stack. Threshold voltage of the transistors at top of the stack is increased because of body effect. Hence, "OFF" transistors at stack have lower subthreshold current than individual transistors. Stacking has secondary effect of Drain induced barrier lowering (DIBL) and slight increase of  $V_{th}$ .

#### **B.** Back Gate Biasing for Leakage Reduction

Back gate biasing schemes focus on varying backgate bias for tuning front channel threshold voltage. All the leakage currents from both front and back gate have been calculated in above section. Leakage currents can be reduced by negative backgate bias and performance can be improved by positive backgate bias. This scheme introduces transition time as well as energy overhead and complicates row decoder design.

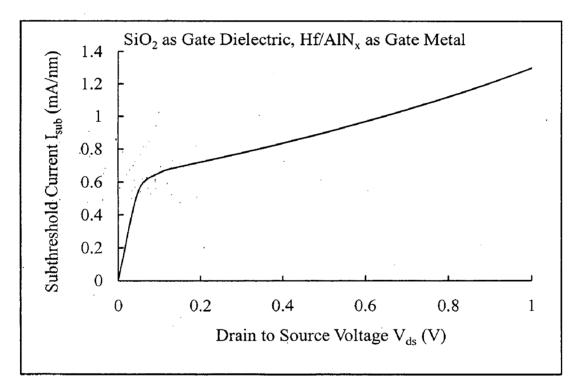

Figure 2.3 Wake up of Subarray in backgate biased SRAM [3]

#### 2.4 Reliability Issues of an SRAM Cell

**Read Failure:** Flipping of cell state due to increase in the '0' storage node above the trip voltage of the other inverter during a read operation is regarded as read failure.

Write Failure: '1' Storage node may not be reduced below the trip point of the other inverter before WL is discharged.

Access Time Violation: The cell access time ( $T_{ACCESS}$ ) is defined as the time required to produce a prespecified voltage difference ( $\Delta_{MIN} \approx 0.1 V_{DD}$ ) between two bit-lines. If due to  $V_{th}$  variation, the access time of the cell is longer than the maximum tolerable limit ( $T_{MAX}$ ), an access time failure is said to have occurred [8]. Access failure is caused by the reduction in the strength of the access and the pull-down transistors. Thus, access failure limits the reduction in the size of the access transistor (required to reduce  $V_{READ}$ ). An increase in the  $V_{th}$  of the access transistor and the pull-down NMOS (caused by the process variation) can significantly increase the access time from its nominal value thereby resulting in an access failure. Thus, both intra-die and inter-die variation in process parameters increase the access failure.

**Hold Failure:** In the stand-by mode, the  $V_{dd}$  of the cell is reduced to reduce the leakage power consumption. As the supply voltage of the cell is lowered, the voltage at the node storing "1" also gets reduced. Moreover, for a low supply voltage leakage of the pull-down NMOS reduces the voltage at its drain node below the supply voltage applied to the cell. If it falls below the trip-point of opposite inverter, then flipping occurs and the data is lost in the hold mode. The supply voltage to be applied in the hold mode is chosen to ensure the holding of the data under nominal condition. However, variation in the process parameter can result in the device mismatch causing hold failures.

# Leakage Current Estimation of MGDG MOSFET

#### 3.1 Proposed Gate Workfunction Engineered MGDG MOSFET

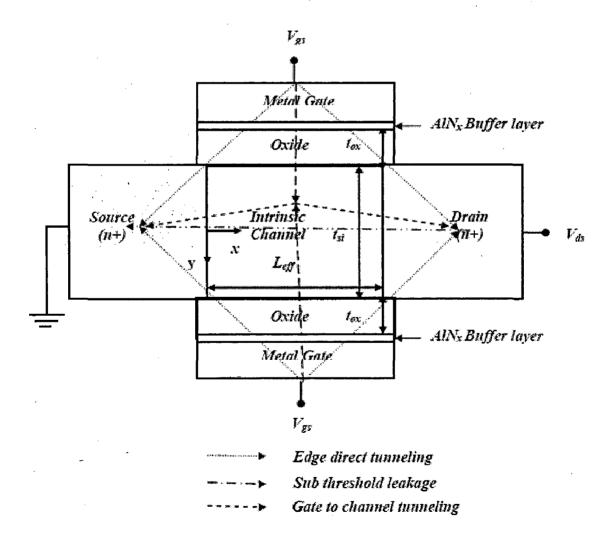

Poly-depletion effect can be eliminated with use of metal gates. Midgap metal gates are easier from fabrication perspective but reduces the performance [16] hence dual metal gates are required for improved performance. An integrable Dual Metal Gate CMOS process using an ultra thin Aluminum Nitride ( $AlN_x$ ) buffer layer in [17] can be used with Haffinium (Hf) as gate metal to achieve dual workfunctions for PMOS and NMOS thereby improving performance in our proposed gate work function engineered MGDG MOSFET.

components.

Using Hf/AlNx we achieve 4.4eV work function, which is ideal for MGDG-NMOSFET and use different metal with workfunction of 4.9eV which gives optimum threshold voltage for MGDG-PMOSFET so that performance of digital designs will be improved. The cross-sectional diagram of the Gate work function engineered Metal Gate Double Gate (MGDG) MOSFET with the associated leakage current components is shown in Figure 3.1.

Advantages of proposed device are,

- Metal gate Eliminates poly depletion effect and eliminates threshold voltage fluctuations.

- Subthreshold current reduces due to less DIBL of 19mV/V and reduced short channel effects.

- Absence of bulk charge and hence negligible surface electric field causes lesser gate to channel leakage.

- Intrinsic body doping eliminates random dopant fluctuation and electric field at the edges as well as interface hence Edge Direct Tunneling Current reduces.

- Stacking effect of series connected transistors in SRAM cell architecture is minimum due to lower short channel effect.

#### 3.2 Modeling of Leakage Currents in MGDG MOSFET

The cross-sectional diagram of the Metal Gate Double Gate (MGDG) MOSFET with the associated leakage current components is shown in **figure 3.1**. Leakage current estimation requires estimation of electron energies available for tunneling and calculation of electric field in the oxide region ( $E_{\alpha x}$ ). In DG devices using ultra thin silicon body electron energies are quantized into different subbands due to structure as well as field present in the body. In our analysis we have considered first two sub bands of first valley and first sub band of second valley as they will contain most of carriers [35]. Electron energy  $E_{(j,i)}$  associated with  $j^{th}$  subband of the  $i^{th}$  valley (both longitudinal and transverse) is given as [36]

$$E_{(j,i)} = \frac{j^2 (2\pi\hbar)^2}{8m_i^* t_{Si}^2} + \left[\frac{3hq\varepsilon_{ins}E_{ox}}{4\varepsilon_{Si}\sqrt{2m_i^*}} \left(j + \frac{3}{4}\right)\right]^{\frac{2}{3}}$$

(3.1)

Where q is electron charge,  $m_i^*$  is the electron effective mass in  $i^{th}$  valley ( $m_1^* = 0.916m_o$ ,  $m_2^* = 0.19m_o$ ),  $m_o$  is free space electron mass,  $\varepsilon_{ox}$  is the permittivity of the oxide layer,  $\varepsilon_{Si}$  is the permittivity of the silicon layer and  $t_{si}$  is silicon film thickness. The first term in equation (3.1) is due to structural quantization and second term is due to field quantization.

#### 3.2.1 Modeling of Threshold Voltage for MGDG MOSFET

Threshold voltage of DG device considering the Short channel effects and quantummechanical (QM) effects is given by [36]-[40]

$$V_{\iota h} = \frac{E_g}{2q} + \frac{1}{1+r} \Big[ \Phi_{Gfs} + r \Phi_{Gbs} \Big] - \left( \frac{\varepsilon_{Sl} t_{Sl} t_{os} V_{ds}}{\varepsilon_{os} \alpha L_{eff}^2} + \frac{\varepsilon_{Sl} t_{Sl} t_{os} E_g}{2\varepsilon_{os} \gamma L_{eff}^2} \right) + \frac{E_g}{2q} - \frac{kT}{q} \ln \left( \frac{Q_{lnv}^{QM} \left( E_F = 0 \right)}{n_i t_{Si}} \right)$$

(3.2)

where,  $r = 3t_{ox}/(3t_{ox} + t_{Si})$  is the sensitivity of threshold voltage to the back gate bias,  $t_{ox}$  is insulator layer thickness,  $E_g$  is silicon bandgap and  $L_{eff}$  is the effective channel length. We have neglected the bulk charge in metal gate devices with intrinsic body doping. For ultra thin channel thickness  $t_{si}$  due to volume inversion back gate bias can impact threshold voltage even after inversion so equation (3.2) is valid in all regions of operation [40]. Here,  $\Phi_{Gfs}$  and  $\Phi_{Gbs}$  are the work-function differences for the front and back gates,  $\alpha$  and  $\gamma$  are the structure and doping dependent empirical factors. From equation (3.2) the threshold voltage for Hf/AlN<sub>x</sub> is evaluated to be 0.31V.

#### 3.2.2 Modeling of Subthreshold Current

Subthreshold current is modeled as [26]

$$I_{sub} = 2\mu_o C_g \frac{W}{L_{eff}} V_r^2 \exp\left(\frac{V_{gs} - V_{th}}{mV_r}\right) \cdot \left(1 - \exp\left(\frac{-V_{ds}}{V_r}\right)\right)$$

(3.4)

where  $\mu_o$  is mobility of intrinsic silicon channel, W is the gate width and  $V_T$  is thermal voltage. The parameter m is called ideality factor which is defined as the ratio of ideal subthreshold swing to that of analytically determined value of the same. Subthreshold swing S [41] [42] has been analytically calculated to be 59.5mV/dec. We have estimated DIBL using our MGDGMOSFET to be 19mV/V.

#### 3.2.3 Effect of Channel Thickness Variation on Subthreshold Current

Threshold voltage control is limited by channel thickness control. Assuming particle in potential box model given by [43] threshold voltage variation can be modeled as,

$$\Delta V_t = -\frac{\hbar^2 \pi^2}{qm^* t_{si}^2} \frac{\Delta t_{si}}{t_{si}}$$

(3.5)

Assuming  $t_{si}$ =5nm and channel thickness control of 20% threshold voltage variation can be controlled to 28mV with the present device which is much lower than supply voltage under worst case variation there by guaranteeing high performance operation in nanoscale regime. As the silicon film thickness varies the inversion charge sheet move away from interface there by reducing gate leakage. Leakage currents can be kept to bare minimum if High-K dielectric is used in combination with metal gate.

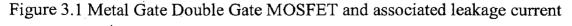

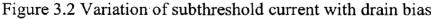

Figure 3.2 shows the variation of subthreshold current with drain bias at channel thicknesses of 5 nm for oxide thicknesses of 1 nm with  $SiO_2$  as a gate dielectric and Hf/AlN<sub>x</sub> as a gate metal. Subthreshold current increases with supply voltage due to DIBL effect.

#### 3.2.4 Gate to Channel Current

For ultra thin dielectrics it has been reported in [44] that electrons no longer enter the insulator conduction band, but tunnel directly through the insulator. In state-of-the-art CMOS technologies, direct tunneling is the dominant current conduction mechanism at operating voltage for insulator thickness less than 3 nm. The different physical mechanisms for gate leakage are: conduction band electron tunneling (CBET), valence band electron tunneling (VBET), and valence band hole tunneling (VBHT). In DG devices due to strong quantum confinement, tunneling occurs from quasi-bound states (QBS) and at the interface electron eigen function is no longer nonzero in the metal gate region. Gate to channel leakage is primarily due to tunneling of electrons from inverted surface channel to gate (CBET) [23] and can be modeled as [45],

$$I_{gc} = WL_{eff} \sum_{j} \sum_{i} Q_{(j,i)} f_{(j,i)} T_{(j,i)}$$

(3.5)

where  $Q_{(j,i)}$  is the inversion charge associated with  $(j,i)^{th}$  state ,  $f_{(j,i)}$  is the impact frequency of electron,  $T_{(j,i)}$  is the transmission probability from the  $(j,i)^{th}$  state estimated using [36]. Inversion charge associated with  $(j, i)^{th}$  state  $Q_{(j,i)}$  is estimated as in [46]-[47].

Figure 3.3 Variation of gate to channel current with gate bias.

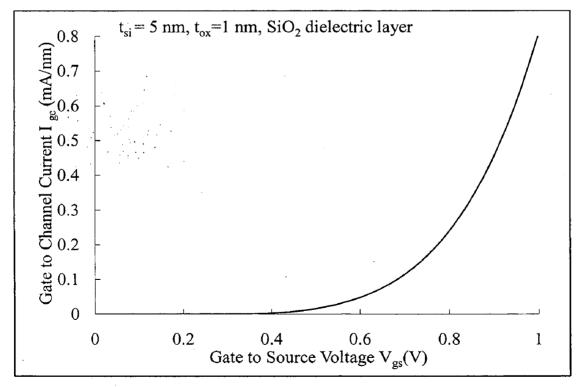

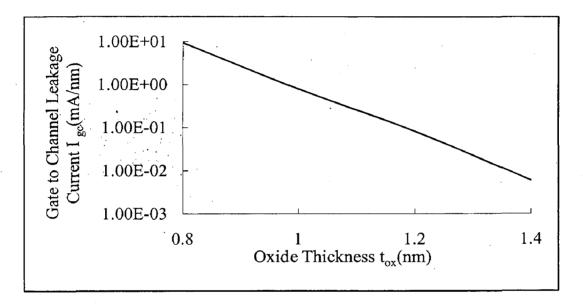

Figure 3.3 shows the variation of gate to channel current with gate to source voltage at channel thickness of 5 nm and for oxide thicknesses of 1 nm with  $SiO_2$  as gate dielectric and Hf/AlN<sub>x</sub> as gate metal. As gate voltage increases due to increased tunneling probability as well as inversion charge gate to channel current increases. Figure 3.4 shows variation of gate to channel current with oxide thickness. Clearly it can be seen that leakage current variation is with in 100times its original value with in standard variation of oxide thickness from ITRS specifications. Variation is less basically due to logarithmic movement of inversion layer into silicon volume due to reduced oxide thickness.

Figure 3.4 Variation of gate to channel current oxide thickness.

#### 3.2.5 Edge Direct Tunneling Current (EDT)

Tunneling through source/drain extension region and gate occurs both in 'on' and 'off' state. In the 'on' state electron tunnels from S/D region to gate, while in 'off' state tunneling of electron occurs in opposite direction. Electric field in the oxide region  $E_{ox}$  across the 1-D gate-dielectric-drain extension structure depends on the voltage drop across drain extension ( $V_{DE}$ ) given by [48],

$$V_{DE} + E_{ox}t_{ox} - (V_{DG} - V_{fb}) = 0$$

(3.6)

where  $V_{DG}$  is drain gate voltage. The voltage drop across drain extension region can be evaluated as in [16].  $V_{DE}$  can be obtained from [15]. Substituting this  $E_{ox}$  in transmission probability equation given in [45] and it can be used in evaluating EDT in 'on' state (which is basically CBET) from equation (3.5). In "off" state of MGDG structure, electrons from the free states below the fermi level in metal constitute EDT. 'Off' state EDT density can be expressed as in [49],

$$J_{EDT} = \frac{4\pi q m^* kT}{h^3} \times \int_{E_{\text{num}}}^{E_{\text{num}}} T(E) \ln \left[ \frac{1 + \exp\{q(\Phi_D - V_{GD} - E_{av})/kT\}}{1 + \exp\{q(\Phi_D - E_{av})/kT\}} \right]$$

(3.7)

$$E_{\max} = \phi_m; E_{\min} = E_C (n^+ drain); E_{av} = (E_{\max} + E_{\min})/2$$

(3.8)

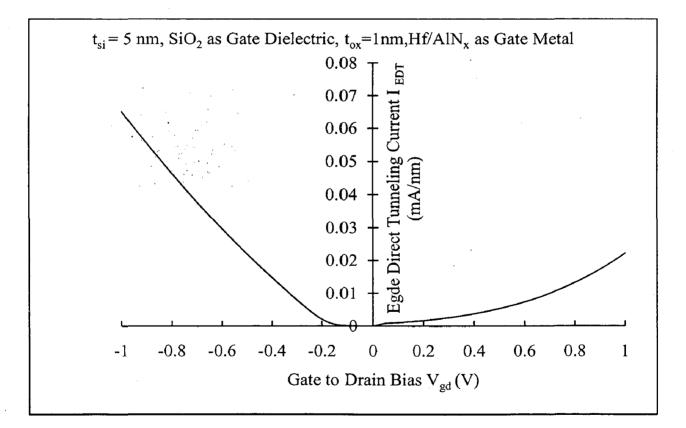

Where transmission probability is evaluated at average energy  $E_{av}$  and  $\phi_m$  is gate work function. The function in integral determines 'off' state EDT density. Figure 3.5 compares variation of edge direct tunneling current with gate to drain bias. In off state due to more window available for tunneling from metal to free states we observe more leakage current than in 'on' state where EDT is primarily due to conduction band electron tunneling.

Figure 3.5 Variation of edge direct tunneling current with gate to drain bias.

#### 3.2.6 Band-to-Band Tunneling Current (BTBT)

Band-to-band tunneling across reverse biased p-n junction occurs from p-side valence band to n-side conduction band, becomes increasingly important with continued device scaling into nanometer regime and increasing electric fields in the channel. At positive drain bias and/or, negative bias, potential across drain-to-body region can exceed the band-gap voltage, especially at the interface causing BTBT between drain and body.  $I_{BTBT}$  is a function of the local electron-hole pair generation rate, given by [50]

$$G_{BTBT} = \frac{q^2 m^{0.5} E^2}{18\pi \hbar^2 E_g^{0.5}} \times \exp\left(-\frac{\pi m^{0.5} E_g^{1.5}}{2\hbar q E}\right)$$

(3.9)

Where *E* is local electric field and  $E_g$  is the energy band gap. The units of  $G_{BTBT}$  are electron-hole pairs/cm<sup>3</sup>-s. Local electric filed is estimated using modeling scheme in [51]. Figure 3.6 shows the variation of band to band tunneling current with gate to source voltage for Hf/AlN<sub>x</sub> as gate metal with silicon thickness of 5 nm and for oxide thickness of 1 nm using SiO<sub>2</sub> as a gate dielectric on the log scale. For negative gate biases drain body junction becomes more reverse biased and hence BTBT current increases.

#### 3.3 Stack Effect Analysis of MGDG MOSFET

Figure 3.7 Stacked DG-NMOS transistors with  $V_{gs} = 0.(a)$  One NMOS, (b) two stacked NMOS transistors, and (c) three stacked NMOS.

Reducing DIBL is crucial for low power applications. In our MGDG MOSFET case DIBL is 19mV/V so leakage current is less and effect of stacking is not much significant. Stack effect analysis for our MGDG MOSFET is presented in Appendix A Stack effect for leakage reduction is more useful only when short channel effects are more prominent and stacking is not much beneficial in MGDG MOSFET and reduces performance.

Figure 3.9 Delay increase observed usign Hspice with increasing number of inputs.

It is observed from figure that self reverse bias failed for MGDGMOSFET. Only backgate biasing is efficient scheme to reduce leakages as well as to improve performance in nanoscale circuits/Memories designed using DGMOSFET.

#### 3.4 Effect of Back Gate Bias on Leakage Currents

Effect of back gate bias on front channel electrical properties is modeled through variation in front channel threshold voltage  $V_{thf}$  [44], [45], [46] as given by,

$$V_{thf} = V_{thfo} - \left(rV_{gbx}\right)$$

$$V_{gbx} = \begin{cases} V_{gb} & V_{gb} < V_{thb}; \\ V_{thb} & V_{gb} > V_{thb}; \end{cases}$$

(3.10)

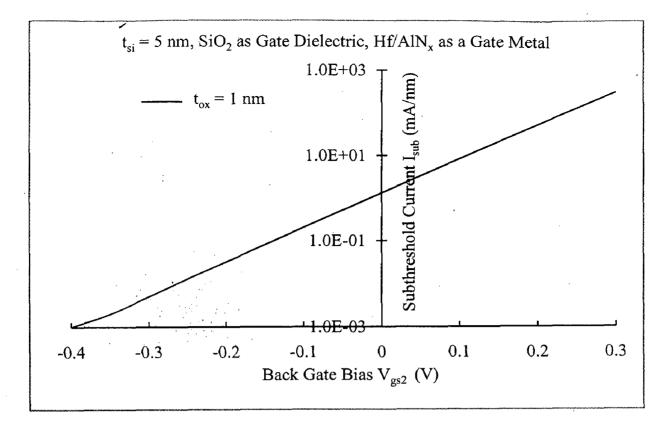

where  $V_{th/b}$  the front gate threshold voltage at zero gate bias,  $V_{th/b}$  is the back gate threshold voltage and  $V_{gb}$  is back gate bias. All the leakage currents from both front and back gate have been calculated with the incorporation of equation (3.10) and it has been found that at a backgate bias of -0.4V all the leakage currents are minimum and at backgate bias of 0.3V performance of MGDG will be improved due to reduced threshold voltage. Subthreshold current variation with the incorporation of backgate bias is as shown in figure 3.10. Figure 3.10 shows the variation of subthreshold current with back gate bias ( $V_{gs2}$ ) using Hf/AlN<sub>x</sub> as gate metal, at channel thickness of 5 nm and oxide thickness of 1 nm with SiO<sub>2</sub> as gate dielectric on log scale. It can be observed that when back gate is in depletion condition ( $V_{gb} < V_{thb}$ ) subthreshold currents starts to decrease with decreasing back gate voltage due to reduced level of inversion at the front interface.

Figure 3.10 Variation of subthreshold current with Back Gate Bias.

Beyond certain negative back gate bias gate-gate coupling effect will be eliminated. In our modeling scheme we are restricting  $V_{gs2}$  to - 0.4V in negative direction by considering power dissipation characteristics. There is no exact value of V<sub>gs2</sub> in negative direction reported in literature beyond which threshold voltage is insensitive to it, since for ultrathin films the possibility of accumulating the back interface is very less and according to Zhang and Roy [44], [45] front gate threshold voltage depends on back gate bias as long as back gate is depleted, where as in positive direction it is limited by the threshold voltage of back gate. Here only BTBT current increases slightly with negative back gate bias except that all leakage currents shows increasing trend with increasing back gate bias from -0.4V to 0.4V similar to that in figure 3.10. Thus for transistors in off state leakage can be reduced to a larger extent by applying suitable negative bias (about -0.4V) to the back gate of these transistors during store '0' operation. The main leakage currents in on state N-transistor are 'on' state EDT and gate to channel leakage. As EDT is much small compared to Gate to Channel current  $(I_{gc})$  our main objective is to reduce  $I_{gc}$ . At a back gate bias of 0.3V threshold voltage of the device gets reduced, so we will observe improved performance for transistors in 'on' state with a back gate bias of 0.3V at the cost of increased leakage by approximately three times.

# Leakages and Nanometer Cache Design Using MGDG MOSFET

#### 4.1 Leakage Currents Present in MGDG SRAM

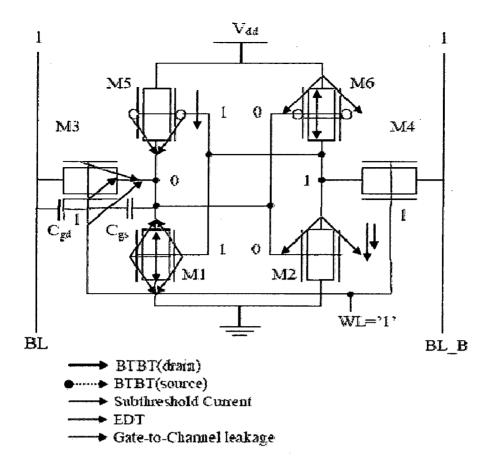

Leakage currents present in typical SRAM cell designed using MGDG MOSFET during idle mode are shown in Figure 4.1.

Figure 4.1 Leakage components in MGDG SRAM cell during idle mode.

Where BL is bitline, BL\_B is complementary bitline and WL indicates wordline activation for accessing the cell. In idle mode when the wordline is not asserted we observe subthereshold leakage in access FET on '0' side and driver FET on '1' side. Mostly we observe gate leakage at all other nodes since terminals are at different potentials. It is clearly observed that when the nodes are at different potentials we observe either Gate-to-Channel current or EDT. If gate potential is zero based on drain source potential Subthreshold Current flows.

#### 4.2 Proposed Backgate Biasing Scheme using MGDG MOSFET

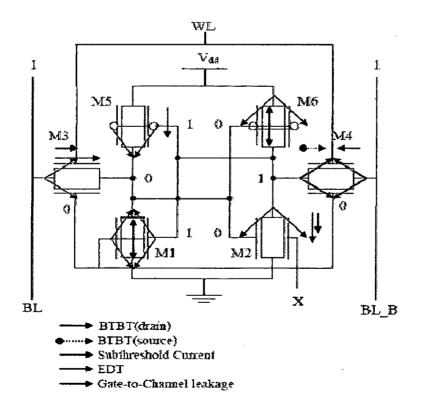

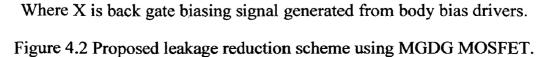

Dual threshold voltage schemes utilize the timing slack of noncritical paths to reduce leakage power by using high threshold voltage devices in noncritical path and low threshold voltage devices in critical path. Making tradeoff between leakage power and performance leads to a significant reduction in the leakage power while sacrificing only some or none of circuit performance. Such a tradeoff is made in Dual Threshold designs [6]. In our design we typically use forward biased back gate devices in critical path during active operation to improve performance and we switch to negative back gate bias during standby mode to reduce leakage. From Chapter 3 it has been found that at a back gate bias of -0.4V all the leakage currents are minimum and at backgate bias of 0.3V performance of MGDG will be improved due to reduced threshold voltage. So, except BTBT current all leakage currents will increase monotonically with increasing back gate voltage from -0.4V to 0.3V.Back gate biasing introduces transition time as well as energy overhead. Each subarray has Subarray select signal (SUBSL) which is generated by row decoder. X line is body biasing signal for subarray and can be routed using an upper layer metal.

In SRAM NMOS access transistor and pull down transistor are critical for read, write operations. So, they are fed with forward bias of 0.3V in 'on' state to get improved performance and with -0.4V back gate bias in 'off' state for reduced leakage. Schematic of the proposed latency minimized cache subarray is shown in figure 4.2.

#### 4.3 Estimation of Semiconductor Capacitance and transition time

But transition time and energy overhead is introduced by back gate bias which in turn depends on parasitic body capacitances and semiconductor capacitance.

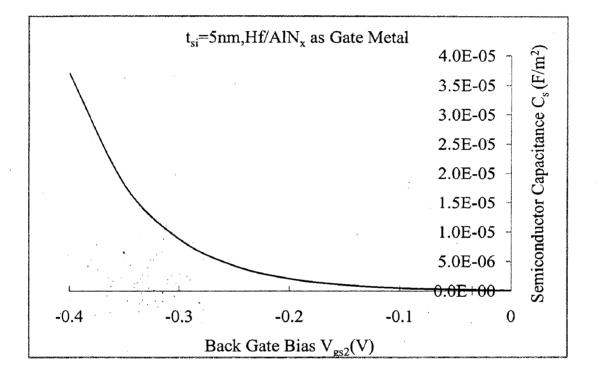

Figure 4.3 Semiconductor capacitance variation with back gate bias

Figure 4.3 shows the semiconductor film capacitance variation with back gate bias from - 0.4V to 0V with unbiased front gate. Assuming film resistance of .1 $\Omega$ -m and with given device dimensions and FBB=0.3V and RBB= -0.4V latency time can be calculated to be 0.69RC=1.021ps. It is clearly observed that transition overhead is very less and facilitating easier design of decoder circuitry without compromising much on performance with application of leakage reduction technique. With this configuration back gate selection signal need not be generated since back gate activation time is very less with present configuration using MGDG MOSFET.

Since MGDG uses fully depleted silicon film, substrate parasitic capacitances are eliminated. Drain to gate capacitance is less in Double gate devices due to increased control of gate on channel. In body biased cache subarray architectures each subarray has a subarray select signal (SUBSL) which is generated by the row decoder circuit [9]. SUBSL selects the subarray ahead of time which is needed for transition from forward back gate bias (FBB) to reverse back gate bias (RBB). The 0.3V FBB and -0.4V for RBB can be generated by a high-efficiency DC–DC switched capacitor converter. For facilitating easier design of switched capacitor converter one can prefer -0.3V and 0.3V as RBB and FBB respectively. Switching between FBB and RBB requires additional transition delay and energy overhead. Four NMOS MGDG's in each SRAM cell yield four gate-body capacitances to charge and discharge in every body transition event. This introduces transition latency and energy overhead. But, the transition overhead is minimum in MGDG devices due to the use of intrinsic body and reduced parasitic substrate capacitance. Parameter variations causes congestion of design margins [10]. MGDG MOSFET is less sensitive to parameter variations and parameter variations reduce considerably if negative backgate bias is applied hence SRAM cell designed by it is more robust.

Chapter 5

## **Small Signal Capacitance and Glitch Voltage Estimation**

#### 5.1 Causes of Potential Rise at Output

In circuits operating at nanoscale regime potential rise at output node during signal transitioning events creates timing, noise and glitch related problems. Glitches at output are result of gate-drain capacitance of MOSFET. So, to perform early power and timing estimates, one needs an efficient method to estimate the small signal capacitances of the selected device structure. Leakage currents also determines the potential rise or fall at critical nodes, so leakage current estimation using interconnection effect and solution of nodal current equations at different nodes of circuit gives better insight into the robustness of the circuit. We have obtained independent small signal capacitances and used them in the glitch voltage estimation of circuits designed with the proposed device. A very good agreement is reached between the DESSIS-ISE Simulations presented in [28] and our analytical modeling. We have evaluated potential rise at output node during signal transitioning events for inverter designed with our MGDG MOSFET both analytically and through **HSPICE Simulations**. Due to reduced gate-drain capacitance the steady state charge injected into the body is less and hence noise power will be reduced.

We did leakage current estimation of SRAM cell using interconnection effect and estimated the potential rise/fall at the '0' and '1' storing nodes. Further the read/write failure probability is reduced since during word line assertion less potential rise is observed due to the reduced gate-drain capacitance.

#### 5.2 Modeling of Small Signal Capacitances of MGDG MOSFET

Explicit charge based expressions are required for evaluating gate-drain capacitances. We have considered explicit charge based expression for mobile charge sheet density/unit area [28],

$$Q = 2C_{ox} \left( -\frac{2C_{ox}V_{T}^{2}}{Q_{o}} + \sqrt{\left(\frac{2C_{ox}V_{T}^{2}}{Q_{o}}\right)^{2} + 4V_{T}^{2}\log^{2}\left[1 + \exp\left(\frac{V_{gs} - V_{th} - V}{2V_{T}}\right)\right]} + \frac{E_{11}}{q} \right)$$

(5.1)

where  $C_{ax}$  is the oxide capacitance/unit area, q is electron charge,  $V_T = kT/q$  is thermal voltage,  $Q_o = 4V_TC_{si}$ ,  $V_{gs}$  is gate bias,  $V_{th}$  is threshold voltage modeling as in section A, V is electron quasi-Fermi potential which depends on  $V_{ds}$  and  $E_{11}$  is the energy of first subband of first valley in which most of the carriers are populated and it models the quantum correction for mobile charge density both due to structural and field quantization. The terminal charges and associated capacitances are essential for AC and transient analysis of MGDG MOSFET. In above the source and drain charge densities can be obtained by substituting 0 and  $V_{ds}$  respectively in equation (5.1) in place of electron quasi-Fermi potential. The drain and source charges at non zero  $V_{ds}$  can be obtained from [28]. Charge conservation requires that all the capacitances be computed in terms of terminal charges given by,

$$C_{ij} = \frac{\partial Q_i}{\partial V_j} \tag{5.2}$$

Where i and j are terminals of MGDG-MOSFET.  $C_{gd}$  can be evaluated from equation (5.1) and (5.2) since it is of most interest in circuit applications and it is the independent capacitance from which others can be evaluated. The expression for  $C_{gd}$  is given by,

$$\frac{C_{gd}}{2WLC_{ox}} = \frac{2V_T \log \left[1 + \exp\left(\frac{V_{gs} - V_{th} - V}{2V_T}\right)\right] * \exp\left(\frac{V_{gs} - V_{th} - V}{2V_T}\right)}{\sqrt{\left(\frac{2C_{ox}V_T^2}{Q_o}\right)^2 + 4V_T^2 \log^2\left[1 + \exp\left(\frac{V_{gs} - V_{th} - V}{2V_T}\right)\right] * \left[1 + \exp\left(\frac{V_{gs} - V_{th} - V}{2V_T}\right)\right]}}$$

(5.3)

while plotting the graphs we normalize all the capacitances with the factor  $2WLC_{ox}$

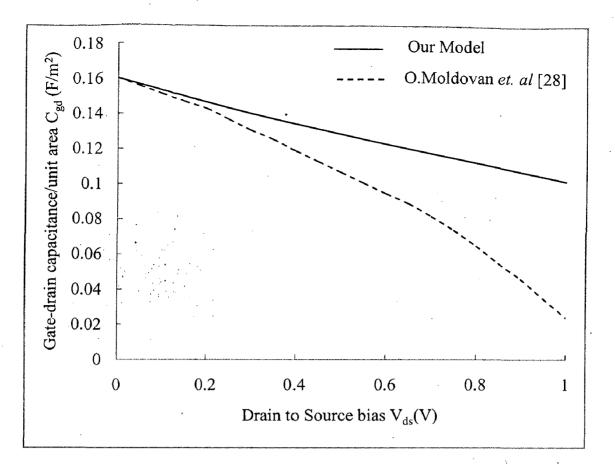

Figure 5.1 compares the variation of normalized gate-to-drain capacitance with drain to source voltage for our case of MGDG-MOSFET and that of DESSIS simulations from [28] with L=1um, W=1um,  $t_{ins}$ =2nm,  $t_{si}$ =20nm. As can be observed from the figure both results agree at very low values of drain to source voltage but as drain to source voltage increases we observe a very small decrement of gate-to drain capacitance in our case due to more rigid gate control of channel in our case and also we will observe performance improvement.

Figure 5.1 Gate-Drain capacitance variation with drain potential from analytical modeling of MGDG –MOSFET vs DESIS-ISE simulation from [28].

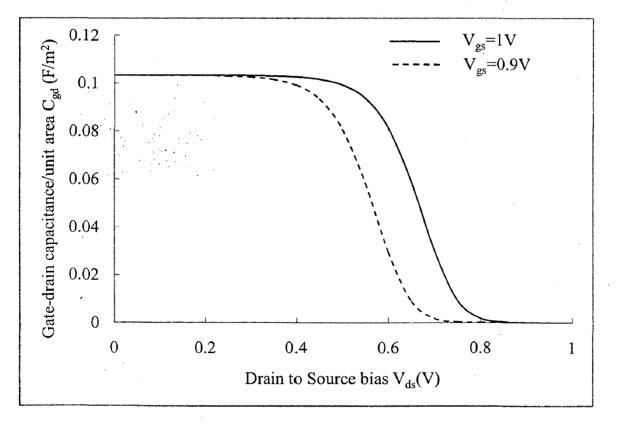

Figure 5.2 shows the variation of normalized gate to drain capacitance with drain to source voltage for two values of gate voltages 1V and 0.9V using  $L_{eff}=20nm$ ,  $t_{ox}=1nm$ ,  $t_{si}=5nm$ , W=30nm with Hf/AlN<sub>x</sub> as gate metal. As can be observed from the figure at lower values of gate potentials the fall in gate drain capacitance is more drastic due to reduced inversion charge. The normalized gate to drain capacitance at V<sub>ds</sub>=0V for conventional bulk MOSFET with same device parameters as MGDG MOSFET is found to be 0.61, which shows the superiority of MGDG MOSFET during signal transitioning events and improves reliability of Memory circuits designed with it. Gate to drain capacitance, gate to source capacitance and drain to gate capacitance shows the same variation with respect to gate voltage for V<sub>ds</sub>=0V. For non zero V<sub>ds</sub> they show little deviation as shown in [28].

Figure 5.3 Normalized Gate-Drain capacitance variation with gate potential from analytical modeling of MGDG -MOSFET.

Figure 5.3 shows the variation of normalized gate to drain capacitance with gate to source voltage for two values of gate voltages 1V and 0.9V using  $L_{eff}$ =20nm,  $t_{ox}$ =1nm,  $t_{si}$ =5nm, W=30nm with Hf/AlN<sub>x</sub> as gate metal. After inversion charge build up gate to drain capacitance increases with gate voltage and attains saturation after threshold condition is reached. Increased drain voltage delays the attainment of saturation point since it delays inversion charge build up.

Figure 5.4 Gate-Source capacitance variation with drain potential from analytical modeling of MGDG –MOSFET

Figure 5.4 shows the variation of normalized gate to source capacitance with drain to source voltage for two values of gate voltages 1V and 0.9V using  $L_{eff}$ =20nm,  $t_{ox}$ =1nm,  $t_{si}$ =5nm, W=30nm with Hf/AlN<sub>x</sub> as gate material. Symmetry can be observed in both C<sub>gs</sub> and C<sub>gd</sub> since both of them attains same values at V<sub>ds</sub>=0V and after that the deviation starts due to partitioning of inversion charge into source and drain regions. From the figure it can be observed that as drain to source voltage increases gate to source capacitance increases due to slight increase of inversion charge and the variation follows that of given in [28] but with reduced normalized values since we are operating with lesser supply voltages. With reduced gate potentials it follows the same variation since inversion charge is increasing in contrast to decrease in case of gate-drain capacitance.

### 5.3 Estimation of Voltage Rise during Signal Transitioning Events

Typical configuration in most of the digital devices is Pullup network consisting of PMOS and Pull down network consisting of NMOS. Since the structure is symmetrical potential rise or fall during any particular transition is same [27]. Typically we can model the structure to be as in Figure 5.5.

Figure 5.5 Glitch Model of General CMOS Logic Circuits.

Applying charge conservation at output node during 0 🔺 transition at input node,

$$V_{dd}C_{gd} + V_{dd}C_{out} = V_{x}C_{out} + (V_{x} - V_{dd})C_{gd}$$

(5.4)

where  $V_x$  is the potential at output during the transition at the input,  $C_{out}$  is the capacitance at the output node,  $V_{dd}$  is the supply voltage 1V in our case and  $C_{gd}$  is the gate-drain capacitance of DG MOSFET under consideration.

By solving above equation (5.4) we obtain,

$$V_{x} = \frac{V_{dd} \left( C_{out} + 2C_{gd} \right)}{\left( C_{out} + C_{gd} \right)}$$

(5.5)

A maximum of 0.7 mV potential rise is observed using fanout=10 in an inverter circuit designed with MGDG MOSFET's. In DG based SRAM's a maximum of 7mV rise is observed which will not affect the failure probabilities much. Drain to gate capacitance is less in Double gate devices due to increased control of gate on channel. The reduced gate-drain capacitance produces less glitch currents during switching the access transistors from off state to on state in SRAM cell and this reduces the problem of false triggering in feedback inverter and improves the read and writes margins there by facilitating more design margin for circuit designers.

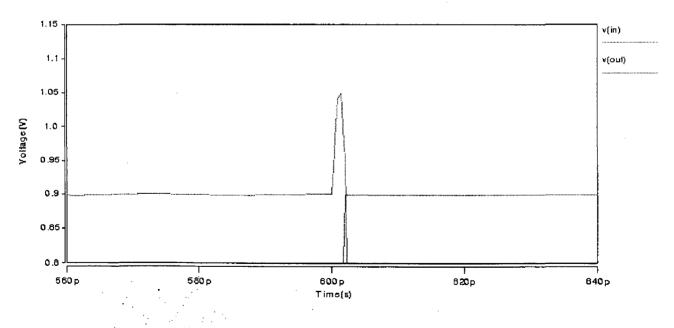

Figure 5.6 shows the transient simulation of voltage transfer characteristics of inverter using BSIM SOI model cards for both front and backgates. V(nd) is output of the inverter and V(vg1) is common gate input of inverter designed using MGDG MOSFET. A delay of 0.8ps is observed for MGDG inverter and the voltage rise observed at the output validates with that of theoretical simulations as shown in Figure 5.7.

Figure 5.7 Validation of Potential fall using our model and HSPICE simulations.

Figure 5.7 Validation of Potential fall using our model and HSPICE simulations. The reduced gate to drain capacitance produces less glitch currents while switching the

access transistors from off state to on state, this reduces the problem of false triggering in feedback inverter used in SRAM design and improves the read noise margin.

Figure 5.8 Inverter Transient simulation of Bulk CMOS inverter using HSPICE

Figure 5.8 shows the transient simulation of inverter designed using bulk MOSFET with similar transistor sizes at 32nm node using BPTM model cards. A delay of 2.1ps is observed showing the inferior performance of double gate structures which are for extending the scaling. But in subthreshold regime DG MOSFET performs well due to its near ideal subthreshold slope.

Figure 5.9 Magnified view of Potential rise using HSPICE simulations of bulk MOSFET.

Figure 5.9 shows the magnified view of the glitch at output of inverter and its value is found to be 0.15V which leads to power, timing and noise related problems and forces increased design margins. This clearly shows the superiority of MGDG devices in terms of glitches at the output.

## 5.4 Failure Probabilities and their Dependency on Leakage Currents

In addition to capacitance between input and output leakage currents in logic/memory circuits causes severe reliability problems especially with low voltage operation in nanometer regime. We found combined potential rise at critical nodes in memory both due to the small signal capacitances and due to leakage currents. Critical nodes are nodes whose potential variation is crucial for that particular read/write operation. Presence of leakage currents as well as on state currents makes voltage at '0' node to be raised to some non-zero voltage and voltage at '1' node to be lower than  $V_{dd}$ . This change in node voltages not only affect the drain to source voltages but also modify the node voltages of the p and n type MOSFETS and thereby influencing the leakage currents. In writing the KCL equations at nodes we have considered that subthreshold current flows in the same path of its origin, where as gate leakage current flows in the neighboring paths.

Applying KCL at the two nodes during read mode in figure 5.10 we get,

For '0' node

$I_{edton_3} + I_{gcs_3} + I_{sub_5} + I_{edtoff_5} + I_{edton_1} + 0.4I_{gcd_1} + I_{edton_6} + I_{edtoff_2} + I_{ds_3} - I_{ds_1} = 0$ (5.6) For '1' node

$$I_{ds_{6}+} I_{gcd_{6}-} I_{btbtd_{2}-} I_{sub_{2}-} I_{edtoff_{2}} = 0$$

(5.7)

In above equations the suffix 'ds' denotes drain current, 'edtoff' denotes offstate EDT current, 'edton' denotes onstate EDT current, 'sub' denotes subthreshold current, 'gcd' denotes gate to channel current and its drain component, 'btbtd' denotes drain to body band to band tunneling current and the symbol after underscore denotes transistor number.

Figure 5.10 Leakage components in nanoscale DG SRAM cell during read operation.

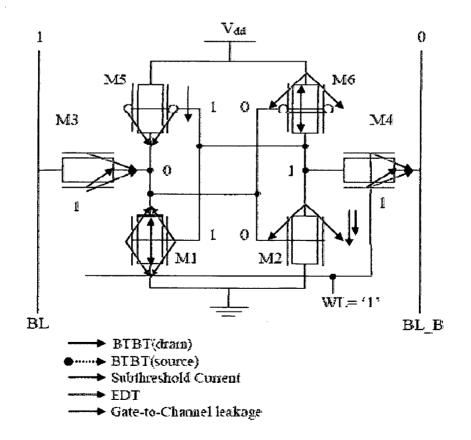

Figure 5.11 Leakage components in nanoscale DG SRAM cell during write operation.

The actual drain current expression is taken from [52], and we included quantum correction effects. We solve (5.6) and (5.7) self consistently in MATLAB simultaneous equation solver by giving some initial guess value to get the potential rise/fall at '0' and '1' nodes and accordingly leakage currents will also get modified. When the cell is in idle mode the potential rise at '0' node is found to be 10mV and potential fall at '1' node is found to be 17mV. The various leakage currents in different n-MOSFETS of MGDG are shown in the **table 5.1**. The first row represents leakage currents without considering the Interconnection effects i.e. potential variation at intermediate nodes due to leakage currents, while 2<sup>nd</sup> row represents those after these effects have been taken into account.

Table 5.1 Leakage Currents estimated using our analytical modeling for NMOS

and their variation with potential fall at source.

| Leakage            | I <sub>sub</sub> (V <sub>ds</sub> =1)<br>(mA/nm) | I <sub>gc</sub> (V <sub>gs</sub> =1)<br>(mA/nm) | I <sub>edton</sub> (V <sub>gd</sub> =1)<br>(mA/nm) | I <sub>edtoff</sub> (V <sub>gd</sub> =-1)<br>(mA/nm) | I <sub>btbtd</sub><br>(V <sub>gs</sub> =-1)<br>(uA/nm) |

|--------------------|--------------------------------------------------|-------------------------------------------------|----------------------------------------------------|------------------------------------------------------|--------------------------------------------------------|

| NMOS               | 1.298                                            | 0.8074                                          | 0.022                                              | 0.065                                                | 0.8712                                                 |

| $NMOS(\Delta V_s)$ | 1.269                                            | 0.7124                                          | 0.0203                                             | 0.0632                                               | 0.762                                                  |

Actually in the above table all leakage currents are found to be reduced but some times they can increase based on their surrounding potential. Suppose if we consider transistor M4 in read mode if at all there is a decrement in potential at '1' node due to leakage currents we will observe finite subthreshold leakage which ideally should be zero.

Table 5.2 Leakage Currents estimated using our analytical modeling for PMOSand their variation with potential fall at source.

|                    |                                                  |                                                 | ·                                                  |                                    |                                                        |

|--------------------|--------------------------------------------------|-------------------------------------------------|----------------------------------------------------|------------------------------------|--------------------------------------------------------|

| Leakage            | I <sub>sub</sub> (V <sub>ds</sub> =1)<br>(uA/nm) | I <sub>gc</sub> (V <sub>gs</sub> =1)<br>(nA/nm) | I <sub>edton</sub> (V <sub>gd</sub> =1)<br>(nA/nm) | $I_{edtoff}(V_{gd}=-1)$<br>(nA/nm) | I <sub>btbtd</sub><br>(V <sub>gs</sub> =-1)<br>(nA/nm) |

| PMOS               | 0.7812                                           | 0.0939                                          | 7.98e-2                                            | 2.63e-2                            | 0.0397                                                 |

| $PMOS(\Delta V_s)$ | 0.7734                                           | 0.0912                                          | 7.734e-2                                           | 2.31e-2                            | 0.0342                                                 |

Gate leakage currents in PMOS are very less since oxide potential barrier is 4.5eV for PMOS compared to 3.14eV for NMOS using SiO<sub>2</sub> as gate dielectric which plays crucial

role in determination of gate leakage and EDT 'on' state leakage. Thus it is seen that due to the interconnection effect some leakage currents increases while others decreases and we are able to find steady state leakage currents due to potential rise/fall at intermediate nodes.

The width of pull-up PMOS considered in the analysis is 40nm and access NMOS transistor is 60nm for better writability and that of pull-down NMOS is 100nm for better readability. The various leakage currents in different n-MOSFETS of MGDG are shown in the **table 5.1** computed from our earlier analysis in [53] same way all leakage currents of PMOS are also tabulated in **table 5.2**. The first row represents leakage currents without considering the Interconnection effects i.e. considering potential variation at intermediate nodes due to leakage currents, while 2<sup>nd</sup> row represents those after these effects have been taken into account.

The threshold voltage of NMOS in our case is 0.31V and that of PMOS is -0.32V. Thus it is seen that due to the interconnection effect some leakage currents increases while others decreases and we are able to find steady state leakage currents due to potential rise/fall at intermediate nodes. In reading '0' node is critical since any potential raise there coupled with process parameter variations in M1 or M6 leads to read failure. When the cell is in idle mode the potential rise at '0' node is found to be 10mV and potential fall at '1' node is found to be 17mV. The potential fall at '1' node is more due to the more subthreshold leakage of M2. Simultaneous solution of KCL equations at '0' storing node of SRAM cell in Figure 5.10 gives potential rise in '0' node during the read operation to be 34mV which coupled with potential rise due to  $C_{gd}\, of\, 7mV$  will not raise above trip point of inverter M2-M6 hence read failure probability can be expected to be reduced. Since we are using supply voltage of 0.9V in above analysis we assumed trip voltage to be 0.4V. Similar analysis on Figure 5.11 using leakage currents in tables 5.1 and 5.2 shows that write failure probability using properly sized access and PMOS transistors (whose width ratio=1.5) is less and quick discharging takes place and it will not be worsened by combined effect of small signal capacitances and leakage currents. Using Berkeley predictive technology models for bulk CMOS technology at 22nm with Metal gate/high-K dielectric gives stand alone gate drain capacitance and gate-drain capacitance at lightly doped part of drain respectively to be[54].

CGD0=7e-11; CGD1=7.5e-13

Assuming symmetrical DGMOSFET structure with careful overlap regions and using BSIM SOI models the same are given by,

CGS0= CGD0=19.27e-27; CGD1=Not given.

Above data shows that stand alone gate-drain capacitance is less as well as extracted small signal  $C_{gd}$  is also less for MGDG MOSFET which gives better noise, power and timing performance in digital/memory circuit design. Stand alone and small signal capacitances are added together while estimating the potential rise.

## Ultra Low Voltage SRAM Design Using MGDG MOSFET

#### 6.1 Design Problems at Ultra Low Voltage SRAM

Memory power consumption can be reduced by reducing supply to a voltage which is just enough to retain data called data retention voltage which is further influenced by process variations of minimum geometry transistors used in present day technology. Maintaining almost constant Static Noise Margin (SNM) across different process corners is still challenging. One should maximize number of cells that can be connected to the bit line with reliable operation. Reduction of supply voltage during standby mode helps to reduce all the leakage currents to the minimum and the voltage which is just enough to retain cell data is called Data retention voltage (DRV). Analytical modeling of DRV for SRAM cell is needed by which the designer can find the minimum operating voltage of SRAM cell under process variations. Further memory in wireless sensor networks is in idle mode for longer times followed by a burst of data, so one should be able to operate reliably in ultralow voltage operation as well as achieving improved performance for faster processing of data.

#### 6.2 Data Retention Voltage Analysis of MGDGMOSFET

In this work, we developed analytical modeling of Data retention voltage for MGDG MOSFET based SRAM cell based on previous work by B. H. Calhoun, H. Qin. *et. al* [9], [11] for bulk MOSFET. We found SNM variations with gate work function engineered MGDGMOSFET under different process corners and it is found that our MGDG MOSFET is more robust against process variations even in ultra low voltage operation. In order to stably preserve data in SRAM cell, the cross coupled inverters must have loop gain greater than one. Stability of SRAM cell is often indicated through Static Noise Margin (SNM), which is defined as the maximum possible square between VTC's of internal inverters [2], [9], [55]. Around Data Retention voltage VTC of internal inverters degrade to such a level that the loop gain reduces to one and SNM of SRAM cell falls to zero. Both PMOS and NMOS are in weak inversion region and equating their currents gives the transfer characteristics of the inverter. Applying above condition for M1-M5 inverters in Figure 6.1 yields,

$$I_{sn} \exp\left(\frac{V_{in} - V_{du}}{m_n V_{T}}\right) \left(1 - \exp\left(\frac{-V_{out}}{V_{T}}\right)\right) = I_{sp} \exp\left(\frac{V_{dd} - V_{in} - V_{dp}}{m_p V_{T}}\right) \left(1 - \exp\left(\frac{V_{dd} - V_{out}}{V_{T}}\right)\right) (6.1)$$

$$V_{in} = V_{T} \left(\frac{m_n m_p}{m_n + m_p}\right) \left(\ln \frac{I_{sp}}{I_{sn}} + \ln\left(\frac{1 - \exp\left(\frac{-V_{dd} + V_{out}}{V_{T}}\right)}{1 - \exp\left(\frac{-V_{out}}{V_{T}}\right)}\right)\right) + \frac{m_n V_{dd}}{m_n + m_p} + \frac{m_n m_p}{m_n + m_p} \left(\frac{V_{dn} - V_{dp}}{m_n - m_p}\right) (6.2)$$

Where  $m_n$ ,  $m_p$  are subthreshold slope factors for NMOS and PMOS respectively.  $V_{_{thn}}$ ,  $V_{_{thp}}$  are threshold voltages for NMOS and PMOS respectively.  $I_{_{sp}}$  and  $I_{_{sn}}$  are subthreshold current at  $V_{_{gs}} = V_{_{th}}$  and  $V_{_{ds}} = 0$  for both PMOS and NMOS respectively.  $V_{_{dd}}$  is supply voltage,  $V_{_{T}}$  is thermal voltage,  $V_{_{in}}$  is input voltage,  $V_{_{out}}$  is output voltage of the inverter considered. Rather than p and n subscript one can use transistor number as subscript as in Figure 6.1.

Applying condition for DRV as the point where loop gain becomes one.

$$\frac{\partial V_1}{\partial V_2}\Big|_{\text{Left inverter}} = \frac{\partial V_1}{\partial V_2}\Big|_{\text{Right inverter}}, \text{ when } V_{\text{dd}} = \text{DRV}$$

(6.3)

From equations (6.1), (6.2) and (6.3) DRV value can be approximately given by,

$$DRV = V_{r} \left( \frac{m_{1}m_{6}}{m_{1} + m_{6}} \right) \log \left[ \left( \left( \frac{m_{2} + m_{6}}{m_{2}m_{6}} \right) \frac{I_{s2}}{I_{s1}} \right) \times \left( \frac{I_{s3}}{m_{1}} + I_{s5} \left( \frac{m_{1} + m_{5}}{m_{1}m_{5}} \right) \right) \right]$$

(6.4)

Above equation assumes that one is at perfectly '0' other node at perfectly '1', in general due to leakage currents it will not be so and there is small potential drain from node storing '1' and little bit rise at node storing '0' which can be evaluated by Kirchhoff's current law for leakage currents at respective nodes and it is estimated that 10mV rise is observed at node storing '0' and 17mV fall is observed at node storing '1'. The initial value of DRV is reasonably valid even leakage current analysis comes into picture. The value of subthreshold factor is analytically calculated to be ideal value of 1 for both PMOS and NMOS from our analysis in chapter 3. Ideal value of subthreshold factor allows for even lower DRV since transistors are almost ideal. We obtained DRV to be 79mV and it is little bit more than predicted by HSPICE simulations of 62mV since PMOS leakage in our case is underestimated.DRV is more influenced by off state

leakage current ratio of PMOS to access NMOS, so by properly optimizing the access transistor one can tune DRV according to the application.

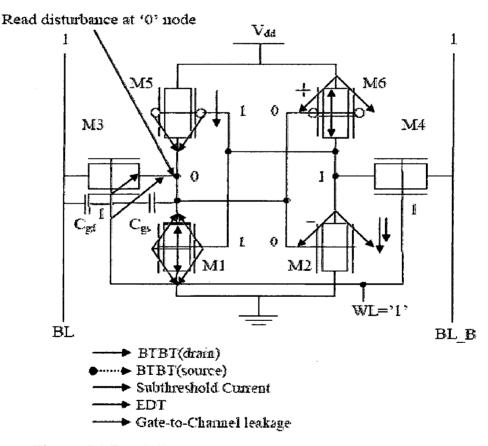

#### 6.3 Description of Subthreshold SRAM Cell Architecture

Figure 6.1 shows the read disturbance present at the '0' storing node of SRAM cell using minimum length transistors and '+' sign on PMOS of right inverter shows due to process variation its strength has been increased and '-' sign on NMOS shows due to process variation its strength has been decreased so it is more prone for read disturbance due to potential rise at '0' storing node and reduced trip point of inverter M2-M6.Read path in the below scheme consist of series connected NMOS's due to less drive current this leads to increase in read delay. Further, the disadvantage of this scheme is reduced driving capability of transistors with reduced supply voltage which results in degraded SNM.

Figure 6.1 Read disturbance caused in nanoscale SRAM

Figure 6.2 shows the modification of conventional dual port memory cell for better readability in nanoscale regime by decoupling the storage nodes from bit lines [53]. In this case voltage at storage node is not influenced by read current so read stability degradation will not occur. Also, sense amplifier senses the current difference between connected gate MGDG with both gates at logic '1' and Independent gate MGDG where one gate is at '1' and other is at '0'. The main advantage of this scheme is improved

SNM. As supply voltage goes down read delay degradation as well as SNM remains almost constant for this scheme because ratio of on current at backgate voltage of  $V_{dd}$  to 0V increases. Read path in the proposed scheme consists of only one transistor compared to two transistors in earlier schemes there by leading to less delay.

Figure 6.2 SRAM cell designed for subthreshold operation [56].

SNM is modeled mathematically [2] as

$F1(V_{L})=V_{L}+c$   $F2(V_{L}-S)=V_{L}-S+c$   $S=F2(V_{L}-S)-F1(V_{L})$   $\frac{\partial F1(V_{L})}{\partial V_{L}}-\frac{\partial F2(V_{L}-SNM)}{\partial V_{L}}=0$ (6.5)

Where F1 is transfer function of first inverter and F2 is transfer function of right inverter. Above equation shows maximum diagonal square that can be inserted into the lobes. Clearly from the above when the driving capability of transistors reduces due to reduction in supply voltage cell is more immune to disturbances due to degraded transfer functions F1 and F2.

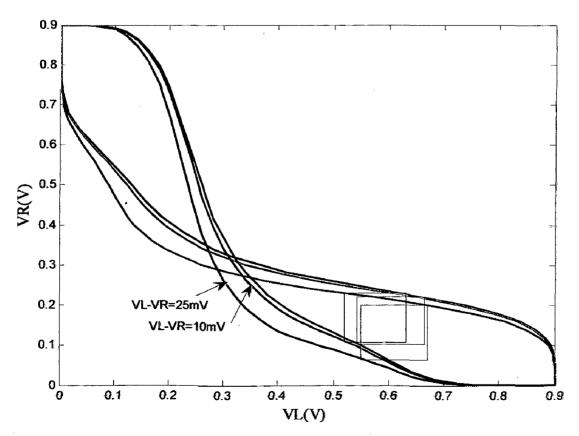

Figure 6.3 shows the Static Noise Margin (SNM) of SRAM cell designed using MGDG MOSFET from H-Spice Simulations and MATLAB plotting. Due to decoupling of storage nodes from bit lines hold mode and read mode SNM are same and at 0.9V SNM is 197mV and at 0.4V it is 156mV clearly this degradation is much smaller than bulk MOSFET based SRAM's [31].

Figure 6.3 SNM under Read/Hold modes at different supply voltages.