## DEVELOPING VERIFICATION ENVIRONMENT FOR

THE USB 2.0 AND WIRELESS USB PHYSICAL LAYER

## **A DISSERTATION**

Submitted in partial fulfillment of the requirements for the award of the degree

of

MASTER OF TECHNOLOGY

in

ELECTRONICS AND COMMUNICATION ENGINEERING (With Specialization in Communication Systems)

DEPARTMENT OF ELECTRONICS AND COMPUTER ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE -247 667 (INDIA) February, 2008

## CANDIDATE'S DECLARATION

I hereby declare that the work, which is being presented in this dissertation, entitled "DEVELOPING VERIFICATION ENVIRONMENT FOR THE USB 2.0 AND WIRELESS USB PHYSICAL LAYER", being submitted in partial fulfillment of the requirements for the award of the degree of MASTER OF TECHNOLOGY with specialization in COMMUNICATION SYSTEMS, in the Department of Electronics and Computer Engineering, Indian Institute of Technology, Roorkee is an authentic record of my own work carried out from January 2007 to July 2007 on "USB 2.0" only, under guidance and supervision of, Mr. Jatinder Verma, Project Manager, Freescale Semiconductors Pvt Ltd INDIA, and continued on Wireless USB from July 2007 to February 2008, the total duration from January 2007 to February 2008 under guidance and supervision of, Dr. Arun Kumar, Professor, Department of Electronics and Computer Engineering, Indian Institute of Technology Roorkee.

The results embodied in this dissertation have not submitted for the award of any other Degree or Diploma.

Date: February, 2008 Place: Roorkee

x Srinin SRINIVAS KUMAR KATA

#### CERTIFICATE

This is to certify that the statement made by the candidate is correct to the best of my knowledge and belief.

laturde Ven

(External Guide)

Mr. Jatinder Verma Project Manager Freescale Semiconductors Pvt Ltd Noida -201301 UP (INDIA)

(Internal Guide) Dr. Arun Kumar Professor, E&C Department Indian Institute of technology, Roorkee Roorkee – 247 667, (INDIA) Freescale Semiconductor India Pvt. Ltd. Express Trade Towers, Floor Nos. 5, 6 & 7, Plot # 15 & 16, Sector - 16 A, Noida - 201 301 U.P. (India) Tel: +91-120-4395000 Fax: +91-120-4395199 Regd. Office : F-40, South Extension Part-I, New Delhi-110 049

July 13,2007

1. 1

#### TRAINING CERTIFICATE

#### TO WHOMSOEVER IT MAY CONCERN

This is to certify that Srinivas Kumar Kata was working with our organization as **Project-Trainee** during the period 15-Jan-07 to 13-July-07 and has successfully completed his Project in the area of "Developing Verification Environment for the USB 2.0 & OTG".

We wish his all the best for future endeavors.

For Freescale Semiconductor India Private Limited.

Taturder Verna

Jatinder Verma Design Manager

#### ACKNOWLEDGEMENTS

It gives me immense pleasure to acknowledge the help and cooperation that I received during this final semester project work.

I take this opportunity to extend my sincere thanks to my project manager, *Mr*. *Jatinder Verma*, who has the attitude and the substance of a genius, and leads his innovative team most effectively. I thank him for giving me an opportunity of working in this interesting field with his outstanding team.

I would like to place on record my earnest thanks to *Mr. Narendra Reddy*, who continually and convincingly conveyed a spirit of adventure in regard to my internship. He showed me different ways to approach a problem. A special thanks goes to him for his insightful comments & encouragement. Without his guidance and persistent help this dissertation would not have been possible.

I thank my project internal guide, *Dr. Arun Kumar*, for giving me the opportunity to work in a very interesting area, for always being patient and cooperative during this project work and for his support and guidance throughout my post graduate studies at IIT Roorkee.

I also express my heartfelt thanks to *Dr. D.K.Mehra*, Professor and Head, Department of E & C Engineering, IIT Roorkee for his support and encouragement during the course of my project work.

#### SRINIVAS KUMAR KATA

#### ABSTRACT

# **KEYWORDS:** Universal Serial Bus Protocol (USB), OTG, UTMI, UTMI+, ULPI, VCS, SystemVerilog.

Freescale Semiconductors is working upon devising an integrated circuit for cellular subscriber device platforms, which aims at satisfying the requirements of high-tier products in the 2008-2009 time frame. Our focus is on one of its modules i.e., the USB 2.0 with OTG Support.

The USB2.0 protocol is a Serial protocol used at the interface for communication between the Host and the Device. It exploits differential data transmit advantage by just having 2 data lines. It is used to connect the external devices to the processor peripheral. The processor peripheral has IP bus interface to the other. Device peripheral will be USB compliant. There is OTG support which is capable of interchanging the roles of Host and Device. UTMI, UTMI+, ULPI interfaces which are introduced for the ease of modeling the USB protocol implementation for the IP vendors are also supported. All the simulations are compiled and run by using the tool VCS.

This project work aims at creation and simulation of a SystemVerilog based USB Verification IP for verifying the USB 2.0 OTG design. SystemVerilog provides a set of hardware-oriented modeling constructs within the context of C++ and Verilog and is emerging as a standard for high-level design, modeling & verification. The USB VIP supports USB2.0 functionality with OTG support for all the Interfaces Serial/UTM+/ULPI and all the speeds Low-/Full-/High-speed.

The Wireless USB is a Wireless protocol which is compatible with the existing USB2.0 which requires no wire connectors. The Physical Layer of the Wireless USB is implemented and verified in MATLAB which verifies all the modules present in the Physical Layer of the Wireless USB. The Program in MATLAB is done using ordinary OFDM instead of Multi Band OFDM as mentioned in the Standard.

| CANDID    | DATE'S DECLARATION                                             | i   |

|-----------|----------------------------------------------------------------|-----|

| ACKNO     | WLEDGEMENT                                                     | ii  |

| ABSTRA    | ACT                                                            | iii |

| ABBREV    | VIATIONS                                                       | iv  |

| Chapter   | 1 INTRODUCTION                                                 | 1   |

| 1.        | 1 Motivation                                                   | 1   |

| 1.:       | 2 Statement of the Problem                                     | 2   |

| . 1.      | 3 Organization of the Report                                   | 2   |

| Chapter   | 2 UNIVERSAL SERIAL BUS                                         | 3   |

| 2.        | 1 Goals for the Universal Serial Bus                           | 3   |

| 2.2       | 2 Feature List                                                 | 3   |

| 2.        | 3 Architecture overview of the USB                             | 4   |

|           | 2.3.1 USB System                                               | 4   |

|           | 2.3.2 Physical Interface                                       | 5   |

|           | 2.3.3 Power                                                    | 5   |

|           | 2.3.4 Bus Protocol                                             | 5   |

|           | 2.3.4 Robustness                                               | 6   |

|           | 2.3.5 System Configuration                                     | 6   |

| 2.4       | 4 USB Communication Flow                                       | 6   |

| Chapter 3 | 3 PROTOCOL ASPECTS                                             | 9   |

| 3.1       | 1 About USB2.0 Protocol                                        | 9   |

| 3.2       | 2 Transfer Types                                               | 14  |

| 3.3       | 3 Device States                                                | 17  |

| 3.4       | 4 OTG Specification                                            | 21  |

|           | 3.4.1 Introduction                                             | 21  |

|           | 3.4.2 Session Request Protocol                                 | 22  |

|           | 3.4.3 Host Negotiation Protocol                                | 23  |

| 3.5       | 5 USB 2.0 Transceiver Macrocell Interface (UTMI) Specification | 25  |

|           | 3.5.1 Introduction                                             | 25  |

|           | 3.5.2 USB 2.0 Transceiver Macrocell (UTM)                      | 26  |

|     | 3.5.3 System Interface Signals with Description | 27 |

|-----|-------------------------------------------------|----|

|     | 3.5.4 Data Receiving and Transmitting           | 30 |

|     | 3.6 UTMI+ Specification                         | 31 |

|     | 3.6.1 Introduction                              | 31 |

|     | 3.6.2 UTMI + signals other than UTMI            | 33 |

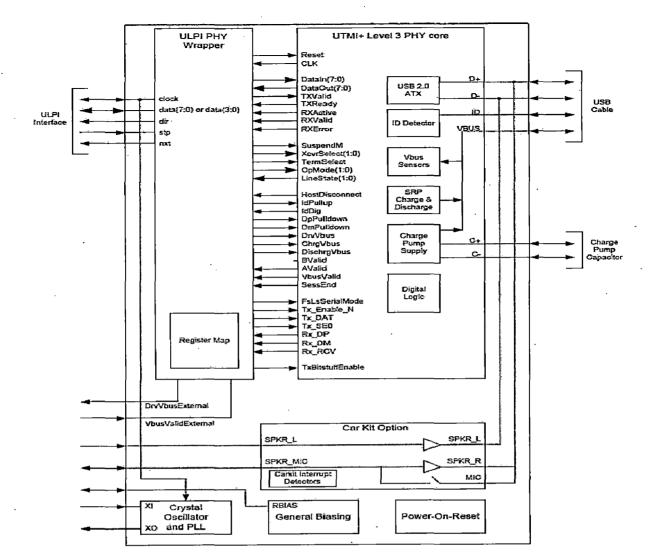

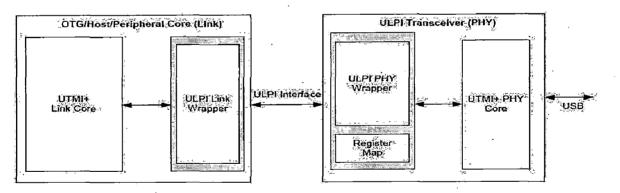

| ,   | 3.7 ULPI Specification                          | 35 |

|     | 3.7.1 Introduction                              | 35 |

|     | 3.7.2 Interface signals of ULPI                 | 37 |

|     | 3.7.3 ULPI Command Bytes                        | 38 |

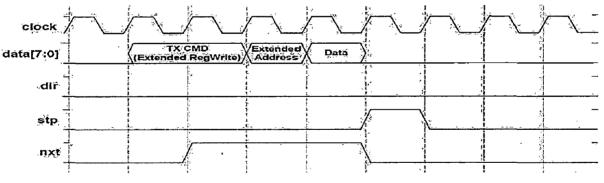

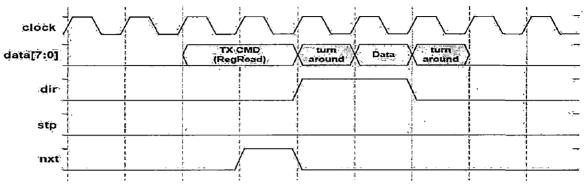

|     | 3.7.4 Register Operations                       | 40 |

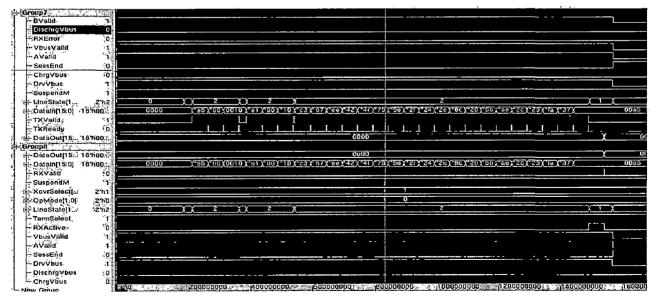

|     | 3.8 Simulation Results                          | 41 |

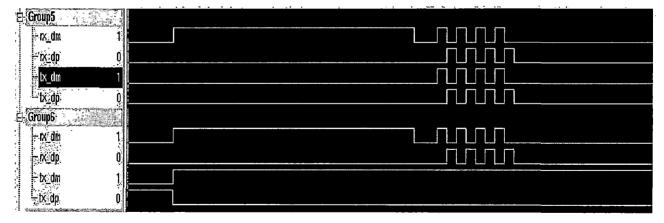

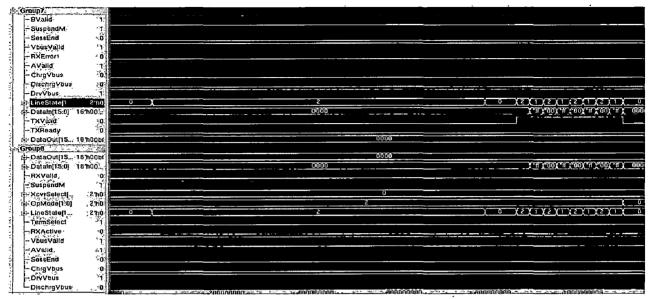

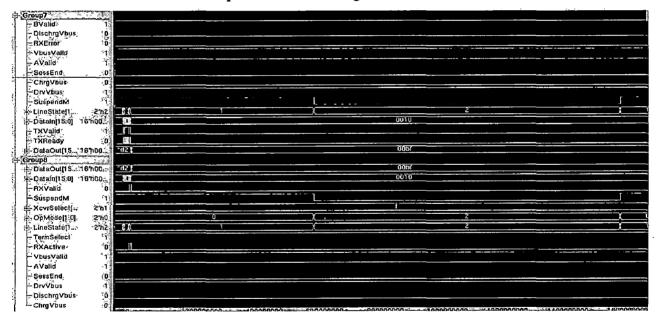

|     | 3.8.1 Serial Interface                          | 41 |

|     | 3.8.2 UTMI+ Interface                           | 42 |

|     | 3.8.3 ULPI Interface                            | 44 |

|     |                                                 |    |

|     | Chapter 4 WIRELESS USB PHYSICAL LAYER           | 46 |

|     | 4.1 General Introduction                        | 46 |

|     | 4.1.1 Architecture Overview                     | 46 |

|     | 4.1.2 Bus Protocol                              | 46 |

|     | 4.1.3 Robustness                                | 46 |

|     | 4.1.4 Security                                  | 47 |

|     | 4.1.5 System Configuration                      | 47 |

|     | 4.2 PHY General Description                     | 47 |

|     | 4.3 MAC General Description                     | 48 |

|     | 4.4 Features Assumed from the PHY               | 48 |

|     | 4.5 PHY Layer Partitioning                      | 49 |

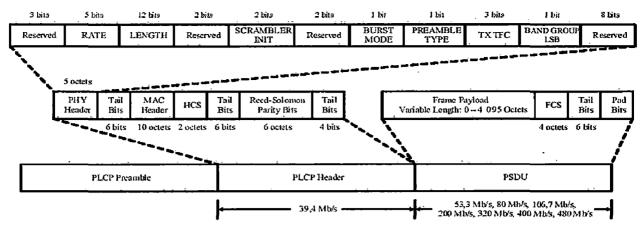

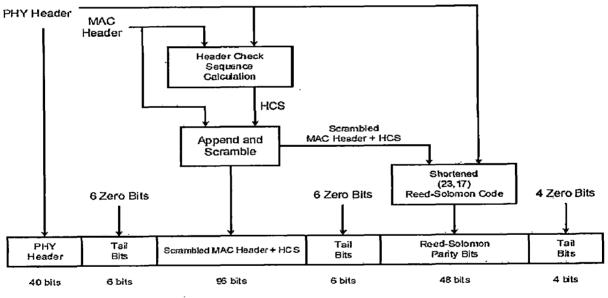

|     | 4.6 PLCP Sublayer                               | 50 |

|     | 4.6.1 PPDU                                      | 50 |

|     | 4.6.2 PLCP Preamble                             | 51 |

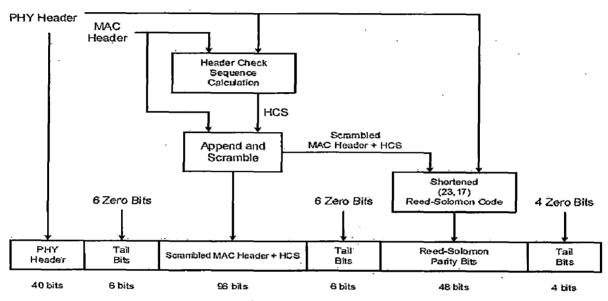

| • • | 4.6.3 PLCP Header                               | 52 |

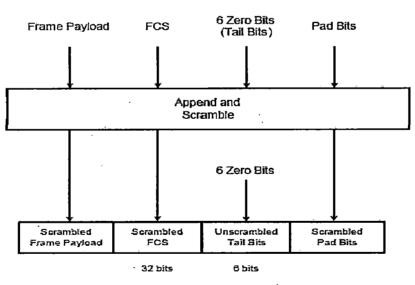

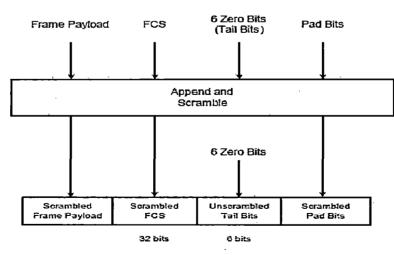

|     | 4.6.4 PSDU                                      | 54 |

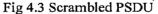

|     | 4.6.5 Data Scrambler                            | 54 |

|     | 4.6.6 Tail Bits                                 | 55 |

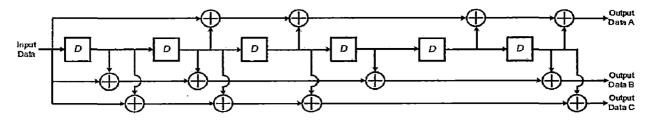

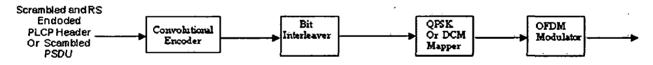

|     | 4.6.7 Convolutional Encoder                     | 55 |

|     |                                                 |    |

|     |                                                 |    |

.

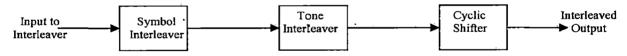

| 4.6.8 Bit Interleaving                              | 56 |

|-----------------------------------------------------|----|

| 4.6.9 Constellation Mapping                         | 56 |

| 4.6.10 OFDM Modulation                              | 57 |

| Chapter 5 SIMULATION OF WIRELESS USB PHYSICAL LAYER | 59 |

| 5.1 Simulation Environment                          | 59 |

| 5.2 Design Flow of Simulation                       | 59 |

| 5.2.1 Transmitter                                   | 59 |

| 5.2.2 Receiver                                      | 62 |

| 5.3 Results                                         | 63 |

| -5.4 MATLAB Code                                    | 64 |

| Chapter 6 CONCLUSION                                | 77 |

| Chapter 7 References                                | 78 |

|                                                     |    |

## APPENDIX

.

#### ABBREVIATIONS

| USB 2.0 | - Universal Serial Bus with High-speed support              |

|---------|-------------------------------------------------------------|

| OTG     | - On-The-Go Support                                         |

| UTMI    | - USB 2.0 Transceiver Macrocell Interface                   |

| UTMI+   | - UTMI with OTG support                                     |

| ULPI    | - UTMI+ Low Pin Interface                                   |

| IP      | - Intellectual Property                                     |

| VIP     | - Verification IP                                           |

| SRP     | - Session Request Protocol                                  |

| HNP     | - Host Negotiation Protocol                                 |

| PID     | - Packet Identifier                                         |

| ENDP    | - END Point number                                          |

| SOF     | - Start of Frame                                            |

| EOP     | - End of Packet                                             |

| AES     | - Advanced Encryption Standard                              |

| CCM     | - Counter Mode Encryption and Cipher Block Chaining Message |

|         | Authentication Code                                         |

| PLCP    | - Physical Layer Convergence Protocol                       |

| PLME    | - Physical Layer Management Entity                          |

| PMD     | - Physical Medium Dependent                                 |

| PPDU    | - PLCP Protocol Data Unit                                   |

| PSDU    | - PHY Service Data Unit                                     |

| UWB     | - Ultra Wideband                                            |

|         |                                                             |

## **1. INTRODUCTION**

#### **1.1 Motivation**

The original motivation for the Universal Serial Bus (USB) [1] came from three interrelated considerations:

- 1. Connection of the PC to the telephone: It is well understood that the merge of computing and communication will be the basis for the next generation of productivity applications. The USB provides a ubiquitous link that can be used across a wide range of PC-to-telephone interconnects.

- 2. Ease-of-use: The combination of user-friendly graphical interfaces and the hardware and software mechanisms associated with new-generation bus architectures have made computers less confrontational and easier to reconfigure. However, from the end user's point of view, the PCs I/O interfaces, such as serial/parallel ports, keyboard /mouse /joystick interfaces, etc., do not have the attributes of plug-and-play.

- 3. Port expansion: The addition of external peripherals continues to be constrained by port availability. The lack of a bidirectional, low-cost, low-to-mid speed peripheral bus has held back the creative proliferation of peripherals such as telephone/fax/modem adapters, answering machines, scanners, PDAs, keyboards, mice, etc. Existing interconnects are optimized for one or two point products. As each new function or capability is added to the PC, a new interface has been defined to address this need.

The more recent motivation for USB 2.0 stems from the fact that PCs have increasingly higher performance and are capable of processing vast amounts of data. At the same time, PC peripherals have added more performance and functionality. User applications such as digital imaging demand a high performance connection between the PC and these increasingly sophisticated peripherals. USB 2.0 addresses this need by adding a third transfer rate of 480 Mb/s to the 12 Mb/s and 1.5 Mb/s originally defined for USB. USB 2.0 is a natural evolution of USB, delivering the desired bandwidth increase while preserving the original motivations for USB and maintaining full compatibility with existing peripherals.

Wireless USB: As technology innovation marches forward, Wireless technologies are becoming more and more capable and cost effective. Ultra-Wideband (UWB) radio

technology, in particular, has characteristics that much traditional USB usage models very well. UWB supports high bandwidth (480Mb/s) but only at limited range (~3 mts). Applying this wireless technology to USB frees the user from worrying about cables, it makes USB even easier to use. Because no physical ports are required, port expansion, or even finding the USB port, is no longer a problem. Losing the cable also means losing a source of power for peripheral which are powered by bus but not for self-powered.

Thus USB (wired or wireless) continues to be the answer to connectivity for the PC architecture. It is a fast, bi-directional, isochronous, low-cost, dynamically attachable interface.

#### **1.2 Statement of the Problem**

This work is aimed for the Verification of the USB 2.0 OTG Support as it is required before producing the design into a chip. To verify the design, a Verification IP is required to do all the verifications supported by USB 2.0 Protocol. There are 3 types of speeds supported by the protocol. There are 3 types of interfaces supported by the protocol. The Vendor has to verify all the interfaces in all speeds for USB2.0 protocol and OTG supplement.

This work also aims at the verification Wireless USB protocol at physical layer using the MATLAB.

#### **1.3 Organization of Report**

The report is organized in six chapters including this chapter. Chapter one gives an overview of the introduction and motivation, summarizes the problem statement for the thesis work. Chapter two gives overview of USB architecture and communication flow of the USB 2.0. Chapter three gives description of protocol types of packets, transactions and transfers and also explains the On-The-Go supplement, UTMI, UTMI+, ULPI specifications along with results obtained from the simulation. Chapter four deals with the introduction of the Wireless USB protocol from the Physical layer point of view. The fifth chapter deals with the simulation done, results obtained and code for wireless USB Physical Layer in MATLAB.

## 2. UNIVERSAL SERIAL BUS

#### 2.1 Goals for the Universal Serial Bus

The USB is specified to be an industry-standard extension to the PC architecture with a focus on PC peripherals that enable consumer and business applications. The following criteria were applied in defining the architecture for the USB [1]:

- 1. Ease-of-use for PC peripheral expansion.

- 2. Low-cost solution that supports transfer rates up to 480 Mb/s.

- 3. Full support for real-time data for voice, audio, and video.

- 4. Protocol flexibility for mixed-mode isochronous data transfers and asynchronous messaging.

- 5. Provision of a standard interface capable of quick diffusion into product.

- 6. Enabling new classes of devices that augment the PCs capability.

#### 2.2 Feature List

The USB Specification provides a selection of attributes that can achieve multiple price/performance integration points and can enable functions that allow differentiation at the system and component level. Features are categorized by the following benefits:

- 1. Easy to use for end user with self-identifying peripherals, automatic mapping of function to driver and configuration and dynamically attachable and reconfigurable peripherals.

- 2. Wide range of bandwidths ranging from a few kb/s to several hundred Mb/s, capable of supporting 127 physical devices, supports transfer of multiple data and message streams between the host and devices with Low protocol overhead.

- 3. Guaranteed bandwidth, low latencies appropriate for telephony, audio, video, etc.

- 4. Flexibility in packet sizes, data rates and flow control for buffer handling.

- 5. Robustness for Error handling/fault recovery mechanism, Dynamic insertion and removal of devices.

- 6. Protocol is simple to implement with plug-and-play architecture and leverages existing operating system interfaces.

- 7. Low-cost implementation.

- 8. Architecture upgradeable to support multiple USB Host Controllers in a system.

#### 2.3 Architecture overview of the USB

The USB is a cable bus that supports data exchange between a host computer and a wide range of simultaneously accessible peripherals. The attached peripherals share USB bandwidth through a host scheduled, token-based protocol. The bus allows peripherals to be attached, configured, used, and detached while the host and other peripherals are in operation.

#### 2.3.1 USB System

A USB system is described by three definitional areas:

- 1. USB Interconnect.

- 2. USB Host.

- 3. USB Devices.

#### **USB** Interconnect

The USB interconnect is the manner in which USB devices are connected to and communicate with the host. This includes the following:

- Bus Topology: Connection model between USB devices and the host.

- Inter-layer Relationships: In terms of a capability stack, the USB tasks that are performed at each layer in the system.

- Data Flow Models: The manner in which data moves in the system over the USB between producers and consumers.

- USB Schedule: The USB provides a shared interconnect. Access to interconnect is scheduled in order to support isochronous data transfers and to eliminate arbitration overhead.

#### **USB Host**

There is only one host in any USB system. The USB interface to the host computer system is referred to as the Host Controller. The Host Controller may be implemented in a combination of hardware, firmware, or software. A root hub is integrated within the host system to provide one or more attachment points.

#### **USB** Devices

USB devices are one of the following:

1. Hubs, which provide additional attachment points to the USB

2. Functions, which provide capabilities to the system, such as an ISDN connection, a digital joystick, or speakers

USB devices present a standard USB interface in terms of the following:

- 1. Their comprehension of the USB protocol.

- 2. Their response to standard USB operations, such as configuration and reset.

- 3. Their standard capability descriptive information.

#### **2.3.2 Physical Interface**

The USB transfers signal and power over a four-wire cable. The signaling occur over two wires (D+/D-) on each point-to-point segment. The power is transmitted over one wire Vbus.

#### 2.3.3 Power

There are two aspects of power:

- 1. Power distribution over the USB deals with the issues of how USB devices consume power provided by the host over the USB.USB devices that rely totally on power from the cable are called bus-powered devices. In contrast, those that have an alternate source of power are called self-powered devices.

- 2. Power management deals with how the USB System Software and devices fit into the host-based power management system. The USB System Software interacts with the host's power management system to handle system power events such as suspend or resume.

#### 2.3.4 Bus Protocol

The USB is a polled bus. The Host Controller initiates all data transfers. Most bus transactions involve the transmission of up to three packets. Each transaction begins when the Host Controller, on a scheduled basis, sends a USB packet describing the type and direction of transaction, the USB device address, and endpoint number. The USB data transfer model between a source or destination on the host and an endpoint on a device is referred to as a pipe. Pipes come into existence when a USB device is configured. One message pipe, the Default Control Pipe, always exists once a device is powered, in order to provide access to the devices configuration, status, and control information.

#### 2.3.4 Robustness

There are several attributes of the USB that contribute to its robustness:

- 1. Signal integrity using differential drivers, receivers, and shielding.

- 2. CRC protection over control and data fields.

- 3. Detection of attach and detach and system-level configuration of resources.

- 4. Self-recovery in protocol, using timeouts for lost or corrupted packets.

- 5. Flow control for streaming data to ensure isochrony and hardware buffer management.

- 6. Data and control pipe constructs for ensuring independence from adverse interactions between functions.

#### 2.3.5 System Configuration

The USB supports USB devices attaching to and detaching from the USB at any time. Consequently, system software must accommodate dynamic changes in the physical bus topology.

## 2.4 USB Communication Flow

The USB provides a communication services between software on the host and its USB function. Functions can have different communication flow requirements for different client-to-function interactions. The USB provides better overall bus utilization by allowing the separation of the different communication flows to a USB function. Each communication flow makes use of some bus access to accomplish communication between client and function. Each communication flow is terminated at an endpoint on a device. Device endpoints are used to identify aspects of each communication flow.

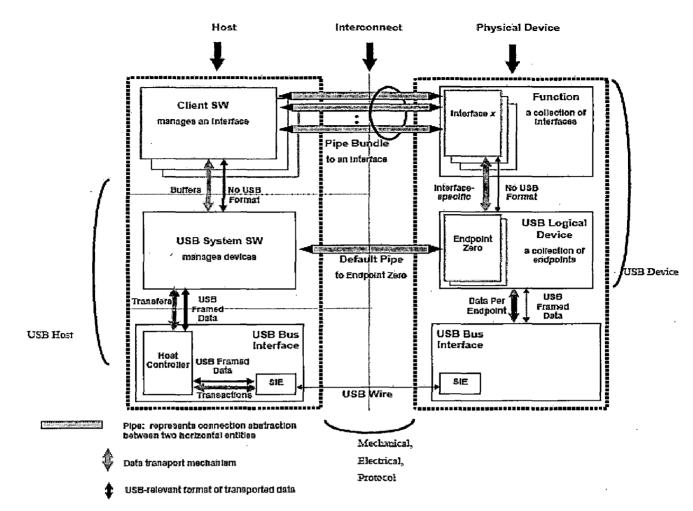

The Functions performed by the blocks in the below diagram are

- 1. Client Software: Software that executes on the host, corresponding to a USB device. This client software is typically supplied with the operating system or provided along with the USB device.

- 2. USB System Software: Software that supports the USB in a particular operating system. The USB System Software is typically supplied with the operating system, independently of particular USB devices or client software.

- 3. USB Host Controller (Host Side Bus Interface): The hardware and software that allows USB devices to be attached to a host.

- 4. USB Logical Device: A USB logical device appears to the USB system as a collection of endpoints. Endpoints are grouped into endpoint sets that implement an interface. Interfaces are views to the function.

- 5. USB Physical Device: A piece of hardware on the end of a USB cable that performs some useful end user function.

Fig 2.1: USB Host/Device Detailed View

The USB System Software manages the device using the Default Control Pipe. Client software manages an interface using pipe bundles (associated with an endpoint set). Client software requests that data be moved across the USB between a buffer on the host and an endpoint on the USB device. The Host Controller (or USB device, depending on transfer direction) packetizes the data to move it over the USB. The Host Controller also coordinates when bus access is used to move the packet of data over the USB.

Software on the host communicates with a logical device via a set of communication flows. The set of communication flows are selected by the device software/hardware designer(s) to efficiently match the communication requirements of the device to the transfer characteristics provided by the USB.

#### **Device Endpoints**

An endpoint is a uniquely identifiable portion of a USB device that is the terminus of a communication flow between the host and device. Each USB logical device is composed of a collection of independent endpoints. Each logical device has a unique address assigned by the system at device attachment time. Each endpoint on a device is given at design time a unique device-determined identifier called the endpoint number. Each endpoint has a device-determined direction of data flow. The combination of the device address, endpoint number, and direction allows each endpoint to be uniquely referenced. Each endpoint is a simplex connection that supports data flow in one direction: either input (from device to host) or output (from host to device).

#### Pipes

Pipes represent the ability to move data between software on the host via a memory buffer and an endpoint on a device. There are two types of pipes: stream and message. Stream data has no USB-defined structure, while message data does. Pipes have associations of data bandwidth, transfer service type, and endpoint characteristics like directionality and buffer sizes.

#### **Frames and Microframes**

USB establishes a 1 millisecond time base called a frame on a full-/low-speed bus and a 125 us time base called a microframe on a high-speed bus. A (micro) frame can contain several transactions. Each transfer type defines what transactions are allowed within a (micro) frame for an endpoint.

## **3. PROTOCOL ASPECTS**

## 3.1 About USB2.0 Protocol

#### **Byte/Bit Ordering**

USB follows the little-endian order, i.e., LSB to MSB for both individual bits and fields.

#### SYNC Field [1]

All packets begin with a synchronization (SYNC) field, which is used by the input circuitry to align incoming data with the local clock. The SYNC pattern used for low-/full-speed transmission is required to be 3 KJ pairs followed by 2 K's for a total of eight symbols. The SYNC pattern used for high-speed transmission is required to be 15 KJ pairs followed by 2 K's, for a total of 32 symbols.

#### **EOP** Width

The width of the SE0 in the EOP is approximately 2 \* TPERIOD i.e., for full-speed transmissions between 160 ns and 175 ns and for low-speed transmissions between 1.25 us and 1.50 us. In high-speed signaling, a bit stuff error is intentionally generated to indicate EOP. A receiver is required to interpret any bit stuff error as an EOP.

#### **Packet Field Formats**

Packet bit definitions are displayed in unencoded data format. All packets have distinct Start-of- Packet (SOP) delimiter which is part of the SYNC field and the End-of-Packet (EOP) delimiter.

Packet Identifier Field (PID): A PID consists of a four-bit packet type field which gives type of packet followed by a four-bit check field which is one's complement of packet type field which ensures reliable decoding of the PID so that the remainder of the packet is interpreted correctly.

• The understanding between the host and device is taken in packet form.

| FEILD | PID | ADDRESS | ENDP | CRC5 |

|-------|-----|---------|------|------|

| BITS  | 8   | 7       | 4    | 5    |

1. Token

Fig 3.1: Token packet format

2. Start of Frame

| FEILD | PID | Frame number               | CRC5 |

|-------|-----|----------------------------|------|

| BITS  | 8   | 11                         | 5    |

|       | · · | Fig 3.2: SOF packet format | t    |

3. Data

| FEILD | PID | DATA                       | CRC16 |

|-------|-----|----------------------------|-------|

| BITS  | 8   | 0-8192                     | 16    |

|       |     | Eta 2.2. Data un alest fau |       |

Fig 3.3: Data packet format

#### Address Fields:

Function endpoints are addressed using two fields: the function address field and the endpoint field. A function needs to fully decode both address and endpoint fields.

- Address Field: Address Field <6:0> 128 possible addresses of function ports.

Function address zero is reserved as the default address and may not be assigned to any other use.

- Endpoint Field: Endpoint Field<3:0> 16 possible varieties of combinations

of transfers. All functions must support a control pipe at endpoint number zero

(the Default Control Pipe). Low-speed devices support a maximum of three

pipes per function. Full-speed and high-speed functions may support up to a

maximum of 16 IN and OUT endpoints.

**Frame Number Field:** The frame number field is an 11-bit field that is incremented by the host on a per-frame basis. The frame number field rolls over upon reaching its maximum value of 7FFH and is sent only in SOF tokens at the start of each (micro) frame.

**Data Field:** The data field may range from zero to 1,024 bytes and must be an integral number of bytes. Data bits within each byte are shifted out LSB first.

- Low speed data field is of 0-8 bytes

- Full speed data field is of 0-511 bytes

- High speed data field is of 0-1023 bytes

**Cyclic Redundancy Checks:** Token and data packet CRCs provide 100% coverage for all single- and double-bit errors.

• Token CRC - A five-bit CRC field is provided for tokens and covers the ADDR and ENDP fields of IN, SETUP, and OUT tokens or the time stamp

field of an SOF token. The PING and SPLIT special tokens also include a five-bit CRC field. The generator polynomial is:

$\mathbf{G}(\mathbf{X}) = \mathbf{X}^5 + \mathbf{X}^2 + \mathbf{1}$

The binary bit pattern that represents this polynomial is 00101B. If all token bits are received without error, the five-bit residual at the receiver will be 01100B.

• Data CRC - The data CRC is a 16-bit polynomial applied over the data field of a data packet. The generating polynomial is:

$G(X) = X^{16} + X^{15} + X^2 + 1$

The binary bit pattern that represents this polynomial is 1000000000000101B. If all data and CRC bits are received without error, the 16-bit residual will be 100000000001101B.

#### **Handshake** Packets

| FEILD | PID |

|-------|-----|

| BITS  | 8   |

Fig 3.4: Handshake packet format

Handshake packets consist of only a PID. Handshake packets are used to report the status of a data transaction and can return values indicating successful reception of data, command acceptance or rejection, flow control, and halt conditions. There are four types of handshake packets and one special handshake packet:

- ACK may be issued either when sequence bits match and the receiver accepted data correctly or when sequence bits mismatch and the sender and receiver must resynchronize to each other

- NAK can only be returned by functions in the data phase of IN transactions or the handshake phase of OUT or PING transactions.

- STALL indicates that a function is unable to transmit or receive data, or that a control pipe request is not supported. Functional STALL is when the *Halt* feature associated with the endpoint is set. Protocol STALL is returned during the Data or Status stage of a control transfer, and the STALL condition, terminates at the beginning of the next control transfer (setup).

- NYET is returned by a hub in response to a split-transaction when the full-/low-speed transaction has not yet been completed or the hub is otherwise not

able to handle the split-transaction. It is returned by a high-speed endpoint as part of the PING protocol.

• ERR is a high-speed only handshake that is returned to allow a high-speed hub to report an error on a full-/low-speed bus.

#### SPLIT

Host controllers and hubs support one additional transaction type called split transactions. This transaction type allows full- and low-speed devices to be attached to hubs operating at high-speed. These transactions involve only host controllers and hubs and are not visible to devices.

#### PING

The host controller queries the high-speed device endpoint with a PING special token. The endpoint either responds to the PING with a NAK or an ACK handshake. A NAK handshake indicates that the endpoint does not have space for a *wMaxPacketSize* data payload.

#### **Transaction** [1]

The mutual transfer of packets (token, data and acknowledgement) between the host and the device is called transaction. It may be of 2 levels or 3 levels.

The protocol overhead for each transaction includes:

- A SYNC field (packet): either 8 bits (full-/low-speed) or 32 bits (high-speed).

- A PID byte (packet): includes PID and PID invert (check) bits.

- An EOP (packet): 3 bits (full-/low-speed) or 8 bits (high-speed).

- In a token packet, the endpoint number, device address, and CRC5 fields (16 bits total).

- In a data packet, CRC16 fields (16 bits total).

- For transaction with multiple packets, the inter packet gap or bus turnaround time required.

For these calculations, there is assumed to be no bit-stuffing required.

Responses for the transactions from host and function for particular tokens

| Host        |                |             | SENDS IN    | TOKEN          |                   |

|-------------|----------------|-------------|-------------|----------------|-------------------|

| Function    | Receives co    | rrectly and | Receives    | Received       | Endpoint is not   |

| Responses   | sends data pac | eket.       | incorrectly | correctly but  | supporting the    |

| in one of   |                |             | and gives   | has no data to | function to       |

| way         |                |             | no          | transmit gives | transmit the data |

|             |                |             | response    | NAK.           | so gives STALL    |

| How the     | If data        | If data     | Retries     | Retries later. | Sets the Endpoint |

| host reacts | packet is      | packet is   | later       |                | Configuration and |

|             | received       | not correct |             |                | Retries by        |

|             | correctly      | discards    |             |                | sending IN token  |

|             | gives ACK      | data        |             |                |                   |

Table 3.1 Function and Host Responses to IN Transactions

Table 3.2 Function Responses to OUT Transactions

| Host        |               | SENDS OUT and   | DATA PACKETS       |                   |

|-------------|---------------|-----------------|--------------------|-------------------|

| Function    | Receives      | Receives        | Received correctly | Endpoint is not   |

| Responses   | correctly and | incorrectly and | but cannot accept  | supporting the    |

| in one of   | gives ACK     | gives no        | data so gives      | function to       |

| way         |               | response        | NAK.               | transmit the data |

|             |               |                 |                    | so gives STALL    |

| How the     | -             | Retries later   | Retries later.     | Sets the Endpoint |

| Host reacts |               |                 |                    | Configuration     |

|             |               |                 |                    | and Retries by    |

|             |               |                 |                    | sending OUT and   |

|             |               |                 |                    | DATA token        |

#### **Function Response to a SETUP Transaction**

SETUP defines a special type of host-to-function data transaction that permits the host to initialize an endpoint's synchronization bits to those of the host. Upon receiving a SETUP token, a function must accept the data. A function may not respond to a SETUP token with either STALL or NAK, and the receiving function must accept the data packet that follows the SETUP token. If a non-control endpoint receives a SETUP token, it must ignore the transaction and return no response.

## **3.2 Transfer Types**

The USB transports data through a pipe between a memory buffer associated with a software client on the host and an endpoint on the USB device. Data transported by message pipes is carried in a USB-defined structure, but the USB allows device-specific structured data to be transported within the USB-defined message data payload. The USB also defines that data moved over the bus is packetized for any pipe (stream or message), but ultimately the formatting and interpretation of the data transported in the data payload of a bus transaction is the responsibility of the client software and function using the pipe.

Each transfer type determines various characteristics of the communication flow including the following:

- 1. Data format imposed by the USB.

- 2. Direction of communication flow.

- 3. Packet size constraints.

- 4. Bus access constraints.

- 5. Latency constraints.

- 6. Required data sequences.

- 7. Error handling

The USB defines four transfer types:

#### **Control Transfers** [1]

Control transfers minimally have two transaction stages: Setup and Status.

- Bursty, non-periodic, host software-initiated request/response communication, typically used for command/status operations.

- A control transfer may optionally contain a Data stage between the Setup and Status stages. The amount of data to be sent during the data stage and its direction are specified during the Setup stage. The Status stage of a control transfer is the last transaction in the sequence.

| Status Response       | Control Write Transfer   | Control Read Transfer(sent |

|-----------------------|--------------------------|----------------------------|

|                       | (sent during data phase) | during handshake phase)    |

| Function completes    | Zero-length data packet  | ACK handshake              |

| Function has an error | STALL handshake          | STALL handshake            |

| Function is busy      | NAK handshake            | NAK handshake              |

#### Table3.3 Status Stage Responses

• The protocol STALL condition lasts until the receipt of the next SETUP transaction, and the function will return STALL in response to any IN or OUT transaction on the pipe until the SETUP transaction is received.

#### **Bulk Transaction**

The bulk transfer type is designed to support devices that need to communicate relatively large amounts of data at highly variable times that can use any available bandwidth.

Requesting a pipe with a bulk transfer type provides the requester with the following:

- 1. Access to the USB on a bandwidth-available basis,

- 2. Retry of transfers, in the case of delivery failure due to errors on the bus,

- 3. Guaranteed delivery of data but no guarantee of bandwidth or latency.

The following are features of the Bulk Transactions

- Non-periodic, large-packet bursty communication, typically used for data that can use any available bandwidth and can also be delayed until bandwidth is available.

- Bulk transactions use a three-phase transaction consisting of token, data and handshake packets are characterized by the ability to guarantee error-free delivery of data between the host and a function by means of error detection and retry.

- If the data is received without error by the function, it will return one of three (or four including NYET, for a high-speed device) handshakes: ACK, NAK, STALL.

#### **Interrupt Transaction**

The interrupt transfer type is designed to support those devices that need to send or receive data infrequently but with bounded service periods. Requesting a pipe with an interrupt transfer type provides the requester with the following:

- 1. Guaranteed maximum service period for the pipe.

- 2. Retry of transfer attempts at the next period, in the case of occasional delivery failure due to error on the bus

The following are features of the Interrupt Transactions

- Low-frequency, bounded-latency communication.

- If the endpoint has no new interrupt information to return the function returns a NAK handshake during the data phase.

• If the Halt feature is set for the interrupt endpoint, the function will return a STALL handshake.

#### **Isochronous Transaction**

In the USB environment, requesting an isochronous transfer type provides the requester with the following:

- Guaranteed access to USB bandwidth with bounded latency.

- Guaranteed constant data rate through the pipe as long as data is provided.

- No retry in the case of a delivery failure due to error.

The USB isochronous transfer type is designed to support isochronous sources and destinations.

- Periodic, continuous communication between host and device, typically used for time-relevant information.

- Isochronous transactions have a token and data phase, but no handshake phase.

- A high-speed Host Controller must be able to accept and send DATA0, DATA1, DATA2, or MDATA PIDs in data packets.

- High bandwidth, high-speed isochronous transactions support data PID sequencing.

There are 3 different speeds and 4 different types of transfers that USB supports and each with different payload sizes depending on the need of the endpoints only required types of transfers are supported by the protocol and each in appropriate proportion of available bandwidth. Here are the types of speeds, transfers and payload sizes (Packet Size constraints).

| Packet       | Control | Interrupt | Bulk       | Isochronous |

|--------------|---------|-----------|------------|-------------|

| Constraints  |         |           |            |             |

| Low-speed    | 8       | 8         | N/A        | N/A         |

| Payload(max) |         |           |            |             |

| Full-speed   | 64      | 64        | 8/16/32/64 | 1023        |

| Payload(max) |         |           |            |             |

| High-speed   | 64      | 1024      | 512        | 1024        |

| Payload(max) | 1       |           |            |             |

|              |         |           |            |             |

Table 3.4 Transfers, Speeds with Max Payload

| Data Format   | USB-defined     | no data content | no data         | no data content |

|---------------|-----------------|-----------------|-----------------|-----------------|

|               | structure       | structure       | content         | structure       |

|               |                 |                 | structure       |                 |

| Direction     | Bi-directional  | Stream pipe,    | stream pipe,    | uni-directional |

|               |                 | uni-directional | uni-directional |                 |

| Bus Access    | part of each    | bus frequency   | On bandwidth-   | Required bus    |

| Constraints   | (micro)frame is | and (micro)     | available       | access period.  |

|               | reserved        | frame           | basis.          |                 |

| Endpoint Used | In ,Out         | In or Out       | In or Out       | In or Out       |

#### **3.3 Device States**

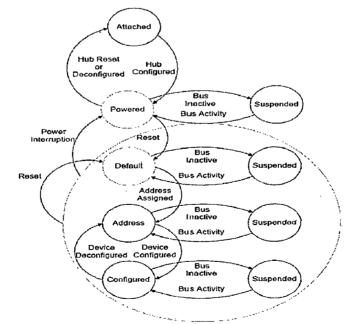

There are few possible states where the device works. Bus Enumeration is the process that the device goes into for participating in the transfers along with the Host.

#### 1. Attached [1]

A USB device may be attached or detached from the USB. The current level on the resistor rises indicating the new connection. The Speed of the device will be detected at the time of attach.

- If the pull-up resistor of USB device is on D- line then the host will move to Low-speed clock after detecting the device

- If the pull-up resistor of USB device is on D+ line then the host will move to Full-speed clock and at the time of reset changes to High-speed depending on negotiation.

The device will permitted to data transfer only after the reset state

#### 2. Powered

USB devices may obtain power from an external source and/or from the USB through the host to which they are attached. Externally powered USB devices are termed self- powered. If the device gets power through the Host it is termed as bus-powered. A device may support both or either of self-powered and bus-powered configurations.

#### 3. Default Address

Host assigns a default address to the device initially after powered it gives the default address and zero-endpoint address. In this state the transfers between the host and device will take place through the default control pipe.

#### **RESET PROCESS:**

A device that is capable of high-speed operation determines whether it will operate at high-speed as a part of the reset process. After detecting SE0 for 2.5us the device recognizes that host is resetting. The reset for Low-speed is for waiting 10ms in SE0 state.

- The HS Detection Handshake is Set along with the reset signaling which is of atleast 10ms.

- A device has up to 6 ms after the reset process starting to assert a minimum of a 1 ms Chirp K.

- If the host is of HS capable then it has to respond for this Chirp K state within 100 us of its completion.

- Then the host has to assert with Chirp K and Chirp J states alternately for at least 3 times and each of the state having an interval of 40-60 us.

- As soon as the device detects the 3 KJ sequences it sets into HS mode by removing the D+ Pull-up resistor and asserts HS terminations, reverts to HS default state and waits for end of reset.

- The channel has to be again set back to SE0 for atleast of 100 us upto a maximum of 500 us. Reset must wake a device from the Suspend state.

- The reset signaling is compatible with low-/full-speed reset.

After the device is successfully reset, the device must also respond successfully to device and configuration descriptor requests and return appropriate information.

Fig 3.5: VISIBLE DEVICE STATES

#### 4. Address

All USB devices use the default address when initially powered or after the device has been reset. Each USB device is assigned a unique address by the host after attachment or after reset. A USB device responds to requests on its default pipe whether the device is currently assigned a unique address or is using the default address. The host assigns a unique address depending on the hub to which the device is attached.

#### 5. Configured

Before a USB device's function may be used, the device must be configured. From the device's perspective, configuration involves correctly processing the request with a non-zero configuration value. After reading the device descriptors the host configures the device. Configuring a device or changing an alternate setting causes all of the status and configuration values associated with endpoints in the affected interfaces to be set to their default values.

#### Descriptor

- Descriptors are also defined that can be used to contain different information on the device. Control transfers provide the transport mechanism to access device descriptors and make requests of a device to manipulate its behavior.

- In order to determine the maximum packet size for the Default Control Pipe, the USB System Software reads the device descriptor. The host will read the first eight bytes of the device descriptor. The device always responds with at least these initial bytes in a single packet. After the host reads the initial part of the device descriptor, it is guaranteed to have read this default pipe's wMaxPacketSize field (byte 7 of the device descriptor). The host reads the device descriptor to determine what actual maximum data payload size this USB device's default pipe can use.

#### 6. Suspended

In order to conserve power, USB devices automatically enter the suspended state. When the device has observed no bus traffic for a specified period attached device must be prepared to suspend at any time they are powered. A USB device exits suspend mode when there is bus activity. A USB device may also request the host to exit suspend mode or selective suspend by using electrical signaling to indicate remote wakeup. The SOF token will occur once per (micro) frame to keep full-/high-speed devices from suspending.

While in the Suspend state, a device must continue to provide power to its D+ (full-/high-speed) or D- (low-speed) pull-up resistor to maintain an idle so that the upstream hub can maintain the correct connectivity status for the device. When a device operating in high-speed mode detects that the data lines have been in the high-speed idle state for at least 3.0 ms, it must revert to the full-speed configuration no later than 3.125 ms after the start of the idle state. No earlier than 100us and no later than 875 us after reverting to full-speed, the device must sample the state of the line. If the state is a full-speed J, the device continues with the suspend process. SE0 would have indicated that the downstream facing port was driving reset, and the device would have gone into the High-speed Detection Handshake. When the resume occurs, the device or host transceiver must revert to high-speed without the need for a reset.

#### Resume

Resume signaling is used by the host or a device to bring a suspended bus segment back to the active condition. Hubs play an important role in the propagation and generation of resume signaling. It must send the resume signaling for at least 20 ms and then end the resume signaling in one of two ways, depending on the speed at which its port was operating when it was suspended. If the port was in low-/full-speed when suspended, the resume signaling must be ended with a standard, low-speed EOP (two low-speed bit times of SE0 followed by a J). If the port was operating in high-speed when it was suspended, the resume signaling must be ended with a transition to the high-speed idle state.

#### Remote wakeup

Remote wakeup allows a suspended USB device to signal a host that may also be suspended. This notifies the host that it should resume from its suspended mode, if necessary, and service the external event that triggered the suspended USB device to signal the host. If a device supports remote wakeup, it must also allow the capability to be enabled and disabled using the standard USB requests. The device can signal the system to resume operation if its remote wakeup capability has been enabled by the USB System Software. The remote wakeup device must hold the resume signaling for at least 1ms but for no more than 15ms.

#### **3.4 OTG Specification**

#### 3.4.1 Introduction [2]

This section is used to describe the feature requires for an ordinary device to become an On-The-Go device which is capable of initiating a new session from a session end state and also negotiate with the host to become host. An ordinary device can be connected to an OTG capable device and data can be transferred as the ordinary USB 2.0 except with low-speed transactions. In addition to being fully compliant USB2.0 device, an OTG device must include the following features and characteristics

- A limited Host capability

- Full-speed operation as a device

- Full-speed support as a Host

- Session Request Protocol

- Host Negotiation Protocol

- One, and only one connection, a Mini-AB receptacle

- Minimum current output on Vbus.

The USB 2.0 specification defines the following connector pairs:

- Standard-A plug and receptacle for the host;

- Standard-B plug and receptacle for the peripheral; and

- Min-B plug and receptacle as alternative connectors for the peripheral.

The OTG supplement defines the following connector components:

- Mini-A plug,

- Mini-A receptacle, and

- Mini-AB receptacle.

The Mini-AB receptacle accepts either a Mini-A plug or a Mini-B plug.

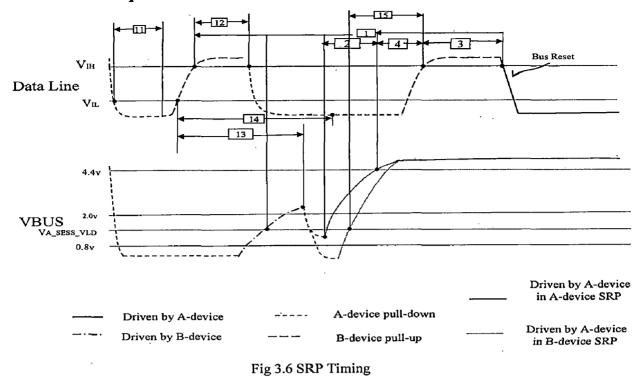

#### 3.4.2 Session Request Protocol

Purpose: In order to conserve power, an A-device is allowed to leave the VBUS turned off when the bus is not being used. If the B-device wants to use the bus when VBUS is turned off, then it requires some way of requesting the A-device to supply power on VBUS.

SRP is to be used as follows: An OTG device is required to respond to SRP if it ever turns off VBUS while an A-plug is inserted. An OTG device that keeps VBUS turned on whenever an A-plug is inserted will never have a need to respond to SRP.

Methods used by an OTG device: There are 2 methods called "data-line passing" and "Vbus pulsing" which a B-device uses to request the A-device begin session which is called Session Request Protocol.

#### **Initial Conditions:**

1. The B-device may not attempt to start a new session until it has determined that the A-device should have detected the end of the previous session. The A-device detects the end of a session by sensing that Vbus has dropped below its session valid threshold.

2. The B-device must detect that both the D+ and D- data lines must have been low (SE0) for atleast Tb\_se0\_srp min. This ensures that the A-device has detected a disconnect condition from the device.

These initial conditions define the period after which the A-device will properly recognize SRP from the B-device. When the above conditions satisfy any previous session on the A-device is over and a new session may start.

**Data-line Pulsing**: To indicate a request for a new session using the data-line pulsing SRP, the B-device waits until the initial conditions are met and then turns on its data line pull-up resistor D+ for a period within the range specified by Tb\_data\_pls. The duration of such a data line pulse is sufficient to allow the A-device to reject spurious voltage transients on the data lines.

**Vbus Pulsing:** The B-device drives Vbus anytime after the initial conditions are met and data line pulsing has concluded. Vbus is driven for a period that is long enough, max to be charged to Vb\_otg\_out min and will not be charged above Vb\_hst\_out max. There are 2 scenarios that a B-device could encounter when pulsing Vbus to initiate SRP. In one scenario, the B-device is connected to an A-device that responds to the Vbus pulsing SRP, where the B-device can drive Vbus above the A-device session valid threshold in order to wake up the A-device. When driving such an Adevice, the B-device shall ensure that Vbus goes above Vb\_otg\_out min, but does not exceed Vb\_otg\_out max. In second scenario, the B-device is attached to a standard host; the B-device shall not drive Vbus above Vb\_hst\_out max. This insures that no damage is done to standard hosts that are not designed to withstand a voltage externally applied to Vbus.

**Duration of SRP**: The maximum time allowed for the B-device to complete all of its SRP initiation activities is Tb\_srp\_init max. The SRP activities include all those activities that transpire while the B-device is not monitoring the state of the Vbus.

Response time of A-device: The A-device may be designed to respond to either of the methods of SRP. After initiating SRP, the B-device is required to wait at least Tb\_srp\_fail min for the A-device to respond, before informing the user that the communication attempt has failed. For this reason, it is recommended that the A-device is to turn on Vbus and generate a bus reset.

#### 3.4.3 Host Negotiation Protocol [2]

HNP is used to transfer control of a connection from the default host (A-device) to default peripheral (B-device). This is accomplished by having the A-device condition the B-device to be able to take control of the bus, and then having the A-device present an opportunity for the B-device to take control.

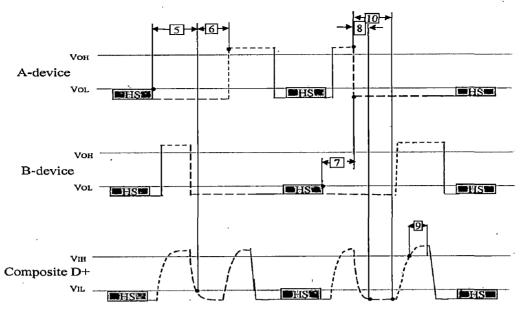

Fig 3.7 Timing Diagram of the HNP for HS devices

The sequence of events for HNP as observed on the USB, are as shown in above figure

- A-device finishes using bus and stops all bus activity (i.e., suspends the bus).

- B-device detects that bus is idle for more than Ta\_aidl\_bdis min and begins HNP by turning off pull-up on D+. This allows the bus to discharge to the SE0 state. If the bus was operating in HS mode, the B-device will first enter the full-speed mode and turn on its D+ pull-up resistor for atleast Tb\_fs\_bdis min before turning off its pull up to start the HNP sequence.

- The A-device detects the SE0 on the bus and recognizes this as a request from the B-device to become Host. The A-device responds by turning on its D+ pull-up within Ta bdis acon max of first detecting the SE0 on the bus.

- After waiting long enough to insure that the D+ line cannot be high due to the residual effect of the B-device pull-up, the B-device sees that the D+ line is high and D- line is low. This indicates that the A-device has recognized the HNP request from the B-device. The B-device becomes Host and asserts bus reset within Tb\_acon\_bse0 max to start using the bus.

- When the B-device completes using the bus, it stops all the bus activity.

- A-device detects lack of bus activity for more than Ta\_bidl\_adis min and turns off its D+ pull-up. If the A-device has no further need to communicate with the B-device, the A-device may turn off Vbus and end the session.

- B-device turns on its pull-up.

• After waiting long enough to insure that the D+ line cannot be high due to the residual effect of the A-device pull-up, the A-device sees that the D+ line is high(and D- line is low) indicating that the B-device is signaling a connect and is ready to respond as a peripheral. The A-device becomes host and asserts bus reset to start using the bus.

The timers in this section are defined in appendix.

## 3.5 USB 2.0 Transceiver Macrocell Interface (UTMI) Specification 3.5.1 Introduction [3]

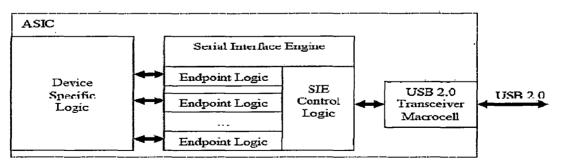

High volume USB 2.0 devices will be designed using ASIC technology with embedded USB 2.0 support. For full-speed USB devices the operating frequency was low enough to allow data recovery to be handled in a vendors VHDL code, with the ASIC vendor providing only a simple level translator to meet the USB signaling requirements. Today's gate arrays operate comfortably between 30 and 60MHz. With USB 2.0 signaling running at hundreds of MHz, the existing design methodology must change. As operating frequencies go up it becomes more difficult to compile VHDL code without modification. This section defines the USB 2.0 Transceiver Macrocell Interface (UTMI) and many operational aspects of the USB 2.0 Transceiver Macrocell (UTM). The intent of the UTMI is to accelerate USB 2.0 peripheral development. ASIC vendors and foundries will implement the UTM and add it to their device libraries. Peripheral and IP vendors will be able to develop their designs, insulated from the high-speed and analog circuitry issues associated with the USB 2.0 interface, thus minimizing the time and risk of their development cycles. There are assumed to be three major functional blocks in a USB 2.0 peripheral ASIC design: the UTM, the Serial Interface Engine (SIE), and the Device specific logic.

Fig 3.8 ASIC Functional Blocks

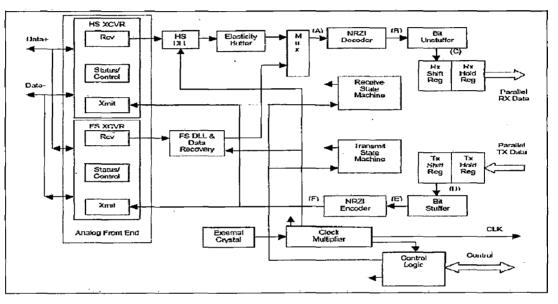

#### 3.5.2 USB 2.0 Transceiver Macrocell (UTM):

This block handles the low level USB protocol and signaling. This includes features such as data serialization and deserialization, bit stuffing and clock recovery and synchronization. The primary focus of this block is to shift the clock domain of the data from the USB 2.0 rate to one that is compatible with the general logic in the ASIC.

Some key features of the USB 2.0 Transceiver are:

- Eliminates high speed USB 2.0 logic design for peripheral developers.

- Standard Transceiver interface enables multiple IP sources for USB 2.0 SIE

VHDL.

Fig 3.9: UTM Functional Block Diagram

- Supports 480 Mbps "High Speed" (HS)/ 12 Mbps "Full Speed" (FS), FS Only and "Low Speed" (LS) Only 1.5 Mbps serial data transmission rates.

- Utilizes 8-bit parallel interface to transmit and receive USB 2.0 cable data.

- SYNC/EOP generation and checking.

- High Speed and Full Speed operation to support the development of "Dual Mode" devices.

- Data and clock recovery from serial stream on the USB.

- Bit-stuffing/unstuffing, bit stuff error detection.

- Holding registers to stage transmit and receive data.

- Logic to facilitate resume signaling.

- Logic to facilitate wake up and suspend detection.

26

小小野

- Ability to switch between FS and HS terminations/signaling.

- Single parallel data clock output with on-chip PLL to generate higher speed serial data clocks.

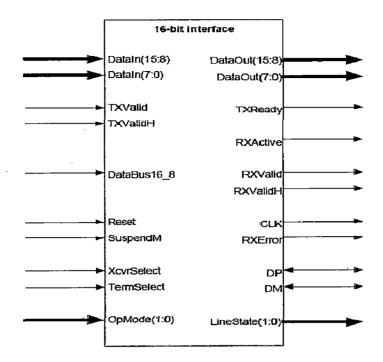

Fig 3.10: UTMI INTERFACE SIGNALS with respect to PHY

#### 3.5.3 System Interface Signals with Description

Table 3.7 UTMI Signals

| Name       | Directi<br>on | Active<br>Level | Description                                            |

|------------|---------------|-----------------|--------------------------------------------------------|

| CLK Output |               | Rising-         | This output is used for clocking receive and transmit  |

|            |               | Edge            | parallel data.                                         |

|            |               |                 | 60 MHz HS/FS, with 8-bit interface                     |

|            |               |                 | 30 MHz HS/FS, with 16-bit interface                    |

|            |               |                 | 48 MHz FS Only, with 8-bit interface                   |

|            |               |                 | 6 MHz LS Only, with 8-bit interface                    |

| Reset      | Input         | High            | Reset all state machines in the UTM.                   |

| XcvrSelect | Input         | N/A             | This signal selects between the FS and HS transceivers |

|            |               |                 | 0: HS transceiver enabled                              |

|            |               |                 | 1: FS transceiver enabled                              |

|            |               |                 | This signal is not provided in FS Only and LS Only     |

|            |               |                 | transceiver implementations.                           |

|            |        |      | · · · · · · · · · · · · · · · · · · ·                   |  |  |  |

|------------|--------|------|---------------------------------------------------------|--|--|--|

| TermSelect | Input  | N/A  | Signal selects between the FS and HS terminations       |  |  |  |

|            |        |      | 0: HS termination enabled                               |  |  |  |

|            |        |      | 1: FS termination enabled                               |  |  |  |

|            |        |      | This signal is not provided in FS Only and LS Only      |  |  |  |

|            |        |      | transceiver implementations.                            |  |  |  |

| SuspendM   | Input  | Low  | Places the Macrocell in a mode that draws minimal       |  |  |  |

|            |        |      | power from supplies.                                    |  |  |  |

|            |        |      | 0: Macrocell circuitry drawing suspend current          |  |  |  |

|            |        |      | 1: Macrocell circuitry drawing normal current           |  |  |  |

| LineState  | Output | N/A  | These signals reflect the current state of the single   |  |  |  |

| (0-1)      |        |      | ended receivers.                                        |  |  |  |

|            |        |      | DM[1] DP[0] Description                                 |  |  |  |

|            |        |      | 0 0 0: SE0                                              |  |  |  |

|            |        |      | 0 1 1: 'J' State                                        |  |  |  |

|            |        |      | 1 0 2: 'K' State                                        |  |  |  |

|            |        |      | 1 1 3: SE1                                              |  |  |  |

| OpMode     | Input  | N/A  | These signals select between various modes:             |  |  |  |

| (0-1)      |        |      | [1] [0] Description                                     |  |  |  |

|            | 1      | ł    | 0 0 0: Normal Operation                                 |  |  |  |

|            |        |      | 0 1 1: Non-Driving                                      |  |  |  |

|            |        |      | 1 0 2: Disable Bit Stuffing and NRZI encoding           |  |  |  |

| 1          |        |      | 1 1 3: Reserved                                         |  |  |  |

| Databus16_ | Input  | High | Set for 16- bit data bus.                               |  |  |  |

| 8          |        |      |                                                         |  |  |  |

| DP         | Bidir  | N/A  | USB data pin Data+                                      |  |  |  |

| DM         | Bidir  | N/A  | USB data pin Data-                                      |  |  |  |

| DataIn0-7  | Input  | N/A  | 8-bit parallel USB data input bus.                      |  |  |  |

|            |        |      | When DataBus16_8 = 1 this bus transfers the low byte    |  |  |  |

|            |        |      | of 16-bit transmit data.                                |  |  |  |

|            |        |      | When DataBus16_8 = 0 all transmit data is               |  |  |  |

|            |        |      | Transferred over this bus.                              |  |  |  |

| DataIn8-15 | Input  | N/A  | An 8-bit parallel USB data input bus that transfers the |  |  |  |

| Datamo-15  | PP     |      |                                                         |  |  |  |

|            |        |      | only valid when $DataBus16_8 = 1$ .                      |

|------------|--------|------|----------------------------------------------------------|

| TXValid    | Input  | High | Indicates that the DataIn bus is valid. The assertion of |

|            |        |      | TXValid initiates SYNC on the USB. The negation of       |

|            |        |      | TXValid initiates EOP on the USB.                        |

| TXValidH   | Input  | High | When DataBus16_8 = 1, this signal indicates that the     |

|            |        |      | DataIn (8-15) bus contains valid transmit data.          |

| TXReady    | Output | High | If TXValid is asserted, the SIE must always have data    |

|            |        |      | available for clocking in to the TX Holding Register     |

| ·          |        |      | on the rising edge of CLK.                               |

| DataOut0-7 | Output | N/A  | 8-bit parallel USB data output bus. When                 |

|            |        |      | DataBus16_8 = 1 this bus transfers the low byte of 16-   |

|            | 1      |      | bit receive data. When DataBus16_8 = 0 all receive       |

|            |        |      | data is transferred over this bus.                       |

| DataOut8-  | Output | N/A  | An 8-bit parallel USB data output bus that transfers     |

| 15         |        |      | the high byte of 16-bit receives data. These signals are |

|            |        |      | only valid when $DataBus16_8 = 1$ .                      |

| RXValid    | Output | High | Indicates that the DataOut bus has valid data. The       |

|            |        |      | Receive Data Holding Register is full and ready to be    |

|            |        |      | unloaded. The SIE is expected to latch the DataOut       |

|            |        |      | bus on the clock edge.                                   |

| RXValidH   | Output | High | When $DataBus16_8 = 1$ this signals indicates that the   |

|            | .      |      | DataOut (8-15) bus is presenting valid receive data.     |

| RXActive   | Output | High | Indicates that receive state machine has detected        |

|            |        |      | SYNC and is active. RXActive is negated after a Bit      |

|            |        |      | Stuff Error or an EOP is detected.                       |

| RXError    | Output | High | 0 Indicates no error.                                    |

|            |        |      | 1 Indicates that a receive error has been detected.      |

|            |        |      | If asserted, it will force the negation of RXValid on    |

|            |        |      | the next rising edge of CLK                              |

## 3.5.4 Data Receiving and Transmitting

- RXActive and RXValid are sampled on the rising edge of CLK.

- The receiver is always looking for SYNC.

- The Macrocell asserts RXActive when SYNC is detected (Strip SYNC state).

- The Macrocell negates RXActive when an EOP is detected (Strip EOP state).

- When RXActive is asserted, RXValid will be asserted if the RX Holding Register is full.

- RXValid will be negated if the RX Holding Register was not loaded during the previous byte time.

- This will occur if 8 stuffed bits have been accumulated.

- The SIE must be ready to consume a data byte if RXActive and RXValid are asserted (RX Data state).

- In FS mode, if a bit stuff error is detected then Receive State Machine will negate RXActive and RXValid.

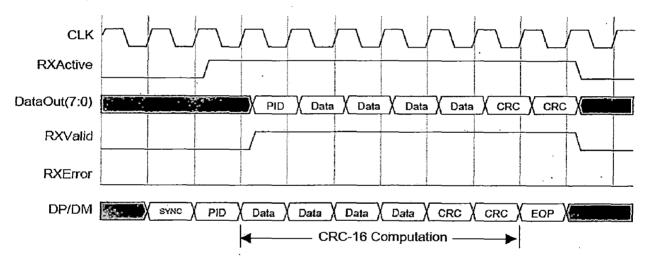

Fig 3.11: Receive Timing for Data Packet (with CRC-16)

Transmit must be asserted to enable any transmissions.

- The SIE asserts TXValid to begin a transmission.

- The SIE negates TXValid to end a transmission.

- After the SIE asserts TXValid it can assume that the transmission has started when it detects TXReady asserted.

- The SIE assumes that the UTM has consumed a data byte if TXReady and TXValid are asserted.

- The SIE must have valid packet information (PID) asserted on the DataIn bus coincident with the assertion of TXValid. Depending on the UTM

implementation, TXReady may be asserted by the Transmit State Machine as soon as one CLK after the assertion of TXValid.

- TXValid and TXReady are sampled on the rising edge of CLK.

- The Transmit State Machine does NOT automatically generate Packet ID's (PIDs) or CRC. When transmitting, the SIE is always expected to present a PID as the first byte of the data stream and if appropriate, CRC as the last bytes of the data stream.

- The SIE must use LineState to verify a Bus Idle condition before asserting TXValid state.

The SIE negates TXValid to complete a packet. Once negated, the Transmit State Machine will never reassert TXReady until after the EOP has been loaded into the Transmit Shift Register. Note that the UTM Transmit State Machine can be ready to start another packet immediately, however the SIE must conform to the minimum inter-packet delays identified in the USB 2.0 Specification.

Fig 3.12: Transmit Timing for a Data packet

## **3.6 UTMI+ Specification**

## 3.6.1 Introduction [4]

**Purpose:** The existing UTMI specification describes an interface only for USB2.0 peripherals. The intention of this UTMI+ specification is to extend the UTMI specification to standardize the interface for USB2.0 hosts and USB2.0 OTG peripherals. The UTMI+ specification defines and standardizes the interoperability characteristics with existing USB2.0 hosts and peripherals. Any transceiver core that has an interface compliant with UTMI+, has all signals compliant with UTMI. A transceiver core with UTMI+ interface can be used for USB2.0 peripheral, host or On-the-Go device designs that support LS, FS and HS traffic.

Additional signals for UTMI+: USB OTG peripherals have some additional capabilities and therefore some new signals need to be implemented.

1. A USB OTG dual role peripheral needs to be capable to distinguish between a mini-A and mini-B plug.

2. A USB OTG peripheral has to know if Vbus is below or above a certain voltage level.

Fig 3.13: UTMI+ Interface with respect to PHY

3. A USB OTG peripheral must be able to drive Vbus and charge or discharge Vbus.

4. A USB OTG dual role peripheral needs to be able to switch the pull-up resistor on DP and the pull-down resistor on both DP and DM.

5. The downstream facing port of a host controller must have 15 k Ohm pull-down resistors on both DP and DM lines.

6. The host controller must be able to detect disconnect of a peripheral. This is possible for a FS peripheral by using LineState.

Therefore an additional signal needs to be implemented. To make the design of the digital SIE easier, this new disconnect signal will be used in both speeds (HS/FS) to indicate if there is a device connected or not.

# 3.6.2 UTMI + signals other than UTMI

| NAME DIRECTION A        |                     | ACTIVE          | DESCRIPTION                                        |  |  |

|-------------------------|---------------------|-----------------|----------------------------------------------------|--|--|

|                         |                     | STATE           |                                                    |  |  |

| The id sign             | al is indicating th | he state of the | ID pin on the USB mini receptacle                  |  |  |

| IdPullup                | Input               | Low             | Signal that enables the sampling of the analog     |  |  |

|                         |                     |                 | Id line.                                           |  |  |

|                         |                     |                 | 0b: Sampling of Id pin is disabled.                |  |  |

|                         |                     |                 | 1b: Sampling of Id pin is enabled.                 |  |  |

| IdDig                   | Output              |                 | Indicates whether the connected plug is a mini-    |  |  |

|                         |                     |                 | A or B. This is valid when IdPullup is set to      |  |  |

| -                       |                     |                 | 1b.                                                |  |  |

|                         |                     |                 | 0b : connected plug is a mini-A                    |  |  |

|                         |                     |                 | 1b : connected plug is a mini-B                    |  |  |

| These are t             | he signals which    | indicate the I  | Link layer about the Strength of the Vbus.         |  |  |

| AValid                  | Output              | High            | Indicates if the session for an A-peripheral is    |  |  |

|                         |                     |                 | valid $(0.8V < Vth < 2V)$ .                        |  |  |

|                         |                     |                 | 0b: Vbus < 0.8V $1b: Vbus > 2V$                    |  |  |

| BValid                  | Output              | High            | Indicates if the session for a B-peripheral is     |  |  |