# IMPLEMENTATION OF DIGITAL DOWN CONVERTER FOR SOFTWARE RADIO

# **A DISSERTATION**

Submitted in partial fulfillment of the requirements for the award of the degree

\_of \_\_\_\_

MASTER OF TECHNOLOGY

. .

in

ELECTRONICS AND COMMUNICATION ENGINEERING (With Specialization in Communication Systems)

# STEERINGTOD THE ALL TH

DEPARTMENT OF ELECTRONICS AND COMPUTER ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE-247 667 (INDIA)

**JUNE, 2007**

### **CANDIDATE'S DECLARATION**

I hereby declare that the work, which is presented in this project report, entitled "IMPLEMENTATION OF DIGITAL DOWN CONVERTER FOR SOFTWARE RADIO", being submitted in partial fulfillment of the requirements for the award of the degree of MASTER OF TECHNOLOGY with specialization in COMMUNICATION SYSTEMS, in the Department of Electronics and Computer Engineering, Indian Institute of Technology, Roorkee is an authentic record of my own work carried out from July 2006 to June 2007, under guidance and supervision of Dr. D. K. MEHRA, Professor, Department of Electronics and Computer Engineering, Indian Institute of Technology, Roorkee.

The results embodied in this dissertation have not submitted for the award of any other Degree or Diploma.

Date: 29 Jun 2007 Place: Roorkee

LT COL A P VERMA

### CERTIFICATE

This is to certify that the statement made by the candidate is correct to the best of my knowledge and belief.

Date: 29.6.07 Place: Roorkee

Brochera

Dr. D. K. MEHRA Professor, E & C E Department Indian Institute of Technology, Roorkee Roorkee – 247 667, (INDIA)

### ACKNOWLEDGEMENTS

It is my privilege and pleasure to express my profound sense of respect, gratitude and indebtedness to my guide, **Dr. D.K. Mehra**, Professor, Department of Electronics and Computer Engineering, Indian Institute of Technology, Roorkee, for his inspiration, guidance, constructive criticisms and encouragement throughout this dissertation work.

I would like to thank **Ms Prerana Gupta**, Ph.D. student, for sharing her knowledge and for her constant support during this course of dissertation work.

Thanks are due to the Lab staff Signal Processing Lab, Department of electronics and Computer Engineering, IIT Roorkee for providing necessary facilities.

I am greatly indebted to all my friends, who have graciously applied themselves to the task of helping me with ample morale support and valuable suggestions. Finally, I would like to extend my gratitude to all those persons who directly or indirectly helped me in the process and contributed towards this work.

•

Lt Col A P Verma

The idea of software radio requires an expansion of Digital Signal Processing (DSP) towards the antenna. Hence, for converting the received signal to baseband, the need of efficient high speed digital down converters (DDC) arises. DDC performs the frequency translation necessary to convert the high sample rates down to lower sample rates for further and easier processing. It is identified as one of the 'critical functionalities' because it has to run at a relative high sample rate, and has to provide high resolution.

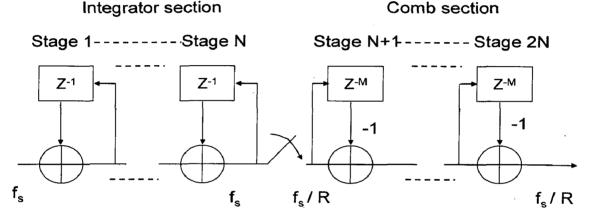

For this purpose, a class of digital linear phase finite impulse response (FIR) filters for decimation (sampling rate decrease) is proposed. They require no multipliers and use limited storage making them an economical alternative to conventional implementations for certain applications. A digital filter in this class consists of cascaded integrator-comb (CIC) stages operating at a high sampling rate and an equal number of comb stages operating at a low sampling rate.

Since their inception, CIC filters have become an important building block for DSP systems. They have found a particular niche in digital transmitters and receivers. They are currently used in highly integrated chips from Intersil, Graychip, Analog Devices, as well as other manufacturers and custom designs.

# CONTENTS

| CANDIDATE'S DECLARATION |     |                                                    |            |  |  |  |  |

|-------------------------|-----|----------------------------------------------------|------------|--|--|--|--|

| ACKNOWLEDGEMENTS        |     |                                                    |            |  |  |  |  |

| ABSTRACT                |     |                                                    |            |  |  |  |  |

| 1                       | CHA | CHAPTER 1 INTRODUCTION                             |            |  |  |  |  |

|                         | 1.1 | SDR Architecture                                   |            |  |  |  |  |

|                         |     | 1.1.1 An Ideal Software Defined Radio Architecture | 4          |  |  |  |  |

|                         |     | 1.1.2 Hardware Architecture                        | 7          |  |  |  |  |

|                         |     | 1.1.3 Critical SDR Components                      | 8          |  |  |  |  |

|                         | 1.2 | Latest Trend                                       | 12         |  |  |  |  |

|                         | 1.3 | Future Trend                                       | 13         |  |  |  |  |

|                         | 1.4 | Statement of the Problem                           | 14         |  |  |  |  |

|                         | 1.5 | Organization of the Report                         | 14         |  |  |  |  |

| 2                       | CHA | CHAPTER 2 ELEMENTS OF SDR                          |            |  |  |  |  |

|                         | 2.1 | Main Blocks of SDR                                 |            |  |  |  |  |

|                         |     | 2.1.1 Intelligent Antenna Technology               | 16         |  |  |  |  |

|                         |     | 2.1.2 Programmable RF Modules                      | 18         |  |  |  |  |

|                         |     | 2.1.3 Digital Signal Processing Techniques         | 1 <b>9</b> |  |  |  |  |

|                         |     | 2.1.4 Interconnect Technology                      | 20         |  |  |  |  |

|                         | 2.2 | Digital-to-Analog/ Analog-to-Digital Conversion    |            |  |  |  |  |

|                         | 2.3 | Upconversion and Downconversion                    | 31         |  |  |  |  |

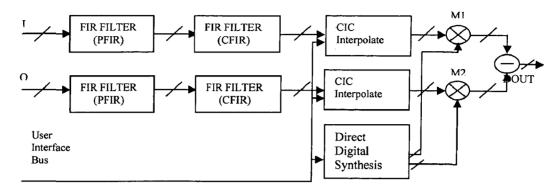

|                         |     | 2.3.1 Digital Upconverter (DUC)                    | 31         |  |  |  |  |

|                         |     | 2.3.1.1 CFIR and PFIR                              | 32         |  |  |  |  |

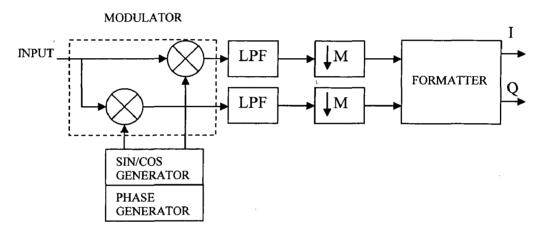

|        |   |     | 2.3.2          | Digital Down Converter (DDC)                                                                                                                                                                                                                                               | 32                                     |

|--------|---|-----|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|        | 3 | CHA | PTER           | 3 DIGITAL DOWNCONVERTER                                                                                                                                                                                                                                                    | 37                                     |

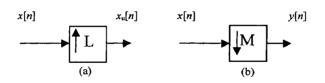

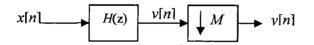

|        |   | 3.1 | Decin          | nation                                                                                                                                                                                                                                                                     | 37                                     |

|        |   |     | 3.1.1          | Multistage Design Of Decimator                                                                                                                                                                                                                                             | 38                                     |

|        |   |     | 3.1.2          | Poly Phase Realization                                                                                                                                                                                                                                                     | 39                                     |

|        |   |     | 3.1.3          | Computationally Efficient Interpolator-Decimator                                                                                                                                                                                                                           | 40                                     |

|        |   |     | 3.1.4          | Software Radio Issues in Cellular Base Stations                                                                                                                                                                                                                            | 42                                     |

|        |   | 3.2 | CIC I          | Decimation Filter                                                                                                                                                                                                                                                          | 44                                     |

|        |   |     | 3.2.1          | CIC Filter Description                                                                                                                                                                                                                                                     | 44 .                                   |

|        |   |     | 3.2.2          | Frequency Characteristics                                                                                                                                                                                                                                                  | 46                                     |

| •<br>• |   | 3.3 | Desig          | n Considerations for CIC Decimation Filter                                                                                                                                                                                                                                 | 49                                     |

|        |   |     | 3.3.1          | Register Growth                                                                                                                                                                                                                                                            | 49                                     |

|        |   |     | 3.3.2          | Truncation and Rounding                                                                                                                                                                                                                                                    | 53                                     |

|        | 4 | IMP | LEMEN          | TATION AND RESULTS                                                                                                                                                                                                                                                         | 57                                     |

|        |   | 4.1 | Gener          | al Description                                                                                                                                                                                                                                                             | 57                                     |

|        |   |     | 4.1.1          | PN Sequence                                                                                                                                                                                                                                                                | 58                                     |

|        |   |     | 4.1.2          | Vector Signal Generator (SMIQ02B)                                                                                                                                                                                                                                          | 59                                     |

|        |   |     |                | 4.1.2.1 Features of Vector Signal Generator                                                                                                                                                                                                                                | 59                                     |

|        |   |     |                |                                                                                                                                                                                                                                                                            |                                        |

|        |   |     |                | 4.1.2.2 Applications of Vector Signal Generator                                                                                                                                                                                                                            | 59                                     |

|        |   |     |                | <ul><li>4.1.2.2 Applications of Vector Signal Generator</li><li>4.1.2.3 RF Characteristics</li></ul>                                                                                                                                                                       | 59<br>60                               |

|        |   |     | 4.1.3          |                                                                                                                                                                                                                                                                            |                                        |

|        |   |     | 4.1.3<br>4.1.4 | 4.1.2.3 RF Characteristics                                                                                                                                                                                                                                                 | 60                                     |

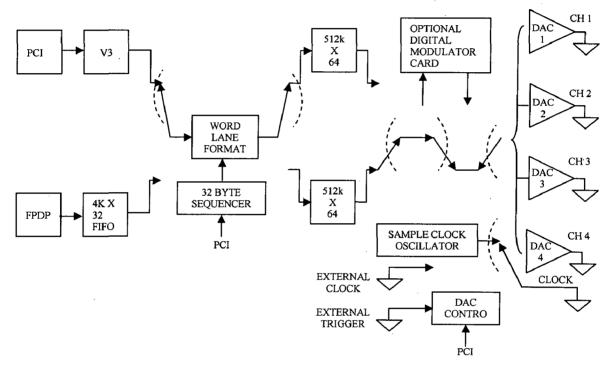

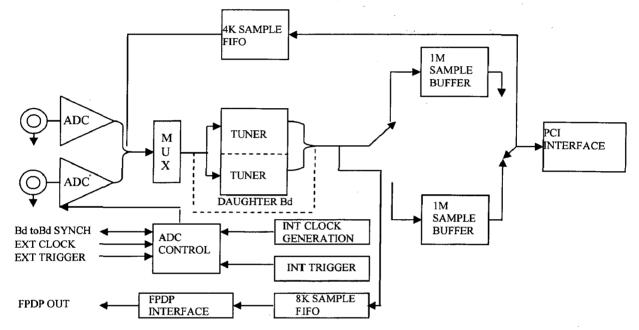

|        |   |     |                | 4.1.2.3 RF Characteristics<br>ICS-660 B Digital to Analog Converter                                                                                                                                                                                                        | 60<br>60                               |

|        |   |     |                | <ul><li>4.1.2.3 RF Characteristics</li><li>ICS-660 B Digital to Analog Converter</li><li>ICS 652 Analog to Digital Converter</li></ul>                                                                                                                                     | 60<br>60<br>61                         |

|        |   |     |                | <ul> <li>4.1.2.3 RF Characteristics</li> <li>ICS-660 B Digital to Analog Converter</li> <li>ICS 652 Analog to Digital Converter</li> <li>4.1.4.1 ADC section</li> </ul>                                                                                                    | 60<br>60<br>61<br>62                   |

|        |   |     |                | <ul> <li>4.1.2.3 RF Characteristics</li> <li>ICS-660 B Digital to Analog Converter</li> <li>ICS 652 Analog to Digital Converter</li> <li>4.1.4.1 ADC section</li> <li>4.1.4.2 Sampling Clock</li> </ul>                                                                    | 60<br>60<br>61<br>62<br>63             |

|        |   |     |                | <ul> <li>4.1.2.3 RF Characteristics</li> <li>ICS-660 B Digital to Analog Converter</li> <li>ICS 652 Analog to Digital Converter</li> <li>4.1.4.1 ADC section</li> <li>4.1.4.2 Sampling Clock</li> <li>4.1.4.3 FPDP interface</li> </ul>                                    | 60<br>60<br>61<br>62<br>63<br>63       |

|        |   |     | 4.1.4          | <ul> <li>4.1.2.3 RF Characteristics</li> <li>ICS-660 B Digital to Analog Converter</li> <li>ICS 652 Analog to Digital Converter</li> <li>4.1.4.1 ADC section</li> <li>4.1.4.2 Sampling Clock</li> <li>4.1.4.3 FPDP interface</li> <li>4.1.4.4 PCI bus interface</li> </ul> | 60<br>60<br>61<br>62<br>63<br>63<br>63 |

|     | 4.1.6                | Design of Chebyshev Filter                 | 66 |  |  |  |

|-----|----------------------|--------------------------------------------|----|--|--|--|

| 4.2 | Application Software |                                            |    |  |  |  |

| 4.3 | Results              |                                            |    |  |  |  |

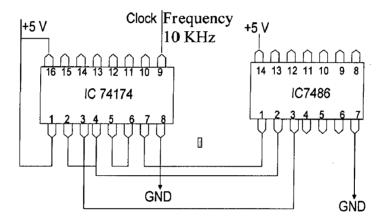

|     | 4.3.1                | PN Sequence Generation                     | 73 |  |  |  |

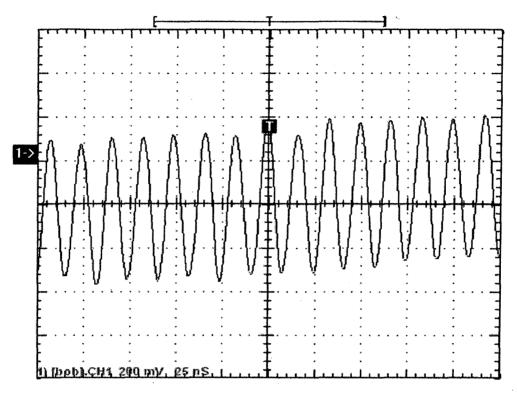

|     | 4.3.2                | Output of Vector Signal Generator SMIQ-02B | 73 |  |  |  |

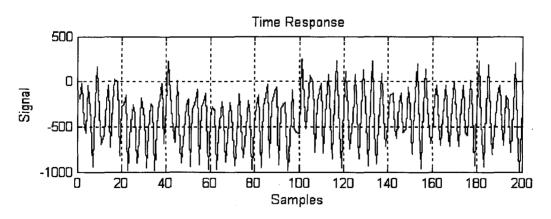

|     | 4.3.3                | Output of ICS-652 ADC card                 | 74 |  |  |  |

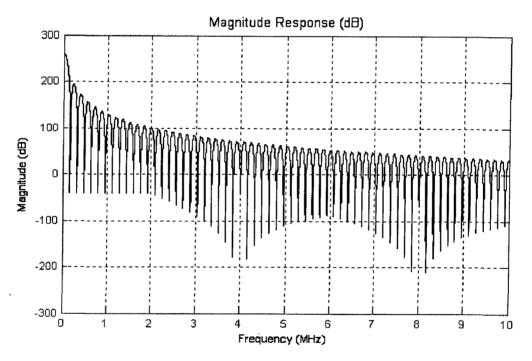

|     | 4.3.4                | CIC Decimation Filter                      | 75 |  |  |  |

|     | 4.3.5                | Chebyshev Low Pass Filter                  | 76 |  |  |  |

| 4.4 | Conclusion           |                                            |    |  |  |  |

|     | 4.4.1                | Nonrecursive CIC Decimation Filters        | 78 |  |  |  |

## REFERENCES

APPENDIX: Code Listing

·· -,

# CHAPTER 1 Introduction

The term "Software Radio" was coined by Joseph Mitola in 1991 to signal the shift from the hardware-intensive digital radios to the multi-band multimode software-based radios. It refers to the class of reprogrammable or reconfigurable radios. The Software Defined Radio (SDR) Forum defines the Ultimate Software Radio (USR) as a radio that accepts fully programmable traffic and control information and supports a broad range of frequencies, air-interfaces, and applications software. The user can switch from one airinterface format to another in milliseconds, use the Global Positioning System (GPS) for location, store money using smartcard technology, or watch a local broadcast station or receive a satellite transmission. A radio that includes a microprocessor or Digital Signal Processor (DSP) does not necessarily qualify as a software radio. However, a radio that defines in software its modulation, error correction, and encryption processes, exhibits some control over the RF hardware, and can be reprogrammed is clearly a software radio.

A good working definition of a software radio is a radio that is substantially defined in software and whose physical layer behavior can be significantly altered through changes to its software. The term software radio generally refers to a radio that derives its flexibility through software while using a static hardware platform. On the other hand, a soft radio denotes a completely configurable radio that can be programmed in software to reconfigure the physical hardware. In other words, the same piece of hardware can be modified to perform different functions at different times, allowing the hardware to be specifically tailored to the application at hand. Nonetheless, the term software radio is sometimes used to encompass soft radios as well. In short, software radios represent a paradigm shift from fixed, hardware-intensive radios to multi-band, multimode, software-intensive radios.

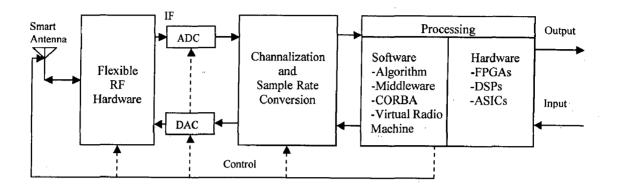

A model of a practical software radio is shown in Figure 1.1. The receiver begins with a smart antenna that provides a gain versus direction characteristic to minimize interference, multipath, and noise [1]. The smart antenna provides similar benefits for the transmitter. Most practical software radios digitize the signal as early as possible in the receiver chain while keeping the signal in the digital domain and converting to the analog

domain as late as possible for the transmitter using a Digital to Analog Converter (DAC). Often the received signal is digitized in the Intermediate Frequency (IF) band.

Figure 1.1: Practical Software Radio

Conventional radio architectures employ a super heterodyne receiver, in which the Radio Frequency (RF) signal is picked up by the antenna along with other spurious/unwanted signals, filtered, amplified with a Low Noise Amplifier (LNA), and mixed with a Local Oscillator (LO) to an IF. Depending on the application, the number of stages of this operation may vary. Digitizing the signal with an Analog to Digital Converter (ADC) in the IF range eliminates the last stage in the conventional model in which problems like carrier offset and imaging are encountered. When sampled, digital IF signals give spectral replicas that can be placed accurately near the baseband frequency, allowing frequency translation and digitization to be carried out simultaneously. Digital filtering (channelization) and sample rate conversion are often needed to interface the output of the ADC to the processing hardware to implement the receiver. Likewise, digital filtering and sample rate conversion are often necessary to interface the digital hardware that creates the modulated waveforms to the digital to analog converter.

Processing is performed in software using DSPs, Field Programmable Gate Arrays (FPGAs), or Application Specific Integrated Circuits (ASICs). The algorithm used to modulate and demodulate the signal may use a variety of software methodologies, such as middleware, e.g., Common Object Request Broker Architecture (CORBA), or virtual radio machines, which are similar in function to JAVA virtual machines. This forms a typical model of a software radio. The software radio provides a flexible radio

architecture that allows changing the radio personality, possibly in real-time, and in the process somewhat guarantees a desired Quality of Service (QoS). The flexibility in the architecture allows service providers to upgrade the infrastructure and market new services quickly. This flexibility in hardware architecture combined with flexibility in software architecture, through the implementation of techniques such as object-oriented programming and object brokers, provides software radio with the ability to seam-lessly integrate itself into multiple networks with widely different air and data interfaces. In addition, software radio architecture gives the system new capabilities that are easily implemented with software. For example, typical upgrades may include interference rejection techniques, encryption, voice recognition and compression, software-enabled power minimization and control, different addressing protocols, and advanced error recovery schemes. Such capabilities are well-suited for 3G and 4G wireless requirements and advanced wireless networking approaches. With radio functionality embedded and processed within software modules, there are numerous advantages associated with the SDR technology [2]. These are listed as under:

• *Flexibility & Upgradeability* is the greatest advantage on the implementation of SDR systems. SDR is based on open architecture and consists of a common, generic hardware platform, which allows for flexible installment of different software applications as required for signal transmission. These generic hardware platforms might be used for support of different protocols, services and products. The results are multiband, multimode radio systems able to conform to various protocols such as AMPS, TDMA, CDMA or GSM, which are the most, used air-interface standards currently

• *Interoperable* systems facilitate reduction of the time-to-market duration, since during transition phases to new technologies, legacy and new standards can coexist until the market's final acceptance of the new standard, enabling faster integration of new technologies and resolving the tyranny of legasets.

• Adaptability is faster migration towards new standards and technologies through programmability and reconfiguration. Especially toward the evolution of future standards supporting high-speed data services, such as GPRS, EDGE and 3G, software defined base stations will be of advantage enabling *integration* of multiple protocols and dynamic capacity shifting between services as required. The positive impact on future capital costs

for service providers through less required infrastructure deployment could eventually cause lower service charges for subscribers.

• Since the need for hardware modifications and replacements is being eliminated through SDR, provider equipment can be used for an extended period of time as insertion and reconfiguration of new standards becomes much easier, either through over-the-air uploads or directly onsite.

• Less fixed hardware components also means *less maintenance*, as well as the utilization of a generic hardware platform results in *cheaper equipment costs*. SDR also provides the advantage of promoting a more efficient use of the spectrum, for example, the requirement to provide backhaul through leased lines or fixed microwave facilities in traditional architectures presents a huge cost factor for wireless service providers, which gets eliminated by the use of SDR.

• SDR integrated base stations present *great opportunities* to both mobile and cellular services providers as well as subscribers. The same advantages will be available in mobile handsets, such as in cellular phones, PDAs, laptops or other handheld devices. This includes accommodation to multiple communication standards and air-interface protocols, migration capabilities to new emerging standards through software downloads and programmability through software modules. Numerous applications such as cellular phone services, web browsing, email, global positioning or video conferencing could be integrated into one system. Although these kinds of highly convergent systems are not even close to being realistic at the moment, the fact that SDR carries these great potentials makes it even more exiting to follow its future path.

### **1.1 SDR ARCHITECTURE**

### 1.1.1 An Ideal Software Defined Radio Architecture

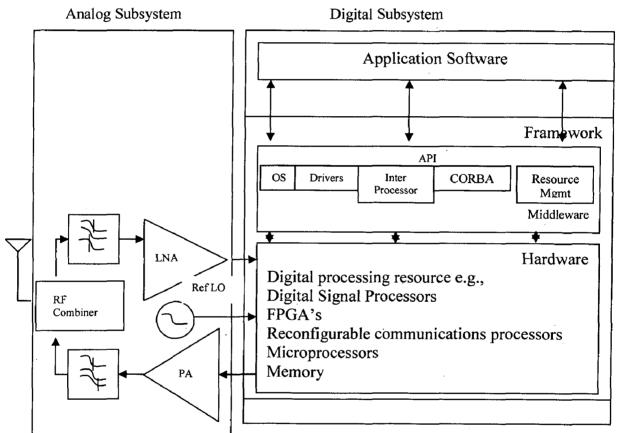

The ideal software radio architecture is shown in Figure 1.2. It consists of a digital subsystem & a simple analog subsystem [3]. The analog functions are restricted to those that cannot be performed digitally-that is antenna, RF filtering, RF combination, receive preamplification, transmit power amplification & reference frequency generation. The architecture pushes the analog conversion stage right up as close as possible to the antenna, in this case prior to the power amplifier (PA) in the transmitter and after the LNA in the receiver. The separation of carriers & up down frequency conversion to

baseband is performed by the digital processing resources. Similarly the channel coding & modulation functions are performed digitally at baseband by the same processing resources. Software for the ideal architecture is layered so that the hardware is completely abstracted away from the application software. A middleware layer achieve this functionality by wrapping up the hardware elements into objects and providing services that allow the objects to communicate with each other via a standard interface- for example, CORBA. Middleware includes the OS, hardware drivers, resource management, & other non-application-specific software. The combination of hardware & middleware is often termed a Frameware.

Figure 1.2: Ideal Software Defined Radio with Layered Hardware & Software

SDR architecture is based upon a high-level generic model with specific functional blocks connected via open interface standards recommendations. The software is implemented by controlling the characteristics of equipment/device subsystems through hierarchical and peer level modules that support scalability and flexible extensions of applications. Modularity is the key to successful implementation of

Implementation of Digital Down Converter for Software Radio, A Dissertation Report

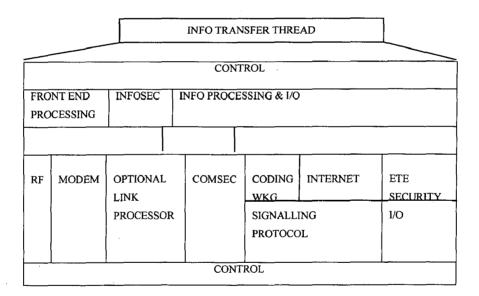

software applications within open systems. Between modules are defined interfaces that are subject to standardization. Within a module the developer is free to implement functionality in the most effective way. Figure 1.3 illustrates a high-level hierarchical functional model for SDR systems. Three views of increasing complexity are presented. The top-level view is a simple representation of an entire information transfer thread. The left side interface is the air interface. The right side interface is the wire side and user interface. The next level view identifies a fundamental ordered functional flow of four significant and necessary functional areas; Front end processing, Information security, Information processing, and Control. The diagrams and processes here are two-way devices i.e. send and receive. The functional model as shown in this figure does not show data or signal flow. These can be explained as follows:

Figure 1.3: Hierarchical Functional Model for Software Defined Radio

• Front End Processing- It is that functional area of the end user device that consists generically of the physical air (or propagation medium) interface, the front-end radio frequency processing, and any frequency up and down conversion that is necessary. Also, modulation/demodulation processing is contained in this functional block area.

6

• Information Security- It is employed for the purpose of providing user privacy, authentication, and information protection. In the commercial environment, this protection is specified by the underlying service standard while in the defense environment, this protection is of a nature that must be consistent with the various Governmental doctrines and policies in effect.

• **Content or Information Processing-** It is for the purpose of decomposing or recovering the embedded information containing data, control, and timing. Content processing and I/O functions map into path selection (including bridging, routing, and gateway), multiplexing, source coding (including vocoding, and video compression/expansion), signaling protocol, and I/O functions.

### 1.1.2 Hardware Architecture

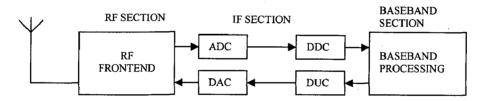

The SDR contains a number of basic functional blocks. The radio can be split into three basic blocks, namely the front end, the IF section and the base-band section as shown in the figure 1.4. Each of the sections undertakes different types of functions and therefore is likely to use different circuit technologies.

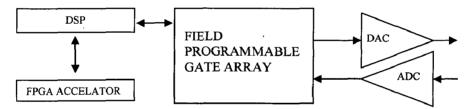

Figure 1.4: Block Diagram of Generic Software Defined Radio

• The front end section uses analogue RF circuitry and it is responsible for receiving and transmitting the signal at the operational frequency, coupling the radio to the antenna or its feeder. It also changes the signal to or from the intermediate frequency. Thus on the receive path the front end server is connected to the antenna input using matching circuitry to ensure the optimum signal transfer occurs. It then amplifies the signal and applies it to a mixer with a signal from a local oscillator to down-convert it to the intermediate frequency. On the transmit path the front end takes the signal from the IF, first up-converting it to the final frequency where it is amplified to the required level, passed through suitable matching circuitry to ensure the maximum power transfer and

then presented at the antenna connection to be routed to the antenna either directly or via a feeder.

The IF section performs the digital to and from analogue conversions. It also contains the processing that undertakes what may be thought of as the traditional radio processing elements, including filtering, modulation and demodulation and any other signal processing that may be required. On the receive path the signal enters the DAC where it is digitized and enters the Digital Down Converter (DDC), where the signal is processed and demodulated to provide the baseband signal for the baseband processor. Similarly on the transmit side the signal arrives from the baseband processor and is modulated onto the carrier and conditioned as required. It is then converted from its digital format to analogue using a digital to analogue converter. The DDC and DUC require significant levels of processing. This is required to perform all the processing on the actual signals in digital format. This processing must be achieved in real time for the system to be able to operate satisfactorily. As a result the processors are implemented in either stock DSPs or Application Specific Integrated Circuits (ASICs). In fact to achieve the full programmability and reconfigurability needed for a software defined radio the signal processors may be implemented as Field Programmable Gate Arrays (FPGAs). In this way the circuit can be totally reconfigured if needed.

• The final stage of the radio is the *baseband processor*. It is at this point that the digital data is processed, with protocols being accommodated and the data payload assembled or disassembled from the datastream. Although not as demanding as the DDC and DUC areas, with protocols becoming ever more complicated and demanding, the level of processing is increasing in these areas as well.

### 1.1.3 Critical SDR Components

It is inarguable that in an ideal setting, the digital conversion of the desired signal would happen immediately upon entry into the system, though numerous road blocks currently prevent a direct-to-digital scenario. There has been growing debate among experts over the most effective combination of ASIC, FPGA, and DSP to handle the steep system requirements for advanced wireless systems. All of these components are essential for operation, but the actual need for each component will be based upon needs assessment of the users. These can be further elaborated as follows:

1. The heart of the software defined radios rests in the Digital Signal *Processing* units. These components implement upper layer protocols in a real-time format, and are manipulated by onboard software, allowing for the interpretation of a variety of signals by simply activating the appropriate software. Using a complex series of algorithms, DSP chips perform functions like channel and source encoding/decoding, filtration, error checking, and modulation/demodulation procedures. Containing a high-speed processing block known as a MAC (Multiply and Accumulate), a DSP processes the signal by retrieving instructions and data from memory, performs requested operations, and stores the results back to memory. The major drawback of DSP units is that they lack the proper processing speeds required for wideband transmissions. To compensate for inadequate performance, some designers suggest that running two DSPs in parallel will result in sufficient function for SDR handsets, and can possibly accommodate the necessary encoding/decoding and symbol processing without the need of ASIC units.

Functions which are often used in wireless applications and are not supported by traditional DSPs are: complex arithmetic, division (such as needed for automatic gain control), coordinate rotation (useful for constellation-based algorithms in a receiver), and square root [4]. Done on a traditional DSP architecture, a combined division and square root operation requires 5N + 12 cycles for N-bit operands. However, coordinate rotation digital computer (CORD1C)-based approaches to these functions may provide significant speedup of execution.

2. *ASIC* performs signal downconversion, digital filtration, and performs at higher rates of speed than FPGAs. Traditionally smaller in size, ASIC chips are designed for specific purposes, and therefore, are not reprogrammable. This is almost a blessing in disguise, resulting in a dedicated device which has a far more efficient power requirement than general purpose processors. Due to the operation-specific nature of ASIC chips; each chip must be designed for a specific application, and can then be reproduced rather cost effectively.

3. *FPGAs* are completely programmable devices which can perform a variety of user-defined tasks including digital down-conversion, signal processing, and

9

filtration. Although FPGAs operate slower than ASIC circuits, in terms of embedded memory both are comparable devices. However, when it comes to logic, FPGAs only have a small fraction of the capacity that can be found in ASICs. Many advocate the use of FPGA chips in SDR applications since they can be implemented "off the shelf," unlike ASICs which need to be created for each specific product. It is suggested that FPGA chips can be integrated along side a DSP, handling a majority of operations; allowing the DSP to operate closer to the level of performance required for wideband applications by leaving only symbol processing to the DSP. Systems which contain both FPGA and DSP chips can deliver signal-processing capabilities ten times more efficiently than with a DSP alone, presenting the welcomed advantages in cost, power, and system footprint as shown in figure 1.5.

Figure 1.5: Hypothetical Combination of Microprocessors in SDR

4. *Configurable Computing Machine (CCM)* ensures the performance enhancement. The advent of software radios has brought a paradigm shift to radio design [5]. A multimode handset with dynamic reconfigurability has the promise of integrated services and global roaming capabilities. However, most of the work to date has been focused on software radio base stations, which do not have as tight constraints on area and power as handsets. Base station software radio technology progressed dramatically with advances in system design, adaptive modulation and coding techniques, reconfigurable hardware, A/D converters, RF design, and rapid prototyping systems, and has helped bring software radio handsets a step closer to reality. However, supporting multimode radios on a small handset still remains a design challenge. A configurable computing machine, which is an optimized FPGA with application-specific capabilities, shows promise for software radio handsets in optimizing hardware implementations for heterogeneous systems. Software radios began to obtain popularity largely in base stations rather than handsets. This is due to the fact that unlike handsets, base stations do not have stringent constraints on power, form factor, and weight. Moreover, when the technology was at its inception, base stations provided the perfect platform for experimenting and evaluating different radio designs. However, as the technology matures, software radio designs are migrating to handsets where their true potential can be realized. The additional constraints placed by handsets with limited resources pose one of the main design challenges.

An optimal software radio solution should be able to tune its hardware to the needs of the current system, thereby minimizing power and silicon area to achieve performance similar to an ASIC implementation. Since such optimal systems are still hard to develop; the designer's goal is to maximize the number of supported radio functions with a minimum amount of hardware. Hardware paging presents an elegant solution to this problem, by allowing algorithms to be implemented on physical hardware as needed. While DSPs and FPGAs provide different levels of reconfigurability and aid in implementing flexible designs, CCMs, the latest in reconfigurable technology, is the only class of processor that can currently provide real-time paging of algorithms on hardware, along with partial reconfigurability. Furthermore, in addition to supporting real-time hardware paging, correctly designed CCMs can provide performance enhancements. Extending the flexibility of software radios through the use of CCMs to alter the hardware can render the radio truly "soft." When compared to ASICs and DSPs, CCMs allow designers to achieve flexibility in hardware. CCMs have static hardware for frequently used cores, such as multiplication, filtering, or other communications- oriented algorithms, which result in efficient radio designs. CCMs attempt to customize FPGAs so that system flexibility is retained while taking advantage of the specific properties of communications-oriented cores. CCMs are regarded as extremely powerful processing engines with ASIC-like speeds, which can also be rapidly reconfigured. However, they are not ideally suited for control operations since they lack a microprocessor-like architecture with flexible event-driven operation. Since

control operations can be efficiently programmed on a DSP, CCMs will be most beneficial as co-processors rather than standalone processors. Software radio handsets require extremely flexible and efficient low power hardware. While DSPs and FPGAs provide reconfigurable alternatives for complex high-speed processing, the use of CCM cores can greatly enhance the performance by optimizing the hardware for the application. CCMs show promise in realizing handheld software radios, and with careful design and good simulation tools, it is possible to design CCMs optimized for mobile communications.

### **1.2 LATEST TREND**

Radio technology as we know it is undergoing sweeping changes [6]. Today, even with advancements in RF design and the powerful digital processing available, all radio receivers still use analog parts to tune the radio to a specific carrier frequency. But this is undergoing a change. The Federal Communications Commission (FCC), the SDR Forum and the radio industry are united in the pursuit of the ideal SDR. According to the FCC, "In a SDR, functions that were formerly carried out solely in hardware, such as the generation of the transmitted signal and the tuning and detection of the received radio signal, are performed by software that controls high-speed signal processors." The SDR Forum defines an SDR device as one that functions independently of carrier frequencies and can operate within a range of transmission protocol environments. But the SDR Forum goes a step further by defining the ideal SDR as one that has transceivers that perform upconversion and downconversion between baseband and the RF carrier itself exclusively in the digital domain, reducing the RF interface to a power amplifier in the transmit path, a low noise amplifier in the receive path, and little or no analog filtering. In this ideal radio, it is possible to upgrade or completely change the features by simply uploading new software. This ideal radio defined by the SDR Forum has, until recently, been unachievable due to the lack of very high-frequency RF to digital converters capable of converting carrier frequencies directly to digital data. Now new integrated circuit processes are offering higher speed and lower power. State-of-the art IC design is being applied to these new processes to enable RF to digital conversion directly on carrier

frequencies above 5 GHz. Recently, Vanu Inc. became the first company to successfully complete the FCC's certification process governing software-radio devices. The Vanu Software Radio consists entirely of software applications that support all of the GSM cellular base station functionality running on off-the-shelf servers with RF subsystem. This system can support multiple radio standards, protocols and frequencies on a single industry standard server. It allows modification of the RF planning and assignment of standards through remote software parameter changes. It supports upgrades to new standards through a software download. The availability of high-speed converters has made possible the implementation of true software-radio transmitters and receivers that avoid the use of passive components to tune and modulate/demodulate high-speed These converters, using conventional CMOS and advanced wireless signals. semiconductor and superconductor technologies have performance comparable to or better than conventional analog front-end circuits and enable tunerless architectures wireless transmitters and receivers. Next-generation devices promise to further exceed the performance of analog components enabling the extraction of weak signals in noisier and more interference-ridden environment.

### **1.3 FUTURE TREND**

Reconfigurability in radio development is not such a new technique [7]. Already during the 1980s reconfigurable receivers were developed for radio intelligence in the short wave range. These receivers included interesting features like automatic recognition of the modulation mode of a received signal or bit stream analysis. A *cognitive radio* (CR) is an SDR that additionally senses its environment, tracks changes, and reacts upon its findings. A CR is an autonomous unit in a communications environment that frequently exchanges information with the networks it is able to access as well as with other CRs. Formally, a Cognitive Radio is an intelligent wireless communication system that is aware of its surrounding environment (i.e., outside world), and uses the methodology of understanding-by-building to learn from the environment and adapt its internal states to statistical variations in the incoming RF stimuli by making corresponding changes in certain operating parameters (e.g., transmit-power, carrier-frequency, and modulation strategy) in real-time, with two primary objectives in mind:

• Highly reliable communications whenever and wherever needed;

13

• Efficient utilization of the radio spectrum.

Six key words stand out in this definition: awareness, intelligence, learning, adaptively, reliability, and efficiency. Implementation of this far-reaching combination of capabilities is indeed feasible today, because of the spectacular advances in digital signal processing, networking, machine learning, computer software, and computer hardware. In the years since Joseph Mitola coined the term "cognitive radio," there has been much speculation about how an intelligent, aware, adaptive, and learning radio could sweep away old ideas about spectrum access and spawn a new era in wireless communications. Cognitive radio researchers are making significant progress in the development of radios that can observe their environment, take action, and learn from the results. While the boundary between "adaptive" and "cognitive" is ill defined, real radio performance is moving toward Mitola's vision.

### **1.4** STATEMENT OF THE PROBLEM

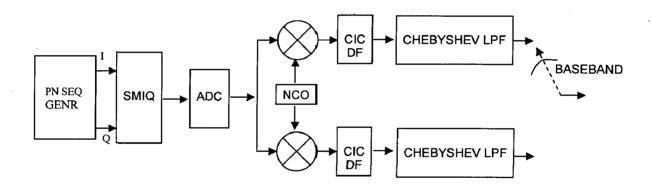

Today's continuously changing technology brings the need to build "futureproof" radios. If the functions that were formerly carried out by hardware can be performed by software, new functionality can be deployed on a radio by updating the software running on it. The aim of the present work is implementation of Digital Down Conversion for Virtual Radio. Vector Signal Generator is used for generating modulated signal, which is digitized using ADC card. This captured signal is then processed using software to recover the baseband signal.

### **1.5 ORGANIZATION OF THE REPORT**

This thesis is presented in four chapters and is organized as follows:

*Chapter 2* explains the various elements of the SDR, covering in detail the ADC/DAC, with due emphasis on Delta-Sigma type of ADC.

**Chapter 3** elucidates the decimation rate technique, the *Digital Downconverter* (DDC) that converts the received signal to baseband, a class of linear phase FIR filters called cascaded integrator-comb (CIC) filters that are used for decimation, and finally the *Low Pass Filter*, which is a *Chebyshev* Low Pass Filter used to filter out high frequency components.

**Chapter 4** entails the implementation of the dissertation work using the facilities available in the Signal Processing Lab. It also elucidates the results obtained thereafter and finally the conclusion at the end.

# CHAPTER 2 Elements of SDR

The choice of building blocks and communications infrastructure are the most critical part of any SDR for both commercial and military applications. They both share similar challenges towards implementation of a true SDR.

In this chapter, the focus is on the hardware technology aspect of the SDR. The main technical objective of a SDR is a versatile reconfigurable platform, which provides interoperability. As depicted in figure 1.1, the practical SDR diagram, the main blocks of a true SDR are namely: intelligent antenna, programmable RF modules, high-performance Digital-to-Analog (DAC) and Analog-to-Digital Converters (ADC), Digital Signal Processing (DSP) techniques/technology and the interconnect technology. In the following sections of the chapter, the current state of the technology and the trend for each of the five mentioned block is briefly reviewed and discussed.

### 2.1 MAIN BLOCKS OF SDR

As discussed above, SDR comprises of five main blocks. Each block has to provide a considerable amount of flexibility while maintaining performance. They are covered in detail as under:

### 2.1.1 Intelligent Antenna Technology

Antenna front-end can be split to the basic antenna element and the related array configuration and processing blocks. Today's antenna solutions for SDR systems are based on several separate antennas to cover a broad range of frequency. This is because, the traditional antenna design techniques limits the extent of application and performance of an antenna. In other words, since the antenna size is always proportional to the operating wavelength, a wideband antenna will be less performing and less cost effective than a narrowband antenna. Thus the main activities in this domain remain mainly in array processing blocks and techniques to make the antenna system more performing and intelligent. The word intelligent covers the very basic feature of frequency band selection and adaptation up to advance capabilities such as interference cancellation and mobile tracking. An ideal antenna for a SDR is a self-adapt, self-align and self-healing antenna, which is capable of complete adaptation to its required application and the transmission

environment. Self-adaptability is a capability that the antenna system would adjust its basic parameters such as gain according to the selected frequency band and required system gain of the application. As soon as the system is set up, self-alignment enables the antenna to direct itself based on the maximum signal reception with an aid provided by a telemetry data or a Global Positioning System (GPS). Self-healing can be defined as a feature that helps the system to combat any friendly or hostile interference by proper use of techniques such as array processing, beam-steering and even variable-polarization.

In order to fulfill the above-mentioned features, besides the required elegant signal processing techniques, high performance and flexible radiating elements are essential. Micro Electro-Mechanical System (MEMS) raises the hope for major breakthroughs in the field of broadband reconfigurable antenna design. For example, by employing MEMS, it is possible to change the operating frequency of a rectangular ring slot antenna electronically. In a square slot antenna, a good performance at a frequency is obtained, when the circumference of the ring is approximately one wavelength. By using MEMS switches, as shown in Figure 2.1, in order to reconfigure the antenna for a new frequency band, it is only required to switch in or out different slot elements. The main advantages of MEMS switch over PIN diode switch are low loss, high isolation and smaller size. They are all significant factors for an antenna system.

Figure 2.1: Application of MEMS switch for reconfigurable antenna

In current cellular systems with omnidirectional or sectored antennas, interference limits the choice of frequencies in each cell to one out of every seven. Preliminary analyses indicate that software-radio-based "Smart Antenna" appliqués can enhance the carrier to interference (C/I) ratio in both the forward and reverse link to allow frequency reuse of 3 to 1. Use of this type of a smart array represents a greater than 2 to 1 increase in capacity and supports a 3 to 1 increase in call arrival rate for the same probability of blocked calls [8]. As the demand for radio spectrum grows, the ability of sophisticated DSP algorithms to combat multipath fading and to reduce interference will become increasingly valuable as a means of adding capacity to cellular and PCS systems. In the

\*

### Chapter 2: Elements of SDR

future, software radios will be the technology of choice in an expanding array of mobile radio applications. Today, the real need is to make more voice channels available in a given geographic area in the finite spectrum allocated. When translating this operational need to a technical requirement for an antenna system, the need is not for a steerable "higher gain" array, but instead an array which can increase the C/I ratio at both the base station and the mobile terminal. If this can be achieved, then more RF channels can be added to the base stations in the area without driving the C/I below an acceptable limit. Suppose that the channels in a conventional system without an array have been allocated to maximize capacity subject to a minimum acceptable C/I. If the smart array is employed, the C/I will increase, allowing the addition of more channels until the C/I is again brought to a minimum acceptable level. By increasing the C/I of the desired signal for both the forward and reverse links, the smart array provides more channel capacity.

The antenna(s) of the software radio span multiple bands, with uniform shape and low losses to provide access to available service bands. In military applications, for example, a mobile terminal may need to employ VHF/UHF line of sight frequencies, UHF satellite communications, and HF as a backup mode. Switched access to such multiple bands requires octave bandwidth antennas and/or multiple antennas per band and an agile frequency reference in the RF Segment [9]. The relationship between interference cancellation capacity and the number of antenna elements varies. A single auxiliary element, for example, can reduce interference of a large number of interferers. Algorithms that reduce interference through non-spatial techniques can also reduce a large number of interferers with one or with no auxiliary antenna elements.

### 2.1.2 Programmable RF Modules

One of the employed techniques for existing SDR systems is to use a bank of RF modules to cover the entire frequency band [10]. By maturing the wideband synthesizer technology, low-noise high-performance semiconductor processes, very flexible RF modules are arising. Implementation of high performance RF devices with a high level of integration of circuits, including switches have been made possible due to low loss and compactness of MEMS technology. The moveable feature of MEMS devices allows dynamic adjustment of the component values. MEMS technology improves the performance and flexibility of several RF components such as:

Implementation of Digital Down Converter for Software Radio, A Dissertation Report

- Low phase noise Voltage Controlled Oscillators (VCO) by using MEMS-based high Q resonators

- Wideband varactors and phase shifters by using MEMS-based variable capacitors and switch-capacitor networks

- Tunable filters by employing MEMS-based variable reactive elements and switches.

The challenge for designing programmable bandpass filters remains to be resolved. They are essential in both transmitters and receivers, insuring efficient use of channel and high sensitivity. Bandpass filters are usually the most expensive items on the list for RF modules and at the same time the least flexible. A SDR implementation requires these elements to be either electronically configurable or to be stacked to forming a filter bank. Today most of SDR implementations rely on the latter.

Also, superconductive technology has enabled to implement tunable bandpass filters with ultra-sharp roll-off characteristics. The low loss nature of this process enables design and realization of multistage thin film filter with low insertion loss and broadband operation.

### 2.1.3 Digital Signal Processing Techniques

DSP is the principal enabling element of SDR. Embedded DSP algorithms in the processing engine are responsible to make all the promises of SDR come true. By employing an efficient DSP architecture and set of algorithms, proprietary waveforms and features can be implemented as the applications matures Among several DSP techniques used in SDR platform, sampling techniques, rate conversion and multirate processing have been instrumental in progress and development of DSP-based systems. Regular implementation choices are based on DSP-processors, ASICs, FPGAs as well as the emerging mixture of these technologies. The most effective combination of Application Specific Integrated Circuits (ASIC), Field Programmable Gate Arrays (FPGA), and Digital Signal Processors (DSP) are used to handle the steep system requirements for advanced wireless systems. All of these components are essential for operation, but the actual need for each component will be based upon needs assessment of the users. These are already discussed in 1.1.3 in detail.

### 2.1.4 Interconnect Technology

One of the main benefit or objective of the SDR is the ability to connect several independent building blocks to set-up a radio link. An open architecture system obliges a set of interface standards to be developed within framework of an interconnect technology. A successful interconnect approach has to address following critical issues:

- Leveraging open standards

- Addressing multiple protocols

- Meeting increasing speed and throughput requirements

- Connecting to traditional circuit networks.

Mainly, there are three main interconnect architecture: bus architecture, switch fabric architecture and tree architecture. These are briefly discussed as under:

- In *bus architecture*, a bus connects different processing modules. Usually, a high-speed data bus provides high-speed data transmission between the functional units, and a lower speed bus is employed for low rate control data transactions. Based on this architecture, at any time, only one functional unit can transmit data on the bus. In other words, bus is time shared between the functional units. Bus assignment is done by a bus arbitration blocks, which processes requests and sets the priority. Time division limits the bandwidth and also restricts the scalability of the interconnect bus architecture. A new version of PCI, called as PCI-X allows the bus to run up to 133 MHz at 64 bits bus to accommodate a peak data rate of 1 Gbyte/s, however this seems to be still not enough for some applications.

- In *switch fabric architecture*, there is an adapter in each functional unit that packages the data from the functional unit before being sent to the switch fabric. The principle of a switch fabric is similar to an IP or an ATM switch. Switch fabric technology has following advantages compared to the bus architecture:

- High scalability in both slot count and aggregate performance

- Flexibility in physical configuration and size

- Cost-effective, high availability designs with no single points of system failure

• Efficiently addressing the disparate needs of different traffic types and communication protocols.

However it should be noted that the use of switch fabric architecture in SDR calls for strict requirement and performance on the switch fabric in terms of throughput and packet delay.

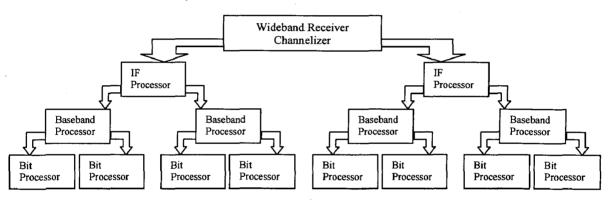

• In a wireless communication system, the product term of data rate by resolution bits becomes lower and lower as we move from RF to IF and baseband processing. This suggests architecture similar to a *tree*, where from the root node to the leaf node, the channel width becomes wider and wider as shown in figure 2.2. The tree architecture optimizes the use of interconnections and avoids providing interconnects between the blocks that do not require such provision. The main disadvantage of this architecture is its implementation and limited flexibility.

Figure 2.2: Tree Interconnect Architecture

### 2.2 DIGITAL-TO-ANALOG / ANALOG - TO- DIGITAL CONVERSION

SDR systems hinge on ADCs and DACs components. They have the unique tasks of conversion between analog to digital domain and vice versa. The flexibility of a SDR can be augmented significantly by pushing the converters closer to the antenna. Putting ADC closer to the antenna eliminates multiple stages of downconversion and analog filtering [11]. Traditional electronic converters are pushing the envelope to achieve more resolution and faster conversion rates. The receiver has always more complexity than the transmitter, the importance of operating at higher rates of conversions for ADCs is more

significant and thus has attracted more effort than DACs. The ever-increasing demand from applications such as broadband wireless communication and software radio are stimulating many innovative state-of-the-art ADC developments. Next generation transceiver operating with different standards necessitates the existence of a wide bandwidth and highly linear ADC. Currently, several projects dealing with the design and implementation of ADC architectures to provide the stringent requirements of the widebandwidth transreceivers are being developed. The ultimate transceiver target architecture is to perform immediately at the radio frequency (RF) the A/D conversion in order to process the signal completely in the digital domain. In this strategy the ADC should match both high linearity and wide bandwidth. A flash ADC with several GHz bandwidth and more than 6-bit resolution will be designed to meet this specification. The flash ADC is more suitable for base-station transceiver where the whole bandwidth needs to be converted. A different target ADC architecture that is more suitable for handheld devices in terms of power consumption is the bandpass sigma delta. The basic idea of  $\Sigma$ - $\Delta$  ADC is to trade sampling speed for number of bits. This is discussed at length subsequently. Here we describe here four major circuit architectures used in A/D converter (ADC) design and outline the role they play in converter choice for various kinds of applications. The most popular ADC architectures available today are successive approximations (sometimes called SAR because a successive-approximations (shift) register is the key defining element), flash (all decisions made simultaneously), pipelined (with multiple flash stages), and sigma-delta (SD), a charge-balancing type.

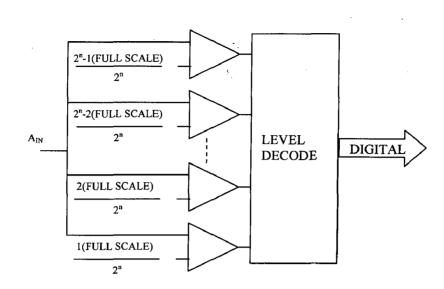

Conceptually, the *Flash Converters* architecture (illustrated in Figure 2.3) is quite straightforward: a set of  $2^{n}$ -1 comparators are used to directly measure an analog signal to a resolution of n bits. For a 4-bit flash ADC, the analog input is fed into 15 comparators, each of which is biased to compare the input to a discrete transition value. These values are spaced one least-significant bit (LSB=FS/ $2^{n}$ ) apart [12]. The comparator outputs simultaneously present  $2^{n}$ -1 discrete digital output states. If for example the input is just above ¼ of full scale, all comparators biased to less than ¼ full scale will output a digital '1', and the others will output a digital '0'. Together, these outputs can be read much like a thermometer. The final step is to level-decode the result into binary form.

Figure 2.3: Basic flash architecture

The flash architecture has the advantage of being very fast, because the conversion occurs in a single ADC cycle. The disadvantage of this approach is that it requires a large number of comparators that are carefully matched and properly biased to ensure that the results are linear. Since the number of comparators needed for an  $^{n}$ -bit resolution ADC is equal to  $2^{n}$ -1, limits of physical integration and input loading keep the maximum resolution fairly low.

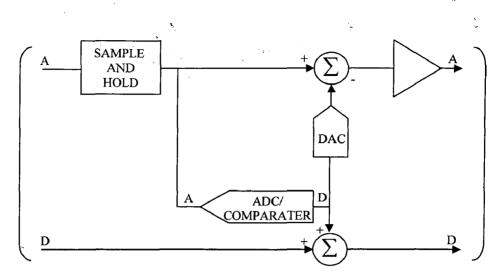

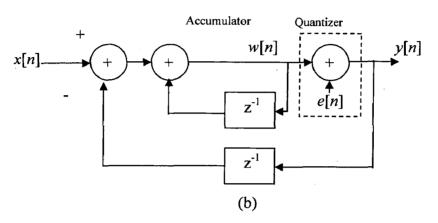

**Pipelined architecture** or pipelined-flash architecture effectively overcomes the limitations of the flash architecture. A pipelined converter divides the conversion task into several consecutive stages. Each of these stages, as shown in figure 2.4, consists of a sample and hold circuit, an *m*-bit ADC (e.g. a flash converter), and an *m*-bit DAC. First the sample and hold circuit of the first stage acquires the signal. The *m*-bit flash converter then converts the sampled signal to digital data. The conversion result forms the most significant bits of the digital output. This same digital output is fed into an *m*-bit digital-to-analog converter, and its output is subtracted from the original sampled signal. The residual analog signal is then amplified and sent on to the next stage in the pipeline to be sampled and converted as it was in the first stage. This process is repeated through as many stages as are necessary to achieve the desired resolution. In principle, a pipelined converter with p pipelined stages, each with an *m*-bit flash converter, can produce a high-speed ADC with a resolution of  $n = p^m$  bits using  $p^*(2^m-1)$  comparators.

Figure 2.4: A single pipelined converter stage

Pipelined converters achieve higher resolutions than flash converters containing a similar number of comparators. This comes at the price of increasing the total conversion time from one cycle to p cycles. But since each stage samples and holds its input, p conversions can be underway simultaneously. The total throughput can therefore be equal to the throughput of a flash converter, i.e. one conversion per cycle. The difference is that for the pipelined converter, we have now introduced latency equal to p cycles. Another limitation of the pipelined architecture is that the conversion process generally requires a clock with a fixed period. Converting rapidly varying non-periodic signals on a traditional pipelined converter can be difficult because the pipeline typically runs at a periodic rate.

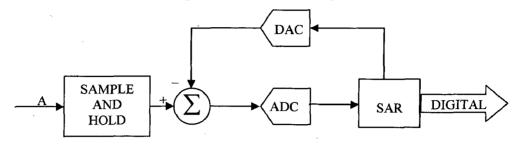

Successive approximations architecture can be thought of as being at the other end of the spectrum from the flash architecture. While a flash converter uses many comparators to convert in a single cycle; a SAR converter, shown in figure 2.5, conceptually uses a single comparator over many cycles to make its conversion. The SAR converter works like an old-fashioned balance scale. On one side of the scale, we place the sampled unknown quantity. On the other side, we place a weight (generated by the SAR and DAC) that has the value of  $\frac{1}{2}$  of full-scale and compare the two values. This first weight represents the most significant bit (MSB). If the unknown quantity is larger, the  $\frac{1}{2}$ -scale weight is retained; if the unknown quantity is smaller, it is removed. This series of steps is repeated n times, using successively smaller weights in binary progression (e.g., 1/4, 1/8, 1/16, 1/32, ...  $1/2^n$  of full scale) until the desired resolution, *n*, is attained. Each weight represents a binary bit, with the largest representing the most significant bit, and the smallest representing the least significant bit.

Figure 2.5: Successive-approximations architecture

A SAR converter can use a single comparator to realize a high resolution ADC. But it requires *n* comparison cycles to achieve *n*-bit resolution, compared to *p* cycles for a pipelined converter and 1 cycle for a flash converter. Since a successive-approximations converter uses a fairly simple architecture employing a single SAR, comparator, and DAC, and the conversion is not complete until all weights have been tested, only one conversion is processed during *n* comparison cycles. For this reason, SAR converters are more often used at lower speeds in higher-resolution applications. SAR converters are also well suited for applications that have non-periodic inputs, since conversions can be started at will. This feature makes the SAR architecture ideal for converting a series of time-independent signals. A single SAR converter and an input multiplexer are typically less expensive to implement than several sigma-delta converters. With dither noise present, SAR and pipelined converters can use averaging to increase the effective resolution of the converter: for every doubling of sample rate, the effective resolution improves by 3 dB or  $\frac{1}{2}$  bit.

One consideration when using a SAR or pipelined converter is aliasing. The process of sampling a signal leads to aliasing - the frequency-domain reflection of signals about the sampling frequency. In most applications, aliasing is an unwanted effect that requires a low-pass anti-alias filter ahead of the ADC to remove high-frequency noise components, which would be aliased into the passband. However, undersampling can put aliasing to good use, most often in communications applications, to convert a high-frequency signal to a lower frequency. Undersampling is effective as long as the total bandwidth of a signal meets the Nyquist criterion (less than one-half the sampling rate),

and the converter has sufficient acquisition and signal sampling performance at the higher frequencies where the signal resides. While fast SAR converters are capable of undersampling, the faster pipelined converters tend to be more effective at it.

ē.

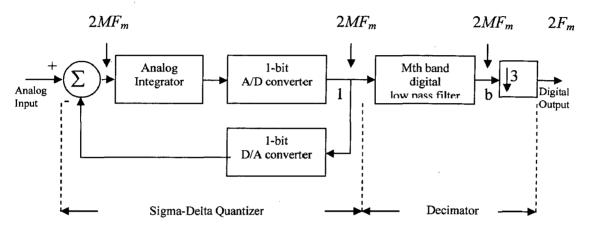

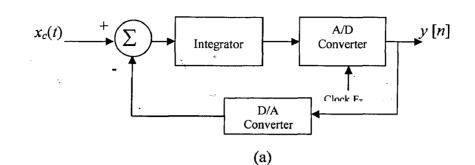

Sigma-Delta architecture takes a fundamentally different approach from those outlined above. In its most basic form, a sigma-delta converter consists of an integrator, a comparator, and a single-bit DAC, as shown in Figure 2.6. The output of the DAC is subtracted from the input signal. The resulting signal is then integrated, and the integrator output voltage is converted to a single-bit digital output (1 or 0) by the comparator. The resulting bit becomes the input to the DAC, and the DAC's output is subtracted from the ADC input signal, etc. This closed-loop process is carried out at a very high "oversampled" rate. The digital data coming from the ADC is a-stream of ones and zeros, and the value of the signal is proportional to the density of digital ones coming from the comparator. This bit stream data is then digitally filtered and decimated to result in a binary-format output. One of the most advantageous features of the sigma-delta architecture is the capability of noise shaping, a phenomenon by which much of the lowfrequency noise is effectively pushed up to higher frequencies and out of the band of interest. As a result, the sigma-delta architecture has been very popular for designing low-bandwidth high resolution ADCs for precision measurement. Also, since the input is sampled at a high "oversampled" rate, unlike the other architectures described above, the requirement for external anti-alias filtering is greatly reduced. A limitation of this architecture is its latency, which is substantially greater than that of the other types. Because of oversampling and latency, sigma-delta converters are not often used in multiplexed signal applications. To avoid interference between multiplexed signals, a delay at least equal to the decimator's total delay must occur between conversions. These characteristics can be improved in sophisticated sigma-delta ADC designs by using multiple integrator stages and/or multi-bit DACs. Let us now discuss Sigma-Delta converter in detail. In this type of converter, the analog signal is sampled at a rate much higher than the Nyquest rate, resulting in very closely spaced samples [13]. As a consequence, the difference between the amplitudes of two consecutive samples is very small, permitting it to be represented in digital form using very few bits, usually by one bit. The sampling rate is then decreased by passing the digital signal first through a factor

26

of M decimator to lower the sampling rate from M  $F_T$  to  $F_T$ . The decimator is designed by cascading an anti-aliasing low pass Mth band digital filter to reduce its bandwidth to  $\pi/M$  and a factor of M down-sampler. The wordlength of the downsampler output determines the resolution of the over sampling A/D converter, and it is much higher than that of the high rate digital signal due to the effect of digital filtering. The basic block diagram representation of the Sigma-Delta A/D converter is shown in figure 2.6.

Figure 2.6: Oversampling Sigma-Delta A/D Converter Structure

The figure indicated the sampling rates at various stages of the structure. The 1-bit output samples of the quantizer after decimation become b-bit samples at the output of the Sigma-Delta A/D converter due to the filtering operations involving b-bit multiplier coefficients of the Mth band digital low pass filter. Since the oversampling ratio M is typically very large in practice, the Sigma-Delta A/D converter is most useful in low frequency applications such as digital telephony, digital audio and digital spectrum analysers.

To understand the operation of Sigma-Delta A/D converter of the figure 2.6, we need to study the operation of the Sigma-Delta quantizer shown in figure 2.7 (a). To this end it is convenient to use the discrete time equivalent circuit of figure 2.7 (b), where the integrator has been replaced with an accumulator.

Figure 2.7: Sigma-Delta Quantization Scheme

Here the input x[n] is a discrete time sequence of analog samples developing an output sequence of binary valued samples y[n]. From this diagram, we observe that at each discrete instant of time, the circuit forms the difference ( $\Delta$ ) between the input and the delayed output, which is accumulated by a summer ( $\sum$ ) whose output is then quantized by a 1-bit A/D converter, i.e. a comparator. Even though the input-output relation of the Sigma-Delta quantizer is basically non-linear, the low frequency content of the input  $x_c(t)$  can be recovered from the output y[n] by passing it through a digital low pass filter. This property can be easily shown for a constant input analog signal  $x_a(t)$  with a magnitude less than +1. In this case, the output w[n] of the accumulator is a bounded sequence with sample values equal to either -1 or +1. This can happen only if the input to the accumulator has an average value of zero. Or in other words, the average value of w[n] must be equal to the average value of the input x[n].

It follows from figure 2.7(b) that the output y[n] of the quantizer is given by y[n] = w[n] + e[n] (2.1) where, w[n] = x[n] - y[n-1] + w[n-1]This gives, y[n] = x[n] + (e[n] - e[n-1])

Implementation of Digital Down Converter for Software Radio, A Dissertation Report

Where the quantity inside the parenthesis represents the noise due to Sigma-Delta modulation. The noise transfer function is simply  $G(z) = (1 - z^{-1})$

The power spectral density of the modulation noise is therefore given by

$$P_{y}(f) = \left| G(e^{j2\pi gT}) \right|^{2} p_{e}(f) = 4\sin^{2} \left( \frac{2\pi gT}{2} \right) p_{e}(f)$$

(2.2)

Where we have assumed the power spectral density  $P_e(w)$  of the quantization noise to be the one sided power spectral density defined for positive frequencies only. For a random signal input x[n],  $P_e(f)$  is constant for all frequencies and is given by

$$P_{e}(f) = \frac{(\Delta V)^{2}/12}{F_{T}/2}$$

(2.3)

Substituting the above in (2.2), we arrive at the power spectral density of the output noise, given by

$$P_{y}(f) = \frac{2}{3} \frac{(\Delta V)^{2}}{F_{T}} \sin^{2}(\pi f T)$$

(2.4)

This can be approximated as

$$P_{y}(f) \cong \frac{2}{3} \frac{(\Delta V)^{2}}{F_{T}} (\pi fT)^{2}$$

(2.5)

$$= \frac{2}{3}\pi^2 (\Delta V)^2 T^3 f^2, \quad f \ll F_T$$

(2.6)

From the above, the in-band noise power of the Sigma-Delta A/D converter is thus given by

$$P_{total,sd} = \int_{0}^{F_{m}} P_{y}(f) df = \frac{2}{3} \pi^{2} (\Delta V)^{2} T^{3} \int_{0}^{F_{m}} f^{2} df$$

(2.7)

$$=\frac{2}{9}\pi^{2}(\Delta V)^{2}T^{3}(F_{m})^{3}$$

(2.8)

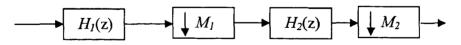

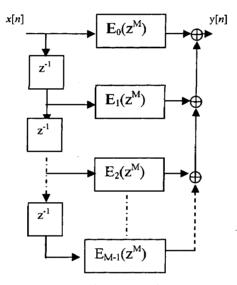

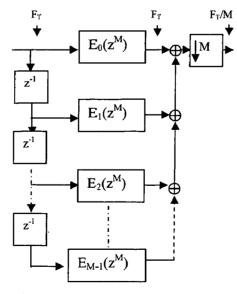

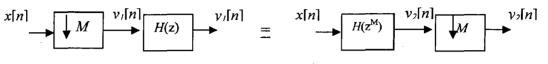

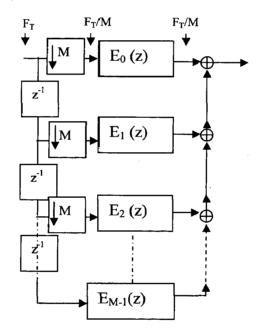

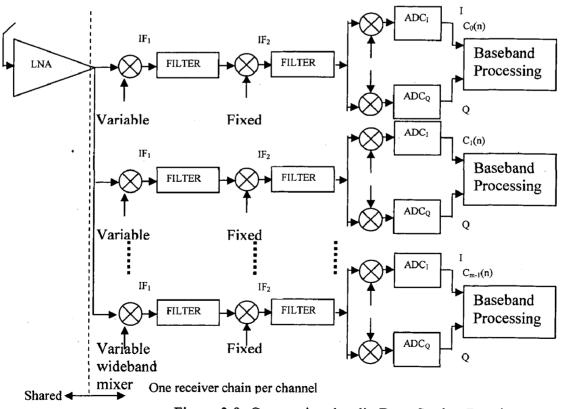

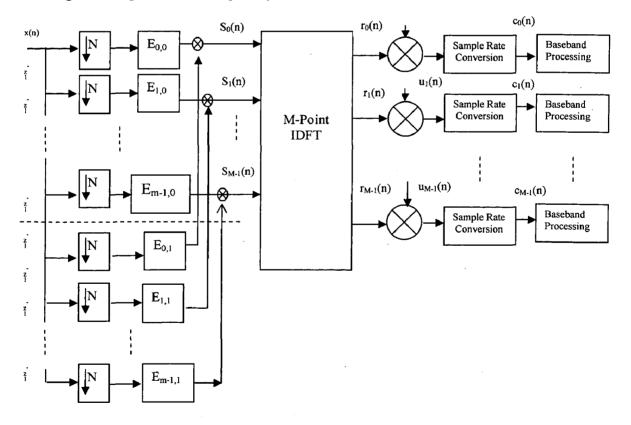

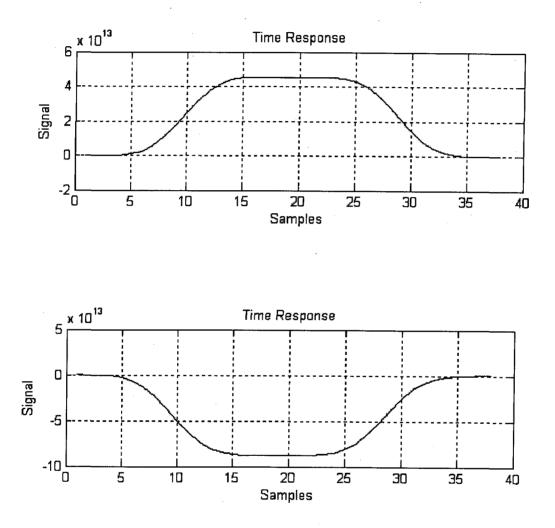

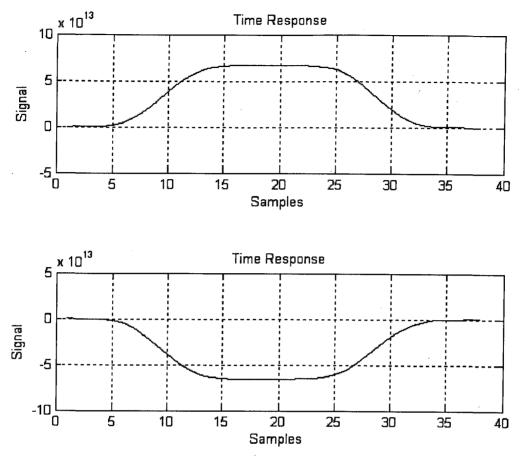

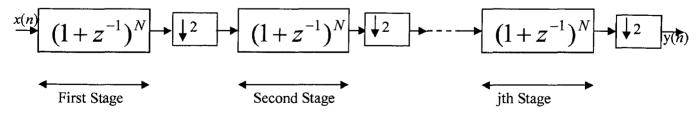

The Sigma-Delta A/D converter exhibits an improved noise performance which results from the shape of  $|G(e^{j2\pi/T})|$  which decreases the noise power spectral density in band  $(0 \le f \le F_m)$  while increasing it outside the signal band of interest  $(f > F_m)$ . Since this type of converter also employes oversampling, it requires a less stringent analog antialiasing filter. Future SDR receivers should have capability to cover multiple channels each of which have the band width of about 100MHz, so that the band width of the SDR receiver is required to be much greater than 100MHz [14]. The ADC used in the SDR receiver needs to have such a broad band width. When the base stations are constructed, ADCs and digital filters are required for each channel. These architectures have the high flexibility for the change of systems' features such as the modulation scheme, allocated frequency band. Broad-band superconducting RF filters and broad-band ADC are essential for each architecture. The common benefits of using superconducting devices to these architectures come from the employment of the superconductor ADC. As mentioned above, the input bandwidth of greater than 100MHz is needed for a future SDR receiver. However, the band-widths of conventional semiconductor ADCs including sub-ranging ADCs and pipelined ADCs except oversampled ADCs are limited by the clock jitter. Due to this limiting factor, the enhancement rate of the band-width for semiconductor ADCs is suppressed. When we employ the oversampled ADCs, the effect of the clock jitter can be reduced considerably. The superconductor oversampled ADCs based on the single flux- quantum (SFQ) logic can operate at frequencies of several tens of GHz, which is 1or 2-orders of magnitude higher than the clock frequency of a semiconductor oversampled ADC. This high clock frequency of superconductor ADCs enables to break the barrier of the clock jitter limit and to enhance the input band-width. Another advantage of SFQ-based ADCs is high sensitivity. The minimum power of input signals required to drive SFQ circuits is less than  $1 \mu$  W, while that of high-speed semiconductor ADCs is around 1mW.