# PERFORMANCE INVESTIGATION OF SINGLE PHASE MULTILEVEL RECTIFIER

## **A DISSERTATION**

Submitted in partial fulfillment of the requirements for the award of the degree

of

## INTEGRATED DUAL DEGREE

in

#### ELECTRICAL ENGINEERING

(With Specialization in Power Electronics)

By

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY ROORKEE ROORKEE - 247 667 (INDIA)

**JUNE, 2012**

# **Candidate's Declaration**

I hereby inform that the dissertation titled, "**Performance investigation of single phase multilevel rectifiers**" being submitted by me in partial fulfillment of the requirements for the award of integrated dual degree in Electrical engineering with the specialization in power electronics at I.I.T Roorkee is a bonafide work carried by me under the guidance and supervision of **Prof. Pramod Agrawal** in the department of Electrical engineering, I.I.T Roorkee.

Date: 6/6/12

Place: Roorkee

PALLAVI AHUJA IDD, EPE, IIT Roorkee

## Certificate

This is to certify that the above declaration made by candidate is correct to the best of my knowledge.

(Dr.Pramod Agarwal) Professor Department of Electrical Engineering Indian Institute of Technology Roorkee Roorkee – 247 667

# Acknowledgement

I wish to place on record my deep sense of gratitude and indebtedness to my guide **Dr. Pramod Agarwal**, Professor, Department of Electrical Engineering, Indian Institute of Technology, Roorkee, for his wholeheartedness and high dedication with which he was involved in this work. I am grateful for the hours he spent in discussing and explaining even the minute details of the work in spite of his hectic schedule of work. He listened patiently and authoritatively as he guided me and gave his valuable suggestions.

I am grateful to all my teachers of EDPE group for their suggestions and constant encouragements.

I am also grateful to my classmates, research scholars of EDPE and to Mr. Dinesh Mohan, Incharge of Embedded Systems laboratory for their valuable suggestions and constant encouragement.

I am grateful to my parents and friends for their inspirational impetus and moral support during the course of this work. I owe many things to them.

Finally, I would like to express my deepest gratitude to the almighty and thank him from the bottom of my heart.

#### PALLAVI AHUJA

## Abstract

Researchers have always been improving the technology when it comes to the power quality improvement. Many converter topologies have been discovered in last 25 years and the research is still on in this area. Years back in around 1975, multilevel converters came into existence which completely changed the whole scenario of converter fed induction motors and many other power electronic applications.

This work starts with the comparison of multilevel rectifiers with other traditional converter topologies showing their edge over others. Different control strategies are discussed. In this dissertation work, basically different rectifier topologies are compared on the basis of their simulation results. The control strategy used here is mainly PWM scheme with hysteresis current control.

MATLAB simulations are carried out for R and RL loads for different topologies with PWM scheme. The hardware has been implemented for just one topology in the laboratory. SPARTAN 3 FPGA kit has been used for the digital control and the VHDL code for the control strategy is been generated by using Xilinx System Generator tool kit.

# **List of Figures**

| Fig. 1.1 Common mode voltages at Fs = 10Khz and Vcm, base = Vdc.                                                                                                                                                                                                                                                | 5       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|                                                                                                                                                                                                                                                                                                                 |         |

| Fig. 1.2(a) Line to line voltage waveform and its spectrum in case of two level converter.                                                                                                                                                                                                                      |         |

| Fig. 1.2(b) Line to line voltage and its spectrum in case of a 17-level converter.                                                                                                                                                                                                                              | 6       |

| Fig. 1.3 Four level DC-DC converter used in 42 automotive systems.                                                                                                                                                                                                                                              | 7       |

| Fig. 1.4 Thirteen level CHB based transformerless STATCOM.                                                                                                                                                                                                                                                      | 8       |

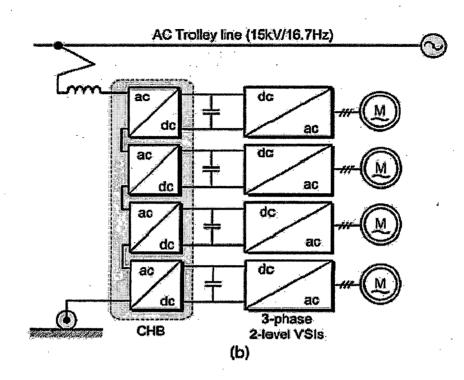

| Fig. 1.5(a) Transrapid maglev train long linear synchronous motor with back to back 3I NPC drive system. (b) CHB transformerless front end for the power interface of a locomotive traction drive                                                                                                               | -ئ<br>9 |

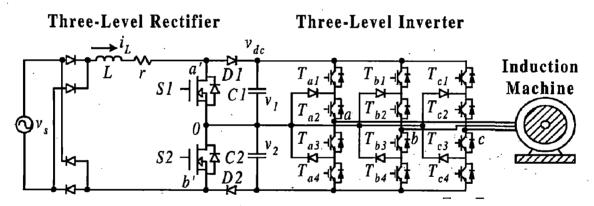

| Fig. 1.6 Three level PWM rectifier/inverter.                                                                                                                                                                                                                                                                    | .9      |

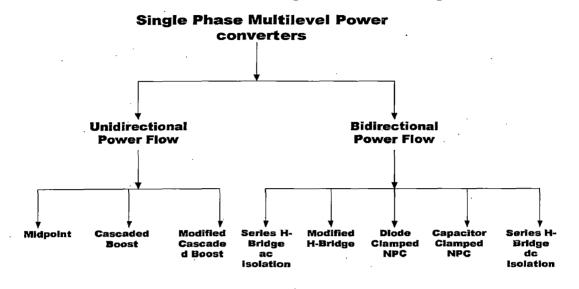

| Fig. 1.7 Classification of single phase MLCs.                                                                                                                                                                                                                                                                   | 10      |

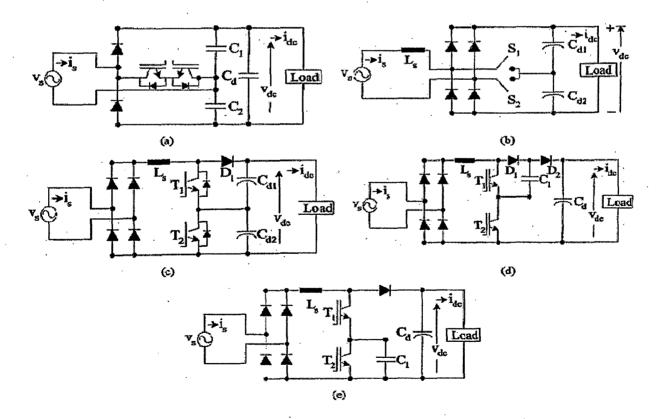

| Fig. 1.8 (a)Half-bridge unidirectional multilevel converter. (b) Two-bidirectional-switch<br>unidirectional multilevel converter. (c) Two-switch midpoint unidirectional multilevel<br>converter. (d) Adapted unidirectional multilevel converter. (e) Modified adapted<br>unidirectional multilevel converter. | . 11    |

| Fig. 1.9 A diode clamped five level configuration.                                                                                                                                                                                                                                                              | 11      |

| Fig. 1.10 Single phase unidirectional flying capacitor topology.                                                                                                                                                                                                                                                | 13      |

| Fig. 1.11 Bidirectional cascaded five level converter.                                                                                                                                                                                                                                                          | 15      |

| Fig. 1.12 Control strategies of MLCs.                                                                                                                                                                                                                                                                           | 18      |

| Fig. 2.1 Unidirectional three level rectifier with capacitor clamped scheme.                                                                                                                                                                                                                                    | 23      |

| Fig. 2.2 Control block of above rectifier.                                                                                                                                                                                                                                                                      | 24      |

| Fig. 2.3 Scope results for input voltage, input source current, three level voltages and DC output voltage.                                                                                                                                                                                                     | 25      |

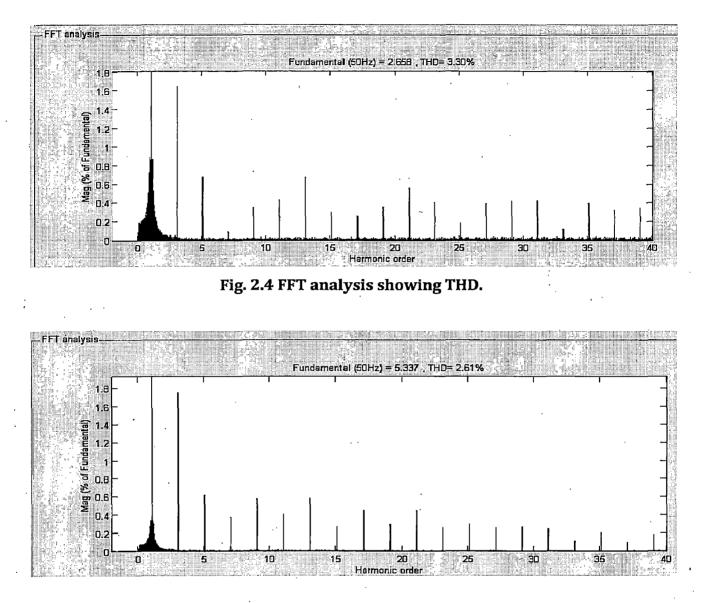

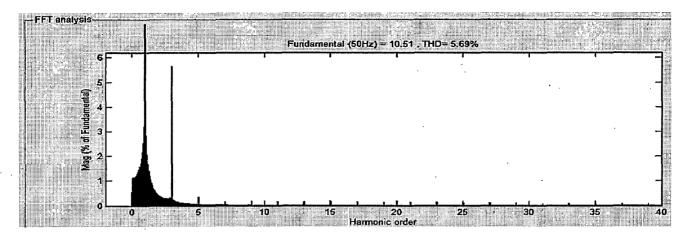

| Fig. 2.4 FFT analysis showing THD.                                                                                                                                                                                                                                                                              | 26      |

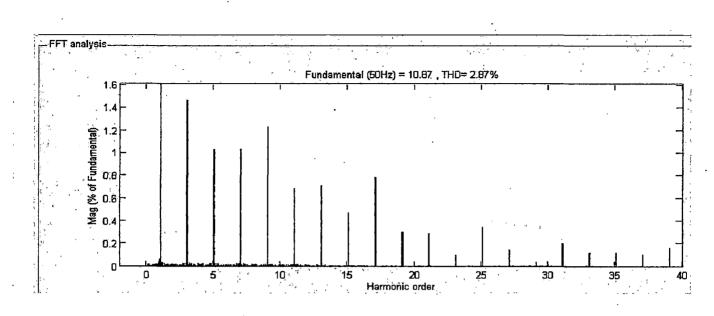

| Fig. 2.5 FFT analysis with load of 2A.                                                                                                                                                                                                                                                                          | 26      |

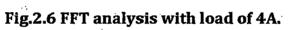

| Fig.2.6 FFT analysis with load of 4A.                                                                                                                                                                                                                                                                           | 27      |

| Fig. 2.7 Scope showing simulation results with input voltage, input source current, multilevel voltages and Dc output voltage.                                                                                                                                                                                  | 28      |

| Fig. 2.8 Operating regions of a three level converter.                                                                                                                                                                                                                                                          | 29      |

| Fig. 2.9 FFT analysis with voltage 70V rms and load 1A.                                                                                                                                                                                                                                                         | 29      |

| Fig. 2.10 FFT analysis for 70V rms supply and load of 2A.                                                                                                                                                                                                                                                       | 29      |

| Fig. 2.11 FFT analysis for 70V rms supply and load of 4A.                                                                    | 30          |

|------------------------------------------------------------------------------------------------------------------------------|-------------|

| Fig. 2.12 Simulation results.                                                                                                | 31          |

| Fig. 2.13 Diode clamped rectifier.                                                                                           | 33          |

| Fig. 2.14 Simulation results                                                                                                 | 34          |

| Fig. 2.15 FFT analysis for loads of 1A, 2A and 4A respectively.                                                              | 35          |

| Fig. 2.16 FFT analysis for loads of 1A, 2A and 4A respectively with 70V rms.                                                 | 36          |

| Fig. 2.17 Simulation results for three level voltages.                                                                       | 37          |

| Fig. 2.18 Simulation results for supply of 50V.                                                                              | 38          |

| Fig. 2.19 Converter topology with neutral point clamped.                                                                     | <b>39</b> . |

| Fig. 2.20 Control block of above rectifier.                                                                                  | 39          |

| Fig. 2.21 Simulation results with three level for 110V supply.                                                               | 40          |

| Fig. 2.22 Simulation results with 70V supply.                                                                                | 41          |

| Fig. 2.23 Power circuit of neutral clamped AC/DC converter.                                                                  | 42          |

| Fig. 2.24 Power circuit of a three level rectifier.                                                                          | 43          |

| Fig. 2.25 Simulation results showing Input mains voltage, input source current, three lev<br>voltages and DC output voltage. | vel<br>44   |

| Fig. 2.26 Power circuit.                                                                                                     | 45          |

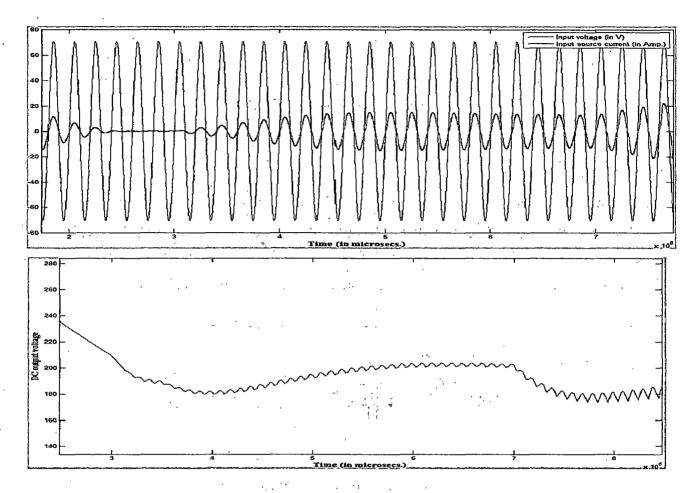

| Fig. 2.27 Simulation results showing input voltage, input current, two level voltages and output voltage.                    | DC<br>46    |

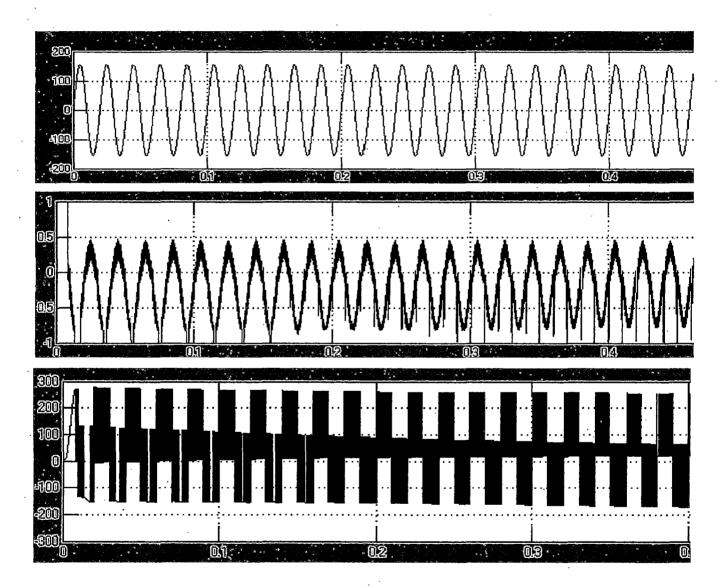

| Fig. 2.28 Simulation results showing input voltage, input current and two level voltages.                                    |             |

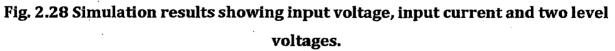

| Fig. 3.1 Xilinx Spartan 6 FPGA board.                                                                                        | 51          |

| Fig. 3.2 Altera Stratix FPGA.                                                                                                | 52          |

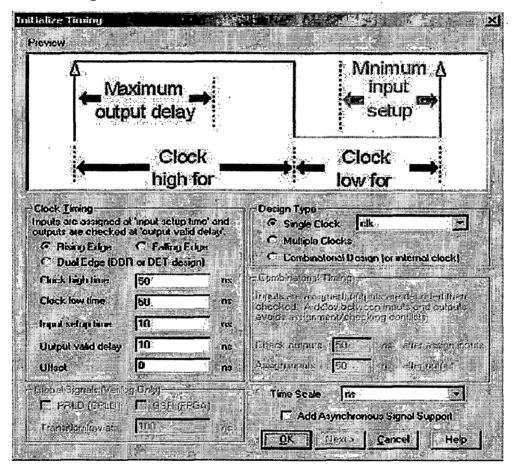

| Fig. 3.3 Clock and time settings.                                                                                            | 53          |

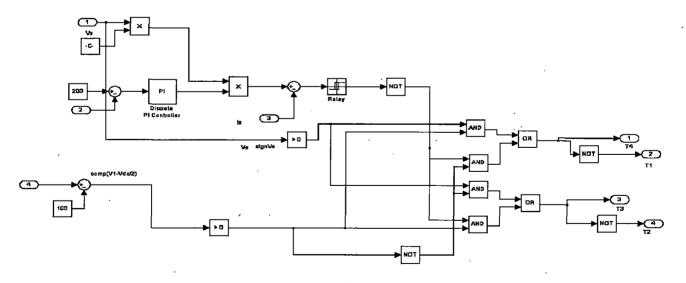

| Fig. 4.1 Control scheme using sim power blocks in SIMULINK.                                                                  | 62          |

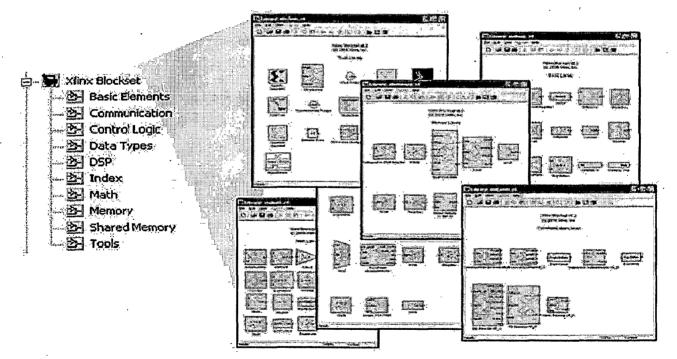

| Fig. 4.2 Xilinx block set in MATLAB SIMULINK.                                                                                | 63          |

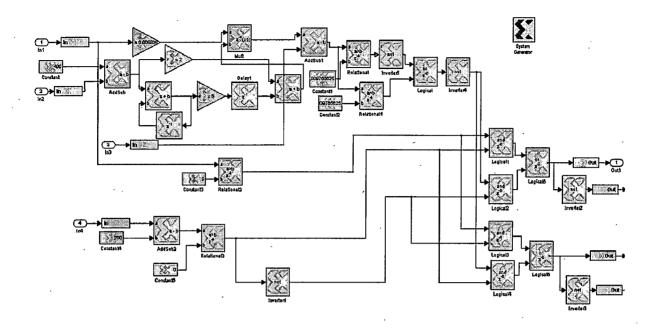

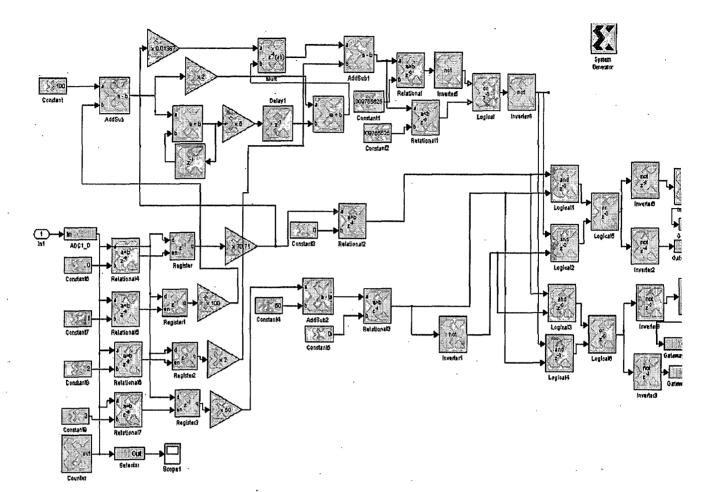

| Fig. 4.3 Control scheme using Xilinx blocks in SIMULINK model.                                                               | 64          |

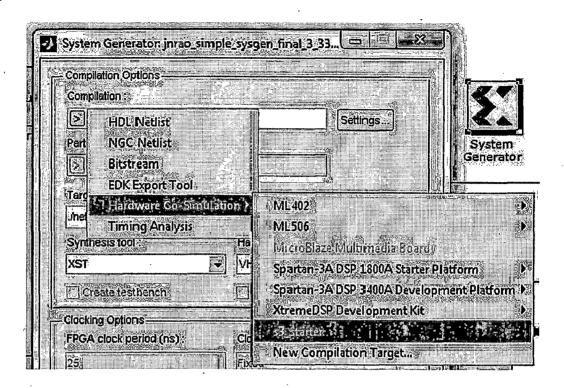

| Fig. 4.4 Compilation settings of system generator.                                                                           | 65          |

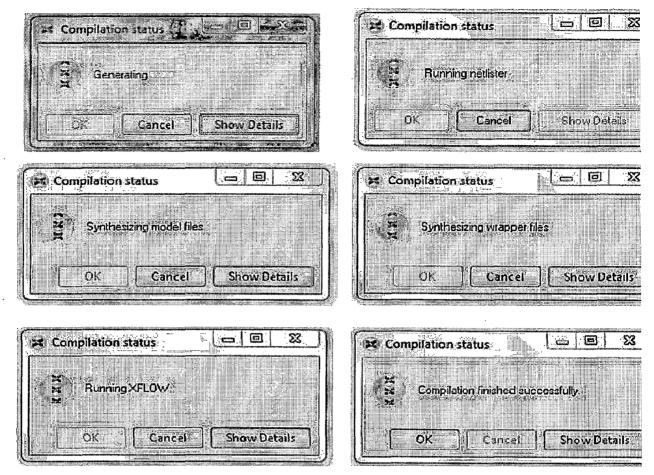

| Fig. 4.5 Compilation Process.                                                                                                | 67          |

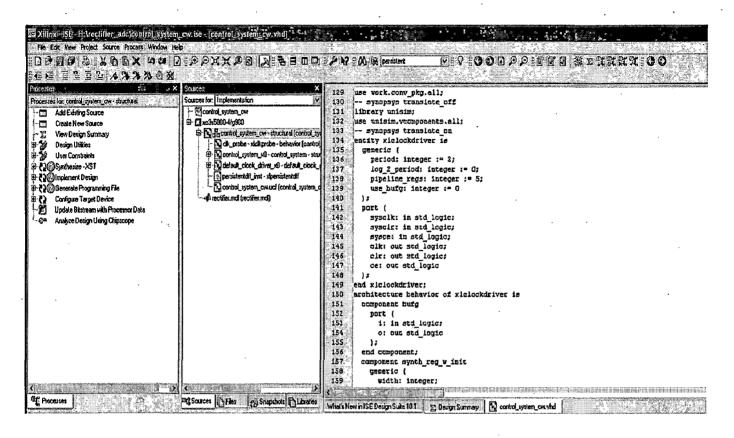

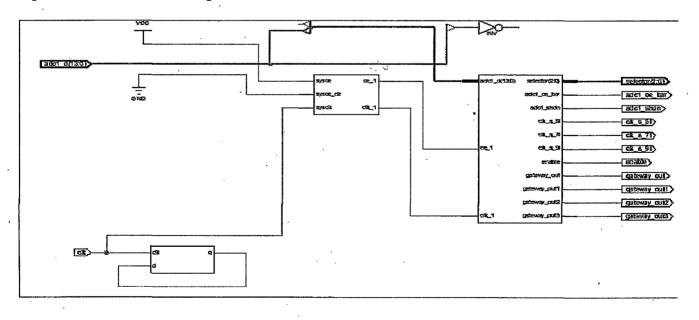

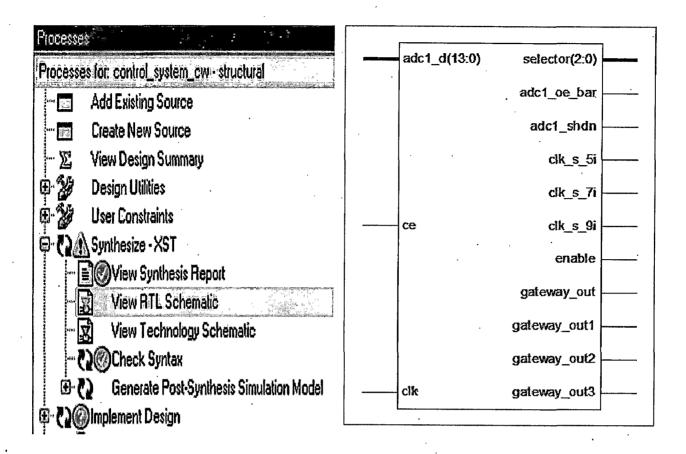

| Fig. 4.6 Process Window with Code generated.                                                                                 | 68          |

| Fig. 4.7 RTL schematic diagram with option in process window.                                                                | <b>69</b>   |

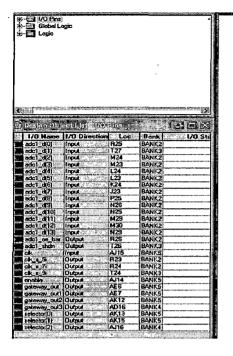

| Fig. 4.8 Xilinx Pace window.                                                                                                 | 70          |

| · ·                                                                                                                          |             |

| ν.                                                                                                                           |             |

|                                                                                                                              |             |

| ig. 4.9 Control model with Xilinx SIMULINK blocks incorporated with ADC.          | 71          |

|-----------------------------------------------------------------------------------|-------------|

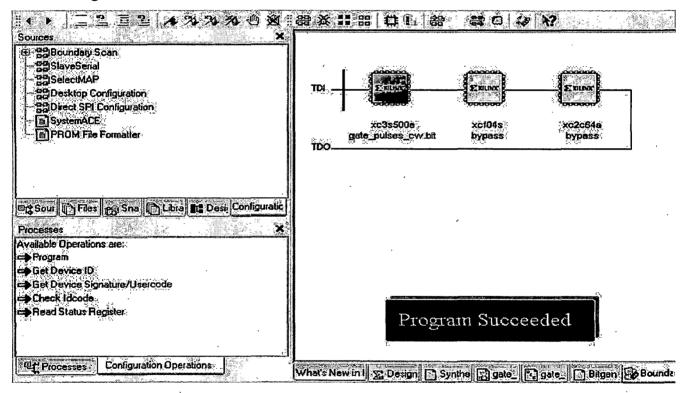

| ig. 4.10 Program succeeded window.                                                | 74          |

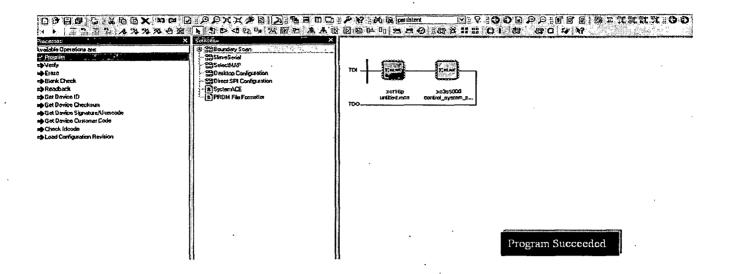

| ig. 4.11 Program succeeded window for .mcs file.                                  | 75          |

| ig. 4.12 Final step of dumping the code into FPGA kit.                            | 75          |

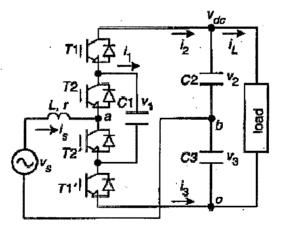

| ig. 5.1 Power circuit of multilevel capacitor clamp rectifier.                    | 77          |

| ig. 5.2 Operation modes of the rectifier (a) Mode1 (b) Mode2 (c)Mode 2(d) Mode 3. | 80          |

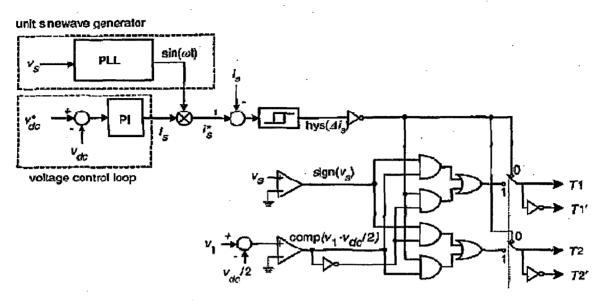

| ig. 5.3 Control block diagram for the rectifier topology.                         | 81          |

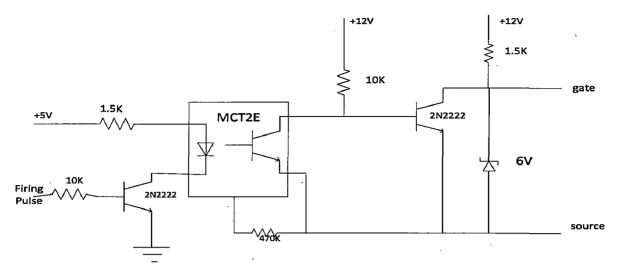

| ig. 5.4 Pulse amplification and isolation circuit.                                | 83          |

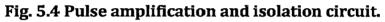

| ig. 5.5 Snubber circuit.                                                          | 83          |

| ig. 5.6 Hardware circuit for driving MOSFETs.                                     | 83          |

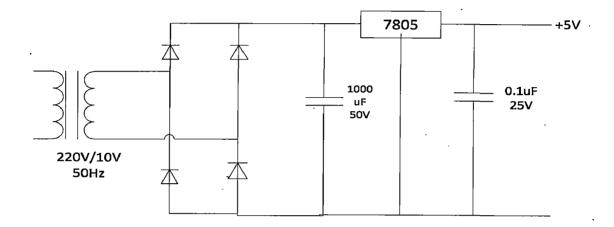

| ig. 5.7(a) Power supply circuit for +5 volts.                                     | 84          |

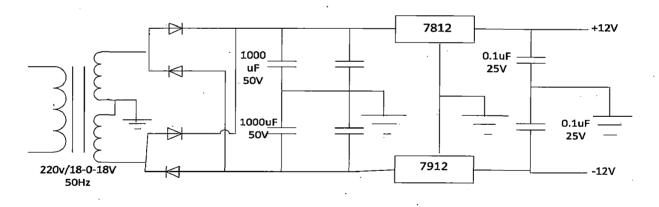

| ig. 5.7(b) Power supply circuit for +12 and -12 volts.                            | 84          |

| ig. 5.8 Power supplies on hardware.                                               | 85          |

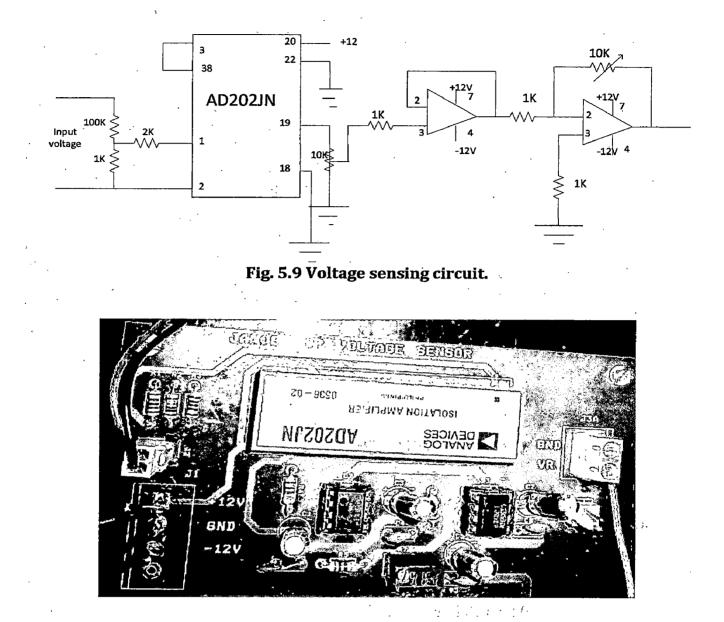

| ig. 5.9 Voltage sensing circuit.                                                  | 86          |

| ig. 5.10 Hardware prototype of voltage sensing circuit.                           | 86          |

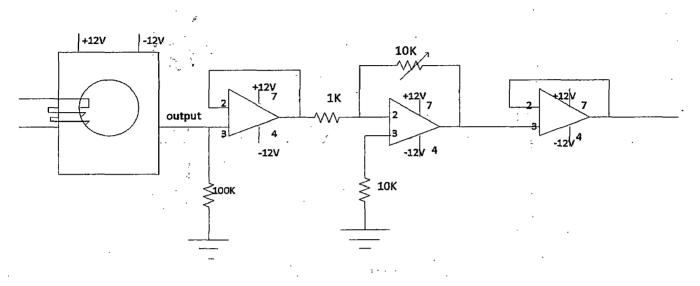

| ig. 5.11 AC current sensing circuit.                                              | 87          |

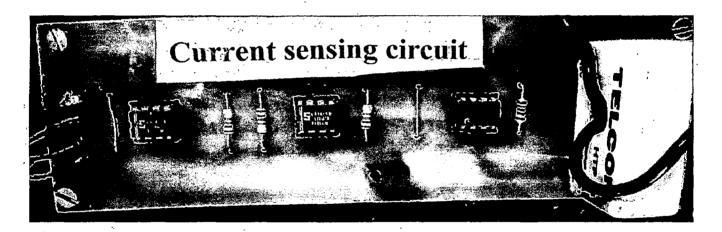

| ig. 5.12 Hardware prototype of current sensing circuit.                           | 87          |

| ig. 5.13 Hardware prototype of multiplexer circuit.                               | <b>88</b> · |

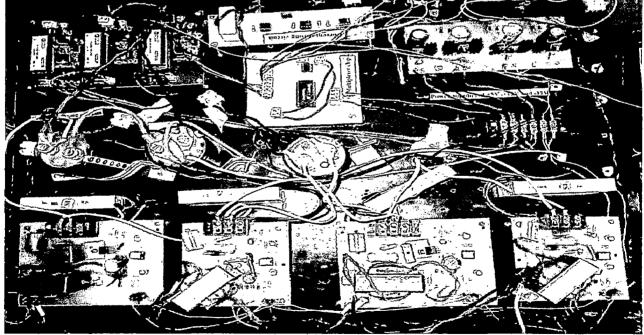

| ig. 5.14 Multilevel rectifier set up.                                             | 88          |

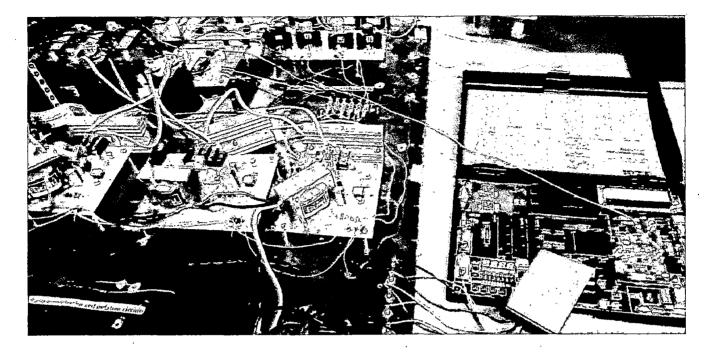

| ig. 5.15 FPGA control to feed the firing pulses.                                  | 89          |

# List of Tables

| Table 1.1 Diode clamped five level rectifier with switching states and voltage levels. | 12 |

|----------------------------------------------------------------------------------------|----|

| Table 1.2 Valid switching states of above mentioned topology.                          | 14 |

| Table 1.3 Summary of different types of H-Bridge converters.                           | 16 |

| Table 2.1 Summary of THDs with varying load and supply voltage.                        | 30 |

| Table 2.2 Summary of THDs with RL load.                                                | 32 |

| Table 2.3 Summary of THDs with varying load and power supply.                          | 36 |

| Table 2.4 THDs with varying load and input supply.                                     | 39 |

| Table 2.5 Summary of THDs with varying loads and power supply.                         | 41 |

| Table 2.6 Summary of THDs for two level voltages.                                      | 42 |

| Table 2.7 Summary of THDs for three level voltages.                                    | 43 |

| Table 2.8 Summary of THDs.                                                             | 45 |

| Table 2.9 Summary of THDs of input source current.                                     | 46 |

| Table 4.1 Mode selection jumper settings.                                              | 73 |

| Table 4.2 Mode selection table.                                                        | 73 |

| Table 5.1 Summary of switching states.                                                 | 79 |

**Table of Contents**

| Candidate's declaration                                      | i    |

|--------------------------------------------------------------|------|

| Acknowledgement                                              | ii   |

| Abstract                                                     | iii  |

| List of Figures                                              | iv   |

| List of Tables                                               | vii  |

| Nomenclature                                                 | viii |

| Table of contents                                            | ix   |

| Chapter 1: Introduction                                      | 1    |

| 1.1 Background                                               | . 1  |

| 1.2 Factors driving the research interest in this area       | 3    |

| 1.3 Advantages over two level converters                     | 4    |

| 1.4 Applications of MLCs                                     | 7    |

| 1.5 Classification of MLCs                                   | 9    |

| 1.6 Basic structure of MLCs                                  | . 11 |

| 1.6.1 Diode clamped topology                                 | 11   |

| 1.6.2 Flying capacitor topology                              | 13   |

| 1.6.3 H-Bridge topology                                      | 15   |

| 1.7 Control Schemes                                          | 17   |

| 1.8 Literature Review                                        | 20   |

| 1.9 Objective of Dissertation work                           | 21   |

| 1.10 Organization of dissertation                            | 21   |

| <b>Chapter 2: Simulations study of Multilevel Converters</b> | 23   |

| 2.1Introduction                                              | 23   |

ix

.....

| 2.2 Simulations of Multilevel Rectifier                      |                                         |

|--------------------------------------------------------------|-----------------------------------------|

| 2.3 Topology 1                                               |                                         |

| 2.3.1 Simulation with R load                                 |                                         |

| 2.3.2 Simulations with RL load                               |                                         |

| 2.3.3 Conclusion                                             | · .                                     |

| 2.4 Topology 2                                               |                                         |

| 2.5 Topology 3                                               |                                         |

| 2.6 Topology 4                                               | · · ·                                   |

| 2.7 Topology 5                                               | ÷                                       |

| 2.8 Topology 6                                               | •                                       |

| 2.9 Topology 7                                               |                                         |

| 2.10 Conclusion                                              | ·<br>·                                  |

| Chapter 3: FPGA application to Multilevel co                 | nverters                                |

| 3.1Background                                                |                                         |

| 3.2 FPGA: An overview                                        |                                         |

| 3.3 Designing with FPGAs                                     |                                         |

| 3.3.1 Entering VHDL code                                     | - · · · · · · · · · · · · · · · · · · · |

| 3.3.2 Synthesis and implementation                           |                                         |

| 3.3.3 Simulation                                             |                                         |

| 3.3.4 Physical realization                                   |                                         |

| <b>3.4 Application of FPGAs</b>                              |                                         |

| 3.5 Major Manufacturers                                      |                                         |

| 3.6 Limitations associated with FPGA system                  | n design                                |

| 3.7 Conclusion                                               |                                         |

| Chapter 4: Implementation of Digital Control                 | for Multilevel Rectifier                |

| 4.1. Software Details                                        |                                         |

| 4.1.1 Xilinx <sup>®</sup> Integrated Software Environment (I | SE™) 10.1 with Xilinx service pack 3    |

|                                                              |                                         |

| . <b>х</b>                                                   |                                         |

| 4.1.2. MATLAB                                                               | 60   |

|-----------------------------------------------------------------------------|------|

| 4.1.3 Xilinx System Generator                                               | 61   |

| 4.1.4 Xilinx System Generator Board Description Builder                     | 61   |

| 4.2 Implementation of the control scheme with SIMULINK and system generator | 62   |

| 4.3 Simple PWM scheme                                                       | 62   |

| 4.4 Hardware Co-Simulation                                                  | · 65 |

| 4.5 Generating BIT STREAM FILE                                              | 71   |

| 4.6 Modes of Downloading Process                                            | . 72 |

| 4.6.1 Boundary Scan Mode                                                    | 72   |

| 4.6.2 Master Serial Mode                                                    | 72   |

| 4.7 Mode settings                                                           | 72   |

| 4.8 Procedure for downloading using iMPACT                                  | 73   |

| 4.9 Procedure for downloading using PROM                                    | 74   |

| 4.10 Conclusion                                                             | 75   |

| Chapter 5: Hardware Implementation and Development of Multilevel Rectifier  | 77   |

| 5.1 Power circuit                                                           | 77   |

| 5.1.1 Operation Principle                                                   | . 78 |

| 5.1.2 Control Scheme                                                        | 80   |

| 5.2 Hardware development                                                    | 81   |

| 5.2.1 Power circuit                                                         | 81   |

| 5.2.2 Pulse amplification and isolation circuit                             | 82   |

| 5.2.3 Power Supplies                                                        | 84   |

| 5.2.4 AC and DC voltage sensing circuit                                     | 85   |

| 5.2.5 AC current sensing circuit                                            | 86   |

| 5.2.6 Multiplexer circuit                                                   | 87   |

| 5.3 Conclusion                                                              | 89   |

| Chapter 6: Conclusions and Future Scope                                     | 90   |

|                                                                             |      |

xi

## 6.1Conclusions

## 6.2 Future Scope in this work

## References Publication

90

**90**

91 92

## 1.1 Background:

Since the birth, power electronics has been in use widely in various applications. Its main objective has always been to maximize the efficiency and minimize the losses. To achieve this objective even researchers have been striving hard when they come to think of improving power quality at the receiving end.

Traditional diode and thyristor based rectifiers used in power converter applications draw pulsed current from the input main which deteriorates the line voltage, produce radiated and electromagnetic interference leading to the poor efficiency. For single phase power applications, passive power filters, active one and two stage PFC rectifiers are typical approaches used to achieve high power factor and low THD but they are bulky and heavy due to which there was a trade-off between their high efficiency, low cost and compactness. Active power factor corrector and active filters have been successfully researched and developed for power factor correction and current harmonics elimination, respectively. Power factor correction based on active currentshaping techniques has been presented in [1, 2] to improve the power quality of power converter systems. Several active power conversion topologies were used for power factor correction. These include the step up or boost converter, flyback converter and active input current shaper (AICS). Among the high power factor converters, the boost type is the most popular [3, 4]for drawing a sinusoidal current from the AC mains with nearly unity power factor. The DC side voltage of the boost converter is always higher than the peak voltage of the AC mains. The buck type AC-DC converters provide a DC bus voltage smaller than the peak voltage of the AC mains. The buck converters can limit the input inrush current and DC short circuit current. However, the high voltage stresses of the power devices are the main drawbacks if the circuits are used in medium voltage or high power applications. It has been shown in the literature that a single staged fly back converter can be operated as a single phase AC/DC converter with active power factor correction [5]. But the disadvantages of this conversion technique attributed mainly to the constant switching frequency and discontinuous nature of the current. In 1999 Active Input Current Shaper (AICS) was proposed [6] to turn a conventional Buck converter into a single

stage AC/DC converter with high efficiency, fast transient response and low cost. Here, the disadvantages mainly attributed to the increased cost compared to the conventional topology due to the extra winding coupled to the buck's output inductor and the voltage magnitude higher than peak value, across the bulk capacitor. Even conventional boost converters posed certain problems despite proving themselves good as power factor correctors. For high power or high voltage applications, the major concerns of conventional boost converters are inductor volume and weight, and losses on the power devices, which will affect converter cost, efficiency and power density. Some other methods were also experimented to improve the power factors due to cancellation of certain low order harmonics of high amplitudes. But again the disadvantages here attributed mainly to the bulkiness, heavy and lossy nature of the converters.

Next came the two level converter topology which was popular in low voltage power conversion market but for applications with high switching frequencies such as high speed drives, traction converters, grid converters, wind power applications, etc. its technological progress has been slow. This two level converter also attributes some disadvantages [7, 8] which are discussed as follows:

- 1. For high switching frequencies the conduction losses increase with high or medium voltage rating devices for same rated currents. For example, 600-V IGBTs feature on-state voltages that are roughly 10% lower than that of a 1200-V IGBT at the same rated current and technology. Similarly, the switching loss energies of a 600-V IGBT with the same device technology and current are smaller by a factor of 3–5.

- 2. Common-mode currents are considered to be the main reasons for bearing currents/failures and electromagnetic interference (EMI) problems. These currents are caused by the common mode voltages which are significantly large in two level voltages.

- 3. Large size of inductors used to filter out the harmonics in AC currents and voltages at the terminal end which contains the high frequency content, thus increasing the effective cost.

- 4. It also uses a DC-link filter to reduce the ripples in DC output voltage which again increases the cost.

2

5. The major disadvantage is in the applications for medium and high voltage converters because to increase the operating voltage of these converters, many semiconductor devices are to be connected in series but this approach introduces high dv/dt which necessitates the use of interfacing transformers with high insulation requirements to withstand the switching of large voltage steps at high frequency (1-2Khz).

To overcome the aforementioned difficulties faced by conventional conversion techniques, multilevel technology came into existence years back in 1975. The very inception of the idea of concept of multilevel converters brought a ray of hope to the world of power electronics by proving themselves IPQCs. The multilevel converters have drawn tremendous interest in the power industry [9]. The general structure of a multilevel converter is to synthesize a sinusoidal voltage from several levels of voltages, typically obtained from capacitor voltage sources. The so-called "multilevel" starts from three-level. A three-level converter is usually called as "neutral clamped" converter. A large volume of research has been documented in the areas of circuit configuration, control and applications. These converters provide high power factor and reduced THD of current at the input ac mains and ripple-free regulated dc output voltage. It has been reported in the literature that using multilevel converters the THD can be reduced below 1% [10]. Multilevel converters have outperformed the conventional AC/DC converters known as rectifiers by achieving an improved power quality in terms of power factor correction, reduced harmonic distortions in AC input mains, higher efficiency, ripple free regulated DC output voltage and reduced stresses on the switching devices.

NOTE: Number of levels as denoted in further chapters of this report is only for half cycle.

## 1.2 Factors driving the research interest in this area:

Multilevel converters have an edge over conventional aforementioned converters due to the following multitude of factors:

One of the major reasons is the self commutating devices unlike thyristor based converters, hence, complex commutation circuits can be escaped. MOSFETS are used mainly for small power ratings, IGBTs for medium, and GTOs for large power applications. These have unsurpassed performances especially for high power applications.

- Yesteryears' trend shows a trade-off between the voltage rating and the switching frequency but the voltage stresses across the switching devices are just a fraction of overall voltage rating of the converter, thus allowing the use of high performance devices available at low voltage rating.

- Common mode voltages and electromagnetic interferences (EMI) caused by the changes in voltage levels at high frequency are reduced in these converters as the voltage is obtained in small steps (stair-case) with low dv/dt.

- Since there is no problem of high voltage stresses on the devices, voltage handling capacity of MLCs is not restricted by the voltage rating of the switches.

- Voltage and current harmonics are significantly reduced in MLCs. As mentioned earlier, the MLCs produce a regulated ripple-free dc output due to which the size of the inductor is reduced and hence, the core losses of the same. Thus, the efficiency and the performance are considerably enhanced. This has the advantage over conventional boost converters where the inductor size is four times the size used in here to ripple out the current [11].

- High voltage handling capability and improved spectral performance reduce the need for step-down and multi-pulse/poly-phase transformers which are used in two level and multi-pulse converters in high voltage applications. Substantial reduction in cost, size, weight and losses are possible by reduction of transformers.

## **1.3** Advantages over two level converters:

A multilevel converter has several advantages over a conventional two-level converter that uses high switching frequency pulse width modulation (PWM). The attractive features of a multilevel converter can be briefly summarized as follows.

• Staircase waveform quality: Multilevel converters not only can generate the output voltages with very low distortion, but also can reduce the dv/dt stresses; therefore electromagnetic compatibility (EMC) problems can be reduced. The voltage stress across the switches in case of multilevel converters is reduced considerably as voltage is synthesized in small steps.

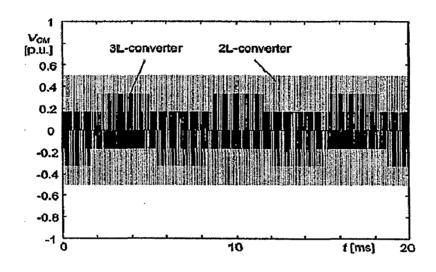

• Common-mode (CM) voltage: Multilevel converters produce smaller CM voltage, therefore, the stress in the bearings of a motor connected to a multilevel motor drive can be reduced. Furthermore, CM voltage can be eliminated by using advanced modulation strategies. Figure 1.1 shows the comparison of common mode voltage at switching frequency of 10Khz and common mode base voltage of output DC voltage in case of MLCs and two level converters.

Fig. 1.1 Common mode voltages at Fs = 10Khz and Vcm,base = Vdc. [7]

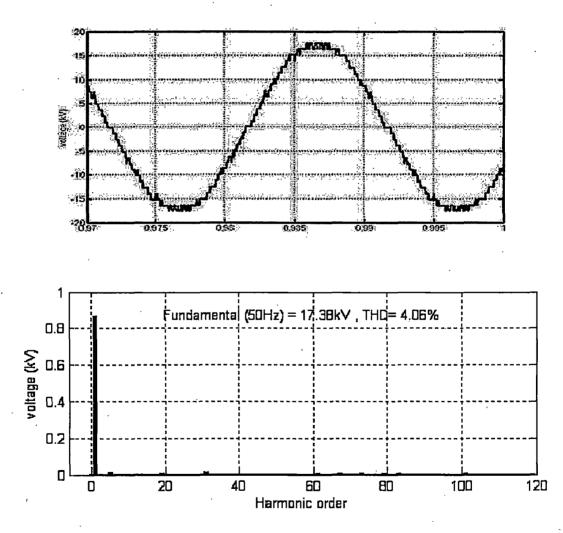

• Multilevel converters can draw input current with low distortion. Line to line voltage waveforms shown in figure 1.2(a) and 1.2(b) along with their spectra show that multilevel converters produce lower harmonic distortion and lower voltage stress on the switches than those in two level converters.

5

Fig. 1.2(a) Line to line voltage waveform and its spectrum in case of two level converter. [8]

Fig. 1.2(b) Line to line voltage and its spectrum in case of a 17-level converter. [8]

6

• Switching frequency: Multilevel converters can operate at both fundamental switching frequency and high switching frequency PWM with lower semiconductor losses than two level converters. It should be noted that lower switching frequency usually means lower switching loss and higher efficiency.

## 1.4 Applications of MLCs:

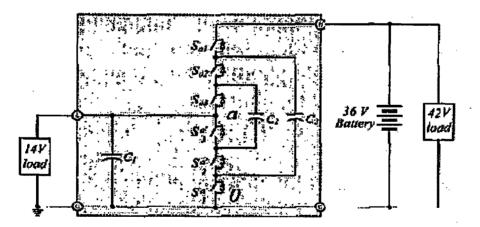

Multilevel converters have been used widely in various applications since the birth. Multilevel ac-dc conversion of electric power is widely used in adjustable-speed drives (ASDs), switch-mode power supplies (SMPSs), uninterrupted power supplies (UPSs), and utility interface with non-conventional energy sources such as solar PV, etc., battery energy storage systems (BESSs), in process technology such as electroplating, welding units, etc., battery charging for electric vehicles, and power supplies for telecommunication systems, measurement and test equipments. Use of multilevel converters in DC-DC applications especially in automotives is commendable. Figure 1.3 shows a four level DC-DC converter used in 42 automotive systems.

Fig. 1.3 Four level DC-DC converter used in 42 automotive systems.

Application of MLC with bi-directional power flow in electric drives forms an important area of research in MLC. MLCs were initially proposed in ac motor drives applications due to their ability to generate low harmonics, multi-tier waveforms. These converters have been extensively applied in ac motor drives in medium and high voltage ratings. Permanent magnet brushless motor (PMSM) drives are used in high power three-phase industrial drives and as well as in

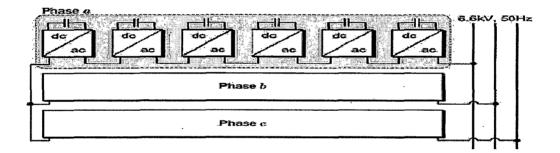

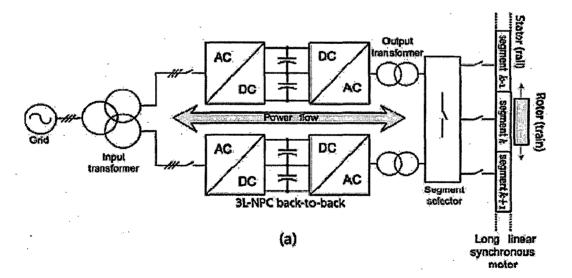

single phase traction drives. These MLCs have various other applications in many fields shown in figures 1.4-1.5. Multilevel power converters have an important application in back to back inter-tie connections where one of the converter acts as rectifier and other acts as inverter thus making the bidirectional power flow possible between them. The result is a well-balanced voltage across each capacitor while maintaining the staircase voltage wave, because the unbalanced capacitor voltages on both sides tend to compensate each other. Such a dc capacitor link is categorized as the "back-to-back intertie." The purpose of the back-to-back intertie is to connect two asynchronous systems. It can be treated as 1) a frequency changer, 2) a phase shifter, or 3) a power flow controller. This back to back intertie configuration is used for driving three phase induction motor drives where front end of the converter set is used as rectifier and back end is used as inverter fed by the DC output of front end rectifier as shown in figure 1.6.

Fig. 1.4 Thirteen level CHB based transformerless STATCOM.

8

Fig. 1.5(a) Transrapid maglev train long linear synchronous motor with back to back 3L-NPC drive system. (b) CHB transformerless front end for the power interface of a locomotive traction drive

Fig. 1.6 Three level PWM rectifier/inverter.

## 1.5 Classification of MLCs:

MLCs are generally classified as diode clamped, flying capacitor and cascaded multilevel converters [12]. Circuit configurations of MLCs are classified [13] on the basis of power flow capability as shown in Figure 1.7. Since this work is mainly on single phase, it is better to

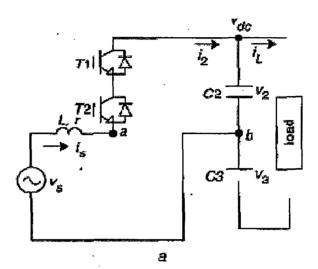

present the classification of single phase topologies. Many single phase circuit configurations are reported in the literature [14],[15],[16],[17] and few are shown in Fig. 1.8(a)–(e) using unidirectional and bidirectional switches with single, dual, and three capacitors at the dc link.

Fig. 1.8 (a)Half-bridge unidirectional multilevel converter. (b) Two-bidirectionalswitch unidirectional multilevel converter. (c) Two-switch midpoint unidirectional multilevel converter. (d) Adapted unidirectional multilevel converter. (e) Modified adapted unidirectional multilevel converter.

## 1.6 Basic structure of MLCs:

#### 1.6.1 Diode clamped topology:

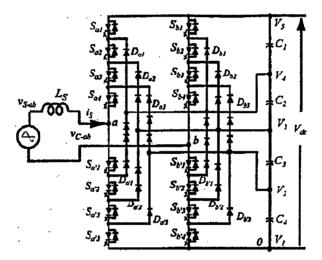

An m-level diode-clamp converter typically and basically consists of (m-1) capacitors on the dc bus and produce *m* levels of the phase voltage. Fig. 1.4 shows a single-phase full bridge five level diode-clamp converter in which the dc bus consists of four capacitors, C<sub>1</sub>, C<sub>2</sub>, C<sub>3</sub> and C<sub>4</sub>. For a dc bus voltage V<sub>dc</sub>, the voltage across each capacitor is V<sub>dc</sub>/4, and each device voltage stress will be limited to one capacitor voltage level, V<sub>dc</sub>/4, through clamping diodes. Table 1.1 lists the voltage levels and their corresponding switch states. State condition 1 means the switch is on, and 0 means the switch is off.

Fig. 1.9 A diode clamped five level configuration.

| Output              | T   |          | ار<br>ب         | Switc | h Stat | e   |   |     |

|---------------------|-----|----------|-----------------|-------|--------|-----|---|-----|

| V <sub>all</sub>    | Sal | $S_{a2}$ | S <sub>a3</sub> | Sat   | Sal    | Saz | S | Say |

| $V_5 = V_{dc}$      | 1   | 1        | 1               | 1     | Q      | 0   | 0 | 0   |

| $V_{s} = 3V_{de}/4$ | 0   | 1        | 1               | 1     | 1      | 0   | 0 | 0   |

| $V_3 = V_{ilc}/2$   | 0   | 0        | 1               | 1     | 1      | 1   | 0 | 0   |

| $V_2 = V_{dc}/4$    | 0   | 0        | 0               | 1     | 1      | 1   | 1 | 0   |

| $V_j = 0$           | 0   | · 0      | 0               | 0     | 1      | 1   | 1 | 1   |

## Table 1.1 Diode clamped five level rectifier with switching states and voltage levels.

There are certain advantages and disadvantages of this diode clamped topology as follows:

#### Advantages:

- When the number of levels is high enough, harmonic content will be low enough to avoid the need for filters.

- Efficiency is high because all devices are switched at the fundamental frequency.

- Reactive power flow can be controlled.

- The control method is simple for a back-to-back intertie system.

#### Disadvantages:

Some of the inherent features of this topology mainly attribute to the disadvantages as described:

- Although each switching device blocks V<sub>dc</sub>/4 only but the each diode blocks a different voltage depending upon its position in the topology. For example, in figure 1.4, diode D<sub>a'1</sub> blocks all three capacitor voltages, when switches S<sub>a'1</sub> S<sub>a'4</sub> are turned ON, equating to 3V<sub>dc</sub>/4. Due to this the diodes are of different voltage ratings. If we employ diodes of equal ratings then the no. of diodes would be increased to (m-1)(m-2) in each leg for m-level converter thus, making the system impractical to implement.

- From Table 1.1, it can be seen that switch  $S_{a1}$  conducts only during  $V_o = V_{dc}$ , while switch  $S_{a4}$  conducts over the entire cycle except during  $V_{ao} = 0$ . Such an unequal conduction duty requires different current ratings for switching devices. When the

inverter design is to use the average duty for all devices, the outer switches may be oversized, and the inner switches may be undersized.

- In most applications, a power converter needs to transfer real power from ac to dc (rectifier operation) or dc to ac (inverter operation). When operating at unity power factor, the charging time for rectifier operation (or discharging time for inverter operation) for each capacitor is different. Such a capacitor charging profile repeats every half cycle, and the result is unbalanced capacitor voltages between different levels.

- Adapted diode clamped topology addresses an important issue of unequal sharing of voltages in clamping diodes and hence neutral point voltage balance problem arises in diode clamped converters with higher number of levels. The topologies with the inherent neutral point voltage balance have been discovered in the literature [18]. These topologies are being extensively used in ac motor drives and other utility applications.

- It is difficult to do real power flow control for the individual converter.

#### **1.6.2** Flying capacitor topology:

Then came the capacitor clamped topology which was an important modification to the diode clamped topology. This topology was proposed to simplify the neutral point voltage balancing and to eliminate clamping diodes. However, this also further faced a couple of difficulties in control which are mentioned in further section of this section. Some basic flying capacitor topology [19] is described as follows:

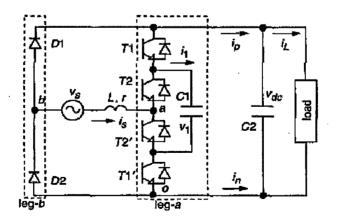

Fig. 1.10 Single phase unidirectional flying capacitor topology.

13

To perform the power factor correction in the proposed rectifier, the operating principle must be considered. There are four power switches, two diodes and one clamped capacitor in the proposed rectifier. To prevent damage to the power switches in the rectifier leg *a*, the constraints on the power switches are  $T_i+T_i'=1$ , i=1,2 where Ti (or Ti')=1 or 0, if power switch Ti (or Ti') is turned on or off, respectively. Therefore, there are two independent power switches and four valid switching states in leg *a*, and two operating states in leg *b*. Table 1.2 gives eight valid switching states in the proposed rectifier. Depending on the voltage level, there is one operating state to generate the voltage levels  $V_{ab} = V_{dc}$  and  $-V_{dc}$ , respectively, and two operating states to perform voltages  $V_{ab} = V_{dc}/2$ , 0 and  $-V_{dc}/2$ , respectively.

| Valid     | is | T1    | T2 | V <sub>ab</sub>       | $V_{ab}(V_1=Vdc/2)$ | Mode |

|-----------|----|-------|----|-----------------------|---------------------|------|

| switching |    |       |    |                       |                     |      |

| states    |    |       |    |                       |                     |      |

| 1         | +  | 0 · · | 0  | 0                     | 0 .                 | 3.   |

| 2         | +  | 0     | 1  | <b>V</b> <sub>1</sub> | V <sub>dc</sub> /2  | 2    |

| 3         | +  | 1 .   | 0  | $V_{de} - V_1$        | V <sub>do</sub> /2  | 2    |

| 4         | +  | 1     | 1  | V <sub>dc</sub>       | V <sub>dc</sub>     | ·1   |

| 5         | -  | 0     | 0  | -V <sub>dc</sub>      | -V <sub>dc</sub>    | 5    |

| 6         | -  | 0     | 1  | $V_1 - V_{dc}$        | -V <sub>do</sub> /2 | 4    |

| 7         | -  | 1     | 0  | -V <sub>1</sub>       | -V <sub>do</sub> /2 | 4    |

| 8         | -  | 1     | 1  | 0                     | 0                   | 3    |

#### Table 1.2 Valid switching states of above mentioned topology.

This configuration is also generally known as capacitor clamped. Now there are certain advantages and disadvantages of this topology as well.

#### Advantages:

- Large number of storage capacitors enables the converter to ride through short duration outages and deep voltage sags.

- Provides switch combination redundancy for balancing different voltage levels.

- When the number of levels is high enough, harmonic content will be low enough to avoid the need for filters.

- Both real and reactive power flow can be controlled, making a possible voltage source converter candidate for high voltage dc transmission.

#### Disadvantages:

- An excessive number of storage capacitors is required when the number of converter levels is high. High-level systems are more difficult to package and more expensive with the required bulky capacitors.

- The control will be very complicated to track the voltage levels of all the capacitors and also their precharging to the same level and start-up are complex.

- Switching utilization and efficiency are poor for real power transmission.

#### 1.6.3 H-Bridge topology:

These converters are generally bidirectional in nature. These are used for even high-power applications such as BESS, metros, traction, etc. These have major applications in STATCOM [20], facts devices as static var compensator for exchanging the reactive power along the power transmission lines. These can be developed for a higher number of levels for high-voltage and high-power applications. A bidirectional H-bridge converter topology is shown in figure 1.6. This topology has used isolation transformer which is application specific.

Fig. 1.11 Bidirectional cascaded five level converter.

Every cell of the H-bridge converter has equal or different input supply depending upon the type of converter which can be further classified [21] as follows.

There are 4 types of H-bridge converters.

- 1. Cascaded H-bridge.

- 2. Hybrid H-bridge.

- 3. Quasilinear.

- 4. New hybrid (ternary).

The summary of  $V_{in}(max)$ , no. of levels and maximum output voltage  $V_{out}(max)$  is described in table 1.3.

| Туре        | V <sub>in (max)</sub>              | V <sub>out (max)</sub>                 | No. of levels         |

|-------------|------------------------------------|----------------------------------------|-----------------------|

| Cascade     | V <sub>dc</sub>                    | SV <sub>dc</sub>                       | 28+1                  |

| Hybrid      | 2 <sup>s-1</sup> V <sub>dc</sub>   | (2 <sup>s</sup> -1)V <sub>dc</sub>     | 2 <sup>S+1</sup> -1   |

| Quasilinear | 2*3 <sup>s-2</sup> V <sub>dc</sub> | (3 <sup>s-1</sup> )V <sub>dc</sub>     | 2*3 <sup>s-1</sup> +1 |

| Ternary     | 3 <sup>s-1</sup> V <sub>dc</sub>   | ((3 <sup>s</sup> -1)/2)V <sub>dc</sub> |                       |

#### Table 1.3 Summary of different types of H-Bridge converters.

This configuration also possesses some advantages and disadvantages as well.

#### Advantages:

- Requires the least number of components among all multilevel converters to achieve the same number of voltage levels.

- Modularized circuit layout and packaging is possible because each level has the same structure, and there are no extra clamping diodes or voltage balancing capacitors.

- Soft-switching can be used in this structure to avoid bulky and lossy resistor-capacitordiode snubbers.

- The number of possible output voltage levels is more than twice the number of dc sources as shown in table 1.3.

- Stage with higher DC link voltage has

- > Lower number of commutations.

- Lower associated switching loss.

- Higher DC link voltage consists of lower switching frequency components.

- Lower DC link voltage consists of higher switching frequency components.

#### Disadvantages:

- Needs separate dc sources for real power conversions, and thus its applications are somewhat limited.

- Connecting separated dc sources between two converters in a back-to-back fashion is not possible because a short circuit will be introduced when two back-to-back converters are not switching synchronously.

## 1.7 Control Schemes:

The control strategy is the heart of any converter system to get the desired output results. It is mainly implemented in three sections as described further.

1. First section involves the sensing of variables being used in the scheme according to the applications. The sensed variables can be the input ac mains voltage, dc output voltage, input current and in some cases some additional variables are also sensed such as the capacitor voltage in the flying capacitor topology. For example in the control scheme of topology shown in figure 1.5 the sensed variables are input voltage, input current, output dc voltage and voltage Vc1 across the capacitor C1. The sensing of these variables involves different sensors.

2. Second section is the most important part of the whole scheme as it comprises the control algorithm which is responsible for the transient and steady state performance. The control algorithm is implemented through several controllers like PID or PI controller, sliding mode control high speed digital controllers, microcontrollers, DSP, application specific integrated circuits(ASIC) depending upon the rating, cost, customer requirements and types of converters. In some of the cases fuzzy logic controllers and neural network based controllers are employed to provide the fast dynamic response. Moreover, high-speed and high-accuracy microcontrollers and digital signal processors (DSPs) are available at reasonably low cost. Many processors are developed to give direct PWM outputs with fast software normally used in some of these converters, which reduces hardware drastically.

3. Third section involves the generating of the firing pulses for the switching devices which actually make any converter work. The output of the controllers used in the second section is obtained by the processing of the error difference between reference parameter and the sensed variable in the controller itself. This output generates the switching signals for the devices. Nowadays, processors are available which are developed only for power electronics applications and have dedicated PWM controllers as an inbuilt feature to implement concurrently all three stages of the control strategy for improving the transient and steady-state performance of these converters. For hardware, the firing pulses are being generated using FPGA tools and DSPs.

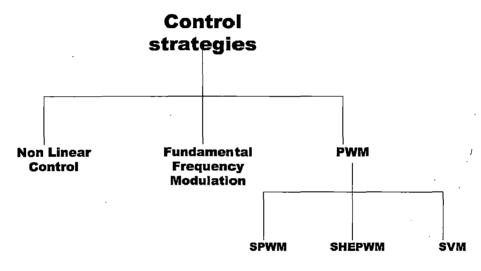

The control strategies for the multilevel power converters can be classified as shown in figure 1.7:

Fig. 1.12 Control strategies of MLCs.

- (a) Non linear control: This scheme is mainly applied to the single phase unidirectional converters due to the inherent non-linearity. The control decision is based on several factors such as magnitude of input voltage, voltage level in individual capacitors and current tracking requirement.

- (b) Fundamental frequency modulation: This modulation technique involves approximation of the required voltage waveform with the discrete voltage levels. Implementation of this scheme is computationally simple and several problems associated with high frequency

switching like EMI/RFI, losses etc are reduced. The main drawback is requirement of controllable dc bus to vary the magnitude of output voltage in inverters.

- (c) Pulse width modulation (PWM): Conventional two-level PWM techniques have been extended to MLCs with consistent results. These include space vector modulation (SVM), multilevel sinusoidal PWM (which has been mainly used in the topologies described in this work), selective harmonics elimination PWM (SHEPWM) and random PWM techniques. In most of the above topologies, PWM scheme is used.

- 1. *Sinusoidal PWM (SPWM):* In multilevel SPWM, multiple bands of carrier signals of high frequency (to achieve the spectral performance comparable to two level converters) are compared to sinusoidal command signal to achieve linear amplification. This sinusoidal command signal is synchronized with high frequency carrier wave. MLCs can operate in low modulation index region in several applications losing one or several levels to provide the required voltage magnitude.

- 2. Space Vector Modulation (SVM): This technique involves synthesis of required voltage vector from a number of voltage vectors corresponding to switching states. Nearest three vectors (NTV) algorithm synthesizes voltage vector from nearest three vectors and is found to be the optimal solution in synthesis of required voltage vector and excellent spectral quality. This control scheme is most common in three phase converters. Large redundancy in three level converters is utilized to maintain neutral point voltage balance and is an inherent part of SVM of multilevel converters. Use of SVM beyond three-level converters is computationally intensive and becomes impractical as number of levels increase. However, some generalized algorithms for SVM in MLCs with higher number of levels provide a less computationally intensive method for MLCs.

## 1.8 Literature Review:

**Ralph Teichmann and Steffen Bernet** presented a paper [7] giving the comparisons between two level and multilevel converters for low voltage applications, traction drives and utility applications. Another paper was presented showing the comparison between two level and multilevel converters for medium voltage applications [8].

**S.** Norrga presented the paper [22] on a bidirectional AC/DC converter for AC fed railway propulsion applications. This topology includes the soft switching of the devices. Many other industrial applications have been shown in the paper [23].

B.R. Lin, S.J. Huang and T.L. Hung presented the paper [24], on a novel single phase AC/DC converter with two PWM schemes including a hysteresis current control scheme. This paper showed that using a new topology with just three switches how a three level converter can be achieved with reduced THD. They have used a flying capacitor topology. B.R. Lin, T.L. Hung and C.H. Huang proposed a single phase half bridge rectifier [25] with capacitor clamp topology. The control scheme proposed here can also perform a shunt active power filter operation to eliminate the harmonic distortions in input source current and compensate the reactive power generated from the non-linear load. B.R. Lin, T.Y. Yang and K.T. Yang presented a paper [26] on a novel single phase half bridge rectifier. Topology comprises two power switches and two diodes. A carrier based current controller is used. B.R. Lin, Y.A. Ou and T.Y. Yang presented a paper [27] on a novel single phase unidirectional power flow rectifier to generate a three level PWM voltage waveform. No flying capacitor or clamping diode is used in this topology. B.R. Lin and C.H. Huang proposed a novel single phase AC/DC/AC converter [28] with capacitor clamped topology with a three leg configuration which has a common leg between AC/DC and DC/AC converters to reduce the number of switching devices compared with the conventional three level AC/DC/AC system.

Bhim Singh, Brij N. Singh, A. Chandra, Kamal Al-Haddad, Ashish Pandey, and Dwarka P. Kothari presented a review paper [12] on improved power quality AC/DC converters including boost, buck and buck-boost converters. In this paper advantages of multilevel converters are also

presented. Bhim Singh along with others also presented a review paper on multilevel AC/DC converters describing types of topologies, control strategies, applications and future scope as well in [13].

## 1.9 Objective of Dissertation work:

After presenting the literature review of multilevel converters over a period of years, we can give the objective of this dissertation work as follows:

- Studying features of multilevel rectifiers and its advantages over conventional two level and other topology rectifiers.

- Simulations of different topologies with sinusoidal PWM control scheme.

- Analysis of THDs for various loads and input power supply.

- FPGA based implementation of sinusoidal PWM scheme.

- Hardware development of one specific topology in the laboratory.

## 1.10 Organization of dissertation:

#### Chapter 1

This chapter gives the introduction to the multilevel rectifiers, its advantages over traditional rectifiers, its control schemes and literature review is also discussed.

#### Chapter 2

In this chapter, simulations of different multilevel rectifier topologies are carried out on MATLAB SIMULINK and study of THDs is analyzed with varying loads and input voltage supply.

#### Chapter 3

This chapter gives an overview of FPGA. Its origin, architecture, applications, design implementation and problems are discussed.

#### **Chapter 4**

In this chapter, the digital control and software implementation is carried out on SPARTAN 3 FPGA kit using Xilinx System Generator tool kit

#### Chapter 5

In this chapter, hardware implementation of a single topology is detailed and other hardware circuits are described.

## Chapter 6'

In this chapter, conclusions and future scope on multilevel rectifier are placed in this chapter.

# Chapter 2: Simulations study of Multilevel Converters

## 2.1Introduction:

In this chapter the simulations of different multilevel rectifier topologies implemented in MATLAB SIMULINK are presented. Topologies are presented one by one with their power circuit, control scheme, simulation results with R load and then RL load, steady state analysis, dynamic analysis and THD analysis.

## 2.2 Simulations of Multilevel Rectifier:

Multilevel rectifier topologies are simulated with R and RL loads by simple PWM control scheme.

One of the topologies is already been discussed in chapter 3, so we will start with the simulations of other topologies and previous topology will be presented at last. There are number of different topologies presented.

## 2.3 Topology 1:

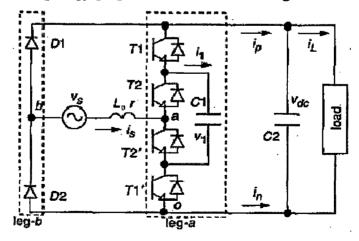

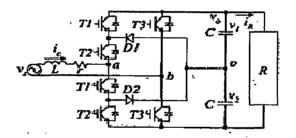

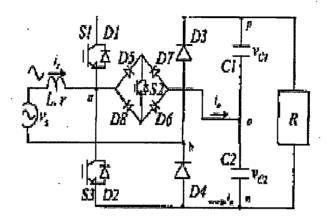

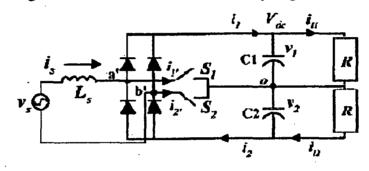

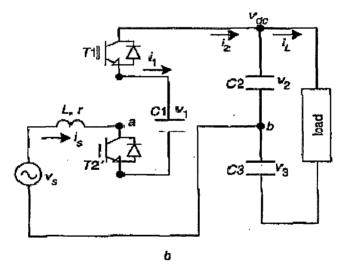

For following topologies the control scheme implements the hysteresis current control in the inner control loop. The first topology [19] is as shown below in figure 2.1.

## Fig. 2.1 Unidirectional three level rectifier with capacitor clamped scheme.

The control scheme block is shown in figure 2.2 below:

Fig. 2.2 Control block of above rectifier.

The control scheme uses a PI controller for the balancing of output DC voltage. The unit template is multiplied with the output of PI controller to give the reference input current which compares the actual input source current with itself and the error goes to the hysteresis current controller. This current tries to track the reference current due to the controller. PWM generator generates the firing pulses for the switching devices of the converter by the different combination of comparator outputs depending upon the direction and sign of input voltage and current.

#### 2.3.1 Simulation with R load:

The simulation parameters are varied with varying loads. Initially the parameters are as follows: Input AC voltage = 110V rms.

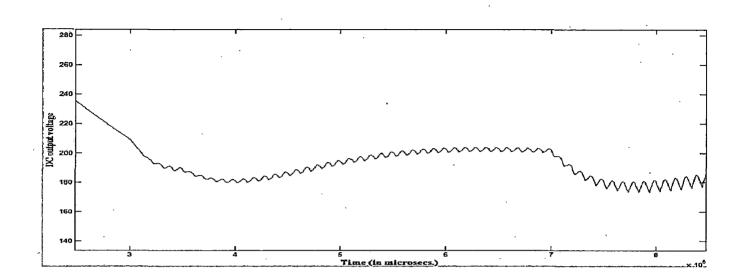

Output DC voltage = 200V.

Hysteresis Band = 0.5A.

R load = 1A.

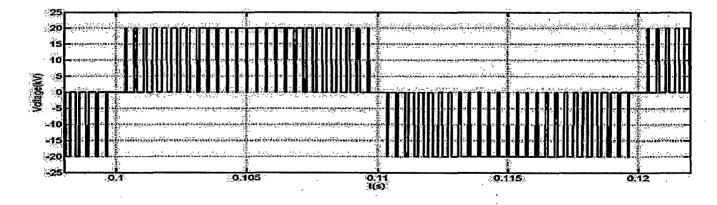

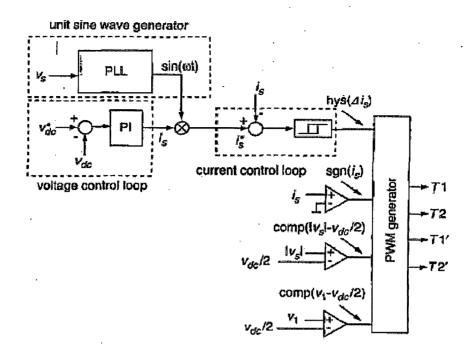

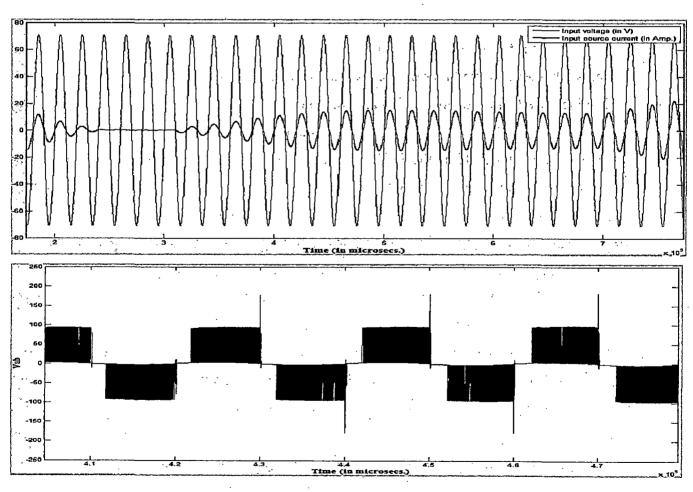

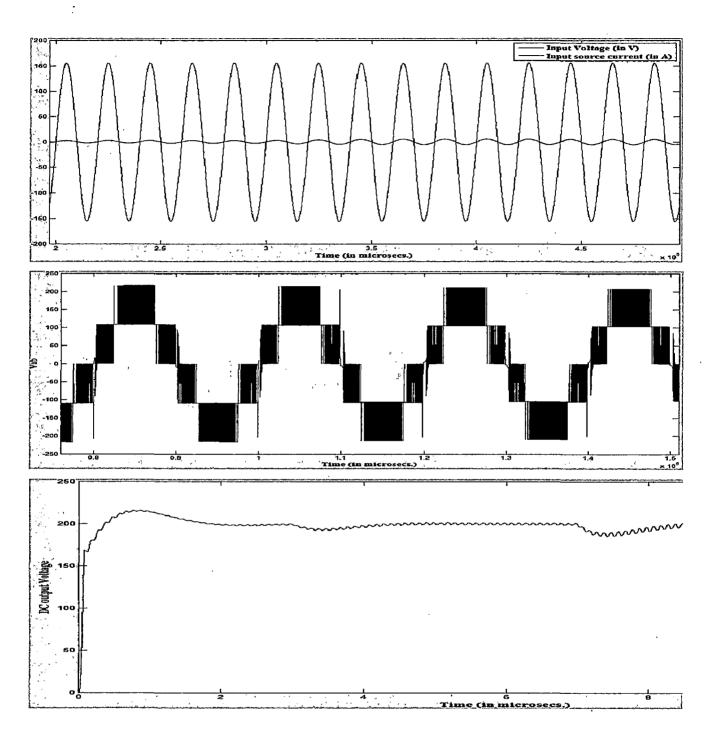

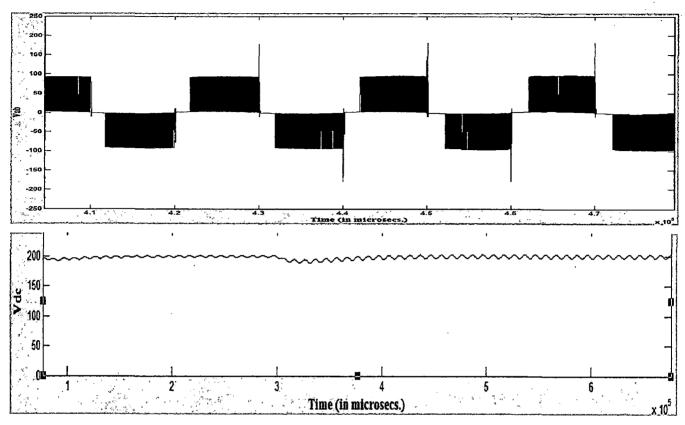

The simulation results for the steady state are shown in figure 2.3.

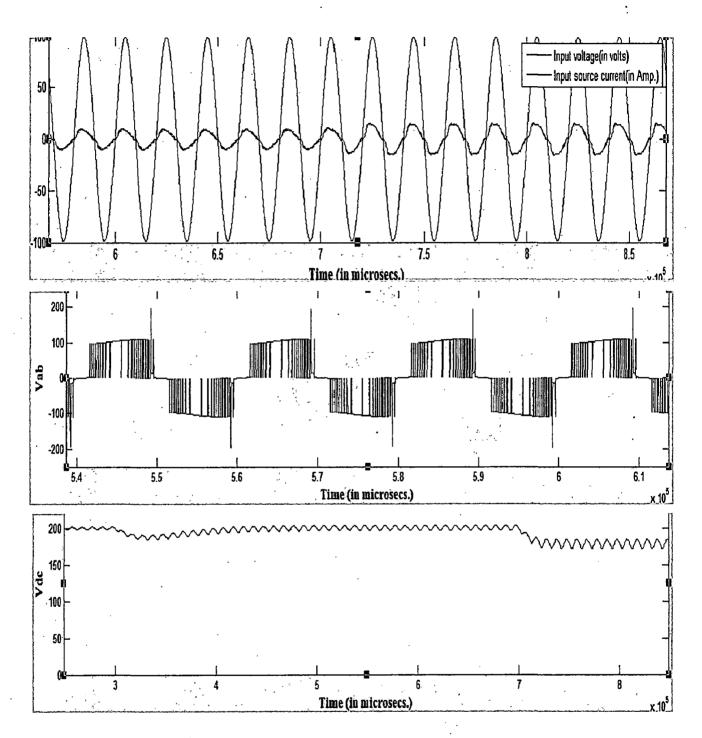

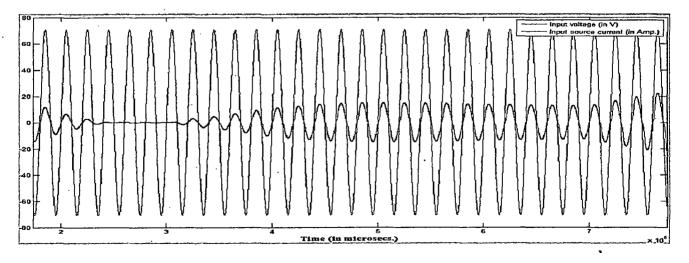

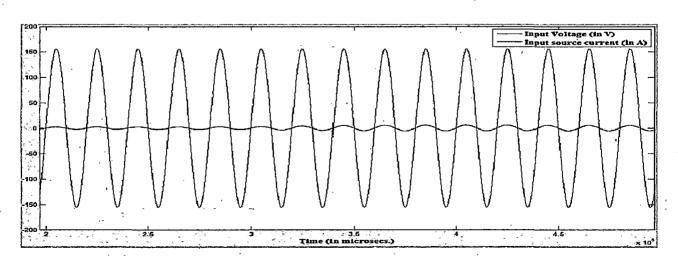

Fig. 2.3 Scope results for input voltage, input source current, three level voltages and DC output voltage.

The first scope window shows input voltage and input source current which are in phase with each other showing the power factor is nearly unity.

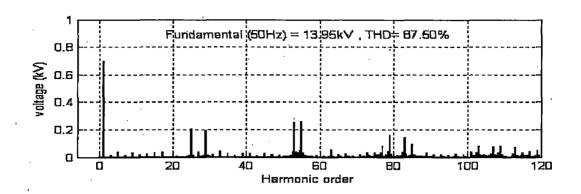

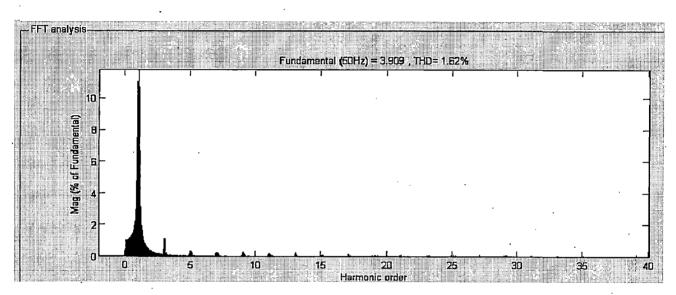

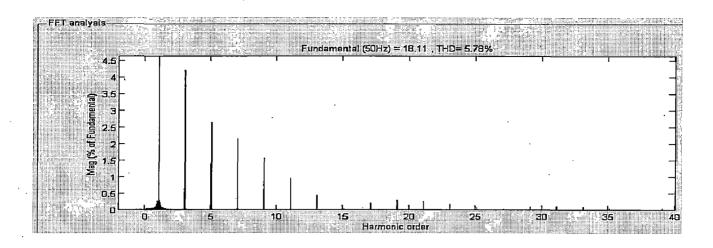

The FFT analysis shows the THD as 3.30% like shown in below figure 2.4.

Fig. 2.5 FFT analysis with load of 2A.

Now the simulation results with R load of 2A are nearly similar to those shown previously except that the input source current is increased and the DC output voltage is not much regulated (reason is explained further in conclusion). FFT analysis is shown in figure 2.5. Similarly the simulation results for 4A load current are shown but the FFT analysis is shown in figure 2.6.

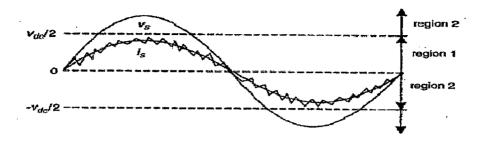

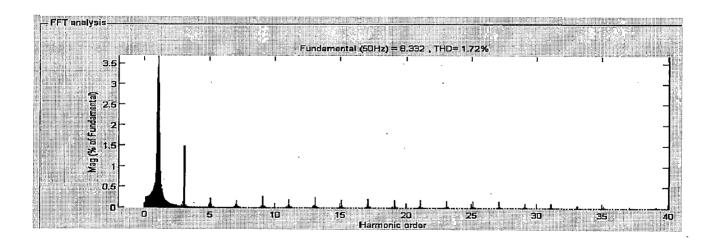

Note: THD of input source current only is talked about in this dissertation work. Now we will vary the input power supply and watch the results. Input power supply is 70V rms. The results are as shown in figure 2.7. This is called as dynamic state study of a converter.

.

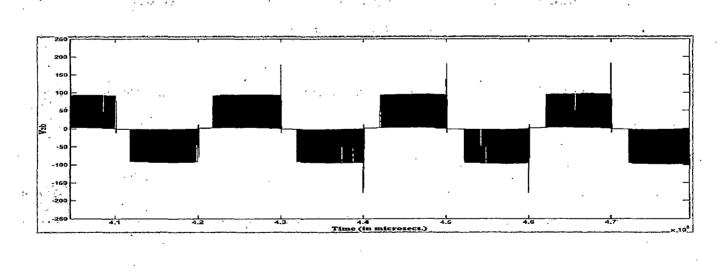

Fig. 2.7 Scope showing simulation results with input voltage, input source current, multilevel voltages and Dc output voltage.

As we can see that after reducing the supply voltage the level has decreased to two. The results of Vab shows that level of voltages on the AC side has decreased to two levels only. Input source current has increased significantly. This has a reason behind it. To generate a three-level voltage waveform on the AC side of the converter, the mains voltage must be less than the DC bus voltage and greater than half of the DC bus voltage. Two operating regions of mains voltage during one cycle of mains frequency are defined and shown in figure 2.8. In the first region, the instantaneous mains voltage is greater than -Vdc/2 and less than Vdc/2. Voltage levels 0 (low voltage level) and Vdc/2 (high voltage level) are generated on voltage Vab in the positive mains voltage to control the line current. During the negative mains voltage, voltage levels -Vdc/2 (low voltage level) and 0 (high voltage level) are selected to control the line current. In the second region, the absolute value of the mains voltage is less than the DC bus voltage Vdc but greater than half of the DC bus voltage Vdc/2. Voltage levels Vdc and Vdc/2 (or -Vdc and -Vdc/2) are generated during the positive (or negative) half-cycle of the mains voltage to control the line current. So, when input mains supply is reduced below the Vdc/2 value (keeping reference Vdc value constant) only region 1 is left for the operation of converter and hence the number of levels on AC side gets reduced. Thus, two such values are chosen for showing the difference. If the magnitude of Vs is reduced even below 70V, the results would be distorted more.

Fig. 2.8 Operating regions of a three level converter.

Fig. 2.9 FFT analysis with voltage 70V rms and load 1A.

Fig. 2.10 FFT analysis for 70V rms supply and load of 2A.

Fig. 2.11 FFT analysis for 70V rms supply and load of 4A.

Now we can summarize the above study of THDs with varying loads and input power supply as shown in table 2.1.

| Input Voltage (rms) | Load current (A) | THD (%) |

|---------------------|------------------|---------|

| 110                 | 1                | 3.30    |

| 110                 | 2                | 2.61    |

| 110                 | 4                | 2.87    |

| 70                  | 1                | 1.62    |

| 70                  | 2                | 1.72    |

| 70                  | 4                | 5.78    |

Table 2.1 Summary of THDs with varying load and supply voltage.

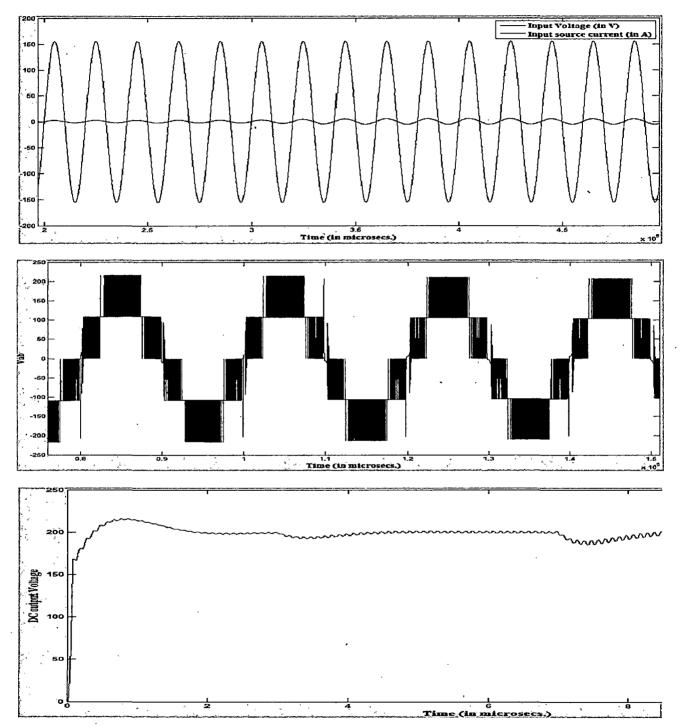

#### 2.3.2 Simulations with RL load:

The topology shown in figure 2.1 is analyzed here with RL load in place of R load. Now the parameters are as given below. Load would be varied for different span of time.

Input voltage = 110V

DC output voltage = 200V

R load = 1A, 2A and 4A.

L load = 5mH, 3mH and 10mH.

Simulation results are shown in figure 2.12.

| Input voltage (V) | Load current (A) | THD (%) |

|-------------------|------------------|---------|

| 110               | 1                | 2.87    |

| 110               | 2                | 2.52    |

| 110               | 4                | 2.82    |

| 50                | 1                | 10.52   |

| 50                | 2                | 5.19    |

| 50                | 4                | 13.25   |

#### Table 2.2 Summary of THDs with RL load.

#### 2.3.3 Conclusions:

From the table 2.2 we can analyze that after adding an inductive load in series with a resistive load there is not much change in the THD of input source current because of following reason: This is an AC/DC converter and at the output end there are capacitors which get charged completely to a fixed voltage so there is hardly any change in the load current when we add inductor to the resistor already added previously. Hence, we can say that there is no need for the simulation results of other topologies.

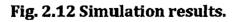

## 2.4 Topology 2:

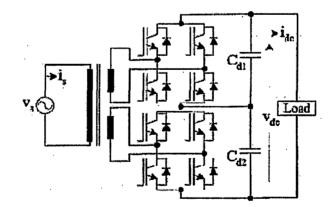

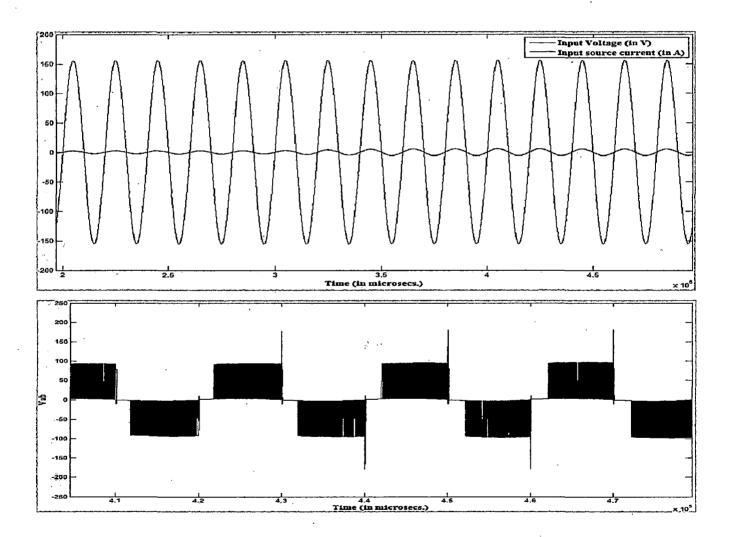

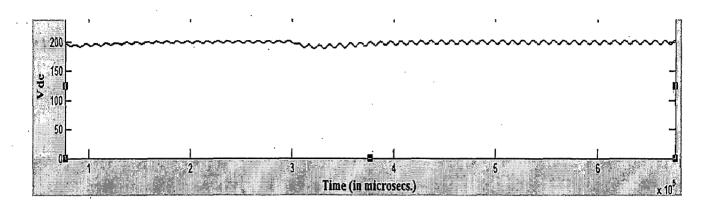

The second topology is the unidirectional diode clamped rectifier [29] which is as shown in figure 2.13. From now on only the resistive load is considered for all topologies. First the simulation results are shown for two level voltages where the control scheme produces the firing pulses for T1 and T2 exactly same and those for T1' and T2' exactly same.

The control scheme is similar to that shown in figure 2.2 except for the PWM generator which generates firing pulses for the rectifier since every topology has different sets of firing pulses. The simulation results for the following parameters are shown in figure 2.14.

Input power supply = 110V rms.

DC output voltage = 200V

R load = 1A, 2A, 4A respectively on same scope window so as to distinguish properly.

Fig. 2.14 Simulation results.

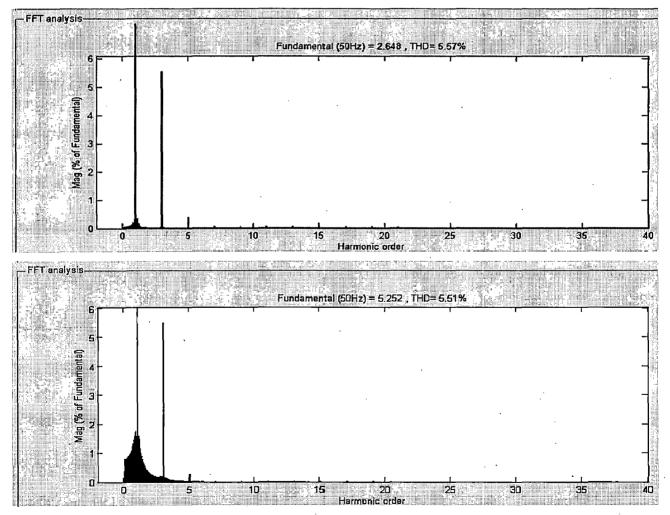

The simulation result for the input source current shows that it is increasing with increasing load current and DC output voltage is more rippled with increasing load current. Figure 2.15 shows the FFT analysis with varying loads of 1A, 2A and 4A respectively for 110V supply.

Fig. 2.15 FFT analysis for loads of 1A, 2A and 4A respectively.

The figure 2.16 shows the FFT analysis for loads of 1A, 2A and 4A respectively for 70V input voltage.

35

Fig. 2.16 FFT analysis for loads of 1A, 2A and 4A respectively with 70V rms.

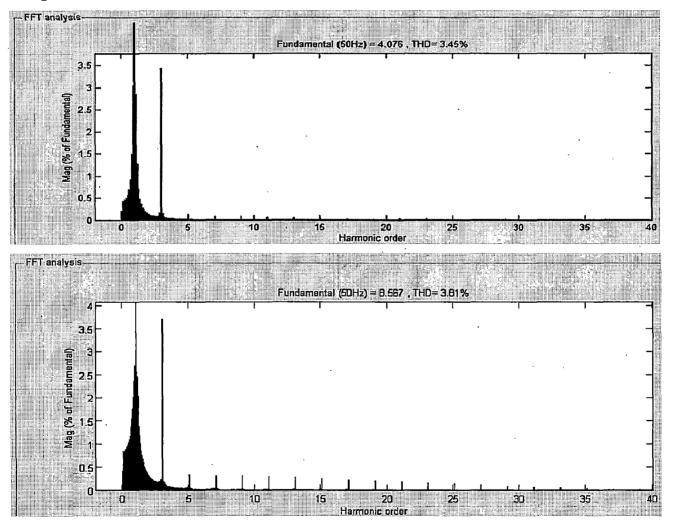

| Input Voltage (V rms) | Load Current (A) | THD(%) |

|-----------------------|------------------|--------|

| 110                   | 1                | 5.57   |

| 110                   | 2                | 5.51   |

| 110                   | 4                | 5.69   |

| . 70                  | 1                | 3.45   |

| 70                    | 2                | 3.81   |

| 70                    | 4                | 7.40   |

Table 2.3 Summary of THDs with varying load and power supply.

Now we will see the simulation results for three level voltages for same topology with same control scheme but different firing pulses resulting in more number of voltage levels. We will follow the same sequence of supply and load for the convenience and simplicity. Again the parameters such as output voltage are same as earlier.

Fig. 2.17 Simulation results for three level voltages.

Now the simulation results for 50V rms supply is as shown in figure 2.18.

#### Fig. 2.18 Simulation results for supply of 50V.

In this case we can see that as we decreased the input supply keeping other parameters same as earlier, the output DC voltage is more rippled with decreased stiffness with increasing load. Level of voltages has also almost decreased to two with a kind of distortion in current waveform. Now we will summarize the THDs in table 2.4.

| Input Voltage (V) | Load current (A) | THD (%) |

|-------------------|------------------|---------|

| 110               | 1                | 7.73    |

| 110               | 2                | 9.37    |

| 110               | 4                | 11.52   |

| 50                | 1                | 9.06    |

| 50                | 2                | 15.02   |

| 50                | 4                | 20.88   |

#### Table 2.4 THDs with varying load and input supply.

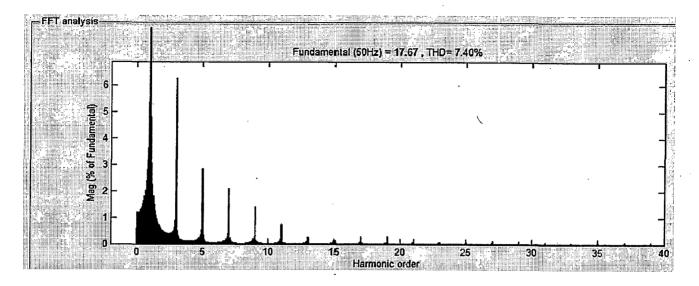

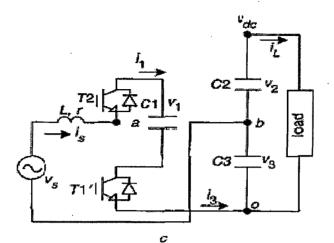

## 2.5 Topology 3:

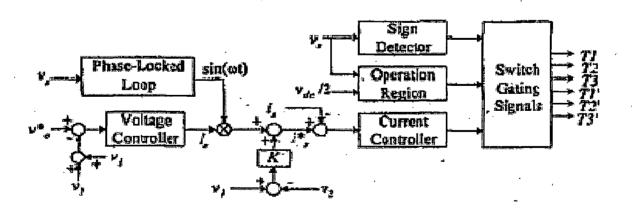

Next is bidirectional converter topology with neutral point clamped [30] as shown in figure 2.19. The control scheme used for this topology is shown in figure 2.20. In next figure (2.21) simulation results for steady state are also shown with following parameters: Input voltage supply = 110V, DC output voltage = 200, Load R = 1A, 2A and 4A.

Fig. 2.19 Converter topology with neutral point clamped.

Fig. 2.20 Control block of above rectifier.

Fig. 2.21 Simulation results with three level for 110V supply.

Fig. 2.22 Simulation results with 70V supply.

As we can see that the voltage levels have reduced. We can now see the summary of THDs with both varying loads and input supply in table 2.5.

| Input voltage (V) | Load current (A) | THD (%) |

|-------------------|------------------|---------|

| 110               | 1                | 4.92    |

| 110               | 2                | 4.93    |

| 110               | 4                | 5.60    |

| 70                | 1                | 5.71    |

| 70                | 2                | 6.97    |

| 70                | 4                | 10.79   |

#### Table 2.5 Summary of THDs with varying loads and power supply.

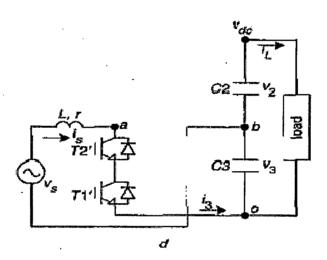

## 2.6 Topology 4:

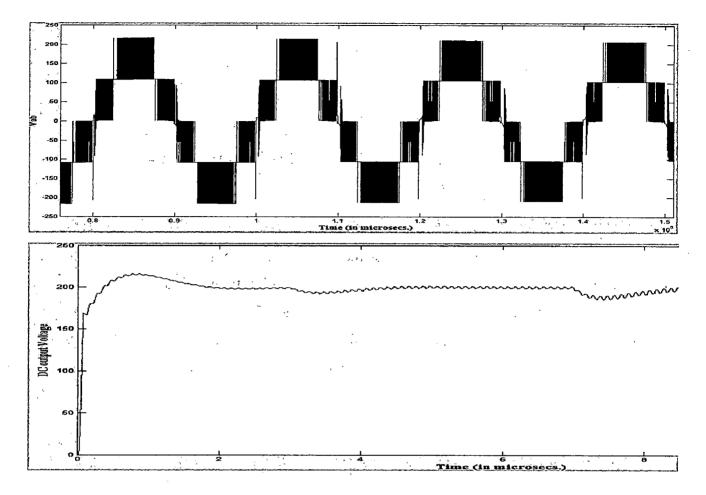

Fig. 2.23 Power circuit of neutral clamped AC/DC converter.

This is the fourth topology shown in figure 2.23 [24] with three switches and a diode bridge clamped in between. This topology can generate two level voltages and three level voltages as well. The simulations results are exactly same as seen for earlier topologies with two level and three level control schemes for following parameters: Input supply = 110V and 50V both, Output DC voltage = 200V and Load R = 1A, 2A and 4A. We can see the summary in table 2.6 and table 2.7 for two level and three level voltages respectively for THDs.

| Input Supply (V) | Input Supply (V) Load current (A) |       |

|------------------|-----------------------------------|-------|

| 110              | 1                                 | 5.70  |

| 110              | 2                                 | 5.56  |

| 110              | 4                                 | 5.77  |

| 50               | 1                                 | 2.66  |

| 50               | 2                                 | 6.09  |

| 50               | 4                                 | 14.27 |

Table 2.6 Summary of THDs for two level voltages.

| Input supply (V) | Load current (A) | THD (%) |

|------------------|------------------|---------|

| 110              | 1                | 5.40    |

| 110              | 2                | 5.01    |

| 1 | 10 |                                       | 4 | 5.56      |  |

|---|----|---------------------------------------|---|-----------|--|

| 5 | 0  | · ·                                   | 1 | 2.45      |  |

| 5 | 0  |                                       | 2 | 5.59      |  |

| 5 | 0  | · · · · · · · · · · · · · · · · · · · | 4 | <br>10.25 |  |

#### Table 2.7 Summary of THDs for three level voltages.

Charle.

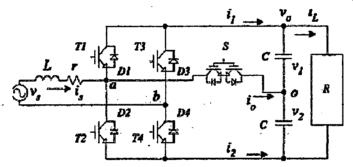

## 2.7 Topology 5:

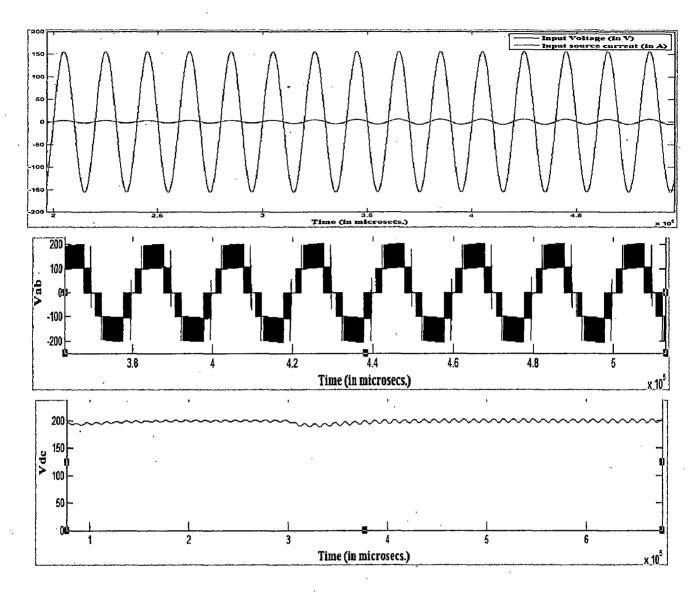

Next topology is the full bridge three level rectifier [31]. The power circuit (shown in figure 2.24) comprises a conventional full bridge rectifier in addition to an AC power switch which is built with two unidirectional switches connected in series. This topology also uses the simple PWM control scheme as used in previous topologies. The simulations results for the parameters as given below are shown in figure 2.25. Parameters are: Input mains voltage = 110V, DC output voltage = 200V, Load current = 1A, 2A, 3A and 5A.

Fig. 2.24 Power circuit of a three level rectifier.

Fig. 2.25 Simulation results showing Input mains voltage, input source current, three level voltages and DC output voltage.

If we decrease the input mains voltage to 50V, the number of level will reduce to two and stiffness of the DC output voltage also decreases significantly as load increases.

| Input Voltage (V) | Load current (A) | THD (%)   |  |

|-------------------|------------------|-----------|--|

| 110               | 1                | 4.80      |  |

| 110               | 2                | 4.82      |  |

| , 110             | 3                | 5.11 5.94 |  |

| 110               | 5                |           |  |

| 50                | 1                | 4.97      |  |

| 50                | 2                | 8.64      |  |

| 50 | 3 | 12.7  |

|----|---|-------|

| 50 | 5 | 19.74 |

Table 2.8 Summary of THDs.

## 2.8 Topology 6:

Next topology is a single phase bridge rectifier [32] comprising a diode bridge and two power switches. Its power circuit is as shown in figure 2.26. This topology also uses the same control scheme as mentioned earlier. The simulation results for the parameters as used in other topologies are shown in figure 2.27. Then a table of summary is given in table 2.9.

Fig. 2.26 Power circuit.

Fig. 2.27 Simulation results showing input voltage, input current, two level voltages and DC output voltage.

| Input voltage (V) | Load current(A) | THD in input source |

|-------------------|-----------------|---------------------|

|                   |                 | current(%)          |

| 110               | 1               | 2.68                |

| 110               | 2               | 2.84                |

| 110               | 4               | 3.33                |

| 50                | 1               | 2.96                |

| 50                | 2               | 5.36                |

| 50                | 4               | 10.98               |

Table 2.9 Summary of THDs of input source current.

## 2.9 Topology 7: